嵌入式Flashmemory技术简介及工作原理

Flash存储芯片工作原理

Flash存储芯片工作原理Flash存储芯片是一种非易失性存储器,广泛应用于各种电子设备中,如个人电脑、手机、相机等。

它的工作原理是基于电荷积累和擦除的原理,具有高速、低功耗和可擦写的特点。

Flash存储芯片由一系列的存储单元组成,每一个存储单元可以存储一个或者多个位的数据。

每一个存储单元由一个浮动栅和控制栅组成,它们之间通过绝缘层隔开。

根据电荷积累与否来表示存储的数据。

Flash存储芯片的工作过程可以分为写入、读取和擦除三个主要步骤。

1. 写入:写入操作是将数据存储到Flash存储芯片中的过程。

首先,将待写入的数据通过控制电路传输到Flash存储芯片中的写入缓冲区。

然后,控制电路根据写入地址将数据传输到相应的存储单元中。

在写入过程中,控制电路会在浮动栅上施加一定的电压,使得电荷能够积累在浮动栅上,从而改变存储单元的电荷状态,表示存储的数据。

2. 读取:读取操作是从Flash存储芯片中获取存储的数据的过程。

当读取请求到达时,控制电路会根据读取地址找到相应的存储单元,并将存储单元中的电荷状态转换为电压信号。

这些电压信号经过放大和解码处理后,最终被传输到输出缓冲区,供外部设备读取。

3. 擦除:擦除操作是将存储单元中的数据清除的过程。

由于Flash存储芯片的存储单元只能进行整体擦除,所以在擦除操作中,需要将整个块或者扇区的数据都清除。

擦除操作需要施加较高的电压,以清除存储单元中的电荷,使其恢复到初始状态。

Flash存储芯片的特点和优势:1. 高速:Flash存储芯片的读取速度较快,可以满足多种应用的要求。

2. 低功耗:Flash存储芯片在读取和写入操作时的功耗较低,有助于延长电池寿命。

3. 高可靠性:Flash存储芯片不受电源中断的影响,存储的数据不会因为断电而丢失。

4. 高密度:Flash存储芯片可以实现较高的存储密度,满足不同应用的存储需求。

5. 可擦写:Flash存储芯片可以多次擦写,具有较长的使用寿命。

flash存储器原理

flash存储器原理Flash存储器原理。

Flash存储器是一种非易失性存储器,它使用了一种称为闪存的技术,可以在断电后仍然保持数据。

它通常用于嵌入式系统、移动设备和存储卡等产品中。

Flash存储器的原理非常复杂,它涉及到许多物理和电子学的知识。

在本文中,我们将深入探讨Flash存储器的原理,帮助读者更好地理解这一技术。

Flash存储器的工作原理主要基于两种不同的技术,NAND和NOR。

NAND和NOR是两种不同的存储单元结构,它们分别适用于不同的应用场景。

NAND适用于大容量、高速度的存储,而NOR适用于低容量、低速度的存储。

这两种技术都是基于晶体管的工作原理,但它们的结构和工作方式有所不同。

NAND存储器是一种串行存储器,它使用了串行连接的晶体管结构来存储数据。

NAND存储器的每个存储单元都是一个晶体管,通过控制晶体管的导通和截断来实现数据的读写操作。

NAND存储器的存储密度很高,可以存储大量的数据,因此被广泛应用于固态硬盘和存储卡等产品中。

NOR存储器是一种并行存储器,它使用了并行连接的晶体管结构来存储数据。

NOR存储器的每个存储单元都是一个晶体管,通过控制晶体管的导通和截断来实现数据的读写操作。

NOR存储器的读取速度比NAND存储器快,但存储密度较低,因此适用于低容量、低速度的存储需求。

除了NAND和NOR存储器,还有一种称为EEPROM的存储器技术,它是一种可擦除可编程只读存储器。

EEPROM存储器可以通过电子擦除操作来擦除存储的数据,然后再进行编程操作来写入新的数据。

EEPROM存储器的擦除和编程操作都是通过电子信号来实现的,因此它是一种非易失性存储器。

总的来说,Flash存储器的原理涉及到晶体管的工作原理、存储单元的结构和连接方式,以及擦除和编程操作的实现方式。

通过深入理解这些原理,我们可以更好地应用Flash存储器技术,设计出更加高效、可靠的存储产品。

希望本文对读者有所帮助,谢谢阅读!。

嵌入式Flashmemory技术简介及工作原理

嵌入式Flashmemory技术简介及工作原理1概述随着数码时代的来临,除了PC外,越来越多的数码信息产品正在或即将进入我们的家庭:移动电话、掌上电脑、数码相机、GPS等等,这些产品越来越多的使用各种移动微存储器。

这些存储器中很大部分是快闪存储器(FlashMemory)。

Flashmemory是从EPROM和EEPROM发展而来的非挥发性存储集成电路,其主要特点是工作速度快、单元面积小、集成度高、可靠性好、可重复擦写10万次以上,数据可靠保持超过10年。

国外从80年代开始发展,到2002年随着数码时代的来临,除了PC外,越来越多的数码信息产品正在或即将进入我们的家庭:移动电话、掌上电脑、数码相机、GPS等等,这些产品越来越多的使用各种移动微存储器。

这些存储器中很大部分是快闪存储器(Flash Memory)。

Flash memory是从EPROM和EEPROM发展而来的非挥发性存储集成电路,其主要特点是工作速度快、单元面积小、集成度高、可靠性好、可重复擦写10万次以上,数据可靠保持超过10年。

国外从80年代开始发展,到2002年,Flash memory的年销售额超过一百亿美元,并增长迅速,预计到2006年,年销售额可达126亿美元/年。

到目前,用于Flash memory生产的技术水平已达0.13μm,单片存储量达几千兆。

除大容量存储器应用外,Flash Memory也大量地替代EPROM、EEPROM嵌入到ASIC、CPU、DSP电路中,如TI公司的TMS320F240系列、TMS280系列分别含有8K―128K Words的Flash Memory,又如Microchip公司,也推出了内嵌Flash Memory的16F系列MCU产品。

Flash Memory电路芯片设计的核心是存储单元(Cell)设计(包括结构、读写擦方式),外围电路都是围绕其设计。

因此,我们首先要研究并确定电路中采用的Flash Memory Cell。

Flash Memory

typically 5s

Multi Layer Cell Flash

MLC Flash characteristics

The application of Flash Memory

the 32GB SanDisk microSDHD面向智能手机市场, 采用第3代32nm工艺。 3-bit-per-cell NAND flash technology.

2Gb Nor Flash Memory

AMD与富士通公司将各自的NOR闪存业务剥离出来,成 立了合资公司Spansion

Apple-Nanຫໍສະໝຸດ Flash 最大买家

苹果发布2010年第四财季财报, 营收203.4亿美元,同比增67%, 利润44.6亿美元,同比增70%。 iPhone 销量1410万部,同比涨 91.4%; Mac电脑销量389万台,同比涨 27.4%; iPod销量905万部,同比跌11%; iPad销量419万台,环比涨28.4%。

NAND Flash

Nand Flash 阵列结构

Why named NAND?

Nand Flash 擦写方式

Fowler -Nordheim (FN) tunneling. Nand 擦除写入均采用FN 沟道效应。

2Gb Nand Flash

Nor vs Nand

typically 4ms

ipad

iphone 4

Thank you!

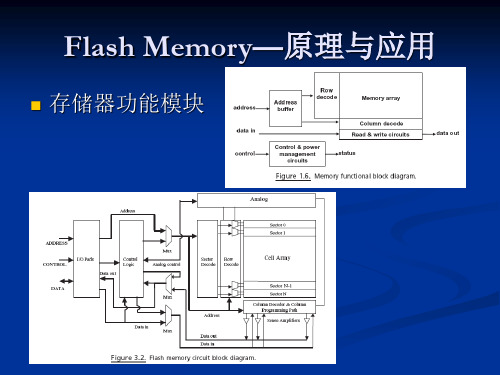

Flash Memory—原理与应用

存储器功能模块

基本单元

信息存储方式

Flash Memory 分类

按读写及擦除方式

Flash存储芯片工作原理

Flash存储芯片工作原理Flash存储芯片是一种常见的非易失性存储器,广泛应用于各种电子设备中,如手机、相机、电脑等。

它具有高速读写、低功耗和可擦写的特点,因此备受青睐。

本文将详细介绍Flash存储芯片的工作原理。

Flash存储芯片是由一系列的存储单元组成的,每一个存储单元可以存储一个或者多个二进制位的数据。

这些存储单元被组织成一个二维的阵列,每一个存储单元都有一个惟一的地址,通过地址可以访问和操作存储单元中的数据。

Flash存储芯片的工作原理可以分为读取和写入两个过程。

1. 读取过程:当需要读取Flash存储芯片中的数据时,首先需要提供要读取的存储单元的地址。

然后,控制电路会根据地址找到对应的存储单元,并将存储单元中的数据读取出来。

读取的数据会被传输到输出缓冲区中,然后通过总线传输给外部设备。

2. 写入过程:当需要向Flash存储芯片中写入数据时,首先需要提供要写入的存储单元的地址。

然后,控制电路会根据地址找到对应的存储单元,并将要写入的数据存储到该存储单元中。

写入数据时,需要先将存储单元中原有的数据擦除,然后再写入新的数据。

这是因为Flash存储芯片的存储单元是非易失性的,惟独在擦除之后才干写入新的数据。

Flash存储芯片的擦除和写入操作是通过电子擦除和编程来实现的。

电子擦除是指通过加高电压来改变存储单元中的电荷状态,从而擦除存储单元中的数据。

编程是指通过加高电压来改变存储单元中的电荷状态,从而写入新的数据。

Flash存储芯片中的存储单元通常被组织成扇区或者块的形式。

每一个扇区或者块都有一个擦除单元,擦除单元是最小的可擦除单元,通常是64KB或者128KB。

在写入数据时,如果只需要修改存储单元中的一部份数据,则需要先将整个扇区或者块擦除,然后再将新的数据写入。

Flash存储芯片的工作原理还涉及到了读写保护机制。

通过设置相应的控制位,可以实现对存储单元的读写保护。

这样可以避免误操作或者未经授权的访问对存储单元中的数据造成破坏。

Flash存储芯片工作原理

Flash存储芯片工作原理Flash存储芯片是一种非易失性存储器,广泛应用于各种电子设备中,如手机、平板电脑、相机等。

Flash存储芯片工作原理是通过电子擦除和写入的方式来存储和读取数据。

本文将详细介绍Flash存储芯片的工作原理。

一、Flash存储芯片的基本结构Flash存储芯片由一系列的存储单元组成,每一个存储单元称为一个位或者一个存储单元。

每一个存储单元可以存储一个或者多个位的数据。

Flash存储芯片通常由多个存储单元组成一个块,多个块组成一个扇区,多个扇区组成一个芯片。

每一个存储单元由一个栅极、源极和漏极组成,通过改变栅极和源极之间的电荷量来存储数据。

二、Flash存储芯片的工作原理1. 读取数据Flash存储芯片的读取操作是通过检测存储单元中的电荷量来实现的。

当读取一个存储单元时,控制电路会将读取命令发送给芯片,并选择要读取的存储单元。

芯片会将选定的存储单元的电荷量读取出来,并转换为相应的数字信号,然后将这些信号传输给控制电路进行处理。

最后,控制电路将处理后的数据发送给主机设备。

2. 写入数据Flash存储芯片的写入操作是通过改变存储单元中的电荷量来实现的。

当写入一个存储单元时,控制电路会将写入命令发送给芯片,并选择要写入的存储单元。

芯片会将写入的数据转换为相应的电荷量,并将其存储到选定的存储单元中。

写入操作通常需要先将存储单元中的电荷量擦除为初始状态,然后再写入新的数据。

3. 擦除数据Flash存储芯片的擦除操作是通过将存储单元中的电荷量擦除为初始状态来实现的。

擦除操作通常是以块为单位进行的,即一次擦除一个块的数据。

在擦除操作之前,需要先将要擦除的块中的数据读取出来并保存,然后再进行擦除操作。

擦除操作是通过向存储单元中加入高电压来实现的,这会导致存储单元中的电荷量被彻底清除。

三、Flash存储芯片的特点1. 非易失性存储器:Flash存储芯片是一种非易失性存储器,即在断电情况下也能保持存储的数据。

电脑芯片制造中的嵌入式存储器分析

电脑芯片制造中的嵌入式存储器分析电子产品的不断进步和发展,使得人们对嵌入式系统的需求越来越高。

嵌入式存储器作为电子产品的核心部件,起到了存储和处理数据的关键作用。

本文将对电脑芯片制造中的嵌入式存储器进行深入分析。

一、嵌入式存储器的概述嵌入式存储器是一种集成在芯片内部的存储单元,其具有高速读写、体积小、功耗低等特点。

它广泛应用于各类电子设备中,如智能手机、平板电脑、数码相机等。

目前,主流的嵌入式存储器有SRAM(静态随机存取存储器)、DRAM(动态随机存取存储器)和闪存(Flash Memory)。

二、SRAM的特点与应用SRAM是一种以电容作为存储单元的存储器,具有读写速度快、写入稳定等特点。

由于其体积较大,通常应用于需要频繁读写的场合,如高速缓存存储器和寄存器文件等。

三、DRAM的特点与应用DRAM是一种以电容和晶体管组成的存储单元,具有体积小、成本低等特点。

然而,由于电容的电荷衰减问题,DRAM需要不断刷新以保持数据的一致性。

因此,它主要应用于主存储器等容量较大、读写操作相对较少的场合。

四、闪存存储器的特点与应用闪存是一种非易失性存储器,可以在断电后仍保存数据,具有体积小、功耗低等优点。

它广泛应用于移动设备和嵌入式系统中,如固态硬盘、MP3播放器等。

五、嵌入式存储器的制造工艺嵌入式存储器的制造工艺是一个复杂的过程,它主要包含以下几个环节:掩膜制备、曝光、蚀刻、沉积和电镀等。

其中,掩膜制备是制造过程的核心环节,它通过特殊的光刻技术将芯片表面进行图案处理,形成存储单元。

六、嵌入式存储器的未来发展随着科技的不断进步,嵌入式存储器在容量、速度、功耗等方面还有很大的提升空间。

未来,随着人工智能、物联网等领域的发展,对嵌入式存储器的需求将不断增加。

因此,研发更具性能优势的嵌入式存储器将成为制造商的重要任务。

总结:在电脑芯片制造中,嵌入式存储器作为核心部件,起到了存储和处理数据的关键作用。

本文从嵌入式存储器的概述、SRAM、DRAM、闪存的特点与应用、制造工艺以及未来发展等方面进行了分析。

mtd原理

mtd原理MTD原理。

MTD(Memory Technology Device)是一种基于Flash技术的存储设备,它可以被用于嵌入式系统中作为存储介质。

MTD原理是指MTD设备的工作原理和内部结构,了解MTD原理对于开发嵌入式系统和进行存储设备驱动程序的编写非常重要。

首先,我们来看一下MTD的内部结构。

MTD设备通常由Flash芯片、控制器和接口组成。

Flash芯片是存储介质,可以分为NOR Flash和NAND Flash两种类型。

NOR Flash适合做代码存储,因为它具有较快的读取速度和较低的擦写次数限制;而NAND Flash适合做数据存储,因为它具有较高的存储密度和较低的成本。

控制器负责管理Flash芯片的读写操作,包括擦除、编程和检查状态等功能。

接口则是控制器和主机系统之间的通信接口,可以是各种总线接口,如SPI、NAND Flash接口等。

MTD设备的工作原理主要包括擦除、编程和读取三个基本操作。

擦除是将Flash芯片中的数据全部清空,使其恢复到初始状态,以便进行新的数据编程。

编程是将数据写入Flash芯片中,而读取则是将数据从Flash芯片中读取出来。

这三个基本操作是MTD设备的核心功能,也是存储设备驱动程序中需要实现的功能。

在嵌入式系统中,MTD设备通常被用于存储文件系统、内核镜像、根文件系统等重要数据。

因此,对MTD设备的管理和操作具有重要意义。

在Linux系统中,MTD设备的管理和操作是通过MTD子系统来实现的。

MTD子系统提供了一组API接口,可以让应用程序和驱动程序对MTD设备进行读写操作。

同时,MTD子系统还提供了一些工具和命令,可以用于对MTD设备进行格式化、擦除、编程等操作。

总的来说,MTD原理是关于MTD设备的工作原理和内部结构的知识,它对于开发嵌入式系统和进行存储设备驱动程序的编写非常重要。

通过了解MTD原理,我们可以更好地理解MTD设备的工作机制,从而更好地应用和管理MTD设备。

flash存储器

Flash存储器1. 简介Flash存储器是一种非易失性存储设备,常用于嵌入式系统和移动设备中。

与传统的硬盘驱动器相比,Flash存储器具有更快的访问速度,更低的能耗和更高的可靠性。

Flash存储器采用闪存技术,利用电子存储介质存储数据,无需机械运动。

本文将详细介绍Flash存储器的特点、工作原理和应用领域。

2. 特点2.1 非易失性Flash存储器是一种非易失性存储设备,意味着即使在断电情况下,存储在Flash存储器中的数据仍然可以保持不变。

这使得Flash存储器非常适合用于存储关键数据,如操作系统、固件和配置文件。

2.2 快速访问Flash存储器具有较快的访问速度,因为它无需机械运动。

与传统的硬盘驱动器相比,Flash存储器具有更短的延迟时间,从而可以实现更快的数据读写操作。

2.3 低能耗Flash存储器的能耗较低,这是由于它没有移动部件。

相比之下,传统硬盘驱动器需要消耗大量的能量来驱动机械运动。

因此,在移动设备或嵌入式系统中,Flash存储器可以延长电池寿命并提高能源效率。

2.4 高可靠性Flash存储器具有较高的可靠性,可以承受更多的物理冲击和振动而不会损坏数据。

这是因为Flash存储器使用了固态电路而不是机械部件。

此外,Flash存储器还具有较长的寿命,可以进行大量的擦除和写入操作而不会出现性能下降。

3. 工作原理Flash存储器使用了一种称为闪存的技术来存储数据。

闪存是一种基于非挥发性快闪电子存储原理的存储器,它可以在断电情况下保持数据的完整性。

Flash存储器由一个或多个存储单元组成,每个存储单元由一个晶体管和一个电容器构成。

Flash存储器的工作原理可以分为写入和擦除两个过程。

当需要写入数据时,Flash控制器将电荷存储在存储单元的电容器中。

通过施加一个较高的电压,数据可以写入存储单元。

而当需要擦除数据时,Flash控制器会将存储单元中的电容器进行放电,从而擦除数据。

需要注意的是,Flash存储器的擦除操作是以块为单位进行的。

Flash存储芯片工作原理

Flash存储芯片工作原理Flash存储芯片是一种非易失性存储器,广泛应用于各种电子设备中,如手机、平板电脑、相机等。

它具有高速读写、低功耗、体积小等优点,成为现代电子产品中重要的存储介质之一。

本文将详细介绍Flash存储芯片的工作原理。

一、Flash存储芯片的基本结构Flash存储芯片由多个存储单元组成,每一个存储单元可以存储一个或者多个比特的数据。

它的基本结构包括控制器、存储单元阵列和I/O接口。

1. 控制器:控制器是Flash存储芯片的核心部份,负责管理存储单元的读写操作。

它包含了存储单元的地址解码器、数据缓存、错误检测和纠正等功能模块。

2. 存储单元阵列:存储单元阵列是Flash存储芯片中存储数据的地方。

每一个存储单元由一个浮栅电容和一个控制栅组成。

通过在浮栅电容中注入或者释放电荷,可以改变存储单元的电荷状态,从而实现数据的存储和擦除。

3. I/O接口:I/O接口是Flash存储芯片与外部设备之间的通信接口,用于传输数据和控制信号。

常见的接口包括SPI、SDIO、eMMC等。

二、Flash存储芯片的工作原理Flash存储芯片的工作原理可以分为读取、写入和擦除三个基本操作。

1. 读取操作:当外部设备需要读取Flash存储芯片中的数据时,首先通过I/O接口发送读取命令和数据地址给控制器。

控制器根据接收到的地址解码器将数据地址转换为存储单元阵列中的行和列,然后通过数据缓存将存储单元中的数据读取出来,并通过I/O接口返回给外部设备。

2. 写入操作:当外部设备需要向Flash存储芯片中写入数据时,首先通过I/O接口发送写入命令和数据地址给控制器。

控制器根据接收到的地址解码器将数据地址转换为存储单元阵列中的行和列,然后将外部设备传输的数据写入到对应的存储单元中。

写入操作需要先将存储单元擦除为全1状态,再将数据写入存储单元。

3. 擦除操作:当外部设备需要擦除Flash存储芯片中的数据时,首先通过I/O 接口发送擦除命令和数据地址给控制器。

Flash存储芯片工作原理

Flash存储芯片工作原理引言概述:Flash存储芯片是一种常见的非易失性存储设备,广泛应用于电子产品中。

本文将详细介绍Flash存储芯片的工作原理,包括存储结构、读取和写入操作、擦除机制、错误校验和纠正等方面。

一、存储结构1.1 逻辑结构:Flash存储芯片通常由多个存储单元组成,每个存储单元可以存储一个或多个位的数据。

这些存储单元按照一定的规则组织成逻辑结构,如页、块和平面等。

1.2 物理结构:Flash存储芯片的物理结构由多个存储阵列组成,每个存储阵列包含多个存储单元。

存储单元通过晶体管和浮动栅极结构实现数据的存储和读取。

二、读取和写入操作2.1 读取操作:Flash存储芯片的读取操作是通过电压的变化来实现的。

当读取某个存储单元时,芯片会将电压施加到该存储单元上,并根据电压的变化来判断存储单元中存储的数据是0还是1。

2.2 写入操作:Flash存储芯片的写入操作是通过改变存储单元中的电荷量来实现的。

当写入数据时,芯片会施加不同的电压来改变存储单元中的电荷量,从而改变存储单元中存储的数据。

三、擦除机制3.1 擦除操作:Flash存储芯片的擦除操作是将存储单元中的数据全部清除为1的过程。

擦除操作需要将存储单元中的电荷量恢复到初始状态,以便后续的写入操作。

3.2 擦除单元:Flash存储芯片中的擦除操作是以块为单位进行的。

每个块包含多个存储单元,擦除时需要同时擦除该块中的所有存储单元。

3.3 擦除次数:Flash存储芯片的擦除次数是有限的,每个存储单元的擦除次数通常在几千次到几十万次之间。

超过擦除次数限制后,存储单元的可靠性会下降。

四、错误校验和纠正4.1 错误校验:Flash存储芯片在读取数据时可能会出现错误,例如由于电压干扰或存储单元老化等原因。

为了提高数据的可靠性,Flash存储芯片通常会使用错误校验码(ECC)来检测和纠正错误。

4.2 纠正算法:Flash存储芯片的纠正算法是通过对读取的数据进行计算和比较来实现的。

Flash存储芯片工作原理

Flash存储芯片工作原理Flash存储芯片是一种非易失性存储设备,被广泛应用于各种数字设备中,如手机、相机、固态硬盘等。

它具有高速读写、低功耗、抗震抗摔等优点,成为了存储领域的重要组成部分。

本文将详细介绍Flash存储芯片的工作原理。

1. 存储单元Flash存储芯片的基本单元是存储单元,也称为存储单元或存储单元。

每个存储单元可以存储一个或多个二进制位的数据。

常见的存储单元有SLC(Single-Level Cell)和MLC(Multi-Level Cell)两种类型。

SLC存储单元每个单元只能存储一个二进制位的数据,而MLC存储单元则可以存储多个二进制位的数据,这使得MLC存储单元的存储密度更高,但其读写速度和寿命相对较低。

2. 位线和字线Flash存储芯片中的存储单元通过位线和字线进行读写操作。

位线是连接存储单元的线路,用于传输数据。

字线是用于选择存储单元的线路。

通过控制位线和字线的电压,可以实现对存储单元的读取和写入操作。

3. 读取操作在读取数据时,首先需要选择要读取的存储单元,这通过控制字线来实现。

当选择了存储单元后,通过控制位线的电压,将存储单元中的数据读取到位线上。

读取的数据经过放大和解码处理后,传递给外部设备。

4. 写入操作在写入数据时,首先需要选择要写入的存储单元,这通过控制字线来实现。

当选择了存储单元后,通过控制位线的电压,将要写入的数据写入到存储单元中。

写入操作是通过改变存储单元中的电荷状态来实现的。

对于SLC存储单元,只需要改变一个二进制位的电荷状态即可;而对于MLC存储单元,需要改变多个二进制位的电荷状态。

5. 擦除操作Flash存储芯片的存储单元是有限的,当需要将存储单元中的数据清除时,就需要进行擦除操作。

擦除操作是通过改变存储单元中的电荷状态来实现的。

对于SLC存储单元,只需要将电荷状态改变为初始状态即可;而对于MLC存储单元,需要将多个二进制位的电荷状态都改变为初始状态。

flash和eeprom工作原理

flash和eeprom工作原理

Flash存储器和EEPROM(Electrically Erasable Programmable Read-Only Memory,可电擦可编程只读存储器)在存储数据和编程操作上存在一些区别。

Flash存储器是一种基于非挥发性存储技术的存储器,常用于存储程序代码和数据。

它被分为多个扇区,每个扇区可以被独立擦除和编程。

Flash存储器的工作原理是利用电子漂移现象,通过在晶体管中储存电荷来表示数据的位状态。

擦除操作会将整个扇区的位状态清零,编程操作会将位状态设置为1。

擦除和编程操作都需要高电压和特定的操作序列。

EEPROM(可电擦可编程只读存储器)是一种可擦写的非挥发性存储器,可以在电子设备中存储和读取数据。

EEPROM的工作原理是利用电子隧道效应,通过在细小的浮栅结构中存储电荷来表示数据的位状态。

相比于Flash 存储器,EEPROM在编程和擦除操作上更为灵活,可以以字节为单位进行操作,而不需要擦除整个扇区。

然而,EEPROM的写入速度相对较慢,且有限的擦写寿命限制了其使用次数。

总的来说,Flash和EEPROM在编程和擦除机制上有所不同。

Flash通常以扇区为单位进行操作,而EEPROM可以以字节为单位进行操作。

此外,EEPROM的写入速度较慢,且具有有限的擦写寿命。

flash memory 原理

flash memory 原理

Flash memory 是一种非易失性存储介质,它的原理是利用了浮栅结构和电荷累积效应来存储数据。

Flash memory 的基本单元是电荷存储晶体管,每个晶体管由一个控制门、一个浮栅和一个通道构成。

通过在浮栅结构上施加电压,可以在晶体管中存储或擦除电荷。

当存储数据时,晶体管处于写入模式。

在控制门施加正电压的同时,通道之间的电场会将电荷注入到浮栅区域。

这个电荷累积在浮栅上,形成一个电子堆。

电子堆的存在与否可以表示存储的二进制数据。

在擦除数据时,晶体管处于擦除模式。

通过在控制门施加负电压的同时,通道之间的电场会将浮栅上的电荷清除,将晶体管恢复到初始状态。

读取数据时,测量浮栅上的电荷量,可以确定存储的数据是0还是1,进而实现数据的读取操作。

Flash memory 的主要优势是速度快、体积小、功耗低、抗震抗撞击等。

它在移动设备、嵌入式系统和固态硬盘等应用中得到广泛应用。

Flash存储芯片工作原理

Flash存储芯片工作原理引言概述:Flash存储芯片是一种非易失性存储设备,被广泛应用于各种电子设备中。

本文将详细介绍Flash存储芯片的工作原理,包括擦除、写入和读取操作的过程,以及其优缺点和应用领域。

一、擦除操作:1.1 擦除单元:Flash存储芯片的最小擦除单元是一个扇区或者一个块,通常为64KB或者256KB。

擦除操作是将整个扇区或者块的数据全部擦除为1。

1.2 擦除方法:Flash存储芯片采用电子擦除方法,通过向存储单元中加入高电压来擦除数据。

这个过程中,存储单元中的浮栅电荷被清除,将其电压重新设置为初始状态。

1.3 擦除速度:Flash存储芯片的擦除速度相对较慢,普通需要几毫秒到几十毫秒的时间。

这是因为擦除操作需要较高的电压和较长的时间来完成。

二、写入操作:2.1 写入单元:Flash存储芯片的最小写入单元是一个页面,通常为512字节或者2KB。

写入操作是将数据写入到一个空白的页面中。

2.2 写入方法:Flash存储芯片采用电子写入方法,通过向存储单元中加入适当的电压来改变单元的电荷状态。

这个过程中,存储单元中的浮栅电荷被改变,将其电压重新设置为目标状态。

2.3 写入速度:Flash存储芯片的写入速度相对较快,普通需要几微秒到几十微秒的时间。

这是因为写入操作只需要改变存储单元的电荷状态,不需要擦除整个扇区或者块。

三、读取操作:3.1 读取单元:Flash存储芯片的最小读取单元是一个字节。

读取操作是将存储单元中的数据读取出来。

3.2 读取方法:Flash存储芯片采用电子读取方法,通过检测存储单元中的电荷状态来读取数据。

根据电荷状态的不同,可以判断出单元中存储的是0还是1。

3.3 读取速度:Flash存储芯片的读取速度相对较快,普通需要几纳秒到几微秒的时间。

这是因为读取操作只需要检测存储单元的电荷状态,不需要改变单元的电荷状态。

四、优缺点和应用领域:4.1 优点:Flash存储芯片具有非易失性、体积小、功耗低、抗震动、抗电磁干扰等优点。

Flash存储芯片工作原理

Flash存储芯片工作原理标题:Flash存储芯片工作原理引言概述:Flash存储芯片是一种常见的非易失性存储设备,广泛应用于各种电子设备中。

其工作原理是通过电子存储技术实现数据的读写和存储。

本文将详细介绍Flash 存储芯片的工作原理及其相关知识。

一、内部结构1.1 存储单元:Flash存储芯片由多个存储单元组成,每个存储单元可以存储一个或多个位的数据。

1.2 位线和字线:存储单元通过位线和字线进行数据读写操作,位线用于选择存储单元,字线用于传输数据。

1.3 控制逻辑:Flash存储芯片内部还包含控制逻辑电路,用于管理数据的读写操作,包括擦除、写入和读取等功能。

二、工作原理2.1 读取数据:当需要读取数据时,控制逻辑会选择相应的存储单元,并通过位线和字线将数据传输到输出端口。

2.2 写入数据:写入数据时,控制逻辑会擦除原有数据,并将新数据写入到指定的存储单元中。

2.3 擦除数据:擦除数据是将存储单元内的数据全部清空,以便写入新的数据。

擦除操作通常需要整个块进行,而非单个存储单元。

三、工作原理之NAND和NOR3.1 NAND结构:NAND Flash存储芯片采用串行结构,存储单元按行排列,适合大容量存储。

3.2 NOR结构:NOR Flash存储芯片采用并行结构,存储单元按列排列,读取速度较快,适合小容量存储。

3.3 差异比较:NAND和NOR Flash存储芯片在结构和工作原理上有所不同,用户可以根据需求选择不同类型的Flash存储芯片。

四、寿命和耐久性4.1 擦写次数:Flash存储芯片的寿命与擦写次数有关,通常为几万到几百万次。

4.2 坏块管理:由于擦写次数限制,Flash存储芯片会出现坏块,需要通过坏块管理算法进行处理。

4.3 原理保护:为了延长Flash存储芯片的寿命,用户应避免频繁擦写操作,合理使用存储空间。

五、应用领域5.1 电子设备:Flash存储芯片广泛应用于手机、平板电脑、相机等电子设备中,用于存储数据和程序。

Flash简介以及嵌入式系统的flash

Flash简介以及嵌入式系统的flash一, flash的简介1,什么是flashFlash 是一种创作工具,设计人员和开发人员可使用它来创建演示文稿、应用程序和其它允许用户交互的内容。

Flash 可以包含简单的动画、视频内容、复杂演示文稿和应用程序以及介于它们之间的任何内容。

通常,使用 Flash 创作的各个内容单元称为应用程序,即使它们可能只是很简单的动画。

您可以通过添加图片、声音、视频和特殊效果,构建包含丰富媒体的 Flash 应用程序。

Flash 特别适用于创建通过 Internet 提供的内容,因为它的文件非常小。

Flash 是通过广泛使用矢量图形做到这一点的。

与位图图形相比,矢量图形需要的内存和存储空间小很多,因为它们是以数学公式而不是大型数据集来表示的。

位图图形之所以更大,是因为图像中的每个像素都需要一组单独的数据来表示。

要在 Flash 中构建应用程序,可以使用 Flash 绘图工具创建图形,并将其它媒体元素导入 Flash 文档。

接下来,定义如何以及何时使用各个元素来创建设想中的应用程序。

2,flash文件的说明在 Flash 中创作内容时,需要在 Flash 文档文件中工作。

Flash 文档的文件扩展名为 .fla (FLA)。

Flash 文档有四个主要部分:a.舞台,是在回放过程中显示图形、视频、按钮等内容的位置。

b. 时间轴, 用来通知 Flash 显示图形和其它项目元素的时间,也可以使用时间轴指定舞台上各图形的分层顺序。

位于较高图层中的图形显示在较低图层中的图形的上方。

图层就像透明的醋酸纤维薄片一样,在舞台上一层层地向上叠加。

图层可以帮助您组织文档中的插图。

可以在图层上绘制和编辑对象,而不会影响其它图层上的对象。

如果一个图层上没有内容,那么就可以透过它看到下面的图层。

使用帧和关键帧。

键帧是这样一个帧:您在其中定义了对动画的对象属性所做的更改,或者包含了 ActionScript 代码以控制文档的某些方面。

Flash存储芯片工作原理

Flash存储芯片工作原理Flash存储芯片是一种非易失性存储器,广泛应用于各种电子设备中,如手机、相机、固态硬盘等。

它具有高速读写、低功耗、体积小等优点,成为了现代电子产品中不可或者缺的一部份。

本文将详细介绍Flash存储芯片的工作原理。

一、Flash存储芯片的基本结构Flash存储芯片由一系列的存储单元组成,每一个存储单元可以存储一个或者多个二进制位的数据。

存储单元是由晶体管和电容器构成的,其中晶体管用于控制电荷的流动,而电容器则用于存储电荷。

Flash存储芯片的基本结构可以分为三个层次:芯片级、块级和页级。

在芯片级,多个块被组合在一起,每一个块又包含多个页。

每一个页又包含多个存储单元。

这种层次结构使得数据的读取和写入变得更加高效。

二、Flash存储芯片的读取原理Flash存储芯片的读取过程主要分为两个步骤:选择和放电。

选择:通过控制晶体管的开关状态,选择要读取的存储单元。

每一个存储单元都有一个惟一的地址,通过选择相应的地址,可以确定要读取的存储单元。

放电:一旦选择了存储单元,就需要将存储单元中的电荷释放出来。

为了实现这一点,需要将存储单元的控制线上的电压调整到一定的水平,以擦除存储单元中的电荷。

这个过程被称为放电。

在读取过程中,通过测量存储单元中的电荷状态,可以确定存储单元中存储的数据。

如果存储单元中有电荷,表示存储的是1;如果存储单元中没有电荷,表示存储的是0。

三、Flash存储芯片的写入原理Flash存储芯片的写入过程也分为两个步骤:选择和充电。

选择:与读取过程类似,通过控制晶体管的开关状态,选择要写入的存储单元。

充电:一旦选择了存储单元,就需要将存储单元中的电荷重新填充。

为了实现这一点,需要将存储单元的控制线上的电压调整到一定的水平,以充电存储单元。

这个过程被称为充电。

在写入过程中,通过控制存储单元中的电荷状态,可以将数据写入存储单元。

如果需要写入的数据是1,则将存储单元充电;如果需要写入的数据是0,则将存储单元放电。

嵌入式系统中Nand-Flash的原理及应用

嵌入式系统中Nand-Flash的原理及应用当前各类嵌入式系统开发设计中,存储模块是不可或缺的重要方面。

NOR 和NAND 是目前市场上两种主要的非易失闪存技术。

Nor-flash 存储器的容量较小、写入速度较慢,但因其随机读取速度快,因此在嵌入式系统中,常应用在程序代码的存储中。

Nor-flash 存储器的内部结构决定它不适合朝大容量发展; 而Nand-flash 存储器结构则能提供极高的单元密度,可以达到很大的存储容量,并且写入和擦除的速度也很快。

Nand-flash 存储器是flash 存储器的-种,其内部采用非线性宏单元模式,为固态大容量存储器的实现提供了廉价有效的解决方案。

Nand-flash 存储器具有容量较大,改写速度快,适用于大量资料的存储,因而在业界得到了越来越广泛的应用,如嵌入式产品中包括数码相机、MP3 随身听记忆卡、体积小巧的U 盘等。

本文以三星公司的K9F1208UOB 芯片为例,介绍Nand-flash 存储器芯片的读写流程和时序。

1 Nand-Flash 存储器的工作原理1.1 Nand-Flash 存储器的组成结构及指令集K9F1208UOB 的容量为64Mb,存储空间按128K 个页(行)、每页中528 个字节(列)的组成方式构成。

备用的16 列,位于列地址的512-527。

K9F1208UOB 还将存储空间分为块(block),每1 块由32 个页构成。

因此K9F1208UOB 中一共有4096 个块。

这种“块-页”结构,恰好能满足文件系统中划分簇和扇区的结构要求。

K9F1208UOB 的内部结构如图1 所示。

图1 K9F1208UOB 的内部结构K9F1208UOB 的读和写都以页为单位,擦除则以块为单位进行操作。

K9F1208UOB 的地址通过8 位端口传送,有效地节省了引脚的数量,并能够保持不同密度器件引脚的一致性,系统可以在电路不作改动的情况下升级为高容量存储器件。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

嵌入式Flashmemory技术简介及工作原理1概述随着数码时代的来临,除了PC外,越来越多的数码信息产品正在或即将进入我们的家庭:移动电话、掌上电脑、数码相机、GPS等等,这些产品越来越多的使用各种移动微存储器。

这些存储器中很大部分是快闪存储器(FlashMemory)。

Flashmemory是从EPROM和EEPROM发展而来的非挥发性存储集成电路,其主要特点是工作速度快、单元面积小、集成度高、可靠性好、可重复擦写10万次以上,数据可靠保持超过10年。

国外从80年代开始发展,到2002年随着数码时代的来临,除了PC外,越来越多的数码信息产品正在或即将进入我们的家庭:移动电话、掌上电脑、数码相机、GPS等等,这些产品越来越多的使用各种移动微存储器。

这些存储器中很大部分是快闪存储器(Flash Memory)。

Flash memory是从EPROM和EEPROM发展而来的非挥发性存储集成电路,其主要特点是工作速度快、单元面积小、集成度高、可靠性好、可重复擦写10万次以上,数据可靠保持超过10年。

国外从80年代开始发展,到2002年,Flash memory的年销售额超过一百亿美元,并增长迅速,预计到2006年,年销售额可达126亿美元/年。

到目前,用于Flash memory生产的技术水平已达0.13μm,单片存储量达几千兆。

除大容量存储器应用外,Flash Memory也大量地替代EPROM、EEPROM嵌入到ASIC、CPU、DSP电路中,如TI公司的TMS320F240系列、TMS280系列分别含有8K―128K Words的Flash Memory,又如Microchip公司,也推出了内嵌Flash Memory的16F系列MCU产品。

Flash Memory电路芯片设计的核心是存储单元(Cell)设计(包括结构、读写擦方式),外围电路都是围绕其设计。

因此,我们首先要研究并确定电路中采用的Flash Memory Cell。

Flash Memory从结构上大体上可以分为AND、NAND、NOR和DINOR等几种,现在市场上两种主要的Flash Memory技术是NOR和NAND结构。

本文分析了NOR和NAND结构的快闪存储器存储单元结构及其应用特点,给出了一种适合嵌人的改进型SSI存储单元结构,并对其的工作原理、性能、组成的存储器存储单元阵列、及可靠性设计进行了详细的分析。

2 存储单元结构2.1 NOR存储单元快闪存储器的擦写技术来源于沟道热电子发射(Channel Hot-Electron Injection)与隧道效应(Fowlerordheim)。

NOR结构的Flash memory主要用于存储指令代码及小容量数据的产品中,目前的单片最高容量为512M,NOR Flash memory产品的主要领导者为Intel公司、AMD公司、Fujitsu公司、ST Microelectronics和公司。

NOR结构的Flash memory采用NOR SGC(Stacked Gate Cell)存储单元,是从EPROM结构直接发展而来,非常成熟的结构,采用了简单的堆叠栅构造。

图1是其结构原理图。

浮栅的充电(写)是通过传统的沟道热电子发射(CHEI)在漏端附近完成的;浮栅的放电(擦除)在源端通过隧道氧化层的隧道效应来实现。

该结构的特点是单元面积小,同EPROM的面积相当,编程(写)时间短,在10μs左右,源漏结可以分开优化,漏结优化沟道热电子发射,源结优化隧道效应,采用了自对准工艺。

随着制造技术的进步,存储单元的特征尺寸越来越小,工作电压降低,带来的负面影响是热电子发射效率降低,编程时较难工作于4V漏源电压下。

为提高热电子发射效率,需要对源结、漏结、沟道掺杂分布进行优化1,整体工艺较复杂,编程电流也较大,大约400μA/bit(0.5μm)技术。

工艺流程以0.25μm-0.35μm产品为例,采用DPDM制造的快闪存储器需要23块Mask版,进行27次光刻。

2.2 隧道效应存储单元隧道效应存储单元是目前快速发展的快闪存储器生产技术,在快闪存储器中一般组成NAND存储阵列,单元面积小,其工艺较简单,容量大,成本低,适用于低价格、高容量、速度要求不高的Flash memory客户用于数据存储;在MP3、PAD、数码相机、2.5G及3G 无线系统中得到了广泛的应用。

NAND快闪存储器产品的生产工艺已达到0.13μm,单片电路的存储容量超过1Gb。

图2是隧道效应存储单元结构原理图,其编程、擦除通过隧道氧化层的隧道效应来实现,类似EEPROM,其优点是在编程时可以工作在2.5V的源漏电压下,功耗低,非常适合非接触式IC卡,同时NAND阵列的单元面积是NORSGC单元面积的二分之一,适合于大容量集成。

隧道效应存储单元擦写工作电压高,一般要求达到16V-20V,对器件、电路的设计要求高,编程(写)时间较长,在50μs-100μs,不适合字节编程,适用于大容量页编程,像EEPROM一样,编程时,加在隧道氧化层上电场强度高,存在SILC(stress induced leakage currents)效应,对工艺要求高。

2.3 源侧热电子发射(SSI)存储单元在九十年代初,报道了SSI(Source-Sidehotelectron Injection)存储单元,结合了NORSGC单元的快速编程与隧道效应存储单元编程功耗低的特点,其原理为split-gate concept2,图3是其编程原理。

SSI存储单元浮栅的充电(写)是通过沟道热电子发射,在源端附近完成的;浮栅的放电(擦除)在漏端通过隧道氧化层的隧道效应来实现。

在编程(写)过程中由于部分沟道由CG 栅(1.5V)控制,改进了NOR SGC单元的编程(写)电流大、优化了沟道热电子发射效率,编程时的源漏电压可低至3.3V。

其存在的问题是必须在数据线译码中使用大量高压开关,电路设计复杂,沟道热电子发射没有完全优化、读出电流小、工艺也比较复杂。

图4是我们采用的、也是本文主要讨论的改进型SSI结构的存储单元结构,在存储单元中增加了编程栅来提高CHEI效率(效率的提高见图5)。

其优点有工艺简单,只要在数字CMOS逻辑电路的基础上增加三次光刻(高压NWELL、高压MOS管选择氧化、Fowler-Nordheim N+埋层注人)就能完成整个电路工艺制造,易于嵌入到普通ASIC电路中;Flash Cell源漏电压在3.3V就能完成编程工作,简化电路设计;编程速度快,0.5μm Flash Cell源漏电压在5V的情况下,编程时间优于500ns,在3.3V下小于10μs,非常适合嵌人式电路设计。

3 阵列结构与工作原理3.1 改进型SSI结构存储单元的工作原理为实现电路存储单元的读写擦工作,需要设置不同工作电压,其工作电压及工作原理见图6。

单元的编程:在单元的漏源加5V电压,在编程栅上加12V电压耦合到浮栅上,控制栅上电压为1.5V,电子从源端出发,在CG控制的沟道中加速,产生热电子,在浮栅下发射到浮栅上,完成电路的编程,约200个沟道电子可产生一个热电子。

编程后的单元的阈值电压为2V。

单元的擦除:在单元的漏源加5V电压,控制栅与编程栅上加-7V电压耦合到浮栅上,在浮栅与漏端间的隧道氧化层达到一定的电场强度,产生隧道电流,浮栅失去电子完成单元的擦除,擦除时间约0.1s-1.Os,擦除后的单元的阈值电压为-2V。

数据的读出:在单元的漏源加2V电压,编程栅电压为OV,控制栅电压为2V,由于控制栅与浮栅的耦合率(<10%)大大低于编程栅与浮栅的偶合率,因此依据浮栅中电荷的信息经小信号放大器读出存储的数据,我们设计的0.5μm的Cell“1”电平时读出电流可达70μA。

3.2 存储单元的阵列结构我们在电路的设计中采用了VGA(Vietual Ground Array)阵列结构来缩小版图面积,见图7,图8与图9分别为W0/W1存储单元的读写擦方式。

4 工艺特点开发该存储单元主要目的是用于嵌入到其它ASIC电路中去,因此要求工艺较为简单,与普通0.5μm CMOS标准工艺兼容性好。

我们开发的工艺包括HVNMOS、HVPMOS器件内整体工艺只比普通CMOS电路多三次光刻,分别是高压NWELL、高压MOS管选择氧化与Fowler-Nordheim N+埋层注入,工艺实现、开发难度低,电路易于集成、嵌入。

表2为主要工艺流程,其中黑体部分为在普通CMOS工艺基础上增加的工艺。

表2 嵌入Flash电路的工艺流程p-/p+外延片→预氧、长Si3N4→光刻、腐蚀、注入、形成HVNWELL→光刻、腐蚀、注入形成NWELL→去Si3N4、注入形成PWELL→制作有源区→N管场区光刻、注入→场氧→Vt调整→高压管栅氧→隧道区选择光刻→隧道氧化→生长多晶I→多晶I电阻注入→光刻、注人多晶I低阻区→多晶Ⅱ光刻、腐蚀→擦除洁、HVNMOS DDD光刻、注入→逻辑电路CMOS栅氧→生长多晶Ⅱ→多晶Ⅱ→光刻、腐蚀→P-LDD光刻、注入→N-LDD光刻、注入→P―SD光刻、注入→N-SD光刻、注入→SILICIDE选择光刻、腐蚀→介质生长、平坦化→接触孔光刻、腐蚀→铝I布线→介质生长、平坦化→通孔光刻、腐蚀→铝Ⅱ布线→介质生长、平坦化→压焊孔光刻、腐蚀5 干扰与可靠性5.1 存储单元与电路设计的可靠性问题存储单元的阈值电压是擦写及读出过程的函数,因此要优化擦写过程的工作条件,提高工艺质量,特别是隧道氧化层、双多晶内氧化层在高场强下的质量与寿命,降低氧化层中陷阱(trap)的产生。

图10是0.5μm单元在擦写循环后的阈值电压的变化。

5.2 超擦(Overerase)超擦NORSGC存储单元存在的主要问题,由于NOR阵列中的存储单元没有选择管,在字线上所有的存储单元漏端连在一起,如果在擦除后,某些单元的阈值电压特别低,在读出过程中,在非选择栅压下(通常为0V),几个单元有漏电,则字线上读不出正确的数据(见图11),特别是多次擦写循环后,增加了阈值电压的不确定性,因此需要在电路中设计验证电路。

改进型SSI存储单元由于存在选择管,未选中的单元选择管关闭,因此基本上不受超擦漏电的影响。

5.3 软写(Soft-Write)在电路正常工作时,读在浮栅上存储有正电荷(“1”电平)的单元,由于有沟道电流,以及在浮栅上有正电压存在,因此有少量的热电子发射,产生软写效应,长时间会使工作存储的信息丢失,为保证电路存储的信息保存时间超过十年,要对单元正常工作电压进行优化,改进型SSI存储单元的软写结果见图12,在电路设计中选择了2V漏源工作电压,可保证数据保存超过十年。

5.4 擦除干扰(Erase Disturb)当电路中存在Sector擦除,并且不同Sector的单元漏端连接到同一条数据线(Bit Line)上时,要考虑到对选定的Sector擦除时,对非选择Sector的擦除干扰。