英文文献 科技类 原文及翻译 (电子 电气 自动化 通信…)10

电气专业英文文献翻译

一个非线性电谐振器作为一个简单的触摸感应开关与记忆存储器摘要我们介绍了一个新的切换机构,它依赖于一个简单的非线性电谐振器,其中包括一个变容二极管作为其电容元件的双稳态的切换动作,开关动作可以快速和自包含在电路中。

不同于一个触发器的翻转,其状态是通过施加一个TTL脉冲翻转,这种非线性开关可以通过磁,电感性或电容性耦合被接合到外部电路,在这种方式中,开关变为本质触摸敏感。

另外,开关动作也可以使用频移键控(FSK)调制,实现有记忆状态的快速操作的承诺。

我们通过构建一个触摸感应的LED 点阵证明这些想法的潜在应用。

关键词:非线性开关;电气谐振器的双稳态特性;触摸灵敏度1.介绍在数字电子技术,可以在两个状态之间进行切换的典型的存储元件,当然是触发器。

SR触发器无处不在,例如,它包含两个交叉的NOR(或NAND)门。

当无信号时,触发器的状态保持在其以前的配置,并以它翻转到另一种状态的简要电压信号(TTL脉冲)被施加到相应的输入。

在这里,我们提出了一个非线性电谐振器,在某些方面的作用就像一个触发器。

正如我们表明,它的两个状态之间的切换是通过驱动频率协议(FSK调制)来实现,或通过将一个磁铁或到附近的谐振器的电感器来完成的,它也可以通过电容耦合被切换。

设置完成后,系统会记住它的状态,直到另一个开关动作。

然而,不像一般的触发器,该元件可被诱导以从电路的外面进行切换。

另外,频率调制方案可以快速切换。

最后,我们将通过构建一个可控的LED阵列展示这一理念的应用程序。

由于开关动作可以出现在响应触摸(通过改变电容)或靠近磁铁或电感器,这种谐振就像触摸感应开关,这也许会让人联想到一个“触摸灯”。

当这种灯的金属外壳被触摸时,它的有效电容增加。

有那么多的方式来电容转换为数字输出[1]。

即使是最简单的方案采用了数字集成电路元件:一个固定幅度的交流电压驱动器充电和放电的住房,并在接触充电电流增加,进一步电路检测这种增强的电流和开关一个触发器。

电气工程及其自动化专业_外文文献_英文文献_外文翻译_plc方面.

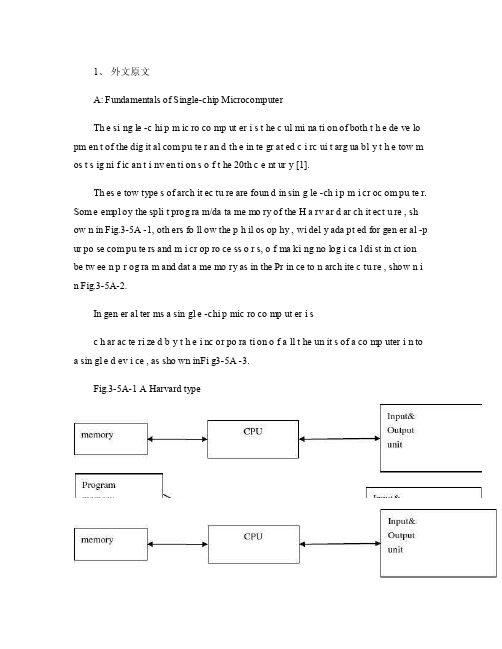

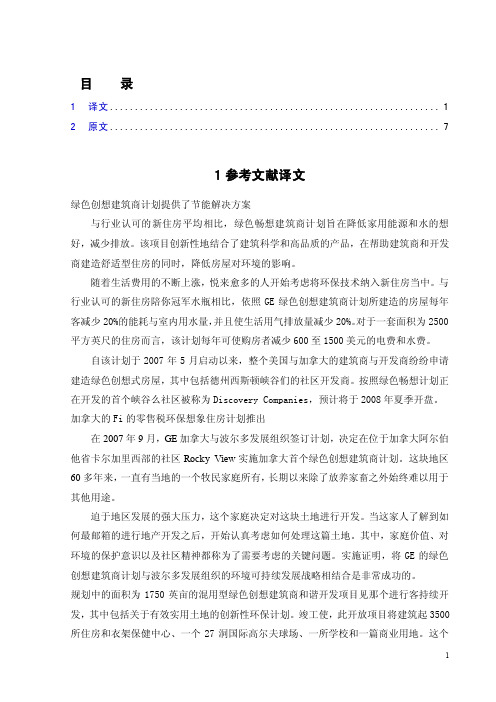

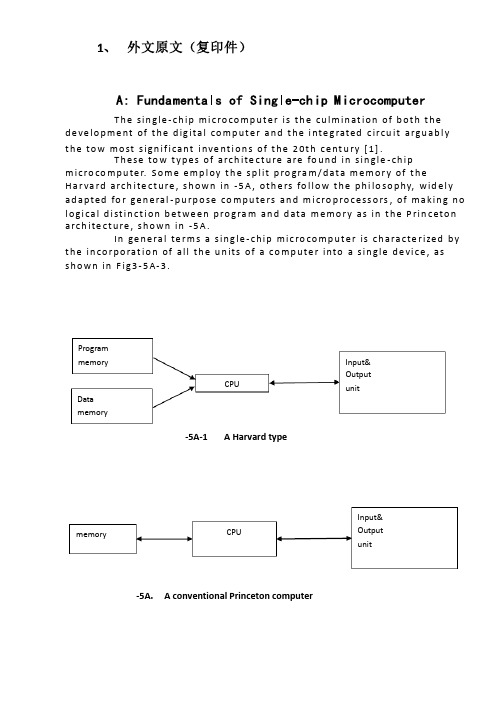

1、外文原文A: Fundamentals of Single-chip MicrocomputerTh e si ng le -c hi p m ic ro co mp ut er i s t he c ul mi na ti on of both t h e de ve lo pm en t of the dig it al com pu te r an d th e in te gr at ed c i rc ui t arg ua bl y t h e tow m os t s ig ni f ic an t i nv en ti on s o f t he 20th c e nt ur y [1].Th es e tow type s of arch it ec tu re are foun d in sin g le -ch i p m i cr oc om pu te r. Som e empl oy the spli t prog ra m/da ta me mo ry of the H a rv ar d ar ch it ect u re , sh ow n in Fig.3-5A -1, oth ers fo ll ow the p h il os op hy , wi del y ada pt ed for gen er al -p ur po se com pu te rs and m i cr op ro ce ss o r s, o f ma ki ng no log i ca l di st in ct ion be tw ee n p r og ra m and dat a me mo ry as in the Pr in ce to n arch ite c tu re , show n i n Fig.3-5A-2.In gen er al ter ms a sin gl e -chi p mic ro co mp ut er i sc h ar ac te ri zed b y t he i nc or po ra ti on of a ll t he un it s of a co mp uter i n to a sin gl e d ev i ce , as sho wn inFi g3-5A -3.Fig.3-5A-1 A Harvard typeFig.3-5A-2. A conventional Princeton computerFig3-5A-3. Principal features of a microcomputerRead only memory (ROM.R OM is usua ll y for the pe rm an ent,n o n-vo la ti le stor a ge of an app lic a ti on s pr og ra m .M an ym i cr oc om pu te rs and m are inte nd e d for high -v ol um e ap pl ic at ions a n d he nc e t h e eco n om ic al man uf act u re of th e de vic e s re qu ir es t h at t he cont en t s o f t he prog ra m me m or y be co mm it t ed perm a ne ntly d u ri ng the man ufa c tu re of ch ip s .Cl ea rl y, thi s im pl ie s a r i go ro us app ro ach to ROM cod e deve l op me nt sin ce cha ng es can not b e mad e afte r manu f a c tu re .Th is dev e lo pm en t proc ess may invo lv e e m ul at io n us in g aso ph is ti ca te d de ve lo pm en t sy ste m wit h a h a rd wa re emu la tio n cap ab il it y as w el l as the use o f po we rf ul s o ft wa re too ls.So me man uf act u re rs pro vi de add it io na l RO M opt i on s by i n cl ud in g in their ra n ge dev ic es wit h (or int en de d fo r use wit h u s er pro gr am ma ble me mo ry. Th e sim p le st of th es e is usu al ly d e vi ce whi ch can op er at e in a micro p ro ce ssor mod e by usi ng som e o f the inp ut /outp u t li ne s as an ad dr es s an d da ta b us fora c ce ss in g ex te rna l mem or y. Thi s t y pe of de vi ce can beh av ef u nc ti on al ly as th e sing le chip mi cr oc om pu te r from whi ch it is d e ri ve d al be it wit h re st ri ct ed I/O and a mod if ied ex te rn al c i rc ui t. The use of thes e d ev ic es is com mo n eve n in prod uc ti on c i rc ui ts wher e t he vo lu me does no tj us ti f y t h e d ev el o pm en t c osts o f c us to m o n -ch i p R OM [2];t he re c a n s ti ll bea s ignif i ca nt saving i n I /O and o th er c h ip s com pa re d to a conv en ti on al mi c ro pr oc es sor b a se d ci rc ui t. Mor e ex ac t re pl ace m en t fo r RO M dev i ce s ca n be o b ta in ed in th e fo rm of va ri an ts w it h 'p ig gy -b ack 'E P RO M(Er as ab le pro gr am ma bl e ROM s oc ke ts or dev ic e s with EPROM i n st ea d o f RO M 。

英文文献科技类原文及翻译(电子电气自动化通信…)50

目录1译文 (1)2原文 (7)1参考文献译文绿色创想建筑商计划提供了节能解决方案与行业认可的新住房平均相比,绿色畅想建筑商计划旨在降低家用能源和水的想好,减少排放。

该项目创新性地结合了建筑科学和高品质的产品,在帮助建筑商和开发商建造舒适型住房的同时,降低房屋对环境的影响。

随着生活费用的不断上涨,悦来愈多的人开始考虑将环保技术纳入新住房当中。

与行业认可的新住房陪你冠军水瓶相比,依照GE绿色创想建筑商计划所建造的房屋每年客减少20%的能耗与室内用水量,并且使生活用气排放量减少20%。

对于一套面积为2500平方英尺的住房而言,该计划每年可使购房者减少600至1500美元的电费和水费。

自该计划于2007年5月启动以来,整个美国与加拿大的建筑商与开发商纷纷申请建造绿色创想式房屋,其中包括德州西斯顿峡谷们的社区开发商。

按照绿色畅想计划正在开发的首个峡谷么社区被称为Discovery Companies,预计将于2008年夏季开盘。

加拿大的Fi的零售税环保想象住房计划推出在2007年9月,GE加拿大与波尔多发展组织签订计划,决定在位于加拿大阿尔伯他省卡尔加里西部的社区Rocky View实施加拿大首个绿色创想建筑商计划。

这块地区60多年来,一直有当地的一个牧民家庭所有,长期以来除了放养家畜之外始终难以用于其他用途。

迫于地区发展的强大压力,这个家庭决定对这块土地进行开发。

当这家人了解到如何最邮箱的进行地产开发之后,开始认真考虑如何处理这篇土地。

其中,家庭价值、对环境的保护意识以及社区精神都称为了需要考虑的关键问题。

实施证明,将GE的绿色创想建筑商计划与波尔多发展组织的环境可持续发展战略相结合是非常成功的。

规划中的面积为1750英亩的混用型绿色创想建筑商和谐开发项目见那个进行客持续开发,其中包括关于有效实用土地的创新性环保计划。

竣工使,此开放项目将建筑起3500所住房和衣架保健中心、一个27洞国际高尔夫球场、一所学校和一篇商业用地。

电气毕业论文设计英语文献原文+翻译.doc

标准文档外文翻译院(系)专业班级姓名学号指导教师年月日Programmable designed for electro-pneumatic systemscontrollerJohn F.WakerlyThis project deals with the study of electro-pneumatic systems and the programmable controller that provides an effective and easy way to control the sequence of the pneumatic actuators movement and the states of pneumatic system. The project of a specific controller for pneumatic applications join the study of automation design and the control processing of pneumatic systems with the electronic design based on microcontrollers to implement the resources of the controller.1. IntroductionThe automation systems that use electro-pneumatic technology are formed mainly by three kinds of elements: actuators or motors, sensors or buttons and control elements like valves. Nowadays, most of the control elements used to execute the logic of the system were substituted by the Programmable Logic Controller (PLC). Sensors and switches are plugged as inputs and the direct control valves for the actuators are plugged as outputs. An internal program executes all the logic necessary to the sequence of the movements, simulates other components like counter, timer and control the status of the system.With the use of the PLC, the project wins agility, because it is possible to create and simulate the system as many times as needed. Therefore, time can be saved, risk of mistakes reduced and complexity can be increased using the same elements.A conventional PLC, that is possible to find on the market from many companies, offers many resources to control not only pneumatic systems, but all kinds of system that uses electrical components. The PLC can be very versatile and robust to be applied in many kinds of application in the industry or even security system and automation of buildings.Because of those characteristics, in some applications the PLC offers to much resources that are not even used to control the system, electro-pneumatic system is one of this kind of application. The use of PLC, especially for small size systems, can be very expensive for the automation project.An alternative in this case is to create a specific controller that can offer the exactly size and resources that the project needs [3, 4]. This can be made using microcontrollers as the base of this controller.The controller, based on microcontroller, can be very specific and adapted to only one kind of machine or it can work as a generic controller that can be programmed as a usual PLC and work with logic that can be changed. All these characteristics depend on what is needed and how much experience the designer has with developing an electronic circuit and firmware for microcontroller. But the main advantage of design the controller with the microcontroller is that the designer has the total knowledge of his controller, which makes it possible to control the size of the controller, change the complexity and the application of it. It means that the project gets more independence from other companies, but at the same time the responsibility of the control of the system stays at the designer hands2. Electro-pneumatic systemOn automation system one can find three basic components mentioned before, plus a logic circuit that controls the system. An adequate technique is needed to project the logic circuit and integrate all the necessary components to execute the sequence of movements properly.For a simple direct sequence of movement an intuitive method can be used [1, 5], but for indirect or more complex sequences the intuition can generate a very complicated circuit and signal mistakes. It is necessary to use another method that can save time of the project, makea clean circuit, can eliminate occasional signal overlapping and redundant circuits. The presented method is called step-by-step or algorithmic [1, 5], it is valid for pneumatic and electro-pneumatic systems and it was used as a base in this work.The method consists of designing the systems based on standard circuits made for each change on the state of the actuators, these changes are called steps.The first part is to design those kinds of standard circuits for each step, the next task is to link the standard circuits and the last part is to connect the control elements that receive signals from sensors, switches and the previous movements, and give the air or electricity to the supply lines of each step. In Figs. 1 and 2 the standard circuits are drawn for pneumatic and electro-pneumatic system [8]. It is possible to see the relations with the previous and the next steps.3. The method applied inside the controllerThe result of the method presented before is a sequence of movements of the actuator that is well defined by steps. It means that each change on the position of the actuators is a new state of the system and the transition between states is called step.The standard circuit described before helps the designer to define the states of the systems and to define the condition to each change betweenthe states. In the end of the design, the system is defined by a sequencethat never chances and states that have the inputs and the outputs well defined. The inputs are the condition for the transition and the outputs are the result of the transition.All the configuration of those steps stays inside of the microcontroller and is executed the same way it was designed. The sequences of strings are programmed inside the controller with 5 bytes; each string has the configuration of one step of the process. There are two bytes for the inputs, one byte for the outputs and two more for the other configurations and auxiliary functions of the step. After programming, this sequence of strings is saved inside of a non-volatile memory of the microcontroller, so they can be read and executed.The controller task is not to work in the same way as a conventional PLC, but the purpose of it is to be an example of a versatile controller that is design for an specific area. A conventional PLC process the control of the system using a cycle where it makes an image of the inputs, execute all the conditions defined by the configuration programmed inside, and then update the state of the outputs. This controller works in a different way, where it read the configuration of the step, wait the condition of inputs to be satisfied, then update the state or the outputs and after that jump to the next step and start the process again.It can generate some limitations, as the fact that this controller cannot execute, inside the program, movements that must be repeated for some time, but this problem can be solved with some external logic components. Another limitation is that the controller cannot be applied on systems that have no sequence. These limitations are a characteristic of the system that must be analyzed for each application.4. Characteristics of the controllerThe controller is based on the MICROCHIP microcontroller PIC16F877 [6,7] with 40 pins, and it has all the resources needed for thisproject .It has enough pins for all the components, serial communication implemented in circuit, EEPROM memory to save all the configuration of the system and the sequence of steps. For the execution of the main program, it offers complete resources as timers and interruptions.The list of resources of the controller was created to explore all the capacity of the microcontroller to make it as complete as possible. During the step, the program chooses how to use the resources reading the configuration string of the step. This string has two bytes for digital inputs, one used as a mask and the other one used as a value expected. One byte is used to configure the outputs value. One bytes more is used for the internal timer , the analog input or time-out. The EEPROM memory inside is 256 bytes length that is enough to save the string of the steps, with this characteristic it is possible to save between 48 steps (Table 1).The controller (Fig.3) has also a display and some buttons that are used with an interactive menu to program the sequence of steps and other configurations.4.1. Interaction componentsFor the real application the controller must have some elements to interact with the final user and to offer a complete monitoring of the system resources that are available to the designer while creating the logic control of the pneumatic system (Fig.3):•Interactive mode of work; function available on the main program for didactic purposes, the user gives the signal to execute the step. •LCD display, which shows the status of the system, values of inputs, outputs, timer and statistics of the sequence execution.•Beep to give important alerts, stop, start and emergency.• Leds to show power on and others to show the state of inputs and outputs.4.2. SecurityTo make the final application works property, a correct configuration to execute the steps in the right way is needed, but more then that itmust offer solutions in case of bad functioning or problems in the execution of the sequence. The controller offers the possibility to configure two internal virtual circuits that work in parallel to the principal. These two circuits can be used as emergency or reset buttons and can return the system to a certain state at any time [2]. There are two inputs that work with interruption to get an immediate access to these functions. It is possible to configure the position, the buttons and the value of time-out of the system.4.3. User interfaceThe sequence of strings can be programmed using the interface elements of the controller. A Computer interface can also be used to generate the user program easily. With a good documentation the final user can use the interface to configure the strings of bytes that define the steps of the sequence. But it is possible to create a program with visual resources that works as a translator to the user, it changes his work to the values that the controller understands.To implement the communication between the computer interface and the controller a simple protocol with check sum and number of bytes is the minimum requirements to guarantee the integrity of the data.4.4. FirmwareThe main loop works by reading the strings of the steps from the EEPROM memory that has all the information about the steps.In each step, the status of the system is saved on the memory and it is shown on the display too. Depending of the user configuration, it can use the interruption to work with the emergency circuit or time-out to keep the system safety. In Fig.4,a block diagram of micro controller main program is presented.5. Example of electro-pneumatic systemThe system is not a representation of a specific machine, but it is made with some common movements and components found in a real one. The system is composed of four actuators. The actuators A, B and C are double acting and D-single acting. Actuator A advances and stays in specified position till the end of the cycle, it could work fixing an object to the next action for example (Fig. 5) , it is the first step. When A reaches the end position, actuator C starts his work together with B, making as many cycles as possible during the advancing of B. It depends on how fastactuator B is advancing; the speed is regulated by a flowing control valve. It was the second step. B and C are examples of actuators working together, while B pushes an object slowly, C repeats its work for some time.When B reaches the final position, C stops immediately its cycle and comes back to the initial position. The actuator D is a single acting one with spring return and works together with the back of C, it is the third step. D works making very fast forward and backward movement, just one time. Its backward movement is the fourth step. D could be a tool to make a hole on the object.When D reaches the initial position, A and B return too, it is the fifth step.Fig. 6 shows the first part of the designing process where all the movements of each step should be defined [2]. (A+) means that the actuator A moves to the advanced position and (A−) to the initial position. The movements that happen at the same time are joined together in the same step. The system has five steps.These two representations of the system (Figs. 5 and 6) together are enough to describe correctly all the sequence. With them is possible to design the whole control circuit with the necessary logic components. But till this time, it is not a complete system, because it is missing some auxiliary elements that are not included in this draws because they work in parallel with the main sequence.These auxiliary elements give more function to the circuit and are very important to the final application; the most important of them is the parallel circuit linked with all the others steps. That circuit should be able to stop the sequence at any time and change the state of the actuators to a specific position. This kind of circuit can be used as a reset or emergency buttons.The next Figs. 7 and 8 show the result of using the method without the controller. These pictures are the electric diagram of the control circuit of the example, including sensors, buttons and the coils of the electrical valves.The auxiliary elements are included, like the automatic/manual switcher that permit a continuous work and the two start buttons that make the operator of a machine use their two hands to start the process, reducing the risk of accidents.6. Changing the example to a user programIn the previous chapter, the electro-pneumatic circuits were presented, used to begin the study of the requires to control a system that work with steps and must offer all the functional elements to be used in a real application. But, as explained above, using a PLC or this specific controller, the control becomes easier and the complexity can be increasealso.Table 2 shows a resume of the elements that are necessary to control the presented example.With the time diagram, the step sequence and the elements of the system described in Table 2 and Figs. 5 and 6 it is possible to create the configuration of the steps that can be sent to the controller (Tables 3 and 4).While using a conventional PLC, the user should pay attention to the logic of the circuit when drawing the electric diagram on the interface (Figs. 7 and 8), using the programmable controller, described in this work, the user must know only the concept o f the method and program only the configuration of each step.It means that, with a conventional PLC, the user must draw the relationbetween the lines and the draw makes it hard to differentiate the steps of the sequence. Normally, one needs to execute a simulation on the interface to find mistakes on the logicThe new programming allows that the configuration of the steps be separated, like described by the method. The sequence is defined by itself and the steps are described only by the inputs and outputs for each step.The structure of the configuration follows the order:1-byte: features of the step;2-byte: mask for the inputs;3-byte: value expected on the inputs;4-byte: value for the outputs;5-byte: value for the extra function.Table 5 shows how the user program is saved inside the controller, this is the program that describes the control of the example shown before.The sequence can be defined by 25 bytes. These bytes can be dividedin five strings with 5 bytes each that define each step of the sequence (Figs. 9 and 10).7. ConclusionThe controller developed for this work (Fig. 11) shows that it is possible to create a very useful programmable controller based on microcontroller. External memories or external timers were not used in case to explore the resources that the microcontroller offers inside. Outside the microcontroller, there are only components to implement the outputs, inputs, analog input, display for the interface and the serial communication.Using only the internal memory, it is possible to control a pneumatic system that has a sequence with 48 steps if all the resources for all steps are used, but it is possible to reach sixty steps in the case of a simpler system.The programming of the controller does not use PLC languages, but a configuration that is simple and intuitive. With electro-pneumatic system, the programming follows the same technique that was used before to design the system, but here the designer work s directly with the states or steps of the system.With a very simple machine language the designer can define all the configuration of the step using four or five bytes. It depends only on his experience to use all the resources of the controller.The controller task is not to work in the same way as a commercial PLC but the purpose of it is to be an example of a versatile controller that is designed for a specific area. Because of that, it is not possible to say which one works better; the system made with microcontroller is an alternative that works in a simple way.应用于电气系统的可编程序控制器约翰 F.维克里此项目主要是研究电气系统以及简单有效的控制气流发动机的程序和气流系统的状态。

电气工程及其自动化专业 外文文献 英文文献 外文翻译 plc方面

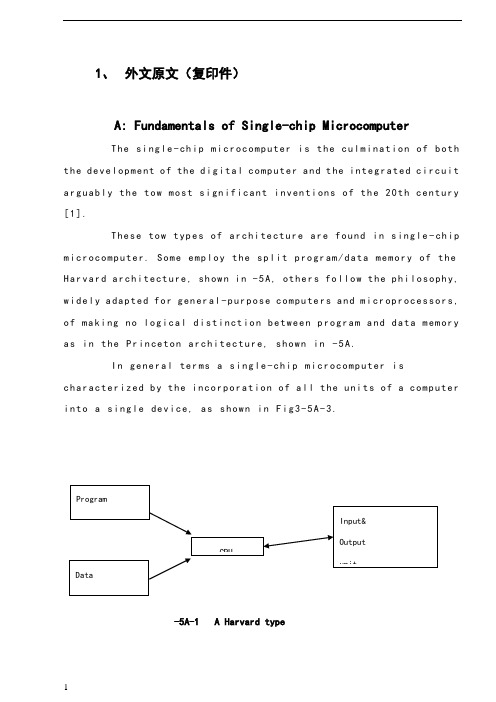

1、外文原文(复印件)A: Fundamentals of Single-chip MicrocomputerTh e si ng le-ch i p mi cr oc om pu ter is t he c ul mi nat i on o f bo th t h e d ev el op me nt o f th e d ig it al com p ut er an d t he int e gr at ed ci rc ui ta r gu ab ly th e t ow m os t s i gn if ic ant i nv en ti on s o f t h e 20t h c en tu ry[1].Th es e to w typ e s of a rc hi te ctu r e ar e fo un d i n s in gl e-ch ip m i cr oc om pu te r. So m e em pl oy t he sp l it p ro gr am/d ata me mo ry o f th e H a rv ar d ar ch it ect u re, sh ow n i n -5A, ot he rs fo ll ow th e ph i lo so ph y, w i de ly a da pt ed fo r g en er al-p ur pos e c om pu te rs an d m i cr op ro ce ss or s, o f m a ki ng no lo gi c al di st in ct io n b e tw ee n p ro gr am a n d da t a m em ory a s i n th e Pr in cet o n ar ch it ec tu re,sh ow n in-5A.In g en er al te r ms a s in gl e-chi p m ic ro co mp ut er i sc h ar ac te ri zed b y the i nc or po ra tio n of al l t he uni t s o f a co mp ut er i n to a s in gl e dev i ce, as s ho wn in Fi g3-5A-3.-5A-1 A Harvard type-5A. A conventional Princeton computerFig3-5A-3. Principal features of a microcomputerRead only memory (ROM).R OM i s u su al ly f or th e p er ma ne nt, n o n-vo la ti le s tor a ge o f an a pp lic a ti on s pr og ra m .M an ym i cr oc om pu te rs an d mi cr oc on tr ol le r s a re in t en de d fo r h ig h-v ol ume a p pl ic at io ns a nd h en ce t he e co nom i ca l ma nu fa ct ure of t he d ev ic es r e qu ir es t ha t the co nt en ts o f the pr og ra m me mo ry b e co mm it te dp e rm an en tl y d ur in g th e m an uf ac tu re o f c hi ps . Cl ear l y, th is im pl ie sa ri g or ou s a pp roa c h t o R OM co de d e ve lo pm en t s in ce c ha ng es ca nn otb e m ad e af te r man u fa ct ur e .T hi s d e ve lo pm en t pr oce s s ma y in vo lv e e m ul at io n us in g a s op hi st ic at ed deve lo pm en t sy st em w i th a ha rd wa re e m ul at io n ca pa bil i ty a s we ll a s th e u se of po we rf ul so ft wa re t oo ls.So me m an uf act u re rs p ro vi de ad d it io na l RO M opt i on s byi n cl ud in g i n th ei r ra ng e de vi ce s wi th (or i nt en de d fo r us e wi th) u s er pr og ra mm ab le m em or y. Th e s im p le st of th es e i s us ua ll y d ev ice w h ic h ca n op er ate in a m ic ro pr oce s so r mo de b y usi n g so me o f th e i n pu t/ou tp ut li ne s as a n ad dr es s an d da ta b us f or acc e ss in g e xt er na l m e mo ry. T hi s t ype o f d ev ic e c an b e ha ve fu nc ti on al l y a s t he si ng le c h ip mi cr oc om pu te r fr om wh ic h i t i s de ri ve d a lb eit w it h r es tr ic ted I/O an d a mo di fie d e xt er na l ci rcu i t. T he u se o f t h es e RO Ml es sd e vi ce s is c om mo n e ve n in p ro du ct io n c ir cu it s wh er e t he v ol um e do es n o t ju st if y th e d e ve lo pm en t co sts of c us to m on-ch i p RO M[2];t he re c a n st il l b e a si g ni fi ca nt s a vi ng in I/O a nd ot he r c hi ps co mp ar ed t o a c on ve nt io nal mi cr op ro ce ss or b as ed c ir cu it. M o re e xa ctr e pl ac em en t fo r RO M d ev ic es c an b e o bt ai ne d in t he f o rm o f va ri an ts w i th 'pi gg y-ba ck'EP RO M(Er as ab le p ro gr am ma bl e ROM)s oc ke ts o rd e vi ce s w it h EP ROM i ns te ad o f R OM 。

电子类文献中英文翻译

外文翻译原文:Progress in ComputersThe first stored program computers began to work around 1950. The one we built in Cambridge, the EDSAC was first used in the summer of 1949.These early experimental computers were built by people like myself with varying backgrounds. We all had extensive experience in electronic engineering and were confident that that experience would stand us in good stead. This proved true, although we had some new things to learn. The most important of these was that transients must be treated correctly; what would cause a harmless flash on the screen of a television set could lead to a serious error in a computer.As far as computing circuits were concerned, we found ourselves with an embarass de richess. For example, we could use vacuum tube diodes for gates as we did in the EDSAC or pentodes with control signals on both grids, a system widely used elsewhere. This sort of choice persisted and the term families of logic came into use. Those who have worked in the computer field will remember TTL, ECL and CMOS. Of these, CMOS has now become dominant.In those early years, the IEE was still dominated by power engineering and we had to fight a number of major battles in order to get radio engineering along with the rapidly developing subject of electronics.dubbed in the IEE light current electrical engineering.properly recognised as an activity in its own right. I remember that we had some difficulty in organising a conference because the power engineers’ ways of doing things were not our ways. A minor source of irritation was that all IEE published papers were expected to start with a lengthy statement of earlier practice, something difficult to do when there was no earlier practice Consolidation in the 1960sBy the late 50s or early 1960s, the heroic pioneering stage was over and the computer field was starting up in real earnest. The number of computers in the worldhad increased and they were much more reliable than the very early ones . To those years we can ascribe the first steps in high level languages and the first operating systems. Experimental time-sharing was beginning, and ultimately computer graphics was to come along.Above all, transistors began to replace vacuum tubes. This change presented a formidable challenge to the engineers of the day. They had to forget what they knew about circuits and start again. It can only be said that they measured up superbly well to the challenge and that the change could not have gone more smoothly.Soon it was found possible to put more than one transistor on the same bit of silicon, and this was the beginning of integrated circuits. As time went on, a sufficient level of integration was reached for one chip to accommodate enough transistors for a small number of gates or flip flops. This led to a range of chips known as the 7400 series. The gates and flip flops were independent of one another and each had its own pins. They could be connected by off-chip wiring to make a computer or anything else.These chips made a new kind of computer possible. It was called a minicomputer. It was something less that a mainframe, but still very powerful, and much more affordable. Instead of having one expensive mainframe for the whole organisation, a business or a university was able to have a minicomputer for each major department.Before long minicomputers began to spread and become more powerful. The world was hungry for computing power and it had been very frustrating for industry not to be able to supply it on the scale required and at a reasonable cost. Minicomputers transformed the situation.The fall in the cost of computing did not start with the minicomputer; it had always been that way. This was what I meant when I referred in my abstract to inflation in the computer industry ‘going the other way’. As time goes on people get more for their money, not less.Research in Computer Hardware.The time that I am describing was a wonderful one for research in computer hardware. The user of the 7400 series could work at the gate and flip-flop level and yet the overall level of integration was sufficient to give a degree of reliability far above that of discreet transistors. The researcher, in a university or elsewhere, could build any digital device that a fertile imagination could conjure up. In the Computer Laboratory we built the Cambridge CAP, a full-scale minicomputerwith fancy capability logic.The 7400 series was still going strong in the mid 1970s and was used for the Cambridge Ring, a pioneering wide-band local area network. Publication of the design study for the Ring came just before the announcement of the Ethernet. Until these two systems appeared, users had mostly been content with teletype-based local area networks.Rings need high reliability because, as the pulses go repeatedly round the ring, they must be continually amplified and regenerated. It was the high reliability provided by the 7400 series of chips that gave us the courage needed to embark on the project for the Cambridge Ring.The RISC Movement and Its AftermathEarly computers had simple instruction sets. As time went on designers of commercially available machines added additional features which they thought would improve performance. Few comparative measurements were done and on the whole the choice of features depended upo n the designer’s intuition.In 1980, the RISC movement that was to change all this broke on the world. The movement opened with a paper by Patterson and Ditzel entitled The Case for the Reduced Instructions Set Computer.Apart from leading to a striking acronym, this title conveys little of the insights into instruction set design which went with the RISC movement, in particular the way it facilitated pipelining, a system whereby several instructions may be in different stages of execution within the processor at the same time. Pipelining was not new, but it was new for small computersThe RISC movement benefited greatly from methods which had recently become available for estimating the performance to be expected from a computer design without actually implementing it. I refer to the use of a powerful existing computer to simulate the new design. By the use of simulation, RISC advocates were able to predict with some confidence that a good RISC design would be able to out-perform the best conventional computers using the same circuit technology. This prediction was ultimately born out in practice.Simulation made rapid progress and soon came into universal use by computer designers. In consequence, computer design has become more of a science and less of an art. Today, designers expect to have a roomful of, computers available to do their simulations, not just one. They refer to such a roomful by the attractive nameof computer farm.The x86 Instruction SetLittle is now heard of pre-RISC instruction sets with one major exception, namely that of the Intel 8086 and its progeny, collectively referred to as x86. This has become the dominant instruction set and the RISC instruction sets that originally had a considerable measure of success are having to put up a hard fight for survival.This dominance of x86 disappoints people like myself who come from the research wings.both academic and industrial.of the computer field. No doubt, business considerations have a lot to do with the survival of x86, but there are other reasons as well. However much we research oriented people would like to think otherwise. high level languages have not yet eliminated the use of machine code altogether. We need to keep reminding ourselves that there is much to be said for strict binary compatibility with previous usage when that can be attained. Nevertheless, things might have been different if Intel’s major attempt to produce a good RISC chip had been more successful. I am referring to the i860 (not the i960, which was something different). In many ways the i860 was an excellent chip, but its software interface did not fit it to be used in a workstation.There is an interesting sting in the tail of this apparently easy triumph of the x86 instruction set. It proved impossible to match the steadily increasing speed of RISC processors by direct implementation of the x86 instruction set as had been done in the past. Instead, designers took a leaf out of the RISC book; although it is not obvious, on the surface, a modern x86 processor chip contains hidden within it a RISC-style processor with its own internal RISC coding. The incoming x86 code is, after suitable massaging, converted into this internal code and handed over to the RISC processor where the critical execution is performed.In this summing up of the RISC movement, I rely heavily on the latest edition of Hennessy and Patterson’s books on computer design as my supporting authority; see in particular Computer Architecture, third edition, 2003, pp 146, 151-4, 157-8.The IA-64 instruction set.Some time ago, Intel and Hewlett-Packard introduced the IA-64 instruction set. This was primarily intended to meet a generally recognised need for a 64 bit address space. In this, it followed the lead of the designers of the MIPS R4000 and Alpha. However one would have thought that Intel would have stressed compatibility with the x86; the puzzle is that they did the exact opposite.Moreover, built into the design of IA-64 is a feature known as predication which makes it incompatible in a major way with all other instruction sets. In particular, it needs 6 extra bits with each instruction. This upsets the traditional balance between instruction word length and information content, and it changes significantly the brief of the compiler writer.In spite of having an entirely new instruction set, Intel made the puzzling claim that chips based on IA-64 would be compatible with earlier x86 chips. It was hard to see exactly what was meant.Chips for the latest IA-64 processor, namely, the Itanium, appear to have special hardware for compatibility. Even so, x86 code runs very slowly.Because of the above complications, implementation of IA-64 requires a larger chip than is required for more conventional instruction sets. This in turn implies a higher cost. Such at any rate, is the received wisdom, and, as a general principle, it was repeated as such by Gordon Moore when he visited Cambridge recently to open the Betty and Gordon Moore Library. I have, however, heard it said that the matter appears differently from within Intel. This I do not understand. But I am very ready to admit that I am completely out of my depth as regards the economics of the semiconductor industry.AMD have defined a 64 bit instruction set that is more compatible with x86 and they appear to be making headway with it. The chip is not a particularly large one. Some people think that this is what Intel should have done. [Since the lecture was delivered, Intel have announced that they will market a range of chips essentially compatible with those offered by AMD.]The Relentless Drive towards Smaller TransistorsThe scale of integration continued to increase. This was achieved by shrinking the original transistors so that more could be put on a chip. Moreover, the laws of physics were on the side of the manufacturers. The transistors also got faster, simply by getting smaller. It was therefore possible to have, at the same time, both high density and high speed.There was a further advantage. Chips are made on discs of silicon, known as wafers. Each wafer has on it a large number of individual chips, which are processed together and later separated. Since shrinkage makes it possible to get more chips on a wafer, the cost per chip goes down.Falling unit cost was important to the industry because, if the latest chipsare cheaper to make as well as faster, there is no reason to go on offering the old ones, at least not indefinitely. There can thus be one product for the entire market.However, detailed cost calculations showed that, in order to maintain this advantage as shrinkage proceeded beyond a certain point, it would be necessary to move to larger wafers. The increase in the size of wafers was no small matter. Originally, wafers were one or two inches in diameter, and by 2000 they were as much as twelve inches. At first, it puzzled me that, when shrinkage presented so many other problems, the industry should make things harder for itself by going to larger wafers. I now see that reducing unit cost was just as important to the industry as increasing the number of transistors on a chip, and that this justified the additional investment in foundries and the increased risk.The degree of integration is measured by the feature size, which, for a given technology, is best defined as the half the distance between wires in the densest chips made in that technology. At the present time, production of 90 nm chips is still building upSuspension of LawIn March 1997, Gordon Moore was a guest speaker at the celebrations of the centenary of the discovery of the electron held at the Cavendish Laboratory. It was during the course of his lecture that I first heard the fact that you can have silicon chips that are both fast and low in cost described as a violation of Murphy’s law.or Sod’s law as it is usually called in the UK. Moore said that experience in other fields would lead you to expect to have to choose between speed and cost, or to compromise between them. In fact, in the case of silicon chips, it is possible to have both.In a reference book available on the web, Murphy is identified as an engineer working on human acceleration tests for the US Air Force in 1949. However, we were perfectly familiar with the law in my student days, when we called it by a much more prosaic name than either of those mentioned above, namely, the Law of General Cussedness. We even had a mock examination question in which the law featured. It was the type of question in which the first part asks for a definition of some law or principle and the second part contains a problem to be solved with the aid of it. In our case the first part was to define the Law of General Cussedness and the second was the problem;A cyclist sets out on a circular cycling tour. Derive an equation giving the direction of the wind at any time.The single-chip computerAt each shrinkage the number of chips was reduced and there were fewer wires going from one chip to another. This led to an additional increment in overall speed, since the transmission of signals from one chip to another takes a long time.Eventually, shrinkage proceeded to the point at which the whole processor except for the caches could be put on one chip. This enabled a workstation to be built that out-performed the fastest minicomputer of the day, and the result was to kill the minicomputer stone dead. As we all know, this had severe consequences for the computer industry and for the people working in it.From the above time the high density CMOS silicon chip was Cock of the Roost. Shrinkage went on until millions of transistors could be put on a single chip and the speed went up in proportion.Processor designers began to experiment with new architectural features designed to give extra speed. One very successful experiment concerned methods for predicting the way program branches would go. It was a surprise to me how successful this was. It led to a significant speeding up of program execution and other forms of prediction followedEqually surprising is what it has been found possible to put on a single chip computer by way of advanced features. For example, features that had been developed for the IBM Model 91.the giant computer at the top of the System 360 range.are now to be found on microcomputersMurphy’s Law remained in a state of suspension. No longer did it make se nse to build experimental computers out of chips with a small scale of integration, such as that provided by the 7400 series. People who wanted to do hardware research at the circuit level had no option but to design chips and seek for ways to get them made. For a time, this was possible, if not easyUnfortunately, there has since been a dramatic increase in the cost of making chips, mainly because of the increased cost of making masks for lithography, a photographic process used in the manufacture of chips. It has, in consequence, again become very difficult to finance the making of research chips, and this is a currently cause for some concern.The Semiconductor Road MapThe extensive research and development work underlying the above advances has been made possible by a remarkable cooperative effort on the part of theinternational semiconductor industry.At one time US monopoly laws would probably have made it illegal for US companies to participate in such an effort. However about 1980 significant and far reaching changes took place in the laws. The concept of pre-competitive research was introduced. Companies can now collaborate at the pre-competitive stage and later go on to develop products of their own in the regular competitive manner.The agent by which the pre-competitive research in the semi-conductor industry is managed is known as the Semiconductor Industry Association (SIA). This has been active as a US organisation since 1992 and it became international in 1998. Membership is open to any organisation that can contribute to the research effort.Every two years SIA produces a new version of a document known as the International Technological Roadmap for Semiconductors (ITRS), with an update in the intermediate years. The first volume bearing the title ‘Roadmap’ was issued in 1994 but two reports, written in 1992 and distributed in 1993, are regarded as the true beginning of the series.Successive roadmaps aim at providing the best available industrial consensus on the way that the industry should move forward. They set out in great detail.over a 15 year horizon. the targets that must be achieved if the number of components on a chip is to be doubled every eighteen months.that is, if Moore’s law is to be maintained.-and if the cost per chip is to fall.In the case of some items, the way ahead is clear. In others, manufacturing problems are foreseen and solutions to them are known, although not yet fully worked out; these areas are coloured yellow in the tables. Areas for which problems are foreseen, but for which no manufacturable solutions are known, are coloured red. Red areas are referred to as Red Brick Walls.The targets set out in the Roadmaps have proved realistic as well as challenging, and the progress of the industry as a whole has followed the Roadmaps closely. This is a remarkable achievement and it may be said that the merits of cooperation and competition have been combined in an admirable manner.It is to be noted that the major strategic decisions affecting the progress of the industry have been taken at the pre-competitive level in relative openness, rather than behind closed doors. These include the progression to larger wafers.By 1995, I had begun to wonder exactly what would happen when the inevitable point was reached at which it became impossible to make transistors any smaller.My enquiries led me to visit ARPA headquarters in Washington DC, where I was given a copy of the recently produced Roadmap for 1994. This made it plain that serious problems would arise when a feature size of 100 nm was reached, an event projected to happen in 2007, with 70 nm following in 2010. The year for which the coming of 100 nm (or rather 90 nm) was projected was in later Roadmaps moved forward to 2004 and in the event the industry got there a little sooner.I presented the above information from the 1994 Roadmap, along with such other information that I could obtain, in a lecture to the IEE in London, entitled The CMOS end-point and related topics in Computing and delivered on 8 February 1996.The idea that I then had was that the end would be a direct consequence of the number of electrons available to represent a one being reduced from thousands to a few hundred. At this point statistical fluctuations would become troublesome, and thereafter the circuits would either fail to work, or if they did work would not be any faster. In fact the physical limitations that are now beginning to make themselves felt do not arise through shortage of electrons, but because the insulating layers on the chip have become so thin that leakage due to quantum mechanical tunnelling has become troublesome.There are many problems facing the chip manufacturer other than those that arise from fundamental physics, especially problems with lithography. In an update to the 2001 Roadmap published in 2002, it was stated that the continuation of progress at present rate will be at risk as we approach 2005 when the roadmap projects that progress will stall without research break-throughs in most technical areas “. This was the most specific statement about the Red Brick Wall, that had so far come from the SIA and it was a strong one. The 2003 Roadmap reinforces this statement by showing many areas marked red, indicating the existence of problems for which no manufacturable solutions are known.It is satisfactory to report that, so far, timely solutions have been found to all the problems encountered. The Roadmap is a remarkable document and, for all its frankness about the problems looming above, it radiates immense confidence. Prevailing opinion reflects that confidence and there is a general expectation that, by one means or another, shrinkage will continue, perhaps down to 45 nm or even less.However, costs will rise steeply and at an increasing rate. It is cost that will ultimately be seen as the reason for calling a halt. The exact point at which an industrial consensus is reached that the escalating costs can no longer be met willdepend on the general economic climate as well as on the financial strength of the semiconductor industry itself.。

电气 自动化 外文文献 外文翻译 英文文献

外文出处:Farhadi, A. (2008). Modeling, simulation, and reduction of conducted electromagnetic interference due to a pwm buck type switching power supply. Harmonics and Quality of Power, 2008. ICHQP 2008. 13th International Conference on, 1 - 6.Modeling, Simulation, and Reduction of Conducted Electromagnetic Interference Due to a PWM Buck Type Switching Power Supply IA. FarhadiAbstract:Undesired generation of radiated or conducted energy in electrical systems is called Electromagnetic Interference (EMI). High speed switching frequency in power electronics converters especially in switching power supplies improves efficiency but leads to EMI. Different kind of conducted interference, EMI regulations and conducted EMI measurement are introduced in this paper. Compliancy with national or international regulation is called Electromagnetic Compatibility (EMC). Power electronic systems producers must regard EMC. Modeling and simulation is the first step of EMC evaluation. EMI simulation results due to a PWM Buck type switching power supply are presented in this paper. To improve EMC, some techniques are introduced and their effectiveness proved by simulation.Index Terms:Conducted, EMC, EMI, LISN, Switching SupplyI. INTRODUCTIONFAST semiconductors make it possible to have high speed and high frequency switching in power electronics []1. High speed switching causes weight and volume reduction of equipment, but some unwanted effects such as radio frequency interference appeared []2. Compliance with electromagnetic compatibility (EMC) regulations is necessary for producers to present their products to the markets. It is important to take EMC aspects already in design phase []3. Modeling and simulation is the most effective tool to analyze EMC consideration before developing the products. A lot of the previous studies concerned the low frequency analysis of power electronics components []4[]5. Different types of power electronics converters are capable to be considered as source of EMI. They could propagate the EMI in both radiated and conducted forms. Line Impedance Stabilization Network (LISN) is required for measurement and calculation of conducted interference level []6. Interference spectrum at the output of LISN is introduced as the EMC evaluation criterion []7[]8. National or international regulations are the references forthe evaluation of equipment in point of view of EMC []7[]8.II. SOURCE, PATH AND VICTIM OF EMIUndesired voltage or current is called interference and their cause is called interference source. In this paper a high-speed switching power supply is the source of interference.Interference propagated by radiation in area around of an interference source or by conduction through common cabling or wiring connections. In this study conducted emission is considered only. Equipment such as computers, receivers, amplifiers, industrial controllers, etc that are exposed to interference corruption are called victims. The common connections of elements, source lines and cabling provide paths for conducted noise or interference. Electromagnetic conducted interference has two components as differential mode and common mode []9.A. Differential mode conducted interferenceThis mode is related to the noise that is imposed between different lines of a test circuit by a noise source. Related current path is shown in Fig. 1 []9. The interference source, path impedances, differential mode current and load impedance are also shown in Fig. 1.B. Common mode conducted interferenceCommon mode noise or interference could appear and impose between the lines, cables or connections and common ground. Any leakage current between load and common ground couldbe modeled by interference voltage source.Fig. 2 demonstrates the common mode interference source, common mode currents Iandcm1 and the related current paths[]9.The power electronics converters perform as noise source Icm2between lines of the supply network. In this study differential mode of conducted interference is particularly important and discussion will be continued considering this mode only.III. ELECTROMAGNETIC COMPATIBILITY REGULATIONS Application of electrical equipment especially static power electronic converters in different equipment is increasing more and more. As mentioned before, power electronics converters are considered as an important source of electromagnetic interference and have corrupting effects on the electric networks []2. High level of pollution resulting from various disturbances reduces the quality of power in electric networks. On the other side some residential, commercial and especially medical consumers are so sensitive to power system disturbances including voltage and frequency variations. The best solution to reduce corruption and improve power quality is complying national or international EMC regulations. CISPR, IEC, FCC and VDE are among the most famous organizations from Europe, USA and Germany who are responsible for determining and publishing the most important EMC regulations. IEC and VDE requirement and limitations on conducted emission are shown in Fig. 3 and Fig. 4 []7[]9.For different groups of consumers different classes of regulations could be complied. Class Afor common consumers and class B with more hard limitations for special consumers are separated in Fig. 3 and Fig. 4. Frequency range of limitation is different for IEC and VDE that are 150 kHz up to 30 MHz and 10 kHz up to 30 MHz respectively. Compliance of regulations is evaluated by comparison of measured or calculated conducted interference level in the mentioned frequency range with the stated requirements in regulations. In united European community compliance of regulation is mandatory and products must have certified label to show covering of requirements []8.IV. ELECTROMAGNETIC CONDUCTED INTERFERENCE MEASUREMENTA. Line Impedance Stabilization Network (LISN)1-Providing a low impedance path to transfer power from source to power electronics converter and load.2-Providing a low impedance path from interference source, here power electronics converter, to measurement port.Variation of LISN impedance versus frequency with the mentioned topology is presented inFig. 7. LISN has stabilized impedance in the range of conducted EMI measurement []7.Variation of level of signal at the output of LISN versus frequency is the spectrum of interference. The electromagnetic compatibility of a system can be evaluated by comparison of its interference spectrum with the standard limitations. The level of signal at the output of LISN in frequency range 10 kHz up to 30 MHz or 150 kHz up to 30 MHz is criterion of compatibility and should be under the standard limitations. In practical situations, the LISN output is connected to a spectrum analyzer and interference measurement is carried out. But for modeling and simulation purposes, the LISN output spectrum is calculated using appropriate software.基于压降型PWM开关电源的建模、仿真和减少传导性电磁干扰摘要:电子设备之中杂乱的辐射或者能量叫做电磁干扰(EMI)。

电气工程及其自动化专业外文文献英文文献外文翻译方面

1、 外文原文(复印件)A: Fundamentals of Single-chip MicrocomputerT h e sin gle -ch ip mi c ro co m p u t e r is t h e cu lm in at io n of b ot h t h e d e ve lo p me nt of t h e d ig ita l co m p u t e r a n d t h e i nte g rated c ircu it a rgu ab l y t h e to w mo st s ign if i cant i nve nt i o n s of t h e 20t h c e nt u ry [1].T h ese to w t yp e s of arch ite ct u re are fo u n d in s in gle -ch ip m i cro co m p u te r. S o m e e mp l oy t h e sp l it p ro gra m /d at a m e m o r y of t h e H a r va rd arch ite ct u re , s h o wn in -5A , ot h e rs fo l lo w t h e p h i lo so p hy, wid e l y ad a p ted fo r ge n e ral -p u rp o se co m p u te rs an d m i cro p ro ce ss o rs , of m a kin g n o l o g i ca l d i st in ct i o n b et we e n p ro gra m an d d ata m e m o r y as in t h e P rin c eto n a rch ite ct u re , sh o wn in -5A.In ge n e ra l te r m s a s in g le -ch ip m ic ro co m p u t e r is ch a ra cte r ized b y t h e in co r p o rat io n of all t h e u n its of a co mp u te r into a s in gle d e vi ce , as s h o w n in F i g3-5A-3.-5A-1A Harvard type-5A. A conventional Princeton computerProgrammemory Datamemory CPU Input& Output unitmemoryCPU Input& Output unitResetInterruptsPowerFig3-5A-3. Principal features of a microcomputerRead only memory (ROM).RO M is u su a l l y fo r t h e p e r m an e nt , n o n -vo lat i le sto rage of an ap p l i cat io n s p ro g ram .M a ny m i c ro co m p u te rs a n d m i cro co nt ro l le rs are inte n d ed fo r h i gh -vo lu m e ap p l i cat io n s a n d h e n ce t h e e co n o m i cal man u fa c t u re of t h e d e vi ces re q u ires t h at t h e co nt e nts of t h e p ro gra m me mo r y b e co mm i ed p e r m a n e nt l y d u r in g t h e m a n u fa ct u re of c h ip s . C lea rl y, t h i s imp l ies a r i go ro u s ap p ro a ch to ROM co d e d e ve lo p m e nt s in ce ch an ges can n o t b e mad e af te r m an u fa ct u re .T h i s d e ve l o p m e nt p ro ces s m ay i nvo l ve e mu l at i o n u sin g a so p h ist icated d e ve lo p m e nt syste m wit h a h ard wa re e mu l at i o n capab i l it y as we ll as t h e u s e of p o we rf u l sof t war e to o l s.So m e m an u fa ct u re rs p ro vi d e ad d it i o n a l ROM o p t io n s b y in clu d in g in t h e i r ran ge d e v ic es w it h (o r inte n d ed fo r u s e wit h ) u se r p ro g ram m a b le m e mo r y. T h e s im p lest of t h e se i s u su a l l y d e v i ce wh i ch can o p e rat e in a m i cro p ro ce s so r mo d e b y u s in g s o m e of t h e in p u t /o u t p u t l in es as an ad d res s a n d d ata b u s fo r a cc es sin g exte rn a l m e m o r y. T h is t yp e o f d e vi ce can b e h ave f u n ct i o n al l y as t h e s in gle ch ip m i cro co m p u t e r f ro m wh i ch it i s d e ri ved a lb e it wit h re st r icted I/O an d a m o d if ied exte rn a l c ircu it. T h e u s e of t h e se RO M le ss d e vi ces i s co mmo n e ve n in p ro d u ct io n circu i ts wh e re t h e vo lu m e d o e s n ot ju st if y t h e d e ve lo p m e nt co sts of cu sto m o n -ch ip ROM [2];t h e re ca n st i ll b e a si gn if i cant sav in g in I/O an d o t h e r ch ip s co m pared to a External Timing components System clock Timer/ Counter Serial I/O Prarallel I/O RAM ROMCPUco nve nt io n al m i c ro p ro ces so r b ased circ u it. M o re exa ct re p l a ce m e nt fo rRO M d e v ice s can b e o b tain ed in t h e fo rm of va ria nts w it h 'p i g g y-b a c k'E P ROM(E rasab le p ro gramm ab le ROM )s o cket s o r d e v ice s w it h E P ROMin stead of ROM 。

1 英文文献 翻译 PLC电梯控制 科技类(电子 电气 自动化 通信…

1 英文文献翻译 PLC电梯控制科技类(电子电气自动化通信…英文文献翻译1 导言...................................................................... (1)2 系统结构...................................................................... .. (2)2.1 电力驱动系统...................................................................... .. (2)2.2 信号控制系统...................................................................... .. (2)2.3 要求...................................................................... (2)3 软件设计...................................................................... .. (4)3.1 厅门呼叫记录和显示...................................................................... .. (5)3.2 呼叫的集选控制...................................................................... . (6)3.3 呼叫的取消...................................................................... (6)3.4 电梯运行方向...................................................................... .. (7)3.5 电梯的停层...................................................................... (8)4 最小的等待时间算法...................................................................... (9)4.1 评估函数...................................................................... . (9)4.2 最小轮侯时间的计算...................................................................... .. (9)4.3 算法的实现...................................................................... . (10)结论...................................................................... .. (12)原文...................................................................... .. (13)参考文献...................................................................... (29)英文文献翻译1随着建筑技术的发展,楼房一座比一座高,电梯自然成了高楼大厦垂直运输的重要工具,承载着来往大厦里居住、办公、参观的人们可以舒适而又快捷到达目的地的责任。

电子科技类 英文原文及翻译 毕业设计开题报告用

4 1.6002�社版出学大华清�京北�.著编满绪古�华强张�东晓祝/》语英业专程工气电《自引�注

,sepyt scisyhp uoy roF( .smota nortcele-4 fo xirtam a otni ytirupmi nortcele-5 a gnicudortni yb lairetam rotcudnocimes a deniatbo eW !tnemom a tiaw tuB .tnerruc lacirtcele na lortnoc yllautca ot yaw yna evah t`nod llits eW .eno rotcudnocimes nocilis a naht erutcafunam ot repaehc dna reisae si rotsiser nobrac nialp A .flesti yb lufesu ylralucitrap t`nsi llits ti ,gnitseretni si tceffe siht elihW .rotcudnocimes a sa nwonk si ti ,eroferehT .rotalusni na regnol on si ti emit emas eht ta tub ,rotcudnoc a dellac eb ylreporp tonnac tI .yticirtcele fo wolf eht ot ecnatsiser emos tibihxe seod tI .revlis ro reppoc ,sa ylidaer dna ylisae sa yticirtcele tcudnoc ton seod noitcurtsnoc sihT .nocilis ”epyt-N“ sa nwonk si ti ,egrahc evitagen a htiw hcae ,snortcele gniyrrac-tnerruc fo ssecxe na sah latsyrc gnitluser eht esuaceB .egatlov lacirtcele deilppa llams a ylno htiw devom eb ylisae nac nortcele sihT .dnob a mrof tonnac nortcele htfif eht tub ,erofeb sa smota nocilis tnecajda htiw dnob snortcele evif eseht fo ruof ,noitacilppa siht nI .smota rehto htiw erahs ot snortcele retuo evif evah dna ,elbaT cidoireP eht fo aV nmuloc morf era stnemele esehT .thgir eht ot nwohs sa ,erutcurts latsyrc eht otni surohpsohp ro cinesra sa hcus ytirupmi na ecudortni ot si siht hsilpmocca ot yaw enO .smota neewteb sdnob ,tnelavoc eht fo etips ni ,latsyrc eht nihtiw ecalp ot ecalp morf evom ot snortcele emos wolla ot yaw a dnif tsum ew ,yticirtcele tcudnoc ot latsyrc nocilis ruo wolla oT .latsyrc cisnirtni na eb ot dias si nocilis erup fo latsyrc A .edixoid nocilis si hcihw ,ssalg tsomla si ti ,tcaf nI .rotalusni doog a etiuq si latsyrc nocilis erup a ,suhT .tnerruc lacirtcele na sa ecalp ot ecalp morf evom ot elbaliava snortcele on era erehT .smota rehto htiw sdnob tnelavoc ekam ot desu era smota nocilis lla fo

英文文献 科技类 原文及翻译 (电子 电气 自动化 通信…)74