数字频率计VHDL源程序程序与仿真

用VHDL语言编写的频率计程序

用VHDL语言编写的频率计程序分频library IEEE;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity FP isport( clk,rst:in std_logic;fp:out std_logic);end FP;Architecture behave of FP issignal cnt: std_logic_Vector(15 downto 0);signal tmp,temp: std_logic;beginprocess(clk,rst)BEGINif Rst='1' thencnt<="0000000000000000";elsif clk'event and clk='1' thenif cnt="0000001111111111" thencnt<="0000000000000000";elsecnt<=cnt + 1;end if;end if;end process;process(clk,rst)beginif clk'event and clk='1' thenif cnt="0000001111111111" thentmp<=not tmp;end if;end if;end process;process(clk,rst)beginif clk'event and clk='1' thenif cnt="0000000111111111" thentemp<= not temp;end if;end if;end process;fp<= tmp XOR temp;end behave;计数LIBRARY IEEE ;USE IEEE.STD_LOGIC_1164.ALL ;USE IEEE.STD_LOGIC_UNSIGNED.ALL ;Entity FRE is port( clk,CLR,EN:in std_logic;COUT:out std_logic;CQ:out std_logic_Vector(3 downto 0)); end FRE;Architecture behave of FRE issignal QN: std_logic_Vector(3 downto 0); beginprocess(clk,CLR)BEGINIF CLR='0' thenQN<="0000";ELSIF clk'event and clk='1' thenif en='1' thenif QN="1001" thenQN<="0000";COUT<='1';elseQN<=QN+1;COUT<='0';end if;end if;END IF;end process;CQ(3 DOWNTO 0)<=QN;end behave;控制use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity CTL isport( clk:in std_logic;EN,CLR,FINISH:out std_logic); end CTL;Architecture behave of CTL issignal DIV: std_logic;beginprocess(clk)BEGINif clk'event and clk='1' thenDIV<= NOT DIV;end if;end process;EN<=DIV;FINISH<=NOT DIV;PROCESS(DIV,CLK)BEGINIF DIV='0' AND CLK='0' THENCLR<='0';ELSECLR<='1';END IF;end process;end behave;显示LIBRARY IEEE ;USE IEEE.STD_LOGIC_1164.ALL ;USE IEEE.STD_LOGIC_UNSIGNED.ALL ;Entity DISPLAY is port( clk:in std_logic;DATA:in std_logic_Vector(15 downto 0); SD:out std_logic_Vector(7 downto 0); SS:out std_logic_Vector(1 downto 0));Architecture behave of DISPLAY issignal C: std_logic_Vector(1 downto 0);signal KEYBUF: std_logic_Vector(3 downto 0);beginprocess(clk)BEGINif clk'event and clk='1' thenC<=C+1;end if;end process;SS<=C;PROCESS(C)BEGINCASE C ISWHEN "00" => KEYBUF<=DATA(15 downto 12);WHEN "01" => KEYBUF<=DATA(11 downto 8);WHEN "10" => KEYBUF<=DATA(7 downto 4);WHEN "11" => KEYBUF<=DATA(3 downto 0);WHEN OTHERS => KEYBUF<="0000";END CASE;END PROCESS;PROCESS(KEYBUF)BEGINcase KEYBUF iswhen "0000" => SD<="00111111";when "0001" => SD <="00110000";when "0010" => SD <="01011011";when "0011" => SD <="01001111";when "0100" => SD <="01100110";when "0101" => SD <="01101101";when "0110" => SD <="01111100";when "0111" => SD <="00000111";when "1000" => SD <="01111111";when "1001" => SD <="01101111";when "1010" => SD <="01110111";when "1011" => SD <="01111100";when "1100" => SD <="00111001";when "1101" => SD <="01011110";when "1110" => SD <="01111011";when "1111" => SD <="01110001";when others => SD <="00000000";END CASE;END PROCESS;显示控制library IEEE;use ieee.std_logic_1164.all;entity REG isport( LOAD:in std_logic;QIN:in std_logic_Vector(15 downto 0);QOUT:out std_logic_Vector(15 downto 0)); end REG;Architecture behave of REG isbeginprocess(LOAD)BEGINif LOAD'event and LOAD='1' thenQOUT<=QIN;end if;end process;end behave;。

基于fpga控制的数字频率计设计(含程序、仿真图)大学毕设论文

目录1 引言 (1)1.1 课题背景 (1)1.2 课题意义 (2)1.3 国内外现状及发展趋势 (2)1.4 系统开发环境及技术分析 (3)1.4.1 FPGA开发简介 (3)1.4.2 VHDL特点及设计方法 (5)2 需求分析 (7)2.1 系统基本要求 (7)2.2 系统结构 (7)3 系统设计 (8)3.1 总体方案比较 (8)3.2 程序流程图 (10)3.3 系统模块设计 (11)3.3.1 整形电路 (11)3.3.2 计数器 (12)3.3.3分频器 (14)3.3.4锁存器 (16)3.3.5控制器 (19)3.3.6 显示器 (22)4 系统仿真及测试 (23)结论 (29)致谢 (30)参考文献 (31)附录1 (32)附录2 (35)1 引言1.1 课题背景进入信息时代以来,微电子技术和计算机技术飞速发展, 各种电子测量仪器在原理、功能、精度及自动化水平等方面都发生了巨大的变化, 特别是DSP技术诞生以后,电子测量技术更是迈进了一个全新的时代[1]。

近年来,DSP逐渐成为各种电子器件的基础器件,逐渐成为21世纪最具发展潜力的朝阳行业,甚至被誉为信息化数字化时代革命旗手。

在电子技术领域内,频率是一个最基本的参数,频率与其它许多电参量的测量方案、测量结果都有十分密切的关系。

如时间,速度等都涉及到或本身可转化为频率的测量。

因此,频率的测量就显得更为重要。

而且,目前在电子测量中,频率的测量精确度是最高的.现在市场上有各种多功能,高精度,高频率的数字频率计,但价格不菲。

而在实际工程中,不是对所有信号的频率测量都要求达到非常高的精度。

因此,本文提出了一种能满足一般测量精度要求,但成本低廉的数字频率计的设计方案。

在电子工程中、资源勘探、仪器仪表等相关应用中,频率计是工程技术人员必不可少的测量工具。

数字频率计是计算机,通信设备,音频视频等科研生产领域不可缺少的车辆仪器,采用VHDL语言编程设计实现的数字频率计,除被测信号的整形部分,键输入部分和数码显示部分以外其余全在一片FPGA芯片上实现,整个设计过程变得十分透明,快捷和方便,特别是对于各层次电路系统的工作时序的了解显得尤为准确而且具有灵活的现场可更改性。

实验三 VHDL设计输入及时钟频率仿真与测试-文档资料

图3-3

4、在VHDL编译窗口中关键字为蓝色(如 end ; port 等), 数据类型为粉红色,注释为绿色。库名、实体名、端口名、 结构体名、均为黑色。这样有助于发现输入错误。

完整的6分频器VHDL程序如下(也可以自己设计):

library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity FPQ3 is Port ( CLK : in std_logic; CP : out std_logic); end FPQ3; architecture Behavioral of FPQ3 is signal a:integer range 0 to 6; begin process(CLK) begin if (CLK'event and CLK='1') then

三、ModelSim Simulator中的时序仿真及周期测量 方法

1、在Sources子窗口选中fpq3-behavioral,点击菜单 ProjectNew Source弹出图3-4对话框,左栏选 Test Bench Waveform,输入文件名fpq3_twb。

图3-4

完成后弹出图3-5对话框。根据图3—5输入数值。点击ຫໍສະໝຸດ K, 在右面显示测试波形,保存一下。

5、生成VHDL模块 结构体内输入完毕后进行保存。在Processes子窗口中, 双击(Design Entry Utilities 下级)Create Schematic Symbol,运行后在Create Schematic Symbol前会打上一 个绿色的✔,表示VHDL模块生成。但不能保证设计语法 没有错误。要通过双击Processes子窗口中的SynthesizXST子项Check Syntax进行语法检测,必须查看控制子 窗口是否有报错、警告,根据指出的错误进行修改,直到 控制子窗口没有报错和警告。

全同步数字频率计的 VHDL设计与仿真

全同步数字频率计的VHDL设计与仿真

1 引言

频率测量不仅在工程应用中有非常重要的意义,而且在高精度定时系统中也处于核心地位,±1个计数误差通常是限制频率测量精度进一步提高的重要原因。

由于测频技术的重要性,使测频方法也有了很大的发展,常用数字频率测量方法有M法,T法,和M/T(等精度测量法)法。

M法,T法,和M/T法都存在±1个计数误差问题:M法存在被测闸门内±1个被测信号的脉冲个数误差,T法或M/T法也存在±1个字的计时误差,这个问题成为限制测量精度提高的一个重要的原因。

全同步频率测量法[1],从根本上消除了限制测量精度提高的±1个计数误差问题,从而使频率测量的精度和性能大为改善。

基于对FPGA器件和EDA技术以及全同步测频方法的研究[2,3],介绍一种利用FPGA实现DC~100 MHz全同步数字频率计的实现方法,并给出VHDL实现代码和仿真波形。

整个系统在研制的FPGA/CPID实验开发系统上调试通过。

本设计采用了高集成度的现场可编程门阵列(Field Program-mable Gata Array,FPGA)Flex EPF10k20TCl44-4芯片[4],通过软件编程对目标器件的结构和工作方式进行重构,能随时对设计进行调整,使得本设计具有集成度高、结构灵活、开发周期短、可靠性高的优点。

在文献[2,5]中所描述的等精度频率测量方法中,其测频原理如图1所示。

其误差与闸门时间和标准时钟频率有关,闸门时间越长,标准时钟频率越。

等精度频率计设计VHDL程序

等精度频率计设计VHDL程序下面是一个基于VHDL的精度频率计设计程序:library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.NUMERIC_STD.ALL;entity Frequency_Counter isgenericTOLERANCE : integer := 1; --容差范围REF_FREQ : natural := 100; --参考频率BIT_WIDTH : integer := 16 --输出频率计数器宽度portclk : in std_logic;reset : in std_logic;frequency : out std_logic_vector(BIT_WIDTH - 1 downto 0) --计数器输出值end entity Frequency_Counter;architecture Behavioral of Frequency_Counter issignal count : unsigned(BIT_WIDTH - 1 downto 0); --计数器signal count_enable : std_logic; --计数使能信号signal ref_counter : unsigned(ceil(log2(real(REF_FREQ * CLK_FREQ) / TOLERANCE)) - 1 downto 0); --参考计数器beginprocess(clk, reset)beginif reset = '1' thencount <= (others => '0'); --复位为0count_enable <= '0';ref_counter <= (others => '0');elsif rising_edge(clk) thencount <= count + 1; --计数信号递增end if;if ref_counter = REF_FREQ - 1 thenelseref_counter <= ref_counter + 1; --参考计数器递增end if;end if;end process;process(clk, reset)beginif reset = '1' thencount_enable <= '0';elsif rising_edge(clk) thencount_enable <= '1'; --参考频率达到后启用计数信号elsecount_enable <= '0';end if;end if;end process;frequency <= std_logic_vector(count);end architecture Behavioral;在此设计中,我们定义了一个Frequency_Counter实体,它有几个泛型参数,包括CLK_FREQ(输入时钟频率),TOLERANCE(容差范围),REF_FREQ(参考频率)和BIT_WIDTH(输出频率计数器的宽度)。

VHDL实现的数字频率计

第5节 利用VHDL语言实现单片简易自动量程数字频率计[学习要求] 能利用VHDL语法实现较为复杂的数字系统。

[重点与难点]重点:复杂数字系统的设计方法。

难点:频率计自动量程的设计;动态显示的原理。

[理论内容]一、数字频率计系统概述该频率计的具体电路如图1所示,图中CPLD可采用FLEX10K10系列实现,数码管采用共阴极方式。

Funknown引脚为未知频率输入,ref_clk为10MHz参考频率输入,sys_rst_l 为复位引脚。

从图中可以看出,使用可编程器件使系统器件数降至最低。

该频率计的计数范围从DC到9.999MHz,共分为四个量程,每个量程的阀门如下表所示:图1 单片CPLD数字频率计电路图量程与阀门宽度对应表频率范围/KHz 阀门宽度/sDC~0.9999 110.00~99.99 0.1100.0~999.9 0.011000~9999 0.001该频率计基本原理是通过对来临的未知频率上升沿在设定的时间段内计数,这个时间段就是所谓的阀门。

当计数溢出时,说明所选择的阀门较宽,此时自动选择较窄的阀门。

阀门开关的切换是立即的。

该频率计CPLD 内部逻辑电路通过VHDL 语言编程实现。

系统大致可分为图2所示的四个模块:控制单元(CONTROL ),主要完成时序生成和量程自动切换等。

计数单元(COUNT ),在阀门内对输入频率进行计数,计数结果为四位十进制数。

显示单元(DISPLAY )对计数结果进行动态的数码显示。

分频单元(DIVIDE )比较简单,将参考频率分频得到动态显示所需的频率。

以下对各单元功能具体分析。

二、系统内部各单元概述1、显示单元(DISPLAY )图3 频率计控制单元工作流图其对外接口如图2所示。

sys_rst_l 为总体复位信号,disp_clk 为动态刷新频率,由ref_clk (10MHz )经DIVIDE 单元分频而来,频率为100KHz 。

其输出digit_out(7:0)和gate_l(3:0)如图1和图2所示。

使用VHDL语言进行的100MHZ数字频率计的设计

《电气工程及其自动化EDA课程设计》课程设计报告\题目:数字频率计的设计院(系):机电与自动化学院专业班级:电气工程及其自动化学生姓名: XXX学号: 2011XXXXXXX指导教师: XXX 】2014年1月6日至2014年1月10日#华中科技大学武昌分校《电气工程及其自动化EDA课程设计》设计任务书(目录摘要 (1)一.课程设计要求及内容 (1)主要技术指标 (1)工作内容及要求 (1)二数字频率计的基本原理 (1)数字频率计的组成 (1):数字频率器的原理 (2)三具体电路模块设计 (2)100MHz分频器 CLK_GEN的设计 (2)带时钟使能的十进制计数器CNT10的设计 (3)32位锁存器REG32B的设计 (5)测频控制信号发生器TESTCTL的设计 (6)动态输入编译译码器HC4511的设计 (7)四数字频率计系统模块的设计 (9)>系统模块程序设计及仿真波形 (9)数字频率计系统顶层设计 (10)五心得体会 (13)课程设计成绩评定表 (14)(摘要数字频率计是一种用十进制数字显示被测信号频率的一种数字测量仪器,其功能是测量正弦信号,方波信号,尖脉冲信号以及其他各种单位时间内变化的物理量,因此已经成为电路设计的常用元器件之一,有它不可替代的地位。

在电子技术中,频率与许多电参量的设计测量方案,测量结果都有着十分紧密的关系,因此频率的测量就显得更为重要。

测量频率的方法有很多种,其中数字计数器测量频率具有精度高,使用方便,测量迅速,以及便于实现测量过程自动化等优点,是频率测量的重要手段之一。

其原理为通过测量一定闸门时间内信号的脉冲个数。

本文阐述了利用VHDL语言在CPLD器件的基础上设计一个简单的数字频率计的过程。

采用VHDL编程技术设计实现的数字频率计,除被测信号的整形部分,键输入部分和数码显示部分以外,其余全部在一片集成电子芯片上实现,整个系统非常精简,而且具有灵活的现场可更改性。

VHDL语言设计数字频率计

数字频率计的设计一、频率计实现的功能要设计的频率计的测量围为1MHz。

为了提高测量的精度,量程分为三档,分别是:10kHz、100kHz、1MHz。

并要求在测量频率大于或小于选择的量程时,频率计自动换档。

1、当读数大于999时,频率计处于超量程状态,下一次测量时,量程自动增加一档。

2、当读数小于009时,频率计处于欠量程状态,下一次测量时,量程自动减小一档。

3、当超出测量围时,显示错误。

4、在计数时不显示数据,计数完成后只显示测量结果。

5、小数点位置要自动移位。

二、频率计各局部的分析在这个设计中,需要用计数器来进展计数,而且计数器在各个档位要被重复使用,在测量的过程中,计数允许时钟信号还要进展调整,故将计数器设计成一个单独的模块,提供计数值的输出。

显示结果包括数值显示,档位显示及溢出标志显示。

其中数值显示要用到三个数码管,实验箱上连在一起的三个数码管中,只有两个数码管部接有译码器,因此我们自己还要在程序中为那个没有译码器的数码管再加一段七段译码器程序来显示结果。

档位标志由三个LED灯来显示,代替数码管上的小数点的功能。

溢出标志由两个LED灯来显示,其中一个显示结果溢出,另一个显示输入信号在测量围之。

该频率计的顶层逻辑电路原理图如图〔1〕所示:图〔1〕三、频率计各局部的设计和实现从上面的分析可以知道,频率计可以由三个模块来组成。

下面对各个模块的设计方法和实现方法进展详细说明。

1、时基进程的设计和实现在实际使用时,输入的信号是随意的,没有方法预知输入的频率。

因此选取频率计的时基是非常重要的。

在设计要求中,将量程分为三档,在某一档进展测量时,需要提供该档的时基。

在10kHz档,该档最大读数为9.99kHz,最小读数为0.01 kHz,所以要提供的时基是频率为0.01 kHz的脉冲。

同理,在100 kHz档上,要提供的时基应该是频率为0.1 kHz的脉冲。

在1 MHz档上,要提供的时基是频率为1 kHz的脉冲。

vhdl数字频率计

VHDL数字系统设计与仿真作业三:数字频率计学院:学号:姓名:一.实验要求截图二.设计思路截图三.各模块设计思路,源程序及仿真1.测量/校验选择模块源程序:meas_test.vhdLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL; ENTITY meas_test ISPORT(func_sel,meas,test:IN STD_LOGIC;CP1:OUT STD_LOGIC);END meas_test;ARCHITECTURE lion OF meas_test ISBEGINPROCESS(func_sel,meas,test)BEGINIF func_sel='1'THEN CP1<=test;ELSECP1<=meas;END IF;END PROCESS;END lion;仿真截图:2.测频控制信号发生器模块源程序:clk2.vhdLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY clk2 ISPORT(clk: IN STD_LOGIC;clk2: OUT STD_LOGIC);END clk2;ARCHITECTURE lion OF clk2 ISSIGNAL clk2_temp:STD_LOGIC;BEGINPROCESS(clk)BEGINIF(clk'EVENT AND clk='1')THEN clk2_temp <= NOT clk2_temp;END IF;END PROCESS;clk2<=clk2_temp;END lion;仿真截图:3.四级十进制计数模块源程序:counter.vhdLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY counter ISPORT(RD:IN STD_LOGIC;CP:IN STD_LOGIC;Q:OUT STD_LOGIC_VECTOR(15 DOWNTO 0);C:OUT STD_LOGIC);END counter;ARCHITECTURE lion OF counter ISSIGNAL count:STD_LOGIC_VECTOR(15 DOWNTO 0);BEGINPROCESS(RD,CP)BEGINIF(RD='0')THENcount<="0000000000000000";C<='0';ELSE IF(CP'EVENT AND CP='1')THEN IF(count="1001100110011001")THEN count<="0000000000000000";C<='1';ELSE IF(count(11 DOWNTO 0)="100110011001")THEN count(15 DOWNTO 12)<=count(15 DOWNTO 12)+1;count(11 DOWNTO 0)<="000000000000";ELSE IF(count(7 DOWNTO 0)="10011001")THEN count(15 DOWNTO 8)<=count(15 DOWNTO 8)+1;count(7 DOWNTO 0)<="00000000"; C<='0';ELSE IF(count(3 DOWNTO 0)="1001")THEN count(15 DOWNTO 4)<=count(15 DOWNTO 4)+1;count(3 DOWNTO 0)<="0000";C<='0';ELSE count<=count+1;END IF;END IF;END IF;END IF;END IF;END IF;END PROCESS;Q<=count;END lion;4.送存选择/报警模块LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY PASS_ALERT ISPORT(K: IN STD_LOGIC;CLK: IN STD_LOGIC;Q: IN STD_LOGIC_VECTOR(15 DOWNTO 0);C: IN STD_LOGIC;D: OUT STD_LOGIC_VECTOR(11 DOWNTO 0);dot: out STD_LOGIC_VECTOR(2 DOWNTO 0);Y: out STD_LOGIC;alert:OUT STD_LOGIC);END PASS_ALERT;ARCHITECTURE lion OF PASS_ALERT ISBEGINPROCESS(K,Q,C)BEGINIF(K='0')THEN Y<='0';IF(Q(15 DOWNTO 12)="0000" AND C='0')THEN D<=Q(11 DOWNTO 0);dot<="001";alert<='0';ELSE D<=Q(11 DOWNTO 0);dot<="001";alert<='1';END IF;ELSE IF(C='0')THEN Y<='1';D<=Q(15 DOWNTO 4);alert<='0';dot<="100";ELSE D<=Q(15 DOWNTO 4);alert<='1';dot<="100";END IF;END IF;END PROCESS;END lion;仿真截图:5.锁存模块源程序:lock_store.vhdLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY LOCK_STORE ISPORT(Q:IN STD_LOGIC_VECTOR(11 DOWNTO 0);--Q2:IN STD_LOGIC_VECTOR(3 DOWNTO 0);--Q1:IN STD_LOGIC_VECTOR(3 DOWNTO 0);LD:IN STD_LOGIC;D:OUT STD_LOGIC_VECTOR(11 DOWNTO 0)--D2:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);--D1:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);--dot:OUT STD_LOGIC;);END LOCK_STORE;ARCHITECTURE lion OF LOCK_STORE ISBEGINPROCESS(LD)BEGINIF(LD'EVENT AND LD='1')THEN D<=Q;END IF;END PROCESS;END lion;仿真截图:6.扫描显示电路模块扫描源程序SCAN.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;ENTITY SCAN ISPORT(CLK:IN STD_LOGIC;D:IN STD_LOGIC_VECTOR(11 DOWNTO 0);Q:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);SEL:OUT STD_LOGIC_VECTOR(1 DOWNTO 0));END SCAN;ARCHITECTURE lion OF SCAN ISBEGINPROCESS(D)VARIABLE init:BOOLEAN:=TRUE;VARIABLE count:INTEGER:=0;BEGINIF(CLK'EVENT AND CLK='1')THENIF(D="000000000000")THEN count:=0;SEL<="00";Q<=D(3 DOWNTO 0);ELSE IF(init) THEN count:=0;SEL<="00";Q<=D(3 DOWNTO 0);init:=FALSE;ELSE IF(count=0) THEN count:=1; SEL<="01";Q<=D(7 DOWNTO 4);ELSE IF(count=1) THEN count:=2; SEL<="10";Q<=D(11 DOWNTO 8);ELSE IF(count=2) THEN count:=0; SEL<="00";Q<=D(3 DOWNTO 0);END IF;END IF;END IF;END IF;END IF;END IF;END PROCESS;END lion;仿真截图:7.显示源程序DEC_LED.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164;ENTITY DEC_LED ISPORT( num:IN BIT_VECTOR(3 DOWNTO 0);dout:OUT BIT_VECTOR(6 DOWNTO 0));END DEC_LED;ARCHITECTURE lion of DEC_LED ISBEGINPROCESS(num)BEGINCASE num ISWHEN "0000"=>dout<="1111110";WHEN "0001"=>dout<="0110000";WHEN "0010"=>dout<="1101101";WHEN "0011"=>dout<="1111001";WHEN "0100"=>dout<="0110011";WHEN "0101"=>dout<="1011011";WHEN "0110"=>dout<="1011111";WHEN "0111"=>dout<="1110000";WHEN "1000"=>dout<="1111111";WHEN "1001"=>dout<="1111011";WHEN OTHERS=>dout<=NULL;END CASE;END PROCESS;END lion;仿真截图:8.顶层模块设计将以上各模块生成对应器件,然后新建顶层工程Digita_Freq.采用图形化输入的方式,调用以上各模块器件,并加入输出输出,及必要的与非门等,并连接。

数字频率计设计与仿真

数字频率计设计一、实验目的1、了解等精度测频的方法和原理。

2、掌握如何在FPGA 内部设计多种功能模块。

3、掌握VHDL 在测量模块设计方面的技巧。

二、实验原理所谓频率就是周期性信号在单位时间(1s)内变化的次数。

若在一定时间间隔T(也称闸门时间)内测得这个周期性信号的重复变化次数为N,则其频率可表示为f=N/T由上面的表示式可以看到,若时间间隔T 取1s,则f=N。

由于闸门的起始和结束的时刻对于信号来说是随机的,将会有一个脉冲周期的量化误差。

进一步分析测量准确度:设待测信号脉冲周期为Tx,频率为Fx,当测量时间为T=1s时,测量准确度为δ=Tx/T=1/Fx。

由此可知这种直接测频法的测量准确度与被测信号的频率有关,当待测信号频率较高时,测量准确度也较高,反之测量准确度较低。

因此,这种直接测频法只适合测量频率较高的信号,不能满足在整个测量频段内的测量精度保持不变的要求。

若要得到在整个测量频段内的测量精度保持不变的要求,应该考虑待精度频率测量等其它方法。

等精度频率测频的实现方法,可以用图23-1 所示的框图来实现。

三、实验内容本实验要完成的任务就是设计一个频率计,系统时钟选择核心板上的20M 的时钟,闸门时间为1s(通过对系统时钟进行分频得到),在闸门为高电平期间,对输入的频率进行计数,当闸门变低的时候,记录当前的频率值,并将频率计数器清零,频率的显示每过2 秒刷新一次。

被测频率通过一个拨动开关来选择是使用系统中的数字时钟源模块的时钟信号还是从外部通过系统的输入输出模块的输入端输入一个数字信号进行频率测量。

当拨动开关为高电平时,测量从外部输入的数字信号,否则测量系统数字时钟信号模块的数字信号。

其实现框图如下图在本实验中,用到的模块有数字信号源模块、拨动开关模块、20M 系统时钟源模块、数码管显示模块等。

其中数码管、数字信号源、拨动开关与FPGA的连接电路和管脚连接在以前的实验中都做了详细说明,这里不在赘述。

在FPGA上用VHDL实现数字频率计 实验报告

数字系统设计实验报告一、设计要求:1、(1)频率测量范围10Hz~1MHz(2)量程自动转换,量程分为10KHz (1s) 、100KHz (0.1s) 、1MHz (10ms)三档。

转换规则如下:当读数大于9999时,频率计处于超量程状态,下一次测量时,量程自动增大一档;当读数小于0999时,频率计处于欠量程状态,下一次测量时,量程自动减小一档(3)数据采用记忆显示方式,即计数过程中不显示数据,待计数过程结束以后,显示计数结果,并将此显示结果保持到下一次计数结束。

(4)用发光二极管显示量程二、方案选则1测量原理:当预置门控信号为高电平时,启动计数器,被测信号(频率为fx) 计数当预置门控信号为低电平时,关闭计数器设在一次预置门控时间Tg内对被测信号计数值为Nx,则fx= Nx / Tg2具体方案:本设计中将2MHz的时钟分三次频,分别作为防抖电路的周期信号、显示模块片选信号、计数及锁存模块闸门信号。

防抖电路滤去窄波,显示模块用模4计数器来分别输出四位测量结果。

计数器通过在0.1s内对输入信号的高电平(发生期)进行计数来得出结果,并且为了达到换挡目的,测量时计六位数,通过结果选择档位进行输出。

二、原理图三、总体电路图四、流程图五、设计清单1、防抖电路LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY debounce ISPORT(key,cp: IN STD_LOGIC; --复位键imp:OUT STD_LOGIC); --去掉窄波后输出END debounce;ARCHITECTURE base OF debounce ISSIGNAL ql,q2:STD_LOGIC;BEGINPROCESS(cp)BEGINIF cp'event AND cp='1'THENq2<=ql; ql<=key;END IF;END PROCESS;imp<=ql AND NOT q2;END base;时序仿真波形:2、分频电路LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_SIGNED.ALL;ENTITY dividefre4 ISPORT(cp_2m:IN STD_LOGIC; --2MHzcpl:OUT STD_LOGIC; --200Hzcp2:OUT STD_LOGIC; --25Hzcp3:OUT STD_LOGIC); --5HzEND dividefre4;ARCHITECTURE behavior OF dividefre4 IS SIGNAL tout:INTEGER RANGE 0 TO 4999; --5000分频SIGNAL toutl:INTEGER RANGE 0 TO 7; --8分频SIGNAL tout2:INTEGER RANGE 0 TO 39; --40分频SIGNAL cp_1:STD_LOGIC;SIGNAL cp_2:STD_LOGIC;SIGNAL cp_3:STD_LOGIC;SIGNAL cp:STD_LOGIC;BEGINPROCESS(cp_2m) –分出400Hz时钟BEGINIF(cp_2m'event AND cp_2m='1')THENIF tout=4999 THENtout<=0;ELSE tout<=tout+1;END IF;IF tout=2499 THENcp<='0';ELSE cp<='1';END IF;END IF;END PROCESS;PROCESS(cp) --200Hz时钟BEGINIF(cp'event AND cp='1')THENcp_1<=NOT cp_1;END IF;END PROCESS;PROCESS(cp_1) --25Hz时钟和5HzBEGINIF(cp_1'event AND cp_1='1')THENIF toutl=7 THEN toutl<=0;ELSE toutl<=toutl+1;END IF;IF toutl=3 THENcp_2<='1';ELSIF toutl=7 THEN cp_2<='0'; --8分频得25Hz END IF;IF tout2=39 THEN tout2<=0; --40分频得5HzELSE tout2<=tout2+1;END IF;IF tout2=39 THENcp_3<='1';ELSIF tout2=19 THEN cp_3<='0';END IF;END IF;END PROCESS;cpl<=cp_1;cp2<=cp_2;cp3<=cp_3;END behavior;仿真波形:(因原程序所分频倍数太大,所以这里将5000倍分频降至50倍)3、计数器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_SIGNED.ALL;ENTITY fretest ISPORT(enable:IN STD_LOGIC; --使能cp3:IN STD_LOGIC; --闸门INput:IN STD_LOGIC; --被测信号reset:IN STD_LOGIC; --复位信号overflow:OUT STD_LOGIC; --大于1000kHzPlay0,playl,play2,play3:OUT INTEGER RANGE 0 TO 9;decimal:OUT STD_LOGIC_VECTOR(2 DOWNTO 0));--小数点,即档位END fretest;ARCHITECTURE behavior OF fretest ISSIGNAL r0_1,r1_1,r2_1,r3_1,r4_1,r5_1:INTEGER RANGE 0 TO 9;BEGINPROCESS(INput,enable,reset,cp3)BEGINIF enable='0'THEN NULL; --不测量ELSIF(input'event AND input='1')THEN --检测被测信号IF reset='1'THEN --同步复位,高电平有效overflow<='0';r0_1<=0;r1_1<=0;r2_1<=0;r3_1<=0;r4_1<=0;r5_1<=0;ELSIF cp3='0'THEN --闸门为0时清零Overflow<='0';r0_1<=0;r1_1<=0;r2_1<=0;r3_1<=0;r4_1<=0;r5_1<=0;ELSE --闸门为高电平计数r0_1<=r0_1+1;IF r0_1=9 THEN r1_1<=r1_1+1;r0_1<=0;IF(r1_1=9)THEN r2_1<=r2_1+1;r1_1<=0;IF(r2_1=9)THEN r3_1<=r3_1+1;r2_1<=0;IF(r3_1=9)THEN r4_1<=r4_1+1;r3_1<=0;IF(r4_1=9)THEN r5_1<=r5_1+1;r4_1<=0;IF(r5_1=9)THEN r5_1<=0;overflow<='1'; --大于1000kHz END IF;END IF;END IF;END IF;END IF;END IF;END IF;END IF;END PROCESS;PROCESS(r5_1,r4_1)BEGINIF r5_1=0 AND r4_1=0 THEN --为小于9999Hz时play0<=r0_1;playl<=r1_1;play2<=r2_1;play3<=r3_1;decimal<="100";ELSIF r5_1=0 THEN --为几十kHz时play0<=r1_1;playl<=r2_1;play2<=r3_1;play3<=r4_1;decimal<="010";ELSE --为几百kHz时play0<=r2_1;playl<=r3_1;play2<=r4_1;play3<=r5_1;decimal<="001";END IF;END PROCESS;END behavior;仿真波形4、锁存器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_SIGNED.ALL;ENTITY frelatch ISPORT(reset:IN STD_LOGIC; --复位cp3:IN STD_LOGIC; --时钟Overflow: IN STD_LOGIC; --大于1000kHz表示play0,playl,play2,play3:IN INTEGER RANGE 0 TO 9;decimal:IN STD_LOGIC_VECTOR(2 DOWNTO 0);--小数点overlatch:OUT STD_LOGIC; --大于1000kHzp0latch,pllatch,p21atch,p31atch:OUT INTEGER RANGE 0 TO 9; delatch:OUT STD_LOGIC_VECTOR(2 DOWNTO 0));--小数点END frelatch;ARCHITECTURE behavior OF frelatch ISBEGINPROCESS(cp3,reset)BEGINIF reset='1'THENoverlatch<='0';p0latch<=0;pllatch<=0;p21atch<=0;p31atch<=0;delatch<=decimal;ELSIF cp3'event AND cp3='0'THENoverlatch<=overflow;p0latch<=play0;pllatch<=playl;p21atch<=play2;p31atch<=play3;delatch<=decimal;END IF;END PROCESS;END behavior;仿真波形5、显示模块LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_SIGNED.ALL;ENTITY display ISPORT( cpl:IN STD_LOGIC; --时钟overflow:IN STD_LOGIC; --高于1000kHz标志p0,p1,p2,p3:IN INTEGER RANGE 0 TO 9;--BCD码输入 show:OUT STD_LOGIC_VECTOR(6 DOWNTO 0);--7段码输出 sel:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));--位扫描码END dISplay;ARCHITECTURE behavior OF display ISSIGNAL count: INTEGER RANGE 0 TO 3;SIGNAL sel_1:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS(cpl)BEGINIF(cpl'event AND cpl='1') THENIF count=3 THEN count<=0;ELSEcount<=count+1;END IF;END IF;END PROCESS;PROCESS(count)BEGINCASE count ISWHEN 0=>sel_1<="1110"; --第0位WHEN 1=>sel_1<="1101"; --第1位WHEN 2=>sel_1<="1011"; --第2位WHEN 3=>sel_1<="0111"; --第3位END CASE;END PROCESS;PROCESS(overflow,sel_1)BEGINIF(overflow='1')THENshow<="0110111"; --高于1000kHz,显示HELSIF(sel_1(0)='0')THEN --第0位数码管译码CASE p0 ISWHEN 0=>show<="1111110";--显示0,a-gWHEN 1=>show<="0110000";--1WHEN 2=>show<="1101101";--2WHEN 3=>show<="1111001";WHEN 4=>show<="0110011";WHEN 5=>show<="1011011";WHEN 6=>show<="0011111";WHEN 7=>show<="1110000";WHEN 8=>show<="1111111";WHEN 9=>show<="1110011";END CASE;ELSIF(sel_1(1)='0')THEN --第1位译码 CASE p1 ISWHEN 0=>show<="1111110";WHEN 1=>show<="0110000";WHEN 2=>show<="1101101";WHEN 3=>show<="1111001";WHEN 4=>show<="0110011";WHEN 5=>show<="1011011";WHEN 6=>show<="0011111";WHEN 7=>show<="1110000";WHEN 8=>show<="1111111"; WHEN 9=>show<="1110011";END CASE;ELSIF(sel_1(2)= '0')THEN --第2位译码 CASE p2 ISWHEN 0=>show<="1111110";WHEN 1=>show<="0110000";WHEN 2=>show<="1101101";WHEN 3=>show<="1111001";WHEN 4=>show<="0110011";WHEN 5=>show<="1011011";WHEN 6=>show<="0011111";WHEN 7=>show<="1110000";WHEN 8=>show<="1111111";WHEN 9=>show<="1110011";END CASE;ELSIF(sel_1(3)='0')THEN --第3位译码 CASE p3 ISWHEN 0=>show<="1111110";WHEN 1=>show<="0110000";WHEN 2=>show<="1101101";WHEN 3=>show<="1111001";WHEN 4=>show<="0110011";WHEN 5=>show<="1011011";WHEN 6=>show<="0011111";WHEN 7=>show<="1110000";WHEN 8=>show<="1111111";WHEN 9=>show<="1110011";END CASE;END IF;END PROCESS; sel<=sel_1; END behavior; 仿真波形。

vhdl四位频率计主要源程序

测频控制电路***************************************LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY FTCTRL ISPORT(CLK: IN STD_LOGIC;CNT_EN: OUT STD_LOGIC;RST_CNT: OUT STD_LOGIC;Load: OUT STD_LOGIC );END FTCTRL ;ARCHITECTURE behav OF FTCTRL ISSIGNAL Div2CLK :STD_LOGIC;BEGINPROCESS (CLK)BEGINIF CLK'EVENT AND CLK='1' THENDiv2CLK<=NOT Div2CLK;END IF;END PROCESS;PROCESS(CLK,Div2CLK)BEGINIF CLK='0' AND Div2CLK='0' THEN RST_CNT<='1';----产生计数器清零信号ELSE RST_CNT<='0';END IF;END PROCESS;Load <=NOT Div2CLK; CNT_EN <=Div2CLK;END behav;***************************************锁存器***************************************LIBRARY IEEE ;USE IEEE.STD_LOGIC_1164.ALL;ENTITY REG32B ISPORT (LK:IN STD_LOGIC;DIN :IN STD_LOGIC_VECTOR(3 DOWNTO 0);DOUT:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END ENTITY REG32B;ARCHITECTURE behav OF REG32B ISBEGINPROCESS (LK,DIN)BEGINIF LK'EVENT AND LK = '1' THEN DOUT <=DIN;END IF;END PROCESS;END behav ;***************************************计数器***************************************LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY COUNTER32B ISPORT(FIN: IN STD_LOGIC;CLR: IN STD_LOGIC;ENABL: IN STD_LOGIC;COUT : OUT STD_LOGIC;DOUT: OUT STD_LOGIC_VECTOR(3 DOWNTO 0) ); END COUNTER32B ;ARCHITECTURE behav OF COUNTER32B ISSIGNAL CQI :STD_LOGIC_VECTOR(3 DOWNTO 0); BEGINPROCESS (FIN,CLR,ENABL)BEGINIF CLR='1' THEN CQI <=(OTHERS=>'0');ELSIF FIN'EVENT AND FIN='1' THENIF ENABL = '1' THEN CQI <=CQI+1;END IF;IF CQI =9 THEN CQI <="0000";COUT<='1';ELSE COUT<='0';END IF;END IF;END PROCESS;DOUT<=CQI;END behav;***************************************频率计顶层文件***************************************LIBRARY IEEE;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY FREQUTEST ISPORT ( CLK1HZ : IN STD_LOGIC;FSIN : IN STD_LOGIC;DOUT : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);DOUT1 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);DOUT2 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);DOUT3 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0) );END FREQUTEST;ARCHITECTURE struc OF FREQUTEST ISCOMPONENT FTCTRLPORT (CLK : IN STD_LOGIC; --1HzCNT_EN : OUT STD_LOGIC; --计数器时钟使能信号端RST_CNT : OUT STD_LOGIC; --计数器清零端Load : OUT STD_LOGIC ); --输出锁存信号端END COMPONENT;COMPONENT COUNTER32BPORT (FIN : IN STD_LOGIC; --时钟信号CLR : IN STD_LOGIC; --清零信号ENABL : IN STD_LOGIC; --计数器使能信号COUT : OUT STD_LOGIC;DOUT : OUT STD_LOGIC_VECTOR(3 DOWNTO 0) ); --计数结果输出END COMPONENT;COMPONENT REG32BPORT (LK : IN STD_LOGIC;DIN : IN STD_LOGIC_VECTOR(3 DOWNTO 0);DOUT : OUT STD_LOGIC_VECTOR(3 DOWNTO 0) );END COMPONENT;SIGNAL TSTEN1 : STD_LOGIC;SIGNAL CLR_CNT1 : STD_LOGIC;SIGNAL Load1 : STD_LOGIC;SIGNAL CARRY_OUT1 : STD_LOGIC;SIGNAL CARRY_OUT2 : STD_LOGIC;SIGNAL CARRY_OUT3 : STD_LOGIC;SIGNAL DTO1 : STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL DTO2 : STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL DTO3 : STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL DTO4 : STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINU1 : FTCTRL PORT MAP(CLK =>CLK1Hz,CNT_EN =>TSTEN1,RST_CNT =>CLR_CNT1,Load =>Load1);U2 : REG32B PORT MAP( LK =>Load1,DIN=>DTO1,DOUT =>DOUT);U3 : COUNTER32B PORT MAP( FIN =>FSIN,CLR=>CLR_CNT1,ENABL=>TSTEN1,COUT=>CARRY_OUT1,DOUT =>DTO1);U4 : COUNTER32B PORT MAP( FIN =>CARRY_OUT1,CLR=>CLR_CNT1,ENABL=>TSTEN1,COUT=>CARRY_OUT2,DOUT =>DTO2);U5 : REG32B PORT MAP( LK =>Load1,DIN=>DTO2,DOUT =>DOUT1);U6 : COUNTER32B PORT MAP( FIN =>CARRY_OUT2,CLR=>CLR_CNT1,ENABL=>TSTEN1,COUT=>CARRY_OUT3,DOUT =>DTO3);U7 : REG32B PORT MAP( LK =>Load1,DIN=>DTO3,DOUT =>DOUT2);U8 : COUNTER32B PORT MAP( FIN =>CARRY_OUT3,CLR=>CLR_CNT1,ENABL=>TSTEN1,DOUT =>DTO4);U9 : REG32B PORT MAP( LK =>Load1,DIN=>DTO4,DOUT =>DOUT3);END struc;。

EDA技术-VHDL-5.10 采用测频法的数字频率计程序设计与仿真

5.10 采用测频法的数字频率计程序设计与仿真实验1.实验目的掌握测频法数字频率计的基本原理,设计VHDL程序实现其基本功能。

2.实验原理系统组成的框图如图5.10.1所示,图中从左至右包括时基产生与测频时序控制电路模块,以及待测信号脉冲计数电路和锁存与译码显示控制电路模块。

图5.10.1 系统组成框图(1)控制模块控制十进制计数器的计数及锁存器的工作,当计数器计数时,锁存器锁存前一次的计数状态,当计数器停止计数则锁存器接收计数器的计数数据,因此控制模块控制计数器与锁存器交替工作。

(2)计数器由于需要使用LED显示频率,所以采用的是10进制可清零、使能功能的计数器模块(3)锁存模块接收四个计数器传输的信号进行锁存。

(4)译码显示模块一共有6个LED需要显示,所以需要6个译码模块。

3.实验内容(1)完成各基本模块的设计,并对各模块进行功能仿真,得到仿真波形。

(2)设计顶层文件,将各模块结合在一起,构成频率计整体,并进行仿真,检查程序功能是否完善。

(3)对设计进行引脚配置并下载。

4.实验预习与思考(1)了解测频原理197(2)锁存模块在该系统的必要性。

(3)编写顶层设计文件时应当注意的问题。

5.程序设计与仿真(1)程序设计①顶层文件(freq_top.vhd)源程序如下:library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity freq_top isPort (CLKIN,RESET,QING1: IN STD_LOGIC; --控制信号DQ1,DQ2,DQ3,DQ4 : OUT STD_LOGIC_VECTOR (6 DOWNTO 0);--4位十进制数输出COUTT : OUT STD_LOGIC);--进位输出end freq_top;architecture Behavioral of freq_top isCOMPONENT TESTCTL —元件说明PORT ( rst, clkk : in std_logic;cnt_en, rst_cnt, load : out std_logic);END COMPONENT;COMPONENT CNT10PORT ( CLK,RST,EN : IN STD_LOGIC;CQ : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);COUT : OUT STD_LOGIC );END COMPONENT;COMPONENT REG4BPort ( load, QING : in std_logic;din : in std_logic_vector(3 downto 0);dout : out std_logic_vector(3 downto 0));END COMPONENT;COMPONENT DECL7SPORT (A : IN STD_LOGIC_VECTOR(3 DOWNTO 0);LED7S : OUT STD_LOGIC_VECTOR(6 DOWNTO 0) );END COMPONENT;--定义中间信号SIGNAL N : STD_LOGIC_VECTOR (24 DOWNTO 0); --秒分频SIGNAL M : STD_LOGIC_VECTOR (11 DOWNTO 0); --被测信号198SIGNAL FIN,F1HZ,EN_S,RST_S,LOAD_S : STD_LOGIC;SIGNAL CQ1,CQ2,CQ3,CQ4 : STD_LOGIC_VECTOR (3 DOWNTO 0);SIGNAL COUT1,COUT2,COUT3 : STD_LOGIC;SIGNAL DOUT1,DOUT2,DOUT3,DOUT4 : STD_LOGIC_VECTOR (3 DOWNTO 0);beginPROCESS(CLKIN,RESET)BEGINIF RESET='1' THEN N<=(OTHERS=>'0'); M<=(OTHERS=>'0');ELSIF(CLKIN'EVENT AND CLKIN='1')THENN<=N+1; M<=M+1;END IF;END PROCESS;F1HZ<=N(24);FIN<=M(11);--元件例化U1:TESTCTL PORT MAP (RST=>RESET,CLKK=>F1HZ,CNT_EN=>EN_S,RST_CNT=>RST_S, LOAD=>LOAD_S);U2 : CNT10 PORT MAP (FIN, RST_S, EN_S, CQ1, COUT1);U3 : CNT10 PORT MAP (COUT1, RST_S, EN_S, CQ2, COUT2);U4 : CNT10 PORT MAP (COUT2, RST_S, EN_S, CQ3, COUT3);U5 : CNT10 PORT MAP (COUT3, RST_S, EN_S, CQ4, COUTT);U6 : REG4B PORT MAP (LOAD_S, QING1, CQ1, DOUT1);U7 : REG4B PORT MAP (LOAD_S, QING1, CQ2, DOUT2);U8 : REG4B PORT MAP (LOAD_S, QING1, CQ3, DOUT3);U9 : REG4B PORT MAP (LOAD_S, QING1, CQ4, DOUT4);U10 : DECL7S PORT MAP (DOUT1, DQ1);U11 : DECL7S PORT MAP (DOUT2, DQ2);U12 : DECL7S PORT MAP (DOUT3, DQ3);U13 : DECL7S PORT MAP (DOUT4, DQ4);end Behavioral;②十进制计数器模块(cnt10.vhd)源程序如下:library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity cnt10 isPort (CLK,RST,EN : IN STD_LOGIC;CQ : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);COUT : OUT STD_LOGIC );end cnt10;199architecture Behavioral of cnt10 isbeginPROCESS(CLK, RST, EN)V ARIABLE CQI : STD_LOGIC_VECTOR(3 DOWNTO 0):="0000";BEGINIF RST = '1' THEN CQI := (OTHERS =>'0');ELSIF CLK'EVENT AND CLK='1' THENIF EN='1' THENIF CQI < "1001" THEN CQI := CQI + 1;ELSE CQI :=(OTHERS=>'0');END IF;END IF;END IF;IF CQI = "0000" THEN COUT <= '1';ELSE COUT<= '0';END IF;CQ <= CQI;END PROCESS;end Behavioral;③四位锁存器模块(reg4b.vhd)源程序如下:library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity reg4b isPort ( load : in std_logic;qing : in std_logic;din : in std_logic_vector(3 downto 0);dout : out std_logic_vector(3 downto 0));end reg4b;architecture Behavioral of reg4b isbeginprocess(load,qing,din)beginif qing = '1' then dout <= "0000";elsif load'event and load = '1' then dout <= din ;end if ;end process;200end Behavioral;④控制模块(testctl.vhd)源程序如下:library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity testctl isPort ( rst, clkk : in std_logic;cnt_en, rst_cnt, load : out std_logic);end testctl;architecture Behavioral of testctl issignal div2clk : std_logic;beginprocess( clkk ,rst)beginif rst = '1' then div2clk <= '0' ;elsif clkk'event and clkk = '1' then div2clk <= not div2clk;end if;end process;process ( clkk, div2clk )beginif clkk = '0' and div2clk='0' then rst_cnt <= '1';else rst_cnt <= '0';end if;end process;load <= not div2clk;cnt_en <= div2clk;end Behavioral;(2)仿真①四位锁存器仿真结果如图5.10.2所示。

数字频率计设计(使用VHDL语言)

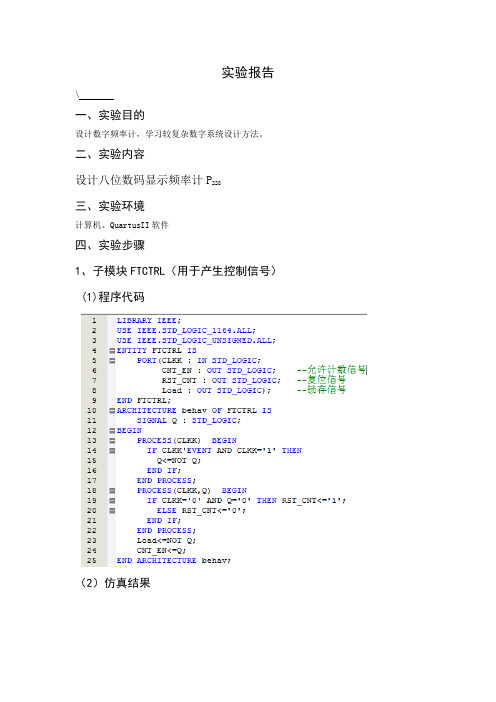

实验报告\

一、实验目的

设计数字频率计,学习较复杂数字系统设计方法。

二、实验内容

设计八位数码显示频率计P228

三、实验环境

计算机、QuartusII软件

四、实验步骤

1、子模块FTCTRL(用于产生控制信号) (1)程序代码

(2)仿真结果

2

、子模块COUNTER32B (用于计数)

(1)程序代码

(2)仿真结果

(3)结果分析

当使能信号ENABLE=‘1’时,允许计数。

当CLR=‘1’时重新计数

3、子模块REG32B(输出数据)

(1)程序代码

(2)仿真结果

(3)结果分析

当LK=’1’时,输出当前数据DIN,否则不做处理。

4、子模块SHOW

(1)程序代码

(2)仿真结果

(3)结果分析

当S=‘0’时,载入数据DATA,否则将数据DATA左移4位。

每次上升沿,SHOW1输出数据的高四位。

综合模块:

五、实验结果与讨论

这个实验花了比较多的时间,在做计数器的时候由于没有考虑到最后使用的是二进制显示的,所以在转换的时候遇到了不少的问题,最后

新亏有老师帮我想了办法解决。

基于VHDL的数字频率计设计与仿真

Science and Technology &Innovation ┃科技与创新2021年第22期·63·文章编号:2095-6835(2021)22-0063-02基于VHDL 的数字频率计设计与仿真*单炜佳1,周丰2(1.嘉兴学院,浙江嘉兴314001;2.嘉兴南湖学院,浙江嘉兴314001)摘要:使用EDA 技术中较为常用的VHDL 语言完成数字频率计的仿真验证分析。

通过仿真分析实现数字频率计的测量电路的设计以及验证数字频率计的测量正确性。

关键词:VHDL ;数字;频率计;仿真分析中图分类号:TM935.1文献标志码:ADOI :10.15913/ki.kjycx.2021.22.027在数字频率计设计过程中,针对于测量仪表,它实现的功能是能够测量SIN 信号以及单位脉冲信号,各种信号的频率范围,通过单位时间内的物理量采集实现。

数字频率的测量,技术上具有很强的技能性以及涵盖性。

就目前的生活而言,人们生活中使用的电视、冰箱、洗衣机以及其他智能家电发展到今天,数字频率计都是不可缺少的部件之一。

因此,数字频率计的测量范围更加广泛,而且它的设计结构越来越复杂,数字频率计对于整个电子产品的发展具有举足轻重的作用。

1系统设计与仿真本文所设计的频率计采用的是测频法的顶层设计中心思想,在软件开发环境中利用VHDL 语言进行设计的频率计,同时通过MODELSIM 软件进行仿真验证其测量正确性。

1.1数字频率计设计原理频率计,它的基本原理是将一个稳定的时钟源作为基准时钟,与其他信号的频率进行对比,实现频率周期性测量以及单位时间内的变化次数,从而实现时间内的重要取值。

同时它可以通过增加门时间的大小使频率值更加准确,但是时间越长,每一次测量的间隔时间就要长,它的测量精度就会受到影响,所以在一定时间间隔内,需要取合适的门时间的大小。

1.2整体程序结构本次程序主要包括实体库和结构体库,设计框图如图1所示。

频率计VHDL程序与仿真

数字频率计VHDL程序与仿真之袁州冬雪创作一、功能:频率计.具有4位显示,能自动根据7位十进制计数的成果,自动选择有效数据的高4位停止动态显示.小数点暗示是千位,即KHz.二、源程序及各模块和主要语句的功能library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity plj isport (start:in std_logic;--复位信号clk:in std_logic; --系统时钟clk1:in std_logic; --被测信号yy1:out std_logic_vector(7 downto 0); --八段码w1 :out std_logic_vector(3 downto 0)); --数码管位选信号end plj;architecture behav of PLj issignal b1,b2,b3,b4,b5,b6,b7:std_logic_vector(3 downto 0); --十进制计数器signal bcd:std_logic_vector(3 downto 0); --BCD码寄存器signal q :integer range 0 to 49999999; --秒分频系数signal qq : integer range 0 to 499999; --动态扫描分频系数signal en,bclk:std_logic; --使能信号,有效被测信号signal sss : std_logic_vector(3 downto 0); --小数点signal bcd0,bcd1,bcd2,bcd3 : std_logic_vector(3 downto 0);--寄存7位十位计数器中有效的高4位数据beginsecond:process(clk) --此过程发生一个持续时间为一秒的的闸门信号beginif start='1' then q<=0;elsif clk'event and clk='1' thenif q<49999999 then q<=q+1;else q<=49999999;end if;end if;if q<49999999 and start='0' then en<='1';else en<='0';end if;end process;and2:process(en,clk1) --此过程得到7位十进制计数器的计数脉冲beginbclk<=clk1 and en;end process;com:process(start,bclk) --此过程完成对被测信号计脉冲数beginif start='1' then --复位b1<="0000";b2<="0000";b3<="0000";b4<="0000";b5<="0000";b6<="0000";b7<="0000";elsif bclk'event and bclk='1' thenif b1="1001" then b1<="0000"; --此IF语句完成个位十进制计数if b2="1001" then b2<="0000";--此IF语句完成百位十进制计数if b3="1001" then b3<="0000"; --此IF语句完成千位十进制计数if b4="1001" then b4<="0000"; --此IF语句完成万位十进制计数if b5="1001" THEN b5<="0000";--此IF语句完成十万位十进制计数if b6="1001" then b6<="0000";--此IF语句完成百万位十进制计数if b7="1001" then b7<="0000";--此IF语句完成千万位十进制计数else b7<=b7+1;end if;else b6<=b6+1;end if;else b5<=b5+1;end if;else b4<=b4+1;end if;else b3<=b3+1;end if;else b2<=b2+1;end if;else b1<=b1+1;end if;end if;end process;process(clk) --此过程把7位十进制计数器有效的高4位数据送入bcd0~3;并得到小数点信息beginif rising_edge(clk) thenif en='0' thenif b7>"0000" then bcd3<=b7; bcd2<=b6; bcd1<=b5; bcd0<=b4; sss<="1110";elsif b6>"0000" then bcd3<=b6; bcd2<=b5; bcd1<=b4; bcd0<=b3; sss<="1101";elsif b5>"0000" then bcd3<=b5; bcd2<=b4; bcd1<=b3; bcd0<=b2; sss<="1011";else bcd3<=b4; bcd2<=b3; bcd1<=b2; bcd0<=b1; sss<="1111";end if;end if;end if;end process;weixuan:process(clk) --此过程完成数据的动态显示beginif clk'event and clk='1' thenif qq< 99999 then qq<=qq+1;bcd<=bcd3; w1<="0111";if sss="0111" then yy1(0)<='0';else yy1(0)<='1';end if;elsif qq<199999 then qq<=qq+1;bcd<=bcd2; w1<="1011";if sss="1011" then yy1(0)<='0';else yy1(0)<='1';end if;elsif qq<299999 then qq<=qq+1;bcd<=bcd1; w1<="1101";if sss="1101" then yy1(0)<='0';else yy1(0)<='1';end if;elsif qq<399999 then qq<=qq+1;bcd<=bcd0; w1<="1110";if sss="1110" then yy1(0)<='0';else yy1(0)<='1';end if;else qq<=0;end if;end if;end process;m0: process (bcd) --译码begincase bcd iswhen "0000"=>yy1(7 downto 1)<="0000001"; when "0001"=>yy1(7 downto 1)<="1001111"; when "0010"=>yy1(7 downto 1)<="0010010"; when "0011"=>yy1(7 downto 1)<="0000110"; when "0100"=>yy1(7 downto 1)<="1001100"; when "0101"=>yy1(7 downto 1)<="0100100"; when "0110"=>yy1(7 downto 1)<="1100000"; when "0111"=>yy1(7 downto 1)<="0001111"; when "1000"=>yy1(7 downto 1)<="0000000"; when "1001"=>yy1(7 downto 1)<="0001100"; when others=>yy1(7 downto 1)<="1111111"; end case;end process;end behav;三、程序仿真图注:仿真中秒分频为50000,动态显示的分频系数也相应调小.频率计仿真全图频率计仿真-开端计数部分频率计仿真-竣事竣事、动态显示部分频率计仿真-复位、重新测频部分。

基于VHDL语言设计数字频率计

基于VHDL语言设计数字频率计摘要:该频率计采用STC公司生产的STC89C51单片机和Altera公司所生产的FPGA芯片EP1C6Q240C8N。

FPGA的软件用VHDL语言描述实现在单片机的控制信号下进行计数。

单片机的软件采用C语言编写,很方便处理运算由FPGA传给单片机的数据。

关键字:一、引言频率检测是电子测量领域的最基本也是最重要的测量之一。

频率信号抗干扰能力强、易于传输,可以获得较高的测量精度,所以测频率方法的研究越来越受到重视。

以往的测频仪都是在低频段利用测周的方法、高频段用测频的方法,其精度往往会随着被测频率的下降而下降。

该设计采用等精度测量方法,解决了这个问题。

本设计中采用的STC89C51是一种低功耗、高性能的8位CMOS单片机,片内有4KB的闪烁可编程/擦除只读存储器,并且与MCS-51引脚和指令系统完全兼容,并且有宽工作电压范围、存储数据保存时间长(10年)等优点,是一款性价比较高的单片机。

EP1C6Q240C8N可容纳各种各样、独立的组合逻辑和时序逻辑函数,可以快速而有效的重新编程,并保证可编程擦除100次,这样可以进行重复烧录,比较方便系统的调试。

FPGA的各种功能块用VHDL语言描述实现。

该测频仪将FPGA 的高速高可靠性、单片机的灵活控制功能和等精度测频原理较高的测量精度相结合,具有速度快、功能全、精度高等特点。

二、设计原理1、设计内容设计一数字频率计,测量功能如下:(1) 能测量正弦波、方波等信号的频率(周期);(2) 能测量脉冲信号的宽度、占空比;(3) 由键盘选择确定测量功能;(4) 能实时显示被测信号的频率(周期)、脉宽等参数;(5) 具有自校功能,时标信号频率为2MHz;系统可由单片机控制单元与FPGA测量单元两部分构成。

其中,单片机控制单元主要实现处理运算FPGA测量单元送来的信号并产生反馈信号,通过单片机处理键盘的键值来选择区分各功能并控制液晶显示测量值。

基于VHDL语言的数字频率计设计

西安工程科技学院学报J o u r n a l o f X i'a nU n i v e r s i t yo f E n g i n e e r i n g S c i e n c e a n d T e c h n o l o g y第19卷第3期(总75期)2005年9月V o l.19,N o.3(S u m N o.75) =================================================================文章编号:1671-850X(2005)03-0321-04基于V H D L语言的数字频率计设计林晓焕1,林刚2(1.西安工程科技学院电信学院,陕西西安710048;2.中国飞行试验研究院,陕西西安710089)摘要:传统数字频率计由于在高频段受基准时钟频率的限制,其测频精度受到很大的限制.本文应用E D A技术,很好的解决了这一问题.文中论述了数字频率计的设计原理、开发环境、设计步骤、设计框架,以及应用V H D L语言对系统的实现方法,说明了各模块和系统输入输出信号的功用.应用M A X+P L U SⅡ对系统进行仿真验证,结果表明所设计的数字频率计不但测频精度达到较高的水平,而且能够实现连续不间断测频.关键词:数字频率计;V H D L语言;可编辑逻辑器件(F P G A)中图分类号:T N095文献标识码:A频率信号抗干扰性强,易于传输,可以获得较高的测量精度,所以测频方法的研究是电子测量领域的重要内容.传统的数字频率计一般由分离元件搭接而成,其测量范围、测量精度和测量速度都受到很大的限制.虽然单片机的发展与应用改善了这一缺陷,但由于单片机本身也受到工作频率及内部计数器位数等因素的限制,所以无法在此领域取得突破性的进展.随着新型可编程逻辑器件F P G A技术的发展,能够将大量的逻辑功能集成于一个单个器件中,根据不同的需要所提供的门数可以从几百门到上百万门,从根本上解决了单片机的先天性限制问题.不但集成度远远超过了以往的数字频率计,而且在基准频率及精度等外部条件的允许下,根据不同场合的精度要求,对硬件描述语言进行一定的改动,使系统在精度提高的同时,用较少的器件来实现系统的功能,从而降低系统的整体造价.此外,系统芯片(S O C)的发展也要求其包含频率测量的功能,所以用F P G A实现数字频率计也是实现系统芯片的前提条件.本文应用V H D L语言设计的集成化数字频率计系统,频率测量范围为1H z~50M H z,输入信号电压幅度为50m V~5V,测量精度为10-7H z.1设计原理目前常用的测频方法可以分为3类,即:(1)比较法通过与标准频率f0比较确定被测频率f x,测量精度主要取决于标准频率f0.主要方法有用于低频频率测量的拍频法、示波器法和用于高频频段测量的差频法等.(2)电路频率特性测量法由电路的已知参数与电路的频率特性得到被测频率f x,主要方法包括用于低频段的电桥法和用于高频或微波频段的谐振法.(3)记数器法由单位时间内周期信号的重复次数测得f x.目前最常用的是电子计数器法,其测量精度主要取决于基准时间和记数的量化误差.*收稿日期:2004-12-15通讯作者:林晓焕(1964-),女,陕西省西安市人,西安工程科技学院副教授,主要从事计算机通信方面的研究.E-m a i l: l i n x i a o h u a n325@y a h o o.c o m.c n本文采用在直接计数基础上发展出的多周期同步测频法[1],测量原理是由控制线路给出闸门开启信号.当待测信号的上升沿到来时,两组计数器开始计数,分别记录待测信号和时基脉冲信号;当控制线路给出闸门关闭信号,并在待测信号下降沿到来时结束计数,完成一个测量周期.待测频率的计算方法为f x =(N x /N 0)f 0.(1)式中f 0时基信号,由晶振产生;N x 为待测信号的计数值;N 0为时基信号的计数值;闸门时间为τ.图1多周期同步法测频原理波形图多周期同步测频法的原理波形如图1所示.由图1可见,对于此方法,其实际闸门与设定的闸门并不严格相等,但最大差值不超过被测信号的一个周期.由于多周期同步测频法的闸门时间是待测信号周期的整数倍,消除了传统直接测频法闸门开启时间与记数脉冲之间时基关系的不相关性,也就消除了由此引起的对待测信号记号产生的±1误差,提高了测量精度,实现了在整个测量频段内的等精度测量.多周期同步测频的相对误差主要由基准时间引起.时基信号的不准会造成主门启闭时间或长或短,对测频结果会产生一定的影响,并且被测频率越高,引起的误差就越大.此相对误差可通过对(1)式微分得到:d f x =-(N x /N 20)f 0d N 0+(N x /N 0)f 0d f 0.令d N 0=±1,τ=N x /f x =N 0/f 0,则有d f x /f x =±1/(τ·f 0)+d f 0/f 0,(2)其中d f 0/f 0为基准频率的误差.当d f 0/f 0与±1/(τ·f 0)相比特别小时,对其忽略不记,则测频的相对误差为d f x /f x =±1/(τ·f 0).(3)此时相对误差仅及闸门时间与时基频率有关,当然,要想进一步提高测频精度,必须提高基准频率的精度.在待测频率大于基准时钟频率时,多周期同步测频法的误差大于直接测频法的误差.为了保证所设计系统在较高频率时也能得到最佳的测频效果,当输入闸门时间内待测频率的测量结果大于基准时钟频率时,系统采用直接测频法工作.2系统的开发环境与设计步骤本数字频率计系统在A L T E R A 公司的M A X +P L U S Ⅱ开发环境下,应用V H D L 语言设计而成.A L T E R A 公司的M A X +P L U S Ⅱ开发环境综合了器件的物理结构,提供了各种的优化措施,最大限度的提高速度与资源利用率之间的平衡.M A X +P L U S Ⅱ提供了原理图形、文本、波形等多种输入手段,配备有编辑、编译、仿真、综合等多项功能,可方便的将电路描述程序做成A S I C 芯片,具有运行速度快、界面统一、功能集中等特点.用M A X +P L U S Ⅱ进行F P G A 开发的流程如图2示.a l t e r a m a x +p l u s Ⅱ设计→输入→编译→仿真→烧录→验证图2在M A X +P L U S Ⅱ环境下进行F P G A 开发的工作流程而V H D L 语言标准规范,易于共享与复用,非常适用于可编程逻辑芯片的应用设计.特别是自I E E E 公布了其标准及其更新版本之后,V H D L 语言逐渐成为系统设计领域最佳的硬件描述语言,其强大的行为描述能力避开了具体的硬件结构,为从逻辑行为上描述和设计大规模电子系统提供了重要保证[2].与传统的硬件描述语言相比,V H D L 语言不但设计功能强大,具有多层次的设计描述功能,可以进行与工艺无关的编程,而且方法灵活,支持广泛,可以很方便的进行A S I C 移植.而作为高密度现场可编程逻辑芯片的F P -G A ,能够将大量的逻辑功能集成到一个单片集成电路中,具有门阵列的高逻辑密度与通用性几用户可编程性.在目前条件下,V H D L 语言程序综合成为具体的F P G A 等目标器件的网表文件已不成问题[3],V H D L 223西安工程科技学院学报第19卷与F P G A 的结合为数字电路的设计带来了极大的方便.本文的设计过程如图3示.设计要求→用V H D L 语言进行设计描述→V H D L 原代码功能仿真→V H D L 原代码综合优化处理→网络表配→时序仿真→器件编程图3系统的设计过程图4系统的结构框图3系统设计与V H D L 语言实现整个系统根据各自功能与控制的关系分为5大模块,此5大模块按照相互间的信号连接关系组合起来,各模块间的流程由V H D L 语言并发处理.需说明的是,由于F P G A 只能实现数字电路,因此输入信号的整形电路需通过外加实现.在此假定F P G A 接收的都是已经整形、变换后的规则方波信号,电压幅值为0~5V .系统功能关系如图4示.控制模块是整个系统的控制部分,所有的控制信号几乎都由此模块产生,控制着其它4个模块的工作.控制模块根据外部对系统的复位和开始等信号,实现系统内部的复位、开始测频等功能,并通过优化模块的标志信号实现连续无间断的频率测量.控制模块首先通过对基准时钟分频得到模块所用时钟,使所产生的测量开始指令脉冲的宽度符合基准时间产生模块的输入要求,然后检测各输入信号,确定各模块的复位、测量、输出等操作.当控制模块接收到优化模块的标志信号时,控制模块先检测在最新一次复位后是否已经接受过系统开始测量脉冲信号.若是,则输出频率测量开始脉冲信号,使基准时间产生模块开始频率测量,同时送到优化模块,复位优化模块的内部变量,使优化模块能够再次输出反馈标志信号.这样,系统只需在开始施加一次频率测量开始脉冲信号,即可实现连续不间断的频率测量.基准时间产生模块用来产生系统所需的基准时间,即闸门时间.为适应对测频精度的不同要求,基准时间的长度可通过修改程序代码加以改变.基准时间越长,测频精度越高;反之,测频精度越低.模块的基准时钟由外加的晶振提供,经分频后用于产生基准时间方波信号.本模块每次输出基准时间方波信号之前,都先对计数模块进行复位,清除计数结果,保证系统在连续不间断测频时的正确性.基准时间产生模块接受控制模块产生的复位、开始指令,同时又向计数模块输出复位和计数指令.计数模块完成系统的频率测量等主要工作,是系统的核心.它通过对待测信号在基准时间内进行计数测量待测信号的频率.计数模块从基准时间产生模块接受复位信号和基准时间方波信号,清除上一次计数结果并进行新的计数,同时向优化模块输出结果信号和使能信号.使能信号在结果信号输出后才变为高电平,以允许优化模块对测频结果进行优化,保证测频结果的准确性.为了在给定条件下尽可能提高测频精度,计数模块首先需要估计对闸门时间内待测频率的大小.当待测频率大于等于基准时钟频率时,采用直接测量法;当待测频率小于基准时钟频率时,采用多周期同步法.这样,系统在低频和高频段都能实现较高的测频精度,突破了基准时钟频率对精度的限制,从而在整体上提高了系统的测频性能.优化模块主要对计数结果进行优化处理,以进一步提高系统的测频精度.其原理是把若干个测频结果加权平均,把加权平均的结果作为系统最后的测频结果,以减小计数器的误差对整个系统的影响.优化模块的复位信号由控制模块提供,结果由计数模块接提供.优化模块将计数结果存储到内部寄存器后,产生一标志信号,送到控制模块,以便新的一轮的频率测量,从而实现连续不间断测频.测频结果经优化后送显示模块显示.显示模块的主要工作是产生共阴级数码管显示所需的控制信号和数据信号,将从优化模块得到的测频结果最终用数码管实时显示出来.模块内用于循环显示的时钟由基准时钟经分频处理后得到.显示模块将二进制的结果信号转换成B C D 码的形式输入给数码管,同时对数码管以较高的频率不断重复进行刷新.模块输出的某一数码管选通信号为低电平时,表示该数码管被选中有效,可以进行显示操作.所需显示数据由模块输出的数据信号提供,根据数据信号各位是否为低电平决定是否点亮数码管中对应的显示段.323第3期基于V H D L语言的数字频率计设计图5数字频率计系统结构整个系统有4个输入信号,分别为基准时钟信号、待测时钟信号、系统复位信号(高电平有效)和开始测量脉冲信号;输出信号有2个,即各个数码管选通信号和系统输出数据信号,如图5示.图5各信号的作用如下:(1)基准时钟信号由外加晶振提供,同时作用于系统的5个模块,整个系统都以它为基准,基准频率经二分频后得到各模块内部所用的时钟信号.(2)待测时钟信号作用于计数模块,经过外加整形电路的整形与放大,符合标准方波的输入要求.(3)系统复位信号作用于控制模块,用于对整个系统的复位工作,为高电平有效.一般在每次测量前都要对系统进行复位操作,系统复位后处于等待测量状态.(4)系统开始测量信号指示系统开始连续不间断的测量,作用于控制模块,其脉冲宽度大于模块的一个时钟周期.当系统收到此信号后,就开始对待测时钟信号进行频率测量并输出测量结果.(5)输出的数码管选通信号和系统输出数据信号用于控制数码管的实时显示,控制信号低电平时表示该控制信号对应的数码管可以进行显示操作,数据信号输出数码管显示所需的数据.4结束语采用自上而下的设计方法,将数字频率计系统划分为5个子模块,针对各个子模块分别进行设计与编程,充分利用V H D L 语言的并行处理功能,同时考虑器件的时延对系统的影响.设计出的系统经过M A X +P L U S Ⅱ的仿真验证,最终完全实现了预定的功能,在测量范围、测量精度、测量速度以及系统造价等方面都比以前有较大的改善.对于1H z ~50M H z 的频率范围,其测量精度达10-7H z ,并且在低频和高频都具有较好的测频性能,能够满足一定场合的测频要求.参考文献:[1]M I L A NP r o k i n .D y n a m i c r e s p o n s e o f a f r e q u e n c ym e a s u r i n g s y s t e m [J ].I E E ET r a n s I n s t r uM e a s ,1992,41(3):390-396.[2]侯伯享,顾新.V H D L 硬件描述语言与数字逻辑电路设计[M].西安:西安电子科技大学出版社,1997.10-65.[3]赵雅兴.FP G A 原理、设计与应用[M].天津:天津大学出版社,1999.5-12.T h e d e s i g no f d i g i t a l c y m o m e t e r b a s e d o nV H D LL I N X i a o -h u a n 1,L I N G a n g2(1.C o l l e g e o f E l e c t r o n i c s &I n f o r m a t i o n ,X A U E S T ,X i 'a n710048,C h i n a ;2.C h i n a F l i g h t T e s t E s t a b l i s h m e n t ,X i 'a n710089,C h i n a )A b s t r a c t :T h e p r e c i s i o no f t r a d i t i o n a l d i g i t a l c y m o m e t e r i s p r o d i g i o u s l i m i t e d b y t h e n o r mc l o c k f r e q u e n c y ,e s p e c i a l -l y i n t h e h i g h f r e q u e n c y b a n d ,b u t t h i s p r o b l e mi s g o o d r e s o l v e d i n h e r e f r o mu s i n g t h e E D At e c h n o l o g y .I n t h i s p a -p e r ,t h e d i g i t a l c y m o m e t e r 's d e s i g n p r i n c i p l e a n d p r o c e s s ,e x p l o i t e n v i r o n m e n t ,f r a m e w o r k a n d r e a l i z a t i o n m e t h o d b yV H D La r e d i s c u s s e d i n d e t a i l ,a n d t h e m o d u l e s a n d i n p u t /o u t p u t s i g n a l s 'f u n c t i o na r e e x p l a i n e d p a r t i c u l a r l y .B ye m u l a t i o n a l v a l i d a t e i n M A X +P L U S Ⅱ,w e c a n s e e t h a t t h e d i g i t a l c y m o m e t e r 's p r e c i s i o n h a s r e a c h e d t o a h i g h -e r l e v e l ,a n d i t c a nr e a l i z e u n i n t e r r u p t e d f r e q u e n c yc o u n t .K e y w o r d s :V H D L ;d i g i t a l c y m o m e t e r ;F P G A 编辑、校对:董军浪423西安工程科技学院学报第19卷。

基于VHDL的数字频率计的设计与实现

/ / 定义变量

BEGIN

IF RST = '1' THEN CQI:=( OTHERS = > '0');

/ / 计数器复位

ELSIF CLK'EVENT AND CLK = '1' THEN

/ / 检测时钟上升沿

IF EN = '1' THEN

/ / 检测是否允许计数

IF CQI < " 1001" THEN CQI:= CQI + 1;

关键词:VHDL;EDA;频率计;自顶而下

中图分类号:TP312

文献标识码:B

文章编号:1004 373X(2005)15 000 03

Design and Realization of Digital Frequency Counter Based on VHDL

WANG Rongcheng,CHEN Kezhong,MING Xin

1 测频原理

测频法就是在确定的闸门时间 Tw 内,记录被测信号 的变化周期数(或脉冲个数) Nx,则被测信号的频率为:

fx = Nx / Tw 测周期法需要有标准信号的频率 fs,在待测信号的一 个周期 Tx 内,记录标准频率的周期数 Ns,则被测信号的

收稿日期:2005 04 05 基金项目:广西大学设备处实验课独立设课项目“ 电子技术

图 4 十进制计数器

参考文献

4 系统初步软硬件联调 (1) 完整的程序编译通过后,可在 Max + PlusⅡ中建

立波形文件( *. SCF),设置好时钟和各信号的初始电平 后,便可运行仿真器进行仿真,仿真波形如图 5 所示。

图 5 说明:FSIN 端输入为待测频率,现假定为 2 Hz; CLK 端为标准时钟输入,闸门值为 1 s;低 4 位 DOUT3 ~ 0 输出为 0010H,即为十进制的 2,因此可以得知该设计的 内部时序运行与预定时序相吻合。

基于VHDL的数字频率计的设计与仿真设计

基于VHDL的数字频率计的设计与仿真设计1 引言1.1 设计背景随着计算机技术和半导体技术的发展,传统的硬件电路电路设计方法已大大落后于当今技术的发展,一种崭新的、采用硬件描述语言的硬件电路设计方法已经兴起,这是电子设计自动化(EDA)领域的一次重大变革。

目前,广泛使用的硬件描述语言VHDL(Very Speed Integrated Circuit Hardware Description Language)和Verilog HDL;它们先后被批准为国际标准语言。

据统计,目前在美国硅谷约有90%以上的ASIC 和FPGA采用硬件描述语言进行设计,VHDL的应用已成为当今以及未来EDA解决方案的核心,而且是复杂数字系统设计的核心。

数字频率计[1]是电子测量与仪表技术最基础的电子仪表类别之一,它是一种用十进制数字显示被测信号频率、周期、占空比的数字测量仪器,是在数字电路中的一个典型应用;实际的硬件设计的多功能数字频率计用到的器件较多,连线比较复杂,而且会产生比较大的延时,造成测量误差、可靠性差,随着复杂可编程逻辑器件(CPLD)的广泛应用,以EDA工具作为开发手段,运用VHDL语言,将使整大大简化,提高整体个系统的性能和可靠性;它是计算机、通信设备、音频视频等科研生产领域不可缺少的测量仪器。

采用VHDL编程设计实习的多功能数字频率计,具有体积小,可靠性高,功耗低的特点;整个系统非常精简,且具有灵活的现场可更改性。

数字频率计是计算机、通讯设备、音频视频等科研生产领域不可缺少的测量仪器,而且它是数字电压必不可少的部件。

当今数字频率计不仅是作为电压表,计算机,天线电广播通讯设备,工艺过程自动化装置、多种仪表仪器与家庭电器等许多电子产品中的数据信息输出显示器反映到人们眼帘。

集成数字频率计由于所用元件少、投资少、体积小、功耗低,且可靠性高、功能强、易于设计和研发,使得它具有技术上的实用性和应用的广泛性。

不论从我们用的彩色电视机、电冰箱、DVD还有我们现在家庭常用到的数字电压表数字万用表等等都包含有频率计。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

二、数字频率计VHDL程序与仿真--文件名:plj.vhd。

--功能:频率计。

具有4位显示,能自动根据7位十进制计数的结果,自动选择有效数据的--高4位进行动态显示。

小数点表示是千位,即KHz。

--最后修改日期:2011.4.9。

library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity plj isport ( start:in std_logic; --复位信号clk :in std_logic; --系统时钟clk1:in std_logic; --被测信号yy1:out std_logic_vector(7 downto 0); --八段码w1 :out std_logic_vector(3 downto 0)); --数码管位选信号end plj;architecture behav of PLj issignal b1,b2,b3,b4,b5,b6,b7:std_logic_vector(3 downto 0); --十进制计数器signal bcd:std_logic_vector(3 downto 0); --BCD码寄存器signal q :integer range 0 to 49999999; --秒分频系数signal qq : integer range 0 to 499999; --动态扫描分频系数signal en,bclk:std_logic; --使能信号,有效被测信号signal sss : std_logic_vector(3 downto 0); --小数点signal bcd0,bcd1,bcd2,bcd3 : std_logic_vector(3 downto 0);--寄存7位十位计数器中有效的高4位数据beginsecond:process(clk) --此进程产生一个持续时间为一秒的的闸门信号beginif start='1' then q<=0;elsif clk'event and clk='1' thenif q<49999999 then q<=q+1;else q<=49999999;end if;end if;if q<49999999 and start='0' then en<='1';else en<='0';end if;end process;and2:process(en,clk1) --此进程得到7位十进制计数器的计数脉冲beginbclk<=clk1 and en;end process;com:process(start,bclk) --此进程完成对被测信号计脉冲数beginif start='1' then --复位b1<="0000";b2<="0000";b3<="0000";b4<="0000";b5<="0000";b6<="0000";b7<="0000"; elsif bclk'event and bclk='1' thenif b1="1001" then b1<="0000"; --此IF语句完成个位十进制计数if b2="1001" then b2<="0000"; --此IF语句完成百位十进制计数if b3="1001" then b3<="0000"; --此IF语句完成千位十进制计数if b4="1001" then b4<="0000"; --此IF语句完成万位十进制计数if b5="1001" THEN b5<="0000"; --此IF语句完成十万位十进制计数if b6="1001" then b6<="0000"; --此IF语句完成百万位十进制计数if b7="1001" then b7<="0000"; --此IF语句完成千万位十进制计数else b7<=b7+1;end if;else b6<=b6+1;end if;else b5<=b5+1;end if;else b4<=b4+1;end if;else b3<=b3+1;end if;else b2<=b2+1;end if;else b1<=b1+1;end if;end if;end process;process(clk) --此进程把7位十进制计数器有效的高4位数据送如bcd0~3;并得到小数点信息beginif rising_edge(clk) thenif en='0' thenif b7>"0000" then bcd3<=b7; bcd2<=b6; bcd1<=b5; bcd0<=b4; sss<="1110";elsif b6>"0000" then bcd3<=b6; bcd2<=b5; bcd1<=b4; bcd0<=b3; sss<="1101";elsif b5>"0000" then bcd3<=b5; bcd2<=b4; bcd1<=b3; bcd0<=b2; sss<="1011";else bcd3<=b4; bcd2<=b3; bcd1<=b2; bcd0<=b1; sss<="1111";end if;end if;end process;weixuan:process(clk) --此进程完成数据的动态显示beginif clk'event and clk='1' thenif qq< 99999 then qq<=qq+1;bcd<=bcd3; w1<="0111";if sss="0111" then yy1(0)<='0';else yy1(0)<='1';end if;elsif qq<199999 then qq<=qq+1;bcd<=bcd2; w1<="1011";if sss="1011" then yy1(0)<='0';else yy1(0)<='1';end if;elsif qq<299999 then qq<=qq+1;bcd<=bcd1; w1<="1101";if sss="1101" then yy1(0)<='0';else yy1(0)<='1';end if;elsif qq<399999 then qq<=qq+1;bcd<=bcd0; w1<="1110";if sss="1110" then yy1(0)<='0';else yy1(0)<='1';end if;else qq<=0;end if;end if;end process;m0: process (bcd) --译码beginwhen "0000"=>yy1(7 downto 1)<="0000001";when "0001"=>yy1(7 downto 1)<="1001111";when "0010"=>yy1(7 downto 1)<="0010010";when "0011"=>yy1(7 downto 1)<="0000110";when "0100"=>yy1(7 downto 1)<="1001100";when "0101"=>yy1(7 downto 1)<="0100100";when "0110"=>yy1(7 downto 1)<="1100000";when "0111"=>yy1(7 downto 1)<="0001111";when "1000"=>yy1(7 downto 1)<="0000000";when "1001"=>yy1(7 downto 1)<="0001100";when others=>yy1(7 downto 1)<="1111111";end case;end process;end behav;程序仿真注:仿真中秒分频为50000,动态显示的分频系数也相应调小。

频率计仿真全图频率计仿真-开始计数部分频率计仿真-结束结束、动态显示部分频率计仿真-复位、重新测频部分。