半整数分频器的设计

分频器的设计

分频器的设计一、课程设计目的1.学会使用电路设计与仿真软件工具Hspice,熟练地用网表文件来描述模拟电路,并熟悉应用Hspice内部元件库。

通过该实验,掌握Hspice的设计方法,加深对课程知识的感性认识,增强电路设计与综合分析能力。

2.分频器大多选用市售成品,但市场上出售的分频器良莠不齐,质量上乘者多在百元以上,非普通用户所能接受。

价格在几十元以下的分频器质量难以保证,实际使用表现平庸。

自制分频器可以较少的投入换取较大的收获。

二.内容分频器-概述分频器是指使输出信号频率为输入信号频率整数分之一的电子电路。

在许多电子设备中如电子钟、频率合成器等,需要各种不同频率的信号协同工作,常用的方法是以稳定度高的晶体振荡器为主振源,通过变换得到所需要的各种频率成分,分频器是一种主要变换手段。

早期的分频器多为正弦分频器,随着数字集成电路的发展,脉冲分频器(又称数字分频器)逐渐取代了正弦分频器,即使在输入输出信号均为正弦波时也往往采用模数转换-数字分频-数模转换的方法来实现分频。

正弦分频器除在输入信噪比低和频率极高的场合已很少使用。

分频器-作用分频器是音箱中的“大脑”,对音质的好坏至关重要。

功放输出的音乐讯号必须经过分频器中的各滤波元件处理,让各单元特定频率的讯号通过。

要科学、合理、严谨地设计好音箱之分频器,才能有效地修饰喇叭单元的不同特性,优化组合,使得各单元扬长避短,淋漓尽致地发挥出各自应有的潜能,使各频段的频响变得平滑、声像相位准确,才能使高、中、低音播放出来的音乐层次分明、合拍,明朗、舒适、宽广、自然的音质效果。

在一个扬声器系统里,人们把箱体、分频电路、扬声器单元称为扬声器系统的三大件,而分频电路对扬声器系统能否高质量地还原电声信号起着极其重要的作用。

尤其在中、高频部分,分频电路所起到的作用就更为明显。

其作用如下:合理地分割各单元的工作频段;合理地进行各单元功率分配;使各单元之间具有恰当的相位关系以减少各单元在工作中出现的声干涉失真;利用分频电路的特性以弥补单元在某频段里的声缺陷;将各频段圆滑平顺地对接起来。

EDA课程设计---基于FPGA的半整数分频器设计

课程设计报告设计名称EDA(VHDL)课程设计专业班级电子0942姓名学号电气与信息工程学院二0一二年一月基于FPGA的半整数分频器设计一、系统设计任务及功能概述本系统是利用VHDL硬件描述语言和原理图输入方式,通过MUX+PLUSⅡ开发软件和ALTER 公司的FLEX系列EPF10K10LC84-4型FPGA方便的完成了半整数分频器电路的设计。

本系统是通过控制单位时间内两种分频比出现的不同次数来获得所需要的小数分频值。

二、系统设计方案和程序设计1.系统设计方案我们采用脉冲吞吐计数器和锁相环技术,先设计两个不同分频比的整数分频器,然后通112entity cont6 isport(clk:instd_logic;rst:instd_logic;en:instd_logic;qa,qb,qc:outstd_logic);end entity cont6;architecturewode of cont6 issignalcount:std_logic_vector(2 downto 0);beginprocess(clk,rst,en)isbeginifrst='1'then count<="000";elsifclk'event and clk='1'thenif en='1'thenif count="101" then count<="000";else count<=count+1;end if;end if;end if;end process;qa<=count(0);qb<=count(1);qc<=count(2);end architecture wode;模六计数器原件生成图如下:图一模六计数器原件生成上面的程序经编译、时序模拟在MAX+PLUSⅡ中可得到如图所示的仿真波形:图2模6计数器仿真波形(2)半整数分频器设计现在通过设计一个分频系数为5.5的分频器给出用FPGA设计半整数分频器的一般方法。

数字信息技术实验分频器设计报告精品

实验名称:分频器设计实验时间:2015年3月17日上午实验人:一、实验项目分频器设计实验:利用QuatusII仿真实现分频器设计。

二、实验仪器及器件计算机、USB-BLASTER下载线、数字系统实验箱、5V稳压电源。

三、实验目的1、熟悉教学实验板的使用,初步了解掌握Verilog HDL语言和VHDL语言。

2、掌握分辨器原理,熟悉分频器的功用,学习分频器的设计、掌握用Verilog HDL 或者VHDL 语言描述分频器的方法。

3、熟悉和掌握FPGA开发软件QuatusII的基本操作,用QuatusII编译Verilog和VHDL语言。

4、掌握USB-BLASTER下载工具的安装、以及程序下载方法。

5、学会FPGA I/O引脚分配和实现过程。

四、实验要求及内容1、首先下载给定的VHDL硬件描述语言编写的分频器示例程序,读懂程序,编译并仔细观察在实验板上的现象。

2、在QuatusII平台上进行波形仿真。

3、扩展内容:设计分频电路得到3分频器、8分频器和32分频器。

编写分频器的Verilog 或VHDL代码,并仿真,同时给出3、8、32分频仿真波形。

五、实验原理分频器主要分为偶数分频、奇数分频、半整数分频和小数分频,如果在设计过程中采用参数化设计,就可以随时改变参量以得到不同的分频需要。

在对时钟要求不是很严格的FPGA系统中,分频通常都是通过计数器的循环计数来实现的。

偶数分频(2N)偶数分频最为简单,很容易用模为N的计数器实现50%占空比的时钟信号,即每次计数满N(计到N-1)时输出时钟信号翻转。

奇数分频(2N+1)使用模为2N+1的计数器,让输出时钟在X-1(X在0到2N-1之间)和2N时各翻转一次,则可得到奇数分频器,但是占空比并不是50%(应为X/(2N+1))。

得到占空比为50%的奇数分频器的基本思想是:将得到的上升沿触发计数的奇数分频输出信号CLK1,和得到的下降沿触发计数的相同(时钟翻转值相同)奇数分频输出信号CLK2,最后将CLK1和CLK2相或之后输出,就可以得到占空比为50%的奇数分频器。

课程设计基于FPGA的半整数分频器设计

课程设计报告设计名称EDA(VHDL)课程设计专业班级电子0942姓名姬鹏冲学号0904451213成绩评定电气与信息工程学院二0一二年一月课程设计要求和成绩考核办法(要求和成绩考核办法在封皮背面打印)1.不允许在教室或实验室内吸烟、吃零食,不准带无关人员到教室或实验室活动,否则扣平时表现分。

2.凡病事假超过3天(每天7小时),或迟到早退三次以上,或旷课两次(1天)以上,不得参加本次考核,按不及格处理,本次课程设计不能通过。

3.病事假必须有请假条,需经班主任或有关领导批准,否则按旷课处理。

4.课程设计的考核由指导教师根据设计表现(出勤、遵守纪律情况等)、设计报告、设计成果、答辩等几个方面,给出各项成绩或权重,综合后给出课程设计总成绩。

该设计考核须经教研室主任审核,主管院长审批备案。

5.成绩评定采用五级分制,即优、良、中、及格和不及格。

6.课程设计结束一周内,指导教师提交成绩和设计总结。

7.设计过程考核和成绩在教师手册中要有记载。

实习报告要求实习报告内容、格式各专业根据实习(设计)类别(技能实习、认识实习、生产实习、毕业实习等)统一规范,经教研室主任审核、主管院长审批备案。

注意:1.课程设计任务书和指导书在课程设计前发给学生,设计任务书放置在设计报告封面后和正文目录前。

2.为了节省纸张,保护环境,便于保管设计报告,统一采用A4纸,课程设计报告建议双面打印(正文采用宋体五号字)或手写,左侧装订,订两个钉。

基于FPGA的半整数分频器设计一、系统设计任务及功能概述本系统是利用VHDL硬件描述语言和原理图输入方式,通过MUX+PLUSⅡ开发软件和ALTER 公司的FLEX系列EPF10K10LC84-4型FPGA方便的完成了半整数分频器电路的设计。

本系统是通过控制单位时间内两种分频比出现的不同次数来获得所需要的小数分频值。

二、系统设计方案和程序设计1.系统设计方案我们采用脉冲吞吐计数器和锁相环技术,先设计两个不同分频比的整数分频器,然后通过控制单位时间内两种分频比出现的不同次数来获得所需要的5.5分频值。

基于FPGA的半整数及整数分频器的参数化设计

基于FPGA的半整数及整数分频器的参数化设计

古良玲;杨永明;郭巧惠

【期刊名称】《电子器件》

【年(卷),期】2005(028)002

【摘要】一种具有通用性的半整数及整数分频电路,应用模块化的思想以及参数化的设计方法,在FPGA实验开发平台上得以实现,通过对具体参数的简单修改就可应用于不同场合,实验仿真以及仪器测试结果均取得了良好的效果.该设计通用性较好,可以应用于各种数字电路系统设计中.

【总页数】3页(P404-406)

【作者】古良玲;杨永明;郭巧惠

【作者单位】重庆大学电气工程学院,重庆,400044;重庆大学电气工程学院,重庆,400044;重庆大学电气工程学院,重庆,400044

【正文语种】中文

【中图分类】TP331.2;TN77

【相关文献】

1.基于FPGA的半整数分频器的设计 [J], 高凡;贾磊磊

2.基于CPLD/FPGA的半整数分频器的设计 [J], 林海波

3.基于CPLD/FPGA的半整数分频器的设计 [J], 夏继军

4.基于CPLD/FPGA的半整数分频器的设计 [J], 王蓉;李伟民

5.基于CPLD/FPGA的半整数分频器的设计 [J], 汪霞

因版权原因,仅展示原文概要,查看原文内容请购买。

分频器的VHDL设计

BEGIN

PROCESS(CLK,C1)

BEGIN

IF RISING_EDGE(CLK) THEN

IF(C1="011") THEN C1<="000"; ELSE C1<=C1+1;END IF;

IF(C1="001") THEN M1<=NOT M1; ELSIF(C1="011") THEN M1<=NOT M1;

IF(C2="001")THEN M2<=NOT M2;ELSIF (C2="100") THEN M2<=NOT M2;

END IF;END IF;

END PROCESS;

K1<=M1;K2<=M2;K_OR<=M1 OR M2;

END BHV;

半整数次分频:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

洛阳理工学院实验报告

系部

计算机与信息工程系

班级

学号

姓名

课程名称

PLD原理与应用

实验日期

2012.11.12

实验名称

实验四分频器的VHDL设计

成绩

实验目的:

1、练习应用QUARTUSⅡ开发环境

2、练习文件的建立,改编,编程,调试,修改,仿真。

3、学会设计奇数、偶数、半整数分频器。

实验条件:

装有QUARTUSⅡ软件的电脑

(1)建立新工程管理窗口。单击对话框第二栏右侧“···”按钮,找到文件夹d:\work\cnt10,选中已存盘文件cnt10.vhd,再单击“打开”按钮。

基于CPLD的任意整数半整数分频器设计

基于CPLD的任意整数半整数分频器设计0 引言在数字系统设计中,根据不同的设计需要,经常会遇到偶数分频、奇数分频、半整数分频等,有的还要求等占空比。

在基于cpld(复杂可编程逻辑器件)的数字系统设计中,很容易实现由计数器或其级联构成各种形式的偶数分频及非等占空比的奇数分频,但对等占空比的奇数分频及半整数分频的实现较为困难。

本文利用vhdl(甚高速集成电路硬件描述语言),通过quartus ⅱ4.2 开发平台,设计了一种能够实现等占空比的整数和近似等占空比的半整数分频器,这种设计方法原理简单,而且只需很少的cpld 逻辑宏单元。

1 设计原理系统设计框图如图1 所示。

根据不同分频系数设置适当的计数器周期,每个计数值对应输入时钟信号fi 的一个周期,让q0 只在fi 的上升沿及适当的计数范围内产生高电平,最后将q0 和q1 进行逻辑或操作,进而得到所需的分频信号fo。

q1 的作用是在奇数分频中补足下降沿处半个时钟周期,使其等占空比,以及在半整数分频中,在时钟下降沿处产生分频信号的上升沿,以实现半整数分频。

下面介绍如何确定计数器周期以及q0、q1 产生高电平输出时各自的计数范围。

为叙述方便,现规定如下标记:分频系数为divide(max downto 0),其中max 是分频数对应二进制数的最高位,对于半整数分频,最低位即第0 位为小数位;q 0_count 和q1_count 分别为q0 和q1 产生高电平的计数范围,并记divide(max downto 1)为a,divide(max downto 2)为b,divide(max downto 0)-1 为c。

1.1 偶数及奇数分频计数器周期都为0 到c。

等占空比的偶数分频很容易实现,在此不加叙述。

对奇数分频,只需当q0_count<a 时q0 输出高电平,当q1_count=a-1 时q1 输出一个周期的高电平,其他情况下q0 和q1 都为低电平,然后把q0 和q1 逻辑或,所得的输出fo。

《EDA(VHDL)课程设计》任务书

3.四组数字智力抢答器的VHDL设计(每班1-30号的双号选择)

系统设计要求是:

(1)设计制作一个可容纳四组参赛者的数字智力抢答器,每组设置一个抢答按钮供抢答者使用。

(1)主、支干道各设有一个绿、黄、红指示灯,两个显示数码管。

(2)主干道处于常允许通行状态,而支干道有车来才允许通行。

(3)当主、支道均有车时,两者交替允许通行,主干道每次放行45s,支干道每次放行25s,在每次由亮绿灯变成亮红灯的转换过程中,要亮5s的黄灯作为过渡,并进行减计时显示。

设计的基本要求

3.输入、输出接口说明

4.报告中有分频器、定时器相关模块的功能仿真和时序仿真结果。

5.编写内容充实、完整和规范的课程设计报告书。

6.课程设计报告要求校对仔细,无错字,A4纸打印,左侧装订。

主要参考文献

[1]谭会生,张昌凡.EDA技术及应用.西安:西安电子科技大学出版社,2006,12.

[2]潘松,黄继业.EDA技术实用教程.北京:科学出版社,2008,8.

2.99分钟定时器的VHDL设计(每班1-30号的单号选择)

任务要求:具有整体清零(reset)功能,定时99分钟。以秒速度递增至99分钟停止,启动报警(cout)5秒钟。具有置位(cn)控制,即cn高电平时,clk脉冲上升沿到来,计数加一;cn低电平时,置位结束,进入倒计时阶段,以秒速度使输出计数减一至零结束,并同时报警(cout)5秒钟。

为了防止雷同,建议每班1-4号设计2.5分频,5-8号设计3.5分频,9-12号设计4.5分频,13-16号设计5.5分频,17-20号设计6.5分频,21-24号设计7.5分频,25-28设计8.5分频,29-32设计9.5分频,33-36设计10.5分频,37-40号设计11.5分频,41-44号设计12.5分频计数器。

基于CPLD的半整数分频器的设计

目录引言 (3)1绪论 (4)2系统设计方案 (5)2.1设计方案比较 (5)2.1.1分频器的设计 (5)2.1.2控制输入装置的设计 (5)2.2 设计方案框图 (6)3系统设计实现 (7)3.1分频器部分 (7)3.1.1设计思路 (7)3.1.2设计实现 (8)3.1.3仿真分析 (10)3.2输入控制部分 (11)3.2.1设计思路 (11)3.2.2设计实现 (11)3.2.3仿真波形 (23)3.3分频显示部分 (24)3.3.1设计思路 (24)3.3.2设计实现 (26)3.3.3仿真分析 (33)3.3.4所需要改进之处 (36)3.4各部分整合 (37)4系统设计验证 (39)4.1适配分析结果 (39)4.2硬件运行 (39)5软硬件平台的介绍 (44)5.1软件平台 (44)5.1.1MAX+PLUS Ⅱ开发工具 (44)5.1.2MAX+PLUS Ⅱ的设计方法 (45)5.2 硬件平台 (46)5.2.1硬件原理 (46)5.2.2引脚规定 (48)5.2.3使用方法 (49)6小数分频技术的拓展 (51)结束语 (54)致谢 (55)附录 (56)A开题报告 (56)B中期报告 (59)C英文资料与中文翻译 (62)引言随着计算机与微电子技术的发展,电子设计自动化EDA技术和可编程逻辑器件PLD的发展都非常迅速,能否熟练地利用EDA软件进行PLD器件开发已成为电子工程师必须掌握的基本技能。

过去传统的设计方法采用标准通用器件和其他元件对电路板进行设计,由于系统所需的元件的种类和数量很多,连线复杂,因而体积大、功耗大、可靠性差。

而先进的EDA工具使传统的“自下而上”的设计方法已经变为“自顶向下”的设计方法,以硬件描述语言HDL来描述系统级设计,利用计算机对系统进行方案设计和功能划分,并支持系统仿真和高层综合,关键电路可使用ASIC来实现,因而使系统的体积、重量减少,功耗降低,具有高性能、高可靠性和高保密性等优点。

基于FPGA的可控分频器的设计

基于FPGA的可控分频器的设计【摘要】本文介绍了两种分频系数为整数或半整数的可控分频器的设计方法。

其中之一可以实现50%的奇数分频。

利用VHDL语言编程,并用QUARTERS||4.0进行仿真,用FPGA 芯片实现。

关键词:半整数,可控分频器,VHDL, FPGA【Abstract】The paper presents two method for designing the controllable frequency divider which division ratio is integer or half-integer. The frequency divider implemented with a FPGA chip is described in VHDL and simulated with.Keywords: half-integer, simulated, controllable frequency divider, VHDL1.引言分频器是数字系统设计中的基本电路,根据不同设计的需要,我们会遇到偶数分频、奇数分频、半整数分频等,有时要求等占空比,有时要求非等占空比。

在同一个设计中有时要求多种形式的分频。

通常由计数器或计数器的级联构成各种形式的偶数分频及非等占空比的奇数分频,实现较为简单。

但对半整数分频,等占空比的奇数分频及可控分频实现较为困难。

本文利用VHDL硬件描述语言,通过QuartusⅡ4.0开发平台,使用Altera公司的FPGA,设计了一种能够满足上述各种要求的较为通用的可控分频器。

只要在分频器的输入端输入相应的分频系数,就可以得到所需的频率。

在通常的FPGA设计方法中,为了能实现等占空比的奇数分频,常采用对输入频率进行二倍频的电路,以及对倍频后的频率F进行偶数分频,这样大大降低了设计电路的最高工作频率,提高了对硬件的要求。

为此,本文的设计在不改变设计要求的前提下,对常规的设计方法进行了改进,实现了在不需要对输入频率进行二倍频的条件下的等占空比分频,从而更好的利用了FPGA的频率资源,同时还降低了设计的复杂性。

奇数和偶数分频器和半整数及任意小数分频器设计

1、半整数分频占空比不为50%//说明:我设计的史上最好用的半整数分频占空比不为50%,包含设计思路module div_5(clk,clk_div,cnt1,cnt2,temp1,temp2);//N+0.5input clk;output clk_div;output reg[31:0]cnt1,cnt2;output reg temp1,temp2;initial begin temp1=0;temp2=1;end //首先进行初始化,temp1=0;temp2=1 parameter N=5; //设定分频系数为N+0.5always @(posedge clk) //temp1上升沿跳变beginif(cnt1==2*N) //2*Nbegin cnt1[31:0]<=32'd0;endelse begin cnt1[31:0]<=cnt1[31:0]+32'd1;endif(cnt1==32'd0) begin temp1<=1;end //高电平时间为N+1;if(cnt1==N+1) begin temp1<=0;end//低电平时间为N;endalways@(negedge clk) //temp2下降沿跳变beginif(cnt2==2*N) //2*Nbegin cnt2[31:0]<=32'd0;endelse begin cnt2[31:0]<=cnt2[31:0]+32'd1;endif(cnt2==32'd0) begin temp2<=0;end //低电平时间为N;if(cnt2==N) begin temp2<=1;end //高电平时间为N+1;endassign clk_div=temp1&&temp2; //逻辑与endmodule//如果要进行N+0.5分频//思路:总的来说要进行N+1+N=2N+1次分频//在时钟的上升沿和下降沿都进行跳变//上升沿进行占空比为N+1比N的时钟temp1;//下降沿进行占空比为N比N+1的时钟temp2;//最后div=temp1&&temp2 即可得到所需要的半整数分频分频5.5仿真结果2、奇数分频占空比为50%//说明:奇数分频。

VHDL语言各种分频器的设计解析

if(clkin”event and clkin=”1”) then

if(cnt<n-1) then

cnt <= cnt+1;

else

cnt <= 0;e Nhomakorabead if;

end if;

end process;

process(cnt) --依据计数值,把握输出时钟脉冲的高、低电平

begin

if(cnt<n/2) then

port(

clkin: IN std_logic;

clkout: OUT std_logic

);

End fdiv;

Architecture a of fdiv is

signal cnt: integer range 0 to n-1;

Begin process(clkin) --计数

begin

port(

clkin: IN std_logic;

clkout: OUT std_logic

);

End fdiv;

Architecture a of fdiv is

signal cnt: std_logic_vector(N-1 downto 0);

Begin

process(clkin)

ELSE

count <= count-1;

--模N计数器减法计数

clkout <= ”0”;

END IF;

END IF;

END PROCESS;

PROCESS(clkout)

BEGIN

IF(clkout”event AND clkout=”1”) THEN

div2 <= NOT div2; --输出时钟二分频

实验七 分频器电路设计

实验七、分频器电路设计一、实验目的1、学习任意分频器的设计方法;2、学习数控分频器的设计、分析和测试方法。

二、实验要求1、基本要求1、设计一个偶分频器2、设计一个2n分频器3、设计一个奇分频器4、设计一个半整数分频器5、设计一个数控分频器2、扩展要求1、设计一个任意N分频计数器。

N为奇数或偶数2、设计一个硬件电子琴电路三、实验原理1、偶数分频对时钟进行偶数分频,使占空比为50%。

只要使用一个计数器,在计数器的前一半时间使输出为高电平,在计数器的后一半时间使输出为低电平,即可得到偶分频时钟。

2、奇数分频对时钟进行奇数分频,使占空比为50%。

先对输入时钟的上升沿进行计数,让一个内部信号在前一半时间(分频系数除2取整)为高电平,后一半时间为低电平;再对输入时钟的下降沿进行计数,让另一个内部信号在前一半时间为高电平,后一半时间为低电平;然后将这内部两个信号相或后即得到奇数分频时钟。

3、2n分频器用一个M(2M>=f0)位的二进制计数器对输入时钟进行计数。

其第0位为输入时钟的二分频,第1位为输入时钟的四分频,第2位为输入时钟的8分频,依此类推,第n-1位为输入时钟的2n分频。

4、半整数分频器分频系数为N=0.5的整数倍的分频器电路可由一个异或门、一个模N的计数器和一个2分频构成。

通用半整数分频器电路组成如图7-1所示。

图7-1 通用半整数分频器电路框图与原理图5、数控分频器数控分频器的功能就是在输入端给定不同的输入数据时,将对输入的时钟信号有不同的分频比。

数控分频器一般是用计数值可并行预置的加法计数器完成的,方法是将计数溢出位与预置数加载输入信号相接即可。

四、实验步骤建立一个工程项目,路径如:D:\20050837\seventh ,项目名和顶层实体名为freq_div 。

1、设计一个分频系数可预置的偶分频器(如8分频器),并进行编译仿真。

2、设计一个2n 分频器(如输入频率为1024HZ ,输出频率为256HZ ,64Hz ,4Hz 等),并进行编译仿真。

EDA半整数分频器课程设计

library ieee;use ieee.std_logic_1164.all;entity fpq isport(fsin: in std_logic;Preset :in std_logic_vector(3 downto 0);clk: in std_logic;dout: out std_logic_vector(31 downto 0);seltmp:out std_logic_vector(7 downto 0);smtmp:out std_logic_vector(6 downto 0)); end;architecture art of fpq iscomponent cnt10port(clk,clr,ena: in std_logic;cq: out std_logic_vector(3 downto 0);carry_out: out std_logic);end component;component reg32bport(load: in std_logic;din: in std_logic_vector(31 downto 0);dout: out std_logic_vector(31 downto 0)); end component;component testctltsten,clr_cnt,load: out std_logic);end component;component deccountPort (inclk :in std_logic;Preset :in std_logic_vector(3 downto 0);--y_tmpdiv,y_tmpclk: out std_logic;Outclk:buffer std_logic);end component;--component zmjsxs--port(ck: in std_logic;--data: in std_logic_vector(31 downto 0);--sel: out std_logic_vector(7 downto 0);--sm: out std_logic_vector(6 downto 0)); --end component;signal tsten: std_logic;signal clr_cnt: std_logic;signal load: std_logic;signal carry1: std_logic;signal carry2: std_logic;signal carry3: std_logic;signal carry5: std_logic;signal carry6: std_logic;signal carry7: std_logic;signal carry8: std_logic;signal din: std_logic_vector(31 downto 0);signal outclk: std_logic;signal fsintmp: std_logic;signal douttmp: std_logic_vector(7 downto 0);beginfsintmp<=fsin;dout<=douttmp;u:deccount port map(inclk=>fsintmp,preset=>preset,outclk=>outclk);u0: testctl port map(clk=>clk,tsten=>tsten,clr_cnt=>clr_cnt,load=>load);u1: cnt10 port map(clk=>outclk,clr=>clr_cnt,ena=>tsten,cq=>din(3 downto 0),carry_out=>carry1);u2: cnt10 port map(clk=>carry1,clr=>clr_cnt,ena=>tsten,cq=>din(7 downto 4),carry_out=>carry2);u3: cnt10 port map(clk=>carry2,clr=>clr_cnt,ena=>tsten,cq=>din(11 downto 8),carry_out=>carry3);u4: cnt10 port map(clk=>carry3,clr=>clr_cnt,ena=>tsten,cq=>din(15 downto 12),carry_out=>carry4);u5: cnt10 port map(clk=>carry4,clr=>clr_cnt,ena=>tsten,cq=>din(19 downto 16),carry_out=>carry5);u6: cnt10 port map(clk=>carry5,clr=>clr_cnt,ena=>tsten,cq=>din(23 downto 20),carry_out=>carry6);u7: cnt10 port map(clk=>carry6,clr=>clr_cnt,ena=>tsten,cq=>din(27 downto 24),carry_out=>carry7);u8: cnt10 port map(clk=>carry7,clr=>clr_cnt,ena=>tsten,cq=>din(31 downto 28),carry_out=>carry8);u9: reg32b port map(load=>load,din=>din(31 downto 0),dout=>douttmp);--u10:zmjsxs port map (ck=>fsintmp,data=>douttmp,sel=>seltmp,sm=>smtmp); end art;Library ieee; -- N-0.5分频器Use ieee.std_logic_1164.all;Use ieee.std_logic_unsigned.all;Entity deccount isPort (inclk :in std_logic; --时钟源Preset :in std_logic_vector(3 downto 0); --预置分频值N--y_tmpdiv,y_tmpclk: out std_logic;Outclk:buffer std_logic); --输出时钟End deccount;Architecture aaa of deccount isSignal clk,divide2:std_logic;Signal count:std_logic_vector(3 downto 0);Begin--y_tmpdiv<=divide2;--y_tmpclk<=Clk;Clk<=inclk xor divide2; --incik与divide2异或后作为模N计数器的时钟Process (clk)BeginIf (clk'event and clk='1') thenIf(count="0000") thenCount<=preset-1; --置整数分频值N=preset-1Outclk<='1';ElseCount <=count-1; --模N计数器减法计数Outclk<='0';End if;End if;End process;Process(outclk)BeginIf (outclk'event and outclk='1')thenDivide2<=not divide2; --输出时钟outclk二分频End if;End process;End aaa;library ieee; --有时钟始能的十进制计数器use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt10 isport(clk: in std_logic; --计数时钟信号clr: in std_logic;ena: in std_logic;cq: out std_logic_vector(3 downto 0);carry_out: out std_logic); --计数进位end cnt10;architecture art of cnt10 issignal cqi: std_logic_vector(3 downto 0);beginprocess(clk,clr,ena)beginif clr='1' then cqi<="0000"; --计数器异步清零elsif clk'event and clk='1' thenif ena='1' thenif cqi<9 then cqi<=cqi+1;else cqi<="0000"; --等于9,则计数器清零end if;end if;end if;end process;process(cqi)beginif cqi=9 then carry_out<='1'; --进位输出else carry_out<='0';end if;end process;cq<=cqi;end art;library ieee; --32位锁存器use ieee.std_logic_1164.all;entity reg32b isport(load: in std_logic;din: in std_logic_vector(31 downto 0);dout: out std_logic_vector(31 downto 0));end reg32b;architecture art of reg32b isbeginprocess(load,din)beginif load'event and load='1' then dout<=din; --锁存输入数据end if;end process;end art;library ieee; --测频控制信号发生器use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity testctl isport(clk: in std_logic; --1HZ测频控制时钟tsten: out std_logic; --计数器时钟始能clr_cnt: out std_logic; --计数器清零load: out std_logic); --输出锁存信号end testctl;architecture art of testctl issignal div2clk: std_logic;beginprocess(clk)beginif clk'event and clk='1' thendiv2clk<=not div2clk; --1HZ时钟二分频end if;end process;process(clk,div2clk)beginif clk='0' and div2clk='0' then --产生计数器清零信号clr_cnt<='1';else clr_cnt<='0';end if;end process;load<=not div2clk;tsten<=div2clk;end art;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all; --"+"操作符重载entity zmjsxs isport(ck: in std_logic;data: in std_logic_vector(31 downto 0); --位显示sel: out std_logic_vector(7 downto 0);sm: out std_logic_vector(6 downto 0)); --段显示end;architecture art of zmjsxs issignal q_s: std_logic_vector(3 downto 0);signal tmp: integer range 0 to 7;beginprocess(ck) isbeginif ck'event and ck='1' thenif tmp=0 then sel<="00000001"; q_s<=data(3 downto 0);elsif tmp=1 then sel<="00000010";q_s<=data(7 downto 4);elsif tmp=2 then sel<="00000100";q_s<=data(11 downto 8);elsif tmp=3 then sel<="00001000";q_s<=data(15 downto 12);elsif tmp=4 then sel<="00010000";q_s<=data(19 downto 16);elsif tmp=5 then sel<="00100000";q_s<=data(23 downto 20);elsif tmp=6 then sel<="01000000";q_s<=data(27 downto 24);else sel<="10000000";q_s<=data(31 downto 28);end if;if tmp>=7 then tmp<=0;else tmp<=tmp+1;end if;end if;end process;process(q_s) isbegincase q_s iswhen "0000"=> sm<="1111110";when "0001"=> sm<="0110000";when "0010"=> sm<="1101101";when "0011"=> sm<="1111001";when "0100"=> sm<="0110011";when "0101"=> sm<="1011011";when "0110"=> sm<="1011111";when "0111"=> sm<="1110000";when "1000"=> sm<="1111111";when "1001"=> sm<="1111011";when others=> sm<="0000000"; end case;end process;end architecture art;。

eda的几个实验仿真图形

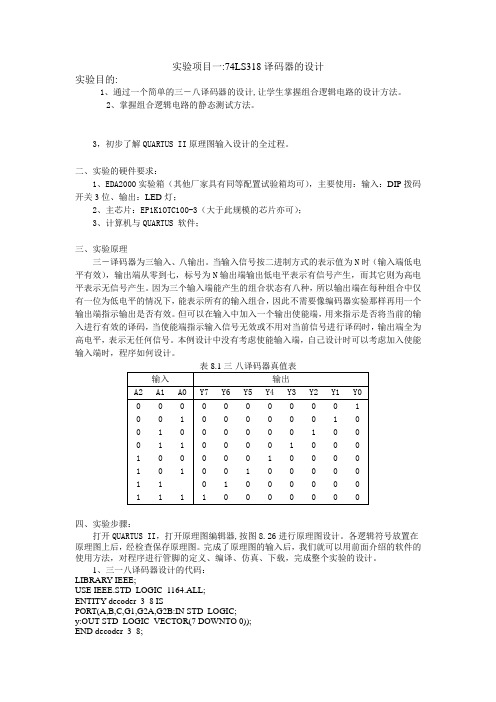

实验项目一:74LS318译码器的设计实验目的:1、通过一个简单的三-八译码器的设计,让学生掌握组合逻辑电路的设计方法。

2、掌握组合逻辑电路的静态测试方法。

3,初步了解QUARTUS II原理图输入设计的全过程。

二、实验的硬件要求:1、EDA2000实验箱(其他厂家具有同等配置试验箱均可),主要使用:输入:DIP拨码开关3位、输出:LED灯;2、主芯片:EP1K1OTC100-3(大于此规模的芯片亦可);3、计算机与QUARTUS 软件;三、实验原理三-译码器为三输入、八输出。

当输入信号按二进制方式的表示值为N时(输入端低电平有效),输出端从零到七,标号为N输出端输出低电平表示有信号产生,而其它则为高电平表示无信号产生。

因为三个输入端能产生的组合状态有八种,所以输出端在每种组合中仅有一位为低电平的情况下,能表示所有的输入组合,因此不需要像编码器实验那样再用一个输出端指示输出是否有效。

但可以在输入中加入一个输出使能端,用来指示是否将当前的输入进行有效的译码,当使能端指示输入信号无效或不用对当前信号进行译码时,输出端全为高电平,表示无任何信号。

本例设计中没有考虑使能输入端,自己设计时可以考虑加入使能输入端时,程序如何设计。

表8.1三-八译码器真值表输入输出A2 A1 A0 Y7 Y6 Y5 Y4 Y3 Y2 Y1 Y00 0 0 0 0 0 0 0 0 0 10 0 1 0 0 0 0 0 0 1 00 1 0 0 0 0 0 0 1 0 00 1 1 0 0 0 0 1 0 0 01 0 0 0 0 0 1 0 0 0 01 0 1 0 0 1 0 0 0 0 01 1 0 1 0 0 0 0 0 01 1 1 1 0 0 0 0 0 0 0四、实验步骤:打开QUARTUS II,打开原理图编辑器,按图8.26进行原理图设计。

各逻辑符号放置在原理图上后,经检查保存原理图。

完成了原理图的输入后,我们就可以用前面介绍的软件的使用方法,对程序进行管脚的定义、编译、仿真、下载,完成整个实验的设计。

实验4 数控分频器设计

分频器设计的基础——计数器

4位二进制加法计数器

计满全1后,产生进位信号cout,cout的频率是计数时钟 频率的16分之一,称cout是clk的十六分频。 如果有一个预置数d[3..0],从d开始计数计到全1,这时进 位信号cout与clk的频率关系是什么呢? 分频比R=“1111”-d[3..0]+1

• • • • • • •

p1:process(cout) begin if cout'event and cout='1' then --信号cout上升沿时,div2取反 div2<=not div2; --即div2是cout的二分频 end if; end process; end;

设计的关键点在于一个信号与0异或,得到的是信号本身;与1异或, 得到的是信号的取反。。

实验四 数控分频器的设计

1.实验目的 (1)学习时序电路VHDL语言设计。 (2)学习多进程设计,掌握变量的用法与信号 的区别。 (3)掌握整数数控分频器的原理及设计方法。 (4)掌握半整数数控分频器的原理及设计方法

2. 背景知识

分频器在时序逻辑电路中应用广泛.数控分频 器的功能就是当在输入端给定不同的输入数据时 ,将对输入的时钟信号有不同的分频比。 整数分频器采用计数初值可并行预置的加法 (或者减法)计数器构成。时钟源与所需频率不 成整数倍关系,需要采用小数分频器进行分频。

பைடு நூலகம்

library ieee; --设计库的打开和程序包的允许使用 use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity pulse is --定义实体pulse port(clk : in std_logic; --初始时钟clk,即分频前时钟 d : in std_logic_vector(7 downto 0); --8位预置数d fout : out std_logic); --分频后输出信号 end; architecture one of pulse1 is --定义结构体 signal full : std_logic; --定义信号full begin p0:process(clk) --进程p0,以clk为敏感参数 variable cnt8 :std_logic_vector(7 downto 0); --定义内部变量cnt8 begin

半整数分频器的VHDL设计

© 1995-2005 Tsinghua Tongfang Optical Disc Co., Ltd. All rights reserved.

林海波 :半整数分频器的 VHDL 设计

61

在 VHDL 中 ,对某个数字系统的硬件抽象称为 实体 ( ENTITY) 。实体既可以单独存在 ,也可以作为 另一个更大实体的一部分 。实体声明定义了一个设 计模块的输入和输出端口 ,即模块对外的特性 。也 就是说 ,实体声明给出了设计模块与外部的接口 ,如 果是顶层模块的话 ,就给出了芯片外部引脚定义 。 一个设计可以包括多个实体 ,描述一个实体的对外 特性及其功能 ,是设计的主要任务 。然而 ,实体只描 述了模块对外的特性 ,并没有给出模块的具体实现 。 模块的具体实现或内部具体描述由结构体 (Archi2 tecture) 来完成 ,每个实体都有与其对应的结构体语 句 ,它既可以是一个算法 ,也可以是一个结构网表 。 具体一个实体的 VHDL 程序设计的基本语法结构 如下 :

除脉冲的时间 ,使输出为一个稳定的脉冲频率 ,而不

是一次 N 分频 ,一次 N - 1 分频 。 3. 2 电路组成

分频系数为 N - 0. 5 的分频器 ,其电路可由一 个异或门 、一个模 N 计数器和二分频器组成 。在实 现时 ,模 N 计数器可设计成带预置的计数器 ,这样 可以实现任意分频系数为 N - 0. 5 的分频器 。图 1 给出了通用半整数分频器电路组成 。

表 1 半整数分频器适配分析结果

选用器件

I/ O 延迟时间 使用引脚数 工作频率

/ ns

/ MHz

EPF10 K10LC84 - 4

14. 6 6/ 84 (7. 2 %) 52. 63MHz

一种占空比可调的新型整数半整数分频器设计

一种占空比可调的新型整数半整数分频器设计靳钊;乔丽萍;王聪华;王江安;郭晨【期刊名称】《电视技术》【年(卷),期】2013(37)13【摘要】提出了一种数字分频器,根据分频器外部输入的分频比和占空比控制参数,对源时钟实现任意偶数、奇数和半整数分频,占空比全范围可调,包含50%.电路由Verilog HDL编程实现,并通过Xilinx公司SPARTAN XC3S250E芯片硬件验证.测试表明该分频器结构简单功能稳定,资源占用不足1%,使用灵活,具有较强的可移植性.%A digital frequency divider is proposed in this paper.According to the input division ratio and duty-cycle,the frequency divider can divide the source clock,no matter the division ratio is even,odd or half-integer.The duty-cycle is controllable in the whole range,including 50%.The circuit,based on Verilog HDL,has passed the hardware verification with SPARTAN XC3S250E of Xilinx.The simulation results show that the divider is simple and stable,and it only occupies less than 1% of the FPGA resources.It is flexible and has strong transplantation.【总页数】4页(P63-66)【作者】靳钊;乔丽萍;王聪华;王江安;郭晨【作者单位】长安大学信息工程学院,陕西西安710064;西藏民族学院信息工程学院,陕西咸阳712082;西藏民族学院信息工程学院,陕西咸阳712082;长安大学信息工程学院,陕西西安710064;长安大学信息工程学院,陕西西安710064【正文语种】中文【中图分类】TN402【相关文献】1.基于FPGA的半整数及整数分频器的参数化设计 [J], 古良玲;杨永明;郭巧惠2.基于FPGA的等占空比任意整数分频器的设计 [J], 汪虹;李宏3.基于FPGA的等占空比的整数分频器设计 [J], 于彤;马社祥;郭琨4.基于VHDL占空比可控的整数半整数分频器 [J], 裴会新;裴东;王全洲;陶中幸5.基于CPLD的任意整数半整数分频器设计 [J], 许永贤因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

22.半整数分频器的设计

一、实验原理:

1小数分频的基本原理

设有一个5 MHz的时钟源,但电路中需要产生一个2 MHz的时钟信号,由于分频比为2.5,因此整数分频器将不能胜任。

采用可编程逻辑器件实现分频系数为2.5的分频器,可采用以下方法:设计一个模3的计数器,再设计一个扣除脉冲电路,加在模3计数器输出之后,每来两个脉冲就扣除一个脉冲(实际上是使被扣除的脉冲变成很窄的脉冲,可由异或门实现),就可以得到分频系数为2.5的小数分频器。

采用类似方法,可以设计分频系数为任意半整数的分频器。

小数分频的基本原理为脉冲吞吐计数法:设计两个不同分频比的整数分频器,通过控制单位时间内两种分频比出现的不同次数,从而获得所需的小数分频值。

例如设计一个分频系数为10.1的分频器,可以将分频器设计成9次10分频,1次11分频,这样总的分频值为 (9×10+1×11)/(9+1) =10.1

从这种实现方法的特点可以看出,由于分频器的分频值在不断改变,因此分频后得到的信号抖动较大。

当分频系数为N-0.5(N为整数)时,可控制扣除脉冲的时间,使输出为一个稳定的脉冲频率,而不是一次N分频,一次N-1分频。

1.2 电路组成

设需要设计一个分频系数为N-0.5的分频器,其电路可由一个模N计数器、一个二分频器和一个异或门组成,如图1所示。

在实现时,模N计数器可设计成带预置的计数器,这样就可以实现任意分频系数为N-0.5的分频器。

二、半整数分频器代码:

VHDL程序:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY deccount IS

PORT (

inclk: IN STD_LOGIC; --时钟源

preset: IN STD_LOGIC_VECTOR(3 DOWNTO 0); --预置分频值N

outclk1: OUT STD_LOGIC;

outclk2: BUFFER STD_LOGIC ); --输出时钟

END deccount;

ARCHITECTURE deccount_arch OF deccount IS

SIGNAL clk, divide2: STD_LOGIC;

SIGNAL count: STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

clk<=inclk XOR divide2; --inclk与divide2异或后作为模N计数器的时钟

outclk1<=inclk; --outclk1和inclk同步

PROCESS(clk)

BEGIN

IF(clk'event AND clk='1') THEN

IF(count="0000") THEN

count<=preset-1; --置整数分频值N

outclk2<='1';

ELSE

count<=count-1; --模N计数器减法计数

outclk2<='0';

END IF;

END IF;

END PROCESS;

PROCESS(outclk2)

BEGIN

IF(outclk2'event AND outclk2='1') THEN

divide2<=NOT divide2; --输出时钟二分频

END IF;

END PROCESS;

END deccount_arch;

三、程序仿真波形

如输入preset=6,即分频值为5.5

功能仿真波形如下

由于内置时钟频率为50MHZ,频率过大使波形不准确。

所以再输入信号前再连接一个分频器

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity clk is

port

( clk : in std_logic;

en : in std_logic;

qcnt : buffer std_logic_vector( 24 downto 0);

clkout :buffer std_logic

);

end clk;

architecture behave of clk is

begin

process (clk)

begin

if(en='1') then

if(clk'event and clk='1') then

if(qcnt="1011111010111100001000000") then

qcnt<="0000000000000000000000000";

else

qcnt<=qcnt+1;

end if;

end if;

end if;

clkout<=qcnt(8);

end process;

end behave;

引脚设置

CLK 62

Preset[0] 33

Preset[1] 34

Preset[2] 35

Preset[3] 36

Outclk1 27

Outclk2 28

可以通过开关量输入接口输入preset,设置N,设计0.5~15.5的分频器示波器连接27,可观察outclk1的波形,即输入波形

示波器连接28,可观察outclk2的波形,即分频后输出波形

四、实验箱结果

输入波形CLK如下

N=2时,分频为1.5,输出outclk2如下

N=3时,分频为2.5,输出outclk2如下

N=4,分频3.5。

输出outclk2如下

N=5,分频4.5,输出outclk2如下

N=6,分频5.5 输出outclk2如下

只需调节开关量输入接口,N可以从0取到16。