高速视频数模转换器ADV7127详细资料中文版

AD9713应用简介

摘要:AD9712B/AD9713B是一款12位的ECL/TTL兼容高速数模转换器,是针对DDS、信号重构、高质量图像信号处理等应用而专门设计的。

该芯片具有小的毛刺和快速建立时间,以及良好的动态性能和谐波抑制能力,因而在各种信号产生设备中有着大量的应用。

文章介绍了该芯片的结构和原理,同时给出了一个AD9713B在雷达视频信号处理中的应用实例。

关键词:DAC AD9712B/AD9713B 视频信号在为线性调频的雷达视频目标产生模拟信号的过程中,为了得到高质量的视频模拟信号,其前端通常采用数字信号处理或DSP+FPGA的结构来设计,然后经过数模转换和低通滤波以生成视频目标模拟信号。

而后端所选用的数模转换芯片的性能优劣对信号的质量有着极为重要的影响。

AD9712B/AD9713B 是AD9712/AD9713的替代产品,为12位高速数模转换器。

同AD9712/AD9713相比,该器件具有更好的静态性能和动态特性。

其中AD9712B与ECL兼容,更新速率可达10MSPS;而AD9713B则与TTL兼容,更新速率可达80MSPS。

由于该D/A转换器是针对DDS、波形重构和高质量图像信号处理等应用而设计的,因此,这两款芯片在动态特性方面表现特别突出,并且具有优良的谐波抑制能力。

本文选用AD9713B来输出雷达视频目标模拟信号。

1 AD9712B/AD9713B的主要特点AD9712B的数据输入口D1~D12和使能口LATCH ENABLE与ECL兼容,内部ECL参考节点也与10K ECL器件相匹配。

而在AD9713B中,每个输入口均加进了TTL转换单元。

除这点以外,AD9712B和AD9713B是完全相同。

AD9712B/AD9713B的主要特性如下:●具有100MSPS的更新速率;●与ECL/TTL兼容;●无杂散动态范围SFDR为70dBc(1MHz);●毛刺电压低至28Pv-s;●建立时间快(27ns);●低功耗:725mW;●1/2LSB DNL (B Grade);●具有40 MHz乘积带宽。

gxconfiguratordpv712中文使用手册

gxconfiguratordpv712中文使用手册

引言

这本手册旨在为您提供关于gxconfiguratordpv712的全面介绍和使用指南。

通过阅读本手册,您将能够了解如何安装、配置和使用gxconfiguratordpv712,从而充分利用其强大的功能来提高您的工作效率。

一、产品概述

gxconfiguratordpv712是一款功能强大的配置工具,专为满足各种配置需求而设计。

它支持多种配置项,包括网络设置、设备参数、安全设置等,使您能够轻松地管理和优化您的设备。

二、安装与配置

在本节中,我们将详细介绍如何安装和配置gxconfiguratordpv712。

1. 安装步骤

(1) 下载并安装gxconfiguratordpv712软件包;

(2) 运行安装程序,按照屏幕提示完成安装过程;

(3) 安装完成后,重启计算机。

2. 配置步骤

(1) 打开gxconfiguratordpv712应用程序;

(2) 选择“设置”菜单中的“网络设置”;

(3) 根据您的需求配置网络参数,如IP地址、子网掩码等;

(4) 配置其他所需的参数,如设备名称、密码等;

(5) 点击“保存”按钮以保存配置。

三、使用指南

在本节中,我们将详细介绍如何使用gxconfiguratordpv712进行设备配置和管理。

1. 网络配置

(1) 打开gxconfiguratordpv712应用程序;

(2) 选择“网络设置”选项卡;

(3) 根据您的需求配置网络参数,如IP地址、子网掩码等;

(4) 点击“应用”按钮以应用配置。

基于ADSP_BF533的多媒体通信终端设计与实现

收稿日期:2004-08-01;修订日期:2004-10-28 作者简介:陶猛(1979-),男,安徽泗县人,硕士研究生,主要研究方向:图像处理、多媒体通信; 黄小红(1979-),女,江西南丰人,硕士研究生,主要研究方向:图像处理、多媒体通信; 刘峰(1964-),男,浙江温州人,副教授,博士,主要研究方向:图像处理、多媒体通信.文章编号:1001-9081(2005)03-0717-03基于ADSP 2BF533的多媒体通信终端设计与实现陶 猛,黄小红,刘 峰(南京邮电学院信息工程系,江苏南京210003)(taomeng1979@hot m ail .com;taomeng79@ )摘 要:采用ADSP 2BF533DSP 处理器设计并实现了基于I P 网路的多媒体通信终端系统。

终端的管理采用μCOS 2II 实时嵌入式操作系统。

在分析μCOS 2II 操作系统特点的基础上,把Lw I P 协议栈移植到μCOS 2II 上实现了网络接口。

试验结果表明,该系统在局域网中多媒体信息的编码、传输是实时的。

关键词:I P 网络;多媒体通信终端;DSP;μCOS 2II ;Lw I P (L ightW eight I nternet Pr ot ocol )中图分类号:TP316.89 文献标识码:AD esi gn and rea li za ti on of m ulti m ed i a term i n a l ba sed on AD SP 2BF 533T AO Meng,HUANG Xiao 2hong,L I U Feng(Infor m ation Engineering D epart m ent ,N anjing U niversity of Posts and Teleco mm unications ,N anjing J iangsu 210003,China )Abstract:A multi m edia communicati on ter m inal based on ADSP 2BF533DSP p r ocess or and used in I P net w ork was designed and i m p le mented .μCOS 2II e mbedded operati on syste m was used in the system,with the trans p lantati on of Lw I P .The experi m ents show that by the multi m edia communicait on ter m inal,the coding and trans portati on of multi m edia inf or mati on can be realized in real ti m e in LAN.Key words:I P net w ork;multi m edia communicati on ter m inal;DSP;μC OS 2II ;Lw I P (L ightW eight I nternet Pr ot ocol )0 引言嵌入式系统通常是指被嵌入到各种产品或工程应用中的,以微处理器或微控制器为核心的软硬件系统。

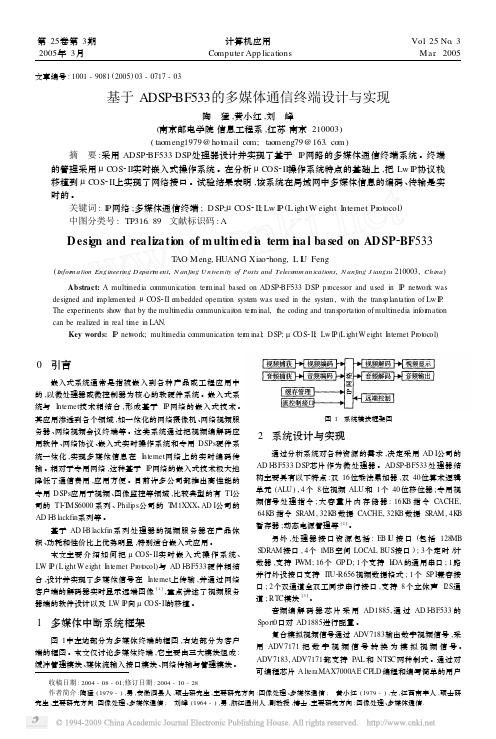

ADV7170中文资料

CGMS & WSS INSERTION BLOCK

TELETEXT INSERTION

BLOCK

8

4:2:2 TO

4:4:4 INTER-

8

POLATOR

8

Y8

YCrCb TO U 8 YUV

MATRIX V8

ADD 9 SYNC

8

ADD BURST 8

INTER- 9 POLATOR

8

INTERPOLATOR 8

Multistandard Video Output Support:

Macrovision AntiTaping Rev 7.01 (ADV7170 Only)**

Composite (CVBS)

Closed Captioning Support

Component S-Video (Y/C)

Teletext Insertion Port (PAL-WST)

Individual ON/OFF Control of Each DAC

WSS (Wide Screen Signalling)

CCIR and Square Pixel Operation

Simultaneous Y, U, V, C Output Format

Integrated Subcarrier Locking to External Video Source

NTSC-M, PAL-M/N, PAL-B/D/G/H/I, PAL-60

Color Signal Control/Burst Signal Control

Single 27 MHz Clock Required (؋2 Oversampling)

GM7123 3通道高清视频编码电路 数据手册说明书

GM71233通道高清视频编码电路数据手册成都国腾电子技术股份有限公司设计上海福跃电子科技有限公司提供销售+86-21-58998693/58994470数据手册3通道高清视频编码电路GM71233 通道高清视频编码电路GM7123版本记录:1.0 当前版本时间:2010年7月新旧版本改动比较:旧版文档页数当前版本文档页数主题(和旧版本相比的主要变化)技术销售服务热线:+86-21-58998693/58994470在使用过程中所遇到问题或申请免费样片及索取相关解决方案均可致电+86-21-58998693/58994470-15或发Email至:***************您会得到工程师快捷、准确的回答.1概述GM7123是一款频率330MHz的3通道10位高速视频DAC芯片,兼容RS-343A/RS-170标准差分输出,输出电流范围是2mA~26mA。

输入兼容TTL电平,内部基准1.23V,单电源3.3V供电,采用LQFP48封装。

该芯片可应用于:数字视频系统(1600×1200@100Hz);高分辨率彩色图像;数字射频调制;图像处理;仪器和视频信号重建等。

2特征GM7123自带3个分离的10位数据输入端口,有视频控制信号SYNC和BLANK分别控制同步和消隐。

芯片带有省电模式,采用CMOS工艺制造。

a)最高330MSPS转换速率b)3个10位DACc)输入兼容TTL电平d)DAC输出电流范围2mA~26mAe)集成带隙基准电压源f)LQFP48封装3封装及引脚功能说明产品采用48引线的四边引线扁平外壳封装,实体尺寸7mm×7mm。

图1 GM7123引脚排布图该芯片的各引脚功能描述见表1:表1.芯片引脚功能说明引脚号引脚名方向说明1 G0 输入绿色通道输入数据2 G1 输入绿色通道输入数据3 G2 输入绿色通道输入数据4 G3 输入绿色通道输入数据5 G4 输入绿色通道输入数据6 G5 输入绿色通道输入数据48 R9 输入红色通道输入数据4 功能描述GM7123包含3个10位DAC ,带有3个输入通道,每个通道都有10位数据寄存器。

基于ADV7125的嵌入式系统VGA接口

基于ADV7125的嵌入式系统VGA接口

目前VGA接口是计算机系统以及智能仪器中重要的标准输出接口,但是大部分硬件系统选择LCD终端输出。

很多显示设备,如常见的CRT或LCD 显示器一般都采用统一的15针VGA显示接口。

如需要外接这些设备,则需要把LCD输出信号的接口转换为VGA接口。

本设计是在三星公司芯片

S3C2440平台下,利用最高频率可以达到330 MHz的ADV7125芯片,设计了能够把输出的LCD信号转换为VGA信号的转换电路。

该设计方案具有电路简单、价格低廉、输出图像清晰稳定等特点。

1 ADV7125芯片介绍

ADV7125是一款单芯片、3通道、高速度的数模转换器。

内置3个高速、8位、带互补输出的视频DAC、1个标准TTL输入接口,以及1个高阻抗、模拟输出电流源。

它具有3个独立的8位宽输入端口。

只需1个+5

V/+3.3V单电源和时钟便能工作。

ADV7125还具有其他视频控制信号:

复合同步信号控制端、消隐信号控制端,以及省电模式控制端。

它能够与各种高分辨率彩色图形系统兼容。

ADV7125功能框图如图1所示。

AD 精选高速数模转换器中文

A D76816-B i t高速数模转换器特性刷新率:30MSPS分辨率:16-Bit线性度:1/2LSBDNL@14Bits1LSBINL@14Bits最快建立时间:满量程25ns,精度0.025%SFDR@1MHz输出:86dBcTHD@1MHz输出:71dBc低干扰脉冲:35pV-s功率消耗:465mW片上基准源:2.5V边沿触发锁存器乘法参考能力应用任意波形发生器通信波形重建矢量图形显示产品描述AD768是16-Bit高速数模转换器(DAC)提供优良的交流和直流性能。

AD768是ADI公司的先进双极CMOS制造(abcmos)处理,结合双极晶体管的速度,激光微调薄膜电阻的精度和有效CMOS逻辑。

一个分段电流源架构与专有开关技术相结合,以减少毛刺能量来获得最大化的动态精度。

边沿触发输入锁存器和一个温度补偿的带隙基准源已集成,提供一个完整的单片DAC解决方案。

AD768是电流输出DAC标称满量程输出电流20mA和一个1K 的输出阻抗。

差分电流输出提供支持单端或差分应用。

电流输出可以绑接输出电阻提供电压输出,或连接到高速放大器的求和点提供一个缓冲电压输出。

同时,差分输出可以连接到变压器或差分放大器。

片上基准源和控制放大器配置为最大的准确性和灵活性。

AD768可以通过芯片上的基准源或由一个外部基准电压基于一个外部电阻的选择驱动。

外部电容器允许用户优化变换参考带宽和噪声性能。

AD768采用±5V电源运行,典型的消耗功率465毫瓦。

该芯片采用28引脚SOIC封装,规定工作在工业温度范围。

产品亮点1、低干扰和快速建立时间提供杰出的波形重建或数字动态性能合成的要求,包括通信。

2、AD768优良的直流精度使得它适合高速A/D转换应用。

3、温度补偿,包括片上2.5V带隙基准。

4、允许的参考同一个外部电阻器使用电流输入。

外部基准也可以使用。

5、AD768电流输出可单独使用或差分,无论是负载电阻,外部运算放大器求和点或变压器。

多媒体接收器DVM179用户手册说明书

DVM179 INSTALLATION/OWNER’S MANUALMultimedia Receiver with Bluetooth®featuring a 7" Touch Screen DisplayCopyright NotesThe Bluetooth® word mark and logos are owned by the Bluetooth SIG, Inc. SD Logo is a trademark of SD-3C, LLC.Other trademarks and trade names are those of their respective owners.DVM179OPERATIONSafety InformationPlease read all instructions carefully before attempting to install or operate.Due to its technical nature, it is highly recommended that your DUAL DVM179 is installed by a professional installer or an authorized dealer. This product is only for use in vehicles with 12VDC negative ground only.To prevent damage or injury:• Make sure to ground the unit securely to the vehicle chassis ground.• Do not remove the top or bottom covers of the unit.• Do not install the unit in a spot exposed to direct sunlight or excessive heat or the possibility of water splashing.• Do not subject the unit to excessive shock.• When replacing a fuse, only use a new one with the prescribed rating. Using a fuse with the wrong rating may cause the unit to malfunction.• To prevent short circuits when replacing a fuse, disconnect the wiring harness first.• Use only the provided hardware and wire harness.• You cannot view video while the vehicle is moving. Find a safe place to park and engage the parking brake.• If you experience problems during installation, consult your nearest DUAL dealer.• If the unit malfunctions, reset the unit as described on page 10 first. If the problem still persists, consult your nearest DUAL dealer or call tech assistance @ 1-866-382-5476.• To clean the monitor, wipe only with a dry silicone cloth or soft cloth. Do not use a stiff cloth, or volatile solvents such as paint thinner and alcohol. They can scratch the surface of the panel and/or remove the printing.• When the temperature of the unit falls (as in winter), the liquid crystal inside the screen will become darker than usual. Normal brightness will return after using the monitor for a while.• When extending the ignition, battery or ground cables, make sure to use automotive-grade cables or other cables with an area of 0.75mm (AWG 18) or more to prevent voltage drops.• Do not touch the liquid crystal fluid if the LCD is damaged or broken. The liquid crystal fluid may be hazardousto your health or fatal. If the liquid crystal fluid from the LCD contacts your body or clothing, wash it off with soap immediately.FCC ComplianceThis device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions:(1) this device may not cause harmful interference, and(2) this device must accept any interference received, including interference that may cause undesired operation. Warning: Changes or modifications to this unit not expressly approved by the party responsible for compliance could void the user’s authority to operate the equipment.Note: This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:• Reorient or relocate the receiving antenna.• Increase the separation between the equipment and receiver.• Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.• Consult the dealer or an experienced radio/TV technician for help.23DVM179OPERATIONBefore You Start • D isconnect negative battery terminal. Consult a qualified technician for instructions.• A void installing the unit where it would be subject to high temperatures, such as from direct sunlight, or where it would be subject to dust, dirt or excessive vibration.Getting Started• Insert the supplied keys into the slots as shown, and slide the unit out of the mounting sleeve. • I nstall mounting sleeve into opening, bending tabs to secure.• C onnect wiring harness as shown on page 4. Consult a qualified technician if you are unsure.• C ertain vehicles may require an installation kit and/or wiring harness adapter (sold separately).• Reconnect negative battery terminal, and test for correct operation.• Snap trim ring into place (if required).Preparation4DVM179OPERATIONWiring Diagram - Inputs/OutputsNote:When replacing a fuse, make sure to use the correct type and amperage. Using an incorrect fuse could cause damage. The unit uses (1) 10 amp ATC mini style fuse located on the power connector. Wiring Notes:Subwoofer outputThe Subwoofer preamp audio output (black jacket with green RCA) is active in all audio modes.Rear camera inputA rear view camera (not included) can be used with the Camerainput.DVM179 OPERATIONControl Locations1. Power / Source Mode2. Play / Pause3. Rotary Volume Up/Down4. Mute - Short Press Rotary5. Tune/Track Up / Answer Call6. Tune/Track Down / End Call7. BT Microphone8. LCD Display9. Open TFT - Press to open/close 10. 3.5mm AUX IN11. USB Media Port / Charging Port 12. microSD Media Port 13. Reset346138571211910BEHIND DOOR1. Power2. Play/Pause / Ok3. Seek Up / Next Track4. Volume Down 7. Dial 3 / Song Repeat 10. Dial 811. Dial 9 #Remove Battery Shipping Protector126DVM179 OPERATION General OperationPower On/OffModeVolumeMuteOpen Auxiliary InputUSB InputmicroSD CardMain MenuReset Momentarily press to turn the unit on. Press and hold to turn the unit off.Press to step through all available input modes: Radio, SD Card, USB, Bluetooth Phone, Bluetooth Music, Auxiliary Input, Rear Camera and Settings. Modes of operation are indicated on the display and/or the monitor. Optional USB device and SD card must be connected/ inserted to appear in the mode selection string.Rotate the volume knob to increase or decrease the volume level. Momentarily press the volume knob to silence the audio. Momentarily press the volume knob again to return to the previously selected volume. Rotating the volume knob while the volume is muted will also cancel the mute function.Press OPEN to open or close the LCD display screen.Connect external audio/video devices to the 3.5mm auxiliary input on the front panel.Insert a USB device to play MP3 audio files or view view XviD or MP4 video files or JPG photos.Insert an microSD card into the microSD slot to play MP3 audio files or view XviD or MP4 video files or JPG photos.Press the house icon in the top left corner to access the Main Menu screen.To resolve abnormal operation or if the unit is inoperable, use the tip of a pen to press the RESET button, which is located behind the door marked "USB". The unit will reset the main processor to the default settings.7DVM179OPERATIONGeneral OperationFrom the Main Menu, press the gear icon to access the Setup menu andadjust the following: General, Clock, Audio, Bluetooth, Display and About.General:• System Language - Select English or Spanish.• Tuner Region - Select between America, Europe or Latin America.• Beep - Turn the audible beep on or off.• Rear Camera Delay - Select 1 second, 2 seconds, 3 seconds of Off.• Reverse Trigger - Enable or disable this feature.Clock:• Mode - Select 12 Hour or 24 Hour clock settings.• Hour - Adjust the hours for time setting.• Minute - Adjust the minutes for time setting.• AM/PM - Adjust the AM/PM setting.Audio:• Camera Audio - Turn audio from the rear camera on or off.• Audio Level - Select preset audio levels for the following modes:Tuner, USB, SD Card and Handsfree.Bluetooth:• Bluetooth - Turn Bluetooth signal on or off.• Auto Connect - Turn auto connect feature on or off.• Auto Answer - Turn auto answer feature on or off.• PIN - Displays the Bluetooth PIN code.• Name - Displays the Bluetooth device name.Display:• Illumination Trigger - Turn illumination trigger on or off.• Brightness Day - Adjust 1-10.• Gamma Day - Adjust -4 to 4.• Panel Angle - Adjust the angle of the LED panel (1-4).• LED RGB - Adjust color of LED lights (or set to automatic).• Wallpaper - Select a wallpaper for the LED display.About:• Screen Calibration - Press to calibrate the touch screen.• Version - Press to display the version number.• System Reset - Press to restore unit to factory settings.• EULA - Need more infoSetup MenuDVM179 OPERATIONGeneral Operation1. Adjust the volume level for the current source.2. Displays the EQ Settings for the current source.3. Turns the EQ function on or off.4. Turns the Loudness function on or off.5. Press to reset to the default EQ settings.6. Press to return to the source screen.7. Select a preset EQ setting, or select User for custom settings.8. Press to display and adjust Balance / Fader screen.Adjust the Balance / Fader screen to select Balance, Fader and Subwoofer settings. These controls do not have source tone 1. Adjust the volume level of the unit.2. Adjust the Fader and Balance settings to distribute audio as desired front to back and left to right.3. Press to reset Balance and Fader to default settings.Turn the subwoofer on or off.Press to return to the source screen.6. Return to EQ control screens3465345DVM179OPERATIONAM/FM Tuner OperationAM/FM Tuner Operation14USB/microSD Card OperationUSB/SD Card Operation1615The following types of files are not compatible:• MP3 PRO format, MP3 playlists • RMP format • WAV format • WMV format• AAC, protected AAC, M4A formatMP3 playback sequence begins in the root folder of the USB flash drive or microSD card. Any folders that do not include MP3/JPG files are skipped. ISO9660 standards:• Maximum nested folder depth is 8 (including the root folder).• Valid characters for folder/file names are letters A-Z (all caps), numbers 0-9, and “_” (underscore). Some characters may not be displayed correctly, depending on the character type.Some files may not play, depending on sampling rates and bit rates. For best results, use the following settings when ripping MP3 files: 128kbps or higher constant bit rate; 44.1kHz or higher sampling frequencyMedia CompatibilityPlayback OrderCompatible Recording FormatsNotesNotes:• For USB mode, it is not possible to view JPG files on the in-dash monitor while the vehicle is moving. This is a safety feature to prevent driver distraction.• The JPG image viewer function will only operate when vehicle is in park and the parking brake is engaged.• Due to ongoing technological advancement, some USB flash drives and/or microSD cards may be incompatible with this unit.Bluetooth Operation1Bluetooth OperationFront 3.5mm Aux InputConnect an optional audio source into the 3.5mm (front panel) input. Select auxiliary input from the Main Menu to listen to audio.Adjust volume on the external audio source as needed (if connected to the headphone output of the device).Auxiliary InputFront/Rear Cameras - (Optional)Connect an optional rear camera to the Rear Camera inputs (Yellow RCA connector for video and Black RCA connector for audio). Refer to the wiring diagram for details.Manual selection - Touch the REAR CAMERA icon from the Main Menu or from any operational mode (when enabled) to select camera mode. Touch the top left area on the screen to exit camera mode.Note: The manual mode is for dedicated cameras that are ALWAYS on while driving, it is not meant for cameras that are connected to the vehicle's reverse light.The unit will automatically select camera mode when connected to the reverse lamp circuitry.Note: The external video output is not active when using the rear camera input.Connect an optional front camera to the Front Camera inputs (Yellow RCAconnector for video; there is no audio connection for a front camera. Refer to the wiring diagram for details.Using Rear CameraAuto SelectionUsing Front CameraSpecificationsFM TunerAM TunerFront USB microSD MonitorGeneralTuning range: 87.5MHz-107.9MHz Usable sensitivity: 10dBf50dB quieting sensitivity: 20dBf Stereo separation @ 1kHz: 38dB Frequency response: 30Hz-13kHz Tuning range: 530kHz-1710kHz Usable sensitivity: 24uVFrequency response: 30Hz-2.3kHz Compatibility: High Speed USB 2.0USB Class: Mass storage classCompatibility: microSD memory card & microSDHC memory card Panel size: 7” diagonal measurementView angle (up/down/left/right): 50/70/70/70Resolution: 800 (H) x 480 (V)Brightness (cd/m 2): 250Contrast ratio: 500:1Pixels: 1,152,000Speaker output impedance: 4 ohms Line output voltage: 4 volt RMS Line output impedance: 200 ohmsChassis dimensions: 7" x 7" x 2" (W x D x H)Design and specifications subject to change without notice.Limited One Year WarrantyThis warranty gives you specific legal rights. You may also have other rights which vary from state to state. Namsung America Inc. warrants this product to the original purchaser to be free from defects in material and workmanship for a period of one year from the date of the original purchase.Namsung America Inc. agrees, at our option, during the warranty period,to repair any defect in material or workmanship or to furnish an equal new, renewed or comparable product (whichever is deemed necessary) in exchange without charges, subject to verification of the defect or malfunction and proof of the date of purchase. Subsequent replacement products are warranted for the balance of the original warranty period. Who is covered? This warranty is extended to the original retail purchaser for products purchased from an authorized Dual dealer and used in the U.S.A.What is covered? This warranty covers all defects in material and workmanship in this product. The following are not covered: software, installation/removal costs, damage resulting from accident, misuse, abuse, neglect, product modification, improper installation, incorrect line voltage, unauthorized repair or failureto follow instructions supplied with the product, or damage occurring during return shipment of the product. Specific license conditions and copyright notices for the software can be found via www. .What to do?1.Before you call for service, check the troubleshooting guide in your owner’s manual. A slight adjustment of any custom controls may save you a service call.2.If you require service during the warranty period, you must carefully pack the product (preferably in the original package) and ship it by prepaid transportation with a copy of the original receipt from the retailer to an authorized service center.3.Please describe your problem in writing and include your name, a return UPS shipping address (P.O. Box not acceptable), and a daytime phone number with your shipment.4.For more information and for the location of the nearest authorized service center please contact us by one of the following methods:•Call: 866-382-5476•E-mail: cs@Exclusion of Certain Damages: This warranty is exclusive and in lieu of any and all other warranties, expressed or implied, including without limitation the implied warranties of merchantability and fitness for a particular purpose and any obligation, liability, right, claim or remedy in contract or tort, whether or not arising from the company’s negligence, actualor imputed. No person or representative is authorized to assume for the company any other liability in connection with the sale of this product. In no event shall the company be liable for indirect, incidental or consequential damages.TroubleshootingDVM179OPERATIONNotes20Dual Electronics Corp.Toll Free: 888-921-4088©2019 Namsung America Inc. All rights reserved.The Bluetooth® word mark and logos are owned by the Bluetooth SIG, Inc. Other trademarks and trade names are those of their respective owners.NSA0719-V01。

oppo A127播放器 说明书

干扰 所有的无线设备都可能受到干扰,从而 影响性能。

在爆破地点附近应关机 请遵守任何相关的限制规定。请勿在进 行爆破操作的地方使用本设备。

合理的使用

仅在正常位置故用手触摸天线区域。

OPPO A127支持多种音频格式的专用音乐播放器,让您轻松玩转音乐;200万像素数码拍照功能,助您将每个美好瞬间变 成永恒;图片处理随时随地;QQ、QQ游戏、飞信让运动、旅途中的您能随时随地和好友聊天或其它娱乐,尽享沟通乐趣; 还有Java游戏、蓝牙2.1+EDR、变换主题更让您乐不停……

使用产品前请仔细阅读本使用说明书。 网址

本文档的内容按产品制造时的状况提供。除非适用的法律另有规定,否则不对文档的准确性、可靠性和内容作出任何类型 的明确或默许的保证。

1 请务必为您产品中存储的所有重要内容和数据制作备份或保存书面记录,因为该内容和数据在产品的使用、维修、电池更换

或 其 他 原 因 都 有 可 能 造 成 资 料 丢 失 或 损 坏 。在 适 用 法 律 允 许 的 最 大 限 度 内 ,在任何情 况 下,O P P O或 其 任 何 许 可 证 持 有 方 均 不对任何数据或收入方面的损失,或任何特殊、偶然、附带或间接损失承担责任,无论该损失由何种原因引起。

本产品经过杜比实验室的许可而制造。杜比和双D符号是杜比实验室的注册商标。

产品的供货情况和相关的应用软件和配件,可能因地区而异。有关详情,请向OPPO指定的经销商查询。

本产品可能包含受中国和其他国家或地区的出口法律和法规控制的商品、技术或软件,严禁任何违反法律的转移行为。

安全事项

请阅读以下简明的规则,如未遵守这些规则可能会导致危险 或触犯法律。本说明书提供了有关安全事项的更详细信息。

Philips DVD-Video Player DVD 712用户指南说明书

100 dB

• Dynamic Range (1kHz) 97 dB

• Crosstalk (1kHz)

110 dB

• Distortion/noise (1kHz) 88 dB

• MPEG MP3 MPEG Audio L3

Connection

• Scart • S-Video output • Video output • Audio L+R Output • Audio Centre • Audio Subwoofer • Digital Output

Power supply

• Power inlet • Power usage • Power usage standby

230 V, 50 Hz 20 watt less than 5 watt

Cabinet

• Dimension

• Weight

435 x 92 x 320 mm (w x h x d) Approx. 4 kg

multi-channel sound

• 3D sound for virtual 5.1 channel sound on 2

speakers

General functionality

• Stop/ play/ pause • Fast forward/ backward • Time search • Step forward/ backward • Slow motion • Title / chapter/ track select • Skip next / skip previous • Repeat (Chapter/ title / all) or (Track / all) • A-B repeat • Shuffle • Scan • New enhanced user graphical interface • Perfect still with digital multi-tap filter • Zoom (x1.33, x2, x4) with picture enhancement • Screen saver (dim 75% after 15 min.) • Cinemalink interconnection for plug & play • 3D sound • Virtual Jog Shuttle • Audio and video bit rate indicator • Smart Picture

AD713

REV.BInformation furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.aAD713One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.Tel: 617/329-4700Fax: 617/326-8703FEATURESEnhanced Replacement for LF347 and TL084AC PERFORMANCE1 s Settling to 0.01% for 10 V Step 20 V/s Slew Rate0.0003% Total Harmonic Distortion (THD)4 MHz Unity Gain BandwidthDC PERFORMANCE0.5 mV max Offset Voltage (AD713K)20 V/°C max Drift (AD713K)200 V/mV min Open Loop Gain (AD713K)2 V p-p typ Noise, 0.1 Hz to 10 Hz True 14-Bit AccuracySingle Version: AD711, Dual Version: AD712Available in 16-Pin SOIC, 14-Pin Plastic DIP and Hermetic Cerdip Packages and in Chip Form MIL-STD-883B Processing Available Standard Military Drawing Available APPLICATIONS Active FiltersQuad Output Buffers for 12- and 14-Bit DACs Input Buffers for Precision ADCsPhoto Diode Preamplifier Applications Quad Precision, Low Cost,High Speed, BiFET Op AmpPRODUCT DESCRIPTIONThe AD713 is a quad operational amplifier, consisting of four AD711 BiFET op amps. These precision monolithic op amps offer excellent dc characteristics plus rapid settling times, high slew rates, and ample bandwidths. In addition, the AD713 pro-vides the close matching ac and dc characteristics inherent to amplifiers sharing the same monolithic die.The single-pole response of the AD713 provides fast settling:l µs to 0.01%. This feature, combined with its high dc precision,makes it suitable for use as a buffer amplifier for 12- or 14-bit DACs and ADCs. It is also an excellent choice for use in active filters in 12-, 14- and 16-bit data acquisition systems. Further-more, the AD713’s low total harmonic distortion (THD) level of 0.0003% and very close matching ac characteristics make it an ideal amplifier for many demanding audio applications.The AD713 is internally compensated for stable operation at unity gain and is available in seven performance grades. The AD713J and AD713K are rated over the commercial tempera-ture range of 0°C to +70°C. The AD713A and AD713B are rated over the industrial temperature of –40°C to +85°C. The AD713S and AD713T are rated over the military temperature range of –55°C to +125°C and are available processed to MIL-STD-883B, Rev. C.CONNECTION DIAGRAMSPlastic (N) and Cerdip (Q) PackagesSOIC (R) PackageOUTPUT OUTPUT–IN +IN OUTPUT–IN +IN +V S OUTPUT –IN –INOUTPUTS OUTPUTOUTPUT–IN –IN +IN +IN +IN –IN NCNC = NO CONNECTNCOUTPUT–IN +IN +V S –V S The AD713 is offered in a 16-pin SOIC, 14-pin plastic DIP and hermetic cerdip package, or in chip form.PRODUCT HIGHLIGHTS1. The AD713 is a high speed BiFET op amp that offers excel-lent performance at competitive prices. It upgrades the per-formance of circuits using op amps such as the TL074/TL084, LT1058, LF347 and OPA404.2. Slew rate is 100% tested for a guaranteed minimum of 16 V/µs (J, A and S Grades).3. The combination of Analog Devices’ advanced processing technology, laser wafer drift trimming and well-matched ion-implanted JFETs provides outstanding dc precision. In-put offset voltage, input bias current and input offset current are specified in the warmed-up condition and are 100%tested.4. Very close matching of ac characteristics between the four amplifiers makes the AD713 ideal for high quality active filter applications.AD713–SPECIFICATIONS(V S = ؎15 V @ T A = +25؇C unless otherwise noted)AD713J/A/S AD713K/B/TParameter Conditions Min Typ Max Min Typ Max Units INPUT OFFSET VOLTAGE1Initial Offset0.3 1.50.20.5mV Offset T MIN to T MAX0.52/2/20.40.7/0.7/1.0mV vs. Temp5520/20/15µV/°C vs. Supply789584100dB vs. Supply T MIN to T MAX76/76/769584100dB Long-Term Stability1515µV/Month INPUT BIAS CURRENT2V CM = 0 V401504075pAV CM = 0 V @ T MAX 3.4/9.6/154 1.7/4.8/77nAV CM = ±10 V5520055120pA INPUT OFFSET CURRENT V CM = 0 V10751035pAV CM = 0 V @ T MAX 1.7/4.8/770.8/2.2/36nA MATCHING CHARACTERISTICSInput Offset Voltage0.5 1.80.40.8mV Input Offset Voltage T MIN to T MAX0.7 2.3/2.3/2.30.6 1.0/1.0/1.3mV Input Offset Voltage Drift8625µV/°C Input Bias Current101001035pA Crosstalk f = 1 kHz–130–130dBf = 100 kHz–95–95dB FREQUENCY RESPONSESmall Signal Bandwidth Unity Gain 3.0 4.0 3.4 4.0MHz Full Power Response V O = 20 V p-p200200kHz Slew Rate Unity Gain16201820V/µs Settling Time to 0.01% 1.0 1.2 1.0 1.2µs Total Harmonic Distortion f = 1 kHz; R L≥ 2 kΩ;0.00030.0003%V O = 3 V rmsINPUT IMPEDANCEDifferential3×1012ʈ5.53×1012ʈ5.5ΩʈpF Common Mode3×1012ʈ5.53×1012ʈ5.5ΩʈpF INPUT VOLTAGE RANGEDifferential3±20±20V Common-Mode Voltage4+14.5, –11.5+14.5, –11.5VT MIN to T MAX–11+13–11+13V Common Mode V CM = ±10 V78888494dB Rejection Ratio T MIN to T MAX76/76/76848290dBV CM = ±11 V72847890dBT MIN to T MAX70/70/70807484dB INPUT VOLTAGE NOISE0.1 Hz to 10 Hz22µV p-pf = 10 Hz4545nV/√Hzf = 100 Hz2222nV/√Hzf = 1 kHz1818nV/√Hzf = 10 kHz1616nV/√Hz INPUT CURRENT NOISE f = 1 kHz0.010.01pA/√Hz OPEN-LOOP GAIN V O = ±10 V; R L≥ 2 kΩ150400200400V/mVT MIN to T MAX100/100/100100V/mV OUTPUT CHARACTERISTICSVoltage R L≥ 2 kΩ+13, –12.5+13.9, –13.3+13, –12.5+13.9, –13.3VT MIN to T MAX±12/±12/؎12+13.8, –13.1؎12+13.8, –13.1V Current Short Circuit2525mA POWER SUPPLYRated Performance±15±15V Operating Range؎4.5؎18؎4.5؎18V Quiescent Current10.013.510.012.0mA TRANSISTOR COUNT# of Transistors120120NOTES1Input Offset Voltage specifications are guaranteed after 5 minutes of operation at TA = +25°C.2Bias Current specifications are guaranteed maximum at either input after 5 minutes of operation at TA = +25°C. For higher temperatures, the current doubles every 10°C.3Defined as voltage between inputs, such that neither exceeds ±10 V from ground.4Typically exceeding –14.1 V negative common-mode voltage on either input results in an output phase reversal.Specifications subject to change without notice.REV. B–2–AD713REV. B–3–ORDERING GUIDE Temperature PackagePackageModel Range Description Option*AD713AQ–40°C to +85°C14-Pin Ceramic DIP Q-14AD713BQ–40°C to +85°C14-Pin Ceramic DIP Q-14AD713JCHIPS0°C to +70°C Bare DieAD713JN0°C to +70°C14-Pin Plastic DIP N-14AD713JR-160°C to +70°C16-Pin Plastic SOIC R-16AD713JR-16-REEL0°C to +70°C16-Pin Plastic SOIC R-16AD713JR-16-REEL70°C to +70°C16-Pin Plastic SOIC R-16AD713KN0°C to +70°C14-Pin Plastic DIP N-14AD713SCHIPS–55°C to +125°C Bare DieAD713SQ–55°C to +125°C14-Pin Ceramic DIP Q-14AD713SQ/883B–55°C to +125°C14-Pin Ceramic DIP Q-14AD713TQ–55°C to +125°C14-Pin Ceramic DIP Q-14AD713TQ/883B–55°C to +125°C14-Pin Ceramic DIP Q-145962-9063301MCA–55°C to +125°C14-Pin Ceramic DIP Q-145962-9063302MCA–55°C to +125°C14-Pin Ceramic DIP Q-14*N = Plastic DIP; Q = Cerdip; R = Small Outline IC (SOIC).ABSOLUTE MAXIMUM RATINGS1, 2Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .±18 VInternal Power Dissipation2Input Voltage3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .±18 VOutput Short Circuit Duration(For One Amplifier) . . . . . . . . . . . . . . . . . . . . . . . .IndefiniteDifferential Input Voltage . . . . . . . . . . . . . . . . . .+V S and –V SStorage Temperature Range (Q) . . . . . . . . . .–65°C to +150°CStorage Temperature Range (N, R) . . . . . . . .–65°C to +125°COperating Temperature RangeAD713J/K . . . . . . . . . . . . . . . . . . . . . . . . . . . .0°C to +70°CAD713A/B . . . . . . . . . . . . . . . . . . . . . . . . . .–40°C to +85°CAD713S/T . . . . . . . . . . . . . . . . . . . . . . . . .–55°C to +125°CLead Temperature Range (Soldering 60 sec) . . . . . . . .+300°CNOTES1Stresses above those listed under “Absolute Maximum Ratings” may cause perma-nent damage to the device. This is a stress rating only and functional operation ofthe device at these or any other conditions above those indicated in the operationalsection of this specification is not implied. Exposure to absolute maximum ratingconditions for extended periods may affect device reliability.2Thermal Characteristics:14-Pin Plastic Package:θJC = 30°C/Watt; θJA = 100°C/Watt14-Pin Cerdip Package:θJC = 30°C/Watt; θJA = 110°C/Watt16-Pin SOIC Package:θJC = 30°C/Watt; θJA = 100°C/Watt3For supply voltages less than ±18 V, the absolute maximum input voltage is equalto the supply voltage.METALIZATION PHOTOGRAPHDimensions shown in inches and (mm).Contact factory for latest dimensions.AD713REV. B–4––Typical CharacteristicsFigure 1.Input Voltage Swing vs.Supply Voltage Figure 4.Quiescent Current vs.Supply Voltage Figure 7.Input Bias Current mon Mode Voltage Figure 3.Output Voltage Swingvs. Load ResistanceFigure 6.Output Impedance vs.Frequency, G = 1Figure 9. Gain Bandwidth Product vs. TemperatureFigure 2.Output Voltage Swing vs.Supply Voltage Figure 5.Input Bias Current vs.Temperature Figure 8.Short Circuit Current Limit vs. TemperatureAD713REV. B–5–Figure 12.Power Supply Rejection vs. FrequencyFigure 15.Output Swing and Error vs. Settling TimeFigure 18.Slew Rate vs. Input Error SignalFigure 11.Open-Loop Gain vs.Supply VoltageFigure rge Signal Frequency Response Figure 17.Input Noise VoltageSpectral Density Figure 10.Open-Loop Gain and Phase Margin vs. FrequencyFigure mon Mode Rejec-tion vs. FrequencyFigure 16.Total Harmonic Distor-tion vs. FrequencyAD713REV. B–6–Figure 19.Crosstalk Test CircuitFigure 20.Crosstalk vs. FrequencyFigure 21b.Unity Gain FollowerPulse Response (Large Signal)Figure 21a.Unity Gain FollowerFigure 22a.Unity Gain InverterFigure 21c.Unity Gain Follower Pulse Response (Small Signal)Figure 22c.Unity Gain InverterPulse Response (Small Signal)Figure 22b.Unity Gain Inverter Pulse Response (Large Signal)AD713REV. B –7–The error signal is thus clamped twice: once to prevent over-loading amplifier A2 and then a second time to avoid overload-ing the oscilloscope preamp. A Tektronix oscilloscope preamp type 7A26 was carefully chosen because it recovers from the ap-proximately 0.4 volt overload quickly enough to allow accurate measurement of the AD713’s 1 µs settling time. Amplifier A2 is a very high speed FET input op amp; it provides a voltage gain of 10, amplifying the error signal output of the AD713 undertest (providing an overall gain of 5).Figure 25.Settling Characteristics to –10 V Step.Upper Trace: Output of AD713 Under Test (5 V/div).Lower Trace: Amplified Error Voltage (0.01%/ div)POWER SUPPLY BYPASSINGThe power supply connections to the AD713 must maintain a low impedance to ground over a bandwidth of 4 MHz or more.This is especially important when driving a significant resistive or capacitive load, since all current delivered to the load comes from the power supplies. Multiple high quality bypass capacitors are recommended for each power supply line in any critical ap-plication. A 0.1 µF ceramic and a 1 µF electrolytic capacitor as shown in Figure 26 placed as close as possible to the amplifier (with short lead lengths to power supply common) will assure adequate high frequency bypassing in most applications. A minimum bypass capacitance of 0.1 µF should be used for anyapplication.Figure 26.Recommended Power Supply BypassingMEASURING AD713 SETTLING TIMEThe photos of Figures 24 and 25 show the dynamic response of the AD713 while operating in the settling time test circuit of Figure 23. The input of the settling time fixture is driven by a flat-top pulse generator. The error signal output from the false summing node of A1, the AD713 under test, is clamped, ampli-fied by op amp A2 and then clamped again.Figure 23.Settling Time Test CircuitFigure 24.Settling Characteristics 0 V to +10 V Step.Upper Trace: Output of AD713 Under Test (5 V/div).Lower Trace: Amplified Error Voltage (0.01%/div)AD713REV. B–8–A HIGH SPEED INSTRUMENTATION AMPLIFIER CIRCUITThe instrumentation amplifier circuit shown in Figure 27 can provide a range of gains from unity up to 1000 and higher using only a single AD713. The circuit bandwidth is 1.2 MHz at a gain of 1 and 250 kHz at a gain of 10; settling time for the entire circuit is less than 5 µs to within 0.01% for a 10 volt step,(G = 10). Other uses for amplifier A4 include an active dataguard and an active sense input.Figure 27.A High Speed Instrumentation Amplifier CircuitTable I provides a performance summary for this circuit. The photo of Figure 28 shows the pulse response of this circuit for a gain of 10.Table I.Performance Summary for the High Speed Instrumentation Amplifier CircuitGainR GBandwidthT Settle (0.01%)1NC 1.2 MHz 2 µs 220 k Ω 1.0 MHz 2 µs 10 4.04 k Ω0.25 MHz 5 µsFigure 28.The Pulse Response of the High Speed Instrumentation Amplifier. Gain = 10A HIGH SPEED FOUR OP AMP CASCADED AMPLIFIER CIRCUITFigure 29 shows how the four amplifiers of the AD713 may be connected in cascade to form a high gain, high bandwidth am-plifier. This gain of 100 amplifier has a –3 dB bandwidth greater than 600 kHz.Figure 29.A High Speed Four Op Amp Cascaded Amplifier CircuitFigure 30.THD Test CircuitHIGH SPEED OP AMP APPLICATIONS AND TECHNIQUESDAC Buffers (I-to-V Converters)The wide input dynamic range of JFET amplifiers makes them ideal for use in both waveform reconstruction and digital-audio DAC applications. The AD713, in conjunction with the AD1860DAC, can achieve 0.0016% THD (here at a 4fs or a 176.4 kHz update rate) without requiring the use of a deglitcher. Just such a circuit is shown in Figure 31. The 470 pF feedback capacitor used with IC2a, along with op amp IC2b and its associated components, together form a 3-pole low-pass filter. Each or all of these poles can be tailored for the desired attenuation and phase characteristics required for a particular application. In this application, one half of an AD713 serves each channel in a two-channel stereo system.AD713REV. B–9–Figure 31.A D/A Converter Circuit for Digital AudioFigure 32.Harmonic Distortion as Frequency for the Digital Audio Circuit of Figure 31Driving the Analog Input of an A/D ConverterAn op amp driving the analog input of an A/D converter, such as that shown in Figure 33, must be capable of maintaining a constant output voltage under dynamically changing load condi-tions. In successive approximation converters, the input current is compared to a series of switched trial currents. The compari-son point is diode clamped but may vary by several hundred millivolts, resulting in high frequency modulation of the A/D in-put current. The output impedance of a feedback amplifier is made artificially low by its loop gain. At high frequencies, where the loop gain is low, the amplifier output impedance can ap-proach its open loop value.Figure 33.The AD713 as an ADC BufferMost IC amplifiers exhibit a minimum open loop output impedance of 25 Ω, due to current limiting resistors. A few hundred microamps reflected from the change in converter loading can introduce errors in instantaneous input voltage.If the A/D conversion speed is not excessive and the band-width of the amplifier is sufficient, the amplifier’s output will return to the nominal value before the converter makes its comparison. However, many amplifiers have relatively narrow bandwidths, yielding slow recovery from output transients. The AD713 is ideally suited as a driver for A/D converters since it offers both a wide bandwidth and a high open loop gain.AD713REV. B–10–Figure 34.Buffer Recovery Time Source Current = 2 mAFigure 35.Buffer Recovery Time Sink Current = 1 mA Driving A Large Capacitive LoadThe circuit of Figure 36 employs a 100 Ω isolation resistor which enables the amplifier to drive capacitive loads exceeding 1500 pF; the resistor effectively isolates the high frequencyfeedback from the load and stabilizes the circuit. Low frequency feedback is returned to the amplifier summing junction via the low pass filter formed by the 100 Ω series resistor and the load capacitance, C1. Figure 37 shows a typical transient responsefor this connection.Figure 36.Circuit for Driving a Large Capacitance Load Table II. Recommended Trim Resistor Values vs.Grades for AD7545 for V D = +5 VTrim JN/AQ/KN/BQ/LN/CQ/GLN/GCQ/ResistorSDTDUDGUDR1500 Ω200 Ω100 Ω20 ΩR2150 Ω68 Ω33 Ω 6.8 ΩFigure 37.Transient Response, R L = 2 k Ω, C L = 500 pF CMOS DAC APPLICATIONSThe AD713 is an excellent output amplifier for CMOS DACs.It can be used to perform both 2 and 4 quadrant operation. The output impedance of a DAC using an inverted R-2R ladder ap-proaches R for codes containing many “1”s, 3R for codes con-taining a single “1” and infinity for codes containing all zeros.For example, the output resistance of the AD7545 will modu-late between 11 k Ω and 33 k Ω. Therefore, with the DAC’s in-ternal feedback resistance of 11 k Ω, the noise gain will vary from 2 to 4/3. This changing noise gain modulates the effect of the input offset voltage of the amplifier, resulting in nonlinear DAC amplifier performance. The AD713, with its guaranteed 1.5 mV input offset voltage, minimizes this effect achieving 12-bit performance.Figures 38 and 39 show the AD713 and a 12-bit CMOS DAC,the AD7545, configured for either a unipolar binary (2-quad-rant multiplication) or bipolar (4-quadrant multiplication) op-eration. Capacitor C1 provides phase compensation which reduces overshoot and ringing.Figure 38.Unipolar Binary OperationFigure 39.Bipolar OperationAD713REV. B–11–Figure 40.A Programmable State Variable Filter CircuitFILTER APPLICATIONSA Programmable State Variable FilterFor the state variable or universal filter configuration of Figure 40 to function properly, DACs A1 and B1 need to control the gain and Q of the filter characteristic, while DACs A2 and B2must accurately track for the simple expression of f C to be true.This is readily accomplished using two AD7528 DACs and one AD713 quad op amp. Capacitor C3 compensates for the effects of op amp gain-bandwidth limitations.This filter provides low pass, high pass and band pass outputs and is ideally suited for applications where microprocessor con-trol of filter parameters is required. The programmable range for component values shown is f C = 0 to 15 kHz and Q = 0.3to 4.5.GIC and FDNR FILTER APPLICATIONSThe closely matched and uniform ac characteristics of the AD713 make it ideal for use in GIC (gyrator) and FDNR (fre-quency dependent negative resistor) filter applications. Figures41 and 43 show the AD713 used in two typical active filters.The first shows a single AD713 simulating two coupled induc-tors configured as a one-third octave bandpass filter. A single section of this filter meets ANSI class II specifications and handles a 7.07 V rms signal with <0.002% THD (20 Hz–20kHz).Figure 43 shows a 7-pole antialiasing filter for a 2 ϫ oversam-pling (88.2 kHz) digital audio application. This filter has <0.05dB pass band ripple and 19.8 ±0.3 µs delay,dc-20 kHz and will handle a 5 V rms signal (V S = ±15 V) with no overload at any internal nodes.The filter of Figure 41 can be scaled for any center frequency by using the formula:f C =1.112πRCwhere all resistors and capacitors scale equally. Resistors R3–R8should not be greater than 2 k Ω in value, to prevent parasitic os-cillations caused by the amplifier’s input capacitance.Figure 41.A 1/3 Octave Filter CircuitAD713REV. B–12–C 1206a –5–11/90P R I N T E D I N U .S .A .If this is not practical, small lead capacitances (10–20 pF)should be added across R5 and R6. Figures 42 and 44 show theoutput amplitude vs. frequency of these filters.Figure 42.Output Amplitude vs. Frequency of 1/3Octave Filter14-Pin Cerdip (Q-14) Package14-Pin Plastic (N-14A) DIP Package 16-Pin SOIC (R-16) Package0.0125 (0.32)00091(023)OUTLINE DIMENSIONSDimensions shown in inches and (mm).Figure 43.An Antialiasing FilterFigure 44.Relative Output Amplitude vs. Frequency of Antialiasing Filter。

AD高速数模转换器中文

AD76816-Bit 高速数模转换器特性刷新率:30MSPS 分辨率:16-Bit 线性度:1/2LSBDNL@14Bits 1LSBINL@14Bits 最快建立时间:满量程25ns,精度0.025%SFDR@1MHz 输出:86dBcTHD@1MHz 输出:71dBc 低干扰脉冲:35pV-s 功率消耗:465mW 片上基准源:2.5V 边沿触发锁存器乘法参考能力应用任意波形发生器通信波形重建矢量图形显示产品描述AD768是16-Bit高速数模转换器(DAC )提供优良的交流和直流性能。

AD768是ADI公司的先进双极CMOS制造(abcmos )处理,结合双极晶体管的速度,激光微调薄膜电阻的精度和有效CMOS 逻辑。

一个分段电流源架构与专有开关技术相结合,以减少毛刺能量来获得最大化的动态精度。

边沿触发输入锁存器和一个温度补偿的带隙基准源已集成,提供一个完整的单片DAC 解决方案。

AD768是电流输出DAC标称满量程输出电流20mA和一个1K的输出阻抗。

差分电流输出提供支持单端或差分应用。

电流输出可以绑接输出电阻提供电压输出,或连接到高速放大器的求和点提供一个缓冲电压输出。

同时,差分输出可以连接到变压器或差分放大器。

片上基准源和控制放大器配置为最大的准确性和灵活性。

AD768 可以通过芯片上的基准源或由一个外部基准电压基于一个外部电阻的选择驱动。

外部电容器允许用户优化变换参考带宽和噪声性能。

AD768采用土5V电源运行,典型的消耗功率465毫瓦。

该芯片采用28引脚SOIC封装,规定工作在工业温度范围。

产品亮点1 、低干扰和快速建立时间提供杰出的波形重建或数字动态性能合成的要求,包括通信。

2、AD768 优良的直流精度使得它适合高速A/D 转换应用。

3、温度补偿,包括片上2.5V 带隙基准。

4、允许的参考同一个外部电阻器使用电流输入。

外部基准也可以使用。

5、AD768 电流输出可单独使用或差分,无论是负载电阻,外部运算放大器求和点或变6、适当选择一个外部电阻和补偿电容允许用户优化AD768 的参考标准和目标带宽应用。

adv7127kru140用法

adv7127kru140用法adv7127kru140用法简介adv7127kru140是一款高性能的视频数字-模拟转换器芯片,可用于图像和视频处理应用。

它支持多种输入和输出格式,并提供了丰富的配置选项。

用法一:选择输入格式•支持的输入格式有:RGB、YCrCb、YUV和YPbPr。

•用户可以通过设置相关寄存器来选择所需的输入格式。

•例如,将寄存器INP_SEL的值设置为0x01,即可选择RGB输入格式。

用法二:配置输出格式•adv7127kru140支持多种输出格式,如模拟CVBS、YPbPr和RGB。

•用户可以根据需要选择合适的输出格式,并通过相关寄存器进行配置。

•例如,将寄存器OUTP_FMT的值设置为0x02,即可选择YPbPr输出格式。

用法三:设置输出电平范围•adv7127kru140可以通过寄存器进行输出电平范围的设置。

•用户可以选择合适的范围以适应不同的使用环境。

•例如,将寄存器OUTP_ELV的值设置为0x01,即可选择1V范围的输出电平。

用法四:调整图像亮度、对比度等参数•adv7127kru140内置了图像处理功能,可实现对图像亮度、对比度等参数的调整。

•通过设置相关寄存器,用户可以根据实际需要对图像进行优化。

•例如,将寄存器CONTRAST的值设置为0x80,即可将对比度设置为中等水平。

用法五:降低功耗•adv7127kru140提供了多种功耗管理功能,可帮助用户降低系统功耗。

•例如,可以通过设置寄存器PD_DACS的值为0x01,将数模转换器的功耗降低到最低。

总结adv7127kru140是一款功能强大的视频数字-模拟转换器芯片,可应用于各种图像和视频处理场景。

通过选择合适的输入格式、配置输出格式、调整图像参数和降低功耗等用法,用户可以根据实际需求灵活使用该芯片。

用法六:配置时钟和同步信号•adv7127kru140需要外部提供时钟和同步信号以确保正常工作。

•用户可以根据实际需求,选择合适的时钟频率和同步信号类型,并通过相关寄存器进行配置。

12位乘法数模转换器AD7845中文版说明书.pdf

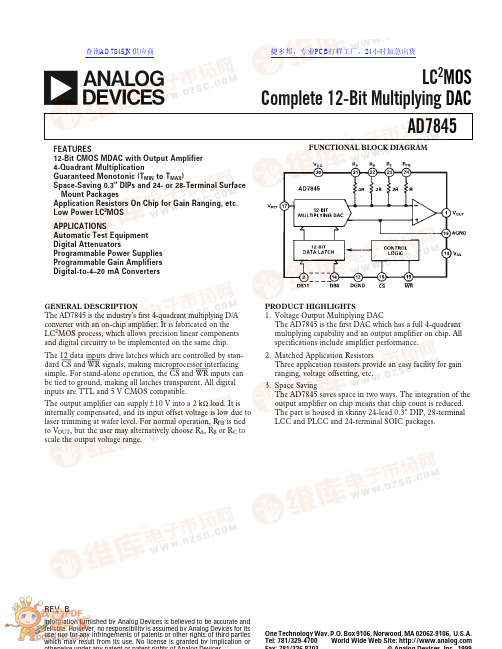

REV.BInformation furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication oraLC 2MOSComplete 12-Bit Multiplying DACAD7845One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.Tel: 781/329-4700World Wide Web Site: FUNCTIONAL BLOCK DIAGRAMPRODUCT HIGHLIGHTS1.Voltage Output Multiplying DACThe AD7845 is the first DAC which has a full 4-quadrant multiplying capability and an output amplifier on chip. All specifications include amplifier performance.2.Matched Application ResistorsThree application resistors provide an easy facility for gain ranging, voltage offsetting, etc.3.Space SavingThe AD7845 saves space in two ways. The integration of the output amplifier on chip means that chip count is reduced.The part is housed in skinny 24-lead 0.3" DIP, 28-terminal LCC and PLCC and 24-terminal SOIC packages.GENERAL DESCRIPTION The AD7845 is the industry’s first 4-quadrant multiplying D/A converter with an on-chip amplifier. It is fabricated on the LC 2MOS process, which allows precision linear components and digital circuitry to be implemented on the same chip.The 12 data inputs drive latches which are controlled by stan-dard CS and WR signals, making microprocessor interfacing simple. For stand-alone operation, the CS and WR inputs can be tied to ground, making all latches transparent. All digital inputs are TTL and 5 V CMOS compatible.The output amplifier can supply ±10 V into a 2 k Ω load. It is internally compensated, and its input offset voltage is low due to laser trimming at wafer level. For normal operation, R FB is tied to V OUT , but the user may alternatively choose R A , R B or R C to scale the output voltage range.FEATURES12-Bit CMOS MDAC with Output Amplifier 4-Quadrant MultiplicationGuaranteed Monotonic (T MIN to T MAX )Space-Saving 0.3" DIPs and 24- or 28-Terminal Surface Mount PackagesApplication Resistors On Chip for Gain Ranging, etc.Low Power LC 2MOSAPPLICATIONSAutomatic Test Equipment Digital AttenuatorsProgrammable Power Supplies Programmable Gain Amplifiers Digital-to-4–20 mA Converters查询AD7845JN供应商捷多邦,专业PCB打样工厂,24小时加急出货(V DD = +15 V, ؎ 5%, V SS = –15 V, ؎ 5%, V REF = +10 V, AGND = DGND = O V,V OUT connected to R FB. V OUT load = 2 k⍀, 100 pF. All specifications T MIN to T MAX unless otherwise noted.)AD7845–SPECIFICATIONS1Parameter J Version K Version A Version B Version S Version T Version Units Test Conditions/CommentsACCURACYResolution121212121212Bits1 LSB = V REF212= 2.4 mVRelative Accuracyat +25°C±1±1/2±1±1/2±1±1/2LSB max All Grades Are Guaranteed T MIN to T MAX±1±3/4±1±3/4±1±3/4LSB max Monotonic over Temperature Differential Nonlinearity±1±1±1±1±1±1LSB max DAC Register Loaded withZero Code Offset Error All 0s.at +25°C±2±1±2±1±2±1mV maxT MIN to T MAX±3±2±3±2±4±3mV maxOffset Temperature Coefficient;(∆Offset/∆Temperature)2±5±5±5±5±5±5µV/°C typGain Error±3±2±3±2±3±2LSB max R FB, V OUT Connected±6±6±6±6±6±6LSB max R C, V OUT Connected, V REF = +5 V±6±6±6±6±6±6LSB max R B, V OUT Connected, V REF = +5 V±7±7±7±7±7±7LSB max R A, V OUT Connected, V REF = +2.5 V Gain Temperature Coefficient;(∆Gain/∆Temperature)2±2±2±2±2±2±2ppm of FSR/°C R FB, V OUT ConnectedtypREFERENCE INPUTInput Resistance, Pin 17888888kΩ min Typical Input Resistance = 12 kΩ161616161616kΩ maxAPPLICATION RESISTORRATIO MATCHING0.50.50.50.50.50 5% max Matching Between R A, R B, R C DIGITAL INPUTSV IH (Input High Voltage) 2.4 2.4 2.4 2.4 2.4 2.4V minV IL (Input Low Voltage)0.80.80.80.80.80.8V maxI IN (Input Current)±1±1±1±1±1±1µA max Digital Inputs at 0 V and V DDC IN (Input Capacitance)2777777pF maxPOWER SUPPLY4V DD Range14.25/15.7514.25/15.7514.25/15.7514.25/15.7514.25/15.7514.25/15.75V min/V maxV SS Range–14.25/–15.75–14.25/–15.75–14.25/–15.75–14.25/–15.75–14.25/–15.75–14.25/–15.75V min/V maxPower Supply Rejection∆Gain/∆V DD±0.01±0.01±0.01±0.01±0.01±0.01% per % max V DD = +15 V ± 5%, V REF = –10 V ∆Gain/∆V SS±0.01±0.01±0.01±0.01±0.01±0.01% per % max V SS = –15 V ± 5%.I DD666666mA max V OUT UnloadedI SS444444mA max V OUT UnloadedAC PERFORMANCE CHARACTERISTICSThese characteristics are included for Design Guidance and are not subject to test.DYNAMIC PERFORMANCEOutput Voltage Settling Time555555µs max To 0.01% of Full-Scale RangeV OUT Load = 2 kΩ, 100 pF.DAC Register Alternately Loadedwith All 0s and All 1s. Typically2.5 µs at 25°C.Slew Rate111111111111V/µs typ V OUT Load = 2 kΩ, 100 pF.Digital-to-Analog555555555555nV–s typ Measured with V REF = 0 V.Glitch Impulse DAC Register Alternately Loadedwith All 0s and All 1s.Multiplying Feedthrough555555mV p-p typ V REF = ±10 V, 10 kHz Sine Wave Error3DAC Register Loaded with All 0s. Unity Gain Small SignalBandwidth600600600600600600kHz typ V OUT, R FB Connected. DAC Loadedwith All 1s V REF = 100 mV p-pSine Wave.Full Power Bandwidth175175175175175175kHz typ V OUT, R FB Connected. DAC Loadedwith All 1s. V REF = 20 V p-pSine Wave. R L = 2 kΩ.Total Harmonic Distortion–90–90–90–90–90–90dB typ V REF = 6 V rms, 1 kHz Sine Wave. OUTPUT CHARACTERISTICS5Open Loop Gain858585858585dB min V OUT, R FB Not ConnectedV OUT = ±10 V, R L = 2 kΩOutput Voltage Swing±10±10±10±10±10±10V min R L = 2 kΩ, C L = 100 pFOutput Resistance0.20.20.20.20.20.2Ω typ R FB, V OUT Connected,Short Circuit Current @ +25°C111111111111mA typ V OUT Shorted to AGNDOutput Noise Voltage Includes Noise Due to Output(0.1 Hz to 10 Hz) @ +25°C222222µV rms typ Amplifier and Johnson Noisef = 10 Hz250250250250250250nV/√Hz typ of R FBf = 100Hz100100100100100100nV/√Hz typf= 1 kHz505050505050nV/√Hz typf = 10kHz505050505050nV/√Hz typf = 100 kHz505050505050nV/√Hz typNOTES1Temperature ranges are as follows: J, K Versions: 0°C to +70°C; A, B Versions: –40°C to +85°C; S, T Versions: –55°C to +125°C.2Guaranteed by design and characterization, not production tested.3The metal lid on the ceramic D-24A package is connected to Pin 12 (DGND).4The device is functional with a power supply of ±12 V.5Minimum specified load resistance is 2 kΩ.AD7845 TIMING CHARACTERISTICS1(V DD = +15 V, ؎ 5%. V SS = –15 V, ؎ 5%. V REF = +10 V. AGND = DGND = O V.)NOTES1Analog Devices reserves the right to ship either ceramic (D-24A) or cerdip(Q-24) hermetic packages.2To order MIL-STD-883, Class B processed parts, add /883B to part number.3E = Leadless Ceramic Chip Carrier; N = Plastic DIP; P = Plastic Leaded ChipCarrier; Q = Cerdip; R = SOIC.AD7845PIN CONFIGURATIONSLCCPLCCDIP, SOICDIGITAL-TO-ANALOG GLITCH IMPULSEThis is the amount of charge injected from the digital inputs to the analog output when the inputs change state. This is nor-mally specified as the area of the glitch in either pA-secs or nV-secs depending upon whether the glitch is measured as a current or voltage. The measurement takes place with V REF =AGND.DIGITAL FEEDTHROUGHWhen the DAC is not selected (i.e., CS is high) high frequency logic activity on the device digital inputs is capacitively coupled through the device to show up as noise on the V OUT pin. This noise is digital feedthrough.MULTIPLYING FEEDTHROUGH ERRORThis is ac error due to capacitive feedthrough from the V REF terminal to V OUT when the DAC is loaded with all 0s.OPEN-LOOP GAINOpen-loop gain is defined as the ratio of a change of output voltage to the voltage applied at the V REF pin with all 1s loaded in the DAC. It is specified at dc.UNITY GAIN SMALL SIGNAL BANDWIDTHThis is the frequency at which the magnitude of the small signal voltage gain of the output amplifier is 3 dB below unity. The device is operated as a closed-loop unity gain inverter (i.e.,DAC is loaded with all 1s).OUTPUT RESISTANCEThis is the effective output source resistance.FULL POWER BANDWIDTHFull power bandwidth is specified as the maximum frequency, at unity closed-loop gain, for which a sinusoidal input signal will produce full output at rated load without exceeding a distortion level of 3%.TERMINOLOGYLEAST SIGNIFICANT BITThis is the analog weighting of 1 bit of the digital word in aDAC. For the AD7845, 1 LSB = V REF212.RELATIVE ACCURACYRelative accuracy or endpoint nonlinearity is a measure of the maximum deviation from a straight line passing through the endpoints of the DAC transfer function. It is measured after adjusting for both endpoints (i.e., offset and gain error are ad-justed out) and is normally expressed in least significant bits or as a percentage of full-scale range.DIFFERENTIAL NONLINEARITYDifferential nonlinearity is the difference between the measured change and the ideal 1 LSB change between any two adjacent codes. A specified differential nonlinearity of +1 LSB max over the operating temperature range ensures monotonicity.GAIN ERRORGain error is a measure of the output error between an ideal DAC and the actual device output with all 1s loaded after offset error has been adjusted out. Gain error is adjustable to zero with an external potentiometer. See Figure 13.ZERO CODE OFFSET ERRORThis is the error present at the device output with all 0s loaded in the DAC. It is due to the op amp input offset voltage and bias current and the DAC leakage current.TOTAL HARMONIC DISTORTIONThis is the ratio of the root-mean-square (rms) sum of the har-monics to the fundamental, expressed in dBs.OUTPUT NOISEThis is the noise due to the white noise of the DAC and the input noise of the amplifier.Typical Performance Characteristics–AD7845Figure 3.Output Voltage Swing vs.Resistive LoadFigure 6.Typical AD7845 Linearityvs. Power Supply Figure 9.Unity Gain Inverter PulseResponse (Small Signal)Figure 4.Noise Spectral DensityFigure 7.Multiplying Feedthrough Error vs. FrequencyTIME – sO U T P U T – m V8010–20220468101214161870200–1040306050Figure 10.Digital-to-Analog Glitch Impulse (All 1s to All 0s Transition)Figure 2.Frequency Response, G = –1Figure 5.THD vs. FrequencyFigure 8.Unity Gain Inverter Pulse Response (Large Signal)AD7845PIN FUNCTION DESCRIPTION (DIP)Pin Mnemonic Description1V OUTVoltage Output Terminal2-11DB11–DB2Data Bit 11 (MSB) to Data Bit 212DGND Digital Ground. The metal lid on the ceramic package is connected to this pin13-14DB1–DB0Data Bit 1 to Data Bit 0 (LSB)15WR Write Input. Active low16CS Chip Select Input. Active low17V REF Reference Input Voltage which can be an ac or dc signal18AGND Analog Ground. This is the reference point for external analog circuitry 19V SS Negative power supply for the output amplifier (nominal –12 V to +15 V)20V DD Positive power supply (nominal +12 V to +15 V)21R A Application resistor. R A = 4 R FB 22R B Application resistor. R B = 2 R FB 23R C Application resistor. R C = 2 R FB24R FBFeedback resistor in the DAC. For normal operation this is connected to V OUTCIRCUIT INFORMATION Digital Section Figure 11 is a simplified circuit diagram of the AD7845 input control logic. When CS and WR are both low, the DAC latch is loaded with the data on the data inputs. All the digital inputs are TTL, HCMOS and +5 V CMOS compatible, facilitating easy microprocessor interfacing. All digital inputs incorporate standard protection circuitry.Figure 11.AD7845 Input Control LogicD/A SectionFigure 12 shows a simplified circuit diagram for the AD7845D/A section and output amplifier.A segmented scheme is used whereby the 2 MSBs of the 12-bit data word are decoded to drive the three switches A-C. The remaining 10 bits drive the switches (S0–S9) in a standard R-2Rladder configuration.Figure 12.Simplified Circuit Diagram for the AD7845 D/A SectionEach of the switches A–C steers 1/4 of the total reference cur-rent with the remaining 1/4 passing through the R-2R section.An output amplifier and feedback resistor perform the current-to-voltage conversion givingV OUT = – D × V REFwhere D is the fractional representation of the digital word. (D can be set from 0 to 4095/4096.)The amplifier can maintain ±10 V across a 2 k Ω load. It is inter-nally compensated and settles to 0.01% FSR (1/2 LSB) in less than 5 µs. The input offset voltage is laser trimmed at wafer level. The amplifier slew rate is typically 11 V/µs, and the unity gain small signal bandwidth is 600 kHz. There are three extra on-chip resistors (R A , R B , R C ) connected to the amplifier invert-ing terminal. These are useful in a number of applications in-cluding offset adjustment and gain ranging.AD7845UNIPOLAR BINARY OPERATIONFigure 13 shows the AD7845 connected for unipolar binary operation. When V IN is an ac signal, the circuit performs2-quadrant multiplication. The code table for Figure 13 is givenin Table I.Figure 13.Unipolar Binary Operation Table I. Unipolar Binary Code Table for AD7845Binary Number In DAC Register Analog Output, V OUT MSB LSB 111111111111–V IN40954096100000000000–V IN 20484096 = –1/2 V IN000000000001–V IN 140960000000000000 VOFFSET AND GAIN ADJUSTMENT FOR FIGURE 13Zero Offset Adjustment1.Load DAC with all 0s.2.Trim R3 until V OUT = 0 V.Gain Adjustment1.Load DAC with all 1s.2.Trim R1 so that V OUT = –V IN40954096.In fixed reference applications, full scale can also be adjusted byomitting R1 and R2 and trimming the reference voltage magni-tude. For high temperature applications, resistors and potenti-ometers should have a low temperature coefficient.BIPOLAR OPERATION(4-QUADRANT MULTIPLICATION)The recommended circuit for bipolar operation is shown in Figure 14. Offset binary coding is used.The offset specification of this circuit is determined by the matching of internal resistors R B and R C and by the zero code offset error of the device. Gain error may be adjusted by varying the ratio of R1 and R2.To use this circuit without trimming and keep within the gain error specifications, resistors R1 and R2 should be ratio matched to 0.01%.The code table for Figure 14 is given in Table II.Figure 14.Bipolar Offset Binary Operation Table II. Bipolar Code Table for Offset Binary Circuit ofFigure 14Binary Number In DAC Register Analog Output, V OUT MSB LSB 111111111111+V IN 20472048100000000001+V IN 120481000000000000 V011111111111–V IN 12048000000000000–V IN20482048= –V INAD7845APPLI CATION S CIRCUITSPROGRAMMABLE GAIN AMPLIFIER (PGA)The AD7845 performs a PGA function when connected as in Figure 15. In this configuration, the R-2R ladder is connected in the amplifier feedback loop. R FB is the amplifier input resis-tor. As the code decreases, the R-2R ladder resistance increases and so the gain increases.V OUT = –VIN × R DACD × 1R FB , D =0to 40954096 = –V IN ×R DAC D × 1R DAC= –VIN D, since R FB = R DACFigure 15.AD7845 Connected as PGAAs the programmed gain increases, the error and noise also increase. For this reason, the maximum gain should be limited to 256. Table III shows gain versus code.Note that instead of using R FB as the input resistor, it is also possible to use combinations of the other application resistors,R A , R B and R C . For instance, if R B is used instead of R FB , the gain range for the same codes of Table II now goes from l/2to 128.Table III.Gain and Error vs. Input Code for Figure 15Digital Inputs Gain Error (%)1111111111114096/4095 ≈ 10.0410000000000020.0701000000000040.1300100000000080.26000100000000160.5100001000000032 1.0200000100000064 2.0000000100000128 4.00000000100002568.0PROGRAMMABLE CURRENT SOURCESThe AD7845 is ideal for designing programmable currentsources using a minimum of external components. Figures 16and 17 are examples. The circuit of Figure 16 drives a program-mable current I L into a load referenced to a negative supply.Figure 17 shows the circuit for sinking a programmable current,I L . The same set of circuit equations apply for both diagrams.I L = I 3 = I 2 + I 1I 1 = D ×|V IN |RDAC ,D =0to 40954096I 2 = 1R 1 D ×|V IN |R DAC R FB = D ×|V IN |R 1, since R FB = R DAC I L =D ×|V IN |R 1 +D ×|V IN |R DAC= D ×|V IN |R 1×1+R 1R DACNote that by making R1 much smaller than R DAC , the circuitbecomes insensitive to both the absolute value of R DAC and its temperature variations. Now, the only resistor determining load current I L is the sense resistor R1.If R1 = 100 Ω, then the programming range is 0 mA to 100 mA,and the resolution is 0.024 mA.Figure 16.Programmable Current SourceAD7845Figure 17.Programmable Current Sink4–20 mA CURRENT LOOPThe AD7845 provides an excellent way of making a 4-20 mAcurrent loop circuit. This is basically a variation of the circuitsin Figures 16 and 17 and is shown in Figure 18. The applicationresistor R A (Value 4R) produces the effective 4 mA offset.I L = I3 = I2 + I1Since I2 > I1,I L = –V X156=2.54R×R FB+2.5R DAC×D×R FB×1156and since R DAC=R FB=RI L =2.54+D×2.5×1000156mA= [4 + (16 ×D)]mA, where D goes from 0 to 1 withDigital CodeWhen D = 0(Code of all 0s):I L = 4 mAWhen D = 1(Code of all 1s):I L = 20mAThe above circuit succeeds in significantly reducing the circuitcomponent count. Both the on-chip output amplifier and theapplication resistor R A contribute to this.Figure 18.4–20 mA Current LoopAPPLICATION HINTSGeneral Ground Management: AC or transient voltagesbetween AGND and DGND can cause noise injection into theanalog output. The simplest method of ensuring that voltages atAGND and DGND are equal is to tie AGND and DGNDtogether at the AD7845. In more complex systems where theAGND and DGND intertie is on the backplane, it is recom-mended that two diodes be connected in inverse parallel be-tween the AD7845 AGND and DGND pins (IN914 orequivalent).Digital Glitches: When a new digital word is written into theDAC, it results in a change of voltage applied to some of theDAC switch gates. This voltage change is coupled across theswitch stray capacitance and appears as an impulse on the cur-rent output bus of the DAC. In the AD7845, impulses on thisbus are converted to a voltage by R FB and the output amplifier.The output voltage glitch energy is specified as the area of theresulting spike in nV-seconds. It is measured with V REF con-nected to analog ground and for a zero to full-scale input codetransition. Since microprocessor based systems generally havenoisy grounds which couple into the power supplies, theAD7845 V DD and V SS terminals should be decoupled to signalground.Temperature Coefficients: The gain temperature coefficientof the AD7845 has a maximum value of 5 ppm/°C. This corre-sponds to worst case gain shift of 2 LSBs over a 100°C tem-perature range. When trim resistors R1 and R2 in Figure 13are used to adjust full-scale range, the temperature coefficientof R1 and R2 must be taken into account. The offset tempera-ture coefficient is 5 ppm of FSR/°C maximum. This corre-sponds to a worst case offset shift of 2 LSBs over a 100°Ctemperature range.The reader is referred to Analog Devices Application Note“Gain Error and Gain Temperature Coefficient of CMOS Mul-tiplying DACs,” Publication Number E630C-5-3/86.AD78458-BIT MICROPROCESSOR SYSTEMSFigure 22 shows an interface circuit for the AD7845 to the 8085A 8-bit microprocessor. The software routine to load data to the device is given in Table IV. Note that the transfer of the 12 bits of data requires two write operations. The first of these loads the 4 MSBs into the 7475 latch. The second write opera-tion loads the 8 LSBs plus the 4 MSBs (which are held by thelatch) into the DAC.Figure 22.8085A Interface Table IV. Subroutine Listing for Figure 222000 LOAD DAC:LXIH,#3000The H,L register pair are loaded with latch address 3000.MVI A,#“MS”Load the 4 MSBs ofdata into accumulator.MOV M,A Transfer data fromaccumulator to latch.INR L Increment H,L pair toAD7845 address.MVI A,#“LS”Load the 8 LSBs ofdata into accumulator.MOVM,A Transfer data fromaccumulator to DAC.RETEnd of routine.MICROPROCESSOR INTERFACING 16-BIT MICROPROCESSOR SYSTEMSFigures 19, 20 and 21 show how the AD7845 interfaces to three popular 16-bit microprocessor systems. These are the MC68000, 8086 and the TM32010. The AD7845 is treated as a memory-mapped peripheral to the processors. In each case, a write instruction loads the AD7845 with the appropriate data.The particular instructions used are as follows:MC68000:MOVE 8086:MOVTMS32010:OUTFigure 19.AD7845 to MC68000 InterfaceFigure 20.AD7845 to 8086 InterfaceFigure 21.TMS32010AD7845Figure 23 and 24 are the interface circuits for the Z80 and MC6809 microprocessors. Again, these use the same basicformat as the 8085A interface.Figure 23.AD7845 to Z80 InterfaceFigure 24.MC6809 InterfaceDIGITAL FEEDTHROUGHIn the preceding interface configurations, most digital inputs to the AD7845 are directly connected to the microprocessor bus.Even when the device is not selected, these inputs will be con-stantly changing. The high frequency logic activity on the bus can feed through the DAC package capacitance to show up as noise on the analog output. To minimize this digital feedthrough isolate the DAC from the noise source. Figure 25 shows an interface circuit which uses this technique. All data inputs are latched from the busy by the CS signal. One may also use other means, such as peripheral interface devices, to reduce the digitalfeedthrough.Figure 25.AD7845 Interface Circuit Using Latches to Minimize Digital FeedthroughAD7845OUTLINE DIMENSIONSDimensions shown in inches and (mm).C 1189b –1–9/99P R I N T E D I N U .S .A .24-Lead Plastic DIP(N-24)24-Lead Cerdip(Q-24)24-Lead Ceramic DIP(D-24A)28-Terminal Leadless Ceramic Chip Carrier(E-28A)28-Terminal Plastic Leaded Chip Carrier(P-28A)24-Lead SOIC(R-24)。

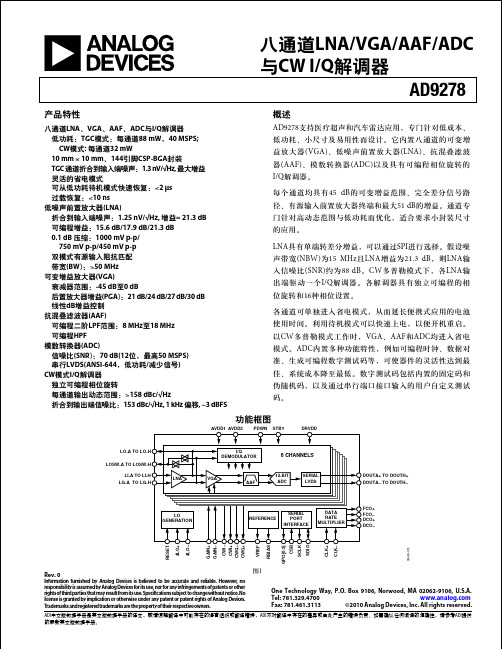

AD9278 八通道LNA VGA AAF ADC 与CW I Q解调器 数据手册说明书

ADI 中文版数据手册是英文版数据手册的译文,敬请谅解翻译中可能存在的语言组织或翻译错误,ADI 不对翻译中存在的差异或由此产生的错误负责。

如需确认任何词语的准确性,请参考ADI 提供的最新英文版数据手册。

八通道LNA/VGA/AAF/ADC 与CW I/Q 解调器AD9278Rev. 0Information furnished by Analog Devices is believed to be accurate and reliable. However , no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Speci cations subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners.One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.Tel: 781.329.4700 Fax: 781.461.3113 ©2010 Analog Devices, Inc. All rights reserved.功能框图AAF12-BIT ADC VGALNASERIAL LVDSI/QDEMODULATOR8 CHANNELSSERIAL PORT INTERFACEDATA RATE MULTIPLIERREFERENCELOGENERATIONLO-A TO LO-HLOSW-A TO LOSW-HLI-A TO LI-H LG-A TO LG-HDOUTA+ TO DOUTH+DOUTA– TO DOUTH–FCO+DRVDDC L K –C L K +S D I OS C L KC S BG P O [0:3]R B I A SV R E FC W Q +C W Q –C W I +C W I –G A I N –G A I N +4L O –4L O +R E S E TSTBYPDWNAVDD2AVDD1FCO–DCO+DCO–09424-001图1产品特性八通道LNA 、VGA 、AAF 、ADC 与I/Q 解调器 低功耗:TGC 模式:每通道88 mW ,40 MSPS; CW 模式: 每通道32 mW 10 mm × 10 mm 、144引脚CSP-BGA 封装 TGC 通道折合到输入端噪声:1.3 nV/√Hz, 最大增益 灵活的省电模式 可从低功耗待机模式快速恢复:<2 μs 过载恢复:<10 ns 低噪声前置放大器(LNA) 折合到输入端噪声:1.25 nV/√Hz, 增益= 21.3 dB 可编程增益:15.6 dB/17.9 dB/21.3 dB 0.1 dB 压缩:1000 mV p-p/ 750 mV p-p/450 mV p-p 双模式有源输入阻抗匹配 带宽(BW ):>50 MHz 可变增益放大器(VGA) 衰减器范围:-45 dB 至0 dB 后置放大器增益(PGA ):21 dB/24 dB/27 dB/30 dB 线性dB 增益控制 抗混叠滤波器(AAF) 可编程二阶LPF 范围:8 MHz 至18 MHz 可编程HPF 模数转换器(ADC) 信噪比(SNR ):70 dB(12位,最高50 MSPS) 串行LVDS(ANSI-644,低功耗/减少信号) CW 模式I/Q 解调器 独立可编程相位旋转 每通道输出动态范围:>158 dBc/√Hz 折合到输出端信噪比:153 dBc/√Hz, 1 kHz 偏移, −3 dBFS概述AD9278支持医疗超声和汽车雷达应用,专门针对低成本、低功耗、小尺寸及易用性而设计。

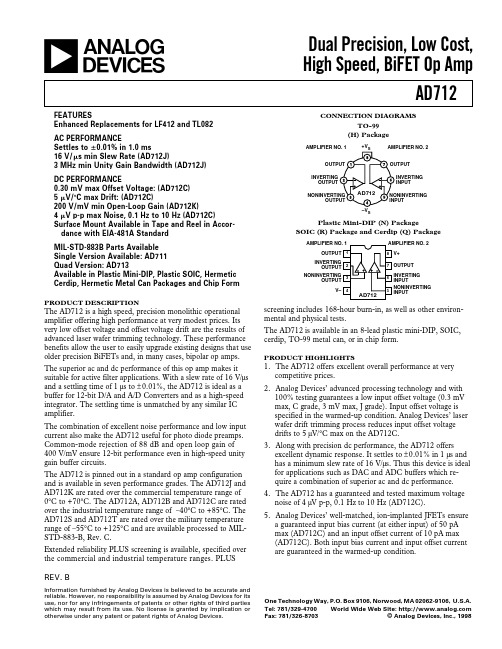

AD712ACHIPS资料

a

FEATURES Enhanced Replacements for LF412 and TL082 AC PERFORMANCE Settles to ؎0.01% in 1.0 ms 16 V/ s min Slew Rate (AD712J) 3 MHz min Unity Gain Bandwidth (AD712J) DC PERFORMANCE 0.30 mV max Offset Voltage: (AD712C) 5 V/؇C max Drift: (AD712C) 200 V/mV min Open-Loop Gain (AD712K) 4 V p-p max Noise, 0.1 Hz to 10 Hz (AD712C) Surface Mount Available in Tape and Reel in Accordance with EIA-481A Standard MIL-STD-883B Parts Available Single Version Available: AD711 Quad Version: AD713 Available in Plastic Mini-DIP, Plastic SOIC, Hermetic Cerdip, Hermetic Metal Can Packages and Chip Form PRODUCT DESCRIPTION

PRODUCT HIGHLIGHTS

1. The AD712 offers excellent overall performance at very competitive prices. 2. Analog Devices’ advanced processing technology and with 100% testing guarantees a low input offset voltage (0.3 mV max, C grade, 3 mV max, J grade). Input offset voltage is specified in the warmed-up condition. Analog Devices’ laser wafer drift trimming process reduces input offset voltage drifts to 5 µV/°C max on the AD712C. 3. Along with precision dc performance, the AD712 offers excellent dynamic response. It settles to ± 0.01% in 1 µs and has a minimum slew rate of 16 V/µs. Thus this device is ideal for applications such as DAC and ADC buffers which require a combination of superior ac and dc performance. 4. The AD712 has a guaranteed and tested maximum voltage noise of 4 µV p-p, 0.1 Hz to 10 Hz (AD712C). 5. Analog Devices’ well-matched, ion-implanted JFETs ensure a guaranteed input bias current (at either input) of 50 pA max (AD712C) and an input offset current of 10 pA max (AD712C). Both input bias current and input offset current are guaranteed in the warmed-up condition.

CS7123 三路10bit 高速视频DA 转换器

特点:● 240MHz的最大采样速度●三路10位D/A转换器● SFDR当时钟频率为50MHZ;输出为1MHZ时,–70dB当时钟频率为140MHZ;输出为40HMZ时,-53dB●与RS-343A/RS-170接口输出兼容●DA转换器的输出电流范围为:2mA到26mA● TTL兼容输入●内部基准参考电压为:1.23V●单电源+5V/+3.3V工作●48脚LQFP封装●低功耗(3V时最小值为30mW)●低功耗的静态模式(3V时典型值为6mW)●工业温度范围(-40C0到+85)描述:CS7123是一个三路高速、数模转换器的单片集成电路。

它包括三路高速、 10位输入的视频DA转换器、标准的TTL输入和互补输出高阻抗的模拟输出电流源。

它有三路独立的10位输入端口,可以在单电源5V下工作,也可以在单电源3.3V下工作。

CS7123还有附加的两个视频控制信号:1:复合SYNC(同步信号)2:BLANK(黑电平)CS7123也有一个待电模式。

CS7123由5VCMOS工艺制造、单片CMOS结构确保了低功耗的性能。

CS7123为48脚LQFP封装。

主要应用:数字视频系统(1600x1200@100HZ)、高分辨率的彩色图片、数字射频调制、图像处理、仪器、视频信号再现。

原理框图:SET V REF IOB IOB IOG IOG IOR IOR图1 CS7123功能框图V REF COMP IOR V AA IOR IOG IOG IOB IOBV AAV A AB B B B B B B B BC L O C B G0G1G2G3G6BLACK SYNC图2 CS7123管脚图1121H1图3 CS7123外形图1.引脚定义2.电特性:5V 静态参数(uF C R V V V VAA L SET REF 10,560,235.1%,55=Ω==±+=,没有特别说明,所以的参数都是指最大温度到最小温度MIN T to MAX T ,最大温度110=J T ℃) 参数 最小值典型值最大值单位 测试条件分辨率(每个DA )10Bits积分非线性误差(INL ) -1 4.0± +1 LSB 静态性能 差分非线性误差(DNL ) -1 25.0± +1 LSB单调性保证 输入高电平(IH V )2 V输入低电平(IL V ) 0.8 V 输入电流(IN V )-1 +1 uAPSAVE 下拉电流20 uA 数字 控制输入 输入电容,IN C10 pFV V IN 0.0=或 DD IN V V =输出电流 2.0 26.5 mA 绿色DAC ,Sync=High输出电流 2.0 18.5 mA R/G/BDAC,Sync=Low DAC 与DAC 之间的匹配度 1.0 5% 输入电压余度,OC V 0 +1.4 V 输出阻抗,OUT R 100 K Ω输出电容,OUT C10 pFmA I OUT 0=失调误差 -0.025 +0.025 %FSR DAC Output =0 测试模拟输入增益误差 -5.0 +5.0 %FSR FSR =17.62mA 电压参考范围输出阻抗,REF V (内部和外部) 1.12 1.235 1.35 V数字电源电流 3.4 9 mA Z CLK MH f 50=数字电源电流 10.5 15 mA Z CLK MH f 140=功耗数字电源电流 18 25 mAZ CLK MH f 240=模拟电源电流 67 72 mA Ω=560SET R 模拟电源电流 8 mAΩ=4933SET R节能电流 2.1 5.0 mA PSA VE =Low,数字和控制输入为DD V电源抑制比 0.1 0.5 %%5V 动态参数(uF C R V V V VAA L SET REF 10,560,235.1%,55=Ω==±+=,没有特别说明,所以的参数都是指最大温度到最小温度MIN T to MAX T ,最大温度110=J T ℃) 参数 最小值典型值最大值 单位 交流线性度无失真动态范围(SFDR )到奈奎斯特频率 单端输出Z CLK MH f 50=;Z OUT MH f 00.1= 67 dBc Z CLK MH f 50=;Z OUT MH f 51.2= 67 dBc Z CLK MH f 50=;Z OUT MH f 04.5= 63 dBcZ CLK MH f 50=;Z OUT MH f 2.20= 55 dBc Z CLK MH f 100=;Z OUT MH f 51.2= 62 dBc Z CLK MH f 100=;Z OUT MH f 04.5= 60 dBc Z CLK MH f 100=;Z OUT MH f 2.20= 54 dBc Z CLK MH f 100=;Z OUT MH f 4.40= 48 dBc Z CLK MH f 140=;Z OUT MH f 51.2= 57 dBc Z CLK MH f 140=;Z OUT MH f 04.5= 58 dBc Z CLK MH f 140=;Z OUT MH f 2.20= 52 dBc Z CLK MH f 140=;Z OUT MH f 4.40=41 dBc双端输出Z CLK MH f 50=;Z OUT MH f 00.1= 70 dBc Z CLK MH f 50=;Z OUT MH f 51.2= 70 dBc Z CLK MH f 50=;Z OUT MH f 04.5= 65 dBc Z CLK MH f 50=;Z OUT MH f 2.20= 54 dBc Z CLK MH f 100=;Z OUT MH f 51.2= 67 dBc Z CLK MH f 100=;Z OUT MH f 04.5= 63 dBc Z CLK MH f 100=;Z OUT MH f 2.20= 58 dBc Z CLK MH f 100=;Z OUT MH f 4.40= 52 dBc Z CLK MH f 140=;Z OUT MH f 51.2= 62 dBc Z CLK MH f 140=;Z OUT MH f 04.5= 61 dBc Z CLK MH f 140=;Z OUT MH f 2.20= 55 dBc Z CLK MH f 140=;Z OUT MH f 4.40=53 dBc 在窗内的非失真动态范围 单端输出Z CLK MH f 50=;Z OUT MH f 00.1=;1MHZ 扫宽 77 dBc Z CLK MH f 50=;Z OUT MH f 04.5=;2MHZ 扫宽 73 dBc Z CLK MH f 140=;Z OUT MH f 04.5=;4MHZ 扫宽64 dBc 双端输出Z CLK MH f 50=;Z OUT MH f 00.1=;1MHZ 扫宽 74 dBc Z CLK MH f 50=;Z OUT MH f 00.5=;2MHZ 扫宽 73 dBc Z CLK MH f 140=;Z OUT MH f 00.5=;4MHZ 扫60 dBc整个谐波失真(THD )Z CLK MH f 50=;Z OUT MH f 00.1= 25+=A T ℃ 66 dBc Z CLK MH f 50=;Z OUT MH f 00.1=;MIN T to MAX T 65 dBc Z CLK MH f 50=;Z OUT MH f 00.2= 64 dBc Z CLK MH f 100=;Z OUT MH f 00.2= 63 dBc Z CLK MH f 140=;Z OUT MH f 00.2=55 dBcDAC 性能抖动脉冲10 pVsDACu 交扰(crosstalk ) 23 dB数据馈通 22 dB 时钟馈通 33 dB5V 时序图:(uF C R V V V VAA L SET REF 10,560,235.1%,55=Ω==±+=,没有特别说明,所以的参数都是指最大温度到最小温度MIN T to MAX T ,最大温度110=J T ℃) 参数值最小 典型 最大 单位 条件模拟输出延时,6t5.5 ns 模拟输出上升/下降沿时间,47t 1.0 ns 模拟输出过渡时间,58t 15 ns 模拟输出跳变69t 1 2 ns 时钟控制7CLK f 0.5 50 MHz 50MHz Grade 7CLK f 0.5 140 MHz 140MHz Grade 7CLK f0.5 240 MHz240MHz GradeCLOCKDIGITAL INPUTS(R9~R0、G9~G0、B9~B0、SYNC 、BLACK )ANALOG OUTPUTS (IOR 、IOG 、IOB 、IOR 、IOG 、IOB )图1. 时序图3.3V 静态参数(uF C R V V V VAA L SET REF 10,560,235.1%,55=Ω==±+=,没有特别说明,所以的参数都是指最大温度到最小温度MIN T to MAX T ,最大温度110=J T ℃) 参数 最小值典型值最大值单位 测试条件分辨率(每个DA )10Bits静态性积分非线性误差(INL ) -1 4.0±+1 LSB单调性保证性能 差分非线性误差(DNL ) -1 25.0±+1 LSB输入高电平(IH V ) 2 V 输入低电平(IL V ) 0.8 V 输入电流(IN V )-1 +1 uAPSAVE 下拉电流20 uA 数字 控制输入 输入电容,IN C10 pF V V IN 0.0=或DD IN V V =输出电流 2.0 26.5 mA 绿色DAC ,Sync=High输出电流 2.0 18.5 mA R/G/B DAC,Sync =Low DAC 与DAC 之间的匹配度 1.0 5% 输入电压余度,OC V 0 +1.4 V 输出阻抗,OUT R 100 K Ω输出电容,OUT C10 pFmA I OUT 0=失调误差 -0.025 +0.025 %FSR DAC Output =0测试模拟输入增益误差 -5.0 +5.0 %FSR FSR =17.62mA 电压参考范围输出阻抗,REF V (内部和外部) 1.12 1.235 1.35 V数字电源电流 3.4 9 mA Z CLK MH f 50=数字电源电流 10.5 15 mAZ CLK MH f 140=数字电源电流 18 25 mA Z CLK MH f 240=模拟电源电流 67 72 mA Ω=560SET R 模拟电源电流 8 mAΩ=4933SET R功耗节能电流 2.1 5.0 mA PSA VE =Low,数字和控制输入为DD V电源抑制比 0.1 0.5 %%3.3V 动态参数(uF C R V V V VAA L SET REF 10,560,235.1%,55=Ω==±+=,没有特别说明,所以的参数都是指最大温度到最小温度MIN T to MAX T ,最大温度110=J T ℃) 参数 最小值典型值最大值 单位 交流线性度无失真动态范围(SFDR )到奈奎斯特频率 单端输出Z CLK MH f 50=;Z OUT MH f 00.1= 67 dBc Z CLK MH f 50=;Z OUT MH f 51.2= 67 dBc Z CLK MH f 50=;Z OUT MH f 04.5= 63 dBc Z CLK MH f 50=;Z OUT MH f 2.20= 55 dBc Z CLK MH f 100=;Z OUT MH f 51.2= 62 dBc Z CLK MH f 100=;Z OUT MH f 04.5= 60 dBc Z CLK MH f 100=;Z OUT MH f 2.20= 54 dBc Z CLK MH f 100=;Z OUT MH f 4.40= 48 dBc Z CLK MH f 140=;Z OUT MH f 51.2= 57 dBc Z CLK MH f 140=;Z OUT MH f 04.5= 58 dBc Z CLK MH f 140=;Z OUT MH f 2.20= 52 dBc Z CLK MH f 140=;Z OUT MH f 4.40=41 dBc 双端输出Z CLK MH f 50=;Z OUT MH f 00.1= 70 dBc Z CLK MH f 50=;Z OUT MH f 51.2= 70 dBc Z CLK MH f 50=;Z OUT MH f 04.5=65 dBcZ CLK MH f 50=;Z OUT MH f 2.20= 54 dBc Z CLK MH f 100=;Z OUT MH f 51.2= 67 dBc Z CLK MH f 100=;Z OUT MH f 04.5= 63 dBc Z CLK MH f 100=;Z OUT MH f 2.20= 58 dBc Z CLK MH f 100=;Z OUT MH f 4.40= 52 dBc Z CLK MH f 140=;Z OUT MH f 51.2= 62 dBc Z CLK MH f 140=;Z OUT MH f 04.5= 61 dBc Z CLK MH f 140=;Z OUT MH f 2.20= 55 dBc Z CLK MH f 140=;Z OUT MH f 4.40=53 dBc 在窗内的非失真动态范围 单端输出Z CLK MH f 50=;Z OUT MH f 00.1=;1MHZ 扫宽 77 dBc Z CLK MH f 50=;Z OUT MH f 04.5=;2MHZ 扫宽 73 dBc Z CLK MH f 140=;Z OUT MH f 04.5=;4MHZ 扫宽64 dBc 双端输出Z CLK MH f 50=;Z OUT MH f 00.1=;1MHZ 扫宽 74 dBc Z CLK MH f 50=;Z OUT MH f 00.5=;2MHZ 扫宽 73 dBc Z CLK MH f 140=;Z OUT MH f 00.5=;4MHZ 扫60 dBc 整个谐波失真(THD )Z CLK MH f 50=;Z OUT MH f 00.1= 25+=A T ℃ 66 dBc Z CLK MH f 50=;Z OUT MH f 00.1=;MIN T to MAX T 65 dBc Z CLK MH f 50=;Z OUT MH f 00.2=64dBcZ CLK MH f 100=;Z OUT MH f 00.2= 64 dBc Z CLK MH f 140=;Z OUT MH f 00.2=55 dBcDAC 性能抖动脉冲10 pVsDACu 交扰(crosstalk ) 23 dB数据馈通 22 dB 时钟馈通 33 dB3.3V 时序图:(uF C R V V V VAA L SET REF 10,560,235.1%,55=Ω==±+=,没有特别说明,所以的参数都是指最大温度到最小温度MIN T to MAX T ,最大温度110=J T ℃) 参数值最小 典型 最大 单位 条件模拟输出延时,6t7.5 ns 模拟输出上升/下降沿时间,47t 1.0 ns 模拟输出过渡时间,58t 15 ns 模拟输出跳变69t 1 2 ns 时钟控制7CLK f 0.5 50 MHz 50MHz Grade 7CLK f 0.5 140 MHz 140MHz Grade 7CLK f0.5 240 MHz240MHz Grade数据和控制建立1t 1.5 ns 数据和控制保持2t 2.5 ns 时钟脉宽高4t 1.875 1.1 ns MHz f MAX 240= 时钟脉宽高5t 1.875 1.25 nsMHz f MAX 240= 时钟脉宽高4t2.85nsMHz f MAX 140=CLOCKDIGITAL INPUTS(R9~R0、G9~G0、B9~B0、SYNC 、BLACK )ANALOG OUTPUTS (IOR 、IOG 、IOB 、IOR 、IOG 、IOB )4.电路描述CS7123包含了三路10位D/A 转换器,有三个通道,毎个通道有一个10位的寄存器。

CS7123 三路10bit 高速视频DA 转换器

特点:● 240MHz的最大采样速度●三路10位D/A转换器● SFDR当时钟频率为50MHZ;输出为1MHZ时,–70dB当时钟频率为140MHZ;输出为40HMZ时,-53dB●与RS-343A/RS-170接口输出兼容●DA转换器的输出电流范围为:2mA到26mA● TTL兼容输入●内部基准参考电压为:1.23V●单电源+5V/+3.3V工作●48脚LQFP封装●低功耗(3V时最小值为30mW)●低功耗的静态模式(3V时典型值为6mW)●工业温度范围(-40C0到+85)描述:CS7123是一个三路高速、数模转换器的单片集成电路。

它包括三路高速、 10位输入的视频DA转换器、标准的TTL输入和互补输出高阻抗的模拟输出电流源。

它有三路独立的10位输入端口,可以在单电源5V下工作,也可以在单电源3.3V下工作。

CS7123还有附加的两个视频控制信号:1:复合SYNC(同步信号)2:BLANK(黑电平)CS7123也有一个待电模式。

CS7123由5VCMOS工艺制造、单片CMOS结构确保了低功耗的性能。

CS7123为48脚LQFP封装。

主要应用:数字视频系统(1600x1200@100HZ)、高分辨率的彩色图片、数字射频调制、图像处理、仪器、视频信号再现。