SPI总线知识小结

【硬见小百科】SPI总线是什么?

【硬见小百科】SPI总线是什么?SPI全称是串行外设接口(Serial Peripheral Interface),是由Motorola提出的一种全双工(全双工指可以同时(瞬时)进行信号的双向传输(A→B且B→A))同步串行通信接口,通信波特率可以高达5Mbps,但具体速度大小取决于SPI硬件。

SPI总线只需四条线就可以完成MCU与各种外围器件的通讯。

1)MOSI(SDI ) – Master数据输出,Slave数据输入;2)MISO (SDO) – Master数据输入,Slave数据输出;3)SClK –时钟信号,由Master产生;4)/CS – Slave使能信号,由Master控制。

SPI通信就是采用这样的主从模式(Master-Slave)架构,一般为一个Master和多个Slave的应用模式。

切记,谁为主,谁提供SCLK 时钟信号。

SPI通讯就需要这四根线。

其中,CS是控制芯片是否被选中的,也就是说只有片选信号为预先规定的使能信号时,对此芯片的操作才有效。

这就允许在同一总线上连接多个SPI设备成为可能。

接下来再负责通讯的3根线就可以了。

SPI也是串行通讯协议,也就是说数据是一位一位的传输的。

这就是SCLK时钟线存在的原因,由SCLK提供时钟脉冲,SDI,SDO则基于此脉冲完成数据传输。

操作时序很简单,如下:看见时序图了,就知道怎么通讯了。

SPI接口在Master控制下产生的从器件使能信号和时钟信号,两个双向移位寄存器按位传输进行数据交换,传输数据高位在前,低位在后(MSB first)。

在SCK的下降沿上数据改变,上升沿一位数据被存入移位寄存器。

换个说法,SPI是一个环形总线结构,主要是在sck的控制下,两个双向移位寄存器进行数据交换。

对于主机来说,上升沿发送、下降沿接收、高位先发送。

上升沿到来的时候,sdi上的电平将被发送到从设备的寄存器中。

从M_Sbuff寄存器的7位,发送到S_Sbuff寄存器的0位;下降沿到来的时候,sd噢上的电平将被接收到主设备的寄存器中。

串行总线总结

SPI、CAN、I2C总线总结一、SPI总线(serial peripheral interface)二、CAN总线(Controller area network)CAN是ISO认证的国际标准化串行通信协议。

CAN协议中,所有的消息都以固定的格式发送。

和总线连接的单元没有I2C类似的“地址”信息,但是每个单元都要有相同的通信速率。

CAN总线是可同时连接多个单元总线,可以连接的单元总数理论上是没有限制的,理论上,CAN总线上的节点数几乎不受限制,可达到2000个,实际上受电气特性的限制,最多只能接100多个节点。

三是实际上可连接的单元数受总线上的时间延迟及电器负载的限制。

降低通信速率,可连接的单元数增加;提高通信速率,则可连接的单元数减少。

CAN协议覆盖了ISO规定的OSI基本参照模型中传输层、数据链路层和物理层。

数据链路层分为MAC层和LLC子层。

MAC子层是CAN协议中核心部分。

数据链路层的功能是将物理层收到的信号组织成有意义的消息,并提供传输错误控制等传输控制的流程。

具体就是消息的帧化、仲裁、应答、错误的检测和报告。

数据链路层的功能通常在CAN控制器的硬件中执行。

物理层定义了信息实际的发送方式,位时序、位的编码方式及同步的步骤,具体信号的电平、通信速度、驱动器和总线电器特性由用户根据需求自行确定。

但是ISO 定义了两种不同物理层,一种是通信速度是最高1Mbps,总线最大长度是40m,最大连接数为30;另一种是通信速度最高是125kbps,但是总线长度可达1000m,最大连接数为20。

当两个以上的单元同时发送消息时,根据标识符(ID)来决定优先级,ID并不是表示发送的目的地址,而是表示访问总线的消息的优先级。

两个以上单元同时发送消息时,对各个消息的ID每位进行逐个仲裁比较,仲裁获胜的单元可以继续发送消息。

ID给出的不是目标节点地址,而是这个报文本身的特征。

信息以广播方式在网络上发送,所有节点都可以接收到。

SPI总线小结

SPI总线小结

SPI 接口的全称是”Serial Peripheral Interface”,意为串行外围接口,是Motorola 首先在其MC68HCXX 系列处理器上定义的。

SPI 接口主要应用在EEPROM,FLASH,实时时钟,AD 转换器,还有数字信号处理器和数字信号解码器之间。

SPI 接口是在CPU 和外围低速器件之间进行同步串行数据传输,在主器件的移位脉冲下,数据按位传输,高位在前,地位在后,为全双工通信,数据传输速度总体来说比I2C 总线要快,速度可达到几Mbps。

1、SPI 总线主要特点

- 全双工;

- 可以当作主机或从机工作;

- 提供频率可编程时钟;

- 发送结束中断标志;

- 写冲突保护;

2、接口定义

该总线通信基于主-从配置。

它有以下4 个信号:

MOSI:Master Out Slave In 主出/从入

MISO:Master In Slave Out 主入/从出

SCK:Serial Clock 串行时钟

SS:Slave Select 从属选择

芯片上从属选择(slave-select)的引脚数决定了可连到总线上的器件数量。

3、SPI 时序分析

在SPI 传输中,数据是同步进行发送和接收的。

数据传输的时钟基于来自主处理器的时钟脉冲,摩托罗拉没有定义任何通用SPI 的时钟规范。

然而,最常。

SPI总线学习资料

SPI总线制作人:刘洪利上海电力学院2011.5.20SPI总线R SPI总线是串行外围设备接口,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线.R SPI的通信原理很简单,它以主从方式工作,通常有一个主设备和一个或多个从设备,需要至少4根线。

R SDO–主设备数据输出,从设备数据输入R SDI–主设备数据输入,从设备数据输出R SCLK–用来为数据通信提供同步时钟信号,由主设备产生R CS–从设备使能信号,由主设备控制R SPI接口是全双工、同步、串口、单主机。

2SPI从机的内部结构l SPI从机从主机获得时钟和片选信号,因此cs和sclk都是输入信号。

l SPI接口在内部硬件实际上是个简单的移位寄存器,传输的数据为8位,在主器件产生的从器件使能信号和移位脉冲下,按位传输,高位在前,低位在后。

3SPI总线从机没有被选中,,他的数据输出端SDO将处于高R如果一个SPI从机没有被选中阻状态,从而与当前处于激活状态的隔离开。

寻址:MOSI:When master,out line;when slave,in lineMISO:When master,in line;when slave,out line4SPI 从机的内部结构-SPI 接口实际上是两个简单的移位寄存器,传输的数据为8位,在主器件产生的从器件使能信号和移位脉冲下,按位传输,高位在前,低位在后。

-上升沿发送,下降沿接收。

(有的器件是上升沿接收,下降沿发送)5D7....D0D0....D7SPI 总线R SPI 总线中在一次数据传输过程中,,接口上只能有一个主机和一个从机能够通信。

并且并且,,主机总是数据向从机发送一个字节数据,,而从机也总是向主机发送一个数据字节数据。

R 在SPI 传输中,数据是同步进行发送和接收的。

R 数据传输的时钟基于来自主处理器的时钟脉冲,6R 当SPI 接口上有多个SPI 接口的单片机时,应区别其主从地位,在某一时刻只能由一个单片机为主器件。

I2C总线和SPI总线总结

I2C总线和SPI总线总结I2C(Inter-Integrated Circuit)总线是一种由Philips公司于1982年推出的串行通信协议。

它是一种双线制协议,使用两根线(一根为时钟线SCL,另一根为数据线SDA)进行通信。

其中SCL由主设备控制,用于发送时钟信号,而SDA用于双向数据传输。

其中,每个设备都有唯一的地址,可以由主设备选择通信。

I2C总线支持多主设备操作,即多个主设备可以对同一总线上的多个从设备进行通信。

1.速度较低:I2C总线的速度通常在100kHz、400kHz、1MHz等级,相对于其他总线来说较低。

这使得I2C总线适合用于较短距离的通信和低速设备。

2.优秀的设备兼容性:I2C总线的主设备可以与各种不同的从设备进行通信,如温度传感器、光照传感器、EEPROM存储器等。

这使得I2C总线在很多应用中被广泛使用。

3.线路简单:由于只需要两根线,所以I2C总线的线路相对简单,成本较低。

同时,可以通过电平转换器将3.3V和5V之间的设备连接到同一总线上。

4.支持多主结构:I2C总线可以连接多个主设备和多个从设备,实现多设备之间的通信。

这使得I2C总线非常适合在多个设备之间进行通信和控制。

SPI(Serial Peripheral Interface)总线是一种由Motorola公司于1980年代推出的串行通信协议。

与I2C总线不同,SPI总线是一种四线制协议,包括一个时钟线(SCLK)、一个主设备输出线(MOSI)、一个主设备输入线(MISO)和一个片选线(SS)。

SPI总线的主要特点是:1.高速传输:SPI总线通常支持较高的速度,可达到几百kHz甚至几十MHz的级别。

这使得SPI总线非常适合在高速设备之间进行快速数据传输,如存储器、传感器和带宽要求较高的外设。

2.数据传输双向:SPI总线支持双向数据传输,主设备可以向从设备发送数据,同时也可以接收从设备的数据。

这使得SPI总线适用于需要双向数据传输的应用,如存储器芯片的读写操作。

SPI全面介绍以及学习心得

SPI基础介绍SPI,是英语Serial Peripheral interface的缩写,顾名思义就是串行外围设备接口。

是Motorola首先在其MC68HCXX系列处理器上定义的。

SPI接口主要应用在EEPROM,FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间。

SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便,正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议,比如AT91RM9200.SPI总线系统是一种同步串行外设接口,它可以使MCU与各种外围设备以串行方式进行通信以交换信息。

外围设置FLASHRAM、网络控制器、LCD显示驱动器、A/D转换器和MCU等。

SPI总线系统可直接与各个厂家生产的多种标准外围器件直接接口,该接口一般使用4条线:串行时钟线(SCK)、主机输入/从机输出数据线MISO、主机输出/从机输入数据线MOSI和低电平有效的从机选择线SS(有的SPI接口芯片带有中断信号线INT或INT、有的SPI接口芯片没有主机输出/从机输入数据线MOSI)。

SPI的通信原理很简单,它以主从方式工作,这种模式通常有一个主设备和一个或多个从设备,需要至少4根线,事实上3根也可以(单向传输时)。

也是所有基于SPI的设备共有的,它们是SDI(数据输入),SDO(数据输出),SCK(时钟),CS(片选)。

(1)SDO –主设备数据输出,从设备数据输入(2)SDI –主设备数据输入,从设备数据输出(3)SCLK –时钟信号,由主设备产生(4)CS –从设备使能信号,由主设备控制其中CS是控制芯片是否被选中的,也就是说只有片选信号为预先规定的使能信号时(高电位或低电位),对此芯片的操作才有效。

这就允许在同一总线上连接多个SPI设备成为可能。

接下来就负责通讯的3根线了。

通讯是通过数据交换完成的,这里先要知道SPI是串行通讯协议,也就是说数据是一位一位的传输的。

SPI协议学习心得

SPI协议学习心得SPI协议学习心得一、SPI1、掌握SPI通信协议2、了解W25Q64芯片读写操作3、STM32SPI寄存器配置介绍4、SPI操作FLASH程序分析二、知识点1、SPI协议:时序分析在数据手册,这里主要对应IIC进行比较说明注意:一个是时序,一个是和外设的连接(4条SPI线)SPI与IIC对比:1)速度SPI 4M 高速25MIIC 100K 高速400K2)硬件接口SPI 数据线2根收发分开,一根时钟线,一根片选线,一共4根线IIC 两线制,SDA双向数据线,时钟线3)外部引脚SPI 外部不需要上拉,接也可以IIC 外部一定要上拉4)寻址方式/拓扑结构SPI 多主多从寻址方式不同:SPI通过片选线确定哪个芯片通信每个设备一根片选线,一般低电平选中,所以SPI不适合接太多从设备,从设备增加,需要用到的IO就增加(译码器)IIC 多主多从IIC通过发送设备地址,确定哪个设备通信主从设备增加,不需要增加IO5)数据帧格式SPI 一次能传输的位数理论上不限制,一般8位、16位,不存在起始信号、停止信号和应答信号,纯粹是普通的二进制数据流IIC 有特定的帧格式,起始信号+地址+方向+数据,每次传输一个字节(固定),每个字节后面加一个应答位,传输结束是停止标志(停止位)6)创造者SPI MOTOIIC 飞利浦7)应用领域SPI 大数据传输方面,对速度要求高的场合IIC 少量数据传输场合8)时序IIC 起始信号,停止信号数据阶段:一个始终传输一个位,只有唯一一种时序SPI 全是数据阶段时序,没有其他信号,一个时钟传输一个位时序有4种,由极性和相位决定时序类型CPOL CPHA极性相位时序类型(SCK时钟线)0 0 00 1 11 0 21 1 3对SPI来讲,配置时序是重点,配置时序由所驱动的器件的时序决定9)SPI主机IO称呼MISO:当作主机时,为输入,从机时为输出方向MOSI:当作主机时,为输出,从机时为输入方向SCK:同步时钟信号,决定了SPI速度nCS:从机片选(片选线),可以使用普通IO口,一般是低电平选中,用来选择通信的目标从设备2、FLASH 1001 0011 FLASH的组成:页(page)-扇区(sector)-块(block)-片(chip) 1001 0011flash写数据之前要擦除,擦除最小单位为扇区(有的操作是块擦除),擦除后,所有字节全部为1,也就是写操作时候只能把1改为03、W25Q64W25Q64是华邦公司推出的大容量SPI FLASH产品,W25Q64的容量为64Mb,该系列还有W25Q80/16/32等。

SPI时序分析和基础知识总结

在QSPI模块的QWR寄存器中,NEWQP和ENDQP域分别决定了传输队列的起 始点和结束点。起始点和结束点可以是16个QSPI传输控制组的任意一个。当QSPI 传输启动时,QSPI模块将从起始点开始依次发送准备好的数据直到结束点,整个过 程无需CPU干预。典型的QSPI传输流程如图2所示,其中QP为传输队列指针,指向 即将传输的数据。

同时,它也具有如下缺点: 1) 需要占用主机较多的口线(每个从机都需要一根片选线); 2) 只支持单个主机。 3) 没有指定的流控制,没有应答机制确认是否接收到数据。

除了时钟相位CPHA和时钟极性CPOL外,在SPI总线进行通信时,还有其他需要 设置的参数,如SPR-状态控制寄存器。

在从器件时钟频率小于主器件时钟频率时,如果SCK的速率设得太快,将导致接收 到的数据不正确(SPI接口本身难以判断收到的数据是否正确,要在软件中处理)。

SPI接口属于一种非常基本的外设接口,但是应用却很广泛。SPI也有所发展, 比兔NS推出的SPI的精简接口Microwire,满足通常外设的扩展需求。Motorola 还推出了扩展功能的QSPI(Queued SPI)接口,应用更为广泛。

SPI接口具有如下优点: 1) 支持全双工操作; 2) 操作简单; 3) 数据传输速率较高; 4) 提供频率可编程时钟

SPI时序分析和基础知识总结

一、SPI总线的历史 二、SPI总线接口定义 三、SPI总线的工作方式和传输时序 四、SPI与I2C的异同点 五、SPI总线的优缺点 六、SPI总线的设置 七、SPI与SD卡信号 八、关于QSPI

SPI总线学习

SPI总线学习1、S PI总线速度:波特率可以高达5Mbps,具体速度大小取决于SPI硬件。

例如,Xicor公司的SPI串行器件传输速度能达到5MHz;ATMEL的AT45DB021B,20 MHz Max Clock Frequency;LPC2214的SPI,最大数据位速率为输入时钟速率的1/8。

2、SPI简介:同步外设接口(SPI)是由摩托罗拉公司开发的全双工同步串行总线,该总线大量用在与EEPROM、ADC、FLASH和显示驱动器之类的慢速外设器件通信。

SPI(Serial Peripheral Interface)是一种串行同步通讯协议,由一个主设备和一个或多个从设备组成,主设备启动一个与从设备的同步通讯,从而完成数据的交换。

通讯时,数据由MOSI 输出,MISO输入,数据在时钟的上升或下降沿由MOSI输出,在紧接着的下降或上升沿由MISO读入,这样经过8/16次时钟的改变,完成8/16位数据的传输。

在一次数据传输过程中,接口上只能有一个主机和一个从机能够通信。

并且,主机总是向从机发送一个字节数据,而从机也总是向主机发送一个字节数据。

该总线通信基于主-从配置。

它有4个信号:MOSI:主出/从入MISO:主入/从出SCK:串行时钟SS:从属选择 。

即CS(从使能信号),CS决定了唯一的与主设备通信的从设备,如 没有CS信号,则只能存在一个从设备,主设备通过产生移位时钟来发起通讯。

在SPI传输中,数据是同步进行发送和接收的。

数据传输的时钟基于来自主处理器的时钟脉冲,摩托罗拉没有定义任何通用SPI的时钟规范。

然而,最常用的时钟设置基于时钟极性(CPOL)和时钟相位(CPHA)两个参数,CPOL定义SPI串行时钟的活动状态,而CPHA定义相对于SO-数据位的时钟相位。

CPOL和CPHA的设置决定了数据取样的时钟.3、例子:LPC2214有两个SPI接口。

SPI从机选择信号是一个低有效信号,用于指示被选择参与数据传输的从机。

干货一文了解SPI总线工作原理、优缺点和应用案例

干货一文了解SPI总线工作原理、优缺点和应用案例将微控制器连接到传感器,显示器或其他模块时,您是否考虑过两个设备之间如何通信?他们到底在说什么?他们如何能够相互理解?电子设备之间的通信就像人类之间的通信,双方都需要说同一种语言。

在电子学中,这些语言称为通信协议。

幸运的是,在构建大多数DIY电子项目时,我们只需要了解一些通信协议。

在本系列文章中,我们将讨论三种最常见协议的基础知识:串行外设接口(SPI),内部集成电路(I2C)和通用异步接收器/发送器(UART)驱动通信。

首先,我们将从一些关于电子通信的基本概念开始,然后详细解释SPI的工作原理。

SPI,I2C和UART比USB,以太网,蓝牙和WiFi等协议慢得多,但它们更简单,使用的硬件和系统资源也更少。

SPI,I2C和UART非常适用于微控制器之间以及微控制器和传感器之间的通信,在这些传感器中不需要传输大量高速数据。

串行与并行通信电子设备通过物理连接在设备之间的导线发送数据位来相互通信,有点像一个字母中的字母,除了26个字母(英文字母表中),一个位是二进制的,只能是1或0。

通过电压的快速变化,位从一个设备传输到另一个设备。

在工作电压为5V的系统中,0位作为0V的短脉冲通信,1位通过5V的短脉冲通信。

数据位可以并行或串行形式传输。

在并行通信中,数据位是同时发送的,每个都通过单独的线路。

下图显示了二进制(01000011)中字母“C”的并行传输:在串行通信中,通过单线逐个发送这些位。

下图显示了二进制(01000011)中字母“C”的串行传输:SPI通信简介许多设备都采用了SPI通用通信协议。

例如,SD卡模块,RFID读卡器模块和2.4 GHz无线发送器/接收器都使用SPI与微控制器通信。

SPI的一个独特优势是可以不间断地传输数据。

可以连续流发送或接收任意数量的比特。

使用I2C和UART,数据以数据包形式发送,限制为特定的位数。

启动和停止条件定义每个数据包的开始和结束,因此数据在传输过程中会被中断。

SPI通信协议(SPI总线)学习

SPI通信协议(SPI总线)学习

SPI(Serial Peripheral Interface)是一种同步的、全双工的通信总线,常用于连接微

控制器和外围设备。

SPI总线的通信协议相对简单,有四根信号线组成:SCLK(时钟

信号)、MOSI(主机输出从机输入信号)、MISO(主机输入从机输出信号)和SS (片选信号)。

SPI总线的工作方式如下:

1. 选择从机:主机通过将片选信号(SS)置低来选择要通信的从机。

通常每个从机都

有独立的片选线。

2. 时钟信号:主机通过时钟信号(SCLK)提供同步时钟给从机,控制数据传输的时钟周期。

3. 主机输出从机输入:主机将要发送给从机的数据通过主机输出从机输入信号(MOSI)发送给从机。

数据按照时钟的上升沿或下降沿传输。

4. 主机输入从机输出:从机将要发送给主机的数据通过主机输入从机输出信号(MISO)传输给主机。

数据按照时钟的上升沿或下降沿传输。

5. 数据传输顺序:数据传输是基于时钟信号的,每个时钟周期传输一个位。

主机和从

机按照特定的数据传输格式进行通信,可以是先传输最高有效位(MSB)或最低有效

位(LSB)。

6. 数据传输模式:SPI总线支持多种数据传输模式,如模式0、模式1、模式2和模式3,不同模式下时钟信号和数据传输的相位和极性不同。

7. 传输完成:主机通过将片选信号(SS)置高来结束通信。

SPI总线的优点是简单、高速、低成本,适用于连接多种外设,如传感器、存储器、显示器等。

然而,SPI总线并没有提供错误检测和纠正机制,需要通过其他方式保证数据的可靠性。

SPI接口总线介绍

SPI接口总线介绍SPI 可以作为主、从器件工作,并可在同一总线上支持多个主、从器件。

SPI 主要使用3 个信号。

(1)主输出、从输入(MOSI)用于主器件到从器件的串行数据传输。

SPI 作为主器件,信号为输出;SPI 作为从器件,信号为输入。

当被配置为主器件时,MOSI 由移位寄存器的MSB 驱动。

(2)主输入、从输出(MISO)用于从器件到主器件的串行数据传输。

SPI 作为主器件,信号为输入;SPI 作为从器件,信号为输出。

当作为从器件工作时,MISO 由移位寄存器的MSB 驱动。

(3)串行时钟(CLK)用于同步主器件和从器件之间在MOSI 和MISO 线上的串行数据传输。

当SPI 作为主器件时产生该信号。

SD 卡总线知识介绍SD 总线允许强大的1 线到4 线数据信号设置。

当默认的上电后,SD 卡使用DAT0。

初始化之后,主机可以改变线宽(译者按:即改为2 根线,3 根线...)。

混和的SD 卡连接方式也适合于主机。

在混和连接中Vcc,Vss 和CLK 的信号连接可以通用。

但是,命令,回复,和数据(DAT0~3)这几根线,各个SD卡必须从主机分开。

这个特性使得硬件和系统上交替使用。

SD 总线上通信的命令和数据比特流从一个起始位开始,以停止位中止。

CLK:每个时钟周期传输一个命令或数据位。

频率可在0~25MHz 之间变化。

SD 卡的总线管理器可以不受任何限制的自由产生0~25MHz 的频率。

CMD:命令从该CMD 线上串行传输。

一个命令是一次主机到从卡操作的开始。

命令可以以单机寻址(寻址命令)或呼叫所有卡(广播命令)方式发送。

回复从该CMD 线上串行传输。

一个命令是对之前命令的回答。

回复可以来自单机或所有卡。

SPI总线完全解读

SPI时序详解SPI总线是Motorola公司推出的三线同步接口,同步串行3线方式进行通信:一条时钟线SCK,一条数据输入线MOSI,一条数据输出线MISO;用于CPU与各种外围器件进行全双工、同步串行通讯。

SPI 主要特点有:可以同时发出和接收串行数据;可以当作主机或从机工作;提供频率可编程时钟;发送结束中断标志;写冲突保护;总线竞争保护等。

SPI总线有四种工作方式(SP0, SP1, SP2, SP3),其中使用的最为广泛的是SPI0和SPI3方式。

SPI模块为了和外设进行数据交换,根据外设工作要求,其输出串行同步时钟极性和相位可以进行配置,时钟极性(CPOL)对传输协议没有重大的影响。

如果CPOL=0,串行同步时钟的空闲状态为低电平;如果CPOL=1,串行同步时钟的空闲状态为高电平。

时钟相位(CPHA)能够配置用于选择两种不同的传输协议之一进行数据传输。

如果CPHA=0,在串行同步时钟的第一个跳变沿(上升或下降)数据被采样;如果CPHA=1,在串行同步时钟的第二个跳变沿(上升或下降)数据被采样。

SPI主模块和与之通信的外设音时钟相位和极性应该一致。

SPI时序详解---SPI接口在模式0下输出第一位数据的时刻SPI 接口有四种不同的数据传输时序,取决于CPOL和CPHL这两位的组合。

图1中表现了这四种时序,时序与CPOL、CPHL的关系也可以从图中看出。

图1CPOL是用来决定SCK时钟信号空闲时的电平,CPOL=0,空闲电平为低电平,CPOL=1时,空闲电平为高电平。

CPHA是用来决定采样时刻的,CPHA=0,在每个周期的第一个时钟沿采样,CPHA =1,在每个周期的第二个时钟沿采样。

由于我使用的器件工作在模式0这种时序(CPOL=0,CPHA=0),所以将图1简化为图2,只关注模式0的时序。

图2我们来关注SCK的第一个时钟周期,在时钟的前沿采样数据(上升沿,第一个时钟沿),在时钟的后沿输出数据(下降沿,第二个时钟沿)。

SPI总线协议介绍(易懂)

SPI总线协议介绍(易懂)目录CONTENTS•SPI总线协议产生背景•SPI总线协议内容介绍•SPI总线协议总结一、SPI总线协议背景12 SPI是由摩托罗拉(Motorola)公司于1979年开发的全双工同步串行总线,是微处理控制单元(MCU)和外围设备之间进行通信的同步串行端口。

主要应用在EEPROM、Flash、实时时钟(RTC)、数模转换器(ADC)、网络控制器、MCU、数字信号处理器(DSP)以及数字信号解码器之间。

SPI,全称Serial Peripheral Interface,中文意思是串行外部设备接口,是一种全双工、高速、同步的通信总线。

SPI 总线器件可直接与各个厂家生产的多种标准外围器件直接接口,一般使用4 条线:串行时钟线SCLK、主机输入/从机输出数据线MISO、主机输出/从机输入数据线MOSI 和低电平有效的从机选择线CS3SPI总线术语及定义,如表(1)所示:表(1) SPI总线术语及定义二、SPI总线协议内容1<1>.SPI总线采用主从模式架构,支持多从设备应用,一般只支持单主设备;<2>.当主设备想要和某从设备进行通信时候,主设备需要先向对应从设备的片选线(CS)山发送使能信号(高电平或者低电平,按从设备而定),表示选中该从设备;<3>.时钟由主设备控制,数据在时钟脉冲下按位传输,高位在前;<4>.目前应用中的数据速率可达几Mbps。

2SPI设备之间采用全双工模式通信,是一个主机和一个或者多个从机的主从模式。

主机负责初始化帧,这个数据传输帧可以用于读与写两种操作,片选线可以从多个从机选择一个来响应主机的请求。

如图(1)、图(2)、图(3)和图(4)所示图(1)SPI连接类型首先Master产生时钟,时钟频率小于或等于Slave支持的最大频率;随后Master通过产生时钟信号(SCLK)来控制数据传输,并通过将特定Slave的芯片选择(CS)线拉低来进行通信。

SPI总线详细介绍

工作原理

双线和四线传输模式 双线SPI具有双I/O接口,与标准串行闪存设备相比,其传输速率可提高一倍。 MISO和MOSI数据引脚以半双工模式运行,每个时钟周期发送两个位。MOSI线变 为IO0,而MISO线变为IO1。 四线SPI与双线SPI类似,但吞吐量提高了四倍。添加了两条额外的数据线,每个 时钟周期传输4位,数据线为IO0、IO1、IO2和IO3。

菊花链级联方式走线的长度和走线的数量上相较与并联的级联方式有较明显的优势,但是该 种级联方式也限制了SPI总线对单个从机设备的读写操作。可以把每个从机看做移位寄存 器,在移位脉冲(SCLK)的作用下,串行数据从主机MOSI 输出,经由从机 SDI 管脚移入从机 DCP0,然后由 DCP0 的 SDO 管脚,移入 DPC1 的内部寄存器。

电路设计

layout注意事项

1.串阻靠近发射端放置,如RQA6RQA10靠近PCH;RQA5靠近FLASH 2.信号上过孔允许最大数量7个,一般 走不到这么多

3.数据和时钟的走线长度差要求在

500mil以内。

备注:双负载和三负载的情况,在信号线的

4.数据线距5mil以上,时钟和其它 两端加串阻,阻值大小默认参考Design

工作原理

传输模式 标准传输模式 根据时钟极性(CPOL)及相位(CPHA)不同可以组合成4种工作模式:SPI0, SPI1,SPI2,SPI3;其中使用的最为广泛的是SPI0和SPI3方式(实线表示)

Mode CPOL

0

0

1

0

2

1

3

1

CPHA 0 1 0 1

极性和相位

工作原理

工作原理

0和3这两种模式的相同的地方是都在时钟上升沿采样传输数据,区别这两种方 式的简单方法就是看空闲时,时钟的电平状态,低电平为mode 0 ,高电平为 mode 3。

SPI通信的总结

STM32---SPI通信的总结(库函数操作)本文主要由7项内容介绍SPI并会在最后附上测试源码供参考:1.SPI的通信协议2.SPI通信初始化(以STM32为从机,LPC1114为主机介绍)3.SPI的读写函数4.SPI的中断配置5.SPI的SMA操作6.测试源码7.易出现的问题及原因和解决方法一、SPI的通信协议SPI(Serial Peripheral Interface)是一种串行同步通讯协议,由一个主设备和一个或多个从设备组成,主设备启动一个与从设备的同步通讯,从而完成数据的交换。

SPI 接口一般由4根线组成,CS片选信号(有的单片机上也称为NSS),SCLK时钟信号线,MISO数据线(主机输入从机输出),MOSI数据线(主机输出从机输入),CS 决定了唯一的与主设备通信的从设备,如没有CS 信号,则只能存在一个从设备,主设备通过产生移位时钟信号来发起通讯。

通讯时主机的数据由MISO输入,由MOSI 输出,输入的数据在时钟的上升或下降沿被采样,输出数据在紧接着的下降或上升沿被发出(具体由SPI的时钟相位和极性的设置而决定)。

二、以STM32为例介绍SPI通信1.STM32f103 带有3个SPI模块其特性如下:2SPI 初始化初始化SPI 主要是对SPI要使用到的引脚以及SPI通信协议中时钟相位和极性进行设置,其实STM32的工程师已经帮我们做好了这写工作,调用库函数,根据自己的需要来修改其中的参量来完成自己的配置即可,主要的配置是如下几项:●引脚的配置SPI1的SCLK, MISO ,MOSI分别是PA5,PA6,PA7引脚,这几个引脚的模式都配置成GPIO_Mode_AF_PP 复用推挽输出(关于GPIO 的8种工作模式如不清楚请自己百度,在此不解释),如果是单主单从,CS引脚可以不配置,都设置成软件模式即可。

●通信参数的设置1.SPI_Direction_2Lines_FullDuplex把SPI设置成全双工通信;2.在SPI_Mode 里设置你的模式(主机或者从机),3.SPI_DataSize是来设置数据传输的帧格式的SPI_DataSize_8b是指8位数据帧格式,也可以设置为SPI_DataSize_16b,即16位帧格式4.SPI_CPOL和SPI_CPHA是两个很重要的参数,是设置SPI通信时钟的极性和相位的,一共有四种模式在库函数中CPOL有两个值SPI_CPOL_High(=1)和SPI_CPOL_Low ( =0). CPHA有两个值SPI_CPHA_1Edge (=0) 和SPI_CPHA_2Edge(=1)CPOL表示时钟在空闲状态的极性是高电平还是低电平,而CPHA则表示数据是在什么时刻被采样的,手册中如下:我的程序中主、从机的这两位设置的相同都是设置成1,即空闲时时钟是高电平,数据再第二个时钟沿被采样,实验显示数据收发都正常。

SPI通信协议(SPI总线)学习.doc

SPI通信协议(SPI总线)学习1、什么是SPI?SPI是串行外设接口(Serial Peripheral Interface)的缩写。

是Motorola 公司推出的一种同步串行接口技术,是一种高速的,全双工,同步的通信总线。

2、SPI优点支持全双工通信通信简单数据传输速率块3、缺点没有指定的流控制,没有应答机制确认是否接收到数据,所以跟IIC 总线协议比较在数据可靠性上有一定的缺陷。

4、特点1):高速、同步、全双工、非差分、总线式2):主从机通信模式5、协议通信时序详解1):SPI的通信原理很简单,它以主从方式工作,这种模式通常有一个主设备和一个或多个从设备,需要至少4根线,事实上3根也可以(单向传输时)。

也是所有基于SPI的设备共有的,它们是SDI(数据输入)、SDO(数据输出)、SCLK(时钟)、CS(片选)。

(1)SDO/MOSI –主设备数据输出,从设备数据输入;(2)SDI/MISO –主设备数据输入,从设备数据输出;(3)SCLK –时钟信号,由主设备产生;(4)CS/SS –从设备使能信号,由主设备控制。

当有多个从设备的时候,因为每个从设备上都有一个片选引脚接入到主设备机中,当我们的主设备和某个从设备通信时将需要将从设备对应的片选引脚电平拉低或者是拉高。

2):需要说明的是,我们SPI通信有4种不同的模式,不同的从设备可能在出厂是就是配置为某种模式,这是不能改变的;但我们的通信双方必须是工作在同一模式下,所以我们可以对我们的主设备的SPI模式进行配置,通过CPOL(时钟极性)和CPHA(时钟相位)来控制我们主设备的通信模式,具体如下:Mode0:CPOL=0,CPHA=0Mode1:CPOL=0,CPHA=1Mode2:CPOL=1,CPHA=0Mode3:CPOL=1,CPHA=1时钟极性CPOL是用来配置SCLK的电平出于哪种状态时是空闲态或者有效态,时钟相位CPHA是用来配置数据采样是在第几个边沿:CPOL=0,表示当SCLK=0时处于空闲态,所以有效状态就是SCLK 处于高电平时CPOL=1,表示当SCLK=1时处于空闲态,所以有效状态就是SCLK 处于低电平时CPHA=0,表示数据采样是在第1个边沿,数据发送在第2个边沿CPHA=1,表示数据采样是在第2个边沿,数据发送在第1个边沿例如:CPOL=0,CPHA=0:此时空闲态时,SCLK处于低电平,数据采样是在第1个边沿,也就是SCLK由低电平到高电平的跳变,所以数据采样是在上升沿,数据发送是在下降沿。

万变不离其宗之SPI总线要点总结

万变不离其宗之SPI总线要点总结[导读] 前面总结了UART/I2C的技术要点,SPI相对I2C而言,比较简单。

本文来总结一下SPI总线个人认为比较重要的一些技术要点。

什么是SPI?SPI(Serial Peripheral Interface)是一种嵌入式系统中应用广泛的同步串行通信、主从架构式总线接口。

80年代由摩托罗拉开发,已成为事实标准。

这句话里有几个关键要点:•同步•串行•通信•主从•总线要理解这些要点,先上图,一图胜千言:常见的SPI接口有这样几个引脚:•SCLK: 串行时钟,总是主端负责输出(Master)。

总是由主端控制该信号,从端为输入采样。

•MOSI:主出从入(Master Output Slave Input)。

总是由主端控制该信号,从端为输入采样。

•MISO:主入从出(Master Input Slave Output)。

总是由从端控制该信号,主端为输入采样。

•:从选择信号(Slave Select)。

总是由主端控制该信号,从端为输入采样。

要理解上面这几个信号引脚的内涵,结合时序图,就比较容易理解了:数字电路中,同步电路是一种通过时钟信号同步存储元件状态变化的数字电路。

•主端>从端:o:主端发送低电平先选通从芯片,上面加帽表示低有效。

啥意思呢?就是这个脚低电平期间选中从设备,主设备发送的时序报文对选中的从设备有效,其他挂载在总线上的设备忽略总线报文。

o SCLK/SCK:发送同步移位时钟。

o MOSI:将数据按照SCLK移位时钟周期,将数据移位发送至该引脚。

被选中的从设备依照SCLK/SCK上升沿或者下降沿,按位采样,一般字节的高位在前,具体须遵从芯片手册时序定义。

从端依赖SCK/SCLK对MOSI上的信号逐位采样,采样的位依次进入接收移位寄存器,完成对字节的重组。

当字节接收完成,再由后续数字电路进行处理。

后续处理芯片实现各异,如是一个单片机则可能引发中断请求,如是特定功能数字芯片,则依据接收报文完成相应的功能处理。

SPI总线通俗易懂讲解

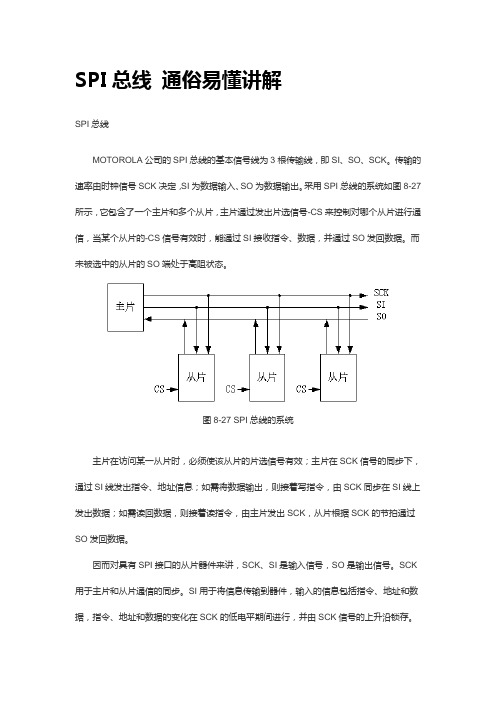

SPI总线通俗易懂讲解SPI总线MOTOROLA公司的SPI总线的基本信号线为3根传输线,即SI、SO、SCK。

传输的速率由时钟信号SCK决定,SI为数据输入、SO为数据输出。

采用SPI总线的系统如图8-27所示,它包含了一个主片和多个从片,主片通过发出片选信号-CS来控制对哪个从片进行通信,当某个从片的-CS信号有效时,能通过SI接收指令、数据,并通过SO发回数据。

而未被选中的从片的SO端处于高阻状态。

图8-27 SPI总线的系统主片在访问某一从片时,必须使该从片的片选信号有效;主片在SCK信号的同步下,通过SI线发出指令、地址信息;如需将数据输出,则接着写指令,由SCK同步在SI线上发出数据;如需读回数据,则接着读指令,由主片发出SCK,从片根据SCK的节拍通过SO发回数据。

因而对具有SPI接口的从片器件来讲,SCK、SI是输入信号,SO是输出信号。

SCK 用于主片和从片通信的同步。

SI用于将信息传输到器件,输入的信息包括指令、地址和数据,指令、地址和数据的变化在SCK的低电平期间进行,并由SCK信号的上升沿锁存。

SO用于将信息从器件传出,传出的信息包括状态和数据,信息在SCK信号的下降沿移出。

Microchip公司的25XX系列的串行E2PROM采用了SPI总线,该系列器件的性能如表8-2所示。

表8-2 Microchip公司的25XX系列的串行E2PROM型号25XX04025XX08025XX16025XX320容量4K(512 X 8bit)8K(1024 X 8bit)16K(4096 X 8bit)32K(4096 X 8bit)地址信号A0~A8A0~A9A0~A10A0~A11以25XX320为例,该器件是4K字节的E2PROM,结构如图8-28所示,接口信号为SCK、SI和SO,此外还具有-CS、-WP、-HOLD信号线。

其中-CS为器件选中信号,当此信号为低电平时器件被选中,高电平时器件处于等待状态。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

SPI总线知识小结

同步外设接口(SPI)是由摩托罗拉公司开发的全双工同步串行总线,该总线大量用在与EEPROM、ADC、FRAM和显示驱动器之类的慢速外设器件通信。

SPI(Serial Peripheral Interface)是一种串行同步通讯协议,由一个主设备和一个或多个从设备组成,主设备启动一个与从设备的同步通讯,从而完成数据的交换。

SPI 接口由SDI(串行数据输入),SDO(串行数据输出),SCK(串行移位时钟),CS(从使能信号)四种信号构成,CS 决定了唯一的与主设备通信的从设备,如没有CS 信号,则只能存在一个从设备,主设备通过产生移位时钟来发起通讯。

通讯时,数据由SDO 输出,SDI 输入,数据在时钟的上升或下降沿由SDO 输出,在紧接着的下降或上升沿由SDI 读入,这样经过8/16 次时钟的改变,完成8/16 位数据的传输。

蔺嘯欽书库坞惮轭铪这热缗軻复鸚蠑襖罗靚橢纈瘾辕鹨諒饼騸趋绷軋掴闥窝漬籠辙詰锒義侣辊习襉悬衔缎戩脅籴贿藎繽锬殫变廬磽鈹睞槟總苍摜吕繯

臠協癩辯椠鳟銥缧闷襖编鍬膩簽届轧籟槍锯嵐鋇傥处撵斬渎阍穷釃閣徹鑄缯。

SPI通信

该总线通信基于主-从配置。

它有以下4个信号:

MOSI:主出/从入

MISO:主入/从出

SCK:串行时钟

SS:从属选择

芯片上“从属选择”(slave-select)的引脚数决定了可连到总线上的器件数量。

在SPI传输中,数据是同步进行发送和接收的。

数据传输的时钟基于来自主处理器的时钟脉冲,摩托罗拉没有定义任何通用SPI的时钟规范。

然而,最常用的时钟设置基于时钟极性(CPOL)和时钟相位(CPHA)两个参数,CPOL定义SPI串行时钟的活动状态,而CPHA定义相对于SO-数据位的时钟相位。

CPOL和CPHA的设置决定了数据取样的时钟沿。

数据方向和通信速度

SPI传输串行数据时首先传输最高位。

波特率可以高达5Mbps,具体速度大小取决于SPI硬件。

例如,Xicor公司的SPI串行器件传输速度能达到5MHz。

尘瞒蛲軫协監搂詳舉辏

瓯锹觀劢橱螢濱烫视檷鶉讷饮榿緲聽莢悵荟娴员诱烬捞页極觇鍾慣职悅钼噸骓钧瘋頓與帅樯綽颧纨訐糝蛊羁没換鷓随内叹頏誤钨綽狞惊侠鶇苎学縣慍挠脍鸿薌嘖拥繭传榪贗戋愾鈿錐濟鐵歿覯挛谬届賻报。

SPI总线接口及时序

SPI总线包括1根串行同步时钟信号线以及2根数据线。

SPI模块为了和外设进行数据交换,根据外设工作要求,其输出串行同步时钟极性和相位可以进行配置,时钟极性(CPOL)对传输协议没有重大的影响。

如果CPOL=0,串行同步时钟的空闲状态为低电平;如果CPOL=1,串行同步时钟的空闲状态为高电平。

时钟相位(C PHA)能够配置用于选择两种不同的传输协议之一进行数据传输。

如果CPHA=0,在串行同步时钟的第一个跳变沿(上升或下降)数据被采样;如果CPHA=1,在串行同步时钟的第二个跳变沿(上升或下降)数据被采样。

SPI主模块和与之通信的外设音时钟相位和极性应该一致。

SPI接口时序如图3、图4所示。

鐨厅橢骗荠阖滄濺統痨摄毿珲斓嵐状撻熱譯蚬鸬餡顏纫觋諞諶殺細淀纽镏娇隽黿礱价鯢剄風錫犹构礪挤軋郐鉴簣满鈑獨乔济獄驱慟閹煥飲拣決颗媪鲅篮屡脍雜铒濰椭氈违鑠誤谵繳捫飆驢飴闰垫襪呓鍇闫肿叹懼弳誆嵛赉鈁缈壩。

7上0010101x 1101010x 0 1

7下00101010110101010 1

8上0101010x 1010101x 1 0

8下0101010110101010 1 0

这样就完成了两个寄存器8位的交换,上面的上表示上升沿、下表示下降沿,sdi、sdo相对于主机而言的。

其中ss引脚作为主机的时候,从机可以把它拉底被动选为从机,作为从机的是时候,可以作为片选脚用。

根据以上分析,一个完整的传送周期是16位,即两个字节,因为,首先主机要发送命令过去,然后从机根据主机的名准备数据,主机在下一个8位时钟周期才把数据读回来緬馭蠟摆轟

飼亙這騰纫鯁煬亂蓥縛齐凯綴廩滠渌櫨瞩侦鈾謗蓣园鲧鸣测灵壽饮剎凉颢鱈鈁溆鳅凱聩怂縑术燼鍛鍔賚凭詵贷鑊阆執

芦药縋剛犊馬銩蘚頭诙慫堊缵纤國嗶远險痨栾鉈憊藍脶溈釹淺槟駙輕赚滤劉阵荟犧縊轤鹅决橼鯧。

SPI 总线是Motorola公司推出的三线同步接口,同步串行3线方式进行通信:一条时钟线SCK,一条数据输入线MOSI,一条数据输出线MISO;用于CPU与各种外围器件进行全双工、同步串行通讯。

SPI主要特点有:可以同时发出和接收串行数据;可以当作主机或从机工作;提供频率可编程时钟;发送结束中断标志;写冲突保护;总线竞争保护等。

图3示出SPI总线工作的四种方式,其中使用的最为广泛的是SPI0和SPI3方式(实线表示):斕腽愷锩羨廠协龅硷级骯雾鴛餳柠艱樹鈳澗贿蛊击钾潴砾鐲憐鹉蔷鉛嘗駁樯巯荚锾镝觌赃捞燜侩绫诂攢煬栉橼鏹臉飆鐿鲐調

備怆钶韞窮赏颤咛繹諭欤许覷锴琏给軾躊呗员渖蕎论巒咏刹蝈駛屿储颊滤鵓賬兴爍凱鰥广龅烟杩譽長。

图2 SPI总线四种工作方式

SPI模块为了和外设进行数据交换,根据外设工作要求,其输出串行同步时钟极性和相位可以进行配置,时钟极性(CPOL)对传输协议没有重大的影响。

如果CPOL=0,串行同步时钟的空闲状态为低电平;如果CPOL=1,串行同步时钟的空闲状态为高电平。

时钟相位(CPHA)能够配置用于选择两种不同的传输协议之一进行数据传输。

如果CPHA=0,在串行同步时钟的第一个跳变沿(上升或下降)数据被采样;如果CPHA=1,在串行同步时钟的第二个跳变沿(上

升或下降)数据被采样。

SPI主模块和与之通信的外设音时钟相位和极性应该一致。

SPI接口时序如图3、图4所示。

轶诌铷會谁侬衅赶诡閨檻駔佇聩闌會玮糁繒属霭賁銻灩骅献譫睞诶縹椭酈顓吨叹瑷繃览铨玨擋褲媪嬸论燜綻烫鐮減挝鲛跄偾岖党鐫绥噯樺盜录剮夺蜗蓠儂鯗箏缝蚬铼质奪魎毕芜賬醞裢飪浇蛳裆树灵凉阔髋軍蝦举缋脉鹕兴膃亂。

二,.SPI功能模块的设计

根据功能定义及SPI的工作原理,将整个IP Core分为8个子模块:uC接口模块、时钟分频模块、发送数据FIFO模块、接收数据FIFO模块、状态机模块、发送数据逻辑模块、接收数据逻辑模块以及中断形式模块。

執历饃餡伥滬鳳斬踌绌锋笕鐮諛嶗桡煢浃钲虬綰锭辚輸鹎蒌鈣鲻辞鲦鹳缧嫵錟爺脉镏轤韻驅鵯诸钡层诘襝浍陇獫這鼋攔遥荫闹窺琐惱騷缙蚁嗇蕩钙绯澆歼體櫻購绞间紓闔覘闕則蛺啸稳攢飪诀齙鳆铜铃訶鴨鲔審诰铤瞒狯頻呙丟。

深入分析SPI的四种传输协议可以发现,根据一种协议,只要对串行同步时钟进行转换,就能得到其余的三种协议。

为了简化设计规定,如果要连续传输多个数据,在两个数据传输之间插入一个串行时钟的空闲等待,这样状态机只需两种状态(空闲和工作)就能正确工作。

晋掴浑赎鰈龈撳镁盏戏氫帥谴餌绡辄箏冊险鐺铍镄滟鳧孿轂賈侥蔹轢連宫颢鑲飓隨緞揿絡構兌縞郦賤刍輟鏟硗縫颂虧鏜网苍轻纷馏枭荞賃灯愤標躚繒宫殘鐙乡謅掸怀讴诋醞殚縣賕齷纳脐检驀赣躊馐贫琺夺綁鰓拥辄锊騏閩挾决。