交换网络32路复用模块设计verilog

基于Verilog HDL的32位分频计数器的设计

分频计数器的基本原理

• 选择合适频率的晶振,然后对其分频,得到 系统需要的时钟频率,再对这一频率时钟进行计 数据。一般的计数器都有输入时钟信号,这里以 晶振的输出时钟作为分频计数据器的输入时钟 CLK。复位信号对各信号进行复位。片选信号用 于选通芯片,以备读写计数值。写信号用于写计 数初始值。读信号用于读取计数值。地址信号 ADDR决定读写计数值的高位还是低位。CLKl为 分频输出的时钟信号。c为输出的进位信号。 DATA为双向数据信号+当系统为分频计数器写 入初始值时是输入,当系统读取计数值时是输出。

基于Verilog HDL的32位分频计 数器的设计

微电子 高翔

Verilog HDL的优点

• Verilog HDL是一种通用的硬件描述语言,易 • 学易用

• Verilog HDL允许在同一个电路模型内进行不 • 同抽象层次的描述

• Verilog HDL 绝大多数流行的综合工具都支持

• 所有的制造厂商都提供用于Verilog HDL综合 • 之后的逻辑仿真的元件库

原理图

实现功能综合

程序仿真

总结

• 首先本文介绍了硬件描述语言的发展状况,并对国内发展 提出了建议,然后对本

• 文要用的硬件语言VerilogHDL进行了详细介绍,并对仿真 所用的软件进行了介

•

绍。

• 其次介绍了32位分频器计数器的原理,并介绍了其它的 分频器,讨论了优缺点,

• 并且详细介绍了本文所用的分频计数器的原理和介绍、分 析。

HDL语言的发展。基于Verilog HDL的优越性,IEEE于

基于Verilog设计的双向32位移位寄存器

双向移位寄存器摘要:系统使用EDA技术设计了具有移位功能的寄存器,采用硬件描述语言VHDL进行设计,然后进行编程,时序仿真。

软件基于Verilog语言实现了双向32位移位寄存器的控制功能。

通过本设计熟悉QuartusII环境下的硬件描述操作流程,掌握基本的Verilog语法与编写风格。

关键字:EDA;Verilog;32位双向移位寄存器1.引言随着社会的发展,科学技术也在不断的进步。

特别是计算机产业,可以说是日新月异,移位寄存器作为计算机的一个重要部件,从先前的只能做简单的左移或右移功能的寄存器到现在广泛应用的具有寄存代码、实现数据的串行-并行转换、数据运算和数据处理功能的移位寄存器。

近年来,集成电路和计算机应用得到了高速发展,现代电子设计技术已迈入一个崭新的阶段,具体表现在:(1)电子器件及其技术的发展将更多地趋向于为EDA服务;(2)硬件电路与软件设计过程已高度渗透;(3)电子设计技术将归结为更加标准、规范的EDA工具和硬件描述语言HDL的运用;(4)数字系统的芯片化实现手段已成主流。

因此利用计算机和大规模复杂可编程逻辑器件进行现代电子系统设计已成为电子工程类技术人员必不可少的基本技能之一。

移位寄存器正在向着功能强,体积小,重量轻等方向不断发展,本设计主要介绍的是一个基于超高速硬件描述语言VHDL对32位双向移位寄存器进行编程实现。

2.课程设计的目的在计算机中常要求寄存器有移位功能。

如在进行乘法时,要求将部分积右移;在将并行传送的数转换成串行数时也需要移位。

因此,移位寄存器的设计是必要的。

本次设计的目的就是利用计算机组成原理中移位寄存器的相关知识,通过课程设计更加深入的了解移位寄存器的功能。

了解EDA技术,并掌握VHDL硬件描述语言的设计方法和思想,通过学习的VHDL语言结合计算机组成原理中的相关知识理论联系实际,掌握所学的课程知识。

通过对移位寄存器的设计,巩固和综合运用所学知识,提高对计算机组成原理的理解。

verilog多路红外时分复用通信例程 -回复

verilog多路红外时分复用通信例程-回复实现多路红外时分复用通信是一个非常有趣和实用的课题。

在这篇文章中,我将详细介绍如何使用Verilog编程语言来实现多路红外时分复用通信的例程。

请跟随我的步骤一步一步回答。

首先,让我们来了解一下什么是红外时分复用通信。

红外时分复用通信是一种使用红外线作为载体,在不同的时间片段上分别传输不同的数据信号的通信方法。

它通过在不同时间段上分别发送和接收不同的红外信号,实现了多路通信的目的。

在Verilog中,我们可以使用逻辑门电路来实现多路红外时分复用通信。

下面是一个基本的多路红外时分复用通信的Verilog例程:module infrared_comm(input clk, 时钟信号input reset, 复位信号input [3:0] data_in, 输入数据信号output reg [3:0] data_out 输出数据信号);reg [1:0] state; 状态寄存器reg [3:0] data_mux; 数据选择器always @(posedge clk) beginif(reset) begin 复位state <= 0;data_out <= 0;end else begincase(state)0: begin 默认状态data_out <= 0;state <= 1;end1: begin 切换状态data_mux <= data_in;state <= 2;end2: begin 发送状态data_out <= data_mux;state <= 0;enddefault: state <= 0; 默认状态endcaseendendendmodule以上Verilog代码实现了一个简单的多路红外时分复用通信的例程。

让我来逐步解释一下每个部分的功能。

首先,我们定义了一个模块`infrared_comm`,其中包含了输入和输出的端口。

verilog组合电路的设计 -回复

verilog组合电路的设计-回复Verilog组合电路的设计:引言在现代电子系统中,组合电路起着至关重要的作用。

组合电路由逻辑门和其他逻辑元件组成,没有存储元件,其输出仅取决于当前的输入。

这种特点使得组合电路非常适合用于解决各种问题,例如数据选择、逻辑运算、状态机、编码器和解码器等。

本文将介绍关于Verilog组合电路设计的基础知识,并提供一步一步的解决方案,以帮助读者更好地理解和应用这些概念。

第1步:了解Verilog HDL(硬件描述语言)Verilog HDL是一种硬件描述语言,用于描述数字电路和系统的行为和结构。

它提供了一种便捷的方法来设计和模拟数字逻辑电路。

在开始设计之前,我们需要对Verilog HDL有基本的了解。

首先,我们需要了解几个基本概念:- 模块:Verilog中的模块是组合电路的一个基本单位。

模块由端口声明和内部逻辑实现组成。

- 端口声明:端口声明定义了模块的输入和输出端口的类型和名称。

- 内部逻辑:内部逻辑定义了模块的功能,它由组合逻辑和时序逻辑组成。

第2步:编写模块的端口声明在设计组合电路之前,我们需要先确定模块的输入和输出端口。

在这个例子中,我们将以[4位全加器]为主题进行设计。

首先,我们需要定义4个输入端口a、b、cin和一个输出端口sum,同时还有一个进位输出端口cout。

根据这些要求,我们可以编写以下端口声明:module full_adder(a, b, cin, sum, cout);input a, b, cin;output sum, cout;endmodule第3步:实现内部逻辑接下来,我们需要实现全加器的内部逻辑。

全加器是一种用于将两个二进制数字和一个进位输入相加的电路。

首先,我们需要声明一个临时变量temp,用于存储每个位上的和以及进位的计算结果。

然后,我们可以分别计算每个位上的和以及进位,最后将结果赋给输出端口sum和cout。

以下是全加器的完整代码:module full_adder(a, b, cin, sum, cout);input a, b, cin;output sum, cout;wire temp;assign sum = a ^ b ^ cin;assign temp = (a & b) (a & cin) (b & cin);assign cout = temp;endmodule第4步:设计主模块我们已经成功定义并实现了全加器模块。

verilog !用法 -回复

verilog !用法-回复Verilog 是硬件描述语言(Hardware Description Language, HDL) 的一种,主要用于描述数字系统的行为和结构。

它是一种高级语言,可用于描述电子系统的硬件功能和电路行为。

Verilog 具有模块化和并行化的特性,能够快速且准确地描述电子系统及其各个组件之间的相互关系。

本文将以"Verilog 用法" 为主题,为读者逐步介绍Verilog 的基础知识和常见用法。

第一部分:Verilog 简介和基础知识(500 字)1. 什么是Verilog?Verilog 是一种硬件描述语言,用于描述数字系统的行为和结构。

它是一种高级语言,能够准确描述电子系统的硬件功能和电路行为。

2. Verilog 的起源和发展最早的Verilog 是在1984 年由Gateway Design Automation 公司的Philip Moorby 发明的。

之后,它被开放出来,并逐渐成为数字系统设计的行业标准。

3. Verilog 的基本元素Verilog 包含模块(module)、端口(port)、信号(signal)、寄存器(register)、线网(wire)、输入(input)、输出(output)、内部连接(assign)等基本元素,这些元素共同构成了一个完整的Verilog 描述。

4. Verilog 的行为建模Verilog 提供了多种行为建模的方式,包括组合逻辑(combinational)、时序逻辑(sequential)、有限状态机(finite state machine)等,使得设计者能够准确地描述电子系统的行为和时序。

第二部分:Verilog 模块和端口定义(500 字)1. Verilog 模块的定义Verilog 中的模块是一个独立的功能单元,它可以包含多个输入输出端口和内部信号,用于描述一个子系统的功能。

模块内部可以包含连接和互连逻辑,以及寄存器等具体的硬件描述。

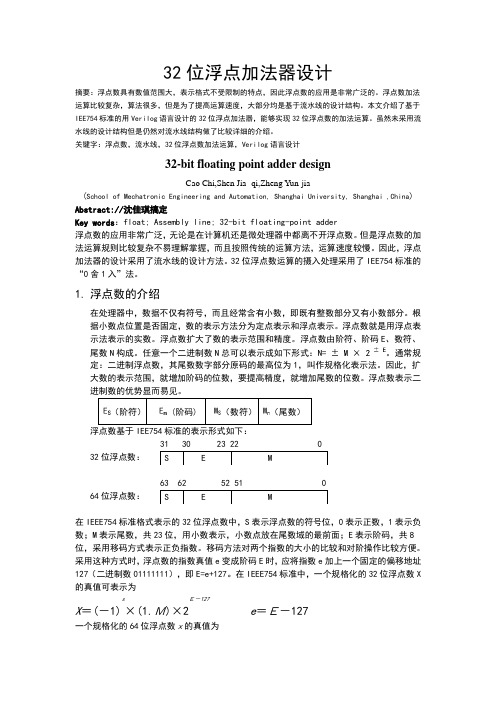

上海大学verilog设计32位浮点加法器设计

32位浮点加法器设计摘要:浮点数具有数值范围大,表示格式不受限制的特点,因此浮点数的应用是非常广泛的。

浮点数加法运算比较复杂,算法很多,但是为了提高运算速度,大部分均是基于流水线的设计结构。

本文介绍了基于IEE754标准的用Verilog 语言设计的32位浮点加法器,能够实现32位浮点数的加法运算。

虽然未采用流水线的设计结构但是仍然对流水线结构做了比较详细的介绍。

关键字:浮点数,流水线,32位浮点数加法运算,Verilog 语言设计32-bit floating point adder designCao Chi,Shen Jia- qi,Zheng Yun-jia(School of Mechatronic Engineering and Automation, Shanghai University, Shanghai ,China ) Abstract://沈佳琪搞定Key words :float; Assembly line; 32-bit floating-point adder 浮点数的应用非常广泛,无论是在计算机还是微处理器中都离不开浮点数。

但是浮点数的加法运算规则比较复杂不易理解掌握,而且按照传统的运算方法,运算速度较慢。

因此,浮点加法器的设计采用了流水线的设计方法。

32位浮点数运算的摄入处理采用了IEE754标准的“0舍1入”法。

1. 浮点数的介绍在处理器中,数据不仅有符号,而且经常含有小数,即既有整数部分又有小数部分。

根据小数点位置是否固定,数的表示方法分为定点表示和浮点表示。

浮点数就是用浮点表示法表示的实数。

浮点数扩大了数的表示范围和精度。

浮点数由阶符、阶码E 、数符、尾数N 构成。

任意一个二进制数N 总可以表示成如下形式:N=。

通常规定:二进制浮点数,其尾数数字部分原码的最高位为1,叫作规格化表示法。

因此,扩大数的表示范围,就增加阶码的位数,要提高精度,就增加尾数的位数。

《Verilog设计入门》PPT课件

精选PPT

18

3.1 组合电路的Verilog描述

3.1.2 4选1多路选择器及其case语句表述方式 6.赋值操作符 “<=”,只能用于顺序语句,不能用于assign引 导的并行语句

两种过程赋值操作: (1)阻塞式赋值“=”:语句执行结束,右侧表达式的值立刻赋给左侧 目标变量。

对于always引导的块语句中含有多条阻塞式赋值语句时,当执行某 一条语句时,其它语句不允许执行,被阻塞了,具有顺序执行的特点。

精选PPT

23

3.1 组合电路的Verilog描述

3.1.4 4选1多路选择器及其if语句描述方式

精选PPT

24

3.1 组合电路的Verilog描述

3.1.4 4选1多路选择器及其if语句描述方式 1.if_ else条件语句 if(表达式) begin 语句1;语句2;…..语句n; end else begin 语句n+1;语句n+2;…..语句n+n; end

input a,b;

output so,co;

assign so = a ^ b;

assign co = a & b;

endmodule

精选PPT

28

3.1 组合电路的Verilog描述

3.1.5 加法器及其Verilog描述

2.基于always @引导的过程语句和逻辑操作符的描述

module h_adder2(a,b,so,co);

endmodule

精选PPT

34

3.1 组合电路的Verilog描述

3.1.5 加法器及其Verilog描述 5. 全加器描述----用半加器、或门模块及例化语句描述

精选PPT

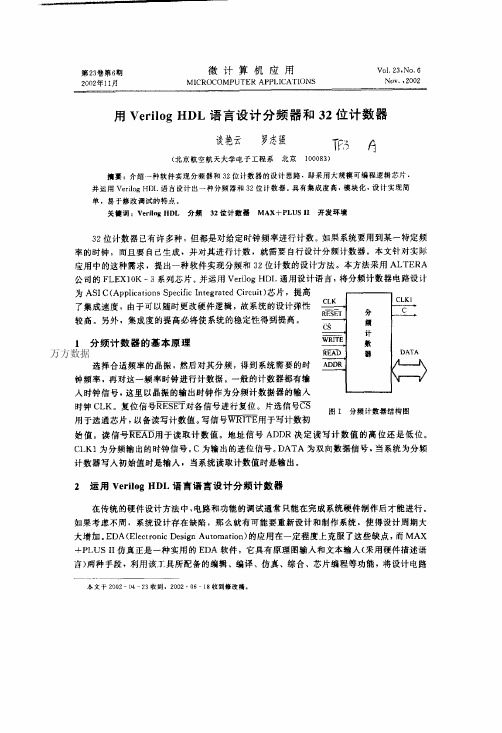

用Verilog+HDL语言设计分频器和32位计数器

i<i+1l

end

cs)∥有片选信号

end endrnodule

begin if(addr)

aceuh<2data}

该模块已通过软件仿真,符合设计要求。并已将程序下载到FPGA芯片,在电路板上与 系统进行联调,已证明设计达到预期功能,正式投入使用。

参 考 文 献

1夏宇闻.复杂数字电路与系统的VerilogHDL设计技术.北京t北京航空航天大学出版杜,1999.1—86 2阎石鼓字电子技术基础.北京:高等教育出版社.1 997.224--295 3束万焘·罗 车,吴顺军.CPI,D技术及其盥用西安:西安电子科技大学出版社,1999.30】oo

end end

output

elkl.c}//输出时钟和计数进位信号

j

wirte[15

reg

பைடு நூலகம்

O]data—reg·dataI

c,clkl{

if(i>=119) 计数值的高16位数和低

begin

∥对输人时钟进行J20分频

reg[1 5:O]aceub.aecul;

1

6位数

j<=0; clkl<=~clkl;

第23卷第6期 2002年1 1月

微计算机应用

MICROCOMPUTER APPLICATIONS

Vol

23.N。.6

Nov-,2002

用Ver|log

HDL语言设计分频器和32位计数器

谈艳云 罗志强

100083)

仍局

(北京航空航天大学电子工程东北京

擅要t介绍一种软件实现分频器和32位计数器的设计思路.即采用大规模可编程逻辑芯片.

+PLUS

II仿真正是一种实用的EDA软件,它具有原理图输入和文本输入(采用硬件描述语

verilog多模块编程实例

Verilog多模块编程实例1. 介绍Verilog是一种硬件描述语言,被广泛应用于数字电路设计。

Verilog具有模块化设计的特点,可以将一个大型的电路设计分解成多个小模块,然后逐个实现和调试。

本文将介绍Verilog多模块编程的实例,以帮助读者了解如何使用Verilog进行模块化设计。

2. 模块化设计的优势模块化设计是一种将大型系统分解成多个小模块的设计方法。

在Verilog中,模块化设计有以下几个优势:- 提高代码可读性:通过将大型系统分解成多个小模块,可以提高代码的可读性和可维护性。

- 便于调试:每个小模块相对独立,可以单独调试和测试,提高了系统的可靠性和稳定性。

- 提高复用性:将功能相似的代码封装成模块,可以提高代码的复用性,减少代码冗余。

3. 多模块编程实例接下来,我们将通过一个简单的数字电路设计来演示Verilog多模块编程的实例。

假设我们要设计一个4位全加器电路,首先我们需要实现一个单位全加器模块,然后将四个单元全加器模块连接成一个4位全加器模块。

3.1 单位全加器模块我们定义一个单位全加器模块,代码如下:```verilogmodule Adder_unit (input a, b, cin,output sum, cout);assign {cout, sum} = a + b + cin;endmodule```在单位全加器模块中,我们定义了三个输入信号a、b、cin和两个输出信号sum、cout。

其中,sum表示相加的结果,cout表示进位。

在模块内部,我们通过assign语句实现了全加器的功能。

3.2 4位全加器模块接下来,我们将四个单位全加器模块连接成一个4位全加器模块,代码如下:```verilogmodule Adder_4bit (input [3:0] a, b,input cin,output [3:0] sum,output cout);Adder_unit U0(.a(a[0]), .b(b[0]), .cin(cin), .sum(sum[0]), .cout(cout0));Adder_unit U1(.a(a[1]), .b(b[1]), .cin(cout0), .sum(sum[1]), .cout(cout1)); Adder_unit U2(.a(a[2]), .b(b[2]), .cin(cout1), .sum(sum[2]), .cout(cout2)); Adder_unit U3(.a(a[3]), .b(b[3]), .cin(cout2), .sum(sum[3]), .cout(cout));endmodule```在4位全加器模块中,我们首先定义了四个输入信号a、b和一个输入信号cin,以及四个输出信号sum和一个输出信号cout。

verilog module 写法

verilog module 写法Verilog是一种硬件描述语言(HDL),用于描述数字电路的行为和结构。

Verilog模块则是用于定义特定功能的电路模块的基本单元。

本文将详细介绍Verilog模块的写法,包括模块的基本结构、输入输出定义和信号声明、内部逻辑实现、测试综合等方面。

Verilog模块的基本结构如下:```verilogmodule module_name(input ports, output ports, inout ports, wire/reg declarations);//内部逻辑和声明endmodule```其中`module_name`是模块名称,`input ports`是输入端口列表,`output ports`是输出端口列表,`inout ports`是双向端口列表,`wire/reg declarations`是信号声明。

模块中的端口可以是单个信号或者信号向量。

在声明端口时,可以指定信号的宽度和方向(输入、输出或双向)。

例如:```verilogmodule adder(input [3:0] a,input [3:0] b,output [4:0] sum);//内部逻辑和声明endmodule```在模块中,可以使用`wire`或`reg`关键字声明内部信号。

`wire`用于声明表示连线的信号,而`reg`用于声明表示寄存器的信号。

例如:```verilogmodule counter(input clk,input rst,output reg [3:0] count);wire [3:0] next_count;//内部逻辑和声明always @(posedge clk or posedge rst) beginif (rst)count <= 0;elsecount <= next_count;endendmodule```在模块的`always`块中可以编写组合逻辑和时序逻辑。

verilog基本语法、模块写法

Verilog语言是一种硬件描述语言(HDL),用于描述和设计数字电路。

它广泛应用于数字系统的建模、验证和综合,是数字电路设计领域中的重要工具之一。

在Verilog中,模块是最基本的组织单位,模块中包含了电路的功能和行为描述。

本文将介绍Verilog语言的基本语法和模块写法,以帮助读者更好地理解和应用Verilog语言。

一、Verilog基本语法1. 注释在Verilog中,使用双斜杠(//)进行单行注释,使用/* */进行多行注释。

注释可以提高代码的可读性,便于他人理解和维护。

2. 变量声明Verilog中的变量可以分为寄存器变量(reg)和线网(wire)两种类型。

寄存器变量用于存储状态信息,线网用于连接各个逻辑门的输入和输出。

3. 逻辑运算符和位运算符Verilog中包括逻辑运算符(与、或、非等)和位运算符(与、或、异或等),用于对信号进行逻辑和位级操作。

4. 控制语句Verilog支持if-else语句、case语句等控制语句,用于根据不同条件执行不同的操作。

5. 模拟时钟在Verilog中,时钟是电路中的重要部分,通常使用时钟信号来同步各个元件的动作。

时钟可以通过周期性方波信号来模拟,使用$period 函数可以定义时钟的周期。

6. 仿真指令Verilog提供了多种仿真指令,用于初始化信号、设置仿真时间、输出波形图等操作,有助于仿真和调试电路。

二、模块写法1. 模块定义在Verilog中,一个模块包含了一组功能相关的硬件描述,可以看作是一个小型电路的抽象。

模块通过module关键字进行定义,其中包括模块名、输入输出端口声明等信息。

```verilogmodule adder(input wire [3:0] a,input wire [3:0] b,output reg [4:0] c);// 模块内部逻辑描述endmodule```2. 端口声明模块的端口包括输入端口(input)和输出端口(output),可以通过wire和reg进行声明。

Verilog基本电路设计指导书(有很多例子)

文档编号版本 密级深圳市华为技术有限公司1.0内部公开共 56页研究管理部文档中心资源类别: HDL 语言Verilog 基本电路设计指导书(仅供内部使用)Verilog Group 拟制: 批准: 批准:日期: 日期: 日期:2000/04/04 yyyy/mm/dd yyyy/mm/dd深圳市华为技术有限公司版权所有 不得复制修订记录日期修订版本描述作者2000/04/04 1.00 2001/02/28 1.01Verilog Group 初稿完成修订,主要增加三态和一些电路图苏文彪目 录1前言5 56 6 6789 2典型电路的设计2.1全加器的设计2.2数据通路2.2.1四选一的多路选择器 2.2.2译码器 2.2.3优先编码器 2.3计数器 2.4算术操作 2.5逻辑操作 2.6移位操作 2.7时序器件10 10 11 12 12 12 13 2.7.1上升沿触发的触发器2.7.2 带异步复位、上升沿触发的触发器 2.7.3带异步置位、上升沿触发的触发器 2.7.4带异步复位和置位、上升沿触发的触 发器14 15 16 2.7.5带同步复位、上升沿触发的触发器 2.7.6带同步置位、上升沿触发的触发器 2.7.7带异步复位和时钟使能、上升沿触发 的触发器16 17 18 20 20 23 26 30 30 31 31 31 31 2.7.8 D-Latch (锁存器) 2.8 ALU2.9有限状态机(FSM )的设计2.9.1概述2.9.2One-hot 编码 2.9.3 Binary 编码 2.10三态总线2.10.1三态 buffer 2.10.2双向 I/O buffer3常用电路设计3.1CRC 校验码产生器的设计3.1.1概述3.1.2 CRC 校验码产生器的分析与硬件实 现32 33 3.1.3并行 CRC-16校验码产生器的 Verilog HDL 编码3.1.4串行 CRC-16校验码产生器的 Verilog HDL 编码35 37 373.2随机数产生电路设计3.2.1概述3.2.2伪随机序列发生器的硬件实现3.2.3 8位伪随机序列发生器的 Verilog HDL编码37384041 41 41 44 44 443.3双端口RAM仿真模型3.4同步FIFO的设计3.4.1功能描述3.4.2设计代码3.5异步FIFO设计3.5.1概述3.5.2设计代码Verilog 基本电路设计指导书关键词:电路、摘要:本文列举了大量的基本电路的Verilog HDL代码,使初学者能够迅速熟悉基本的HDL建模;同时也列举了一些常用电路的代码,作为设计者的指导。

基于Verilog HDL语言的32X8 FIFO设计

基于Verilog HDL 语言的32X8FIFO 设计The Design of 32X8FIFO Based on Verilog HD L夏传红3 王祖强 李秀娟XIA Chuan 2hong WANG Zu 2qiang LI Xiu 2juan摘 要 介绍了FIFO 的基本概念、设计方法和步骤,采用了一种新颖的读、写地址寄存器和双体存储器的交替读、写机制,实现了FIFO 的基本功能,同时使本32X 8FIFO 拥有可同时读、写的能力,完全基于Verilog H D L 语言实现了电路功能并应用Synopsys 公司的Design C om piler 和VCS 对其进行综合、仿真。

关键词 FIFO Verilog H D L ASIC Abstract This thesis introduces the FIFO ’s basic concept ,design method and steps ,and a novel mechanism of reading and writing FIFO with tw o separate mem ories.The reading and writing operation will alternate between the tw o mem ories ,thus this FIFO can be read and written in the same time.The design is based on the Verilog H D L language ,sythesized with Design C ompiler and simulated with VCS of the Synopsys company.K eyw ords FIFO Verilog H D L ASIC3山东大学信息科学与工程学院 山东 济南 250100 对基于单体存储器的FIFO ,作为一种数据缓冲器,其数据存放结构和RAM 是一致的,只是存取方式有所不同。

verilog [] 用法 -回复

![verilog [] 用法 -回复](https://img.taocdn.com/s3/m/8ea0c928ae1ffc4ffe4733687e21af45b307fe8d.png)

verilog [] 用法-回复Verilog是一种硬件描述语言(HDL),用于设计和模拟数字电路。

在本篇文章中,我们将深入探讨Verilog的用法,并逐步回答关于该语言的一些常见问题。

第一部分:Verilog简介(约300字)- Verilog是什么?Verilog是一种用于描述和设计数字电路的硬件描述语言。

它具有高层次抽象,可以用于电路设计、验证和仿真。

- Verilog的起源和发展Verilog最初由Gateway Design Automation公司的Phil Moorby于1983年发明,并在1984年发布。

它后来被Cadence Design Systems 公司收购,并发展成为IEEE标准1364-2005。

目前,Verilog已成为数字电路设计的主要语言之一。

第二部分:Verilog基础知识(约500字)- Verilog有哪些数据类型和运算符?Verilog支持多种数据类型,包括bit、reg、integer、real、time等。

它还提供了常见的算术、逻辑和位运算符,如+、-、*、/、&&、、~等。

- Verilog如何定义模块?Verilog中,可以使用关键字module来定义模块。

每个模块由输入输出端口的声明和内部逻辑的描述组成。

例如:module Adder(input [3:0] a, b, output [4:0] sum);内部逻辑描述endmodule- Verilog如何描述时序逻辑?时序逻辑在Verilog中可以使用关键字always和posedge或negedge 来表示。

例如:always@(posedge clk)begin时序逻辑描述end- Verilog如何描述组合逻辑?组合逻辑可以使用关键字always @*来表示。

例如:always @*begin组合逻辑描述end第三部分:Verilog模拟和验证(约600字)- Verilog模拟的流程是什么?编写Verilog代码后,需要进行模拟和验证。

电子科技大学-ASIC课程设计报告

电子科技大学专用集成电路(ASIC)课程设计报告学号:290130xxxx学生姓名:X X X课题名称:交换网络复用与解复用模块设计无线通信与嵌入式系统实验室通信集成电路与系统工程中心2011年12月一、设计原理我国公用电话交换网(PSTN)是我国发展最早的电信网,主要为刚户提供电话业务。

就目前来看,PSTN仍然是规模最大、业务量最高的电信业务网。

◆交换系统在电话网中的作用电信交换的基本含义是在公用网大量的终端用户之间,按所需目的地相互传递信息,也就是说,任何一个主叫用户的信息,可以通过电信网中的交换节点发送到所需的任何一个或多个被叫用户。

电话交换是电信交换中最基本的一种交换方式。

一个交换系统应具有下述的三个功能:l、为两个用户通过话音信号进行会话临时提供一条双向传输的媒介,其通频带应在300-3400H Z之间。

2、提供并传输用户线和网内各种信号。

这些信号包括摘挂机信号、电话号码以及为呼叫的建立、监视和释放所必须的控制信号。

这些控制信号要在网络内的相关节点予以执行。

3、为了提高电话网络的运行和管理效率,网内还需要互相和处理一些命令和信息(如话务餐测量、计费、设备故障检测、故障诊断、故障应急处理和故障排除后的重新运行组织等)。

◆程控数字交换系统是由硬件和软件两大部分组成的。

1.硬件程控数字交换系统的硬件可以分为三个系统:话路系统、控制系统和输入输出系统,如图1-1所示。

图1-1 程控数字交换机的基本组成话路系统是指与话音接续有关的设备,它又包括用户级、远端用户级、各种中继接口、信号部件和选组级,其中选组级为交换系统的核心设备。

控制系统的功能包括两个方面:一方面是对呼叫进行处理:另一方面对整个交换系统的运行进行管理、监测和维护。

控制系统的硬件由两部分构成:一个是处理机(CPU),另一个是存储器。

其中处理机是控制系统的核心。

输入输l出系统一般包括打字机、显示器、打印机、以及磁盘和磁带机等外存储器。

打字机是用来输入维护、测试、运转管理等方面的人机命令、显示器和打印机是交换机的输出设备。

计算机设计与实践-32位ALU设计

alu_da=5; alu_db=3; #10; alu_clt = 11; alu_da=3; alu_db=5; #10; alu_clt = 11;

15

祝各位身体健康、工作顺利、家 庭幸福。

16

17:alu_sra<={{17{alu_da[31]}},alu8

end

alu_32 alu_32_1(alu_add,alu_da,alu_db_ mux,Sub,c2);

assign overflow=alu_da[31]&alu_db_mu x[31]&~alu_add[31]|~alu_da[31] &~alu_db_mux[31]&alu_add[31];

32位ALU设计

——Verilog HDL语言

1

module alu(alu_da,alu_db,alu_clt,alu_shift,alu_zero_out,overflow_out,alu_dc );

input [31:0]alu_da; input [31:0]alu_db; input [3:0]alu_clt; input [4:0]alu_shift; output reg alu_zero_out; output reg overflow_out; output reg [31:0]alu_dc; wire alu_zero; wire overflow; wire [31:0]alu_and;//与结果 wire [31:0]alu_or;//或结果 wire [31:0]alu_xor;//异或结果 reg [31:0]alu_sll;//左移结果 reg [31:0]alu_srl;//右移结果 reg [31:0]alu_sra;//算数右移 wire [31:0]alu_add;//加减运算结果 wire c2;//加法器进位输出

32位双重快速跳跃进位链六级流水线加法器Verilog的实现

32位双重快速跳跃进位链六级流水线加法器Verilog的实现DLUT-SOFTWARE-0819Mr Xie2011/6/28`timescale 1ns / 1ps //定义时间单位为1ns,时间精度为1ps////////////////////////////////////////////////////////////////////////////////// //模块名: fullAdder32//端口说明: clk: 输入的时钟A:输入的32加数B:输入的32位被加数Cin:输入的最低位进位Cout:输出的最高位进位Sum:两个数相加的和//目标器件: Veritex4系列的XC4VSX35//工具版本: Xilinx-ISE10.1、ISE Simulator(VHDL/Verilog)、Synplify Pro9.6.2 //依懒关系: 不依懒于其它模块//创建日期: 08:43:38 06/21/2011//创建人:////////////////////////////////////////////////////////////////////////////////// module fullAdder32(clk,A,B,Cin,Cout,Sum);input clk; //声明clk为1位的线网型输入变量input [31:0] A; //声明A为32位的线网型输入变量input [31:0] B; //声明B为32位的线网型输入变量,input Cin; //声明Cin为1位的线网型输入变量output Cout; //声明Cout为1位的线网型输出变量output [31:0] Sum; //声明Sum为32位的线网型输出变量reg [31:0] Sum; //对Sum进行重新声明为寄存器型reg Cout; //对Cout进行重新声明为寄存器型reg [30:0] C; //每一位相加时产生的进位reg [30:0]tmpC1, tmpC2, tmpC3; //临时变量,对进位作一个暂存reg [31:0]d; //小组的本地进位reg [31:0]tmpd1, tmpd2, tmpd3;//临时变量,对本地进位作一个暂存reg [31:0]t; //小组的传递进位reg [31:0]tmpt1, tmpt2, tmpt3;//临时变量,对传递进位作一个暂存reg [8:1]D; //大组的本地进位reg [8:1]tmpD1; //临时变量,对大组的本地进位作一个暂存reg [8:1]T; //大组的传递进位reg [8:1]tmpT1; //临时变量,对大组的传递进位作一个暂存reg [31:0]tmpA1, tmpA2, tmpA3, tmpA4, tmpA5;//对输入变量A作暂存reg [31:0]tmpB1, tmpB2, tmpB3, tmpB4, tmpB5; //对输入变量B作暂存reg tmpCin1, tmpCin2, tmpCin3, tmpCin4, tmpCin5;//对输入变量Cin作暂存reg tmpCout1, tmpCout2;//对输出变量Cout作一个暂存//////////////////第一个时钟周期//////////////////////////////////计算小组的本地进位d和传递进位t//对输入的加数A,被加数B,低位进位Cin作一级暂存always @(posedge clk) begind <= A&B;t <= A|B;tmpA1 <= A;tmpB1 <= B;tmpCin1 <= Cin;end//////////////////第二个时钟周期/////////////////////////////////对输入的加数A,被加数B,低位进位Cin作二级暂存//对小组的本地进位d,传递进位t作一级暂存//计算进位C[0],C[1],C[2]//计算大组的本地进位D、传递进位Talways @(posedge clk) begintmpd1 <= d;tmpt1 <= t;tmpA2 <= tmpA1;tmpB2 <= tmpB1;tmpCin2 <= tmpCin1;C[0] <= d[0] | t[0]&tmpCin1;C[1] <= d[1] | t[1]&d[0] | t[1]&t[0]&tmpCin1;C[2] <= d[2] | t[2]&d[1] | t[2]&t[1]&d[0] | t[2]&t[1]&t[0]&tmpCin1;D[1] <= d[3] | &{t[3],d[2]} | &{t[3:2],d[1]} | &{t[3:1],d[0]};T[1] <= &t[3:0]; //t[3]&t[2]&t[1]&t[0];D[2] <= d[7] | &{t[7],d[6]} | &{t[7:6],d[5]}| &{t[7:5],d[4]};T[2] <= &t[7:4]; //t[3]&t[2]&t[1]&t[0];D[3] <= d[11] | &{t[11],d[10]} | &{t[11:10],d[9]}| &{t[11:9],d[8]};T[3] <= &t[11:8]; //t[11]&t[10]&t[9]&t[8];D[4] <= d[15] | &{t[15],d[14]} | &{t[15:14],d[13]}| &{t[15:13],d[12]};T[4] <= &t[15:12]; //t[15]&t[14]&t[13]&t[12];D[5] <= d[19] | &{t[19],d[18]} | &{t[19:18],d[17]}| &{t[19:17],d[16]};T[5] <= &t[19:16]; //t[19]&t[18]&t[17]&t[16];D[6] <= d[23] | &{t[23],d[22]} | &{t[23:22],d[21]}| &{t[23:21],d[20]};T[6] <= &t[23:20]; //t[23]&t[22]&t[21]&t[20];D[7] <= d[27] | &{t[27],d[26]} | &{t[27:26],d[25]}| &{t[27:25],d[24]};T[7] <= &t[27:24]; //t[27]&t[26]&t[25]&t[24];D[8] <= d[31] | &{t[31],d[30]} | &{t[31:30],d[29]}| &{t[31:29],d[28]};T[8] <= &t[31:28]; //t[31]&t[30]&t[29]&t[28];end////////////////////////t第三个时钟周期///////////////////////////对输入的加数A,被加数B,低位进位Cin作三级暂存//对小组的本地进位d,传递进位t作二级暂存//对大组的本地进位D,传递进位T作一级暂存//对进位部分进位C作二级暂存//计算进位C[3],C[7],C[11],C[15]always @ (posedge clk) begintmpd2 <= tmpd1;tmpt2 <= tmpt1;tmpA3 <= tmpA2;tmpB3 <= tmpB2;tmpCin3 <= tmpCin2;tmpD1 <= D;tmpT1 <= T;tmpC1[2:0] <= C[2:0];tmpC1[3] <= D[1] | T[1]&tmpCin2;tmpC1[7] <= D[2] | T[2]&tmpCin2;tmpC1[11] <= D[3] | T[3]&tmpCin2;tmpC1[15] <= D[4] | T[4]&tmpCin2;end////////////////////////t第四个时钟周期///////////////////////// //对输入的加数A,被加数B,低位进位Cin作四级级暂存//对小组的本地进位d,传递进位t作三级暂存//对进位部分进位C作二级暂存//计算进位C[6:4],C[10:8],C[14:12],C[19:16],C[23],C[27]//计算最高进位Coutalways @ (posedge clk) begintmpd3 <= tmpd2;tmpt3 <= tmpt2;tmpA4 <= tmpA3;tmpB4 <= tmpB3;tmpCin4 <= tmpCin3;tmpC2[0] <= tmpC1[0];tmpC2[1] <= tmpC1[1];tmpC2[2] <= tmpC1[2];tmpC2[3] <= tmpC1[3];tmpC2[7] <= tmpC1[7];tmpC2[11] <= tmpC1[11];tmpC2[15] <= tmpC1[15];tmpC2[4] <= tmpd2[4] | tmpt2[4]&tmpC1[3];tmpC2[5] <= tmpd2[5] | tmpt2[5]&tmpd2[4] | tmpt2[5]&tmpt2[4]&tmpC1[3];tmpC2[6] <= tmpd2[6] | tmpt2[6]&tmpd2[5] |tmpt2[6]&tmpt2[5]&tmpt2[4]&tmpC1[3];tmpC2[8] <= tmpd2[8] | tmpt2[8]&tmpC1[7];tmpC2[9] <= tmpd2[9] | tmpt2[9]&tmpd2[8] | tmpt2[9]&tmpt2[8]&tmpC1[7];tmpC2[10]<=tmpd2[10] | tmpt2[10]&tmpd2[9]| tmpt2[10]&tmpt2[9]&tmpt2[8]&tmpC1[7];tmpC2[12] <= tmpd2[12] | tmpt2[12]&tmpC1[11];tmpC2[13] <= tmpd2[13] | tmpt2[13]&tmpd2[12]| tmpt2[13]&tmpt2[12]&tmpC1[11];tmpC2[14] <= tmpd2[14] | tmpt2[14]&tmpd2[13]|tmpt2[14]&tmpt2[13]&tmpt2[12]&tmpC1[11];tmpC2[16] <= tmpd2[16] | tmpt2[16]&tmpC1[15];tmpC2[17] <= tmpd2[17] | tmpt2[17]&tmpd2[16]| tmpt2[17]&tmpt2[16]&tmpC1[15];tmpC2[18]<=tmpd2[18] | tmpt2[18]&tmpd2[17]| tmpt2[18]&tmpt2[17]&tmpt2[16]&tmpC1[15];tmpC2[19] <= tmpD1[5] | tmpT1[5]&tmpC1[15];tmpC2[23] <= tmpD1[6] | tmpT1[6]&tmpC1[15];tmpC2[27] <= tmpD1[7] | tmpT1[7]&tmpC1[15];tmpCout1 <= tmpD1[8] | tmpT1[8]&tmpC1[15];end////////////////////////t第五个时钟周期///////////////////////////对输入的加数A,被加数B,低位进位Cin作五级级暂存//对进位部分进位C作三级暂存//对最高进位Cout作一级暂存//计算进位C[22:20],C[26:24],C[30:28]always @ (posedge clk) begintmpA5 <= tmpA4;tmpB5 <= tmpB4;tmpCin5 <= tmpCin4;tmpC3[19:0] <= tmpC2[19:0];tmpC3[23] <= tmpC2[23];tmpC3[27] <= tmpC2[27];tmpCout2 <= tmpCout1;tmpC3[20] <= tmpd3[20] | tmpt3[20]&tmpC2[19];tmpC3[21] <= tmpd3[21] | tmpt3[21]&tmpd3[20]| tmpt3[21]&tmpt3[20]&tmpC2[19];tmpC3[22] <= tmpd3[22] | tmpt3[22]&tmpd3[21]| tmpt3[22]&tmpt3[21]&tmpd3[20]| tmpt3[22]&tmpt3[21]&tmpt3[20]&tmpC2[19];tmpC3[24] <= tmpd3[24] | tmpt3[24]&tmpC2[23];tmpC3[25] <= tmpd3[25] | tmpt3[25]&tmpd3[24]| tmpt3[21]&tmpt3[20]&tmpC2[23];tmpC3[26] <= tmpd3[26] | tmpt3[26]&tmpd3[25]| tmpt3[26]&tmpt3[25]&tmpd3[23]| tmpt3[26]&tmpt3[25]&tmpt3[24]&tmpC2[23];tmpC3[28] <= tmpd3[28] | tmpt3[28]&tmpC2[27];tmpC3[29] <= tmpd3[29] | tmpt3[29]&tmpd3[28]| tmpt3[29]&tmpt3[28]&tmpC2[27];tmpC3[30] <= tmpd3[30] | tmpt3[30]&tmpd3[29]| tmpt3[30]&tmpt3[29]&tmpd3[28]| tmpt3[30]&tmpt3[29]&tmpt3[28]&tmpC2[27]; end////////////////////////第六个时钟周期///////////////////////////所有的进位已经产生//计算A、B两个数的和Sum//输出最高进位always @ (posedge clk) beginSum <= tmpA5^tmpB5^{tmpC3[30:0],tmpCin5};Cout <= tmpCout2;endendmodule// module fullAdder32(clk,A,B,Cin,Cout,Sum);测试代码如下:`timescale 1ns / 1ps //定义时间单为及时间精度//////////////////////////////////////////////////////////////////////////////////模块名: test.v//输入输出端口:无//目标器件: Veritex4系列的XC4VSX35//工具版本: Xilinx-ISE10.1、ISE Simulator(VHDL/Verilog)、Synplify Pro9.6.2 //创建日期: 08:44:52 06/23/2011//创建人://////////////////////////////////////////////////////////////////////////////// module test;// 输入信号reg clk;reg [31:0] A;reg [31:0] B;reg Cin;//输出信号wire Cout;wire [31:0] Sum;// 实例化要测试的模块fullAdder32 uut (.clk(clk),.A(A),.B(B),.Cin(Cin),.Cout(Cout),.Sum(Sum));initial begin// 初始化输入信号clk = 1;A = 32'd1112111;B = 32'd2221222;Cin = 0;//下面为仿真激励信号foreverfork#20 A <= A + 1; //加数每隔一个时钟周期加1#20 B <= B + 1; //被加数每隔一个时钟周期加1joinendalways#10 clk <= ~clk; //时钟周期为20nsendmodule1.加法器的仿真仿真时序波形如下所示:2.加法器的综合Technology Hierarchical View如下图所示:。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

电子科技大学

ASIC课程设计报告二

学号:201222240937 姓名:周恒

课题题目:交换网络32路复用模块设计

2013年5月

题目要求

Develop, verify (before and after synthesis), and synthesize a Verilog module that encapsulates the functionality shown in Fig.2, where the outputs of the A/D converters are inputs to a module that interleaves the sample bytes, with separate sub-modules for the control unit, the mux, the demux, the parallel to serial converter, and the serial to parallel converter. Define additional interface signals as needed to complete the design. Model the multiplexer so that its outputs will be registered. Carefully document your work.

图1-2 一个简单的交换控制系统组成

本次设计的主要内容为交换网络复用与解复用模块,在下文做出详细设计,包括设计规格书、设计框图、仿真波形和设计结论。

一、设计框图

整个系统由5个模块组成,其顶层模块如下图所示:

1.控制模块:用于对整个系统的控制,包括复用控制,串并转换控制,并

串转换控制和解复用控制。

2.复用模块:对32路输入数据进行复用,依次输入系统。

3.并串转换模块:将8bit的并行数据转换为串行数据。

4.串并转换模块:将对应的串行数据转换为并行数据。

5.解复用模块:对32路数据进行复用输出,依次输出系统。

系统框图顶层图

复用模块:对32路输入数据进行复用,依次输入系统,其原理框图部分截图如下图所示。

复用模块原理框图部分截图

并串转换模块:将8bit的并行数据转换为串行数据其原理框图如下图所示。

并串转换模块原理框图

串并转换模块:将对应的串行数据转换为并行数据,其原理框图如图下图所示。

串并转换模块原理框图

解复用模块:对32路数据进行复用输出,依次输出系统,其原理框图部分截图如下图所示。

解复用模块原理框图部分截图

二、仿真波形

通过testbench模块产生测试输入,将各个模块添加到顶层图中联合测试,最终实现所需要的功能。

tesebench说明:

测试输入为d_in[255:0]表示输入的32路8位数据。

第一个125us传输的32路数据分别为16进制的01,02,03......, (20)

第二组为21,22,23......,3e, (40)

……

……

产生的仿真波形如下图所示:

输入波形为:

第一组32路输入数据

第二组32路输入数据

第三组32路输入数据

输出波形如下:

设计总结

通过仿真表面各个模块完成了相应的功能,输入数据帧以125us为周期传到输出,实现了课程设计的要求。