基于fpga的eeprom设计

基于FPGA的电子万年历的设计与实现

基于FPGA的电子万年历的设计与实现

李承铭;王佳欣;柯骏;李丝天;李翔;陈初侠

【期刊名称】《电脑知识与技术》

【年(卷),期】2024(20)4

【摘要】文章基于FPGA芯片EP4CE6E22C8设计了一款电子万年历。

首先根据设计要求,将电子万年历分成多个底层电路并用VerilogHDL语言对其进行设计和仿真,然后调用已设计好的各底层电路采用原理图方式设计顶层电路,最后对设计好的顶层电路进行管脚锁定并下载到FPGA芯片中进行硬件验证。

结果表明,所设计的电子万年历能实现秒、分、时、星期、日、月、年的显示、时间的设置和整点报时功能,集多功能于一体,具有较好的实用性。

【总页数】4页(P106-109)

【作者】李承铭;王佳欣;柯骏;李丝天;李翔;陈初侠

【作者单位】巢湖学院电子工程学院

【正文语种】中文

【中图分类】TP29

【相关文献】

1.基于AT89S52单片机的电子万年历设计与实现

2.基于LED点阵显示的电子万年历的设计与实现

3.基于I2C总线电子万年历的设计与实现

4.基于FPGA的电子万年历设计

5.一种电子万年历的设计与实现

因版权原因,仅展示原文概要,查看原文内容请购买。

FPGA开发平台硬件系统设计及实现

研发设计 I RESEARCH DESIGN樓块图1系统总体设计框图近几年,随着FPGA (可编程逻辑器件)规模的日益增大, 我国数字电路设计取得了迅猛发展,硬件设计环境不断向实 用化、可靠化方向发展,为功能电路设计工作的有序开展提 供了硬件支持。

为此,如何科学设计和实现FPGA 开发平台 硬件系统、不断完善相关功能电路是相关软件开发人员必须思考和解决的问题。

1.系统总体设计FPGA 开发平台硬件系统主要由网 络模块、PS 2接口模 块和U S B 模块等模 块组成,系统总体 设计框图如图1所 示。

为了保证该系 统的运行性能,相关软件开发人员要重视对这些模块的设计与实现,为用户带 来良好的体验感。

1.1网络(D M 900A )模块电路设计网络(DM 900A )作为一种先进的接口芯片,充分利用 了以太网的应用优势,具有以下几种特征:①能够实现物理 层接口的全面集成;②内部含有FIFO 缓存,主要用于对大 量字节的接收和发送:③能够很好地兼容和支持不同类型的 主机工作模式;④在HP 证背景下,能够很好地实现自动翻 转功能和直接互联功能;⑤能够充分利用tcp /tp 加速器的应 用优势,避免CPU 承担过高的存储负担,从而实现对整机 运行性能的全面提高:⑥极大地缩短了读写时间。

总之,在 以太网控制器的应用背景下,相关软件开发人员要严格遵循 相关网络传输标准和要求,从而实现网速的提高和网络环境 的优化。

同时,在对网络模块电路进行科学设计的过程中, 确保该电路能够实现对相关接口的集成和应用,并采用接口 输入的方式将各种接口与芯片进行深度融合,以促进FPGA 开发平台硬件系统向智能化、自动化、信息化方向不断发展。

1.2USB 模块电路设计对于U S B 模块电路而言,为了保证其设计水平,相关软件开发人员要重 视对 CY 7C 68013A 芯片的使用,将 传输速度设置为摘要:随着社会经济水平的不断提高和信息时代的不断发展,FPGA (可编程逻辑器件)在集成电路领域中取得了良好的应用 效果,不仅有效扩大了编程器件电路的数量,还避免了定制电路的局限性,为更好地改进多种逻辑应用功能和结构发挥了 重要作用。

基于FPGA实现四选一选择器的设计

基于FPGA实现四选一选择器的设计摘要本文是基于FPGA的四选一选择器的设计:基于FPGA在数据选择方面的优势,把FPGA作为选择器的控制核心;主要研究如下:软件部分——四选一选择器程序。

针对数据选择器的设计,对FPGA进行了型号选择,使用VHDL语言在型号FLEX10K/20RC208-4上编写了四选一选择器的程序,通过使能端的控制,从而达到四选一的功能。

硬件部分——使用protel画出原理图并作出PCB板。

本设计采用了单八路模拟开关CD4051,通过输入端的控制,选择一路信号,通过ADC0804模数转化,输出8路信号给FLEX10K/20RC208-4,经FLEX10K/20RC208-4处理后,接TCL7528后,将数字信号转换为模拟信号并输出。

本文通过软件和硬件的两个方面的设计,实现了四选一选择器的功能。

关键词:FPGA ;VHDL ;PROTEL ;选择器内蒙古科技大学毕业设计说明书(毕业论文)FPGA implementation based on four selected design of a selectorAbstrateThis article is based on a choice selection of four FPGA Design: FPGA-based data selection in the advantages of the FPGA as a selector control center; main research are as follows:Software parts - 4 election a choice program. Design for data selection, model selection on the FPGA, using the VHDL language in the model FLEX10K/20RC208-4 four selected to write a program selector, by enabling the client to control, so as to achieve a function of four elections.Hardware - protel schematic drawing and make a PCB board. This design uses a single eight-way analog switches CD4051, through the control input, select the way the signal, ADC0804 module through the transformation of the output signal 8 to FLEX10K/20RC208-4, by FLEX10K/20RC208-4 treatment, then TCL7528, will digital signal is converted to analog signals and output.In this paper, two aspects of hardware and software design, implementation, choose one of four selector functions.Keywords: FPGA ; VHDL ; ROTEL ; selectorI目录摘要 .............................................................................................................................................. Abstrate (I)第一章绪论 01.1 FPGA简介 01.1.1 FPGA发展现状 01.1.2 FPGA的发展趋势 (1)1.1.3 FPGA基本结构 (1)1.1.4 FPGA的特点 (3)1.1.5 FPGA选型 (4)1.1.6 FPGA设计原则 (5)1.2本论文研究的主要内容 (6)第二章FPGA芯片设计 (7)2.1 BTYG-EDA实验开发系统简介 (7)2.1.1 BTYG-EDA实验开发系统特点 (7)2.1.2 BTYG-EDA实验开发系统资源介绍 (7)2.1.3 主芯片引脚和外部硬件连接关系 (7)2.2 FLEX10K/20RC208-4 (11)2.3 本章小结 (13)第三章MAX+plus II软件和VHDL语言――软件部分 (14)3.1 MAX+plus II开发软件 (14)3.1.1 MAX+plus II功能特点 (14)3.1.2 MAX+plus II系统要求 (15)3.1.3 MAX+plus II设计流程 (15)3.2 VHDL语言简介 (18)3.2.1 VHDL基本介绍 (18)3.2.2 VHDL语言的特点 (19)3.2.3 VHDL系统优势 (20)II内蒙古科技大学毕业设计说明书(毕业论文)3.2.4 VHDL程序基本结构 (20)3.3 MAX十plus II中硬件描述语言输入的设计过程 (21)3.3.1 输入VHDL文件 (21)3.3.2 将文件指定为设计项目 (21)3.3.3 项目编译 (22)3.3.4 项目仿真 (22)3.4 程序仿真介绍及仿真图 (22)3.5本章小结 (24)第四章protel99——硬件部分 (25)4.1 protel简介 (25)4.1.1 Protel99SE的功能特点 (25)4.1.2 用Protel99SE进行电路设计的步骤 (26)4.2 四选一选择器的原理图及各元件介绍 (26)4.3 本章小结 (33)第五章总结与展望 (34)5.1 取得的成果 (34)5.2 工作展望 (34)参考文献 (35)附录A (36)附录B (37)致谢 (39)III第一章绪论1.1 FPGA简介1.1.1 FPGA发展现状当今社会是数字化的社会,是数字集成电路广泛应用的社会,数字集成电路本身在不断地进行更新换代。

用FPGA实现PROM配置信息擦除的方法

用FPGA实现PROM配置信息擦除的方法

王吕大;张淑萍

【期刊名称】《计算机工程与设计》

【年(卷),期】2007(28)23

【摘要】通过对边界扫描测试技术原理的分析理解,特别是测试访问接口控制器的16种状态的相互转换分析,总结出边界扫描测试的核心操作,归纳出相应的操作流程.并结合工具软件产生的SVF文件和产商提供的BSDL文件,用硬件描述语言设计了一种基于边界扫描测试标准的擦除PROM配置信息的方法,并用FPGA进行了该方法的验证和实现.

【总页数】4页(P5745-5747,5764)

【作者】王吕大;张淑萍

【作者单位】北京计算机技术及应用研究所,北京,100039;北京计算机技术及应用研究所,北京,100039

【正文语种】中文

【中图分类】TP309+.2

【相关文献】

1.采用EEPROM对大容量FPGA芯片数据实现串行加载 [J], 范宏波;李一民;朱红梅

2.软件配置信息设计实现方法 [J], 张萍;易东云

3.基于FPGA的E2PROM读写控制设计及实现 [J], 宋翠芳;张道武;刘海华

4.基于FPGA嵌入式的PROM接口实现 [J], 张京晶;万旻;程甘霖;包斌

5.用电吸收调制器实现标记擦除的新方法 [J], 程黎黎;邵宇丰;陈林;文双春;刘海燕因版权原因,仅展示原文概要,查看原文内容请购买。

基于FPGA的PCM编码器与解码器的设计与实现(2).

基于FPG A 的PC M 编码器与解码器的设计与实现陈建洪,李彩芳,佘丽贞(莆田电业局设计所,福建莆田351100摘要:针对传统数字电路难以支持实现高码速率的PC M 功能,提出将PC M 的编、解码功能集成到具有硬件密度高、结构灵活、加密性好的现场可编程门阵列(FPG A,Field Pr ogra mmable Gate A rray 上的实现方案。

介绍了PC M 码型定义和帧格式,阐述了该方案的结构框架和设计方法,并结合实例和实测波形,说明PC M 编、解码器的功能实现过程。

实践表明,FPG A 可以有效地用于PC M 高码速率场合,在遥测系统中有实用意义。

关键词:脉码调制;现场可编程门阵列;编码;解码中图分类号:T N76;T N911.22文献标识码:B 文章编号:1005-7641(200512-0064-03收稿日期:2005-05-10;修回日期:2005-06-100引言随着遥测系统的发展,帧结构越来越复杂,这就要求遥测系统具备高码速率、实时可重构、处理复杂帧结构的能力,传统的数字电路难以实现这些复杂功能。

FPG A 是近几年发展起来的硬件可编程芯片,具有硬件密度高、结构灵活、可编程、加密性强等良好性能,在高速信号处理领域占有至关重要的地位,也为高码速率PC M 的实现,提供有效的途径。

FPG A 可以将复杂的逻辑功能集成在一块芯片上,易于实现片上系统SoC (System on a Chi p 。

为此,本设计将PC M (Pulse Code Modulati on 的编码功能和解码功能集成在FPG A 上。

1PC M 标准PC M 码是以串行方式进行传输的,分为NRZ 和B i Φ两大类码型。

这里仅介绍文章所要涉及的NRZ -L 、B i Φ-L 、B i Φ-M 三种码型。

根据I R I G 106-99标准,码型的定义如图1所示,其中,B i Φ-M 码的波形在半位码上要有电平的变化。

基于FPGA的数字频率计

2.3 方案选择

3单元模块电路设计

3.1电路设计总体框图

本设计主要由8个部分组成,以CPLD芯片部分为核心展开,待测信号输入,由外部电源,复位电路,单片机电路,液晶显示,标准时钟以及JTAG下载各个单元配合起来实现测试频率并在液晶显示屏上实时显示出数字频率信号。

图3.1 电路设计总体框图

3.2标准时钟(100MHz)产生部分

3.7电源部分

CPLD芯片工作电压在3.3V,单片机工作电压为5V。所以,在要求进行电压转换时,用到芯片LM1117进行5V电压到3.3V电压。

3.8单片机部分

3.8.1STC12_LQFP芯片介绍

如图3.8.1所示,STC12系列单片机为增强型8051芯片,1T,单时钟/机器周期,指令代码完全兼容传统8051单片机。通用I/O口(27/23/15个),复位后为:准双向口/弱上拉(普通8051传统I/O口)可设置成四种模式:准双向口/弱上拉,推挽/强上拉,仅为输入/高阻,开漏每个I/O口驱动能力均可达到20mA,但整个芯片最大不得超过55mA。ISP(在系统可编程)/IAP(在应用可编程),无需专用编程器,无需专用仿真器可通过串口(P3.0/P3.1)直接下载用户程序,数秒即可完成一片,EEPROM功能,看门狗定时器内部集成MAX810 专用复位电路(外部晶体20M 以下时,可省外部复位电路)。时钟源:外部高精度晶体/ 时钟,内部R/C 振荡器

表2-1显示了每个设备的行和列数,以及行和列毗邻地区的快闪记忆体数量的EPM570,EPM1270和EPM2210器件。长排满行延长从一排I/ O块到其他。简短的行毗邻超滤膜块,其长度是在列的宽度显示。

每一个LAB包括驱动控制信号LES的专用逻辑。控制信号包括两个时钟,两个时钟使能,两个异步清除,1同步清除,异步预置/负载,同步载荷,加/减控制信号,提供了一次10个控制信号最大。虽然同步负载和清除的信号通常用于执行时计数,也可以用于其他功能。

eeprom的标准电路参考设计

eeprom的标准电路参考设计EEPROM 的标准电路参考设计**前言**嘿,朋友们!在当今这个数字化、智能化的时代,电子设备无处不在,而 EEPROM(Electrically Erasable Programmable Read-Only Memory,电可擦可编程只读存储器)作为一种重要的存储器件,在很多电路设计中都扮演着关键的角色。

比如说,我们常见的智能手机、电脑、汽车电子系统等等,都离不开它。

今天咱们就来好好聊聊EEPROM 的标准电路参考设计,目的呢,就是为了让大家在设计电路的时候能有个靠谱的指南,少走弯路,做出更稳定、更高效的电路!**适用范围**咱们这个 EEPROM 的标准电路参考设计呀,适用的场景那可多了去了。

比如说,在消费电子领域,像智能手表、蓝牙耳机这类小型设备中,需要存储一些用户的个性化设置、使用记录等数据,EEPROM就能大显身手。

再比如,在工业控制领域,一些自动化设备需要记录关键的运行参数和故障代码,这时候 EEPROM 也是不二之选。

给您举个例子,一款智能门锁,它需要记住不同用户的开锁密码,还有开锁的记录。

这时候,使用EEPROM 来存储这些信息就非常合适,因为它能够在掉电的情况下依然保存数据,而且可以多次擦写更新。

说白了,只要是需要非易失性存储、数据量不大、且需要频繁更新数据的场景,都可以考虑使用 EEPROM 并参考咱们的标准电路设计。

**术语定义**为了让咱们后面的交流更顺畅,先给大家解释几个关键的术语。

“非易失性存储”:这就是说,即使电源关闭了,存储在里面的数据也不会丢失。

你可以想象一下,就像把重要的东西放进一个保险箱,不管停电还是怎样,东西都还在里面。

“擦写次数”:EEPROM 不是能多次修改数据嘛,那它能承受的修改次数就叫擦写次数。

“存储容量”:简单说,就是 EEPROM 能存多少数据。

**正文**1. 电路设计的基本原则- 电源供应稳定在 EEPROM 的电路设计中,稳定的电源供应是至关重要的。

基于fpga的eeprom设计

二线制I2C CMOS 串行EEPROM 的FPGA设计姓名:钱大成学号:080230114院系:物理院电子系2011年1月1日一、课程设计摘要:(1)背景知识:A、基本介绍:二线制I2C CMOS 串行EEPROM AT24C02/4/8/16 是一种采用CMOS 工艺制成的串行可用电擦除可编程只读存储器。

B、I2C (Inter Integrated Circuit)总线特征介绍:I2C 双向二线制串行总线协议定义如下:只有在总线处于“非忙”状态时,数据传输才能被初始化。

在数据传输期间,只要时钟线为高电平,数据线都必须保持稳定,否则数据线上的任何变化都被当作“启动”或“停止”信号。

图1 是被定义的总线状态。

①总线非忙状态(A 段)数据线SDA 和时钟线 SCL 都保持高电平。

②启动数据传输(B 段)当时钟线(SCL)为高电平状态时,数据线(SDA)由高电平变为低电平的下降沿被认为是“启动”信号。

只有出现“启动”信号后,其它的命令才有效。

③停止数据传输(C 段)当时钟线(SCL)为高电平状态时,数据线(SDA)由低电平变为高电平的上升沿被认为是“停止”信号。

随着“停在”信号出现,所有的外部操作都结束。

④数据有效(D 段)在出现“启动”信号以后,在时钟线(SCL)为高电平状态时数据线是稳定的,这时数据线的状态就要传送的数据。

数据线(SDA)上的数据的改变必须在时钟线为低电平期间完成,每位数据占用一个时钟脉冲。

每个数传输都是由“启动”信号开始,结束于“停止”信号。

⑤应答信号每个正在接收数据的EEPROM 在接到一个字节的数据后,通常需要发出一个应答信号。

而每个正在发送数据的EEPROM 在发出一个字节的数据后,通常需要接收一个应答信号。

EEPROM 读写控制器必须产生一个与这个应答位相联系的额外的时钟脉冲。

在EEPROM 的读操作中,EEPROM 读写控制器对EEPROM 完成的最后一个字节不产生应答位,但是应该给EEPROM 一个结束信号。

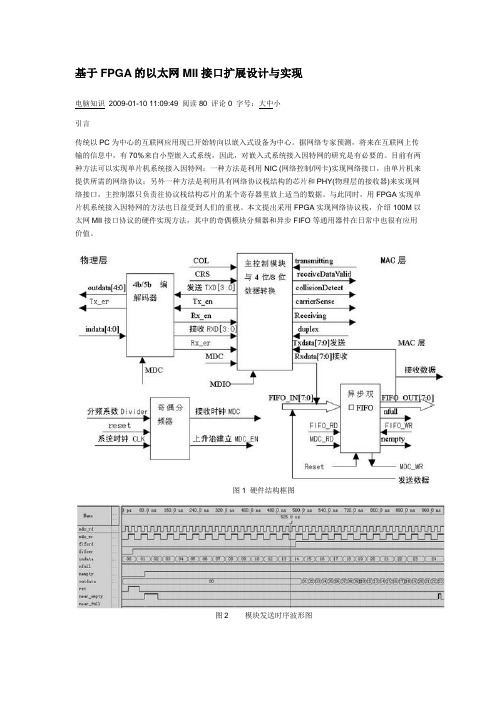

基于FPGA的以太网MII接口扩展设计与实现

基于FPGA的以太网MII接口扩展设计与实现电脑知识2009-01-10 11:09:49 阅读80 评论0 字号:大中小引言传统以PC为中心的互联网应用现已开始转向以嵌入式设备为中心。

据网络专家预测,将来在互联网上传输的信息中,有70%来自小型嵌入式系统,因此,对嵌入式系统接入因特网的研究是有必要的。

目前有两种方法可以实现单片机系统接入因特网:一种方法是利用NIC (网络控制/网卡)实现网络接口,由单片机来提供所需的网络协议;另外一种方法是利用具有网络协议栈结构的芯片和PHY(物理层的接收器)来实现网络接口,主控制器只负责往协议栈结构芯片的某个寄存器里放上适当的数据。

与此同时,用FPGA实现单片机系统接入因特网的方法也日益受到人们的重视。

本文提出采用FPGA实现网络协议栈,介绍100M以太网MII接口协议的硬件实现方法,其中的奇偶模块分频器和异步FIFO等通用器件在日常中也很有应用价值。

图1 硬件结构框图图2 模块发送时序波形图以太网MII接口协议IEEE802协议标准系列中,数据链路层包括LLC (逻辑链路控制)子层和MAC (媒体访问控制)子层。

其中MAC单独作为一个子层,完成数据帧的封装、解封、发送和接收功能。

物理层PHY的结构随着传输速率的不同而有一定差异,在100M和1000M以太网中,依次为PCS子层、PMA子层和PMD子层。

MII接口是连接数据链路层和物理层的接口,因为本设计中以太网速率采用100Mb/s,所以MII接口实际连接的是MAC子层和PCS子层。

根据协议,要求MII接口具有的功能有:数据和帧分隔符的读写时钟同步,提供独立的读写数据通道,为MAC层和PCS层提供相应的管理信号,以及支持全双工模式。

扩展MII接口功能及其FPGA实现由于100M以太网的物理层采用4b/5b编码,为了扩展MII接口的功能,要求其能够实现直接物理层5位数据和MAC层8位数据的发送接收传输转换。

即把从MAC子层用于发送的数据和从PHY用于接收的数据存入数据缓冲FIFO,同时要求MII接口将从PHY传来的信号COL、CRS转为信号Carrier和Collision,并提供给MAC子层用于载波监听和冲突检测,以及发送和接收时的时钟、使能、错误位信号的传送。

基于Nios_的EEPROMControllerCore的设计

基于N i os Ⅱ的EEPROM Contr oller Core 的设计Design of EEPROM Contr oller Core Based on N ios Ⅱ麦 胤1 柳 沁2(重庆邮电大学光电工程学院1,重庆 400065;重庆邮电大学自动化学院2,重庆 400065)摘 要:介绍了基于N i os Ⅱ的Contr oller Core 的基本组成结构,并详细介绍了如何在S OPC 中设计EEPROM Contr oller Core,用Veril og HDL 语言实现其硬件逻辑部分,并编写了相关驱动程序和应用层软件,构建了基于N ios Ⅱ的S OPC 。

同时以AT24C02EEPROM 为例,通过设计的EEPROM Contr oller 在A ltera Stratix1S10系列的FPG A 上实现了读写操作,试验结果正确。

关键词:片上可编程系统 控制器 硬件描述语言 I 2C 接口 驱动中图分类号:T N409 文献标志码:AAbstract:The basic structural compositi on of the Controller Core based on N ios Ⅱis intr oduced,and the method of designing EEPROM Con 2tr oller Core in S OPC is described in detail .The hardware part was i m p lemented by using Verilog HDL and the related drivers as well as app lica 2ti on s oft ware were written to build the S OPC based on N i os Ⅱ.W ith AT24C02EEPROM as examp le,thr ough the design of EEPROM Control 2ler,it is i m p lemented to read and write on Stratix1S10FPG A from A ltera Cor poration .The test results turn out t o be correct .Keywords:S OPC Contr oller HDL I 2C interfaceD rive 修改稿收到日期:2007-06-07。

EEPROM程序设计概要

EEPROM 程序设计概要一、有关协议一、有关协议上位机下发协议:上位机下发协议:地址地址 字节数字节数定义定义内容内容0 1 帧头 见帧类型表1 1 子帧编号 一包数据发不完,用于填写包序号2 2 数据长度DLEN4 DLEN 数据DLEN 可以为0,但最大不超过1024字节,否则分包发送4+DLEN1校验和串口操作E2PROM地址 字节数 定义 内容 01EEPROM 操作类型OXOA OXOA:读:读 OXOB OXOB:写:写1 2 EEPROM 操作地址 实际使用低8位,高8位填031 读写数据长度N4N数据E2PROM 用于存放口1控制面积(8字节)、口2控制面积(8字节)、分辨率(4字节)、亮度值(1字节)、色温值(2字节)、GAMMA 值等小数据量参数,具体定义请参照E2PROM 存储结构。

存储结构。

E2PROM 参数存储定义:第0~7字节存储 口1控制面积参数(8字节) 第8~15字节存储口2的控制面积参数(8字节) 第16~19字节存储分辨率参数(4字节) 第20字节存储亮度参数(1字节) 第21~22字节存储色温值(2字节) 第23字节存储GAMMA 参数值(1字节)第24~255字节为保留字(232字节)由以上协议,由指令解析模块解析出数据操作EEPROM 时,共有24字节数据(目前为24字节,由上可知)。

故本方案操作EEPROM 时采用页写和连续读方式。

时采用页写和连续读方式。

(FM24C02A,2K 串行电可擦除存储器:内部共分为32页,每页8字节,以8位地址寻址)地址寻址)系统整体框架如图1所示:所示:上位机下发数据包串口接收模块串口发送模块指令解析模块EEPROM EEPROM读写控制器读写控制器EEPROM EEPROM((FM24C02A FM24C02A))上位机下发数据数据传输给指令解析模块指令解析模块解析出数据以后进行相应的读写读回传数据读回传数据读回传数据SDASCLFPGA FPGA部分部分图1 E2PROM 部分整体框图部分整体框图如上图所示,上位机通过串口发送和接收数据后,把从上位机接收的数据送到指令解析模块进行解析(主要判断是否为操作EEPROM 数据,判断该指令时读或是写),指令解析完后按照一定时序把所要读写的数据读出或写入EEPROM 中。

基于FPGA的PCM编码器与解码器的设计与实现

基于FPG A 的PC M 编码器与解码器的设计与实现陈建洪,李彩芳,佘丽贞(莆田电业局设计所,福建莆田351100)摘要:针对传统数字电路难以支持实现高码速率的PC M 功能,提出将PC M 的编、解码功能集成到具有硬件密度高、结构灵活、加密性好的现场可编程门阵列(FPG A,Field Pr ogra mmable Gate A rray )上的实现方案。

介绍了PC M 码型定义和帧格式,阐述了该方案的结构框架和设计方法,并结合实例和实测波形,说明PC M 编、解码器的功能实现过程。

实践表明,FPG A 可以有效地用于PC M 高码速率场合,在遥测系统中有实用意义。

关键词:脉码调制;现场可编程门阵列;编码;解码中图分类号:T N76;T N911.22文献标识码:B 文章编号:1005-7641(2005)12-0064-03收稿日期:2005-05-10;修回日期:2005-06-100 引言随着遥测系统的发展,帧结构越来越复杂,这就要求遥测系统具备高码速率、实时可重构、处理复杂帧结构的能力,传统的数字电路难以实现这些复杂功能。

FPG A 是近几年发展起来的硬件可编程芯片,具有硬件密度高、结构灵活、可编程、加密性强等良好性能,在高速信号处理领域占有至关重要的地位,也为高码速率PC M 的实现,提供有效的途径。

FPG A 可以将复杂的逻辑功能集成在一块芯片上,易于实现片上系统SoC (System on a Chi p )。

为此,本设计将PC M (Pulse Code Modulati on )的编码功能和解码功能集成在FPG A 上。

1 PC M 标准PC M 码是以串行方式进行传输的,分为NRZ 和B i Φ两大类码型。

这里仅介绍文章所要涉及的NRZ -L 、B i Φ-L 、B i Φ-M 三种码型。

根据I R I G 106-99标准,码型的定义如图1所示,其中,B i Φ-M 码的波形在半位码上要有电平的变化。

基于fpga的毕业设计

基于fpga的毕业设计基于FPGA的毕业设计毕业设计是每个大学生的必修课程,它是对所学知识的综合应用和实践的一次检验。

在计算机科学与技术专业中,基于FPGA(Field-Programmable Gate Array)的毕业设计成为了一种热门选择。

FPGA是一种可编程逻辑器件,具有灵活性和可重构性,因此在设计和实现各种数字电路方面具有广泛的应用。

在我的毕业设计中,我选择了基于FPGA的图像处理系统。

这个项目的目标是实现一个能够对输入图像进行实时处理和增强的系统。

通过使用FPGA,我们可以利用硬件的并行性和高速性能来加快图像处理的速度,同时还可以通过重新编程FPGA来实现不同的图像处理算法。

首先,我需要选择一个合适的FPGA开发板。

市场上有许多不同的选择,包括Xilinx的Zynq系列和Altera的Cyclone系列。

我选择了一块基于Xilinx Zynq的开发板,因为它具有强大的处理能力和丰富的资源。

接下来,我需要设计和实现图像处理算法。

在这个项目中,我选择了一些常见的图像处理算法,如边缘检测、图像滤波和图像分割。

这些算法可以提高图像的质量和清晰度,使其更适合用于其他应用,如目标识别和图像分析。

为了实现这些算法,我需要使用HDL(Hardware Description Language)来描述电路的行为。

Verilog和VHDL是两种常用的HDL语言,我选择了Verilog来描述我的电路。

通过编写Verilog代码,我可以描述图像处理算法的功能和操作,并将其映射到FPGA的逻辑单元和寄存器中。

在设计完成后,我需要进行仿真和验证。

通过使用仿真工具,如ModelSim,我可以模拟电路的行为,并验证其正确性和性能。

如果仿真结果符合预期,我就可以将设计加载到FPGA开发板上进行实际测试。

在实际测试中,我需要将输入图像加载到FPGA开发板上,并观察输出图像的质量和处理速度。

如果结果满足要求,我就可以认为我的基于FPGA的图像处理系统是成功的。

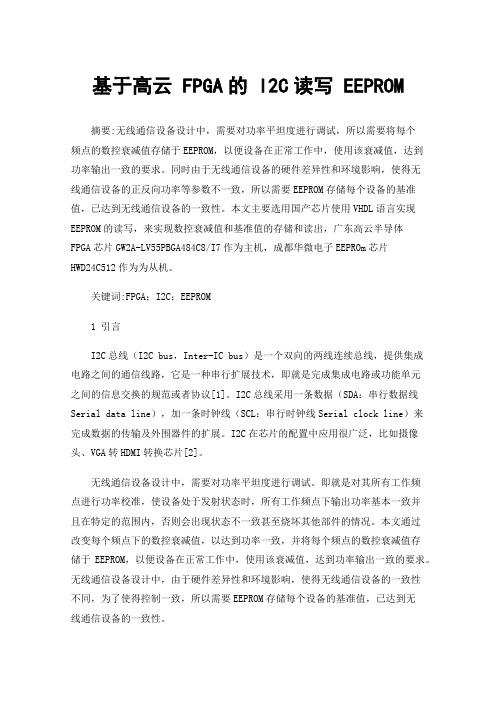

基于高云FPGA的I2C读写EEPROM

基于高云 FPGA的 I2C读写 EEPROM摘要:无线通信设备设计中,需要对功率平坦度进行调试,所以需要将每个频点的数控衰减值存储于EEPROM,以便设备在正常工作中,使用该衰减值,达到功率输出一致的要求。

同时由于无线通信设备的硬件差异性和环境影响,使得无线通信设备的正反向功率等参数不一致,所以需要EEPROM存储每个设备的基准值,已达到无线通信设备的一致性。

本文主要选用国产芯片使用VHDL语言实现EEPROM的读写,来实现数控衰减值和基准值的存储和读出,广东高云半导体FPGA芯片GW2A-LV55PBGA484C8/I7作为主机,成都华微电子EEPROm芯片HWD24C512作为为从机。

关键词:FPGA;I2C;EEPROM1 引言I2C总线(I2C bus,Inter-IC bus)是一个双向的两线连续总线,提供集成电路之间的通信线路,它是一种串行扩展技术,即就是完成集成电路或功能单元之间的信息交换的规范或者协议[1]。

I2C总线采用一条数据(SDA:串行数据线Serial data line),加一条时钟线(SCL:串行时钟线Serial clock line)来完成数据的传输及外围器件的扩展。

I2C在芯片的配置中应用很广泛,比如摄像头、VGA转HDMI转换芯片[2]。

无线通信设备设计中,需要对功率平坦度进行调试。

即就是对其所有工作频点进行功率校准,使设备处于发射状态时,所有工作频点下输出功率基本一致并且在特定的范围内,否则会出现状态不一致甚至烧坏其他部件的情况。

本文通过改变每个频点下的数控衰减值,以达到功率一致,并将每个频点的数控衰减值存储于EEPROM,以便设备在正常工作中,使用该衰减值,达到功率输出一致的要求。

无线通信设备设计中,由于硬件差异性和环境影响,使得无线通信设备的一致性不同,为了使得控制一致,所以需要EEPROM存储每个设备的基准值,已达到无线通信设备的一致性。

本文以实际项目中用于存储参数的EEPROM的读写设计为实例。

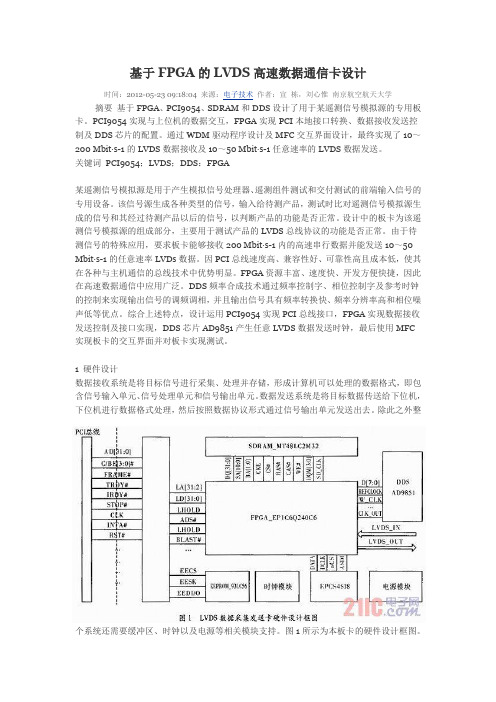

基于FPGA的LVDS高速数据通信卡设计

基于FPGA的LVDS高速数据通信卡设计时间:2012-05-23 09:18:04 来源:电子技术作者:宣栋,刘心惟南京航空航天大学摘要基于FPGA、PCI9054、SDRAM和DDS设计了用于某遥测信号模拟源的专用板卡。

PCI9054实现与上位机的数据交互,FPGA实现PCI本地接口转换、数据接收发送控制及DDS芯片的配置。

通过WDM驱动程序设计及MFC交互界面设计,最终实现了10~200 Mbit·s-1的LVDS数据接收及10~50 Mbit·s-1任意速率的LVDS数据发送。

关键词PCI9054;LVDS;DDS:FPGA某遥测信号模拟源是用于产生模拟信号处理器、遥测组件测试和交付测试的前端输入信号的专用设备。

该信号源生成各种类型的信号,输入给待测产品,测试时比对遥测信号模拟源生成的信号和其经过待测产品以后的信号,以判断产品的功能是否正常。

设计中的板卡为该遥测信号模拟源的组成部分,主要用于测试产品的LVDS总线协议的功能是否正常。

由于待测信号的特殊应用,要求板卡能够接收200 Mbit·s-1内的高速串行数据并能发送10~50 Mbit·s-1的任意速率LVDs数据。

因PCI总线速度高、兼容性好、可靠性高且成本低,使其在各种与主机通信的总线技术中优势明显。

FPGA资源丰富、速度快、开发方便快捷,因此在高速数据通信中应用广泛。

DDS频率合成技术通过频率控制字、相位控制字及参考时钟的控制来实现输出信号的调频调相,并且输出信号具有频率转换快、频率分辨率高和相位噪声低等优点。

综合上述特点,设计运用PCI9054实现PCI总线接口,FPGA实现数据接收发送控制及接口实现,DDS芯片AD9851产生任意LVDS数据发送时钟,最后使用MFC实现板卡的交互界面并对板卡实现测试。

1 硬件设计数据接收系统是将目标信号进行采集、处理并存储,形成计算机可以处理的数据格式,即包含信号输入单元、信号处理单元和信号输出单元。

fpga中memory的实现方式

fpga中memory的实现方式FPGA(Field Programmable Gate Array)中的内存实现方式有多种,其中包括SRAM(Static Random Access Memory)、DRAM(Dynamic Random Access Memory)、ROM(Read-Only Memory)和Flash Memory等。

下面我将分段解释每种内存的实现方式。

1. SRAM(静态随机存取存储器):SRAM是一种高速、易于访问的内存类型。

在FPGA中,SRAM通常用于存储逻辑电路中的寄存器、缓冲器和Look-Up Table(LUT)的配置信息。

它是基于触发器和门电路构建的存储单元,能够在时钟的边沿进行读写操作。

SRAM的实现方式是通过FPGA芯片中的可编程存储单元来存储数据,这些存储单元可以通过逻辑门进行访问。

2. DRAM(动态随机存取存储器):DRAM是一种高密度、低功耗的内存类型,广泛用于FPGA中的存储器实现。

与SRAM相比,DRAM的存储单元由一个电容和一个开关组成,需要定期刷新以保持数据的有效性。

在FPGA中,DRAM通常用于存储大量的数据,例如图像、音频和视频等。

它的实现方式是通过使用FPGA芯片中的存储器单元来存储数据,并通过控制电路来管理存储单元的刷新操作。

3. ROM(只读存储器):ROM是一种只读存储器,用于存储固定的数据和程序。

在FPGA中,ROM通常用于存储程序指令、查找表和常量数据等。

它的实现方式是通过在FPGA芯片中存储数据并使用编程器进行配置,以确保存储的数据不会被修改。

ROM的访问速度比较慢,但在FPGA中可以通过并行读取和查找表的方式来提高访问速度。

4. Flash Memory(闪存存储器):Flash Memory是一种非易失性存储器,可以在掉电情况下保持数据的保存。

在FPGA中,Flash Memory通常用于存储FPGA配置位流以及其他的程序和数据。

毕业设计 基于FPGA数字信号处理

前言PIC16F87X系列是由Microchip公司研制和开发的新产品,可以实现在线调试和在线编程。

并开发了一套在线调试工具MPLAB-ICD和相应的开发平台。

本设计是用PIC16F877单片机设计一个串口显示电路,主要对串口显示的硬件和一些简单的程序进行了介绍。

有PIC16F877的功能和管脚、串口显示的硬件电路图、程序以及程序流程图等。

PIC16F877是由Microchip公司所生产开发的新产品,属于PIC micro系列单片微机,具有Flash program程序内存功能,可以重复烧录程序,适合教学、开发新产品等用途;而其内建ICD(In Circuit Debug)功能,可以让使用者直接在单片机电路或产品上,进行如暂停微处理器执行、观看缓存器内容等,能快速地进行程序除错与开发。

目录第一部分、设计要求- - - - - - - - - - - - - - - - - - - 3一、设计题目 - - - - - - - - - - - - - - - - - - - - - - 3二、设计要求 - - - - - - - - - - - - - - - - - - - - - - 3三、设计步骤 - - - - - - - - - - - - - - - - - - - - - - 3 第二部分、元器件的介绍 - - - - - - - - - - - - - - 3一、PIC16F877的结构介绍- - - - - - - - - - - - - 3 1.PIC16F877的基本功能模块 - - - - - - - - - - - - - - 3 2.PIC16F877的专用功能模块- - - - - - - - - - - - - - 4二、PIC16F877的引脚- - - - - - - - - - - - - - 4 1.系统配置引脚 - - - - - - - - - - - - - - - - - - - - 5 2.I/O功能引脚 - - - - - - - - - - - - - - - - - - - - 6三.特殊内嵌功能- - - - - - - - - - - - - - - - - - - 9四.74LS164的介绍 - - - - - - - - - - - - - - - - - - - - 9第三部分、电路部分- - - - - - - - - - - - - - - - - - - 9一、PIC16F877基本电路- - - - - - - - - - - - - - - 101、PIC振荡频率电路 - - - - - - - - - - - - - - - - - - 102.外加电源与重置电路 - - - - - - - - - - - - - - - - - 12第四部分、程序设计部分- - - - - - - - - - - - - - 12一、程序流程图- - - - - - - - - - - - - - - - - - - - 12二、程序设计- - - - - - - - - - - - - - - - - - - - - 12 第五部分、心得体会- - - - - - - - - - - - - - - - - - 15第一部分、设计要求一、设计题目:PIC16F877的串口显示二、设计要求:1、用PIC16F877串口实现显示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

二线制I2C CMOS 串行EEPROM 的FPGA设计姓名:钱大成学号:080230114院系:物理院电子系2011年1月1日一、课程设计摘要:(1)背景知识:A、基本介绍:二线制I2C CMOS 串行EEPROM AT24C02/4/8/16 是一种采用CMOS 工艺制成的串行可用电擦除可编程只读存储器。

B、I2C (Inter Integrated Circuit)总线特征介绍:I2C 双向二线制串行总线协议定义如下:只有在总线处于“非忙”状态时,数据传输才能被初始化。

在数据传输期间,只要时钟线为高电平,数据线都必须保持稳定,否则数据线上的任何变化都被当作“启动”或“停止”信号。

图1 是被定义的总线状态。

①总线非忙状态(A 段)数据线SDA 和时钟线 SCL 都保持高电平。

②启动数据传输(B 段)当时钟线(SCL)为高电平状态时,数据线(SDA)由高电平变为低电平的下降沿被认为是“启动”信号。

只有出现“启动”信号后,其它的命令才有效。

③停止数据传输(C 段)当时钟线(SCL)为高电平状态时,数据线(SDA)由低电平变为高电平的上升沿被认为是“停止”信号。

随着“停在”信号出现,所有的外部操作都结束。

④数据有效(D 段)在出现“启动”信号以后,在时钟线(SCL)为高电平状态时数据线是稳定的,这时数据线的状态就要传送的数据。

数据线(SDA)上的数据的改变必须在时钟线为低电平期间完成,每位数据占用一个时钟脉冲。

每个数传输都是由“启动”信号开始,结束于“停止”信号。

⑤应答信号每个正在接收数据的EEPROM 在接到一个字节的数据后,通常需要发出一个应答信号。

而每个正在发送数据的EEPROM 在发出一个字节的数据后,通常需要接收一个应答信号。

EEPROM 读写控制器必须产生一个与这个应答位相联系的额外的时钟脉冲。

在EEPROM 的读操作中,EEPROM 读写控制器对EEPROM 完成的最后一个字节不产生应答位,但是应该给EEPROM 一个结束信号。

C、3. 二线制I2C CMOS 串行EEPROM读写操作① EEPROM 的写操作(字节编程方式)所谓EEPROM 的写操作(字节编程方式)就是通过读写控制器把一个字节数据发送到EEPROM 中指定地址的存储单元。

其过程如下:EEPROM 读写控制器发出“启动”信号后,紧跟着送4 位I2C 总线器件特征编码1010 和3 位EEPROM 芯片地址/页地址XXX 以及写状态的R/W 位(=0),到总线上。

这一字节表示在接收到被寻址的EEPROM 产生的一个应答位后,读写控制器将跟着发送1 个字节的EEPROM 存储单元地址和要写入的1 个字节数据。

EEPROM 在接收到存储单元地址后又一次产生应答位以后,读写控制器才发送数据字节,并把数据写入被寻址的存储单元。

EEPROM 再一次发出应答信号,读写控制器收到此应答信号后,便产生“停止”信号。

字节写入帧格式如图2 所示:②二线制I2C CMOS 串行EEPROM 的读操作所谓EEPROM 的读操作即通过读写控制器读取EEPROM 中指定地址的存储单元中的一个字节数据。

串行EEPROM 的读操作分两步进行:读写器首先发送一个“启动”信号和控制字节(包括页面地址和写控制位)到EEPROM,再通过写操作设置EEPROM 存储单元地址(注意:虽然这是读操作,但需要先写入地址指针的值),在此期间EEPROM 会产生必要的应答位。

接着读写器重新发送另一个“启动”信号和控制字节(包括页面地址和读控制位R/W = 1),EEPROM 收到后发出应答信号,然后,要寻址存储单元的数据就从SDA 线上输出。

读操作有三种:读当前地址存储单元的数据、读指定地址存储单元的数据、读连续存储单元的数据。

在这里只介绍读指定地址存储单元数据的操作。

读指定地址存储单元数据的帧格式如图3:(2)实现功能及设计思路:EEPROM是要实现接收来自信号源模型产生的读信号、写信号、并行地址信号、并行数据信号,并把它们转换为相应的串行信号发送到串行EEPROM(AT24C02/4/8/16)的行为模型中去的功能,同时它还发送应答信号(ACK)到信号源模型,以便让信号源来调节发送或接收数据的速度以配合EEPROM模型的接收(写)和发送(读)数据。

其基本设计思路是利用同步有限状态机的设计方法实现,根据串行EEPROM的读写特性,用五个状态时钟完成写操作,用七个状态时钟完成读操作,通过编写EEPROM读写器的模块以及随机读写数据模块,再加上信号产生模块,最终封装在一块完成初步的设计。

二、系统设计部分(1)整体设计的组织结构(2)子单元设计结构:①EEPROM 的行为模型为了设计这样一个电路我们首先要设计一个EEPROM 的Verilog HDL 模型,而设计这样一个模型我们需要仔细地阅读和分析EEPROM 器件的说明书,因为EEPROM 不是我们要设计的对象,而是我们验证设计对象所需要的器件,所以只需设计一个EEPROM 的行为模型,而不需要可综合风格的模型,这就大大简化了设计过程。

下面的Verilog HDL 程序就是这个EEPROM(AT24C02/4/8/16)能完成一个字节数据读写的部分行为模型。

这里只对在操作中用到的信号线进行模拟,对于没有用到的信号线就略去了。

对EEPROM用于基本总线操作的引脚SCL和SDA说明如下:SCL,串行时钟端,这个信号用于对输入和输出数据的同步,写入串行EEPROM的数据用其上升沿同步,输出数据用其下降沿同步;SDA,串行数据(/地址)输入/输出端。

EEPROM的行为模型如下://---------------eeprom.v文件开始-----------------`define timeslice 100module EEPROM(scl,sda);input scl;inout sda;reg out_flag;reg[7:0] memory[2047:0];reg[10:0] address;reg[7:0] memory_buf;reg[7:0] sda_buf;reg[7:0] shift;reg[7:0] addr_byte;reg[7:0] ctrl_byte;reg[7:0] State;integer i;//------------------------------------------parameter r7= 8'b10101111, w7= 8'b10101110, //main7 r6= 8'b10101101, w6= 8'b10101100, //main6 r5= 8'b10101011, w5= 8'b10101010, //main5 r4= 8'b10101001, w4= 8'b10101000, //main4 r3= 8'b10100111, w3= 8'b10100110, //main3 r2= 8'b10100101, w2= 8'b10100100, //main2 r1= 8'b10100011, w1= 8'b10100010, //main1 r0= 8'b10100001, w0= 8'b10100000; //main0 //---------------------------------------------assign sda =(out_flag == 1) ? sda_buf[7] : 1'bz;//---------------------寄存器和存储器初始化--------initialbeginaddr_byte = 0;ctrl_byte = 0;out_flag = 0;sda_buf = 0;State = 2'b00;memory_buf = 0;address = 0;shift = 0;for(i=0;i<2047;i=i+1)memory[i] = 0;end//--------------启动信号-----------------------always@(negedge sda)if(scl == 1)beginState = State + 1;if(State == 2'b11)disable write_to_eeprm;end//----------------主状态机----------------------always@(posedge sda)if(scl == 1)stop_W_R;elsebegincasex(State)2'b01:/******************************************************************************************************/ Beginread_in;if(ctrl_byte == w7 || ctrl_byte == w6 || ctrl_byte == w5|| ctrl_byte == w4 || ctrl_byte == w3 || ctrl_byte == w2 || ctrl_byte == w1 || ctrl_byte == w0 )beginState = 2'b10;write_to_eeprm;endelseState = 2'b00;end2'b11:read_from_eeprm;default:State=2'b00;endcaseend//------------------------操作停止----------------------task stop_W_R;beginState = 2'b00;addr_byte = 0;ctrl_byte = 0;out_flag = 0;sda_buf = 0;endendtask//--------------------读进控制字和存储单元地址--------------task read_in;beginshift_in(ctrl_byte);shift_in(addr_byte);endendtask//--------------------EEPROM的写操作-----------------------task write_to_eeprm;beginshift_in(memory_buf);address ={ctrl_byte[3:1],addr_byte};memory[address] =memory_buf;$display("eeprm-----memory[%0h]=%0h",address,memory[address]); State =2'b00;endendtask//----------------------EEPROM的读操作--------------------task read_from_eeprm;beginshift_in(ctrl_byte);if(ctrl_byte == r7 || ctrl_byte == r6 || ctrl_byte == r5|| ctrl_byte == r4 || ctrl_byte == r3 || ctrl_byte == r2|| ctrl_byte == r1 || ctrl_byte == r0)beginaddress ={ctrl_byte[3:1],addr_byte};sda_buf = memory[address];shift_out;State = 2'b00;endendendtask//---SDA数据线上的数据存入寄存器,数据在SCL的高电平有效----------task shift_in;output[7:0]shift;begin@(posedge scl) shift[7] = sda;@(posedge scl) shift[6] = sda;@(posedge scl) shift[5] = sda;@(posedge scl) shift[4] = sda;@(posedge scl) shift[3] = sda;@(posedge scl) shift[2] = sda;@(posedge scl) shift[1] = sda;@(posedge scl) shift[0] = sda;@(negedge scl)begin#`timeslice ;out_flag =1;sda_buf =0;end@(negedge scl)#`timeslice out_flag = 0;endendtask//---EEPROM存储器中的数据通过SDA数据线输出,数据在SCL低电平时变化-------task shift_out;beginout_flag = 1;for(i=6;i>=0;i=i-1)begin@(negedge scl);#`timeslice;sda_buf = sda_buf<<1;end@(negedge scl) #`timeslice sda_buf[7] = 1;@(negedge scl) #`timeslice out_flag = 0;endendtaskendmodule//-----------------eeprom.v文件结束----------------------------②EEPROM读写器的可综合的Verilog HDL模型下面的程序是一个串行EEPROM读写器的可综合的Verilog HDL模型,它接收来自信号源模型产生的读信号、写信号、并行地址信号、并行数据信号,并把它们转换为相应的串行信号发送到串行EEPROM(AT24C02/4/8/16)的行为模型中去;它还发送应答信号 (ACK)到信号源模型,以便让信号源来调节发送或接收数据的速度以配合EEPROM模型的接收(写)和发送(读)数据。