计数器作业及往届考题

厦门市选修三第一单元《计数原理》测试卷(含答案解析)

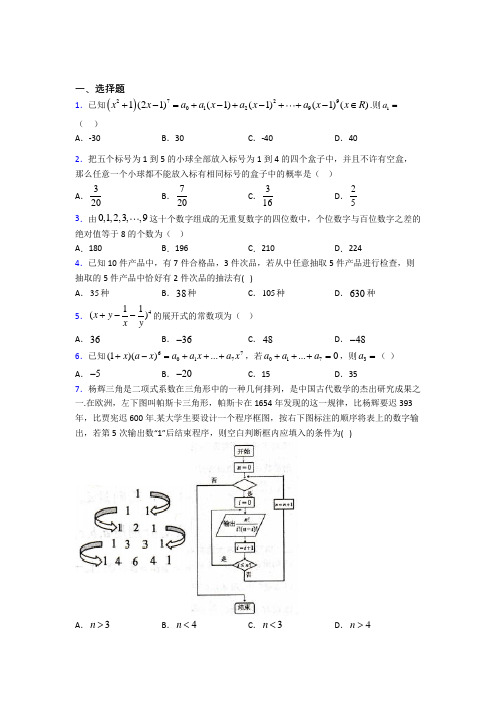

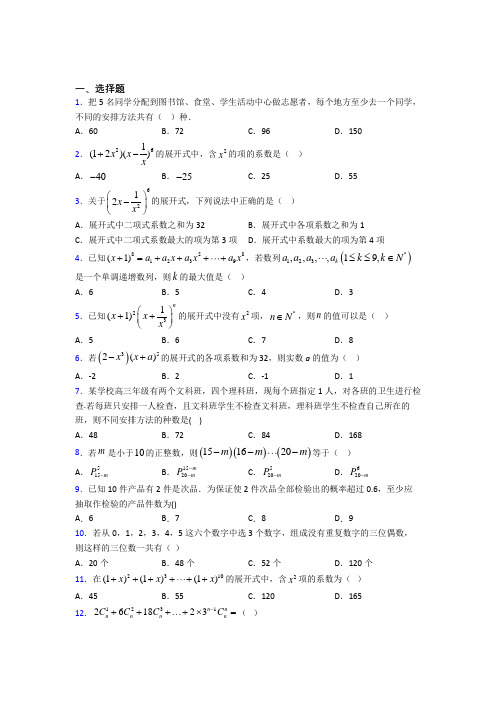

一、选择题1.已知()272901291(21)(1)(1)(1)()x x a a x a x a x x R +-=+-+-++-∈.则1a =( ) A .-30B .30C .-40D .402.把五个标号为1到5的小球全部放入标号为1到4的四个盒子中,并且不许有空盒,那么任意一个小球都不能放入标有相同标号的盒子中的概率是( ) A .320B .720C .316D .253.由0,1,2,3,,9这十个数字组成的无重复数字的四位数中,个位数字与百位数字之差的绝对值等于8的个数为( )A .180B .196C .210D .2244.已知10件产品中,有7件合格品,3件次品,若从中任意抽取5件产品进行检查,则抽取的5件产品中恰好有2件次品的抽法有( ) A .35种 B .38种C .105种D .630种5.411()x y x y+--的展开式的常数项为( ) A .36B .36-C .48D .48-6.已知67017(1)()...x a x a a x a x +-=+++,若017...0a a a +++=,则3a =( )A .5-B .20-C .15D .357.杨辉三角是二项式系数在三角形中的一种几何排列,是中国古代数学的杰出研究成果之一.在欧洲,左下图叫帕斯卡三角形,帕斯卡在1654年发现的这一规律,比杨辉要迟393年,比贾宪迟600年.某大学生要设计一个程序框图,按右下图标注的顺序将表上的数字输出,若第5次输出数“1”后结束程序,则空白判断框内应填入的条件为( )A .3n >B .4n <C .3n <D .4n >8.若,m n 均为非负整数,在做m n +的加法时各位均不进位(例如,134********+=),则称(),m n 为“简单的”有序对,而m n +称为有序数对(),m n 的值,那么值为2964的“简单的”有序对的个数是( ) A .525 B .1050C .432D .8649.若2132020x x C C -+=,则x 的值为( )A .4B .4或5C .6D .4或610.1231261823n nn n n n C C C C -+++⋯+⨯=( )A .2123n +B .()2413n- C .123n -⨯ D .()2313n- 11.在622x x ⎛⎫- ⎪⎝⎭的展开式中,常数项为( ) A .15-B .15C .60-D .60 12.899091100⨯⨯⨯⨯可表示为( )A .10100AB .11100AC .12100AD .13100A第II 卷(非选择题)请点击修改第II 卷的文字说明参考答案二、填空题13.二项式261(2)x x-的展开式中的常数项是_______.(用数字作答)14.设06126201262m m m m x a x a x a x a x x ⎛⎫-=++++ ⎪⎝⎭,则0126m m m m ++++=_________________.15.4名志愿者被随机分配到、、A B C 三个不同的岗位服务,每个岗位至少有一名志愿者,则甲、乙两名志愿者没有分配到同一个岗位服务的概率为______.16.有4位同学参加学校组织的政治、地理、化学、生物4门活动课,要求每位同学各选一门报名(互不干扰),则地理学科恰有2人报名的方案有______. 17.若()()7280128112x x a a x a x a x +-=++++,则127a a a +++的值为__.18.二项式61(2x )x-的展开式中常数项为______(用数字表示). 19.已知25270127(231)(2)x x x a a x a x a x ++-=++++,求01234567a a a a a a a a +++++++=_______20.已知02a π=⎰,若2020220200122020(1)()ax b b x b x b x x R -=+++⋯+∈,则20201222020222b b b ++⋯+的值为__. 三、解答题21.已知二项式*1)(,2)2nn N n x∈≥,若该二项式的展开式中前三项的系数的绝对值成等差数列. (1)求正整数n 的值;(2)求展开式中二项式系数最大项,并指出是第几项?22.在二项式12312x x ⎛⎫+ ⎪⎝⎭的展开式中. (1)求该二项展开式中所有项的系数和的值; (2)求该二项展开式中含4x 项的系数; (3)求该二项展开式中系数最大的项.23.计算:(1)2490n n A A =;(2)383321nn nn C C -++.24.已知:22)nx(n ∈N *)的展开式中第五项的系数与第三项的系数的比是10:1. (1)求展开式中各项系数的和;(2)求展开式中含32x 的项.25.已知数列{}n a 的首项为1,令()()12*12nn n n n a C a C a f n N n C =+++∈.(1)若{}n a 为常数列,求()f n 的解析式;(2)若{}n a 是公比为3的等比数列,试求数列(){}31f n +的前n 项和n S .26.在n的展开式中,前3项的系数的和为73. (1)求n 的值及展开式中二项式系数最大的项;(2)求展开式中的有理项.【参考答案】***试卷处理标记,请不要删除一、选择题 1.B 解析:B 【分析】令1t x =-,得29012927(22)(21)()a a t t t t a t a t x R =++++++∈+,进而得含t 的项为767722(2)tC C t +,从而得解.【详解】令1t x =-,则有:27290129[(1)1][2(1)1]()t t a a t a t a t x R +++-=++++∈,即29012927(22)(21)()a a t t t t a t a t x R =++++++∈+,7(21)t +展开式的通项公式为:77(2)r r C t -,所以29012927(22)(21)()a a t t t t a t a t x R =++++++∈+中含t 的项为:767722(2)30tC C t t +=.故选:B. 【点睛】关键点点睛:本题解题的关键是令1t x =-,转化为求27(22)(21)t t t +++的展开中含t 的项.2.B解析:B 【分析】由题意可以分两类,第一类第5球独占一盒,第二类,第5球不独占一盒,根据分类计数原理得到答案. 【详解】解:第一类,第5球独占一盒,则有4种选择;如第5球独占第一盒,则剩下的三盒,先把第1球放旁边,就是2,3,4球放入2,3,4盒的错位排列,有2种选择,再把第1球分别放入2,3,4盒,有3种可能选择,于是此时有236⨯=种选择; 如第1球独占一盒,有3种选择,剩下的2,3,4球放入两盒有2种选择,此时有236⨯=种选择,得到第5球独占一盒的选择有4(66)48⨯+=种,第二类,第5球不独占一盒,先放14-号球,4个球的全不对应排列数是9;第二步放5号球:有4种选择;9436⨯=,根据分类计数原理得,不同的方法有364884+=种.而将五球放到4盒共有2454240C A ⨯=种不同的办法,故任意一个小球都不能放入标有相同标号的盒子中的概率84724020P == 故选:B . 【点睛】本题主要考查了分类计数原理,关键是如何分步,属于中档题.3.C解析:C 【分析】首先分析可得,个位数字与百位数字之差的绝对值等于8的情况有2种,即:①当个位与百位数字为0,8时,②当个位与百位为1,9时,分别求出所有的情况,由加法原理计算可得答案. 【详解】 分两种情况:(1)个位与百位填入0与8,则有2228A A 个; (2)个位与百位填入1与9,则有722711A A A 个. 则共有2221128277210A A A A A +=个. 故选:C 【点睛】本题考查排列、组合的综合运用,注意分类讨论的运用.4.C解析:C 【分析】根据题意,分2步进行分析,第一步从3件次品中抽取2件次品,第二步从7件正品中抽取3件正品,根据乘法原理计算求得结果. 【详解】根据题意,分2步进行分析:①.从3件次品中抽取2件次品,有23C 种抽取方法,;②.从7件正品中抽取3件正品,有37C 种抽取方法, 则抽取的5件产品中恰好有2件次品的抽法有2337105C C ⨯=种; 故选:C .【点睛】本题考查排列组合的实际应用,注意是一次性抽取,抽出的5件产品步需要进行排列.5.A解析:A 【分析】先对多项式进行变行转化成441()1x y xy ⎛⎫+- ⎪⎝⎭,其展开式要出现常数项,只能第1个括号出22x y 项,第2个括号出221x y项.【详解】∵4444111()1x y x y x y x y x y xy xy ⎛⎫⎛⎫⎛⎫++--=+-=+- ⎪ ⎪ ⎪⎝⎭⎝⎭⎝⎭,∴411x y x y ⎛⎫+-- ⎪⎝⎭的展开式中的常数项为22244222(C (C 361))x y x y ⨯=.故选:A. 【点睛】本题考查二项式定理展开式的应用,考查运算求解能力,求解的关键是对多项式进行等价变形,同时要注意二项式定理展开式的特点.6.A解析:A 【分析】令1x =,可得66017...(11)(1)2(01)a a a a a ++++-=⨯-==,解得1a =,把二项式化为66(1)(1)x x x +--,再利用二项展开式的通项,即可求解. 【详解】由题意,令1x =,可得66017...(11)(1)2(01)a a a a a ++++-=⨯-==,解得1a =,所以二项式为666(1)(1)(1)(1)x x x x x =++---所以展开式中3x 的系数为332266(1)(1)20155C C -+-=-+=-,故选A .【点睛】本题主要考查了二项式定理的应用,其中解答熟练应用赋值法求得二项展开式的系数,以及二项展开式的通项是解答的关键,着重考查了推理与运算能力,属于基础题.7.C解析:C 【分析】 利用()!!!in n C i n i =-,执行程序框图,只要按照程序框图规定的运算方法逐次计算,直到达到输出的值为22C ,即可得到输出条件. 【详解】 利用()!!!in n C i n i =-,执行程序框图,当0n =时,输出的是00C ; 当1n =时,输出的是0111,C C ; 当2n =时,012222,,C C C ;当3n =时,输出的是01233333,,,C C C C ,因为第5次输出数“1”,即2n =,输出22C 后结束程序, 所以3n =时不满足条件,结束程序,所以,空白判断框内应填入的条件为3n <,故选C. 【点睛】本题主要考查程序框图的循环结构流程图,属于中档题. 解决程序框图问题时一定注意以下几点:(1) 不要混淆处理框和输入框;(2) 注意区分程序框图是条件分支结构还是循环结构;(3) 注意区分当型循环结构和直到型循环结构;(4) 处理循环结构的问题时一定要正确控制循环次数;(5) 要注意各个框的顺序,(6)在给出程序框图求解输出结果的试题中只要按照程序框图规定的运算方法逐次计算,直到达到输出条件即可.8.B解析:B 【分析】由题意知本题是一个分步计数原理,第一位取法两种为0,1,2,第二位有10种取法,从0,1,2,3,4,5,6,7,8,9 ,第三位有7种取法,从0,1,2,3,4,5,6取一个数字,第四为有5种,从0,1,2,3,4取一个数字,根据分步计数原理得到结果. 【详解】由题意知本题是一个分步计数原理, 第一位取法3种为0,1, 2,第二位有10种为0,1,2,3,4,5,6,7,8,9 , 第三位有7种为0,1,2,3,4,5,6, 第四为有5种为0,1,2, 3,4根据分步计数原理知共有3×10×7×5=1050个 故选:B. 【点睛】解答排列、组合问题的角度:解答排列、组合应用题要从“分析”、“分辨”、“分类”、“分步”的角度入手. (1)“分析”就是找出题目的条件、结论,哪些是“元素”,哪些是“位置”; (2)“分辨”就是辨别是排列还是组合,对某些元素的位置有、无限制等; (3)“分类”就是将较复杂的应用题中的元素分成互相排斥的几类,然后逐类解决; (4)“分步”就是把问题化成几个互相联系的步骤,而每一步都是简单的排列、组合问题,然后逐步解决.9.D解析:D 【解析】 因为2132020x x C C -+=,所以213x x -=+ 或21320x x -++=,所以4x = 或6x =,选D.10.B解析:B 【解析】1212618323n nn n n C C C C -++++⨯=1220012222(333)(33331)33n n n n n n n n n n n C C C C C C C =⨯+⨯+⨯=⨯+⨯+⨯+⨯-22[(13)1](41)33n n =+-=-选B. 11.D解析:D根据二项展开式的通项公式计算即可求解. 【详解】631216C (1)2rr r r r T x --+=-,令3120r -=,即4r =, ∴常数项为60, 故选:D 【点睛】本题主要考查了二项式定理,二项展开式的通项公式,属于中档题.12.C解析:C 【分析】由排列数的定义即可得出结果. 【详解】12100=10099(100121)1009989⨯⨯⨯-+=⨯⨯⨯A故选:C 【点睛】本题考查了排列数的定义,考查了理解辨析能力和逻辑推理能力,属于一般题目.二、填空题13.60【分析】根据二项式展开式的通项公式求解【详解】有题意可得二项式展开式的通项为:令可得此时【点睛】本题考查二项式定理的应用考查通项公式考查计算能力属于基础题解析:60 【分析】根据二项式展开式的通项公式求解. 【详解】有题意可得,二项式展开式的通项为:()62612316612(1)2rrr r r r rr T C xC xx ---+⎛⎫=-=- ⎪⎝⎭令1230r -=可得4r = ,此时2456260T C ==.【点睛】本题考查二项式定理的应用,考查通项公式,考查计算能力,属于基础题.14.21【分析】由二项式定理得出的展开式的通项进而得出的展开式即可得出答案【详解】的展开式的通项为则故答案为:【点睛】本题主要考查了二项式定理的应用属于中档题解析:21由二项式定理得出622x x ⎛⎫- ⎪⎝⎭的展开式的通项,进而得出622x x ⎛⎫- ⎪⎝⎭的展开式,即可得出答案. 【详解】622x x ⎛⎫- ⎪⎝⎭的展开式的通项为()621231662(2)rrr r r rr T C x C x x --+⎛⎫=-=- ⎪⎝⎭则622x x ⎛⎫- ⎪⎝⎭ 00121192263334405536666666666(2)(2)(2)(2)(2)(2)(2)C x C x C x C x C x C x C x --+++++=-+------0126129630(3)(6)21m m m m ∴+++⋯+=+++++-+-=故答案为:21 【点睛】本题主要考查了二项式定理的应用,属于中档题.15.【分析】要保证每个岗位至少一人人所以首先将四个人分成三组在将三组全排列求出总事件数然后再将甲乙分到不同两组得出甲乙不在同一岗位的基本事件数总而得出概率【详解】因为每个岗位至少有一人所以要将四个人分成解析:56【分析】要保证每个岗位至少一人人,所以首先将四个人分成三组,在将三组全排列求出总事件数,然后再将甲乙分到不同两组,得出甲乙不在同一岗位的基本事件数,总而得出概率. 【详解】因为每个岗位至少有一人,所以要将四个人分成三组,则只能是211、、所以总事件数为: 2113421322=36C C C A A ⋅⋅⋅, 甲乙不在同一岗位的基本事件数:()11232223+=30C C C A ⋅⋅ 所以甲、乙两名志愿者没有分配到同一个岗位服务的概率305=366P =, 故答案为:56. 【点睛】本题考查等可能性事件的概率,利用排列组合公式求出基本事件的总数和满足某个事件的基本事件个数是解答本题的关键.16.【分析】由排列组合及分步原理得到地理学科恰有2人报名的方案即可求解得到答案【详解】由题意先在4位同学中选2人选地理学科共种选法再将剩下的2人在政治化学生物3门活动课任选一门报名共3×3=9种选法故地 解析:54【分析】由排列组合及分步原理得到地理学科恰有2人报名的方案,即可求解,得到答案. 【详解】由题意,先在4位同学中选2人选地理学科,共246C =种选法,再将剩下的2人在政治、化学、生物3门活动课任选一门报名,共3×3=9种选法, 故地理学科恰有2人报名的方案有6×9=54种选法, 故答案为54. 【点睛】本题主要考查了排列、组合,以及分步计数原理的应用,其中解答中认真审题,合理利用排列、组合,以及分步计数原理求解是解答的关键,着重考查了分析问题和解答问题的能力,属于基础题.17.125【解析】分析:令可得;令可得;又故可得的值详解:在中令可得;令可得;又∴点睛:对形如(ax +b)n(ax2+bx +c)m(ab ∈R)的式子求其展开式的各项系数之和常用赋值法只需令x =1即可;对解析:125 【解析】分析:令0x =可得01a =;令1x =,可得01282a a a a ++++=-;又78(2)a =-128=-,故可得127a a a +++的值.详解:在()()7280128112x x a a x a x a x +-=++++中,令0x =,可得01a =; 令1x =,可得01282a a a a ++++=-;又78(2)128a =-=-,∴12721281125a a a +++=-+-=.点睛:对形如(ax +b )n ,(ax 2+bx +c )m (a ,b ∈R)的式子求其展开式的各项系数之和,常用赋值法,只需令x =1即可;对形如(ax +by )n (a ,b ∈R)的式子求其展开式各项系数之和,只需令x =y =1即可.解题时如何赋值,要观察所求和式与差式的特点,根据所求值的式子的特征选择适合的方法.18.-160【解析】二项式的展开式的通项为令可得即展开式中常数项为答案:解析:-160 【解析】二项式612x x ⎛⎫- ⎪⎝⎭的展开式的通项为66621661(2)()(1)2r r r r r r rr T C x C x x ---+=-=-⋅⋅⋅,0,1,2,,6r =.令3r =,可得33346(1)2160T C =-⋅⋅=-,即展开式中常数项为160-.答案:160-19.【分析】在展开式中令可得系数和【详解】令得故答案为:【点睛】本题考查二项式定理在二项展开式中求系数和或部分项的系数项的常用方法是赋值法设二项展开式为则有:奇数项系数和为偶数项系数和为解析:6-【分析】在展开式中令1x =可得系数和.【详解】令1x =得501234567(231)(12)6a a a a a a a a +++++++=++-=-.故答案为:6-.【点睛】本题考查二项式定理,在二项展开式中求系数和或部分项的系数项的常用方法是赋值法,设二项展开式为2012()n n f x a a x a x a x =+++,则有:012(1)n f a a a a =++++, 奇数项系数和为024(1)(1)2f f a a a +-+++=, 偶数项系数和为135(1)(1)2f f a a a --+++=. 20.【分析】根据题意由定积分公式求出的值进而在中分别令和分析可得答案【详解】解:根据题意则令可得:即令可得:又由则;故答案为:【点睛】本题考查二项式定理的应用涉及特殊值的应用关键是求出的值属于基础题解析:1-【分析】根据题意,由定积分公式求出a 的值,进而在20202020(1)(12)ax x -=-中,分别令0x=和1x =,分析可得答案.【详解】解:根据题意,20221(2)24a πππ==⨯⨯⨯=, 则20202020220200122020(1)(12)()ax x b b x b x b x x R -=-=+++⋯+∈,令0x =可得:202001b =,即01b =, 令12x =可得:20202020120220201(12)02222b b b b -⨯=+++⋯+=, 又由01b =,则202012220201222b b b ++⋯+=-;故答案为:1-【点睛】本题考查二项式定理的应用,涉及特殊值的应用,关键是求出a 的值,属于基础题.三、解答题21.(1)8;(2)2358x -,展开式中二项式系数最大项为第五项. 【分析】(1)根据二项展开式的通项,分别求得123,,T T T ,结合等差中项公式,列出方程,即可求解;(2)根据二项式系数的性质,即可求解.【详解】(1)由二项式*1)(,2)2n n N n x ∈≥,可得0212012123111,,222n n n n n n T C T C T C x x x --⎛⎫⎛⎫⎛⎫=-=-=- ⎪ ⎪ ⎪⎝⎭⎝⎭⎝⎭, 因为展开式中前三项的系数的绝对值成等差数列,可得10211224n n n C C C ⨯⨯=+, 整理得1(1)142n n n -=+,即2980n n -+=,解得1n =或8n =. 因为*,2n N n ∈≥,所以8n =. (2)当8n =时,展开式中二项式系数最大项为第五项44425813528T C x x -⎛⎫=-= ⎪⎝⎭. 【点睛】对于二项式中的项的求解方法:(1)求二项式的特定项问题,实质是在考查通项r n r r r n T C a b -=的特点,一把需要建立方程求得r 的值,在将r 的值代回通项,主要r 的取值范围(0,1,2,,)k n =; (2)若n 为偶数时,中间一项(第12n +项)的二项式系数最大; (3)若n 为奇数时,中间一项(第12n +项和第112n ++项)的二项式系数最大. 22.(1)123(2)7920(3)20126720x【分析】(1)令1x =,即可得该二项展开式中所有项的系数和的值;(2)在通项公式中,令x 的幂指数等于4,求得r 的值,可得含4x 项的系数;(3)根据1211312121211112122222r r r r r r r r C C C C ----+-⎧⎨⎩,求得r 的值,可得结论;【详解】(1)令1x =,可得该二项展开式中所有项的系数和的值为123;(2)二项展开式中,通项公式为123641122r r r r T C x --+=,令3644r -=,求得8r =, 故含4x 项的系数为841227920C =.(3)第1r +项的系数为12122rr C -,由1211312121211112122222r r r r r r r r C C C C ----+-⎧⎨⎩,求得4r =, 故该二项展开式中系数最大的项为 384201421(2)()126720C x x x =.【点睛】本题考查二项式定理的应用,二项展开式的通项公式,二项式系数的性质,属于中档题. 23.(1)12;(2)466.【分析】(1)由排列数公式化简后再解方程可得;(2)由组合数性质求得n 的范围,求得n ,再利用组合性质变形后计算.【详解】(1)由2490n n A A =,得90(1)(1)(2)(3)n n n n n n -=---,且4n ≥,解得12n =; (2)由题意383321n n n n -≤⎧⎨≤+⎩,*n N ∈,解得10n =. ∴383321n n n n C C -++283021303130313029314662C C C C ⨯=+=+=+=. 【点睛】本题考查排列数公式和组合数公式,掌握排列数和组合数性质是解题关键.在组合数中一定要注意上标不大于下标.24.(1)1,(2)3216x -【解析】由题意知,第五项系数为44(2)n C ⋅-,第三项的系数22(2)n C ⋅-,则有4422(2)10(2)n n C C ⋅-=⋅-,解8n =. (1)令1x =得各项系数的和为8(12)1-=.(2)通项公式828218822()(2)r r r r r r r r T C C x x ---+=⋅⋅-=⋅-⋅,令83222r r --=, 则1r =,故展开式中含32x 的项为32216T x =-. 25.(1)()21n f n =-;(2)()4413n n S =-. 【分析】(1)由题意得到12()n n n n f n C C C =+++,结合二项展开式的性质,即可求解;(2)先求得1113n n n a a q --==,得到12231()333n n n n n n f n C C C C -=++++,进而求得3()14n f n +=,结合等比数列的前n 项和公式,即可求解.【详解】(1)由{}n a 为常数列,且1n a =,所以120()221n n n n n n n f n C C C C =+++=-=-.(2)由n a 是公比为3的等比数列,且1n a =,所以1113n n n a a q --==,所以12231()333n n n n n n f n C C C C -=++++,所以122333()13333(13)41n n n n n n n n f n C C C C +=++++=+=+, 由等比数列的前n 项和公式,可得()()414441143n n nS -==--. 【点睛】 本题主要考查了二项展开式的性质,以及等比数列的前n 项和公式的应用,其中解答中熟记二项展开式的性质,熟练应用等比数列的n 项和公式是解答的关键,着重考查推理与运算能力.26.(1)6n =,34160x ;(2)3x 和240. 【分析】(1)根据前3项系数和,建立方程求出n ,结合二项式系数的性质进行求解即可. (2)求出展开式的通项公式,结合x 的次数进行求解即可.【详解】(1)依题意得:0122473n n n C C C ++=,即22173n +=,得236n = 6n ∴=-或6n =*n N ∈∴6n =.∴展开式中二项式系数最大的项为第四项,即3333446=160T C x =. (2)展开式的通项公式为:33416=2(),(0,1,...,6)r rr r T C x r -+=,展开式的通项公式为:61662k k k k k T C C -+==334k k x -, 当0k =时,3334k -=,此时为有理项31T x =, 当1k =时,39344k -=,此时不是有理项,当2k =时,33342k -=,此时不是有理项, 当3k =时,33344k -=,此时不是有理项, 当4k =时,3304k -=,此时为有理项5240T =, 当5k =时,33344k -=-,此时不是有理项, 当6k =时,33342k -=-,此时不是有理项, ∴展开式中的有理项为3x 和240.【点睛】本题主要考查二项式定理、有理项等基础知识,考查观察能力、运算求解能力、推理能力和函数与方程思想,属于中档题.。

(常考题)北师大版高中数学高中数学选修2-3第一章《计数原理》检测(包含答案解析)

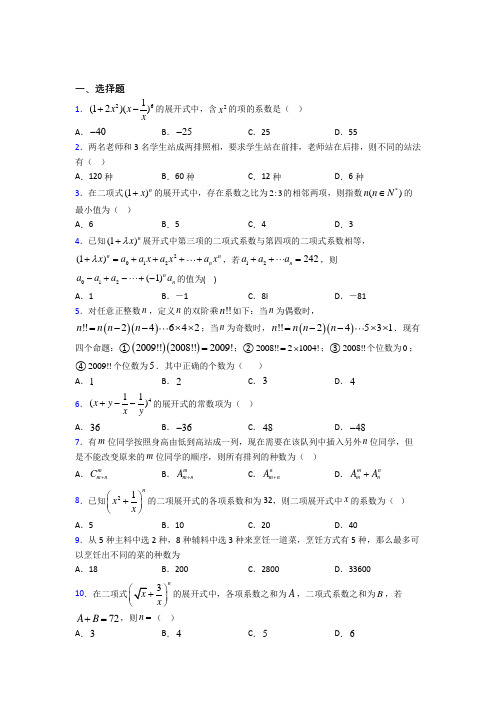

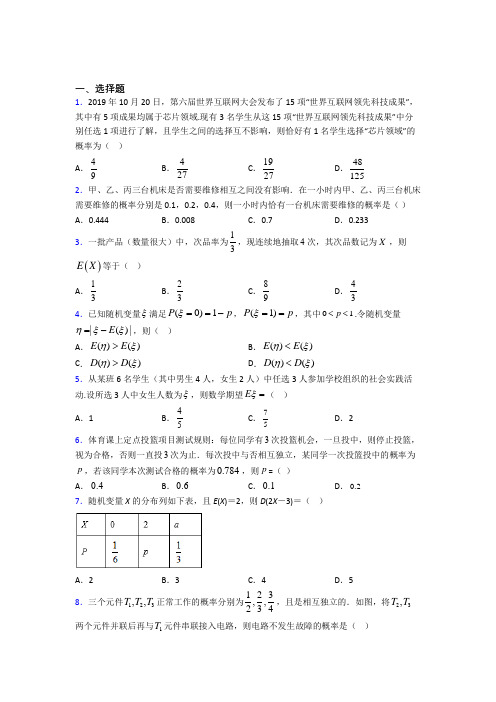

一、选择题1.2019年10月20日,第六届世界互联网大会发布了15项“世界互联网领先科技成果”,其中有5项成果均属于芯片领域.现有3名学生从这15项“世界互联网领先科技成果”中分别任选1项进行了解,且学生之间的选择互不影响,则恰好有1名学生选择“芯片领域”的概率为( ) A .49B .427C .1927D .481252.西大附中为了增强学生对传统文化的继承和发扬,组织了一场类似《诗词大会》的PK 赛,A 、B 两队各由4名选手组成,每局两队各派一名选手PK ,除第三局胜者得2分外,其余各胜者均得1分,每局的负者得0分.假设每局比赛A 队选手获胜的概率均为23,且各局比赛结果相互独立,比赛结束时A 队的得分高于B 队的得分的概率为( ) A .2027B .5281C .1627D .793.已知ξ的分布列如图所示,设2-5ηξ=,则()=E η( )A .12B .13C .23D .324.先后投掷骰子(骰子的六个面分别标有1、2、3、4、5、6个点)两次落在水平桌面后,记正面朝上的点数分别为,x y ,设事件A 为“x y +为偶数”,事件B 为“x y 、中有偶数,且x y ≠”,则概率()P B A =( ) A .13B .12C .14D .255.设1~(10,)B p ξ,2~(10,)B q ξ,且14pq >,则“()()12E E ξξ>”是“()()12D D ξξ<”的( )A .充分不必要条件B .必要不充分条件C .充要条件D .既不充分也不必要条件6.已知随机变量ξ满足(0)1P p ξ==-,(1)P p ξ==,其中01p <<.令随机变量|()|E ηξξ=-,则( )A .()()E E ηξ>B .()()E E ηξ<C .()()D D ηξ>D .()()D D ηξ<7.已知随机变量X 服从正态分布()100,4N ,若()1040.1359P m X <<=,则m 等于 ( )[附:()()0.6826,220.9544P X P X μσμσμσμσ-<<+=-<<+=]A .100B .101C .102D .D .1038.已知随机变量ξ服从正态分布2(4,)N σ,(5)0.89P ξ≤=,则(3)P ξ≤=( ) A .0.89B .0.22C .0.11D .0.789.口袋中装有大小、轻重都无差别的5个红球和4个白球,每一次从袋中摸出2个球,若颜色不同,则为中奖每次摸球后,都将摸出的球放回口袋中,则3次摸球恰有1次中奖的概率为( ). A .80243B .100243C .80729D .10072910.设随机变量X 的分布列为()()1,2,32iP X i i a===,则()2P X ≥= ( ) A .16B .56 C .13D .2311.如下五个命题:①在线性回归模型中,2R 表示解释变量对于预报变量变化的贡献率,在对女大学生的身高预报体重的回归分析数据中,算得20.64R ≈,表明“女大学生的体重差异有64%是由身高引起的”②随机变量的方差和标准差都反映了随机变量取值偏离于均值的平均程度,方差或标准差越小,则随机变量偏离于均值的平均程度越大;③正态曲线关于直线x σ=对称,这个曲线只有当()3,3x σσ∈-时,才在x 轴上方; ④正态曲线的对称轴由μ确定,当μ一定时,曲线的形状由σ决定,并且σ越大,曲线越“矮胖”;⑤若随机变量()~0,1N ξ,且()1,P p ξ>=则()1102P p ξ-<<=-; 其中正确命题的序号是 A .②③B .①④⑤C .①④D .①③④12.将3颗骰子各掷一次,记事件A 为“三个点数都不同”,事件B 为“至少出现一个1点”,则条件概率(A |B)P 和(|)P B A 分别为( ) A .160,291B .560,1891C .601,912D .911,2162二、填空题13.对某个数学题,甲解出的概率为23,乙解出的概率为34,两人独立解题.记X 为解出该题的人数,则E (X )=________.14.某人乘车从A 地到B 地,所需时间(分钟)服从正态分布N (30,100),求此人在40分钟至50分钟到达目的地的概率为__________.参考数据:若2~(,)Z N μσ,则()0.6826P Z μσμσ-<<+=,(22)0.9544P Z μσμσ-<<+=,(33)0.9974P Z μσμσ-<<+=.15.随机变量()2,XN μσ,()()222x f x μσ--=满足:(1)x R ∀∈,()()f x f x ''-=-; (2)()f σ'-=, 则()12P X <≤=________.附:()0.6827P X μσμσ-<≤+≈;()220.9545P X μσμσ-<≤+≈;()330.9973P X μσμσ-<≤+≈.16.某市一次高三年级数学统测,经抽样分析,成绩X 近似服从正态分布()284,N σ,且(7884)0.3P X <≤=.该市某校有400人参加此次统测,估计该校数学成绩不低于90分的人数为____.17.(理)设随机变量ξ的概率分布律如下表所示:其中a ,b ,c 成等差数列,若随机变量ξ的均值为43,则ξ的方差为__________. 18.袋中有5只大小相同的乒乓球,编号为1至5,从袋中随机抽取3只,若以ξ表示取到球中的最大号码,则ξ的数学期望是______. 19.已知随机变量服从正态分布()22,N σ,若(0)0.16P X ≤=,则(24)P X <≤=________.20.一个碗中有10个筹码,其中5个都标有2元,5个都标有5元,某人从此碗中随机抽取3个筹码,若他获得的奖金数等于所抽3个筹码的钱数之和,则他获得奖金的期望为________.三、解答题21.某校准备从报名的6位教师(其中男教师3人,女教师3人)中选3人去边区支教. (1)设所选3人中女教师的人数为X ,求X 的分布列及数学期望;(2)若选派的三人依次到甲、乙、丙三个地方支教,求甲地是男教师的情况下,乙地为女教师的概率.22.近来国内一些互联网公司为了赢得更大的利润、提升员工的奋斗姿态,要求员工实行996''工作制,即工作日早9点上班,晚上21点下班,中午和傍晚最多休息1小时,总计工作10小时以上,并且一周工作6天的工作制度,工作期间还不能请假,也没有任何补贴和加班费.消息一出,社交媒体一片哗然,有的人认为这是违反《劳动法》的一种对员工的压榨行为,有的人认为只有付出超越别人的努力和时间,才能够实现想要的成功,这是提升员工价值的一种有效方式.对此,国内某大型企业集团管理者认为应当在公司内部实行996''工作制,但应该给予一定的加班补贴(单位:百元),对于每月的补贴数额集团人力资源管理部门随机抽取了集团内部的1000名员工进行了补贴数额(单位:百元)期望值的网上问卷调查,并把所得数据列成如下所示的频数分布表:(Ⅰ)求所得样本的中位数(精确到百元);(Ⅱ)根据样本数据,可近似地认为员工的加班补贴X 服从正态分布()251,15N ,若该集团共有员工4000,试估计有多少员工期待加班补贴在8100元以上;(Ⅲ)已知样本数据中期望补贴数额在[]80,100范围内的8名员工中有5名男性,3名女性,现选其中3名员工进行消费调查,记选出的女职员人数为Y ,求Y 的分布列和数学期望.附:若()2~,X N μσ,则()0.6826P X μσμσ-<<+=,()220.9544P X μσμσ-<<+=,()330.9974P X μσμσ-<<+=.23.2020年寒假是特殊的寒假,因为抗击疫情全体学生只能在家进行网上在线学习,为了研究学生在网上学习的情况,某学校在网上随机抽取120名学生对线上教育进行调查,其中男生与女生的人数之比为11:13,其中男生30人对于线上教育满意,女生中有15名表示对线上教育不满意.(1)完成22⨯列联表,并回答能否有99%的把握认为对“线上教育是否满意与性别有关”;8名学生中抽取3名学生,作线上学习的经验介绍,其中抽取男生的个数为ξ,求出ξ的分布列及期望值.参考公式:附:22()()()()()n ad bc K a b a c b d c d -=++++24.某种工业机器生产商,对一次性购买2台机器的客户,推出两种超过质保期后两年内的延保维修优惠方案:方案一:交纳延保金700元,在延保的两年内可免费维修2次,超过2次每次收取维修费200元;方案二:交纳延保金1000元,在延保的两年内可免费维修4次,超过4次每次收取维修费100元.某工厂准备一次性购买2台这种机器.现需决策在购买机器时应购买哪种延保方案,为此搜集并整理了50台这种机器超过质保期后延保两年内维修的次数,得下表: 维修次数 0 1 2 3 台数5201015以这50台机器维修次数的频率代替1台机器维修次数发生的概率.记X 表示这2台机器超过质保期后延保的两年内共需维修的次数. (1)求X 的分布列;(2)以所需延保金及维修费用的期望值为决策依据,工厂选择哪种延保方案更合算? 25.数学是研究数量、结构、变化、空间以及信息等概念的一门科学.在人类历史发展和社会生活中,数学发挥着不可替代的作用,也是学习和研究现代科学技术必不可少的基本工具.(1)为调查大学生喜欢数学命题是否与性别有关,随机选取50名大学生进行问卷调查,当被调查者问卷评分不低于80分则认为其喜欢数学命题,当评分低于80分则认为其不喜欢数学命题,问卷评分的茎叶图如下:依据上述数据制成如下列联表:请问是否有90%的把握认为大学生是否喜欢数学命题与性别有关?参考公式及数据:22(),()()()()n ad bc K n a b c d a b c d a c b d -==+++++++. 20()P K k ≥0.100 0.050 0.010 0.0010k2.7063.841 6.635 10.828(2)在某次命题大赛中,A 同学要进行3轮命题,其在每轮命题成功的概率均为(01)p p <<,各轮命题相互独立,若该同学在3轮命题中恰有2次成功的概率为49,记该同学在3轮命题中的成功次数为X ,求()E X .26.现有甲乙两组学生,分别参加某项体能测试,所得成绩的茎叶图如图.规定测试成绩大于等于90分为优秀,80至89分为良好,60至79分为合格,60分以下为不合格.(1)现从甲组数据中抽取一名学生的成绩,有放回地抽取6次,记抽到优秀成绩的次数为X ,求4P X ;(2)从甲、乙两组学生中任取3名学生,记抽中成绩优秀的学生数为Y ,求Y 的概率分布与数学期望.【参考答案】***试卷处理标记,请不要删除一、选择题 1.A 解析:A 【分析】根据题设分析知:芯片领域被选、不被选的概率分别为13、23,而3名学生选择互不影响,则选择芯片领域的学生数{0,1,2,3}X =,即X 服从二项分布,则有3321()()()33n n n P X n C -==即可求恰好有1名学生选择“芯片领域”的概率.【详解】由题意知,有3名学生且每位学生选择互不影响,从这15项“世界互联网领先科技成果”中分别任选1项,5项成果均属于芯片领域,则: 芯片领域被选的概率为:51153=;不被选的概率为:12133-=;而选择芯片领域的人数{0,1,2,3}X =,∴X 服从二项分布1~3(,3)X B ,3321()()()33nnn P X n C -==,那么恰好有1名学生选择“芯片领域”的概率为123214(1)()()339P X C ===. 故选:A. 【点睛】本题考查了二项分布,需要理解题设条件独立重复试验的含义,并明确哪个随机变量服从二项分布,结合二项分布公式求概率.2.A解析:A 【分析】比赛结束时A 队的得分高于B 队的得分的情况有3种:A 全胜;A 三胜一负、A 第三局胜,另外三局一胜两负.利用独立重复试验的概率公式可求得所求事件的概率. 【详解】比赛结束时A 队的得分高于B 队的得分的情况有3种:A 全胜;A 三胜一负、A 第三局胜,另外三局一胜两负.所以,比赛结束时A 队的得分高于B 队的得分的概率为43232432212122033333327P C C ⎛⎫⎛⎫⎛⎫=+⋅⋅+⋅⋅=⎪ ⎪ ⎪⎝⎭⎝⎭⎝⎭. 故选:A. 【点睛】本题考查概率的求解,考查独立重复试验概率的求解,考查计算能力,属于中等题.3.C解析:C 【分析】根据分布列的性质,求得13m =,由期望的公式,可得17()6E ξ=,再根据()()5E E ηξ=-,即可求解.【详解】由题意,根据分布列的性质,可得1111663m +++=,解得13m =,所以随机变量ξ的期望为111117()123466336E ξ=⨯+⨯+⨯+⨯=, 又由2-5ηξ=,可得172()2563E η=⨯-=. 故选:C. 【点睛】本题主要考查了随机变量的期望的计算,其中解答中熟记分布列的性质和期望的计算公式是解答的关键,着重考查了计算能力.4.A解析:A 【分析】根据题意有()))|(=(n AB P n A A B ,所以只须分析事件A 和事件AB 所包含的基本事件,即可根据公式求出结果. 【详解】解:事件A 中“x y +为偶数”,所以,x y 同奇同偶,共包含22318⨯=种基本事件;事件AB 同时发生,则,x y 都为偶数,且x y ≠,则包含236A =个基本事件;()()61=)13|=(8n AB n A P B A =. 故选:A. 【点睛】本题考查条件概率的应用,考查基本事件的求法,解题的关键是辨析条件概率,属于基础题.5.C解析:C 【分析】根据二项分布的期望和方差公式,可知()110E p ξ=,()210E q ξ=,那么()()12E E ξξ>等价于1010p q >,即p q >,并且()()1101D p p ξ=-,()()2101D q q ξ=-,则()()12D D ξξ>等价于()()101101pp q q -<-,即()()11p p q q -<-,分情况讨论,看这两个条件是否可以互相推出即得. 【详解】由题得,()110E p ξ=,()210E q ξ=,故()()12E E ξξ>等价于1010p q >,即p q >. 又()()1101D p p ξ=-,()()2101D q q ξ=-,故()()12D D ξξ>等价于()()101101p p q q -<-,即()()11p p q q -<-.若p q >,因为14pq >,说明12p >,且()()211124p p p p pq +-⎛⎫-<=< ⎪⎝⎭,故1p q -<,故有1122p q ->-.若12q <,则221122p q ⎛⎫⎛⎫->- ⎪ ⎪⎝⎭⎝⎭,若12q ≥,则自然有11022p q ->->,则221122p q ⎛⎫⎛⎫->- ⎪ ⎪⎝⎭⎝⎭,故221122p q ⎛⎫⎛⎫->- ⎪ ⎪⎝⎭⎝⎭即()()11p p q q -<-.若()()11p p q q -<-,则221122p q ⎛⎫⎛⎫->- ⎪ ⎪⎝⎭⎝⎭,又因为()()1114p p q q pq -<-≤<,1p q -<,即1122p q ->-.若102p -≤,则与221122p q ⎛⎫⎛⎫->- ⎪ ⎪⎝⎭⎝⎭矛盾,故12p >,若12q ≤,则自然有p q >,若12q >,则由221122p q ⎛⎫⎛⎫->- ⎪ ⎪⎝⎭⎝⎭知1122p q ->-,即p q >. 所以是充要条件.故选:C 【点睛】本题综合的考查了离散型随机变量期望方差和不等式,属于中档题.6.D解析:D 【分析】根据题意,列表求得随机变量ξ及η的分布列,可知均为两点分布.由两点分布的均值及方差表示出()(),E D ξξ和()E η()D η,根据01p <<比较大小即可得解. 【详解】随机变量ξ满足(0)1P p ξ==-,(1)P p ξ==,其中01p <<. 则随机变量ξ的分布列为:所以,1E p D p p ==- 随机变量|()|E ηξξ=-,所以当0ξ=时,()E p ηξξ=-=,当1ξ=时,()1E p ηξξ=-=-所以随机变量|()|E ηξξ=-的分布列如下表所示(当0.5p =时,η只有一个情况,概率为1):则1121E p p p p p p =-+-=-()()()()22211121D p p p p p p p p η=--⋅-+---⋅⎡⎤⎡⎤⎣⎦⎣⎦()()2121p p p =--当()()E E ξη=即()21p p p =-,解得12p =.所以A 、B 错误. ()()D D ξη-()()()21121p p p p p =----()22410p p =->恒成立.所以C 错误,D 正确 故选:D 【点睛】本题考查了随机变量的分布列,两点分布的特征及均值和方差求法,属于中档题.7.C解析:C 【分析】 由()()0.1322259P X P X μσμσμσμσ-<<+--<<+=,再根据正态分布的对称性,即可求解. 【详解】由题意,知()()0.6826,220.9544P X P X μσμσμσμσ-<<+=-<<+=, 则()()220.95440.682620.13592P X P X μσμσμσμσ-<<+--<<+-==,所以要使得()1040.1359P m X <<=,则102m =,故选C. 【点睛】本题主要考查了正态分布的应用,其中解答中熟记正态分布的对称性,以及概率的计算方法是解答的关键,着重考查了运算与求解能力,属于基础题.8.C解析:C 【分析】由随机变量ξ服从正态分布()24,6N ,可得这组数据对应的正态曲线的对称轴4μ=,利用正态曲线的对称性,即可得到结论. 【详解】随机变量ξ服从正态分布()24,6N ,∴这组数据对应的正态曲线的对称轴4μ=,()()35P P ξξ∴≤=≥, ()50.89P ξ≤=, ()510.890.11P ξ∴≥=-=,()30.11P ξ∴≤=,故选C.【点睛】本题主要考查正态分布的性质,属于中档题.有关正态分布应用的题考查知识点较为清晰,只要熟练掌握正态分布的性质,特别是状态曲线的对称性以及各个区间概率之间的关系,问题就能迎刃而解.9.A解析:A 【解析】每次摸球中奖的概率为114529C C 2059C 36==,由于是有放回地摸球,故3次摸球相当于3次独立重复实验,所以3次摸球恰有1次中奖的概率2135580C 199243P ⎛⎫=⨯⨯-= ⎪⎝⎭.故选A .点睛:判断一个随机变量是否服从二项分布,要看两点:①是否为n 次独立重复试验,在每次试验中事件A 发生的概率是否均为p ;②随机变量是否为在这n 次独立重复试验中某事件发生的次数,且()()1n kk kn p X k C p p -==-表示在独立重复试验中,事件A 恰好发生k 次的概率.10.B解析:B 【解析】 由概率和为1,可知1231222a a a++=,解得3a =,()P X 2≥=235(2)(3)666P X P X =+==+=选B. 11.B解析:B 【解析】对于命题①,因为2R 表示解释变量对于预报变量变化的贡献率,所以算得20.64R ≈,表明“女大学生的体重差异有64%是由身高引起的”,故该命题①是正确的;对于命题②,由于随机变量的方差和标准差都反映了随机变量取值偏离于均值的整齐程度,因此方差或标准差越小,则随机变量偏离于均值的差异越大,命题②是错误;对于命题③,由于整个正太曲线都在轴上方,所以命题③的说法是不正确的;对于命题④,由于正态曲线的对称轴由μ确定,当μ一定时,曲线的形状由σ决定,并且σ越大,曲线越贴近于轴,因此命题④的说法是正确的;对于命题⑤,由于随机变量()~0,1N ξ,且()1P p ξ>= ,所以依据正太曲线的对称性可得()1P p ξ<-= ,故()1112,P p ξ-<<=- 所以()1102P p ξ-<<=-,即命题⑤是正确的,综上应选答案B 。

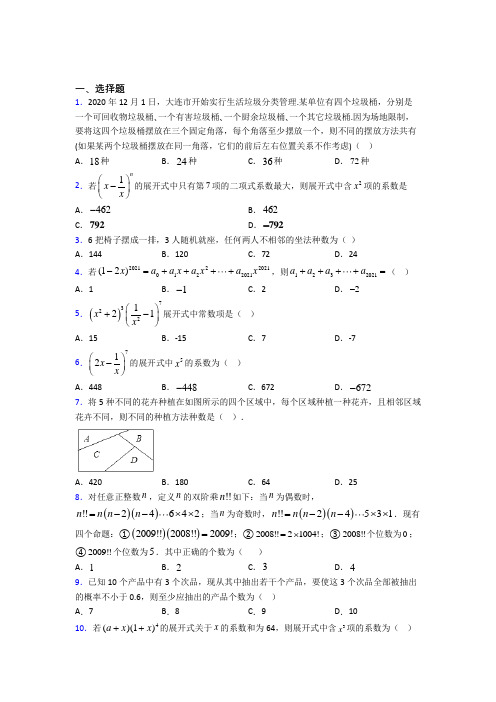

(常考题)北师大版高中数学高中数学选修2-3第一章《计数原理》检测卷(答案解析)(4)

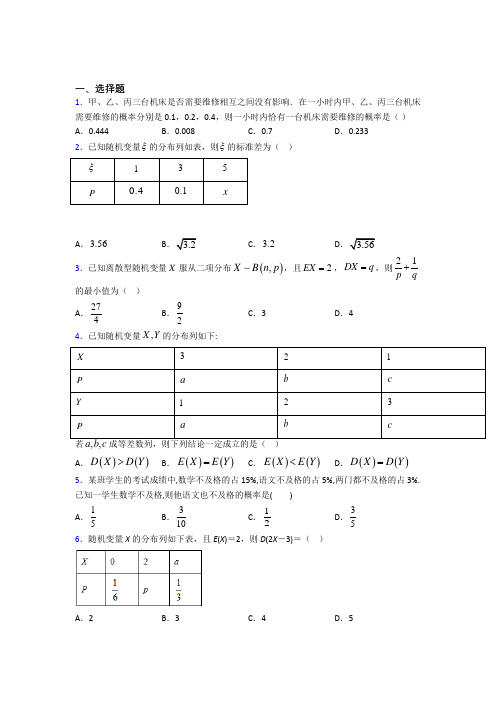

一、选择题1.甲、乙、丙三台机床是否需要维修相互之间没有影响.在一小时内甲、乙、丙三台机床需要维修的概率分别是0.1,0.2,0.4,则一小时内恰有一台机床需要维修的概率是()A.0.444 B.0.008 C.0.7 D.0.2332.西大附中为了增强学生对传统文化的继承和发扬,组织了一场类似《诗词大会》的PK 赛,A、B两队各由4名选手组成,每局两队各派一名选手PK,除第三局胜者得2分外,其余各胜者均得1分,每局的负者得0分.假设每局比赛A队选手获胜的概率均为23,且各局比赛结果相互独立,比赛结束时A队的得分高于B队的得分的概率为()A.2027B.5281C.1627D.793.位于坐标原点的一个质点P按下述规则移动:质点每次移动一个单位,移动的方向为向上或向右,并且向上、向右移动的概率都是12,则质点P移动六次后位于点(2,4)的概率是()A.612⎛⎫⎪⎝⎭B.44612C⎛⎫⎪⎝⎭C.62612C⎛⎫⎪⎝⎭D.6246612C C⎛⎫⎪⎝⎭4.已知离散型随机变量X的分布列为则D(X)的最大值是()A.29B.59C.89D.2095.星期天上午,甲、乙、丙、丁到绿博园、四牟园、湿地公园、蟹岛游玩,每人只去一个地方,设事件A为“4个人去的地方各不相同”,事件B为“甲独自去一个地方”,则()P A B=()A.29B.13C.49D.596.已知某射击运动员射击1次命中目标的概率为0.9,记他在10次独立射击中命中目标的次数为随机变量ξ,则()Dξ=()A.0.09B.9C.1D.0.97.在10个排球中有6个正品,4个次品.从中抽取4个,则正品数比次品数少的概率为()A .542B .435C .1942D .8218.若随机变量ξ满足(1)4E ξ-=,(1)4D ξ-=,则下列说法正确的是 A .4,4E D ξξ=-= B .3,3E D ξξ=-= C .4,4E D ξξ=-=- D .3,4E D ξξ=-=9.若随机变量X 的分布列为:已知随机变量Y aX b =+(,,0)a b R a ∈>,且()10,()4E Y D Y ==,则a 与b 的值为( ) A .10,3a b ==B .3,10a b ==C .5,6a b ==D .6,5a b ==10.根据以往数据统计,某酒店一商务房间1天有客人入住的概率为45,连续2天有客人入住的概率为35,在该房间第一天有客人入住的条件下,第二天也有客人入住的概率为( ) A .13B .12C .35D .3411.口袋中装有大小、轻重都无差别的5个红球和4个白球,每一次从袋中摸出2个球,若颜色不同,则为中奖每次摸球后,都将摸出的球放回口袋中,则3次摸球恰有1次中奖的概率为( ). A .80243B .100243C .80729D .10072912.设随机变量X 的分布列为()()1,2,32iP X i i a===,则()2P X ≥= ( ) A .16B .56 C .13D .23二、填空题13.中国光谷(武汉)某科技公司生产一批同型号的光纤通讯仪器,每台仪器的某一部件由三个电子元件按如图方式连接而成,若元件1或元件2正常工作,且元件3正常工作,则该部件正常工作.由大数据统计显示:三个电子元件的使用寿命(单位:小时)均服从正态分布N (1000,210).且各个元件能否正常工作相互独立.现从这批仪器中随机抽取1000台检测该部件的工作情况(各部件能否正常工作相互独立),那么这1000台仪器中该部件的使用寿命超过1000小时的平均值为______台.14.若随机变量~(2,)X B p ,随机变量~(3,)Y B p ,若4(2)9P X ==,则(21)E Y +的值为_______.15.为响应国家号召,打赢脱贫致富攻坚战,武汉大学团队带领湖北省大悟县新城镇熊湾村村民建立有机、健康、高端、绿色的蔬菜基地,并策划“生产、运输、销售”一体化的直销供应模式,据统计,当地村民两年时间成功脱贫.蔬菜种植基地将采摘的有机蔬菜以每份三斤称重并保鲜分装,以每份10元的价格销售到生鲜超市,每份15元的价格卖给顾客,如果当天前8小时卖不完,则超市通过促销以每份5元的价格卖给顾客(根据经验,当天能够把剩余的有机蔬菜都低价处理完毕,且处理完毕后,当天不再进货).该生鲜超市统计了100天有机蔬菜在每天的前8小时内的销售量(单位:份),制成如下表格(注:*,x y N ∈,且30x y +=).若以100天记录的频率作为每日前8小时销售量发生的概率,该生鲜超市当天销售有机蔬菜利润的期望值为决策依据,若购进17份比购进18份的利润的期望值大,则x 的最小值是________.16.(理)某科技创新大赛设有一、二、三等奖(参与活动的都有奖)且相应奖项获奖的概率是以a 为首项,2为公比的等比数列,相应的奖金分别是以7000元、5600元、4200元,则参加此次大赛获得奖金的期望是_________元.17.甲乙两人进行乒乓球比赛,约定每局胜者得1分,负者得0分,比赛进行到有一人比对方多2分或打满6局时停止.设甲在每局中获胜的概率为23,乙在每局中获胜的概率为13,且各局胜负相互独立,比赛停止时一共已打ξ局, 则ξ的期望值()E ξ=______. 18.若随机变量3~34X B ⎛⎫ ⎪⎝⎭,, 则方差()D x =____________.19.某次测量中,测量结果2(2,)(0) ξN σσ∈>,若ξ在(0,2)内取值的概率为0.4,则ξ在(,4)-∞内取值的概率为__________20.有一批种子的发芽率为0.9,出芽后的幼苗成活率为0.8,在这批种子中,随机抽取一粒,则这粒种子能成长为幼苗的概率为________.三、解答题21.已知一个袋子里有形状一样仅颜色不同的6个小球,其中白球2个,黑球4个.现从中随机取球,每次只取一球.()1若每次取球后都放回袋中,求事件“连续取球四次,至少取得两次白球”的概率; ()2若每次取球后都不放回袋中,且规定取完所有白球或取球次数达到五次就终止游戏,记游戏结束时一共取球X 次,求随机变量X 的分布列与期望.22.2019年春节期间,我国高速公路继续执行“节假日高速公路免费政策”某路桥公司为掌握春节期间车辆出行的高峰情况,在某高速公路收费点记录了大年初三上午9:20~10:40这一时间段内通过的车辆数,统计发现这一时间段内共有600辆车通过该收费点,它们通过该收费点的时刻的频率分布直方图如下图所示,其中时间段9:20~9:40记作区间[)20,40,9:40~10:00记作[)40,60,10:00~10:20记作[)60,80,10:20~10:40记作[)80,100.例如:10点04分,记作时刻64.(1)估计这600辆车在9:20~10:40时间段内通过该收费点的时刻的平均值(同一组中的数据用该组区间的中点值代表);(2)为了对数据进行分析,现采用分层抽样的方法从这600辆车中抽取10辆,再从这10辆车中随机抽取4辆,设抽到的4辆车中,在9:20~10:00之间通过的车辆数为X ,求X 的分布列与数学期望;(3)由大数据分析可知,车辆在每天通过该收费点的时刻T 服从正态分布()2,N μσ,其中μ可用这600辆车在9:20~10:40之间通过该收费点的时刻的平均值近似代替,2σ可用样本的方差近似代替(同一组中的数据用该组区间的中点值代表),已知大年初五全天共有1000辆车通过该收费点,估计在9:46~10:40之间通过的车辆数(结果保留到整数).参考数据:若()2,T N μσ~,则()0.6827P T μσμσ-<≤+=,()220.9545P T μσμσ-<≤+=,()330.9973P T μσμσ-<≤+=.23.甲、乙两人各射击一次,击中目标的概率分别是12和25,假设两人射击是否击中目标,相互之间没有影响,每次射击是否击中目标,相互之间没有影响. (1)求甲射击5次,至少1次未击中目标的概率; (2)求两人各射击3次,甲恰好比乙多击中目标2次的概率24.在全球抗击新冠肺炎疫情期间,我国医疗物资生产企业加班加点生产口罩.防护服、消毒水等防疫物品,保障抗疫一线医疗物资供应,在国际社会上赢得一片赞誉.我国某口罩生产厂商在加大生产的同时,狠抓质量管理,不定时抽查口罩质量,该厂质检人员从某日所生产的口罩中随机抽取了100个,将其质量指标值分成以下五组:[)100,110,[)110,120,[)120130,,[)130140,,[]140,150,得到如下频率分布直方图.(1)规定:口罩的质量指标值越高,说明该口罩质量越好,其中质量指标值低于130的为二级口罩,质量指标值不低于130的为一级口罩.现从样本口罩中利用分层抽样的方法随机抽取8个口罩,再从中抽取3个,记其中一级口罩个数为X ,求X 的分布列及数学期望;(2)在2020年“五一”劳动节前,甲计划在该型号口罩的某网络购物平台上参加A 店一个订单“秒杀”抢购,同时乙计划在该型号口罩的某网络购物平台上参加B 店一个订单“秒杀”抢购,其中每个订单均由()2,n n n *≥∈N 个该型号口罩构成.假定甲、乙两人在A ,B 两店订单“秒杀”成功的概率均为()212n +,记甲,乙两人抢购成功的订单总数量、口罩总数量分别为X ,Y .①求X 的分布列及数学期望()E X ;②当Y 的数学期望()E Y 取最大值时正整数n 的值.25.在一次猜灯谜活动中,共有20道灯谜,两名同学独立竞猜,甲同学猜对了12个,乙同学猜对了8个,假设猜对每道灯谜都是等可能的,试求: (1)任选一道灯谜,恰有一个人猜对的概率; (2)任选一道灯谜,甲、乙都没有猜对的概率.26.某次数学测验共有12道选择题,每道题共有四个选项,且其中只有一个选项是正确的,评分标准规定:每选对1道题得5分,不选或选错得0分. 在这次数学测验中,考生甲每道选择题都按照规则作答,并能确定其中有9道题能选对;其余3道题无法确定正确选项,在这3道题中,恰有2道能排除两个错误选项,另1题只能排除一个错误选项. 若考生甲做这3道题时,每道题都从不能排除的选项中随机挑选一个选项作答,且各题作答互不影响.在本次测验中,考生甲选择题所得的分数记为x (1)求55x =的概率; (2)求x 的分布列和数学期望.【参考答案】***试卷处理标记,请不要删除一、选择题 1.A 解析:A 【分析】直接利用对立事件和独立事件的概率求解. 【详解】因为在一小时内甲、乙、丙三台机床需要维修的概率分别是0.1,0.2,0.4, 所以一小时内恰有一台机床需要维修的概率是:()()()()0.110.210.40.210.110.4p =⨯-⨯-+⨯-⨯- ,()()0.410.210.10.444+⨯-⨯-=.故选:A 【点睛】本题主要考查独立事件和对立事件的概率,属于中档题.2.A解析:A 【分析】比赛结束时A 队的得分高于B 队的得分的情况有3种:A 全胜;A 三胜一负、A 第三局胜,另外三局一胜两负.利用独立重复试验的概率公式可求得所求事件的概率. 【详解】比赛结束时A 队的得分高于B 队的得分的情况有3种:A 全胜;A 三胜一负、A 第三局胜,另外三局一胜两负.所以,比赛结束时A 队的得分高于B 队的得分的概率为43232432212122033333327P C C ⎛⎫⎛⎫⎛⎫=+⋅⋅+⋅⋅=⎪ ⎪ ⎪⎝⎭⎝⎭⎝⎭. 故选:A. 【点睛】本题考查概率的求解,考查独立重复试验概率的求解,考查计算能力,属于中等题.3.C解析:C 【分析】根据题意,质点P 移动六次后位于点(4,2),在移动过程中向右移动4次向上移动2次,即6次独立重复试验中恰有4次发生,由其公式计算可得答案. 【详解】根据题意,易得位于坐标原点的质点P 移动六次后位于点(2,4),在移动过程中向上移动4次向右移动2次,则其概率为4262466111222C P C ⎛⎫⎛⎫⎛⎫ ⎪ ⎪ ⎪⎝⎭⎝⎭⎝⎭==.故选:C . 【点睛】本题考查二项分布与n 次独立重复试验的模型,考查对基础知识的理解和掌握,考查分析和计算能力,属于常考题.4.C解析:C 【分析】根据分布列中概率和为1可得a 的范围和b 的值,再求出,EX DX 的表达式,转化成求二次函数在闭区间的最值问题. 【详解】12133b a a b +-+=⇒=,又110033a a -≥⇒≤≤, 1242()3333EX b a a a b a =+⨯-+⨯=++=+,2221(1)(2)()(3)3DX EX b EX a EX a =-⋅+-⋅-+-⋅2221215()()()()3333a b a a a a =--⋅+-⋅-+-⋅22212215()()()()33333a a a a a =--⋅+-⋅-+-⋅27239a a =-++,对称轴为7163a =>,∴max 1728()9999DX =-++=, 故选:C. 【点睛】本题考查标准差的最值求解,考查函数与方程思想、转化与化归思想,考查逻辑推理能力、运算求解能力,求解时注意将问题转化为函数的最值问题.5.A解析:A 【分析】甲独自去一个景点,有14C 种方法,其余3人去剩下的3个景点,有3327=种方法,由分步计数原理可求得甲独自去一个景点的有1427C ⋅种选择方法.若4个人去的地方各不相同,则属于排列问题,有44A 种.根据条件概率计算公式,即可求出相应的概率. 【详解】甲单独去一个景点有14C 4=种方法,其余3人去剩下的3个景点,有3327=种方法,则甲独自去一个景点,有427108⨯=种方法, 而4个人去的地方各不相同,有4424A =种方法, 则242()1089P A B ==. 故选:A. 【点睛】本题考查了条件概率,分步乘法计数原理,排列问题,属于中档题.6.D解析:D 【分析】在10次独立射击中命中目标的次数为随机变量ξ,则随机变量(10,0.9)B ξ,利用方差的公式,即可求解. 【详解】由题意,在10次独立射击中命中目标的次数为随机变量ξ,则随机变量(10,0.9)B ξ,所以()100.9(10.9)0.9D ξ=⨯⨯-=,故选D . 【点睛】本题主要考查了二项分布的方差的计算,其中解答根据题意得到在10次独立射击中命中目标的次数服从二项分布是解答的关键,着重考查了分析问题和解答问题的能力,属于基础题.7.A解析:A 【解析】分析:根据超几何分布,可知共有410C 种选择方法,符合正品数比次品数少的情况有两种,分别为0个正品4个次品,1个正品3个次品,分别求其概率即可. 详解:正品数比次品数少,有两种情况:0个正品4个次品,1个正品3个次品,由超几何分布的概率可知,当0个正品4个次品时444101210C P C ==当1个正品3个次品时136441024421035C C P C === 所以正品数比次品数少的概率为1452103542+= 所以选A点睛:本题考查了超几何分布在分布列中的应用,主要区分二项分布和超几何分布的不同.根据不同的情况求出各自的概率,属于简单题.8.D解析:D 【解析】分析:由题意结合随机变量的性质整理计算即可求得最终结果. 详解:随机变量ξ满足()14E ξ-=,()14D ξ-=, 则:()214,14E D ξξ-=-=, 据此可得:3,4E D ξξ=-=. 本题选择D 选项.点睛:本题主要考查期望的数学性质,方差的数学性质等知识,意在考查学生的转化能力和计算求解能力.9.C解析:C 【解析】 分析:详解:由随机变量X 的分布列可知,m 10.20.8=-=, ∴()00.210.80.8E X =⨯+⨯=,()10.20.80.16D X =⨯⨯=,∴()()()()2b 10?4E Y aE X D Y a D X =+===, ∴20.8a b 10? 0.164a +==, ∴5,6a b == 故选C点睛:本题考查了随机变量的数学期望及其方差,考查了推理能力与计算能力,属于中档题.10.D解析:D 【分析】首先设出所求的概率为P ,根据题中的条件,可以列出P 所满足的等量关系式,从而求得相应的结果. 【详解】设第二天也有客人入住的概率为P ,根据题意有43=55P ⋅,解得34P =,故选D.【点睛】该题考查的是有关两个事件同时发生的概率问题,也可以看做是有关条件概率的问题,在解题的过程中,需要正确应用公式求得结果.11.A解析:A 【解析】每次摸球中奖的概率为114529C C 2059C 36==,由于是有放回地摸球,故3次摸球相当于3次独立重复实验,所以3次摸球恰有1次中奖的概率2135580C 199243P ⎛⎫=⨯⨯-= ⎪⎝⎭.故选A .点睛:判断一个随机变量是否服从二项分布,要看两点:①是否为n 次独立重复试验,在每次试验中事件A 发生的概率是否均为p ;②随机变量是否为在这n 次独立重复试验中某事件发生的次数,且()()1n kk kn p X k C p p -==-表示在独立重复试验中,事件A 恰好发生k 次的概率.12.B解析:B 【解析】 由概率和为1,可知1231222a a a++=,解得3a =,()P X 2≥=235(2)(3)666P X P X =+==+=选B. 二、填空题13.375【分析】由正态分布可知每个元件正常工作超过10000小时的概率为从而求出部件正常工作超过10000小时的概率再根据二项分布求出平均值【详解】由正态分布可知每个元件正常工作超过10000小时的概解析:375 【分析】由正态分布可知,每个元件正常工作超过10000小时的概率为12,从而求出部件正常工作超过10000小时的概率,再根据二项分布求出平均值. 【详解】由正态分布可知,每个元件正常工作超过10000小时的概率为12, 则部件正常工作超过10000小时的概率为21131228⎡⎤⎛⎫-⨯=⎢⎥ ⎪⎝⎭⎢⎥⎣⎦,又1000台仪器的该部件工作服从二项分布,所以平均值为310003758⨯=台. 故答案为:375. 【点睛】本题考查正态分布和相互独立事件及二项分布,考查逻辑推理能力、运算求解能力.14.5【分析】根据随机变量和求出从而确定随机变量再用均值公式求解【详解】因为随机变量所以所以所以随机变量所以所以故答案为:5【点睛】本题主要考查了随机变量的二项分布还考查了运算求解的能力属于基础题解析:5 【分析】根据随机变量~(2,)X B p ,和2224(2)9===P X C p 求出p ,从而确定随机变量~(3,)Y B p ,再用均值公式求解.【详解】因为随机变量~(2,)X B p ,所以2224(2)9===P X C p 所以23p =所以随机变量2~(3,)3Y B , 所以()2==E Y np所以(21)2()15+=+=E Y E Y 故答案为:5 【点睛】本题主要考查了随机变量的二项分布,还考查了运算求解的能力,属于基础题.15.25【分析】先根据条件求出分布列和期望再根据购进17份比购进18份的利润的期望值大即可得出答案【详解】解:若该超市一天购进17份这种有机蔬菜表示当天的利润(单位:元)那么的分布列为 65 75 85解析:25 【分析】先根据条件求出分布列和期望,再根据“购进17份比购进18份的利润的期望值大”即可得出答案. 【详解】解:若该超市一天购进17份这种有机蔬菜,1Y 表示当天的利润(单位:元),那么1Y 的分布列为1Y 的数学期望()16575100100E Y =⨯+⨯83001085100100x x--+⨯=, 若该超市一天购进18份这种有机蔬菜,2Y 表示当天的利润(单位:元),那么2Y 的分布列为2Y 的数学期望()26070100100E Y =⨯+⨯167480+90100100x -+⨯⨯854020100x-=, ∵购进17份比购进18份的利润的期望值大, ∴830010854020100100x x-->,且30x <,解得2430x <<,又*x ∈N , ∴x 的最小值为25,故答案为:25. 【点睛】本题主要考查离散型随机变量的分布列和期望,属于中档题.16.【分析】根据概率和为1求再根据期望公式求结果【详解】因为所以期望是故答案为:【点睛】本题考查数学期望公式考查基本分析求解能力属基础题 解析:5000【分析】根据概率和为1求a ,再根据期望公式求结果. 【详解】因为12417a a a a ++=∴=所以期望是700056002420041000160024005000a a a ⨯+⨯+⨯=++= 故答案为:5000 【点睛】本题考查数学期望公式,考查基本分析求解能力,属基础题.17.【分析】首先确定所有可能的取值;根据每个取值所对应的情况计算出其所对应的概率从而根据数学期望计算公式求得结果【详解】由题意可知所有可能的取值为:则;;本题正确结果:【点睛】本题考查离散型随机变量的数解析:26681【分析】首先确定ξ所有可能的取值;根据每个取值所对应的情况计算出其所对应的概率,从而根据数学期望计算公式求得结果. 【详解】由题意可知ξ所有可能的取值为:2,4,6则()222152339P ξ⎛⎫⎛⎫==+= ⎪ ⎪⎝⎭⎝⎭;()3311221212204333381P C C ξ⎛⎫⎛⎫⎛⎫⎛⎫==⨯+⨯= ⎪ ⎪ ⎪ ⎪⎝⎭⎝⎭⎝⎭⎝⎭;()520166198181P ξ==--=()520162662469818181E ξ∴=⨯+⨯+⨯=本题正确结果:26681【点睛】本题考查离散型随机变量的数学期望的求解,关键是能够准确求解出随机变量每个取值所对应的概率,从而结合公式直接求得结果,属于常考题型.18.【分析】利用方差公式即可得出答案【详解】结合方差【点睛】本题考查了方差计算公式记住即可 解析:916【分析】利用方差公式()D x npq =,即可得出答案. 【详解】结合方差()31934416D x npq ==⋅⋅=. 【点睛】本题考查了方差计算公式,记住()D x npq =,即可.19.【解析】【分析】先由服从正态分布得出正态曲线关于x=2直线对称于是得到与的关系最后进行求解【详解】由正态分布可知正态分布密度曲线的对称为x=2由得所以填09【点睛】正态曲线:(1)从形态上看正态分布 解析:0.9【解析】 【分析】先由ξ服从正态分布()22,(0)N ξσσ∈>得出正态曲线关于x=2直线对称,于是得到(4)P ξ>与(4)P ξ<的关系,最后进行求解.【详解】由正态分布()22,(0)N ξσσ∈>,可知正态分布密度曲线的对称为x=2,由(02)0.4P ξ<<=,得(24)0.4P ξ<<=,(0)0.1P ξ<=,(0)(4)0.1P P ξξ==所以(4)1(4)0.9P P ξξ=-=,填0.9. 【点睛】正态曲线:(1)从形态上看,正态分布是一条单峰、对称呈钟形的曲线,其对称轴为x=μ,并在x=μ时取最大值。

深圳华师一附中实验学校选修三第一单元《计数原理》测试题(包含答案解析)

一、选择题1.()7322121x x ⎛⎫+- ⎪⎝⎭展开式中常数项是( ) A .15 B .-15 C .7 D .-72.在第二届乌镇互联网大会中, 为了提高安保的级别同时又为了方便接待,现将其中的五个参会国的人员安排酒店住宿,这五个参会国要在a 、b 、c 三家酒店选择一家,且每家酒店至少有一个参会国入住,则这样的安排方法共有 A .96种 B .124种 C .130种D .150种3.二项式2()nx x-的展开式中,第3项的二项式系数比第2项的二项式系数大9,则该展开式中的常数项为( ) A .160-B .80-C .80D .1604.已知(1)n x λ+展开式中第三项的二项式系数与第四项的二项式系数相等,2012(1)n n n x a a x a x a x λ+=++++,若12242n a a a ++⋅⋅⋅=,则012(1)n n a a a a -+-⋅⋅⋅+-的值为( )A .1B .-1C .8lD .-815.在10的展开式中,系数的绝对值最大的项为( ) A .10532B .56638x -C .531058xD .5215x -6.若()()()()()201923201901232019122222x a a x a x a x a x -=+-+-+-+⋅⋅⋅+-,则01232019a a a a a -+-+⋅⋅⋅-的值为( )A .-2B .-1C .0D .17.已知()()()()1521501215111x a a a x a x a x +=+-+-+⋅⋅⋅+-中0a >,若13945a =-,则a 的值为()A .2B .3C .4D .58.设5nx⎛- ⎝的展开式的各项系数之和为M ,二项式系数之和为N ,若M N -=240,则展开式中x 的系数为( )A .300B .150C .-150D .-3009.在下方程序框图中,若输入的a b 、分别为18、100,输出的a 的值为m ,则二项式342()(1)x x x+⋅-的展开式中的常数项是A .224B .336C .112D .56010.在某互联网大会上,为了提升安全级别,将5名特警分配到3个重要路口执勤,每个人只能选择一个路口,每个路口最少1人,最多3人,且甲和乙不能安排在同一个路口,则不同的安排方法有( ) A .180种 B .150种C .96种D .114种11.设(1+x )+(1+x )2+(1+x )3+…+(1+x )n =a 0+a 1x+a 2x 2+…+a n x n ,当a 0+a 1+a 2+…+a n =254时,n 等于( ) A .5B .6C .7D .812.疫情期间,上海某医院安排5名专家到3个不同的区级医院支援,每名专家只去一个区级医院,每个区级医院至少安排一名专家,则不同的安排方法共有( ) A .60种B .90种C .150种D .240种二、填空题13.从3名男医生和5名女医生中,选派3人组成医疗小分队,要求男、女医生都有,则不同的选取方法种数为__________(用数字作答).14.某老师安排甲、乙、丙、丁4名同学从周一至周五值班,每天安排1人,每人至少1天,若甲连续两天值班,则不同的安排方法种数为______.(请用数字作答)15.已知[0,3]a ∈,若62a x x ⎛⎫+ ⎪⎝⎭展开式的常数项的值不大于15,则a 取值范围为________.16.4名志愿者被随机分配到、、A B C 三个不同的岗位服务,每个岗位至少有一名志愿者,则甲、乙两名志愿者没有分配到同一个岗位服务的概率为______.17.同宿舍的6个同学站成一排照相,其中甲只能站两端,乙和丙必须相邻,一共有_____种不同排法(用数字作答)18.已知集合{}08A C =,{}1288,B C C =,{}456888,,C C C C =,若从这三个集合中各取一个元素构成空间直角坐标系中点的坐标,则确定不同点的个数为___________. 19.若()()7280128112x x a a x a x a x +-=++++,则127a a a +++的值为__.20.已知集合S={﹣1,0,1},P={1,2,3,4},从集合S ,P 中各取一个元素作为点的坐标,可作出不同的点共有_____个.三、解答题21.在二项式()32nx -的展开式中.(1)若前3项的二项式系数和等于67,求二项式系数最大的项; (2)若第3项的二项式系数等于第18项的二项式系数,求奇次项系数和.22.已知数列{}n a 是等比数列,11a =,公比是4214x x ⎛⎫+ ⎪⎝⎭的展开式的第二项(按x 的降幂排列).(1)求数列{}n a 的通项n a ; (2)求数列{}n a 前n 项和n S ;(3)若2112nn n n n n A C S C S C S =++⋅⋅⋅+,求n A .23.已知在)23nx的展开式中各项系数的和比它的二项式系数的和大992.(1)求n 的值; (2)求展开式中6x 的项; (3)求展开式中系数最大的项.24.按照下列要求,分别求有多少种不同的方法?(用数字作答) (1) 6个不同的小球放入4个不同的盒子;(2) 6个不同的小球放入4个不同的盒子,每个盒子至少一个小球; (3) 6个相同的小球放入4个不同的盒子,每个盒子至少一个小球; (4) 6个不同的小球放入4个不同的盒子,恰有1个空盒. 25.已知数列{}n a 的首项为1,令()()12*12nn n n n a C a C a f n N n C =+++∈.(1)若{}n a 为常数列,求()f n 的解析式;(2)若{}n a 是公比为3的等比数列,试求数列(){}31f n +的前n 项和n S .26.若2012112nn n x a a x a x a x ⎛⎫-=++++ ⎪⎝⎭,且27a =.(1)求112nx ⎛⎫- ⎪⎝⎭的展开式中二项式系数最大的项; (2)求23112342222n n a a a a a -+++++的值.【参考答案】***试卷处理标记,请不要删除一、选择题 1.B 解析:B 【分析】先求得7211x ⎛⎫- ⎪⎝⎭展开式的通项公式,分别令r =4,5,6,7,求得对应的四项,又()3264226128x x x x +=+++,则()7322121x x ⎛⎫+- ⎪⎝⎭展开式中所有x 的零次幂的系数和即为常数项,计算化简,即可得结果. 【详解】7211x ⎛⎫- ⎪⎝⎭的通项公式为721417721()(1)(1)r r r r r r r T C C x x --+=⋅⋅-=⋅-⋅,令4r =,得446657(1)35T C x x --=⋅-⋅=, 令=5r ,得554467(1)21T C x x --=⋅-⋅=-,令6r =,得662277(1)7T C x x --=⋅-⋅=, 令7r =,得77087(1)1T C x =⋅-⋅=-,又()3264226128x x x x +=+++,所以()7322121x x ⎛⎫+- ⎪⎝⎭展开式中常数项为351(21)6712(1)815⨯+-⨯+⨯+-⨯=-, 故选:B 【点睛】本题考查利用赋值法解决展开式中常数项的问题,考查分析理解,计算求值的能力,属中档题.2.D解析:D 【分析】根据题意,分2步进行分析:①把5个个参会国的人员分成三组,一种是按照1、1、3;另一种是1、2、2;由组合数公式可得分组的方法数目,②,将分好的三组对应三家酒店;由分步计数原理计算可得答案. 【详解】根据题意,分2步进行分析:①、五个参会国要在a 、b 、c 三家酒店选择一家,且这三家至少有一个参会国入住, ∴可以把5个国家人分成三组,一种是按照1、1、3;另一种是1、2、2 当按照1、1、3来分时共有C 53=10种分组方法;当按照1、2、2来分时共有22532215C C A = 种分组方法;则一共有101525+= 种分组方法;②、将分好的三组对应三家酒店,有336A = 种对应方法;则安排方法共有256150⨯= 种;【点睛】本题考查排列组合的应用,涉及分类、分步计数原理的应用,对于复杂一点的计数问题,有时分类以后,每类方法并不都是一步完成的,必须在分类后又分步,综合利用两个原理解决.3.A解析:A 【分析】根据展开式的二项式系数关系求解n ,结合通项即可得到常数项. 【详解】由题第3项的二项式系数比第2项的二项式系数大9,即()21219,,2,9,61802n n n n C C n N n n n n *--=∈≥-=--= 解得:6n =,二项式62()x x-的展开式中,通项6162()r r rr T C x x-+=-,当r =3时,取得常数项,3333162()160T C x x+=-=-. 故选:A 【点睛】此题考查二项式定理,根据二项式系数关系求解参数,根据通项求展开式中的指定项.4.B解析:B 【分析】根据二项式系数的性质,可求得n ,再通过赋值求得0a 以及结果即可. 【详解】因为(1)nx λ+展开式中第三项的二项式系数与第四项的二项式系数相等, 故可得5n =,令0x =,故可得01a =, 又因为125242a a a +++=,令1x =,则()501251243a a a a λ+=++++=, 解得2λ=令1x =-,则()()5501251211a a a a -=-+-+-=-.故选:B. 【点睛】本题考查二项式系数的性质,以及通过赋值法求系数之和,属综合基础题.5.D【分析】根据最大的系数绝对值大于等于其前一个系数绝对值;同时大于等于其后一个系数绝对值;列出不等式求出系数绝对值最大的项; 【详解】10∴二项式展开式为:(10)113211012kk k k T C x x --+⎛⎫⎛⎫=- ⎪ ⎪⎝⎭⎝⎭设系数绝对值最大的项是第1k +项,可得11101011101011221122kk k k k k k k C C C C --++⎧⎛⎫⎛⎫≥⎪ ⎪ ⎪⎪⎝⎭⎝⎭⎨⎛⎫⎛⎫⎪≥ ⎪ ⎪⎪⎝⎭⎝⎭⎩可得11112101112k k k k -⎧≥⎪⎪⎨-⎪≥⋅⎪+⎩,解得81133k ≤≤*k N ∈ ∴3k =在10的展开式中, 系数的绝对值最大的项为:3711310523241215x x T C x -⎛⎫⎛⎫=-= ⎪⎭- ⎪⎝⎭⎝故选:D. 【点睛】本题考查二项展开式中绝对值系数最大项的求解,涉及展开式通项的应用,考查分析问题和解决问题的能力,属于中等题.6.B解析:B 【分析】令1x =,即可求01232019a a a a a -+-+⋅⋅⋅-出的值. 【详解】解:在所给等式中,令1x =,可得等式为()20190123201912a a a a a -=-+-+⋅⋅⋅-,即012320191a a a a a -+-+⋅⋅⋅-=-.【点睛】本题考查二项式定理的展开使用及灵活变求值,特别是解决二项式的系数问题,常采用赋值法,属于中档题.7.A解析:A 【分析】根据()1515[(1)(1)]x a a x +=--++-利用二项展开式的通项公式、二项式系数的性质、以及13945a =-,即可求得a 的值,得到答案. 【详解】由题意,二项式()()()()1521501215111x a a a x a x a x +=+-+-+⋅⋅⋅+-, 又由()1515[(1)(1)]x a a x +=--++-,所以()()()2151501215[(1)(1)]111a x a a x a x a x --++-=+-+-+⋅⋅⋅+-, 其中0a >,由13945a =-,可得:1321315[(1)]945a C a =-⋅-+=-,即2105(1)945a -+=-,即2(1)9a +=,解得2a =, 故选A . 【点睛】本题主要考查了二项式定理的应用,二项展开式的通项公式,二项式系数的性质,其中解答中熟记二项展开式的通项及性质是解答的关键,着重考查了推理与运算能力,属于中档试题.8.B解析:B 【分析】分别求得二项式展开式各项系数之和以及二项式系数之和,代入240M N -=,解出n 的值,进而求得展开式中x 的系数. 【详解】令1x =,得4n M =,故42240n n M N -=-=,解得4n =.二项式为45x⎛⎝,展开式的通项公式为()()134442244515rr rr rr rC x x C x ----⎛⎫⋅⋅-=-⋅⋅⋅ ⎪⎝⎭,令3412r -=,解得2r,故x 的系数为()2422415150C --⋅⋅=.故选B. 【点睛】本小题主要考查二项式展开式系数之和、二项式展开式的二项式系数之和,考查求指定项的系数,属于中档题.9.D解析:D 【分析】由程序图先求出m 的值,然后代入二项式中,求出展开式中的常数项 【详解】由程序图可知求输入18100a b ==,的最大公约数,即输出2m =则二项式为())348332812161x x x x x x x ⎛⎫⎛⎫+⋅-=+++ ⎪ ⎪⎝⎭⎝⎭)81的展开通项为()82181r rr r T C x-+=-要求展开式中的常数项,则当取38x 时,令832r-= 解得2r =,则结果为288224C =,则当取12x 时,令812r-=,解得6r =,则结果为6812336C =,故展开式中的常数项为224336560+=,故选D【点睛】本题考查了运用流程图求两个数的最大公约数,并求出二项式展开式中的常数项,在求解过程中注意题目的化简求解,属于中档题10.D解析:D 【解析】分析:先不管条件甲和乙不能安排在同一个路口,先算出总共的安排方法,再减去甲和乙在同一个路口的情况即可.详解:先不管条件甲和乙不能安排在同一个路口,分两种情况:①三个路口人数情况3,1,1,共有335360C A =种情况;②三个路口人数情况2,2,1,共有2235332290C C A A ⋅=种情况. 若甲乙在同一路口,则把甲乙看作一个整体,则相当于将4名特警分配到三个不同的路口,则有234336C A =种,故甲和乙不能安排在同一个路口,不同的安排方法有609036114+-=种. 故选:D.点睛:本题考查排列、组合的实际应用,考查分析问题、解决问题的能力,注意解题方法的积累,属于中档题.11.C解析:C 【解析】试题分析:观察已知条件a 0+a 1+a 2+…+a n =254,可令(1+x )+(1+x )2+(1+x )3+…+(1+x )n=a0+a1x+a2x2+…+a n x n中的x=1,可得254=2n+1﹣2,解之即可.解:∵(1+x)+(1+x)2+(1+x)3+…+(1+x)n=a0+a1x+a2x2+…+a n x n ∴令x=1得2+22+23+…+2n=a0+a1+a2+…+a n,而a0+a1+a2+…+a n =254==2n+1﹣2,∴n=7故答案为C考点:数列的求和;二项式定理的应用.12.C解析:C【分析】先分组1,2,2和1,1,3再安排得解【详解】5名专家到3个不同的区级医院,分为1,2,2和1,1,3两种情况;分为1,2,2时安排有1223542322C C CAA;分为1,1,3时安排有1133543322C C CAA所以一共有12211333542543332222150 C C C C C CA AA A+=故选:C【点睛】本题考查排列组合问题,先分组再安排是解题关键.二、填空题13.【分析】根据题意分为两类:2男1女和1男2女结合分类计数原理和组合数的计算公式即可求解【详解】由题意从3名男医生和5名女医生中选派3人组成医疗小分队要求男、女医生都有可分为两类:第一类若2男1女共有解析:45【分析】根据题意分为两类:2男1女和1男2女,结合分类计数原理和组合数的计算公式,即可求解.【详解】由题意,从3名男医生和5名女医生中,选派3人组成医疗小分队,要求男、女医生都有,可分为两类:第一类,若2男1女,共有213515C C=种不同的选取方法;第二类,若1男2女,共有123530C C=种不同的选取方法,由分类计数原理,可得不同的选取方法种数为153045+=种.故答案为:45.【点睛】本题主要考查了分类计数原理的应用,以及组合数的计算,其中解答中根据题设条件,合理分类,结合分类计数原理求解是解答的关键,着重考查分析问题和解答问题的能力.14.24【分析】首先在周一到周五任选连续的两天安排甲值班即有种方式其它三天安排乙丙丁值班有种方式由分步计数原理即有总方法有种即可求得所有安排方法数【详解】从周一至周五值班甲连续两天值班乙丙丁每人值班一天解析:24 【分析】首先在周一到周五任选连续的两天安排甲值班,即有14C 种方式,其它三天安排乙、丙、丁值班,有33A 种方式,由分步计数原理,即有总方法有14C 33A 种,即可求得所有安排方法数 【详解】从周一至周五值班,甲连续两天值班,乙、丙、丁每人值班一天,可知 周一到周五任选连续的两天安排给甲值班,则有:14C 种安排方法 甲值班两天除外,其它三天安排乙、丙、丁值班,则有:33A 种安排方法 以上两步是分步计数方法:故总的不同的安排方法为14C 33A = 24种 故答案为:24 【点睛】本题考查了排列组合,应用分步计数原理求总计数,注意其中“对甲连续两天的值班安排”应用了捆绑法15.【分析】由二项式定理及展开式通项得:又所以又时展开式无常数项即a 取值范围为得解【详解】由二项式定理可得:展开式的常数项为又展开式的常数项的值不大于15则又所以又时展开式无常数项即a 取值范围为故答案为 解析:(]0,1【分析】由二项式定理及展开式通项得:41515a ≤,又[]0,3a ∈,所以01a ≤≤,又0a =时,展开式无常数项,即a 取值范围为01a <≤,得解. 【详解】由二项式定理可得:26()a x x+展开式的常数项为422446()()15a C x a x=, 又26()a x x+展开式的常数项的值不大于15, 则41515a ≤, 又[]0,3a ∈, 所以01a ≤≤,又0a =时,展开式无常数项,即a 取值范围为01a <≤, 故答案为:(]0,1. 【点睛】本题考查了二项式定理及展开式通项,属中档题.16.【分析】要保证每个岗位至少一人人所以首先将四个人分成三组在将三组全排列求出总事件数然后再将甲乙分到不同两组得出甲乙不在同一岗位的基本事件数总而得出概率【详解】因为每个岗位至少有一人所以要将四个人分成解析:56【分析】要保证每个岗位至少一人人,所以首先将四个人分成三组,在将三组全排列求出总事件数,然后再将甲乙分到不同两组,得出甲乙不在同一岗位的基本事件数,总而得出概率. 【详解】因为每个岗位至少有一人,所以要将四个人分成三组,则只能是211、、所以总事件数为: 2113421322=36C C C A A ⋅⋅⋅, 甲乙不在同一岗位的基本事件数:()11232223+=30C C C A ⋅⋅ 所以甲、乙两名志愿者没有分配到同一个岗位服务的概率305=366P =, 故答案为:56. 【点睛】本题考查等可能性事件的概率,利用排列组合公式求出基本事件的总数和满足某个事件的基本事件个数是解答本题的关键.17.【分析】设甲乙丙之外的三人为ABC 将乙和丙看作一个整体与ABC 三人全排列然后排甲甲只能在两端有2种站法利用分步乘法计数原理可求出答案【详解】设甲乙丙之外的三人为ABC 将乙和丙看作一个整体与ABC 三人 解析:96【分析】设甲乙丙之外的三人为A 、B 、C ,将乙和丙看作一个整体,与A 、B 、C 三人全排列,然后排甲,甲只能在两端,有2种站法,利用分步乘法计数原理可求出答案. 【详解】设甲乙丙之外的三人为A 、B 、C ,将乙和丙看作一个整体,与A 、B 、C 三人全排列,有2424A A 48=种,甲只能在两端,甲有2种站法,则共有48296⨯=种排法.【点睛】本题考查了排列组合,考查了相邻问题“捆绑法”的运用,属于基础题.18.【分析】由组合数的性质得出先求出无任何限制条件下所确定的点的个数然后考虑坐标中有两个相同的数的点的个数将两数作差可得出结果【详解】由组合数的性质得出不考虑任何限制条件下不同点的个数为由于坐标中同时含 解析:33【分析】由组合数的性质得出2688C C =,先求出无任何限制条件下所确定的点的个数,然后考虑坐标中有两个相同的数的点的个数,将两数作差可得出结果. 【详解】由组合数的性质得出2688C C =,不考虑任何限制条件下不同点的个数为11323336C C A =, 由于2688C C =,坐标中同时含28C 和68C 的点的个数为133C =,综上所述:所求点的个数为36333-=,故答案为33. 【点睛】本题考查排列组合思想的应用,常用的就是分类讨论和分步骤处理,本题中利用总体淘汰法,可简化分类讨论,考查分析问题和解决问题的能力,属于中等题.19.125【解析】分析:令可得;令可得;又故可得的值详解:在中令可得;令可得;又∴点睛:对形如(ax +b)n(ax2+bx +c)m(ab ∈R)的式子求其展开式的各项系数之和常用赋值法只需令x =1即可;对解析:125 【解析】分析:令0x =可得01a =;令1x =,可得01282a a a a ++++=-;又78(2)a =-128=-,故可得127a a a +++的值.详解:在()()7280128112x x a a x a x a x +-=++++中,令0x =,可得01a =; 令1x =,可得01282a a a a ++++=-;又78(2)128a =-=-,∴12721281125a a a +++=-+-=.点睛:对形如(ax +b )n ,(ax 2+bx +c )m (a ,b ∈R)的式子求其展开式的各项系数之和,常用赋值法,只需令x =1即可;对形如(ax +by )n (a ,b ∈R)的式子求其展开式各项系数之和,只需令x =y =1即可.解题时如何赋值,要观察所求和式与差式的特点,根据所求值的式子的特征选择适合的方法.20.23【解析】试题分析:由题意知本题是一个分步计数问题S 集合中选出一个数字共有3种选法P 集合中选出一个数字共有4种结果取出的两个数字可以作为横标和纵标因此要乘以2去掉重复的数字得到结果解:由题意知本题解析:23 【解析】试题分析:由题意知本题是一个分步计数问题,S 集合中选出一个数字共有3种选法,P 集合中选出一个数字共有4种结果,取出的两个数字可以作为横标和纵标,因此要乘以2,去掉重复的数字,得到结果.解:由题意知本题是一个分步计数问题, 首先从S 集合中选出一个数字共有3种选法, 再从P 集合中选出一个数字共有4种结果,取出的两个数字可以作为横标,也可以作为纵标,共还有一个排列, ∴共有C 31C 41A 22=24,其中(1,1)重复了一次.去掉重复的数字有24﹣1=23种结果, 故答案为23考点:计数原理的应用.三、解答题21.(1)5610777536T x =-,677185024T x =;(2)19152+.【分析】(1)由题意得01267n n n C C C ++=,化简为21320n n +-=,解得n 的值,可以写出结果;(2)由题意得217n n C C =,解得n =19,在()1932x -的展开式中,分别令1x =和1x =-,得到2个式子,相减可得要求式子的值. 【详解】(1)在二项式()32nx -的展开式中,前3项的二项式系数和为01267n n n C C C ++=,化简为21320n n +-=,解得11n =或12n =-(舍),二项式为()1132x -,展开式共有12项,∴则展开式中二项式系数最大的项为第6和第7项,()55656113210777536T C x x =-=-和()6656711327185024T C x x =-=.(2)当第3项的二项式系数等于第18项的二项式系数,得217n n C C =,计算得19n =,二项式为()1932x -.在()192319012319..32.a a x a x a x x a x =+++++-中, 令1x =,则0123191...a a a a a =+++++,①令1x =-,则190123195...a a a a a =-+-+-,②①+②得()1902418152...a a a a +=++++,奇次项系数和为19152+.【点睛】本题主要考查二项式定理的应用,二项展开式的通项公式,二项式系数的性质,展开式的奇次项系数和,属于中档题.22.(1)1n n a x -=;(2),11,11n n n x S x x x =⎧⎪=⎨-≠⎪-⎩;(3)()12,121,11n nn n n x A x x x -⎧⋅=⎪=⎨-+≠⎪-⎩. 【分析】(1)利用二项式定理求得4214x x ⎛⎫+ ⎪⎝⎭的展开式的第二项,可求得数列{}n a 的公比,利用等比数列的通项公式可求得n a ;(2)分1x =和1x ≠两种情况讨论,利用等比数列的求和公式可求得n S ; (3)分1x =和1x ≠两种情况讨论,利用二项式定理可求得n A 的表达式. 【详解】(1)4214x x ⎛⎫+ ⎪⎝⎭的展开式的第二项为1324214T C x x x =⋅⋅=,所以,数列{}n a 的公比为x ,则111n n n a a x x --=⋅=;(2)当1x =时,则1n a =,n S n =; 当1x ≠时,()11111n n na x x S xx--==--.综上所述,,11,11n n n x S x x x=⎧⎪=⎨-≠⎪-⎩;(3)当1x =时,n S n =,()()()()111!!!!1!!k k k nk nn n n n C S kC k nC k n k k n k --⋅-==⋅==---,此时,()101112112112nn n n n n n n n n n A C S C C n C S S C C n -----=++⋅=++=+⋅⋅⋅+; 当1x ≠时,()()()()()1220120122111n n nn nn n n n n n n n n n n C x C x C x C C C C C C x C x C x ⋅-+⋅-++⋅-=++++-++++()21nn x =-+,此时,()1212211nn n n n n nn xA x C S C S C S =++⋅⋅-+=+-⋅. 综上所述,()12,121,11n nn n n x A x x x -⎧⋅=⎪=⎨-+≠⎪-⎩. 【点睛】本题考查等比数列通项的求解、等比数列求和以及利用二项式定理求和,考查计算能力,属于中等题.23.(1)5n =;(2)6390T x =;(3)2635405T x=【分析】(1)代入1x =求得各项系数和为4n ,又二项式系数和为2n ,根据二者相差992可得方程,解方程求得n ;(2)根据展开式通项公式,令x 的幂指数等于6,求得r ,进而可得所求项;(3)由展开式通项可知系数通项为53r rC ,利用115511553333r r r r r r r r C C C C ++--⎧≥⎨≥⎩解得r ,进而求得系数最大的项. 【详解】(1))23nx展开式各项系数的和为:)2314nn ⨯=;二项式系数的和为:2n又各项系数的和比二项式系数的和大99242992n n ∴-=,即()2229920n n --=,解得232n =5n ∴=(2))523x展开式的通项公式为:()10452315533r rrr r rr TCx C x+-+==令10463r+=,解得2r展开式中6x 的项为:226635390T C x x == (3)设第1r +项的系数为1r t +,则153r rr t C +=由121r r r r t t t t +++≥⎧⎨≥⎩,即115511553333r r r r r rr r C C C C ++--⎧≥⎨≥⎩ 解得:7922r ≤≤,所以4r = 展开式系数最大项为:26264433553405T C xx ==【点睛】本题考查二项式定理的应用,涉及到二项式系数和、各项系数和的求解、特定项系数的求解以及最大项的求解问题,关键在于能够熟练运用展开式的通项公式,属于常规题型. 24.(1)4096(2)1560(3)10(4)2160 【解析】试题分析:解 (1)46=4 096; 3分(2)2211346421642222C C C C C A A A ⎛⎫+ ⎪⎝⎭=1 560; 6分 (3) 24C +4=10;或25C =10; 9分(4) 222321236426315433C C C C C C C A A ⎛⎫++ ⎪⎝⎭=2 160. 12分 考点:排列组合的运用点评:主要是考查了排列组合的运用,属于中档题. 25.(1)()21n f n =-;(2)()4413nn S =-. 【分析】(1)由题意得到12()n n n n f n C C C =+++,结合二项展开式的性质,即可求解;(2)先求得1113n n n a a q --==,得到12231()333n nn n n n f n C C C C -=++++,进而求得3()14n f n +=,结合等比数列的前n 项和公式,即可求解.【详解】(1)由{}n a 为常数列,且1n a =,所以120()221n n n n n n n f n C C C C =+++=-=-.(2)由n a 是公比为3的等比数列,且1n a =,所以1113n n n a a q --==, 所以12231()333n nn n n n f n C C C C -=++++,所以122333()13333(13)41n nn n n n n n f n C C C C +=++++=+=+,由等比数列的前n 项和公式,可得()()414441143n nn S -==--. 【点睛】本题主要考查了二项展开式的性质,以及等比数列的前n 项和公式的应用,其中解答中熟记二项展开式的性质,熟练应用等比数列的n 项和公式是解答的关键,着重考查推理与运算能力. 26.(1)4358x (2)12-【分析】(1)由二项展开式通项公式得出2a ,然后由27a =求出n ,根据二项式系数的性质得出最大项的项数,再求出该项即可;(2)在展开式中令0x =可得0a ,令2x =再结合0a 可得结论. 【详解】(1)因为22222321124n n T C x C x a x ⎛⎫=-== ⎪⎝⎭,且27a =, 所以21(1)7(8)(7)048n n n C n n -==⇒-+=,解得8n =或7n =-(舍), 故112nx ⎛⎫- ⎪⎝⎭的展开式中二项式系数最大的项为第5项,为4544813528T C x x ⎛⎫=-=⎪⎝⎭;(2)令0x =,可知01a =,令2x =,得23401234022222n n a a a a a a =++++++,所以2341234222221n n a a a a a +++++=-,故()231234123412341122222222222n n n n a a a a a a a a a a -+++++=+++++=-. 【点睛】本题考查二项式定理,考查二项式系数的性质,考查赋值法求系数的和.属于基本题型.。

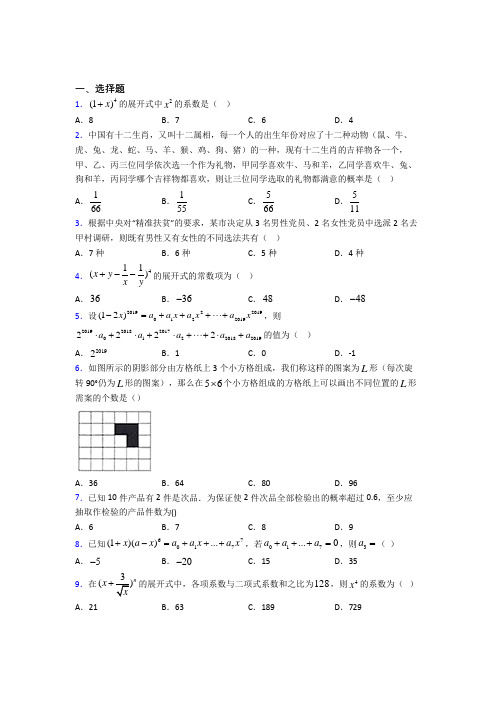

(必考题)高中数学高中数学选修2-3第一章《计数原理》测试题(有答案解析)(2)

一、选择题1.甲、乙、丙三台机床是否需要维修相互之间没有影响.在一小时内甲、乙、丙三台机床需要维修的概率分别是0.1,0.2,0.4,则一小时内恰有一台机床需要维修的概率是( ) A .0.444B .0.008C .0.7D .0.2332.已知()~,X B n p ,且()2E X =,()43D X =,则n =( ) A .5B .6C .7D .83.孔子曰“三人行,必有我师焉.”从数学角度来看,这句话有深刻的哲理,古语说三百六十行,行行出状元,假设有甲、乙、丙三人中每一人,在每一行业中胜过孔圣人的概率为1%,那么甲、乙、丙三人中至少一人在至少一行业中胜过孔圣人的概率为( )(参考数据:3600.990.03≈,3600.010≈,30.970.912673≈) A .0.0027%B .99.9973%C .0D .91.2673%4.将三枚质地均匀的骰子各掷一次,设事件A =“三个点数之和等于15”,B =“至少出现一个5点”,则概率()|P A B 等于( ) A .5108B .113C .17D .7105.在如图所示的正方形中随机投掷1000个点,则落入阴影(曲线为正态分布(0,1)N 的密度曲线)的点的个数的估计值为( )(附:若2~(,)X N μσ,则()0.6826P X μσμσ-<+=,(22)0.9544P X μσμσ-<+=)A .239B .272C .341D .4776.随机变量X 的分布列如表所示,若1()3E X =,则(32)D X -=( ) X 1-1P16abA .59B .53C .5D .77.下列命题中真命题是( )(1)在18的二项式展开式中,共有4项有理项;(2)若事件A 、B 满足()0.15P A =,()0.60P B =,()0.09P AB =,则事件A 、B 是相互独立事件;(3)根据最近10天某医院新增疑似病例数据,“总体均值为2,总体方差为3”,可以推测“最近10天,该医院每天新增疑似病例不超过7人”. A .(1)(2)B .(1)(3)C .(2)(3)D .(1)(2)(3)8.从某班6名学生(其中男生4人,女生2人)中任选3人参加学校组织的社会实践活动.设所选3人中女生人数为ξ,则数学期望E ξ=( ) A .1B .45C .75D .29.已知在5件产品中混有2件次品,现需要通过逐一检测直至查出2件次品为止,每检测一件产品的费用是10元,则所需检测费的均值为( ) A .32元B .34元C .35元D .36元10.设X 为随机变量,且1:,3X B n ⎛⎫ ⎪⎝⎭,若随机变量X 的方差()43D X =,则()2P X == ( )A .4729B .16C .20243D .8024311.如下五个命题:①在线性回归模型中,2R 表示解释变量对于预报变量变化的贡献率,在对女大学生的身高预报体重的回归分析数据中,算得20.64R ≈,表明“女大学生的体重差异有64%是由身高引起的”②随机变量的方差和标准差都反映了随机变量取值偏离于均值的平均程度,方差或标准差越小,则随机变量偏离于均值的平均程度越大;③正态曲线关于直线x σ=对称,这个曲线只有当()3,3x σσ∈-时,才在x 轴上方; ④正态曲线的对称轴由μ确定,当μ一定时,曲线的形状由σ决定,并且σ越大,曲线越“矮胖”;⑤若随机变量()~0,1N ξ,且()1,P p ξ>=则()1102P p ξ-<<=-; 其中正确命题的序号是 A .②③B .①④⑤C .①④D .①③④12.小明的妈妈为小明煮了 5 个粽子,其中两个腊肉馅三个豆沙馅,小明随机取出两个,事件‘‘"A 取到的两个为同一种馅,事件‘‘"B =取到的两个都是豆沙馅,则()P B A =∣ ( )A .14B .34C .110D .310二、填空题13.若有一个不透明的袋子内装有大小、质量相同的6个小球,其中红球有2个,白球有4个,每次取两个,取后放回,连续取三次,设随机变量ξ表示取出后都是白球的次数,则()E ξ=______ .14.中国光谷(武汉)某科技公司生产一批同型号的光纤通讯仪器,每台仪器的某一部件由三个电子元件按如图方式连接而成,若元件1或元件2正常工作,且元件3正常工作,则该部件正常工作.由大数据统计显示:三个电子元件的使用寿命(单位:小时)均服从正态分布N (1000,210).且各个元件能否正常工作相互独立.现从这批仪器中随机抽取1000台检测该部件的工作情况(各部件能否正常工作相互独立),那么这1000台仪器中该部件的使用寿命超过1000小时的平均值为______台.15.测量某一目标的距离时,所产生的随机误差X 服从正态分布()220,10N ,如果独立测量3次,至少一次测量误差在()0,30内的概率是__________.附参考数据:()0.68P X μδμδ-<≤+=,()220.95P X μδμδ-<≤+=,()330.99P X μδμδ-<≤+=,20.1850.03=,30.1850.006=,20.8150.66=,30.8150.541=.16.一批排球中正品有m 个,次品有n 个,()10m n m n +=≥,从这批排球中每次随机 取一个,有放回地抽取10次,X 表示抽到的次品个数若 2.1DX =,从这批排球中随机一次取两个,则至少有一个次品的概率p =___________ 17.已知随机变量服从正态分布()22,N σ,若(0)0.16P X ≤=,则(24)P X <≤=________.18.已知随机变量X 服从正态分布()2,1N . 若()130.6826P X ≤≤=,则()3P X >等于______________.19.有一批种子的发芽率为0.9,出芽后的幼苗成活率为0.8,在这批种子中,随机抽取一粒,则这粒种子能成长为幼苗的概率为________.20.已知某次数学考试中,学生的成绩X 服从正态分布,即()~N 85,225X ,则这次考试中,学生成绩落在区间[]100,130之内的概率为____________.(注:()0.6826P X μσμσ-<<+=,()220.9544P X μσμσ-<<+=,()330.9974P X μσμσ-<<+=)三、解答题21.某市有两家共享单车公司,在市场上分别投放了黄、蓝两种颜色的单车,已知黄、蓝两种颜色的单车的投放比例为2:1.监管部门为了了解两种颜色的单车的质量,决定从市场中随机抽取5辆单车进行体验,若每辆单车被抽取的可能性相同. (1)求抽取的5辆单车中有2辆是蓝色颜色单车的概率;(2)在骑行体验过程中,发现蓝色单车存在一定质量问题,监管部门决定从市场中随机地抽取一辆送技术部门作进一步抽样检测,并规定若抽到的是蓝色单车,则抽样结束,若抽取的是黄色单车,则将其放回市场中,并继续从市场中随机地抽取下一辆单车,并规定抽样的次数最多不超过4次.在抽样结束时,已取到的黄色单车以ξ表示,求ξ的分布列. 22.某知名电脑品牌为了解客户对其旗下的三种型号电脑的满意情况,随机抽取了一些客户进行回访,调查结果如表: 电脑型号 Ⅰ Ⅱ Ⅲ 回访客户(人数) 250 400 350 满意度0.50.40.6满意度是指,回访客户中,满意人数与总人数的比值.用满意度来估计每种型号电脑客户对该型号电脑满意的概率,且假设客户是否满意相互独立.(1)从型号Ⅰ和型号Ⅱ电脑的所有客户中各随机抽取1人,记其中满意的人数为X ,求X 的分布列和期望;(2)用“11ξ=”,“21ξ=”,“31ξ=”分别表示Ⅰ,Ⅱ,Ⅲ型号电脑让客户满意,“10ξ=”,“20ξ=”,“30ξ=”分别表示Ⅰ,Ⅱ,Ⅲ型号电脑让客户不满意,比较三个方差()1D ξ、()2D ξ、()3D ξ的大小关系.23.国庆70周年阅兵式上的女兵们是一道靓丽的风景线,每一名女兵都是经过层层筛选才最终入选受阅方队,筛选标准非常严格,例如要求女兵身高(单位:cm )在区间[]165,175内.现从全体受阅女兵中随机抽取200人,对她们的身高进行统计,将所得数据分为[)165,167,[)167,169,[)169,171,[)171,173,[]173,175五组,得到如图所示的频率分布直方图,其中第三组的频数为75,最后三组的频率之和为0.7.(1)请根据频率分布直方图估计样本的平均数x 和方差2s (同一组中的数据用该组区间的中点值代表);(2)根据样本数据,可认为受阅女兵的身高X (cm )近似服从正态分布()2,N μσ,其中μ近似为样本平均数x ,2σ近似为样本方差2s .(i )求()167.86174.28P X <<;(ii )若从全体受阅女兵中随机抽取10人,求这10人中至少有1人的身高在174.28cm 以上的概率.参考数据:若()2~,X N μσ,则()0.6826P X μσμσ-<<+=,()220.9544P X μσμσ-<<+=,11510.7≈,100.95440.63≈,90.97720.81≈,100.97720.79≈.24.将名为《高等代数》、《数学分析》、《概率论》和《复变函数》的4本不同的书随机放入甲、乙、丙、丁4个书包中.(1)求4本书恰好放在4个不同书包中的概率;(2)随机变量X 表示放在丙书包中书的本数,求X 的概率分布和数学期望()E X . 25.某运动会将在深圳举行,组委会招募了12名男志愿者和18名女志愿者,将这30名志愿者的身高编成如图所示的茎叶图(单位:cm ),身高在175cm 以上(包括175cm )定义为“高个子”,身高在175cm 以下(不包括175cm )定义为“非高个子”.(1)如果用分层抽样的方法从“高个子”和“非高个子”中抽取5人,再从这5人中选2人,求至少有一人是“高个子”的概率;(2)若从身高180cm 以上(包括180cm )的志愿者中选出男、女各一人,设这2人身高相差cm ξ(0ξ≥),求ξ的分布列和数学期望(均值).26.某单位选派甲、乙、丙三人组队参加知识竞赛,甲、乙、丙三人在同时回答一道问题时,已知甲答对的概率是34,甲、丙两人都答错的概率是112,乙、丙两人都答对的概率是14,规定每队只要有一人答对此题则该队答对此题. (1)求该单位代表队答对此题的概率;(2)此次竞赛规定每队都要回答10道必答题,每道题答对得20分,答错得10-分.若该单位代表队答对每道题的概率相等且回答任一道题的对错对回答其他题没有影响,求该单位代表队必答题得分的均值(精确到1分).【参考答案】***试卷处理标记,请不要删除一、选择题 1.A 解析:A 【分析】直接利用对立事件和独立事件的概率求解. 【详解】因为在一小时内甲、乙、丙三台机床需要维修的概率分别是0.1,0.2,0.4, 所以一小时内恰有一台机床需要维修的概率是:()()()()0.110.210.40.210.110.4p =⨯-⨯-+⨯-⨯- ,()()0.410.210.10.444+⨯-⨯-=.故选:A 【点睛】本题主要考查独立事件和对立事件的概率,属于中档题.2.B解析:B 【解析】∵~(,)X B n p ,∴()2E X =,4()3D X =,∴2np =,且4(1)3np p -=,解得613n p =⎧⎪⎨=⎪⎩, ∴6n =,故选B .3.B解析:B 【分析】先求出一个人在所有行业中都不能胜过孔圣人的概率,再求出三个人在所有行业中都不能胜任孔圣人的概率,用1减去此概率即为所求. 【详解】一个人三百六十行全都不如孔圣人的概率为3600.990.03≈,三个人三百六十行都不如孔圣人的概率为30.030.000027=,所以至少一人在至少一行业中胜过孔圣人的概率为10.0000270.99997399.9973%-==.故选:B . 【点睛】本题考查相互独立事件的概率乘法公式,考查至多至少问题用对立事件解决的方法,属于中档题.4.B解析:B 【分析】根据条件概率的计算公式即可得出答案. 【详解】3311166617()216A P AB C C C +==,11155561116691()1216C C C P B C C C =-=()()()72161|2169113P AB P A B P B ∴==⨯= 故选:B 【点睛】本题主要考查了利用条件概率计算公式计算概率,属于中档题.5.C解析:C 【分析】求出1(01)0.68260.3412P X <=⨯=,即可得出结论.【详解】解:由题意1(01)0.68260.3412P X <=⨯=,∴落入阴影部分点的个数的估计值为10000.341341⨯=.故选:C . 【点睛】本题考查正态分布曲线的特点及曲线所表示的意义,考查正态分布中两个量μ和σ的应用,考查曲线的对称性.6.C解析:C 【分析】 由1()3E X =,利用随机变量X 的分布列列出方程组,求出13a =,12b =,由此能求出()D X ,再由(32)9()D X D X -=,能求出结果.【详解】 1()3E X =∴由随机变量X 的分布列得:1161163a b b ⎧++=⎪⎪⎨⎪-+=⎪⎩,解得1312a b ⎧=⎪⎪⎨⎪=⎪⎩, 2221111115()(1)(0)(1)3633329D X ∴=--⨯+-⨯+-⨯=,5(32)9()959D X D X ∴-==⨯=故选:C . 【点睛】本题考查方差的求法,考查离散型随机变量的分布列、数学期望、方差等基础知识,考查运算求解能力,考查函数与方程思想,是基础题.7.D解析:D 【分析】对三个命题分别判断真假,即可得出结论. 【详解】对于(1),18的二项展开式的通项为1815163621818rrr r rC x x C x ---⎛⎫⎛⎫⋅⋅=⋅ ⎪ ⎪⎝⎭⎝⎭, 当0r =、6、12、18时,为有理项,共有4个有理项,故(1)正确; 对于(2),事件A 、B 满足()0.15P A =,()0.60P B =,()0.09P AB =, 所以()()()0.150.600.09P AB P A P B =⨯==,满足A 、B 为相互独立事件,故(2)正确;对于(3),当总体平均数是2,若有一个数据超过7,则方差就接近于3, 所以,总体均值为2,总体方差为3时,没有数据超过7,故(3)正确. 故选:D. 【点睛】本题考查命题真假的判断,考查分析法与基本运算能力,考查分析问题和解决问题的能力,属于中等题.8.A解析:A 【解析】 【分析】随机变量随机ξ的所有可能的取值为0,1,2.分别求出其对应的概率,列出分布列,求期望即可. 【详解】随机变量ξ的所有可能的取值为0,1,2,P (ξ=0)30423615C C C ==,()214236315C C P C ξ===, ()124236125C C P C ξ===, 所有随机变量ξ的分布列为:所以ξ的期望()0121555E ξ=⨯+⨯+⨯= ,故选A . 【点睛】本题考查了离散型随机变量的期望,属于中档题.9.C解析:C 【解析】 【分析】随机变量X 的可能取值为20,30,40,结合组合知识,利用古典概型概率公式求出各随机变量对应的概率,从而可得分布列,进而利用期望公式可得X 的数学期望. 【详解】X 的可能取值为20,30,40,()222521202010A P X A ====;()311232323562323306010A C C A P X A +⋅⋅+⨯⨯====; ()()()1334012030110105P X P X P X ==-=-==--=,数学期望2030403510105EX =⨯+⨯+⨯=, 即需检测费的均值为35,故选C. 【点睛】本题主要考查组合的应用、古典概型概率公式以及离散型随机变量的分布列与数学期望,属于中档题. 求解数学期望问题,首先正确要理解题意,其次要准确无误的找出随机变量的所以可能值,计算出相应的概率,写出随机变量的分布列,正确运用均值、方差的公式进行计算,也就是要过三关:(1)阅读理解关;(2)概率计算关;(3)公式应用关.10.D解析:D 【解析】随机变量X 满足二项分布,所以1224(),3393D x npq n n ==⨯⨯==n=6,所以224612(2)()()33P X C ===80243,选D.11.B解析:B 【解析】对于命题①,因为2R 表示解释变量对于预报变量变化的贡献率,所以算得20.64R ≈,表明“女大学生的体重差异有64%是由身高引起的”,故该命题①是正确的;对于命题②,由于随机变量的方差和标准差都反映了随机变量取值偏离于均值的整齐程度,因此方差或标准差越小,则随机变量偏离于均值的差异越大,命题②是错误;对于命题③,由于整个正太曲线都在轴上方,所以命题③的说法是不正确的;对于命题④,由于正态曲线的对称轴由μ确定,当μ一定时,曲线的形状由σ决定,并且σ越大,曲线越贴近于轴,因此命题④的说法是正确的;对于命题⑤,由于随机变量()~0,1N ξ,且()1P p ξ>= ,所以依据正太曲线的对称性可得()1P p ξ<-= ,故()1112,P p ξ-<<=- 所以()1102P p ξ-<<=-,即命题⑤是正确的,综上应选答案B 。

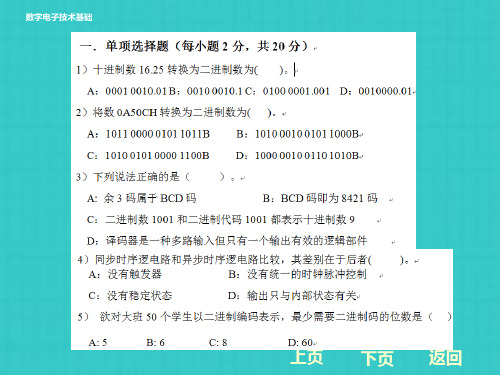

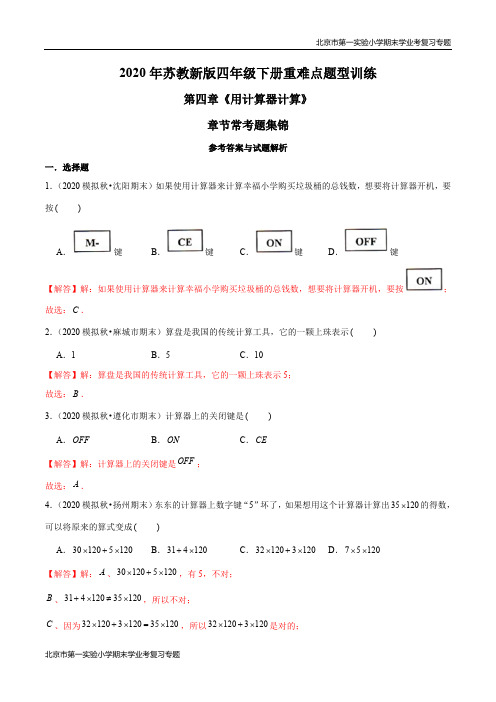

数字逻辑课程三套作业及答案

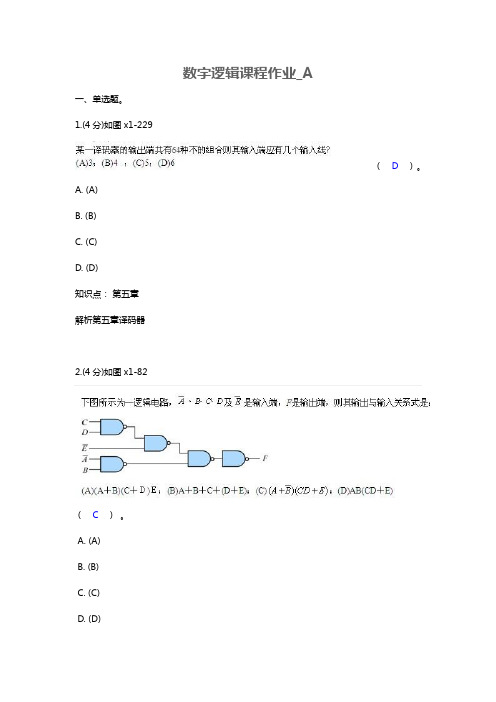

数字逻辑课程作业_A一、单选题。

1.(4分)如图x1-229(D)。

A. (A)B. (B)C. (C)D. (D)知识点:第五章解析第五章译码器2.(4分)如图x1-82(C)。

A. (A)B. (B)C. (C)D. (D)知识点:第二章解析第二章其他复合逻辑运算及描述3.(4分)N个触发器可以构成最大计数长度(进制数)为(D)的计数器。

A. NB. 2NC. N2次方D. 2N次方知识点:第九章解析第九章计数器4.(4分)n个触发器构成的扭环型计数器中,无效状态有(D)个。

A. A.nB. B.2nC. C.2n-1D. D.2n-2n知识点:第九章解析第九章集成计数器5.(4分)如图x1-293(A)。

A. (A)B. (B)C. (C)D. (D)知识点:第十一章解析第十一章数字系统概述6.(4分)如图x1-317(D)。

A. (A)B. (B)C. (C)D. (D)知识点:第二章解析第二章其他复合逻辑运算及描述7.(4分)EPROM是指(C)。

A. A、随机读写存储器B. B、只读存储器C. C、光可擦除电可编程只读存储器D. D、电可擦可编程只读存储器知识点:第十章解析第十章只读存储器8.(4分)如图x1-407(B)。

A. (A)B. (B)C. (C)D. (D)知识点:第十一章解析第十一章数字系统概述9.(4分)为实现将JK触发器转换为D触发器,应使(A)。

A. J=D,K=D非B. B. K=D,J=D非C. C.J=K=DD. D.J=K=D非知识点:第六章解析第六章各种触发器的比较10.(4分)一位8421BCD码计数器至少需要(B)个触发器。

A. 3B. B.4C. C.5D. D.10知识点:第九章解析第九章计数器11.(4分)为把50Hz的正弦波变成周期性矩形波,应当选用(A)。

A. A、施密特触发器B. B、单稳态电路C. C、多谐振荡器D. D、译码器知识点:第六章解析第六章集成触发器12.(4分)下列描述不正确的是(A)。

计数器作业及往届考题

上页 下页 返回

数字电子技术基础

D. 动态RAM存储单元的结构比静态RAM存储单元的结构简单。

上页 下页 返回

数字电子技术基础

上页 下页 返回

数字电子技术基础

上页 下页 返回

数字电子技术基础

Y 1A B C A B C A C B A B C

Y1 AB Y 1A BBAB BAB

上页 下页 返回

数字电子技术基础

上页 下页 返回

数字电子技术基础

上页 下页 返回

数字电子技术基础

[解] (1) 555组成了多谐振荡器,74193为异步置数,置数始终 有效,电路状态一直为1110B;4538组成了单稳态电路。 (2) uo1的周期 T=0.7×(R1+2R2)×C=0.35ms (3) 74193不计数,进位端一直为高。 (4) 4538输出一直为稳态,低电平,无波形输出。

整个电路实现了锯齿波发生器。由于输出波形的频率是CLK的256分频, 改变电阻R1、R2或电容C都可以改变555产生CLK的频率,也就改变了输出 波形的频率。改变I/U转换电路的反馈电阻RF或VREF的值都可以改变输出波 形的幅度。

上页 下页 返回

数字电子技术基础

7.5 用一个4位二进制计数器74161、一个4位D/A转换电路和 一个二输入与非门设计一个能够产生图题波形的波形发生器 电路。

Inhibit

上页

下页

返回

数字电子技术基础 (设直流电源电压为+5V) (2) 从F与CP的关系看,该电路实现何种功能?

作业

[例] 试分析图所示电路,写出逻辑表达式,列出真值表,分析整个电路具有什么逻辑功能?

(2) u5o1.的3周期试T=0分. 析图题所示电路的逻辑功能。

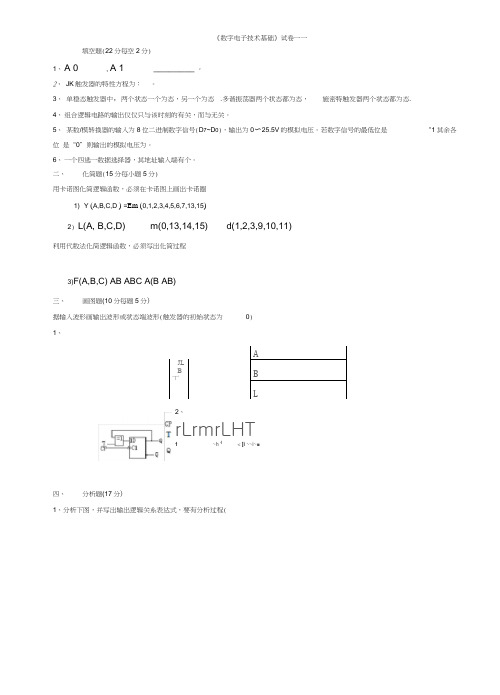

数电试题和答案解析[五套]。

![数电试题和答案解析[五套]。](https://img.taocdn.com/s3/m/0001513203d8ce2f006623bd.png)

《数字电子技术基础》试题一一、 填空题(22分 每空2分)1、=⊕0A , =⊕1A 。

2、JK 触发器的特性方程为: 。

3、单稳态触发器中,两个状态一个为 态,另一个为 态.多谐振荡器两个状态都为 态, 施密特触发器两个状态都为 态.4、组合逻辑电路的输出仅仅只与该时刻的 有关,而与 无关。

5、某数/模转换器的输入为8位二进制数字信号(D 7~D 0),输出为0~25.5V 的模拟电压。

若数字信号的最低位是“1”其余各位是“0”,则输出的模拟电压为 。

6、一个四选一数据选择器,其地址输入端有 个。

二、化简题(15分 每小题5分)用卡诺图化简逻辑函数,必须在卡诺图上画出卡诺圈1)Y (A,B,C,D )=∑m(0,1,2,3,4,5,6,7,13,15) 2)∑∑+=)11,10,9,3,2,1()15,14,13,0(),,,(d m D C B A L利用代数法化简逻辑函数,必须写出化简过程3)__________________________________________________)(),,(B A B A ABC B A C B A F +++=三、画图题(10分 每题5分)据输入波形画输出波形或状态端波形(触发器的初始状态为0). 1、2、四、分析题(17分)1、分析下图,并写出输出逻辑关系表达式,要有分析过程(6分)2、电路如图所示,分析该电路,画出完全的时序图,并说明电路的逻辑功能,要有分析过程(11分)五、设计题(28分)1、用红、黄、绿三个指示灯表示三台设备的工作情况:绿灯亮表示全部正常;红灯亮表示有一台不正常;黄灯亮表示两台不正常;红、黄灯全亮表示三台都不正常。

列出控制电路真值表,要求用74LS138和适当的与非门实现此电路(20分)2、中规模同步四位二进制计数器74LS161的功能表见附表所示;请用反馈预置回零法设计一个六进制加法计数器。

(8分)六、分析画图题(8分)V作用下,输出电压的波形和电压传输特性画出下图所示电路在i74LS138功能表如下:74LS161功能表《数字电子技术基础》试题一答案一、填空题(22分每空2分) 1、A ,A 2、n n n Q K Q J Q +=+13、稳态,暂稳态,暂稳态,稳态4、输入,电路原先状态5、0.1V6、两二、化简题(15分 每小题5分)1)Y (A,B,C,D )=∑m(0,1,2,3,4,5,6,7,13,15)=BD A +2) AC AD B A d m D C B A L ++=+=∑∑)11,10,9,3,2,1()15,14,13,0(),,,(3))(),,(__________________________________________________________________________________=+++=++++=+++=A BC B A B A AB BC B A B A B A ABC B A C B A F三、画图题(10分 每题5分) 1、 2、四、分析题(17分) 1、(6分)B A L ⊕=2、(11分)五进制计数器五、设计题(28分) 1、(20分)1)根据题意,列出真值表由题意可知,令输入为A 、B 、C 表示三台设备的工作情况,“1”表示正常,“0”表示不正常,令输出为R ,Y ,G 表示红、黄、绿三个批示灯的 状态,“1”表示亮,“0”表示灭。

(完整版)数电试题及标准答案(五套)。

《数字电子技术基础》试卷一一填空题(22分每空2分)1、A 0 , A 1 ________ 。

2、JK触发器的特性方程为:。

3、单稳态触发器中,两个状态一个为态,另一个为态.多谐振荡器两个状态都为态,施密特触发器两个状态都为态.4、组合逻辑电路的输出仅仅只与该时刻的有关,而与无关。

5、某数/模转换器的输入为8位二进制数字信号(D7~D0),输出为0〜25.5V的模拟电压。

若数字信号的最低位是“1其余各位是“0”则输出的模拟电压为。

6、一个四选一数据选择器,其地址输入端有个。

二、化简题(15分每小题5分)用卡诺图化简逻辑函数,必须在卡诺图上画岀卡诺圈1) Y (A,B,C,D ) =Em (0,1,2,3,4,5,6,7,13,15)2) L(A, B,C,D) m(0,13,14,15) d(1,2,3,9,10,11)利用代数法化简逻辑函数,必须写岀化简过程3)F(A,B,C) AB ABC A(B AB)三、画图题(10分每题5分)据输入波形画输岀波形或状态端波形(触发器的初始状态为0)1、AJLBB丁L2、rLrmrLHT1 ~h 1< [i ~~i~■四、分析题(17分)1、分析下图,并写岀输岀逻辑关系表达式,要有分析过程(2、电路如图所示,分析该电路,画出完全的时序图,并说明电五、设计题(28分)1、用红、黄、绿三个指示灯表示三台设备的工作情况:绿灯亮表示全部正常;红灯亮表示有一台不正常;黄灯亮表示两台不正常;红、黄灯全亮表示三台都不正常。

列岀控制电路真值表,要求用74LS138和适当的与非门实现此电路(20分)2、中规模同步四位二进制计数器74LS161的功能表见附表所示;请用反馈预置回零法设计一个六进制加法计数器。

(8分)六、分析画图题(8分)画岀下图所示电路在V作用下,输岀电压的波形和电压传输特性74LS138功能表如下:2 / 26(勿74LS161功能表 清零 预置 使能 时钟 预置数据输入 输出 RD LDEP ETCPD C B AQ D Q C Q B Q A L XX X X XXXXL L L L H L X XT D C B AD C B A H H LXX XXXX 保 持 HH X LX XXXX 保 持 HHH HTXXXX计 数《数字电子技术基础》试卷一答案一、 填空题(22分每空2分)n 1nn1、A ,A2、Q JQ KQ3、稳态,暂稳态,暂稳态,稳态4、输入,电路原先状态5、0.1V6、两二、 化简题(15分 每小题5分)1) Y (A,B,C,D ) =Em (0,1,2,3,4,5,6,7,13,15) = A BDG1 G 2A G 2BC BAY 0Y 1Y 2Y 3Y 4Y 5Y 6Y 7 X H X X X XHHHHHHHHXX HX X XHHHHHHHHL XX XXXHHHHHHHHH L LL L L LHHHHHHHLL H HLHHHHHH H L LL H L HHLHHHHHLHHHHHLHHHHH L LH L L HHHHLHHH H L LH LH HHHHHLHH H L LH HLHHHHHHLHH L LH HHHHHHHHHLH L LH L L输 入输出2)L(A,B,C,D) m(0,13,14,15) d(1,2,3,9,10,11) AB AD AC3)F(A,B,C) AB ABC A(B AB) A B BC AB AB A B BC A 0 三、画图题(10分每题5分) 1、n2、 rA 1钉厂LTLrLTLRr 1 U1―r丁 H : ■ : um四、分析题(17分)1、(6 分) L A B2、(11 分) 五进制计数器12 34 5 67 8 9.JWWWWL五、设计题(28分) 1、(20 分) 1 )根据题意,列岀真值表 由题意可知,令输入为 A 、B 、C 表示三台设备的工作情况,A B C R Y G 0 0 01 1 0 00 10 1 0 0 1 0 0 1 0 0 1 1 1 0 0 1 0 0 0 1 0 1 0 1 1 0 0 11 0 1 0 0 11 10 0 1“1”表示正常,“0”表示不正常,令输岀为 R ,Y ,G 表示红、黄、绿二个批示灯的状态,“1”表示亮,“0”表示灭。

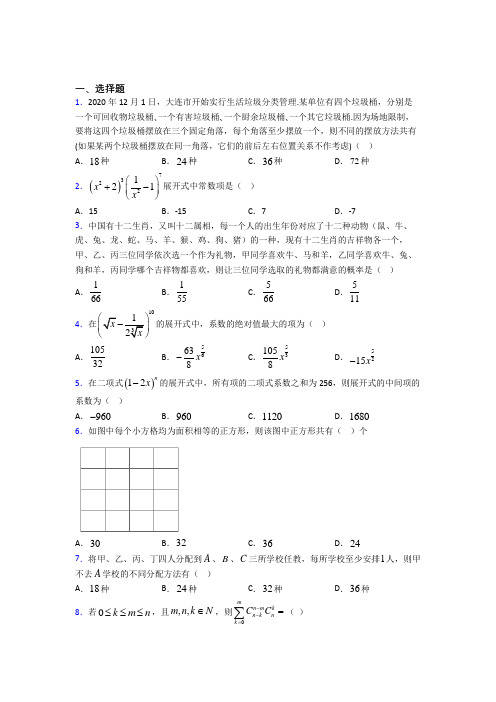

(必考题)高中数学选修三第一单元《计数原理》测试(包含答案解析)(1)

一、选择题1.2020年12月1日,大连市开始实行生活垃圾分类管理.某单位有四个垃圾桶,分别是一个可回收物垃圾桶、一个有害垃圾桶、一个厨余垃圾桶、一个其它垃圾桶.因为场地限制,要将这四个垃圾桶摆放在三个固定角落,每个角落至少摆放一个,则不同的摆放方法共有(如果某两个垃圾桶摆放在同一角落,它们的前后左右位置关系不作考虑)( ) A .18种B .24种C .36种D .72种2.()7322121x x ⎛⎫+- ⎪⎝⎭展开式中常数项是( ) A .15B .-15C .7D .-73.中国有十二生肖,又叫十二属相,每一个人的出生年份对应了十二种动物(鼠、牛、虎、兔、龙、蛇、马、羊、猴、鸡、狗、猪)的一种,现有十二生肖的吉祥物各一个,甲、乙、丙三位同学依次选一个作为礼物,甲同学喜欢牛、马和羊,乙同学喜欢牛、兔、狗和羊,丙同学哪个吉祥物都喜欢,则让三位同学选取的礼物都满意的概率是( ) A .166B .155C .566D .5114.在1032x x ⎛- ⎪⎝⎭的展开式中,系数的绝对值最大的项为( ) A .10532B .56638x -C .531058xD .5215x -5.在二项式()12nx -的展开式中,所有项的二项式系数之和为256,则展开式的中间项的系数为( ) A .960-B .960C .1120D .16806.如图中每个小方格均为面积相等的正方形,则该图中正方形共有( )个A .30B .32C .36D .247.将甲、乙、丙、丁四人分配到A 、B 、C 三所学校任教,每所学校至少安排1人,则甲不去A 学校的不同分配方法有( ) A .18种B .24种C .32种D .36种8.若0k m n ≤≤≤,且,,m n k N ∈,则mn m k n k n k CC --==∑( )A .2m n +B .2m n m CC .2n mn C D .2m mn C9.如图所示的阴影部分由方格纸上3个小方格组成,我们称这样的图案为L 形(每次旋转90°仍为L 形的图案),那么在56⨯个小方格组成的方格纸上可以画出不同位置的L 形需案的个数是()A .36B .64C .80D .9610.已知*n N ∈,设215nx x ⎛⎫- ⎪⎝⎭的展开式的各项系数之和为M ,二项式系数之和为N ,若992M N -=,则展开式中x 的系数为( )A .-250B .250C .-500D .50011.若从0,1,2,3,4,5这六个数字中选3个数字,组成没有重复数字的三位偶数,则这样的三位数一共有( ) A .20个B .48个C .52个D .120个12.如图,用6种不同的颜色把图中A,B,C,D 四块区域涂色分开,若相邻区域不能涂同一种颜色,则不同涂法的种数为( )A .400B .460C .480D .496二、填空题13.二项式261(2)x x-的展开式中的常数项是_______.(用数字作答)14.从3名男医生和5名女医生中,选派3人组成医疗小分队,要求男、女医生都有,则不同的选取方法种数为__________(用数字作答).15.设122012(1)(1)(1)n n n x x x a a x a x a x ++++++=++++,其中n *∈N ,且2n ≥,若0121022n a a a a ++++=,则n =_____16.设集合{}{}12310(,,,...,)1,0,1,1,2,3,...,10i A x x x x x i =∈-=,则集合A 中满足条件“123101+9x x x x ≤+++≤…”的元素个数为_____.17.已知()()()()()23n2012111...+1...*n n x x x x a a x a x a x n N +++++++=++++∈,且012126n a a a a +++⋯+=,那么nx x 的展开式中的常数项为______.18.若348,n n A C =则n 的值为_______.19.设n 为正整数,32nx x ⎛⎫- ⎪⎝⎭展开式中仅有第5项的二项式系数最大,则展开式中的常数项为__________. 20.若()202022020012202032x a a x a x a x +=++++,则1352019a a a a ++++被12整除的余数为______.三、解答题21.已知二项式*1()(,2)2nx n N n x-∈≥,若该二项式的展开式中前三项的系数的绝对值成等差数列. (1)求正整数n 的值;(2)求展开式中二项式系数最大项,并指出是第几项?22.已知nx x ⎛+ ⎪⎝⎭的展开式中只有第五项的二项式系数最大.(1)求该展开式中有理项的项数; (2)求该展开式中系数最大的项.23.为提高学生学习的数学的兴趣,南京港师范大学附属中学拟开设《数学史》、《微积分先修课程》、《数学探究》、《数学建模》四门校本选修课程,甲、乙、丙三位同学打算在上述四门课程中随机选择一门进行学习,已知三人选择课程时互不影响,且每人选择每一门课程都是等可能的.(1)求三位同学选择的课程互不相同的概率:(2)求甲、乙两位同学不能选择同一门课程,求三人共有多少种不同的选课种数; (3)若至少有两位同学选择《数学史》,求三人共有多少种不同的选课种数.24.已知3()nx x-的二项展开式中,所有二项式系数之和为1024. (1)求n 的值,并求展开式所有项的系数之和; (2)写出展开式中所有x 的整数次幂的项. 25.若7270127(2)x a a a x a x a x -=++++,且4560a =-.(Ⅰ)求实数a 的值; (Ⅱ)求372126222a a a a ++++的值. 26.在42nx x ⎛+ ⎪⎝⎭的二项展开式中,(1)当6n =时,求该二项展开式中的常数项;(2)若前三项系数成等差数列,求该二项展开式中的所有有理项.【参考答案】***试卷处理标记,请不要删除一、选择题 1.C 解析:C 【分析】分析题意,得到有一个固定点放着两个垃圾桶,先选出两个垃圾桶,之后相当于三个元素分配到三个地方,最后利用分步乘法计数原理,求得结果. 【详解】根据题意,有四个垃圾桶放到三个固定角落,其中有一个角落放两个垃圾桶, 先选出两个垃圾桶,有246C =种选法,之后与另两个垃圾桶分别放在三个不同的地方有33A 种放法;所以不同的摆放方法共有23436636C A ⋅=⨯=种, 故选:C. 【点睛】思路点睛:该题考查的是有关排列组合综合题,解题方法如下:(1)首先根据题意,分析出有两个垃圾桶分到同一个地方,有246C =种选法; (2)之后就相当于三个元素的一个全排; (3)利用分步乘法计数原理求得结果.2.B解析:B 【分析】先求得7211x ⎛⎫- ⎪⎝⎭展开式的通项公式,分别令r =4,5,6,7,求得对应的四项,又()3264226128x x x x +=+++,则()7322121x x ⎛⎫+- ⎪⎝⎭展开式中所有x 的零次幂的系数和即为常数项,计算化简,即可得结果. 【详解】7211x ⎛⎫- ⎪⎝⎭的通项公式为721417721()(1)(1)r r r r r r r T C C x x --+=⋅⋅-=⋅-⋅,令4r =,得446657(1)35T C x x --=⋅-⋅=, 令=5r ,得554467(1)21T C x x --=⋅-⋅=-, 令6r =,得662277(1)7T C x x --=⋅-⋅=, 令7r =,得77087(1)1T C x =⋅-⋅=-,又()3264226128x x x x +=+++,所以()7322121x x ⎛⎫+- ⎪⎝⎭展开式中常数项为351(21)6712(1)815⨯+-⨯+⨯+-⨯=-, 故选:B 【点睛】本题考查利用赋值法解决展开式中常数项的问题,考查分析理解,计算求值的能力,属中档题.3.C解析:C 【分析】对甲分甲选牛或羊作礼物、甲选马作礼物,利用分步计数原理和分类计数原理计算出事件“三位同学都选取了满意的礼物”所包含的基本事件数,然后利用古典概型的概率公式可计算出所求事件的概率. 【详解】若甲选牛或羊作礼物,则乙有3种选择,丙同学有10种选择,此时共有231060⨯⨯=种;若甲选马作礼物,则乙有4种选择,丙同学有10种选择,此时共有141040⨯⨯=种. 因此,让三位同学选取的礼物都满意的概率为31260401005132066A +==. 故选:C. 【点睛】本题考查古典概型概率的计算,同时也涉及了分类计数和分步计数原理的应用,考查分析问题和解决问题的能力,属于中等题.4.D解析:D 【分析】根据最大的系数绝对值大于等于其前一个系数绝对值;同时大于等于其后一个系数绝对值;列出不等式求出系数绝对值最大的项; 【详解】10∴二项式展开式为:(10)113211012kk k k T C x x --+⎛⎫⎛⎫=- ⎪ ⎪⎝⎭⎝⎭设系数绝对值最大的项是第1k +项,可得11101011101011221122kk k k k k k k C C C C --++⎧⎛⎫⎛⎫≥⎪ ⎪ ⎪⎪⎝⎭⎝⎭⎨⎛⎫⎛⎫⎪≥ ⎪ ⎪⎪⎝⎭⎝⎭⎩可得11112101112kkkk-⎧≥⎪⎪⎨-⎪≥⋅⎪+⎩,解得81133k≤≤*k N∈∴3k=在10的展开式中,系数的绝对值最大的项为:3711310523241215x xT C x-⎛⎫⎛⎫=-=⎪⎭-⎪⎝⎭⎝故选:D.【点睛】本题考查二项展开式中绝对值系数最大项的求解,涉及展开式通项的应用,考查分析问题和解决问题的能力,属于中等题.5.C解析:C【分析】先根据条件求出8n=,再由二项式定理及展开式通项公式,即可得答案.【详解】由已知可得:2256n=,所以8n=,则展开式的中间项为44458(2)1120T C x x=-=,即展开式的中间项的系数为1120.故选:C.【点睛】本题考查由二项式定理及展开式通项公式,考查函数与方程思想、转化与化归思想,考查逻辑推理能力、运算求解能力.6.A解析:A【分析】设方格纸上的小方格的边长为1,按正方形的边长进行分类讨论,求出每种情况下正方形的个数,由加法原理即可得答案.【详解】设方格纸上的小方格的边长为1,当正方形的边长为1时,有4×4=16个正方形,当正方形的边长为2时,有3×3=9个正方形,当正方形的边长为3时,有2×2=4个正方形,当正方形的边长为4时,有1×1=1个正方形,则有16+9+1+4=30个正方形; 故选:A . 【点睛】本题涉及分类计数原理的应用,属于基础题,进行分类讨论是解题的关键.7.B解析:B 【分析】根据题意,分两种情况讨论:①其他三人中有一个人与甲在同一个学校,②没有人与甲在同一个学校,由加法原理计算可得答案. 【详解】解:根据题意,分两种情况讨论,①其他三人中有一个人与甲在同一个学校,有11232212C A A =种情况, ②没有人与甲在同一个学校,则有12223212C C A =种情况;则若甲要求不到A 学校,则不同的分配方案有121224+=种; 故选:B . 【点睛】本题考查排列、组合的应用,涉及分类加法原理的应用,属于中等题.8.D解析:D 【分析】先利用特殊值排除A,B,C ,再根据组合数公式以及二项式定理论证D 成立. 【详解】 令0m =得,CC C C 1mn m k n n k n n n k --===∑,在选择项中,令0m =排除A ,C ;在选择项中,令1m =,101110C C C C C C 2mn m k n n n k n n n n n k n -----==+=∑排除B ,0()!!()!()!!()!mmn m k n knk k n k n CC n m m k k n k --==-=⋅---∑∑000!!2()!!!()!mm mm k m k m mn m n m n k k k n m C C C C C n m m k m k ====⋅=⋅==--∑∑∑,故选D【点睛】本题考查组合数公式以及二项式定理应用,考查基本分析化简能力,属中档题.9.C解析:C 【分析】把问题分割成每一个“田”字里,求解. 【详解】每一个“田”字里有4个“L ”形,如图因为56⨯的方格纸内共有4520⨯=个“田”字,所以共有20480⨯=个“L ”形.. 【点睛】本题考查排列组合问题,关键在于把“要做什么”转化成“能做什么”,属于中档题.10.A解析:A 【分析】分别计算各项系数之和为M ,二项式系数之和为N ,代入等式得到n ,再计算x 的系数. 【详解】215nx x ⎛⎫- ⎪⎝⎭的展开式取1x =得到4n M = 二项式系数之和为2n N = 429925n n M N n -=-=⇒=5251031551(5)()5(1)r r r r r r r r T C x C x x---+=-=- 取3r = 值为-250故答案选A 【点睛】本题考查了二项式定理,计算出n 的值是解题的关键.11.C解析:C 【分析】由于0不能在首位数字,则分2种情况讨论:①若0在个位,此时0一定不在首位,由排列公式即可得此时三位偶数的数目;②若0不在个位,要排除0在首位的可能,由分步计数原理可得此情况下三位偶数的数目,综合2种情况,由分类计数原理计算可得答案. 【详解】根据题意,分2种情况讨论: ①若0在个位,此时只须在1,2,3,4,5中任取2个数字,作为十位和百位数字即可,有A 52=20个没有重复数字的三位偶数; ②若0不在个位,此时必须在2或4中任取1个,作为个位数字,有2种取法,0不能作为百位数字,则百位数字有4种取法,十位数字也有4种取法, 此时共有2×4×4=32个没有重复数字的三位偶数,综合可得,共有20+32=52个没有重复数字的三位偶数. 故选C . 【点睛】本题考查排列组合的应用,涉及分类、分步计数原理的应用,解题需要注意偶数的末位数字以及0不能在首位等性质.12.C解析:C 【解析】分析:本题是一个分类计数问题,只用三种颜色涂色时,有31116321C C C C 种方法,用四种颜色涂色时,有41126322C C C A 种方法,根据分类计数原理得到结果.详解:只用三种颜色涂色时,有31116321120C C C C =种方法, 用四种颜色涂色时,有41126432360C C C A =种方法,根据分类计数原理得不同涂法的种数为120+360=480. 故答案为C.点睛:(1)本题主要考查计数原理,考查排列组合的综合应用,意在考查学生对这些知识的掌握水平和分析推理能力.(2)排列组合常用的方法有一般问题直接法、相邻问题捆绑法、不相邻问题插空法、特殊对象优先法、等概率问题缩倍法、至少问题间接法、复杂问题分类法、小数问题列举法.二、填空题13.60【分析】根据二项式展开式的通项公式求解【详解】有题意可得二项式展开式的通项为:令可得此时【点睛】本题考查二项式定理的应用考查通项公式考查计算能力属于基础题解析:60 【分析】根据二项式展开式的通项公式求解. 【详解】有题意可得,二项式展开式的通项为:()62612316612(1)2rrr r r r rr T C xC xx ---+⎛⎫=-=- ⎪⎝⎭令1230r -=可得4r = ,此时2456260T C ==.【点睛】本题考查二项式定理的应用,考查通项公式,考查计算能力,属于基础题.14.【分析】根据题意分为两类:2男1女和1男2女结合分类计数原理和组合数的计算公式即可求解【详解】由题意从3名男医生和5名女医生中选派3人组成医疗小分队要求男、女医生都有可分为两类:第一类若2男1女共有解析:45【分析】根据题意分为两类:2男1女和1男2女,结合分类计数原理和组合数的计算公式,即可求解. 【详解】由题意,从3名男医生和5名女医生中,选派3人组成医疗小分队,要求男、女医生都有, 可分为两类:第一类,若2男1女,共有213515C C =种不同的选取方法; 第二类,若1男2女,共有123530C C =种不同的选取方法,由分类计数原理,可得不同的选取方法种数为153045+=种. 故答案为:45. 【点睛】本题主要考查了分类计数原理的应用,以及组合数的计算,其中解答中根据题设条件,合理分类,结合分类计数原理求解是解答的关键,着重考查分析问题和解答问题的能力.15.9【分析】记函数利用等比数列求和公式即可求解【详解】由题:记函数即故答案为:9【点睛】此题考查多项式系数之和问题常用赋值法整体代入求解体现出转化与化归思想解析:9 【分析】记函数122012()(1)(1)(1)n n n f x x x x a a x a x a x =++++++=++++,012222(1)2n n f a a a a =+++=++++,利用等比数列求和公式即可求解. 【详解】由题:记函数212012()(1)(1)(1)n n n f x a a x a x a x x x x =++++=++++++,021222(12)(21)212n nn f a a a a -=++++++=-=+, 即1221022n +-=,121024,9n n +==故答案为:9 【点睛】此题考查多项式系数之和问题,常用赋值法整体代入求解,体现出转化与化归思想.16.58024【分析】依题意得的取值是1到10的整数满足的个数等于总数减去和的个数【详解】集合中共有个元素其中的只有1个元素的有个元素故满足条件的元素个数为59049-1-1024=58024【点睛】本解析:58024 【分析】依题意得12310+x x x x +++⋯的取值是1到10的整数,满足123101+9x x x x ≤+++≤…的个数等于总数减去12310+0x x x x +++⋯=和12310+10x x x x +++⋯=的个数.【详解】集合A 中共有个元素10359049= ,其中12310+0x x x x +++⋯=的只有1个元素,12310+10x x x x +++⋯=的有1021024= 个元素,故满足条件“123101+9x x x x ≤+++≤…”的元素个数为59049-1-1024=58024. 【点睛】本题考查计数原理,方法:1、直接考虑,适用包含情况较少时;2、间接考虑,当直接考虑情况较多时,可以用此法.17.-20【分析】由题意令x =1可得n =6再利用二项展开式的通项公式求得展开式中的常数项【详解】∵已知且∴令可得∴那么的展开式的通项公式为令求得可得展开式中的常数项为故答案为﹣20【点睛】本题主要考查二解析:-20 【分析】由题意令x =1,可得n =6,再利用二项展开式的通项公式,求得展开式中的常数项. 【详解】∵已知()()()()()232*0121111nnn x x x x a a x a x a x n N++++++⋯++=+++⋯+∈,且012126n a a a a +++⋯+=,∴令1x =,可得()210122122222212612n n n n a a a a +-+++⋯+=++⋯+==-=-,∴6n =,那么6n =的展开式的通项公式为()3161r rr r T C x -+=⋅-⋅, 令30r -=,求得3r =,可得展开式中的常数项为3620C -=-,故答案为﹣20. 【点睛】本题主要考查二项式定理的应用,赋值法,求展开式的系数和,项的系数,准确计算是关键,属于基础题.18.【分析】由排列数和组合数展开可解得n=6【详解】由排列数和组合数可知化简得所以n=6经检验符合所以填6【点睛】本题考查排列数组合数方程一般用公式展开或用排列数组合公式化简求得n 注意n 取正整数且有范围 解析:6【分析】由排列数和组合数展开可解得n=6. 【详解】由排列数和组合数可知(1)(2)(3)(1)(2)8()4321n n n n n n n -----=⨯⨯⨯,化简得313n -=,所以n=6,经检验符合,所以填6. 【点睛】本题考查排列数组合数方程,一般用公式展开或用排列数组合公式化简,求得n,注意n 取正整数且有范围限制.19.112【解析】由展开式中仅有第5项的二项式系数最大得则令则展开式中的常数项为解析:112 【解析】由展开式中仅有第5项的二项式系数最大得8n =则()884188322rr rrrr r T C xC x x --+⎛⎫=-=- ⎪⎝⎭,令840r -=,2r =则展开式中的常数项为()2282112C -=20.0【分析】根据题意给自变量赋值取和两个式子相减得到的值用二项展开式可以看出被12整除的结果得到余数【详解】在已知等式中取得取得两式相减得即因为能被12整除所以则被12整除余数是0故答案为:0【点睛】解析:0 【分析】根据题意,给自变量x 赋值,取1x =和1x =-,两个式子相减,得到1352019a a a a +++的值,用二项展开式可以看出被12整除的结果,得到余数.【详解】在已知等式中,取1x =得202001220205a a a a ++++=,取1x =-得01220201a a a a -+-+=, 两式相减得202013520192()51a a a a +++=-,即()202013520191512a a a a +++=⨯-,因为()()()1010202010101111512512412222⨯-=⨯-=⨯+- ()01010110091010101010101010101124242422C C C C =⨯++++- ()0101011009110101010101012424242C C C =⨯+++能被12整除,所以则1352019a a a a ++++被12整除,余数是0.故答案为:0. 【点睛】本题考查二项式定理的应用和带余除法,本题解题的关键是利用赋值的方法、利用二项式定理得到式子的结果,属于中等题.三、解答题21.(1)8;(2)2358x -,展开式中二项式系数最大项为第五项. 【分析】(1)根据二项展开式的通项,分别求得123,,T T T ,结合等差中项公式,列出方程,即可求解;(2)根据二项式系数的性质,即可求解. 【详解】(1)由二项式*1)(,2)2nn N n x∈≥,可得212012123111,,222nn n nn n T CT C T C x x x --⎛⎫⎛⎫⎛⎫=-=-=- ⎪ ⎪ ⎪⎝⎭⎝⎭⎝⎭, 因为展开式中前三项的系数的绝对值成等差数列,可得10211224n n n C C C ⨯⨯=+, 整理得1(1)142n n n -=+,即2980n n -+=,解得1n =或8n =.因为*,2n N n ∈≥,所以8n =.(2)当8n =时,展开式中二项式系数最大项为第五项44425813528T C x x -⎛⎫=-= ⎪⎝⎭.【点睛】对于二项式中的项的求解方法:(1)求二项式的特定项问题,实质是在考查通项r n rr r n T C ab -=的特点,一把需要建立方程求得r 的值,在将r 的值代回通项,主要r 的取值范围(0,1,2,,)k n =;(2)若n 为偶数时,中间一项(第12n+项)的二项式系数最大; (3)若n 为奇数时,中间一项(第12n +项和第112n ++项)的二项式系数最大. 22.(1)5;(2)121792x和11792x - 【分析】(1)先求出8n =,再写出二项式展开式的通项382182k kkk T C x-+=⨯⨯,令382kZ -∈即可求解;(2)设第1k +项系数最大,则118811882222k k k k k k k k C C C C --++⎧⨯≥⨯⎨⨯≥⨯⎩,即可解得k 的值,进而可得展开式中系数最大的项. 【详解】(1)由题意可得:152n+=,得8n =,8x ⎛+ ⎝的展开式通项为138********k k k k k k k k T C x x C x ---+=⨯⨯=⨯⨯,()08k ≤≤, 要求展开式中有理项,只需令382kZ -∈, 所以0,2,4,6,8k = 所以有理项有5项,(2)设第1k +项系数最大,则118811882222k k k k kk k k C C C C --++⎧⨯≥⨯⎨⨯≥⨯⎩ , 即()()()()()()118!8!22!8!1!81!8!8!22!8!1!81!k k k k k k k k k k k k -+⎧⨯≥⨯⎪---+⎪⎨⎪⨯≥⨯⎪-+--⎩,即2191281k k k k ⎧≥⎪⎪-⎨⎪≥⎪-+⎩,解得:56k ≤≤,因为k Z ∈, 所以5k =或6k =所以1155226821792T C x x =⨯⨯=,166127821792T C x x -=⨯⨯=所以展开式中系数最大的项为121792x 和11792x -. 【点睛】解二项式的题关键是求二项式展开式的通项,求有理项需要让x 的指数位置是整数,求展开式中系数最大的项需要满足第1k +项的系数大于等于第k 项的系数,第1k +项的系数大于等于第2k +项的系数,属于中档题 23.(1)38;(2)48;(3)10.【分析】(1)先计算出三位同学选择课程的选法种数以及三位同学选择的课程互不相同的选法种数,利用古典概型的概率公式可求得结果;(2)考虑甲、乙两位同学不选同一门课程的选法种数,并求出丙选课程的选法种数,利用分步乘法计数原理可求得结果;(3)分两种情况讨论:①有两位同学选择《数学史》;②三位同学都选择《数学史》.分别计算出两种情况下不同的选课种数,利用分类加法计数原理可得结果. 【详解】(1)三位同学选择课程共有3464=种情况;三位同学选择的课程互不相同共有3424A =种情况,所求概率为243648=;(2)甲、乙两位同学不选择同一门课程共有2412A =种情况,丙有4种不同的选择,所以甲、乙两位同学不能选择同一门课程共有12448⨯=种情况;(3)分两种情况讨论:①有两位同学选择《数学史》,共有21339C C ⨯=种不同的情况; ②有三位同学选择《数学史》共有1种情况. 综上所述,总共有9110+=种不同的选课种数. 【点睛】本题主要考查了等可能事件的概率,分步计数原理分类计数原理,排列组合的基本应用,属于中等题.24.(1)10, 1;(2)3360,51024x -. 【分析】(1)由题意结合二项式系数的性质可得21024n =,即可求得n ;令1x =,即可得展开式所有项的系数之和;(2)由题意结合二项式定理可得10展开式的通项公式,分别令4r =、10r =,即可得解.【详解】(1)因为n的二项展开式中,所有二项式系数之和为1024,所以21024n =,解得10n =;令1x =,则展开式所有项的系数之和为101=;(2)由题意可得10展开式的通项公式为:()()1020510326110101022rr r rrr r rr r r T C C xC x ----+⎛=⋅⋅=⋅-⋅=⋅-⋅ ⎝, 当4r =时,()()20544061010223360r r r C xC x -⋅-⋅=⋅-⋅=,当10r =时,()()20510105561010221024r rr C xC x x ---⋅-⋅=⋅-⋅=,所以展开式中x 的整数次幂的项为3360,51024x -. 【点睛】本题考查了二项式系数的性质及二项式定理的应用,考查了运算求解能力,熟练掌握二项式定理、合理赋值是解题关键,属于中档题. 25.(Ⅰ)1a =;(Ⅱ)2 【分析】(Ⅰ)解法1:将()72x a -展开,找出4x 项的系数表达式,结合条件列方程4280a =-求出a 的值;解法2:利用二项式定理写出()72x a -的通项,令x 的指数为4,列方程求出参数的值,再将参数代入通项得出4x 的系数的表达式,结合条件4280a =-列方程求出实数a 的值; (Ⅱ)解法1:令0x =代入题干等式求出0a 的值,再令12x =可得出712027222a a a a ++++的值,减去0a 可得出71227222a a a +++,再乘以2可得出答案; 解法2:利用二项式定理求出1a 、2a 、3a 、4a 、5a 、6a 、7a 的值,代入代数式可得出答案. 【详解】(Ⅰ)解法1:因为343472()a C a =⨯⨯-33516560a =-⨯=-,所以1a =, 解法2:()()()()77717722kkkk k k k k T C x a C a x ---+=-=⋅-⋅,()334472560a C a ∴=⋅⋅-=,所以1a =.(Ⅱ)解法1:当0x =时,01a =-,当12x =时,3712023702222a a a aa +++++=, 371202372()02222a a a a a +++++=,3721262222a a aa ++++=; 解法2:由二项展开式分别算出123456714,84,280,560,672,448,128a a a a a a a ==-==-==-=,代入得:3721262222a a a a ++++=. 【点睛】本题考查二项式定理的应用,考查二项式指定项的系数问题,考查项的系数和问题,一般利用赋值法来求解,考查计算能力,属于中等题. 26.(1)1516(2)41T x =,5358T x =,921256T x =. 【分析】(1)写出二项展开式的通项第1r +项234112rn rrr n T C x-+⎛⎫= ⎪⎝⎭,令x 的指数为0,即可求得结果;(2)由二项展开式的通项写出前三项的系数,可求得8n =,在根据通项求有理项即可。

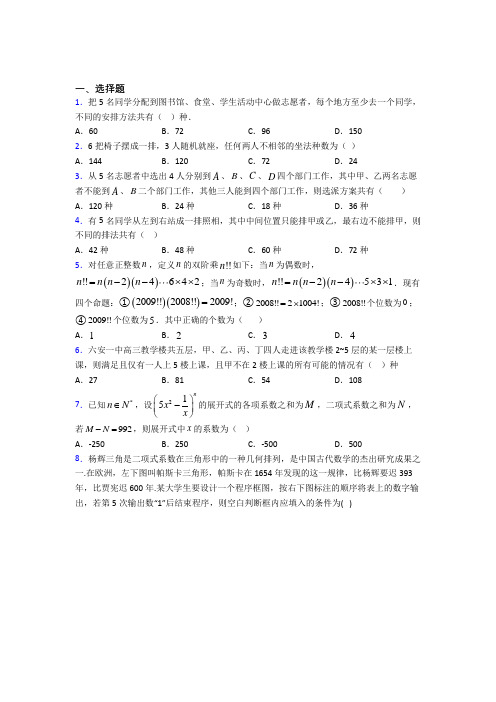

(人教版)福州市选修三第一单元《计数原理》检测题(包含答案解析)

一、选择题1.把5名同学分配到图书馆、食堂、学生活动中心做志愿者,每个地方至少去一个同学,不同的安排方法共有( )种. A .60 B .72 C .96 D .150 2.6把椅子摆成一排,3人随机就座,任何两人不相邻的坐法种数为( )A .144B .120C .72D .243.从5名志愿者中选出4人分别到A 、B 、C 、D 四个部门工作,其中甲、乙两名志愿者不能到A 、B 二个部门工作,其他三人能到四个部门工作,则选派方案共有( ) A .120种B .24种C .18种D .36种4.有5名同学从左到右站成一排照相,其中中间位置只能排甲或乙,最右边不能排甲,则不同的排法共有( ) A .42种B .48种C .60种D .72种5.对任意正整数n ,定义n 的双阶乘!!n 如下:当n 为偶数时,()()!!24642n n n n =--⨯⨯;当n 为奇数时,()()!!24531n n n n =--⨯⨯.现有四个命题:①()()2009!!2008!!2009!=;②2008!!21004!=⨯;③2008!!个位数为0;④2009!!个位数为5.其中正确的个数为( ) A .1B .2C .3D .46.六安一中高三教学楼共五层,甲、乙、丙、丁四人走进该教学楼2~5层的某一层楼上课,则满足且仅有一人上5楼上课,且甲不在2楼上课的所有可能的情况有( )种 A .27B .81C .54D .1087.已知*n N ∈,设215nx x ⎛⎫- ⎪⎝⎭的展开式的各项系数之和为M ,二项式系数之和为N ,若992M N -=,则展开式中x 的系数为( )A .-250B .250C .-500D .5008.杨辉三角是二项式系数在三角形中的一种几何排列,是中国古代数学的杰出研究成果之一.在欧洲,左下图叫帕斯卡三角形,帕斯卡在1654年发现的这一规律,比杨辉要迟393年,比贾宪迟600年.某大学生要设计一个程序框图,按右下图标注的顺序将表上的数字输出,若第5次输出数“1”后结束程序,则空白判断框内应填入的条件为( )A .3n >B .4n <C .3n <D .4n >9.在()nx x的展开式中,各项系数与二项式系数和之比为128,则4x 的系数为( ) A .21B .63C .189D .72910.已知自然数k ,则(18)(19)(20)(99)k k k k ----…等于( ) A .1899kk C --B .8299k C -C .1899kk A -- D .8299k A -11.在二项式3nx x ⎫⎪⎭的展开式中,各项系数之和为A ,二项式系数之和为B ,若72A B +=,则n =( )A .3B .4C .5D .612.1231261823n nn n n n C C C C -+++⋯+⨯=( )A .2123n + B .()2413n- C .123n -⨯ D .()2313n- 二、填空题13.已知()2311nx x x ⎛⎫++ ⎪⎝⎭的展开式中没有2x 项,*N n ∈且58n ≤≤,则n =______. 14.对于无理数x ,用x 表示与x 最接近的整数,如3π=32=.设n *∈N ,对于区间11,22n ⎛⎫-+ ⎪⎝⎭的无理数x ,定义x x m m C C =,我们知道,若m *∈N ,()n m n *∈N ≤和()r r n *∈N ≤,则有以下两个恒等式成立:①m n m n n C C -=;②11r r r m m m C C C -+=+,那么对于正整数n 和两个无理数()0,m n ∈,()1,r n ∈,以下两个等式依然成立的序号是______;①m n m n n C C -=;②11r r r n n n C C C -+=+.15.若()*212nx n x ⎛⎫-∈ ⎪⎝⎭N 的展开式中所有项的二项式系数之和为64,则展开式中的常数项是__________.16.已知集合S={﹣1,0,1},P={1,2,3,4},从集合S ,P 中各取一个元素作为点的坐标,可作出不同的点共有_____个. 17.已知25270127(231)(2)x x x a a x a x a x ++-=++++,求01234567a a a a a a a a +++++++=_______18.()6221x x x ⎛⎫+- ⎪⎝⎭展开式中的常数项为______. 19.用0,1,2,3,4,5这六个数字组成没有重复数字的三位数,且是偶数,则这样的三位数有______个.20.从6男2女共8名学生中选出队长1人,副队长1人,普通队员3人,组成5人服务队,要求服务队中至少有1名女生,共有________种不同的选法(用数字作答)三、解答题21.已知nx⎛+ ⎝的展开式中只有第五项的二项式系数最大.(1)求该展开式中有理项的项数; (2)求该展开式中系数最大的项. 22.已知()()2*01212,6nn n x a a x a x a x n N n +=++++∈,其中012,,,,n a a a a R ∈.(1)当6n =时,求6(12)x +的展开式中二项式系数最大的项和系数最大的项;(2)若n 为偶数,求246n a a a a +++⋯+的值. 23.三个女生和五个男生排成一排.(1)如果女生必须全排在一起,有多少种不同的排法; (2)如果女生必须全分开,有多少种不同的排法.24.已知(1n -的展开式中,所有项的二项式系数之和为128. (1)求展开式中的有理项;(2)求展开后所有项的系数的绝对值之和.25.已知在1nx ⎛+ ⎝的展开式中所有奇数项的二项式系数和为128. (1)求展开式中常数项;(2)求展开式中二项式系数最大的项.26.按照下列要求,分别求有多少种不同的方法?(用数字作答) (1) 6个不同的小球放入4个不同的盒子;(2) 6个不同的小球放入4个不同的盒子,每个盒子至少一个小球; (3) 6个相同的小球放入4个不同的盒子,每个盒子至少一个小球;(4) 6个不同的小球放入4个不同的盒子,恰有1个空盒.【参考答案】***试卷处理标记,请不要删除一、选择题 1.D 解析:D 【分析】先把5名同学分成3组,有113,122++++两种情况,再将他们分配下去即可求出. 【详解】5名同学分成3组,有113,122++++两种情况,故共有1235452225C C C A +=种分组方式,再将他们分配到图书馆、食堂、学生活动中心有336A =种方式,根据分步乘法计数原理可知,不同的安排方法共有256150⨯=种. 故选:D . 【点睛】本题主要考查有限制条件的排列组合问题的解法应用,解题关键是对“至少”的处理,属于中档题.方法点睛:常见排列问题的求法有: (1)相邻问题采取“捆绑法”; (2)不相邻问题采取“插空法”; (3)有限制元素采取“优先法”;(4)特殊元素顺序确定问题,先让所有元素全排列,然后除以有限制元素的全排列数.2.D解析:D 【解析】试题分析:先排三个空位,形成4个间隔,然后插入3个同学,故有3424A =种考点:排列、组合及简单计数问题3.D解析:D 【分析】根据题意,分两种情况讨论:①、甲、乙中只有1人被选中,②、甲、乙两人都被选中,根据分类计数原理可得 【详解】解:根据题意,分两种情况讨论:①、甲、乙中只有1人被选中,需要从甲、乙中选出1人,到C ,D 中的一个部门,其他三人到剩余的部门,有113223··24C C A =种选派方案.②、甲、乙两人都被选中,安排到C ,D 部门,从其他三人中选出2人,到剩余的部门,有2223·12A A =种选派方案, 综上可得,共有24+12=36中不同的选派方案, 故选D . 【点睛】本题考查排列、组合的应用,涉及分类加法原理的应用,属于中档题.4.A解析:A 【分析】根据题意,分2种情况讨论:①甲在最中间,将剩余的4人全排列,②乙在中间,分析可得此时的排法数目,由加法原理计算可得答案. 【详解】根据题意,中间只能排甲或乙,分2种情况讨论:①甲在中间将剩余的4人全排列,有4424A =种情况,②乙在中间,甲不能在最右端,有3种情况,将剩余的3人全排列,安排在剩下的三个位置,此时有33318A ⨯=种情况,则一共有241842+=种排法。

大连市选修三第一单元《计数原理》检测题(包含答案解析)