verilog语言编写八选一数据选择器

八选一数据选择器(DOC)

八选一数据选择器(DOC)1.4’b1001<<2=(6‘b100100),4’b1001>>2=(4’b0010 )。

2、完整的条件语句将产生(组合逻辑电路)电路,不完整的条件语句将产生(时序逻辑电路)电路。

3、用EDA技术进行电子系统设计的目标是最终完成(专用集成电路ASIC)的设计。

4、可编程器件分为(现场可编程列阵FPGA)和(复杂可编程逻辑器件 PLD)5、系统函数和任务函数的首字符标志为($),预编译指令首字符标志为(#)。

6、一个基本的Verilog-HDL程序由(Verilog-HDL )模块构成。

7、EDA技术在应用设计领域主要包含哪四个方面的内容(HDL)、(PLD )、( EDA工具软件)、(EDA开发系统)8、EDA技术的基本特征主要有哪5个方面:(自顶向下的设计方法)、(采用硬件描述语言)、(高层综合和优化).(并行工程)、(开放性和标准化)9、当前最流行的并成为IEEE标准的硬件描语言是( VHDI )和( Verilog-HDL)10、一个完整的Verilog-HDL设计模块包括:(模块关键字和模块名)、(端口列表)、(端口定义)、(功能描述)这4部分。

11Verilog-HDL模块的I/O端口声明用来声明模块端口定义中各端口数据流动方向,包括(输入端口)、(输出端口)、和(双向端口)12、Verilog-HDL语言的三种常用的模型描述方法为(行为描述)、(数据描述)和(结构描述)13、Verilog-HDL的数值集合由哪四种基本的值组成(0)、(1 )、 x)、( z )14、10’hxf=(10’xx xxxx1111 )10’hzf=(10’zzzzzz1111 )15、若a=5’b10x01,b=5’b10x01,则a= =b的结果为( X )、a= = =b的结果为( 1 )16、Wire[15:0] wire-b表示连线宽度为(16 )位,其最高位为(15),最低位为(0)。

fpga8选1数据选择器

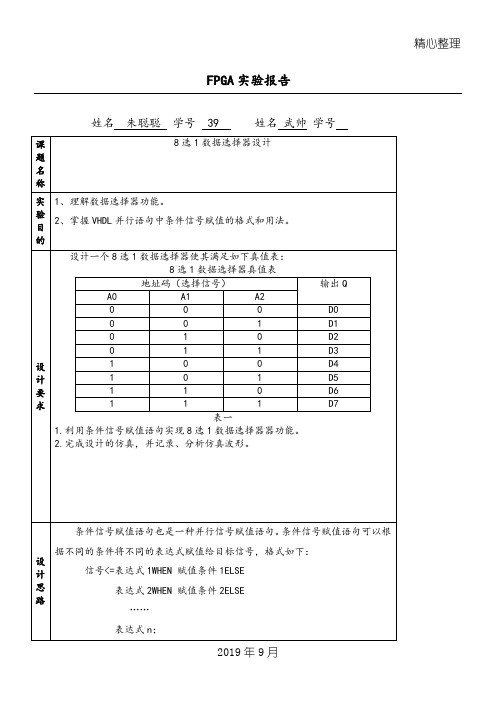

精心整理2019年9月FPGA 实验报告姓名 朱聪聪 学号 39 姓名 武帅 学号 课题名称 8选1数据选择器设计实验目的1、理解数据选择器功能。

2、掌握VHDL 并行语句中条件信号赋值的格式和用法。

设计要求设计一个8选1数据选择器使其满足如下真值表:8选1数据选择器真值表地址码(选择信号)输出Q A0 A1 A20 0 0D0 0 0 1D1 0 1 0D2 0 1 1D3 1 0 0D4 1 0 1D5 1 1 0D6 1 1 1D7 表一1.利用条件信号赋值语句实现8选1数据选择器器功能。

2.完成设计的仿真,并记录、分析仿真波形。

设计思路 条件信号赋值语句也是一种并行信号赋值语句。

条件信号赋值语句可以根据不同的条件将不同的表达式赋值给目标信号,格式如下:信号<=表达式1WHEN 赋值条件1ELSE表达式2WHEN 赋值条件2ELSE ……表达式n ;精心整理2019年9月设计原理图及源程序 LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY MUX8 ISPORT(D:IN STD_LOGIC_VECTOR(7 DOWNTO 0);A:IN STD_LOGIC_VECTOR(2 DOWNTO 0);Q:OUT STD_LOGIC);END ENTITY MUX8;ARCHITECTURE one OF MUX8 IS BEGIN Q<=D(0) WHEN A="000" ELSE D(1) WHEN A="001" ELSE D(2) WHEN A="010" ELSED(3) WHEN A="011" ELSED(4) WHEN A="100" ELSED(5) WHEN A="101" ELSED(6) WHEN A="110" ELSED(7) WHEN A="111" ELSE'Z';END one;.. 仿真波形图实验总结及个人心得体会通过本次实验,复习了之前学习的条件信号赋值语句。

实验三8选1数据选择器实验报告

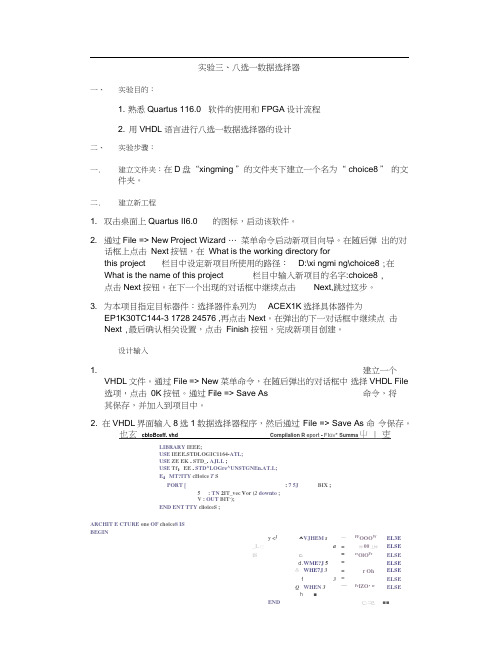

实验三、八选一数据选择器一、实验目的:1. 熟悉Quartus 116.0 软件的使用和FPGA设计流程2. 用VHDL语言进行八选一数据选择器的设计二、实验步骤:一.建立文件夹:在D盘“xingming ”的文件夹下建立一个名为“ choice8 ” 的文件夹。

二.建立新工程1. 双击桌面上Quartus II6.0 的图标,启动该软件。

2. 通过File => New Project Wizard … 菜单命令启动新项目向导。

在随后弹出的对话框上点击Next按钮,在What is the working directory forthis project 栏目中设定新项目所使用的路径:D:\xi ngmi ng\choice8 ;在What is the name of this project 栏目中输入新项目的名字:choice8 ,点击Next按钮。

在下一个出现的对话框中继续点击Next,跳过这步。

3. 为本项目指定目标器件:选择器件系列为ACEX1K选择具体器件为EP1K30TC144-3 1728 24576 ,再点击Next。

在弹出的下一对话框中继续点击Next ,最后确认相关设置,点击Finish按钮,完成新项目创建。

设计输入1. 建立一个VHDL文件。

通过File => New 菜单命令,在随后弹出的对话框中选择VHDL File 选项,点击0K按钮。

通过File => Save As 命令,将其保存,并加入到项目中。

2.在VHDL界面输入8选1数据选择器程序,然后通过File => Save As 命令保存。

也玄cbtoBceff. vhd Compilalion R eport - FI GV* Summa屮 | 吏LIBRARY IEEE;USE IEEE.STDLOGIC1164-ATL;USE ZE EK . STD_. AJLL ;USE Tf:EE . STD^LOGre^UNSTGNEn.AT.L;E:MT?ITY cHoice T SPORT [ : 7 5J BIX ;5 : TN 2IT_vec V or (2downto ;V : OUT BIT-);END ENT TTY clioiceS ;ARCHIT E CTURE one OF choice8 ISBEGINy <J-A V JHEM s—FF OOO W EL3E_L巳a=忡00丄忡ELSEiS C-=rr OlO Fr ELSEd.W ME?J 5=ELSE吕WHE7J 3=r Oh ELSEf3=ELSEQ WHEN 3—Fr lZO,rr ELSEh■END匸:二已■■四.综合适配1. 选择Processing =>Start Compilation 命令, 检查发现无程序语法错误。

八选一数据选择器

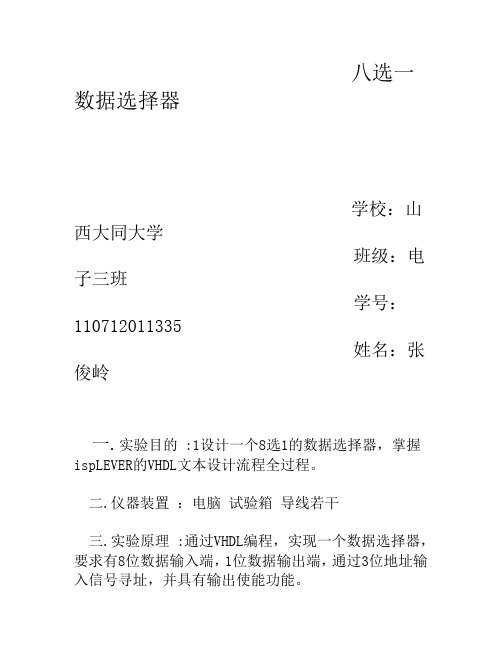

八选一数据选择器学校:山西大同大学班级:电子三班学号:110712011335姓名:张俊岭一.实验目的 :1设计一个8选1的数据选择器,掌握ispLEVER的VHDL文本设计流程全过程。

二.仪器装置:电脑试验箱导线若干三.实验原理 :通过VHDL编程,实现一个数据选择器,要求有8位数据输入端,1位数据输出端,通过3位地址输入信号寻址,并具有输出使能功能。

四.实验步骤:1 编写八选一多路选择器的源代码,编译完成后,新建波形仿真文件,进行功能仿真,验证真值关系是否满足。

2 引脚指定后,下载到芯片ispLSI1032E-70LJ84中,测试逻辑关系,验证本项设计的功能。

五实验记录: LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY EIGHT_XUAN_1 ISPORT( ST: IN STD_LOGIC;A: IN STD_LOGIC_VECTOR(2 DOWNTO 0);D: IN STD_LOGIC_VECTOR(7 DOWNTO 0);Q: OUT STD_LOGIC);END;ARCHITECTURE HBV OF EIGHT_XUAN_1 ISSIGNAL Q1: STD_LOGIC;BEGINPROCESS(A)BEGINIF ST='1' THEN Q1<='0';ELSECASE A ISWHEN "000"=> Q1 <= D(0);WHEN "001"=> Q1 <= D(1);WHEN "010"=> Q1 <= D(2);WHEN "011"=> Q1 <= D(3);WHEN "100"=> Q1 <= D(4);WHEN "101"=> Q1 <= D(5);WHEN "110"=> Q1 <= D(6);WHEN "111"=> Q1 <= D(7);WHEN OTHERS => NULL;END CASE;END IF;END PROCESS;Q<= Q1;END HBV;六.问题及讨论:1.这次实验运用ispLEVER软件设计并仿真了8选1数据选择器。

verilog语言编写八选一数据选择器

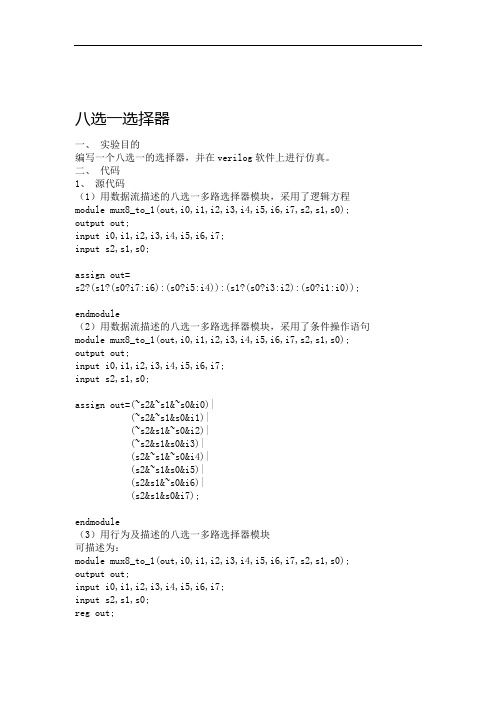

八选一选择器一、实验目的编写一个八选一的选择器,并在verilog软件上进行仿真。

二、代码1、源代码(1)用数据流描述的八选一多路选择器模块,采用了逻辑方程module mux8_to_1(out,i0,i1,i2,i3,i4,i5,i6,i7,s2,s1,s0); output out;input i0,i1,i2,i3,i4,i5,i6,i7;input s2,s1,s0;assign out=s2?(s1?(s0?i7:i6):(s0?i5:i4)):(s1?(s0?i3:i2):(s0?i1:i0));endmodule(2)用数据流描述的八选一多路选择器模块,采用了条件操作语句module mux8_to_1(out,i0,i1,i2,i3,i4,i5,i6,i7,s2,s1,s0); output out;input i0,i1,i2,i3,i4,i5,i6,i7;input s2,s1,s0;assign out=(~s2&~s1&~s0&i0)|(~s2&~s1&s0&i1)|(~s2&s1&~s0&i2)|(~s2&s1&s0&i3)|(s2&~s1&~s0&i4)|(s2&~s1&s0&i5)|(s2&s1&~s0&i6)|(s2&s1&s0&i7);endmodule(3)用行为及描述的八选一多路选择器模块可描述为:module mux8_to_1(out,i0,i1,i2,i3,i4,i5,i6,i7,s2,s1,s0); output out;input i0,i1,i2,i3,i4,i5,i6,i7;input s2,s1,s0;reg out;always @(s2 or s1 or s0 or i0 or i1 or i2 or i3 or i4 or i5 or i6or i7)begincase({s2,s1,s0})3'b000:out=i0;3'b001:out=i1;3'b010:out=i2;3'b011:out=i3;3'b100:out=i4;3'b101:out=i5;3'b110:out=i6;3'b111:out=i7;defult:$dispiay(Invalid control signals);endcaseendendmodule或者是:module mux8_to_1(out,i0,i1,i2,i3,i4,i5,i6,i7,s2,s1,s0);output out;input i0,i1,i2,i3,i4,i5,i6,i7;input s2,s1,s0;reg out;always @(s2 or s1 or s0 or i0 or i1 or i2 or i3 or i4 or i5 or i6or i7)begincase({s2,s1,s0})3'd1:out=i0;3'd2:out=i1;3'd3:out=i2;3'd4:out=i3;3'd5:out=i4;3'd6:out=i5;3'd7:out=i6;3'd8:out=i7;defult:$dispiay(Invalid control signals);endcaseendendmodule2、激励模块`timescale 1ns/100psmodule mux8_to_1_tb;reg I0,I1,I2,I3,I4,I5,I6,I7;reg S2,S1,S0;wire OUT;mux8_to_1 ul(.out(OUT),.i0(I0),.i1(I1),.i2(I2),.i3(I3),.i4(I4),.i5(I5),.i6(I6),.i7(I7),.s2(S2),.s1(S1),.s0(S0));initialbeginI0=1;I1=0;I2=0;I3=1;I4=1;I5=1;I6=0;I7=0;S2=0;S1=0;S0=0;#10 S2=0;S1=0;S0=1;#10 S2=0;S1=1;S0=0;#10 S2=0;S1=1;S0=1;#10 S2=1;S1=0;S0=0;#10 S2=1;S1=0;S0=1;#10 S2=1;S1=1;S0=0;#10 S2=1;S1=1;S0=1;endendmodule三、仿真波形四、波形说明波形图中,从上至下依次为:输入数据I0,I1,I2,I3,I4,I5,I6,I7,选择端口S2,S1,S0,输出COUT。

8路抢答器verilog语言程序

8路抢答器v e r i l o g语言程序-CAL-FENGHAI-(2020YEAR-YICAI)_JINGBIAN/****************************************************************************** **Copyright(c) , All right reservedProject name : 八路抢答器File name :Author : THE CEmail============================================================================= Description : 八路抢答器Called by :File tree :============================================================================= Revision History:Date By Ver. Change Description------------------------------------------------------------------------------2012-12-26 THE C 首次归档******************************************************************************* */`timescale 1ns/100psmodule choose8_1(input clk,input rst,input [7:0] keyin,output reg [2:0] sel,output reg [7:0] display);reg [9:0] count;reg clk_1hz,flag;reg [4:0] t;reg [3:0] disp;reg [3:0] data;always @ (negedge clk)if (count<999)count=count+1;elsebegincount=0;clk_1hz=~clk_1hz;endalways @ (posedge clk or negedge rst)beginif (!rst)begindata <= 4'b1010;flag <= 1'b0;endelseif (!flag && t)case (keyin [7:0])8'b00000001 : begin data<=4'b0001; flag<=1; end 8'b00000010 : begin data<=4'b0010; flag<=1; end 8'b00000100 : begin data<=4'b0011; flag<=1; end 8'b00001000 : begin data<=4'b0100; flag<=1; end 8'b00010000 : begin data<=4'b0101; flag<=1; end 8'b00100000 : begin data<=4'b0110; flag<=1; end 8'b01000000 : begin data<=4'b0111; flag<=1; end 8'b : begin data<=4'b1000; flag<=1; enddefault : begin data<=data; flag<=flag; endendcaseelse;endalways @ (posedge clk_1hz or negedge rst)beginif (!rst)t<=30;elseif (t>0 && !flag)t<=t-1;elset<=t;endalways @ (posedge clk or negedge rst)beginif (!rst)sel [2:0] <= 3'b000;elsebeginsel [2:0] <= sel[2:0]+3'b001;endendalways @ (*)begincase( sel[2:0] )3'b000: disp [3:0] = t/10;3'b001: disp [3:0] = t%10;3'b010: disp [3:0] = 4'b1111;3'b011: disp [3:0] = 4'b1010+clk_1hz;3'b100: disp [3:0] = 4'b1010+clk_1hz;3'b101: disp [3:0] = 4'b1010+clk_1hz;3'b110: disp [3:0] = 4'b1111;3'b111: disp [3:0] = data;endcaseendalways @ (*)begincase( disp )4'b0000: display [7:0]=8'b01111110; //04'b0001: display [7:0]=8'b00110000; //14'b0010: display [7:0]=8'b01101101; //24'b0011: display [7:0]=8'b01111001; //34'b0100: display [7:0]=8'b00110011; //44'b0101: display [7:0]=8'b01011011; //54'b0110: display [7:0]=8'b01011111; //64'b0111: display [7:0]=8'b01110000; //74'b1000: display [7:0]=8'b01111111; //84'b1001: display [7:0]=8'b01111011; //94'b1010: display [7:0]=8'b00000001; //-default: display [7:0]=8'b00000000; //全灭 endcaseendendmodule。

八选一数据选择器逻辑电路设计思路

八选一数据选择器逻辑电路设计思路哎呀,这道题目可真是让人头疼啊!不过,别着急,我们一起来想办法解决这个问题吧!我们来看看这个题目的要求:八选一数据选择器逻辑电路设计思路。

简单来说,就是要我们设计一个逻辑电路,它可以从8个输入信号中选择其中一个输出。

这听起来好像很简单,但是实际上还是有一些细节需要注意的。

那么,我们现在就开始着手解决这个问题吧!我们需要明确一下这个逻辑电路的基本结构。

一般来说,这种类型的逻辑电路通常由触发器和多路复用器组成。

触发器可以用来存储输入信号的状态,而多路复用器则可以用来选择不同的输入信号进行处理。

接下来,我们需要考虑一下具体的实现方法。

对于这个问题,我们可以使用两个触发器和三个多路复用器来实现。

具体来说,我们可以将第一个触发器的Q0引脚连接到第二个触发器的D引脚上,这样就可以实现第一个触发器的输出与第二个触发器的输入相同。

然后,我们将第一个触发器的Q1引脚连接到第三个多路复用器的A引脚上,将第一个触发器的Q2引脚连接到第四个多路复用器的A引脚上,将第一个触发器的Q3引脚连接到第五个多路复用器的A引脚上,将第一个触发器的Q4引脚连接到第六个多路复用器的A引脚上,将第一个触发器的Q5引脚连接到第七个多路复用器的A引脚上,将第一个触发器的Q6引脚连接到第八个多路复用器的A引脚上。

这样一来,当第一个触发器的输出为1时,第二个触发器的输出就会被选择出来;当第一个触发器的输出为0时,第二个触发器的输出就不会被选择出来。

同样的道理,当第一个触发器的输出为1时,第三个、第四个、第五个、第六个、第七个和第八个多路复用器的输出都会被选择出来;当第一个触发器的输出为0时,这些多路复用器的输出就不会被选择出来。

我们还需要考虑一下如何控制这个逻辑电路的工作状态。

一般来说,我们可以使用一些基本的逻辑门来实现这一点。

比如说,我们可以使用与门来控制触发器的输出是否为高电平;使用或门来控制多路复用器的选择功能是否被激活;使用非门来控制整个逻辑电路的工作状态是否被改变。

Verilog HDL复习题

聂雄题型介绍:一、选择题(每小题2分,共20分)1.在verilog中,下列语句哪个不是分支语句?( d )161(A) if-else (B) case (C) casez (D) repeat循环2.下列哪些的不属于基本门级元件( d )136(A) nand (B) nor (C) and (D) RAM3.已知“a =1b’1; b=3b'001;”那么{a,b}=( c )120 131(A) 4b'0011 (B) 3b'001 (C) 4b'1001 (D) 3b'101…………其它略……….二、填空题(每小题2分,共10分)1. 完整的条件语句将产生组合电路,不完整的条件语句将产生时序电路。

2. 阻塞性赋值符号为 = ,非阻塞性赋值符号为《= 。

…………其它略……….三、简答题:(每小题5分,共20分)1. 结构化描述可以通过哪几种方式进行结构建模?(5分)1172. FPGA芯片主流的生产厂家有哪3家?每个厂家列举2个型号芯片,并说明它所具有的逻辑门数量和IO端口数量。

(5分)…………其它略……….六、设计题(每小题10分,共40分)1. 使用Verilog语言,设计一个带有异步复位控制端的100进制计数器。

(10分)1862. 基于Verilog语言设计一个8选一数据选择器,写出Verilog代码。

(10分)180 module option(a,b,c,d,e,f,g,h,s0,s1,s2,out);input [2:0] a,b,c,d,e,f,g,h;input s0,s1,s2;output [2:0] out;reg [2:0] out;always@(a or b or c or d or e or f or g or h or s0 or s1 or s2)begincase({s0,s1,s2})3'd0 : out=a;3'd1 : out=b;3'd2 : out=c;3'd3 : out=d;3'd4 : out=e;3'd5 : out=f;3'd6 : out=g;3'd7 : out=h;endcase endendmodule…………其它略……….网上试题:填空:1.已知x=4’b1001,y=4’0110,则 x 的 4 位补码为4’b1111,而 y 的 4 位的补码为4’b0110?2.在 case 语句中至少要有一条 default 语句。

八选一数据选择器逻辑电路设计思路

八选一数据选择器逻辑电路设计思路数据选择器逻辑电路设计,让复杂变简单嘿,朋友们!今天咱们来聊一聊那个让人头疼又爱不释手的东西——数据选择器逻辑电路。

别急,让我用轻松幽默的方式,带你一起走进这个小小的“魔法世界”。

想象一下,你手里有一堆颜色各异的糖果,想要选出一种特定的颜色,比如红色。

这听起来是不是有点像我们在设计数据选择器时的挑战?没错,就是那种既需要精准又得巧妙处理的选择难题。

你得知道数据选择器是什么。

简单来说,它就像是个小魔术师,能够从一大堆数据中,挑选出你想要的那一个。

但它可不是随便选一个就行,而是要根据输入的信号来决定输出的。

这个过程就像是一场智慧与勇气的较量,既要有策略,又要有胆量。

接下来,咱们说说设计思路。

设计数据选择器的时候,你得先搞清楚你要控制的是哪一类信号。

比如,你是想控制数字信号还是模拟信号?是单端还是差分信号?这些问题就像是一座座山,只有越过它们,你才能找到通往成功的道路。

然后,你需要规划你的电路结构。

想象一下,你正在搭建一座城堡,每个元件就像是城堡里的一间房,而你的设计思路就像是城堡的蓝图。

你得确保所有的房间都按照计划建造好,这样才能保证城堡稳固、美观。

当然啦,设计过程中难免会遇到一些“小麻烦”。

比如,有时候信号可能会混在一起,让你难以分辨哪个才是你想要的。

这时候,你得学会运用各种“技巧”,比如滤波器、多路复用器等等,来帮助你解决问题。

别忘了测试和调试。

就像战士在战斗结束后要检验战利品一样,你在完成设计后也要对电路进行测试,确保它能够正常工作,没有遗漏任何细节。

数据选择器逻辑电路的设计并不是一件容易的事情,但只要你有耐心、细心,再加上一点点创意和想象力,你一定能够成为那个出色的“魔法师”。

在这个过程中,你会发现自己不仅学会了如何解决问题,还收获了成长和快乐。

所以,不要害怕挑战,勇敢地去迎接吧!。

八加一数据选择器组合逻辑电路设计思路

八加一数据选择器组合逻辑电路设计思路下载提示:该文档是本店铺精心编制而成的,希望大家下载后,能够帮助大家解决实际问题。

文档下载后可定制修改,请根据实际需要进行调整和使用,谢谢!本店铺为大家提供各种类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by this editor. I hope that after you download it, it can help you solve practical problems. The document can be customized and modified after downloading, please adjust and use it according to actual needs, thank you! In addition, this shop provides you with various types of practical materials, such as educational essays, diary appreciation, sentence excerpts, ancient poems, classic articles, topic composition, work summary, word parsing, copy excerpts, other materials and so on, want to know different data formats and writing methods, please pay attention!八加一数据选择器组合逻辑电路设计思路1. 简介在数字电路设计中,数据选择器是一种常见的组合逻辑电路,用于从多个输入中选择一个输出。

八选一数据选择器逻辑电路设计思路

八选一数据选择器逻辑电路设计思路哎呀,这题目真是让人头疼啊!不过没关系啦,小生我可是万能的,一定能帮你解决这个问题。

我们得明确一下题目的要求:设计一个八选一数据选择器逻辑电路。

听起来好像挺复杂的,但是别担心,小生我可是经验丰富,一定能让你轻松搞定。

我们要了解一下八选一数据选择器的原理。

它其实就是一个有8个输入端口和1个输出端口的电路。

当我们给这个电路输入不同的数据时,它会根据一定的逻辑关系,从8个输入端口中选择其中一个输出。

这个过程就像是在一堆人里面挑出一个人一样,只不过这个人是根据某种规则挑选出来的而已。

那么,我们该如何设计这样一个逻辑电路呢?其实,方法有很多种。

比如说,我们可以用三态门来实现。

三态门是一种特殊的逻辑门,它有3个输出状态:高电平、低电平和高阻态。

我们可以通过控制三态门的输入和输出,来实现八选一数据选择器的功能。

具体来说,我们可以这样设计:我们用4个二极管和2个三极管搭建一个基本的触发器电路。

然后,我们在这个触发器的基础上,加上一些逻辑门,用来实现八选一的功能。

具体来说,我们可以用一个或门(OR)来连接8个输入端口和一个与门(AND)。

当且门的输入端都是高电平时,与门的输出端就会是高电平;否则,与门的输出端就会是低电平。

这样一来,我们就可以根据与门的输出端来判断应该选择哪个输入端口作为输出了。

当然啦,这只是一种方法而已。

实际上,还有很多其他的方法可以用来实现八选一数据选择器的功能。

比如说,我们还可以用乘法器和加法器来实现;或者用寄存器和移位寄存器来实现等等。

只要我们掌握了这些基本的逻辑知识,就一定能够设计出一个高效的八选一数据选择器逻辑电路。

好啦,现在我们已经知道了一个八选一数据选择器的原理和实现方法。

接下来呢,我们就要开始动手实践了!我们需要准备一些基本的电子元器件,比如二极管、三极管、电阻、电容等等。

然后呢,我们就可以按照前面提到的方法,开始搭建我们的逻辑电路了。

哎呀呀,这可不是一件容易的事情哦!有时候会遇到各种各样的问题,比如说电路接错了、元件烧坏了等等。

实验3 多路选择器的设计

实验3 多路选择器的设计

一、实验目的

1.熟练掌握多路选择器的设计方法

2.熟悉门级描述的编程方法;

二、实验内容

1.编写程序实现2选1的多路选择器

2.编写程序实现8选1的数据选择器

三、实验要求

1.根据参考内容,用Verilog HDL语言设计多路选择器。

2.用Quartus II或Modelsim 对其进行功能或时序进行波形仿真验证;

3.下载到FPGA开发板验证;

四、实验环境

Quartus Ⅱ

五、实验原理

数据选择是指经过选择,把多个通道的数据传送到唯一的公共数据通道上去。

实现数据选择功能的逻辑电路称为数据选择器,它的作用相当于多个输入的单刀多掷开关。

二选一数据选择器的原理框图如图1,真值表见图2。

六、 实验步骤

(1)打开Quartus II 新建工程,并进行相关配置; (2)添加Verilog HDL 文件,编辑代码; (3)编译、代码综合与波形仿真; (4)下载程序至FPGA 开发板。

图2 选1数据选择器真值表

图1 2选1数据选择器原理图

图3 8选1数据选择器原理图

七、实验程序(或者电路图)

八、实验结果

2选1数据选择器RTL

8选1数据选择器RTL

2选1数据选择器波形图仿真

8选1数据选择器波形图仿真

九、实验结果讨论

(结合实验过程、实验结果或老师的提出问题自行讨论)。

八选一数据选择器

《集成电路设计实践》报告题目:8选1数据选择器院系:自动化学院电子工程系专业班级:微电学生学号:学生姓名:指导教师姓名:职称:讲师起止时间:2015-12-21——2016-1-9 成绩:一、设计任务1) 依据8选1数据选择器的真值表,给出八选一MUX电路图,完成由电路图到晶体管级的转化(需提出至少2种方案);2) 绘制原理图(Sedit),完成电路特性模拟(Tspice,瞬态特性),给出电路最大延时时间;3) 遵循设计规则完成晶体管级电路图的版图,流程如下:版图布局规划-基本单元绘制-功能块的绘制-布线规划-总体版图);4) 版图检查与验证(DRC检查);5) 针对自己画的版图,给出实现该电路的工艺流程图。

二、电路设计方案的确定数据选择器是指经过选择,把多个通道的数据传送到唯一的公共数据通道上去,实现数据选择功能的逻辑电路称为数据选择器。

它的作用相当于多个输入的单刀多掷开关,其示意图如下所示数据选择器除了可以实现一些组合逻辑功能以外,还可以做分时多路传输电路,函数发生器及数码比较器等,常见的数据比较器有2选1,4选1,8选1,16选1电路。

示意图在多路数据传送过程中,能够根据需要将其中任意一路选出来的电路,叫做数据选择器。

数据选择器(MUX)的逻辑功能是在地址选择信号的控制下,从多路数据中选择一路数据作为输出信号。

本次设计的是8选1数据选择器。

选择控制端(地址端)为K2,K1,K0,按二进制译码,从8个输入数据D0-D7中,选择一个需要的数据送到输出端Y。

根据多路开关的开关状态(地址码)K2,K1,K0的状态选择D0-D7中某一个通道的数据输送到输出端Y。

如:K2K1K0=000,则选择D0数据到输出端,即Y=D0。

如:K2K1K0=001,则选择D1数据到输出端,即Y=D1,其余类推。

8选1 MUX功能表如下:K2 K1 K0 Y0 0 0 D00 0 1 D10 1 0 D20 1 1 D31 0 0 D41 0 1 D51 1 0 D61 1 1 D7电路图设计如下:1:此电路为组合逻辑门电路,电路为CMOS实现功能,电路规模较大,工作量大,版图布局规模较大,相比之下,选择传输门电路实现8选1数据选择器功能。

八选一数据选择器和四位数据比较器verilog实验报告

Verilog HDV数字设计与综合实验报告微电子0901班姓名:袁东明 _学号:_04094026一、实验课题:1.八选一数据选择器2.四位数据比较器二、八选一数据选择器Verilog程序:2.1主程序module option(a,b,c,d,e,f,g,h,s0,s1,s2,out);input [2:0] a,b,c,d,e,f,g,h;input s0,s1,s2;output [2:0] out;reg [2:0] out;always@(a or b or c or d or e or f or g or h or s0 or s1 or s2) begincase({s0,s1,s2})3'd0 : out=a;3'd1 : out=b;3'd2 : out=c;3'd3 : out=d;3'd4 : out=e;3'd5 : out=f;3'd6 : out=g;3'd7 : out=h;endcaseendendmodule2.2激励程序module sti;reg [2:0] A,B,C,D,E,F,G,H;reg S0,S1,S2;wire [2:0] OUT;option dtg(A,B,C,D,E,F,G,H,S0,S1,S2,OUT);initialbeginA=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=0;S1=0;S2=0;#100 A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=0;S1=0;S2=1; #100 A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=0;S1=1;S2=0; #100 A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=0;S1=1;S2=1; #100 A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=1;S1=0;S2=0; #100 A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=1;S1=0;S2=1;#100 A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=1;S1=1;S2=0; #100 A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=1;S1=1;S2=1; endendmodule三、四位数据比较器3.1主程序module fourcompare(a,b,c);input[3:0] a,b;output [1:0] c;reg[1:0] c;always@(a or b)beginif(a>b)c=2'd2;else if(a<b)c=2'd1;elsec=2'd0;endendmodule3.2激励程序module sti;reg [3:0] A,B;wire [1:0]C;fourcompare fte(A,B,C);initialbeginA=2'd0;B=2'd1;#100 A=2'd2;B=2'd1;#100 A=2'd1;B=2'd1;endendmodule四、实验波形图截图:4.1八选一数据选择器4.2四位数据比较器四、波形分析及实验心得:4.1.波形分析1.八选一数据选择器输入数据为A=000,B=001,C=010,D=011,E=100,F=101,g=110,h=111;S0,S1,S2,为选择控制端,它们组成一个三位数,记为enable,控制数据的输出,其中S0为最高位,S1次之,S2为最低位。

八选一数据选择器逻辑电路设计思路

八选一数据选择器逻辑电路设计思路哎呀,这道题目真是让人头疼啊!不过没关系,我们一起来聊聊八选一数据选择器逻辑电路设计思路吧!我们得明确什么是八选一数据选择器。

它就是一种电子元件,可以将8个输入信号中的任意一个信号输出。

听起来好像很简单的样子,但是要想设计出一个好用的八选一数据选择器,可不是一件容易的事情哦!那么,我们该如何设计这样一个逻辑电路呢?我们需要了解一下基本的逻辑门电路知识。

比如与门、或门、非门等等。

这些门电路可以用来实现各种不同的逻辑功能。

而八选一数据选择器所需要的功能,其实就是从8个输入信号中选出一个输出信号。

这个功能可以通过组合使用多个与门和或门来实现。

具体来说,我们可以先用两个与门来分别对应输入信号的前四个和后四个。

然后再用一个或门将这两个结果进行组合。

这样就可以实现从8个输入信号中选出任意一个输出信号的功能了。

如果你想要更加灵活地选择输出信号的话,还可以使用其他的组合方式。

比如可以使用三个与门和一个或门来实现同样的功能。

除了基本的逻辑门电路之外,我们还需要了解一下常用的触发器电路。

触发器是一种能够保存并根据时钟信号改变其状态的电路。

在八选一数据选择器的设计中,我们常常会用到多路复用触发器和边沿触发器这两种类型的触发器。

多路复用触发器可以同时处理多个输入信号,并且可以根据不同的输入信号改变其输出状态。

而边沿触发器则只能在输入信号发生变化的时候改变其状态。

因此,在设计八选一数据选择器时,我们需要根据具体的应用场景来选择合适的触发器类型。

我们还需要注意一下电路板的设计问题。

毕竟,一个好的电路板不仅可以提高电路的性能和稳定性,还可以让整个系统更加美观和易于维护。

因此,在设计八选一数据选择器的电路板时,我们需要考虑到PCB布局、元器件放置等因素。

设计一款优秀的八选一数据选择器并不是一件容易的事情。

需要我们具备扎实的电子基础知识、熟练掌握各种逻辑门电路和触发器的使用方法,并且还需要有一定的电路板设计经验。

verilog设计

Verilog 程序设计报告一、课题概述:任务:本实验主要完成8位比较器、分频器、阻塞赋值和非阻塞赋值的区别、8路的数据选择器、有限状态机的设计。

目的:通过实验掌握基本组合逻辑电路、时序逻辑电路的实现流程;条件语句及case语句的用法;在实验中认识阻塞赋值和非阻塞赋值的区别;能够设计出简单的有限状态机。

要求:熟练掌握verilog的基本语法知识和一些基本语句的用法。

二、设计思路及采取方案思路:(1)8位比较器可以用数据流描述方法(assign赋值语句)或行为描述方法(always语句)或结构描述方法(元件例化)实现。

(2)分频器可以采用if…else语句或case语句实现。

(3)阻塞赋值和非阻塞赋值的区别可以通过观察波形图及分析综合出的电路图来得到。

(4)8位数据选择器可以采用assign赋值语句及always语句实现。

(5)有限状态机可以采用case语句实现。

方案:(1)8位的比较器采用assign赋值语句实现。

(2)用if…else条件语句实现分频器的设计。

(3)通过观察波形图,得出利用阻塞赋值和非阻塞赋值设计电路的特点和区别。

(4)利用always语句实现8位数据选择器。

(5)利用case语句完成有限状态机的设计。

三、实验结果结果:我基本完成以上的5个任务,并且通过这些任务的完成,巩固了已经学过的知识,提高了自己的动手操作能力,坚定了继续学习的信心。

四、实验体会体会:第一次接触学习硬件编程语言,感受到verilog与软件编程语言有着许多显著的差别,最重要的是用verilog可以编出并行执行的程序,通过不断的学习和实践,习惯了用硬件结构思路编程,由于一些细节把握不到位,在设计中出现了许多错误;像进程赋值语句声明寄存器变量时格式出错、begin-end声明语句没有注意相互匹配、在声明语句的末尾忘了写上分号等等。

编译不成功时,我会不厌其烦的去查找错误,直至编译成功、满足题目的要求。

通过实验不仅巩固了已经学过的知识而且加强了自己的动手操作能力,为以后的考研及工作打下了基础。

8位数据选择器

8位数据选择器姓名:高军宝班级:微电子0803学号:04084095(30)报告日期:1.实验目的练习在ModelSim下编写Verilog程序,熟悉ModelSim运行过程,并学会用verilog编写一个8位数据选择器。

2.实验任务编写一个8位数据选择器。

功能模块和激励模块的写在两个文件中。

3.实验内容及步骤3.1 实验内容编写8位数据选择器的功能模块和激励模块。

3.2 本次所实现的功能描述8位数据选择器有两个输入端:一个是使能端,一个数据选择端;一个数据输出;本实验采用行为级级建模进行编程。

3.3 本次实验的设计方案1.进入modelsim后点击file ----> new ---->project.之后出现一个建立工程的对话框,键入sel8工程名后,再在下面路径添加一个自己的文件夹。

确认后会弹出一个对话框,点击creat New File,在工程sel8下建立两个文件分别叫做sel8的功能模块文件和sel8_top的测试激励模块文件。

2.双击进入文件后编写程序3.编译,如果程序出错对程序进行修改。

之后再编译,编译成功后点击simulate进行仿真。

.4.观察仿真结果是否符合事先的设计。

不符合继续修改程序。

sel8.vmodule sel8( data_out,en,data_sel);input en;input [2:0] data_sel;reg [2:0] data_out;always @(data_sel)if(en)begincase(data_sel)3'b000: data_out=3'd0;3'b001: data_out=3'd1;3'b010: data_out=3'd2;3'b011: data_out=3'd3;3'b100: data_out=3'd4;3'b101: data_out=3'd5;3'b110: data_out=3'd6;3'b111: data_out=3'd7;endcaseendelseendmodulesel8_top.v`timescale 10ns/1nsmodule sel8_top;wire [2:0] data_out;reg en;reg [2:0] data_sel;integer i;sel8 s1(.data_out(data_out),.en(en),.data_sel(data_sel));initialbeginen=1'b1;data_sel=3'b0;endalways #70 en=~en;alwaysif(i!=8)begin#5 data_sel=data_sel+1'b1;i=i+1;endelsebegindata_sel=3'b0;i=0;endendmodule3.4 本次实验设计的结果本实验测试结果:4.实验总结这也是数电书上的电路,要写一个完整的,健壮的程序,必须考虑完全,并且要使程序的可综合性强,写激励时要将所包含的每个情况考虑进去,最主要的一点是要勤动手,多写程序,多思,才能有所提高。

八选一数据选择器逻辑电路设计思路

八选一数据选择器逻辑电路设计思路哎呀,这可是个不简单的题目啊!不过别着急,我们一起来聊聊八选一数据选择器逻辑电路设计思路吧!咱们得明确什么是八选一数据选择器。

它就是一个小小的电路,能从8个输入信号中选出1个输出信号。

听起来挺简单的,但实际上可不是那么回事哦!要想设计一个好用的八选一数据选择器,我们得先了解一下它的工作原理。

简单来说,八选一数据选择器的输入端有8个信号,输出端只有1个信号。

当输入信号发生变化时,电路会根据一定的规则来选择其中一个信号输出。

那么,这个规则是什么呢?其实很简单啦!就是根据输入信号的高低电平来决定输出哪个信号。

具体来说,当输入信号为高电平时,电路会选择第一个输入信号输出;当输入信号为低电平时,电路会选择第二个输入信号输出;以此类推,直到输入信号为高电平时,电路会选择第八个输入信号输出。

明白了原理之后,我们就可以开始设计八选一数据选择器了。

我们需要准备一些基本的电子元器件,比如电阻、电容、二极管等等。

然后,我们可以按照以下步骤来进行设计:1. 我们需要搭建一个基本的放大电路。

这个放大电路的作用是将输入信号放大一定的倍数,以便于后面的处理。

我们可以选择一个合适的放大倍数,比如10倍左右。

2. 接下来,我们需要搭建一个多路开关电路。

这个多路开关电路的作用是将放大后的信号分成8路,每路对应一个输入信号。

我们可以选择一个合适的多路开关芯片,比如4位二进制计数器芯片。

3. 然后,我们需要搭建一个译码电路。

这个译码电路的作用是根据多路开关芯片输出的状态来决定哪一路输入信号被选中。

我们可以选择一个合适的译码芯片,比如74HC154译码器芯片。

4. 我们需要搭建一个输出驱动电路。

这个输出驱动电路的作用是将选中的输入信号放大一定的倍数后输出。

我们可以选择一个合适的输出驱动芯片,比如TDA2030功率放大器芯片。

好了,经过以上的设计步骤之后,我们就成功地搭建了一个八选一数据选择器电路!当然啦,这只是一个基本的设计思路,实际应用中可能还需要根据具体情况进行调整和优化哦!。

八选一数据选择器和四位数据比较器verilog实验报告

八选一数据选择器和四位数据比较器verilog实验报告实验报告:八选一数据选择器和四位数据比较器一、引言数据选择器和数据比较器是数字电路中常用的基本电路模块,它们在许多数字系统中起着重要的作用。

本实验通过使用Verilog语言,设计并实现了八选一数据选择器和四位数据比较器电路。

本实验报告将分别介绍这两个电路的设计原理、实验过程以及实验结果。

二、八选一数据选择器的设计1.设计原理八选一数据选择器是一种多路选择器,根据控制信号来选择其中一个输入信号输出。

其输入端包括8个数据输入信号(D0-D7)、3个控制信号(S2、S1、S0)以及一个使能信号(EN),输出端为一个数据输出信号(Y)。

当使能信号为高电平时,根据控制信号的值,将对应的输入信号输出。

2.设计过程本实验中,我们使用Verilog语言进行八选一数据选择器的设计。

首先,我们声明输入输出端口:module mux8to1(input [7:0] D, input [2:0] S, input EN,output reg Y);然后,我们使用case语句来实现根据控制信号选择输出信号的功能:beginif (EN)case (S)3'b000:Y=D[0];3'b001:Y=D[1];3'b010:Y=D[2];3'b011:Y=D[3];3'b100:Y=D[4];3'b101:Y=D[5];3'b110:Y=D[6];3'b111:Y=D[7];default: Y = 1'bx;endcaseelseY = 1'bx;end最后,我们将设计的模块实例化并进行仿真和综合验证。

三、四位数据比较器的设计1.设计原理四位数据比较器用于比较两个四位二进制数的大小。

其输入端包括两个四位二进制数(A、B),输出端为一个比较结果信号(OUT)。

当输入A大于B时,OUT为1;当A等于B时,OUT为0;当A小于B时,OUT为-12.设计过程本实验中,我们同样使用Verilog语言进行四位数据比较器的设计。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

八选一选择器

一、实验目的

编写一个八选一的选择器,并在verilog软件上进行仿真。

二、代码

1、源代码

(1)用数据流描述的八选一多路选择器模块,采用了逻辑方程module mux8_to_1(out,i0,i1,i2,i3,i4,i5,i6,i7,s2,s1,s0);

output out;

input i0,i1,i2,i3,i4,i5,i6,i7;

input s2,s1,s0;

assign out=

s2?(s1?(s0?i7:i6):(s0?i5:i4)):(s1?(s0?i3:i2):(s0?i1:i0));

endmodule

(2)用数据流描述的八选一多路选择器模块,采用了条件操作语句module mux8_to_1(out,i0,i1,i2,i3,i4,i5,i6,i7,s2,s1,s0);

output out;

input i0,i1,i2,i3,i4,i5,i6,i7;

input s2,s1,s0;

assign out=(~s2&~s1&~s0&i0)|

(~s2&~s1&s0&i1)|

(~s2&s1&~s0&i2)|

(~s2&s1&s0&i3)|

(s2&~s1&~s0&i4)|

(s2&~s1&s0&i5)|

(s2&s1&~s0&i6)|

(s2&s1&s0&i7);

endmodule

(3)用行为及描述的八选一多路选择器模块

可描述为:

module mux8_to_1(out,i0,i1,i2,i3,i4,i5,i6,i7,s2,s1,s0);

output out;

input i0,i1,i2,i3,i4,i5,i6,i7;

input s2,s1,s0;

reg out;

always (s2 or s1 or s0 or i0 or i1 or i2 or i3 or i4 or i5 or i6 or i7)

begin

case({s2,s1,s0})

3'b000:out=i0;

3'b001:out=i1;

3'b010:out=i2;

3'b011:out=i3;

3'b100:out=i4;

3'b101:out=i5;

3'b110:out=i6;

3'b111:out=i7;

defult:$dispiay("Invalid control signals");

endcase

end

endmodule

或者是:

module mux8_to_1(out,i0,i1,i2,i3,i4,i5,i6,i7,s2,s1,s0);

output out;

input i0,i1,i2,i3,i4,i5,i6,i7;

input s2,s1,s0;

reg out;

always (s2 or s1 or s0 or i0 or i1 or i2 or i3 or i4 or i5 or i6 or i7)

begin

case({s2,s1,s0})

3'd1:out=i0;

3'd2:out=i1;

3'd3:out=i2;

3'd4:out=i3;

3'd5:out=i4;

3'd6:out=i5;

3'd7:out=i6;

3'd8:out=i7;

defult:$dispiay("Invalid control signals");

endcase

end

endmodule

2、激励模块

`timescale 1ns/100ps

module mux8_to_1_tb;

reg I0,I1,I2,I3,I4,I5,I6,I7;

reg S2,S1,S0;

wire OUT;

mux8_to_1 ul(

.out(OUT),

.i0(I0),

.i1(I1),

.i2(I2),

.i3(I3),

.i4(I4),

.i5(I5),

.i6(I6),

.i7(I7),

.s2(S2),

.s1(S1),

.s0(S0)

);

initial

begin

I0=1;I1=0;I2=0;I3=1;I4=1;I5=1;I6=0;I7=0;

S2=0;S1=0;S0=0;

#10 S2=0;S1=0;S0=1;

#10 S2=0;S1=1;S0=0;

#10 S2=0;S1=1;S0=1;

#10 S2=1;S1=0;S0=0;

#10 S2=1;S1=0;S0=1;

#10 S2=1;S1=1;S0=0;

#10 S2=1;S1=1;S0=1;

end

endmodule

三、仿真波形

四、波形说明

波形图中,从上至下依次为:输入数据I0,I1,I2,I3,I4,I5,I6,I7,选择端口S2,S1,S0,输出COUT。

该程序实现的是控制选择端口选择对应的数据并输出。

当S2=0,S1=0,S0=0时,选择I0,输出I0的值1;

当S2=0,S1=0,S0=1时,选择I1,输出I0的值0;

当S2=0,S1=1,S0=0时,选择I2,输出I0的值0;

当S2=0,S1=1,S0=1时,选择I3,输出I0的值1;

当S2=1,S1=0,S0=0时,选择I4,输出I0的值1;

当S2=1,S1=0,S0=1时,选择I5,输出I0的值1;

当S2=1,S1=1,S0=0时,选择I6,输出I0的值0;

(当S2=1,S1=1,S0=1时,选择I7,输出I0的值0;)

在行为级描述的模块中,当输入端口的输入不符合既定要求的时候,则会输出 $dispiay("Invalid control signals");

五、实验过程中碰到的问题

经过前两次的实验,本次实验在操作过程中基本很流畅,没有再碰到对软件不够熟悉的情况,但是,本次实验结果却存在一定问题,从波形中也可以看到,选择端口S2=1,S1=1,S0=1的波形没有出现,当时在实验过程中没有找到问题所在,后来实验过后,我自己分析,是时间的设置太短,没有跑出那段波形,但是由于自己没有modelsim软件,通过各种自己可以达到的方法也无法下载到,所以只能等下次实验的时候再对这个问题进行分析。

六、实验心得

在实验过程中,不断的出现问题,然后修改问题,有时候还会在修改后出现新的问题,这个过程中,有过被一大堆问题弄的头晕眼花准备放弃的时候,但是自己写的程序,自己调试不好总觉得心有不甘,虽然这个实验报告可能达不到要求,因为里面是有错误的,但是我会尽力把这个错误纠正掉,最后提交一份合格的实验报告,也给自己的努力一个交代。