VHDL语言程序的基本结构

vhdl简答

1、简述信号与变量的区别。

a.信号延时赋值,变量立即赋值b.信号的代入使用<=,变量的代入使用:=;c.信号在实际的硬件当中有对应的连线,变量没有2、简述可编程逻辑器件的优点。

a.集成度高,可以替代多至几千块通用IC芯片.极大减小电路的面积,降低功耗,提高可靠性b.具有完善先进的开发工具.提供语言、图形等设计方法,十分灵活.通过仿真工具来验证设计的正确性c.可以反复地擦除、编程,方便设计的修改和升级d.灵活地定义管脚功能,减轻设计工作量,缩短系统开发时间f.保密性好3、试比较moore状态机与mealy状态机的异同。

Moore输出只是状态机当前状态的函数. Mealy输出为有限状态机当前值和输入值的函数3、简述VHDL语言与计算机语言的差别。

a. 运行的基础。

计算机语言是在CPU+RAM构建的平台上运行。

VHDL设计的结果是由具体的逻辑、触发器组成的数字电路b.执行方式.计算机语言基本上以串行的方式执行.VHDL在总体上是以并行方式工作c.验证方式.计算机语言主要关注于变量值的变化.VHDL要实现严格的时序逻辑关系6、VHDL与计算机语言的区别?VHDL语言可以并行执行,计算机语言只能顺序执行。

3.1比较常用硬件描述语言VHDL、Verilog和ABEL语言的优劣。

1.VHDL:描述语言层次较高,不易控制底层电路,因而对综合器的性能要求较高。

有多种EDA工具选择,已成为IEEE标准。

应用VHDL进行工程设计的优点是多方面的,具体如下:(1) 与其他的硬件描述语言相比,VHDL具有更强的行为描述能力。

(2) VHDL具有丰富的仿真语句和库函数,使得在任何大系统的设计早期,就能查验设计系统的功能可行性,随时可对系统进行仿真模拟,使设计者对整个工程的结构和功能可行性做出判断。

(3) VHDL语句的行为描述能力和程序结构,决定了它具有支持大规模设计的分解和已有设计的再利用功能。

(4) 用VHDL完成一个确定的设计,可以利用EDA工具进行逻辑综合和优化,并自动把VHDL描述设计转变成门级网表(根据不同的实现芯片)。

EDA技术实用教程(潘松第5版)第3章-VHDL设计初步

库—STD库

VHDL定义了两个标准程序包,即STANDARD和 TEXTIO(文件输入/输出)程序包,它们都收入在 STD库中,可随时调用。由于STD库符合VHDL语言 标准,在应用中不必用打开库语句。即

LIBRARY

STD;

STD.STANDARD.ALL

是不必要的。

库— WORK库

WORK库是用户的VHDL设计的现行工作库,用 于存放用户设计和定义的一些设计单元和程序包。 WORK库自动满足VHDL语言标准,在实际调用中, 也不必显示预先说明,即不必在VHDL程序中明确 打开并指定。 基于VHDL所要求的WORK库的基本概念,利用 VHDL进行设计时,不允许在根目录下进行,而是 必须为此设定一个文件夹,用于保存所有此项目 的设计文件,VHDL综合器将此文件默认为WORK库。 还要注意的是,工作库并不是这个文件夹的名字, 而是一个逻辑名。综合器将指示器指向该文件夹 的路径。

库的用法

例:

LIBRARY

USE

IEEE;

IEEE.STD_LOGIC_1164.STD_ULOGIC;

USE

IEEE. STD_LOGIC_1164.RISING _EDGE;

表示向当前设计实体开放了IEEE. STD_LOGIC_1164程序包中的RISING_EDGE函数, 但由于此函数要用到IEEE. STD_ULOGIC,所以在 其前面加了一条USE语句,开放同一程序包中的这 一数据类型。

设计实体

结构体 (Architecture) (P62)

结构体用于描述设计实体的内部结构和实

体端口间的逻辑关系,在电路上相当于器件的内

部电路结构。结构体由信号声明部分和功能描述

语句部分组成。信号声明部分用于结构体内部使

(完整版)VHDL复习

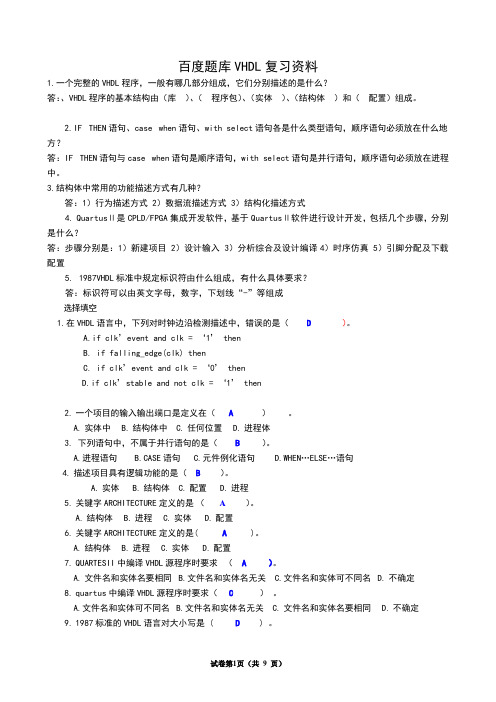

百度题库VHDL复习资料1.一个完整的VHDL程序,一般有哪几部分组成,它们分别描述的是什么?答:、VHDL程序的基本结构由(库)、(程序包)、(实体)、(结构体)和(配置)组成。

2.IF THEN语句、case when语句、with select语句各是什么类型语句,顺序语句必须放在什么地方?答:IF THEN语句与case when语句是顺序语句,with select语句是并行语句,顺序语句必须放在进程中。

3.结构体中常用的功能描述方式有几种?答:1)行为描述方式 2)数据流描述方式 3)结构化描述方式4.QuartusⅡ是CPLD/FPGA集成开发软件,基于QuartusⅡ软件进行设计开发,包括几个步骤,分别是什么?答:步骤分别是:1)新建项目 2)设计输入 3)分析综合及设计编译4)时序仿真 5)引脚分配及下载配置5.1987VHDL标准中规定标识符由什么组成,有什么具体要求?答:标识符可以由英文字母,数字,下划线“-”等组成选择填空1.在VHDL语言中,下列对时钟边沿检测描述中,错误的是( D )。

A.if clk’event and clk = ‘1’ thenB. if falling_edge(clk) thenC. if clk’event and clk = ‘0’ thenD.if clk’stable and not clk = ‘1’ then2.一个项目的输入输出端口是定义在( A )。

A.实体中B.结构体中C.任何位置D.进程体3. 下列语句中,不属于并行语句的是( B )。

A.进程语句B.CASE语句C.元件例化语句D.WHEN…ELSE…语句4.描述项目具有逻辑功能的是( B )。

A.实体B.结构体C.配置D.进程5.关键字ARCHITECTURE定义的是( A)。

A.结构体B.进程C.实体D.配置6.关键字ARCHITECTURE定义的是( A )。

A.结构体B.进程C.实体D.配置7.QUARTESII中编译VHDL源程序时要求( A )。

vhdl 程序的基本结构 vhdl程序一般由5个部分组成

块语句

块标号:BLOCK[保护表达式] [类属子句;] [端口子句;] [块说明部分;] BEGIN <块语句部分;> END BLOCK 块标号;

类属子句用于参数的定义;端口子句用于信号的定义; 块说明部分对该块要用到的信号、常数、元件和子程序 等进行说明;块语句部分对该块的功能进行描述,块语 句部分的语句是并行执行的,和书写顺序无关。

IEEE: IEEE认可的标准库 std_logic_1164:定义了 std_logic, std_logic_vector, std_ulogic, std_ulogic_vector 等数据类型

VHDL 程序的基本结构

VHDL程序一般由5个部分组成: Library(库) Package(程序包)

CONFIGURATION small_count OF counter IS FOR count_255 END FOR; END small_count; CONFIGURATION big_count OF counter IS FOR count_64K END FOR; END big_count;

Library(程序库) Package(程序包)

Entity(实体) Architecture(构造体) Configuration(配置)

库和程序包

库 :存放已编译过的实体、构造体、 程序包和配置 程序包:由一组对外可见的信号、常量、 数据类型、子程序、属性等组成 的程序集合

库和程序包的使用

子程序调用语句 过程名(参数表);

子程序调用语句若位于 “构造体” 或 “块语句” 中,它就是并发语句; 若位于 “进程语句” 或 另一个“子 程序”中,它就是顺序语句;

二VHDL语言程序的基本结构

例2-1是一个最基本的设计单元,只有实体和构造体就行 了。如前所述,它描述的是一个二选一选择器电路。利用EDA 工具可以对它进行编译、综合生成TTL的器件。

该设计单元仅由实体和构造体这两个描述部分组成。这是 有条件的:

第一,在实体和构造体中所使用的数据类型一定是在STD 库中定义的,如BIT类型。STD库已自动挂接在VHDL语言的 编译器中,因而无需在设计单元描述中进行独立的库声明。

q: OUT BIT); END mux2; ARCHITECTURE connect OF mux2 IS SIGNAL tmp: BIT; BEGIN;

PROCESS(d0,d1,sel); VARIABLE tmp1,tmp2,tmp3: BIT;

BEGIN; tmp1=d0 AND sel; tmp2=d1 AND(NOT sel); tmp3=tmp1 OR tmp2; tmp<=tmp3; q<=tmp AFTER m; END PROCESS;

库(Library)说明、包集合(Package)说明、实体(Entity)描 述、 构造体(Architecture)描述和配置(Configuration)描述。

1.最基本的设计单元构成 一个最基本的设计单元由实体和构造体两部分组成, 如例2-1所示。

【例2-1】

ENTITY mux2 IS PROT(d0,d1,sel: IN BIT;

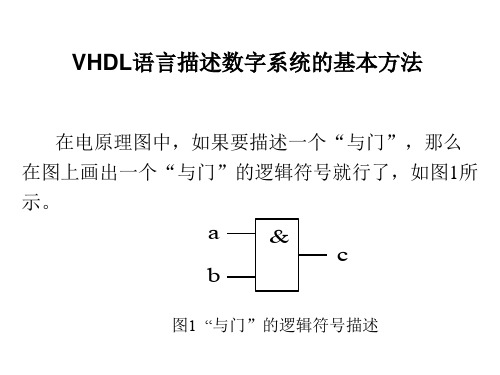

VHDL语言描述数字系统的基本方法

在电原理图中,如果要描述一个“与门”,那么 在图上画出一个“与门”的逻辑符号就行了,如图1所 示。

a& c

b

图1 “与门”的逻辑符号描述

人们看到了这个逻辑符号(如图1所示),就会联想到两件事:

1)VHDL程序有哪些基本部分组成

习题1)VHDL程序有哪些基本部分组成?2)什么进程的敏感信号?进程与赋值语句有何异同?3)什么是并行语句?什么是顺序语句?4)怎样使用库及库内的程序包?列举出三种常用的程序包。

5)BIT类型数据与STD_LOGIC类型数据有什么区别?6)信号与变量使用时有何区别?7)BUFFER与INOUT有何异同?8)为什么实体中定义的整数类型通常要加上一个范围限制?9)怎样将两个字符串hello和world组合为一个字符串?10)IF语句与CASE语句的使用效果有何不同?使用CASE语句时是否需要加语句WHEN OTHERS?为什么?11)进程语句是如何启动的?12)找出下面VHDL程序中的错误,并加以改正。

(a)ENTITY many_errors ISPORT(a:BIT_VECTOR(3 TO 0);b:OUT STD_LOGIC_VECTOR(0 TO 3);c:IN BIT_VECTOR(6 DOWNTO 0);)END many_errors;ARCHITECTURE not_so_good OF many_errors ISBEGINmy_label:PROCESSBEGINIF c = x "F" THENb< = aELSEb< = '0101';END IFEND PROCESS;END not_so_good(b)ENTITY basiccount ISPORT(clk: IN BIT;q: OUT BIT_VECTOR(7 DOWNTO 0));END basiccount;ARCHITECTURE a OF basiccount ISBEGINPROCESS(clk)IF clk'event AND clk='1' THENq<=q+1;END IF;END PROCESS;END a;13)已知逻辑表达式为f = a+bc,试用并行运算语句编写VHDL源程序,并进行时序仿真验证。

第二章 VHDL语言程序的基本结构

2.1.2 构造体

构造体是一个基本设计单元的实体,它具体地指 明了该基本设计单元的行为、元件及内部的连接关系, 也就是说它定义了设计单元具体的功能。构造体对其 基本设计单元的输入输出关系可以用3种方式进行描 述,即行为描述(基本设计单元的数学模型描述)、 寄存器传输描述(数据流描述)和结构描述(逻辑元 件连接描述)。不同的描述方式,只体现在描述语句 上,而构造体的结构是完全一样的。

ENTITY mux IS PORT(d0,d1:IN BIT; sel:IN BIT; q:OUT BIT); END mux; ARCHITECTURE dataflow OF mux IS SIGNAL s1,s2:BIT; BEGIN s1<=d0 AND sel ; s2<=(NOT sel AND d1; q<=s1 OR s2; END ARCHITECTURE dataflow;

当端口被说明为BIT_VECTOR数据类型时,该端 口的取值可能是一组二进制位的值。例如,某一数据 总线输出端口,具有8位的总线宽度。那么这样的总 线端口的数据类型可以被说明成BIT_VECTOR。总线 端口上的值由8位二进制位的值所确定。

(4) 端口说明举例1

PORT(d0,d1,sel:IN BIT; q:OUT BIT;

2.2.1 BLOCK语句的结构

采用BLOCK语句描述局部电路的书写格式如下所示:

实体说明

设计的基本单元 构造体

设计的基本单元举例

下面的程序是二选一电路的VHDL描述,我们可以把它看成是一个设计 的基本单元。

ENTITY mux IS GENERIC(m:TIME:=1ns); PORT(d0,d1,sel:IN BIT; 实体说明 q:OUT BIT); END ENTITY mux; ARCHITECTURE connect OF mux IS SIGNAL tmp:BIT; BEGIN cale:PROCESS(d0,d1,sel) IS VARIABLE tmp1,tmp2,tmp3:BIT; BEGIN 构造体 tmp1:=d0 AND sel; tmp2:=d1 AND (NOT sel); tmp3:=tmp1 OR tmp2; tmp<=tmp3; q<=tmp AFTER m; END PROCESS cale; END ARCHITECTURE connect;

第3章_VHDL语言程序的基本结构

VARIABLE tmp1,tmp2,tmp3:BIT;

BEGIN tmp1:=d0 AND sel;

构造体

tmp2:=d1 AND (NOT sel);

tmp3:=tmp1 OR tmp2;

tmp<=tmp3;

q<=tmp AFTER m;

END PROCESS cale;

END ARCHITECTURE connect;

该 例 中 BIT 类 型 用 STD_LOGIC 说 明 , 而 bus 则 用 STD_LOGIC_VECTOR(7 DOWNTO 0)说明。 在用STD_LOGIC和STD_LOGIC_VECTOR说明时,在实体说明以前 必须增加例中所示的两个语句,以便在对VHDL语言程序编译时,从 指定库的包集合中寻找数据类型的定义。

END BLOCK cale; END connect;

END ARCHITECTURE behav;

信号定义和端口说明的语句一样,应有信号名和 数据类型的说明。因它是内部连接用的信号,故没有 也不需要有方向说明。

3、 并行处理语句

并行处理语句处于语句BEGIN和END之间,这 些语句具体地描述了构造体的行为及其连接关系。例 如,二选一的数据流方式描述可以写为:

第三章 VHDL语言程序的基本结构

VHDL语言程序的五个组成部分

库说明

包集合说明

基 实体说明

本 单

元 构造体描述

配置语句

库存放已编译的实体、构造体、包集合、和配 置。相当于书库。 包集合存放各设计模块能共享的数据类型、常数和 子程序。相当于书架。

实体用于说明所设计的系统的外部接口信号。

构造体用于描述系统内部的结构和行为。

VHDL试卷6套

填空题(20分,每空格1 分)1、一个完整的VHDL语言程序通常包含实体(entity ) , 构造体(architecture ),酉己置 (configuration ),包集合(package)禾和库(library ) 5 各部分。

2、在一个实体的端口方向说明时,输入使用in表示,那么构造体内部不能再使用的输出是用out 表示;双向端口是用in out 表示;构造体内部可再次使用的输出是用buffer表示;3、一个构造体可以使用几个子结构,即相对比较独立的几个模块来构成。

VHDL语言可以有以下3种形式的子结构描述语句:BLOCK 语句结构;PROCESS语句结构和SUBPROGRAMS结构。

4、VHDL的客体,或称数据对象包括了常数、变量variable 和信号signal 。

5、请列出三个VHDL语言的数据类型,如实数、位等。

位矢量,字符,布尔量。

6、设D0 为'0', D1 为'0', D2为'1', D3为'0', D0 & D1 & D2 & D3 的运算结果是“ 0010”,D3 & D2 & D1 & D0 的运算结果是“ 0100 ”。

7、构造体的描述方式包括三种,分别是寄存器传输(RTL)描述方法或称数据流;构造体的结构描述方式和构造体的行为描述方式。

1、传统的系统硬件设计方法是采用自上而下(top down )的设计方法,利用硬件描述语言(HDL的硬件电路设计方法采用自下而上 (bottom up)的设计方法。

(X )传统的系统硬件设计方法是采用自下而上(bottom up)的设计方法,利用硬件描述语言(HDL 的硬件电路设计方法采用自上而下(top down )的设计方法2、VHDL可以采用层次化的设计,一个高层的结构体中可以调用低层的实体(V )3、一个VHAL程序中仅能使用一个进程(process )语句。

VHDL语言的结构

BEGIN

[功能描述语句]

END 结构体名;

2.1 结构体名 结构体名由设计者自行定义,OF后面的 实体名指明了该结构体所对应的是哪个实体。 有些设计实体有多个结构体,这些结构体的 结构体名不可相同,通常用dataflow(数据 流)、behavior(行为)、structural(结构)

命名。这3个名称体现了3种不同结构体的描

实体语句结构如下:

ENTITY 实体名 IS [GENERIC(类属表);] [PORT(端口表);]

END ENTITY 实体名;

例: ENTITY or2 IS

PORT(a,b:IN STD_LOGIC;

C: OUT STD_LOGIC);

END ENTITY or2;

注意:实体应以语句“ENTITY 实体名 IS”开始,语句“END ENTITY 实体名;” 结束。 在层次化系统设计中,实体说明是整个 模块或整个系统的输入输出(I/O)接口; 在一个器件级的设计中,实体说明是一个 芯片的输入输出(I/O)。

图中5种功能描述语句的基本组成和功能分别 是:

块语句是由一系列并行语句构成的组合体, 它的功能是将结构体中的并行语句组成一个 或多个子模块。

进程语句定义顺序语句模块,用以将从外部 获得的信号值或内部运算数据向其他的信号 进行赋值。

信号赋值语句将设计实体内的处理结果向定 义的信号或界面端口进行赋值。 子程序调用语句可以调用进程或参数,并将 获得的结果赋值于信号。 元件例化语句对其他的设计实体做元件调用 说明,并将此元件的端口与其他元件、信号 或高层实体的界面端口进行连接。 各语句后面将介绍

PROCESS语句的结构

[进程标号] PROCESS [(敏感信号表)] [IS] [进程说明语句] BEGIN 顺序描述语句

EDA技术及应用 (5)

第 5 章 VHDL程序结构

表 5-1 端口模式说明

端口模式

端口模式说明(以设计实体为主体)

IN

OUT

BUFFER INOUT LINKAGE

输入,只读模式,将变量或信号信息通过该端口读入,与 IN、INOUT 及 BUFFER 型端口连接

输出,单向赋值模式,将信号通过该端口输出,与 OUT、INOUT 及 BUFFER 型端 口连接

第 5 章 VHDL程序结构

3. PORT端口 端口类似于原理图部件符号上的管脚,实体通过端口与外界 通信。 实体端口格式如下:

PORT(端口名:端口模式 数据类型; 端口名:端口模式 数据类型);

第 5 章 VHDL程序结构

(1) 端口名:由设计者定义的与外部通信的引脚名称,命名 应符合VHDL命名规则。

(5) 为了使同一个VHDL源程序文件能适应各个EDA开发软件 的使用要求,建议各个源程序文件的命名均与其实体名 一致。

第 5 章 VHDL程序结构

5.1 实 体

1. 实体语句结构 实体语句结构如下: ENTITY 实体名 IS

[GENERIC(类属表);] [PORT(端口表);] END [ENTITY] 实体名;

第 5 章 VHDL程序结构 (2) STD库。VHDL语言定义了两个标准程序包,即STANDARD

和TEXTIO程序包,它们都被收入在STD库中。只要在VHDL应用环 境中,可随时调用这两个程序包中的所有内容,即在编译和综合 过程中,VHDL的每一项设计都自动地将其包含进去了。由于STD 库符合VHDL语言标准,因而在应用中不必如IEEE库那样显式表达 出来。

第 5 章 VHDL程序结构 【例5.3】 构造体功能描述举例。 ARCHITECTURE bhv OF dff2 IS Signal Q1:STD_LOGIC; BEGIN PROCESS(clk0,cl) BEGIN

VHDL填空题

VHDL填空题一、填空题(20分,每空格1分)1、一个完整的VHDL语言程序通常包含实体(entity),构造体(architecture),配置(configuration),包集合(package)和库(library)5各部分。

2、在一个实体的端口方向说明时,输入使用in表示,那么构造体内部不能再使用的输出是用out 表示;双向端口是用inout 表示;构造体内部可再次使用的输出是用buffer 表示;3、一个构造体可以使用几个子结构,即相对比较独立的几个模块来构成。

VHDL语言可以有以下3种形式的子结构描述语句:BLOCK 语句结构;PROCESS 语句结构和SUBPROGRAMS结构。

4、VHDL的客体,或称数据对象包括了常数、变量variable 和信号signal 。

5、请列出三个VHDL语言的数据类型,如实数、位等。

位矢量,字符,布尔量。

6、设D0为'0', D1为'0', D2为'1', D3为'0', D0 & D1 & D2 & D3的运算结果是“0010”,D3 & D2 & D1 & D0的运算结果是“0100”。

7、构造体的描述方式包括三种,分别是寄存器传输(RTL)描述方法或称数据流;构造体的结构描述方式和构造体的行为描述方式。

一、填空题(20分,每空格1分1、试举出两种可编程逻辑器件CPLD 、FPGA 。

2、VHDL程序的基本结构包括库、程序包、实体和结构体。

3、more_ _11标识符合法吗?不合法。

8bit标识符合法吗?不合法。

variable标识符合法吗?不合法。

4、信号的代入通常用<= ,变量用:= 。

5、表示‘0’‘1’;两值逻辑的数据类型是bit(位),表示‘0’‘1’‘Z’等九值逻辑的数据类型是std_logic(标准逻辑),表示空操作的数据类型是NULL 。

EDA

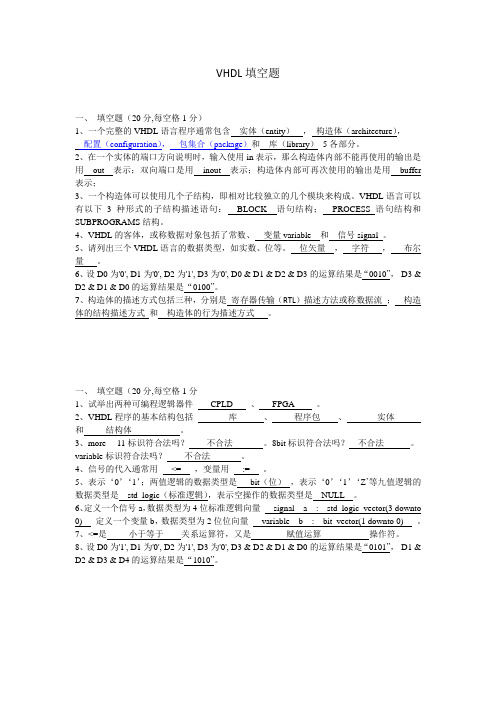

1.说明VHDL语言的基本结构。

VHDL语言程序的一般结构包括:实体(ENTITY)、构造体(ARCHITECTURE)、配置(CONFIGURATION)、包集合(PACKAGE)、库(LIBRARY)。

2.说明端口模式的INOUT与BUFFER的异同。

INOUT为输入输出双向端口,即从端口内部看,可以对端口进行赋值,即输出数据。

也可以从此端口读入数据,即输入。

BUFFER为缓冲端口,功能与INOUT类似,区别在于当需要读入数据时,只允许内部回读内部产生的输出信号,即反馈。

举个例子,设计一个计数器的时候可以将输出的计数信号定义为BUFFER,这样回读输出信号可以做下一计数值的初始值。

3.VHDL语言有几种数据对象,请说明他们的功能以及使用方法,举例说明数据对象与数据类型之间的关系。

1.常量(CONSTANT):常量为全局量,是指在设计描述过程中保持某一规定类型特定值不变的量。

常量名:数据类型:=表达式;2.变量(VARIABLE):变量为局部量,常用来存储中间数据,以便实现程序的算法。

它只能在进程语句、函数语句和过程语句的结构中使用。

变量名1[ , 变量名2, …]: 数据类型[ := 初始值] ;3.信号(SIGNAL):信号是描述硬件系统的基本数据对象,它是电子电路内部硬件连接的抽象,可以作为设计实体中并行语句模块间的信息交流通道。

信号名:数据类型[:=初值];4.试用结构描述方式来描述图4-18(P137)所示的硬件电路。

Library IEEE;USE IEEE SID_LOGIC_1164.ALLENTITY fadder 3 ISPORT,(a,b,c:IN SID_LOGICY:OUT SID_LOGIC);END fadder 3;ARCHLIECTURE SUM OF fadder3 isSIGNAL to ,t1:SID_LOGICBEGINTo <=(NOT a,ANI) c T1<=(NOT a, ANI) b T2<=(NOT to ANI) t1 END SUM;1.用VHDL语言设计一个8位二进制全加器。

第四章 VHDL语言程序基本结构

1. 对于VHDL的编译器和综合器来说,程序文字的大小 写不加区分。 2. 为了使程序结构清晰,易于阅读和调试,书写和输入 程序时,使用层次缩进格式,同一层次的语句对齐, 底层次的语句较高层次的语句缩进两个字符。 3. 程序中的注释使用双横线“--”。在VHDL程序的任 何一行中,双横线“--”后的文字都不参加编译和综 合。

4.1 设计实体

设计实体总由实体说明和结构体两部分构成

【例4-1】

EDA技术讲义

ENTITY mux21a IS PORT( a, b : IN BIT ; s : IN BIT; y : OUT BIT ) ; END ENTITY mux21a ;

实体说明

ARCHITECTURE one OF mux21a IS BEGIN y <= a WHEN s = '0' ELSE b ; END ARCHITECTURE one ;

复杂组合逻辑电路,如:

• 译码器、编码器、加减法器、多路选择器、地址译码器…...

状态机 等等……..

EDA技术讲义

VHDL的功能和标准

VHDL 描述

输入端口 输出端口 电路的行为和功能

VHDL有过两个标准:

IEEE Std 1076-1987 (called VHDL 1987) IEEE Std 1076-1993 (called VHDL 1993)

2选1多路选择器的VHDL描述

图4-1 mux21a实体

结构体

图4-2 mux21a结构体

4.1 设计实体

4.1.1 实体说明

EDA技术讲义

实体说明主要描述的是一个设计的外貌,即对外 的输入输出接口以及一些用于结构体的参数的定义。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

5

二选一电路的VHDL语言描述

entity mux is

architecture connect of mux is

实 generic(m: time :=1 ns); signal tmp: bit;

体 说

port(d0,d1,sel: in bit;

明

q: out bit);

begin cale:process(d0,d1,sel) is

q: out bit); end entity mux;

8

VHDL语言不区分大小写; 除了第一行 entity … is 以外,每一句以分号

“;”结束 ; 编写程序时,一行可以含若干句(以分号间隔),

一句也可以写若干行; 在一句结束后,可以在“--”符号后接说明文字,

有助于理解程序,不会对编译产生影响; 单词之间必须使用空格; 并列信号间使用逗号; 根据不同的层次关系最好设定不同的缩进。

3

2.1 VHDL语言设计的基本单元及其构成

VHDL语言程序是用于描述硬件连接的结构性程 序,采用文本文件编写。

硬件电路模块具有外部接口和内部结构。

VHDL用程序模块表达硬件模块:设定外部端口、 设计内部结构。

4

input1 inputn

Entity

Symbol

output1 outputn

end entity mux;

variable tmp1,tmp2,tmp3: bit;

begin

构 造

tmp1:=d0 and sel;

体

tmp2 :=d1 and (not sel);

定 义

tmp3 :=tmp1 or tmp2;

tmp<=tmp3;

q<=tmp after m;

end process;

声明在实体中将用到的常数定义、数 据类型、函数定义和过程定义等。

3.实体(Entity)

定义所设计电路系统的外部接口。

描述电路内部的功能。一个实体可以

4.构造体(Architecture) 对应很多个构造体,但在同一时间,

只有一个构造体被使用。

5.配置(Configuration) 决定哪一个构造体被使用。

a b c

d

sel

2

Architecture

Schematic

mux_out

D

Q

Байду номын сангаас

clk

ENA CLRN

clr

V实H体D说L明语部分言:程规 序 单 明 定输脚外观设出 ;设元图计接 它计由。单口 对的实元信 应(E的号 于基体n输或 电ti本说t入引 路y Declaration) 和 构 构造造体定体义定部分义: (定A义rc设hi计tec单tu元re的具 D体e构fin造iti和on操) 两作 (部行 分 为路原)构;理成它图。对。应 于 电

15

例2-1

entity mu is

port(d0,d1,sel : in bit;

实

q : out bit;

体 说

bus : out bit_vector(7 downto 0)); end mu;

明

例2-2

示

library ieee;

例

use ieee.std_logic_1164.all;

entity mu is

10

3)端口说明格式:

端口说明是对基本设计实体(单元)与外部接 口的描述,也可以说是对外部引脚信号的名称, 数据类型和输入、输出方向的描述。

port (端口名[,端口名]:方向 数据类型名;

…… 端口名[,端口名]:方向 数据类型名);

注:port为关键字

11

端口说明语法要点

(1) 端口名是赋予每个外部引脚的名称;

端口方向

含义

输入端口(in)

仅允许信号从端口输 入到构造体

输出端口(out)

仅允许信号从构造体 内经端口输出

缓冲端口(buffer)

用于输出及构造体内 部反馈

双向端口(inout)

可作为in\out\buffer使 用

示意图

13

14

(3) 端口数据类型

所有端口都必须规定其数据类型,VHDL语言中 有10种数据类型,在数字电路设计中最常用的类 型为:bit 和 bit_vector 。

port(d0,d1,sel : in std_logic;

q : out std_logic;

bus : out std_logic _vector(7 downto 0));

Bit:单个逻辑量 Bit_vector:逻辑数组、总线逻辑量 在VHDL语言的标准库IEEE库当中的包集合

std_logic_1164提供的std_logic和std_logic_vector 分别与bit和bit_vector对应,完全等效。只是在使 用时要声明使用了该包集合。下面给出一个例子。

end architecture connect;

7

1. 实体说明

1) 实体说明的基本格式:

entity 实体名 is [类属参数说明];--确定局部常量或实体时限 [端口说明]; --确定输入/输出端口数量及类型 end entity 实体名;

entity mux is generic (m: time :=1 ns); port (d0,d1,sel: in bit;

第二章 VHDL语言 程序的基本结构

1

本章内容:

VHDL语言设计的基本单元及其构成 VHDL语言构造体的子结构描述

块语句 进程语句 子程序语句

包集合、库及配置

2

完整VHDL语言程序结构

1.库(Library)

存放已经编译的包集合、实体、构造 体和配置。

2.包(Package)

9

2)类属参数说明格式:

generic([类属常量名:类型 [:=静态表达式]; ……

[类属常量名:类型 [:=静态表达式]);

要点: (1) 类属说明必须在端口说明之前,为设计实体和外

部环境提供静态数据传输通道; (2) generic 为关键字,静态表达式为可选项; (3) 示例:

generic(m: time :=1 ns); q<=tmp after m;

命名规则: 英文字母和数字构成,字母开头; 可在名称中使用单个下划线符号_; 字母不分大小写; 名称应具有意义,方便记忆; 名称不能重复使用; VHDL中的关键字保留字不能用做名称。

注:该命名规则适用于实体、端口、信号、变量、文件的命名

12

(2) 端口方向:定义外部引脚的信号方向是输入还是 输出 。