多芯片封装MCP学习资料

芯片封装技术培训课件

芯片封装技术培训课件芯片封装技术培训课件芯片封装技术是现代电子行业中不可或缺的一环。

它起到了保护芯片、传导热量、提高电气连接性和机械强度等重要作用。

本文将介绍芯片封装技术的基本原理、封装材料的选择以及未来发展趋势。

一、芯片封装技术的基本原理芯片封装技术是将芯片封装在外壳中,以保护芯片免受外界环境的影响。

它通过将芯片与外界连接,实现芯片与外界设备的通信和互动。

封装过程中,需要将芯片与封装材料进行粘合,并通过焊接等手段实现电气连接。

芯片封装技术的基本原理可以分为以下几个步骤:首先,将芯片放置在封装基板上,并使用导电胶水将芯片固定在基板上。

接下来,通过焊接技术将芯片的引脚与基板上的连接线连接起来,形成电气连接。

最后,使用封装材料将芯片封装在外壳中,以保护芯片免受外界环境的影响。

二、封装材料的选择封装材料的选择对芯片封装技术起着至关重要的作用。

合适的封装材料可以提供良好的机械强度、导热性能和电气连接性,从而保护芯片的正常运行。

在选择封装材料时,需要考虑以下几个因素:首先,材料的导热性能。

芯片在工作过程中会产生大量的热量,如果导热性能不好,会导致芯片温度过高,影响芯片的正常工作。

其次,材料的机械强度。

封装材料需要具备足够的机械强度,以保护芯片不受外力损伤。

最后,材料的电气连接性。

封装材料需要具备良好的导电性能,以实现芯片与外界设备的电气连接。

常见的封装材料包括有机封装材料、无机封装材料和复合封装材料等。

有机封装材料通常具有良好的导热性能和电气连接性,但机械强度较差;无机封装材料具有较好的机械强度和导热性能,但电气连接性较差;复合封装材料则综合了有机和无机封装材料的优点,具有较好的综合性能。

三、芯片封装技术的未来发展趋势随着电子行业的快速发展,芯片封装技术也在不断进步和创新。

未来,芯片封装技术将朝着以下几个方向发展:首先,封装材料的研发将更加注重环保和可持续性。

随着环境保护意识的增强,封装材料的研发将更加注重减少对环境的影响,并提高材料的可持续性。

三星MCP手机内存芯片全攻略

文章的开头首先介绍一下什么是MCP,MCP=Multi-Chip Package 中文意思是多制层封装芯片,其主要应用领域为手机等手持智能终端设备。

其优点在于体积小,能适应各种手持设备节省空间的原则。

成本方面较独立的芯片组和要有优势。

三星从2004年开始致力于手机内存芯片的推广,2005年在全球取得了不到10%市场份额,当时这方面的前两位分别是INTEL和SPANSION这两个厂商。

2006年是三星MCP内存芯片市场份额大幅提高的一年,在2006年下半年由于SPANSION的128+32和64+16/64+31NOR+SRAM的MCP大面积缺货给了三星一次很好的机会,三星在8月开始逐步进入手机MCP领域,其推出的128+32MCP芯片只要在软件方面作一些简单的调整就可以PIN TO PIN取代SPANSION的129系列产品,并且价格比当时的SPANSION 128+32的同类产品要低0.5USD,这使得中国大陆这一B类手机制造基地的设计公司和厂家纷纷切入到三星的MCP中来。

在2007年年初,三星又推出了其最新128+32的产品2931和2731,这两款产品的推出,将冲击SPANSION很大的市场份额。

下面针对三星的MCP产品做个简单的介绍,介绍从MCP制成和具体型号以及配合手机的主方案进行:MCP大致有三类:一;替换目前市场主流的SPANSION的NOR+SRAM(PSRAM)系列32+8型号为K5A3281CT(B)M--此款MCP主要可以应用于一些低端手机,包括英飞凌等低端方案,都可采用此款MCP。

64+16型号为K5J6316CT(B)M:三星已经在2007年将此款IC 停产,转移产能大量生产64+32制成的MCP64+32型号为K5J6332T(B)M:这使三星2007年主要推广的MCP之一,目前已经有很多方案认可,包括MTK 6226/6219以及展讯的6600D等方案都广泛采用此款芯片。

第6章 多芯片组件(MCM)(精简版)

6.2 MCM的概念、分类与特性

至今对MCM尚无统一的定义,综合国外专家对MCM所下的定 义,MCM原则上应具备以下条件: (1)多层基板有4层以上的导体布线层。 (2)封装效率(芯片面积/基板面积)大于20%。

(3)封装壳体通常应有100个以上的I/O引脚。

其他附加条件:布线宽度每英寸从250根到500根,有多个 LSI和(或)VLSI裸芯片等。 从组装(或封装)对MCM定义为:两个或更多的集成电路裸芯 片电连接于共用电路基板上,并利用它实现芯片间互连的组件。

6.8.3 封装中的几个问题 1. 粘接剂

采用AT&T公司研制的绝缘性芯片粘接剂,配方和性能是特有的。

2. 焊球

每个BGA I/O焊区都有焊球,用这些焊球将MCM BGA组件与母 板连接起来,AT&T公司已就焊球材料及制作工艺申请了专利。 在包封并采用特定的超厚膜板印制特有的AT&T YD系列BGA焊 膏后,通过倒置BGA基板来连接焊球。 AT&T公司焊料合金有两种: 单面板:采用43%Sn-43%Pb-14%Bi配方。 双面板: 95%Sn-5%Pb配方。

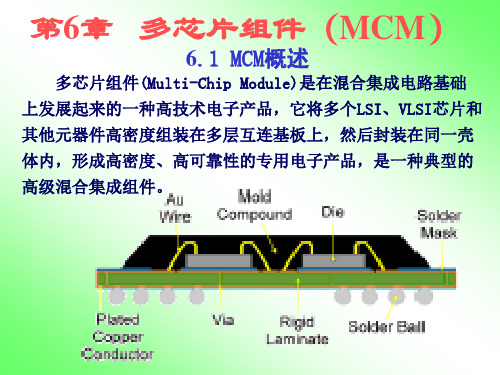

mcm61mcm概述多芯片组件multichipmodule是在混合集成电路基础上发展起来的一种高技术电子产品它将多个lsivlsi芯片和其他元器件高密度组装在多层互连基板上然后封装在同一壳体内形成高密度高可靠性的专用电子产品是一种典型的高级混合集成组件

第6章 多芯片组件(MCM)

6.1 MCM概述

用了面积为152mm2、运算能力为1.25亿次/秒的MCM作为处理组

件,使整个处理系统的尺寸由原来的机框变成了一块插件,系

统运算能力达到5亿次/秒,经扩展可达80亿次/秒。

MCM可分为五大类: MCM—L(with Laminated Substrate):有机叠层布线基

多芯片封装(MCM)方案(二)

多芯片封装(MCM)方案随着科技的飞速发展,电子产品对高性能、小型化和低成本的需求日益增长。

为了满足这些需求,多芯片封装(MCM)技术应运而生。

本文将详细介绍MCM方案在产业结构改革中的重要性、工作原理、实施步骤、适用范围、创新点、预期效果、收益以及优缺点,并针对下一步改进提出建议。

一、实施背景随着物联网、人工智能和5G等技术的快速发展,电子产品的复杂性和集成度不断提高。

传统的单芯片封装已经无法满足这些需求,因此需要采用多芯片封装技术,将多个芯片集成到一个封装内,以提高性能、减小体积并降低成本。

二、工作原理MCM技术是一种将多个集成电路芯片同时封装在一个封装内的制造过程。

它通过将多个芯片连接到一个共享的基板上,实现芯片之间的互连和通信。

这种技术可以显著提高电子设备的性能和可靠性,同时降低成本和体积。

三、实施计划步骤1.确定封装需求:根据产品需求确定需要封装的芯片数量、类型和封装尺寸。

2.选择合适的基板:根据封装需求选择合适的基板材料和大小,确保基板具有优良的电气性能和热稳定性。

3.芯片贴装:将多个芯片贴装到基板上,确保芯片之间的间距和连接正确。

4.芯片互联:通过金属线或其他互联技术将芯片连接到底层基板上,实现芯片之间的互连和通信。

5.封装保护:对封装体进行保护,防止外界环境对芯片产生不良影响。

6.测试与验证:对封装好的芯片进行测试和验证,确保其性能符合要求。

四、适用范围MCM技术适用于各种需要高性能、小型化和低成本的电子产品,如手机、笔记本电脑、平板电脑、服务器、交换机等。

五、创新要点MCM技术的创新点在于它将多个芯片集成到一个封装内,从而实现高性能、小型化和低成本的目标。

此外,MCM 技术还可以采用先进的互联技术,如无线互联和光互联,进一步提高芯片之间的通信速度和可靠性。

六、预期效果与收益采用MCM技术可以带来以下预期效果和收益:1.提高性能:通过将多个芯片集成到一个封装内,可以显著提高电子设备的性能和可靠性。

多芯片封装(MCM)方案(一)

多芯片封装(MCM)方案一、实施背景随着科技的飞速发展,电子产品对高性能、小型化和低成本的需求日益增强。

其中,多芯片封装(MCM)技术成为满足这些需求的关键。

MCM方案通过将多个芯片集成到一个封装内,提高了芯片间的通信效率,降低了功耗,并减少了产品体积。

这种技术对于推动产业结构改革,尤其是在高集成度、高性能和低功耗的领域,具有重大意义。

二、工作原理MCM技术利用先进的封装工艺,将多个芯片(如处理器、存储器和模拟芯片等)集成到一个封装内。

通过缩短芯片间的距离,提高互连密度,降低信号传输延迟,从而提高整个系统的性能。

此外,MCM技术还通过优化散热设计,降低芯片工作温度,提高系统的稳定性。

三、实施计划步骤1.需求分析:首先明确产品的需求,包括性能、尺寸、功耗等。

这将有助于确定所需芯片类型及数量。

2.芯片选择:根据需求分析,选择适合的芯片。

这需要考虑芯片的性能、功耗、成本等因素。

3.封装设计:设计适合多芯片封装的架构,包括芯片的布局、互连设计、散热设计等。

4.制造与测试:利用所选的芯片和设计,进行MCM的制造和测试。

这包括前道制造和后道测试等环节。

5.验证与优化:对制造和测试的结果进行验证,根据结果进行优化,以提高产品的性能和稳定性。

四、适用范围MCM技术适用于多种领域,如移动设备、云计算、人工智能、物联网等。

在移动设备中,MCM可以提高设备的性能并降低功耗;在云计算中,MCM可以实现高速数据传输和低延迟处理;在人工智能和物联网中,MCM可以提高设备的计算能力和通信效率。

五、创新要点MCM技术的创新点在于其高集成度、高性能和低功耗的特点。

通过将多个芯片集成到一个封装内,不仅提高了芯片间的通信效率,还降低了功耗和产品体积。

此外,MCM技术还通过优化散热设计,提高了系统的稳定性。

六、预期效果与收益预期通过实施MCM方案,可以带来以下效果和收益:1.提高性能:MCM技术将多个芯片集成到一个封装内,提高了芯片间的通信效率,从而提高了整个系统的性能。

mcp芯片

mcp芯片MCP(Multi-Chip Package),中文名称为多芯片封装,是一种集成了多个芯片的封装技术。

它将多个芯片封装在一个包内,通过高密度的互连线路将芯片之间进行连接。

MCP芯片常用于需要高度集成和较小尺寸的应用场景,如移动设备、嵌入式系统等。

MCP芯片的核心技术是通过三维堆叠封装技术将多个芯片层叠在一起,并通过互连线路实现芯片之间的通信。

这种技术能够大大提高芯片的集成度,减少设备的尺寸,并提高系统的性能。

MCP芯片通常由主控芯片、存储芯片、射频芯片等多个功能模块组成。

封装方式可以是球栅阵列封装(BGA)或者无焊盖封装(FCBGA),常见的MCP芯片封装尺寸从几毫米到几厘米不等。

MCP芯片的优势主要体现在以下几个方面:1. 高集成度:MCP芯片可以将多个芯片集成在一个包内,实现多个功能模块的集成。

这样不仅可以减小设备的尺寸,提高设备的性能,还能降低系统成本。

2. 低功耗:MCP芯片通过在一个封装内集成多个功能模块,可以有效减少功耗。

各个芯片之间通过短距离的互连线路进行通信,能够降低传输功耗,提高系统的能效。

3. 高性能:MCP芯片集成了多个芯片,能够实现不同功能模块之间的高速通信和协同工作。

通过集成多个功能模块,可以提高系统的整体性能,满足高性能应用的需求。

4. 灵活性:MCP芯片可以根据应用的需求进行定制设计。

不同功能模块可以选择不同的芯片,灵活组合,实现定制化的功能需求。

5. 可靠性:MCP芯片通过三维堆叠封装技术,能够实现芯片之间的密集互连,减少因互连线路导致的问题。

同时,MCP芯片还可以通过多重备份机制提高系统的可靠性,降低故障率。

MCP芯片在移动设备、嵌入式系统等领域有着广泛的应用。

在手机中,MCP芯片可以集成处理器、内存、无线模块等多个芯片,实现高性能和低功耗的手机设计。

在汽车电子系统中,MCP芯片可以集成多个功能模块,如车载娱乐系统、导航系统等,提供丰富的车载应用。

总之,MCP芯片作为一种高度集成的封装技术,在提高设备性能、减小尺寸、降低功耗等方面有着独特的优势。

多层集成电路(MCP)产品参考手册说明书

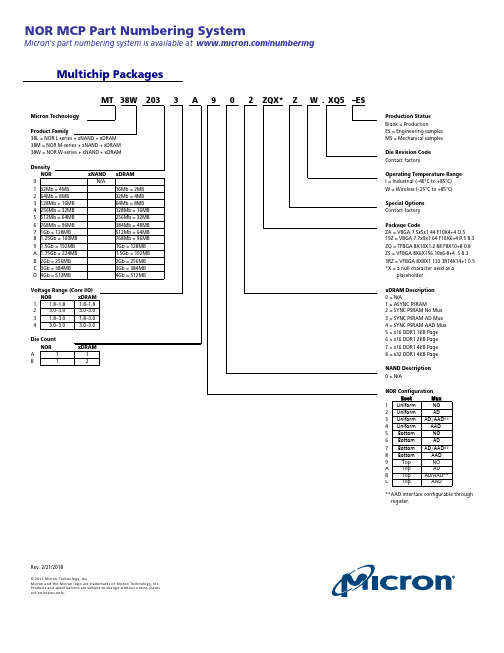

NOR MCP Part Numbering SystemMicron's part numbering system is available at /numbering Multichip PackagesProduction StatusBlank = ProductionES = Engineering samplesMS = Mechanical samplesDie Revision CodeContact factoryOperating Temperature Range0I = Industrial (–40°C to +85°C)1W = Wireless (–25°C to +85°C)23Special Options4Contact factory56Package Code7ZA = VBGA 7.5x5x1 44 F10X4+4 O.5 819Z = VBGA 7.7x9x1 64 F10X6+4 P.5 B.3 9ZQ = TFBGA 8X10X1.2 88 F8X10+8 0.8 A ZS = VFBGA 8X6X156 10x6-8+4 .5 B.3B3RZ = VFBGA 8X8X1 133 3R14X14+1 0.5 C*X = a null character used as aD placeholder.xDRAM Description0 = N/A1 1 = ASYNC PSRAM2 2 = SYNC PSRAM No Mux3 3 = SYNC PSRAM AD Mux4 4 = SYNC PSRAM AAD Mux5 = x16 DDR1 1KB Page6 = x16 DDR1 2KB Page7 = x16 DDR1 4KB PageA8 = x32 DDR1 4KB PageBNAND Description0 = N/ANOR ConfigurationBoot Mux1Uniform NO2Uniform AD3Uniform AD/AAD**4Uniform AAD5Bottom NO6Bottom AD7Bottom AD/AAD**8Bottom AAD9Top NOA Top ADB Top AD/AAD**C Top AAD**AAD interface configurable throughregister.Rev. 2/21/2018© 2012 Micron Technolog y, Inc.Micron and the Micron log o are trademarks of Micron Technolog y, Inc.Products and specifications are subject to chang e without notice. Datesare estimates only.NAND MCP Part Numbering SystemMicron's part numbering system is available at /numberingMultichip PackagesDie RevisionProduction Status Blank = ProductionES = Engineering samples MS = Mechanical samplesSpecial Options Blank = StandardE = On-die ECC enabledOperating Temperature RangeAIT = Automotive industrial (–40°C to +85°C)AAT = Automotive (–40°C to +105°C)IT = Industrial (–40°C to +85°C)WT = Wireless (–30°C to +85°C)LPDRAM Access Time-107 = 933 MHz CL13 (LPDDR 1866)-18 = 533 MHz CL8 (LPDDR 1066)-25 = 400 MHz CL6 (LPDDR 800)-53 = 1866 MHz -62 = 1600 MHzPackage CodeGA = 149-ball: 8.0mm x 9.5mm x 0.8mm GM = 240-ball: 14mm x 14mm x 0.85mm MF = 168-ball: 12mm x 12mm x .85PB = 221-ball: 11.5mm x 13mm x 0.8mm PL = 162-ball: 11.5mm x 13mm x .80mm SK = 162-ball: 11.5mm x 13mm x .9mm TB = 162-ball: 8mm x 10.5mm x 0.9mm H = 1 NAND Flash; 2 LPDRAM TN = 121-ball: 7.5mm x 8mm x 0.8mm I = 2 NAND Flash; 2 LPDRAM WD= 162-ball: 8.0mm x 10.5mm x 0.9mmM = 2 NAND Flash; 1 LPDRAM*Z = a null character used as a placeholder.Rev. 2/21/2018© 2017 Micron Technolog y, Inc.Micron and the Micron log o are trademarks of Micron Technolog y, Inc.Products and specifications are subject to chang e without notice. Dates are estimates only. CCMMD-1707390403-10399MCP/PoP Part Numbering SystemMicron's part numbering system is available at /numberingMultichip PackagesProduction Status Blank = ProductionES = Engineering samples MS = Mechanical samples Operating Temperature Range IT = Industrial (–40°C to +85°C)WT = Wireless (–25°C to +85°C)Special Options Blank = StandardE = On-die ECC enabled LPDRAM Access Time -5 = 200 MHz CL3-54 = 185 MHz CL3-6 = 166 MHz CL3-75 = 135 MHz CL3-8 = 125 MHz CL3-10 = 100 MHz -48 = 208 MHz Package CodeJA =137-ball TFBGA, 10.5 x 13 x 1.2, MCP JC =107-ball TFBGA, 10.5 x 13 x 1.2, MCP A JG =168-ball VFBGA, 12 x 12 x 0.90, PoP B JI =168-ball TFBGA, 12 x 12 x 1.1, PoP C JR =137-ball LFBGA, 10.5 x 13 x 1.4, MCP D JS =137-ball TFBGA, 10.5 x 13 x 1.2 , MCP E JV =168-ball VFBGA, 12 x 12 x 1.0, PoP F KC =107-ball TFBGA, 10.5 x 13 x 1.1, MCP G KD =137-ball TFBGA, 10.5 x 13 x 1.1, MCP H KN =184-ball VFBGA, 14 x 14 x 1.0, PoP J KQ =168-ball WFBGA, 12 x 12 x 0.75, PoP K KS =137-ball VFBGA, 10.5 x 13 x 1.0, MCP L MA =168-ball WFBGA, 12 x 12 x 0.70, PoP M MC =240-ball WFBGA, 14 x 14 x 0.80, PoP N MD =130-ball VFBGA, 8 x 9 x 1.0, MCP P ME =240-ball TFBGA, 14 x 14 x 1.12, PoP R MF =168-ball VFBGA, 12 x 12 x 0.85, PoP T MJ =240-ball VFBGA, 14 x 14 x 0.85, PoP U MK =153-ball VFBGA, 10 x 12 x 0.90, MCP V ML =153-ball VFBGA, 8 x 9 x 0.90, MCP Y MS =191-ball WFBGA, 12 x 12 x 0.80, PoP Z NE =133-ball VFBGA, 11 x 10 x 1.0, MCP AA RN =160-ball FBGA, 11.5 x 11.5 x 0.94, MCP AB TE =153-ball VFBGA, 10 x 12 x 1.0, MCPAC AD Chip CountAE AF A AG B AH C AI D AJ E AL F KH G H AKRev. 2/21/2018© 2016 Micron Technolog y, Inc.Micron and the Micron log o are trademarks of Micron Technolog y, Inc. Products and specifications are subject to chang e w ithout notice. Dates are estimates only.All-in-One Part Numbering SystemMicron's part numbering system is available at /numberingAiO PackagesMT29JZ*ZZ*2D WM A F JV-6I ES.63mDie Revision CodeContact factoryProduct FamilyProduction StatusBlank = ProductionES = Engineering samplesMS = Mechanical samplesSpecial OptionsBlank = StandardA = Customer variantB = 2MB boot area/2MB RPMBE = On-die ECC enabledF = SEC COUNT/custom boot area/custom RPBMOperating Temperature RangeA = Automotive (–40°C to +105°C)T AI = Industrial (–40°C to +85°C)U B W = Wireless (–25°C to +85°C)V CW D LPDRAM Speed GradeX E-046 = 2133 MHz (LPDDR 4266)Y F-062 = 1600 MHz (LPDDR 3200)1-107 = 933 MHz CL13 (LPDDR 1866)2-125 = 800 MHz CL12 (LPDDR 1600)3-18 = 533 MHz CL8 (LPDDR 1066)4-25 = 400 MHz CL6 (LPDDR 800)6-3 = 333 MHz CL5 (LPDDR 667)7-37 = 266 MHz CL4 (LPDDR 533)8-5 = 200 MHz CL3 (LPDDR 400)9-53 = 1866 MHz (LPDDR 3732)A-54 = 185 MHz CL3 (LPDDR 1)B-6 = 166 MHz CL3 (LPDDR 333)C-75 = 133 MHz CL3 (LPDDR 266)Package CodeV Chip CountWX12456789ABABCD*Z = a null character used as a placeholder.EFGHJKLMNPQRRev. 2/21/2018Density© 2017 Micron Technolog y, Inc.Micron and the Micron log o are trademarks of Micron Technolog y,Inc. Products and specifications are subject to chang e without notice.Dates are estimates only. CCMMD-1707390403-10399。

多芯片封装MCP

多芯片封装MCP多芯片封装(Multi-Chip Package,MCP)是将两个或多个芯片封装在同一个封装内,形成一种更小、更集成化的封装方式。

在今天的电子产品中,MCP已经成为一种更加常见的封装方式。

本文将讨论MCP的特点、优势和应用。

MCP的特点和优势1.小尺寸高密度MCP封装方式将多个芯片封装在一个封装内,有效地降低了芯片的空间占用,使得整个芯片的体积更小、更紧凑。

同时,高度集成化的设计,使得MCP芯片可以用于一些空间较小的电子设备中。

2.高可靠性和稳定性MCP的封装方式还可以有效的降低芯片的热量而且降低芯片的使用温度,从而有效的提高芯片的可靠性和稳定性。

对于那些需要长时间运行的电子设备,使用MCP芯片可以有效的提高设备的使用寿命和稳定性,减少设备的维修和更换次数。

3.节省成本使用MCP封装可以节省封装占用的PCB面积,同时降低芯片的制造成本。

MCP芯片的生产线比单独生产多个芯片的生产线要简单和便捷,这使得MCP芯片的成本低廉,特别是对于大批量生产或定制化生产的芯片而言。

4.多功能集成MCP芯片的封装方式通过将各个芯片的功能集成在同一个封装内,使电子设备的制造更加简单和方便,节省了设计时间和成本。

MCP在不同领域的应用MCP芯片的应用涉及多个领域,如计算机、通信、医疗设备、军工等,以下是部分领域的应用案例。

1.计算机MCP芯片可用于计算机的主板、内存,存储、网络、声音等各个不同的部件上,实现对计算机系统的完整集成和逻辑控制。

同时,这些芯片也可以用于笔记本电脑、平板和便携式设备中,使设备更加小巧和轻便。

2.通信MCP芯片在通信领域的应用非常多,如手机、电视、游戏机、照相机等设备都可以使用MCP芯片。

MCP芯片可以集成各种通信模块,如WiFi、蓝牙、移动通信等,可以减少设备占用空间和加快设备通信速度,提供更加完整的通信功能。

3.医疗设备MCP芯片也被广泛应用于医疗设备领域,如血压计、心率监测器等设备中。

一文详解多芯片组件MCM技术

多芯片组件MCM(Mul TI-Chip Module)1 多芯片组件组成多芯片组件技术是为适应现代电子系统短,小,轻,薄和高速、高性能、高可靠性、低成本的发展方向二在PCB和SMT的基础上发展起来的新一代微电子封装与组装技术,是实现系统集成的有力手段。

多芯片组件是在高密度多层互连基板上,采用微焊接、封装工艺将构成电子电路的各种微型元器件(IC裸芯片及片式元器件)组装起来,形成高密度、高性能、高可靠性的微电子产品(包括组件、部件、子系统、系统)。

它是为适应现代电子系统短、小、轻、薄和高速、高性能、高可靠性、低成本的发展方向而在多层印制板(PCB)和表面安装技术(SMT)的基础上发展起来的新一代微电子封装与组装技术,是实现系统集成的有力手段。

随着技术的进展,关于多芯片组件的定义有了更多的理解:首先,MCM 的主要构成应当是集成度更高的 VLSI/ULSI/ASIC裸芯片,而非较低集成度的中小规模电路;其次,MCM 应以更高的速度、性能、可靠性以及更多的功能为目标,而非一般混合集成的降低重量和体积;最后,典型的 MCM 须满足上述的关于芯片面积、基板层数和引脚数目的要求。

图1.1是 MCM组件的一种基本结构示意图。

图 1.1 MCM组件结构从图上也可以看到MCM组件包括了芯片、基板、管壳或者高密度I/O 管脚。

从MCM的外表看,就是一个带由较多引出脚的壳体。

可以称之为模表1.1 MCM组件的组成2 多芯片组件分类MCM因使用的材料与工艺技术的不同,可以有不同的分类方式,其分类方法也因认识角度的不同而异。

根据多层互连基板的结构和工艺技术的不同,MCM大体上可分为三类:①层压介质MCM(MCM-L: La mi na te);②陶瓷或玻璃瓷MCM(MCM-C: Ce ram ics);③硅或介质材料上的淀积布线MCM(MCM-D: Deposi TI on)。

2.1 MCM-L(Mul TI-Chip Module-Laminate)图2.1 MCM-L Module封装实物与截面示意图MCM-L称之为L型(即叠层型)多芯片组件。

集成电路芯片封装技术培训课程(2024)

2024/1/28

生物医学应用中的特殊封装实例

如植入式医疗设备、生物传感器、神经刺激器等。

26

06

封装设备选型及使用注意事项

2024/1/28

27

关键设备介绍及选型建议

封装设备分类

根据封装工艺和芯片类型,封装设备可分为手动、半自动和全自动 三类。

关键设备介绍

包括贴片机、焊线机、塑封机、切筋打弯机等,分别用于芯片贴装 、焊接、塑封和引脚成型等工序。

金

高导电性、抗氧化、耐腐 蚀,用于高端封装中的引 线和触点。

8

绝缘材料

陶瓷

高热稳定性、良好的绝缘 性和机械强度,用于高端 封装和特殊环境。

2024/1/28

塑料

低成本、易加工、良好的 绝缘性,广泛用于中低端 封装。

玻璃

较高的热稳定性和绝缘性 ,用于某些特定封装中。

9

密封材料

环氧树脂

低成本、良好的密封性和绝缘性,广 泛用于中低端封装。

主要以金属罐封装为主,体积大 、重量重、成本高。

2024/1/28

中期封装技术

逐渐出现塑料封装和陶瓷封装,体 积减小、重量减轻、成本降低。

现代封装技术

不断追求小型化、轻量化、高性能 化和低成本化,出现了多种先进封 装技术,如BGA、CSP、3D封装等 。

5

常见封装类型及其特点

DIP封装

双列直插式封装,引脚从两侧引出,插装方便 ,但封装密度较低。

选型建议

根据生产需求、预算和工艺要求,选择适合的设备型号和配置,注意 设备的精度、稳定性、生产效率和易维护性。

2024/1/28

28

设备操作规范与维护保养要求

2024/1/28

操作规范

mcp存储器分类及其工作原理

mcp存储器分类及其工作原理MCP存储器分类及其工作原理MCP存储器是一种集成了多个存储单元的存储器,其中MCP代表Multi-Chip Package,意味着多芯片封装。

MCP存储器常用于手机、平板电脑等小型电子设备中,因为它具有体积小、功耗低等优点。

本文将介绍MCP存储器的分类及其工作原理。

一、MCP存储器分类根据存储介质的不同,MCP存储器可以分为以下几种类型:1. NOR Flash MCP:NOR Flash MCP是一种非易失性存储器,可以用于存储程序代码和数据。

它具有读取速度快的特点,适用于需要频繁读取数据的应用。

NOR Flash MCP常用于手机等设备的固件存储。

2. NAND Flash MCP:NAND Flash MCP也是一种非易失性存储器,常用于存储大容量的数据。

相比于NOR Flash MCP,NAND Flash MCP的读取速度较慢,但写入速度更快,适用于需要频繁写入数据的应用。

NAND Flash MCP常用于存储手机的照片、视频等大容量数据。

3. PSRAM MCP:PSRAM(Pseudo Static Random Access Memory)MCP是一种伪静态随机存取存储器,结合了静态随机存取存储器(SRAM)和动态随机存取存储器(DRAM)的特点。

PSRAM MCP具有较快的读写速度和相对较低的功耗,适用于高速缓存和数据存储等应用。

二、MCP存储器的工作原理MCP存储器由多个存储芯片组成,每个存储芯片都包含若干存储单元。

这些存储单元以网格状的方式排列,每个存储单元由一个晶体管和一个电容组成。

MCP存储器的工作原理可以简单描述为以下几个步骤:1. 地址译码:当系统需要读取或写入数据时,首先需要将逻辑地址转换为物理地址。

地址译码器会将逻辑地址转换为对应的存储单元地址。

2. 读取数据:当需要读取数据时,MCP存储器会根据物理地址找到对应的存储单元,并通过晶体管控制电容的充放电状态,将存储单元中的数据读取到电路中。

多芯片封装技术

多芯片封装技术

多芯片封装技术可以提供更高的集成度和性能,同时减小封装体积和功耗。它在移动设备 、无线通信、计算机、消费电子、汽车电子等领域得到广泛应用。然而,多芯片封装技术也 面临着封装复杂性、互连可靠性和热管理等挑战,需要综合考虑设计、制造和测试等方面的 问题。

多芯片封装技术

多芯片封装技术(Multi-Chip Package,MCP)是一种集成电路封装技术,它将多个芯 片集成在一个封装中。这种封装技术可以在一个封装内实现多个功能模块的集成,提高集成 度和性能,同时减小封装体积和功耗。

多芯片封装技术通常包括以下几种形式:

1. 多芯片模块(Multi-Chip Module,MCM):在一个封装中集成多个芯片,每个芯片 可以是不同的功能模块,如处理器、存储器、传感器等。这些芯片通过高密度互连技术(如 焊球、焊盘、线缆等)进行连接。MCM可以提供高速、高带宽的数据传输和低延迟的通信。

多芯片封装技术

2. 堆叠封装(Stacked Package):将多个芯片堆叠在一起,形成一个垂直的结构。每个 芯片可以是不同的功能模块,通过封装内的互连技术进行连接。堆叠封装可以实现更高的集 成度和更小的封装体积,同时提高芯片之间的通信速度和带宽。

3. 系统级封装(System-in-Package,SiP):将多个芯片和其他组件(如电容器、电感 器、滤波器等)集成在一个封装中,形成一个完整的功能模块。SiP可以实现更高Байду номын сангаас集成度和 更小的封装体积,同时提供更好的电磁兼容性和热管理。

最新的多芯片模块(MCM)封装类型

(small die)或者小芯片(chiplet)。

这些小芯片通常采用不同的工艺节点制造,并被集成到单个封装中。

它能够满足严苛的PPA目标,是值得开发者努力的方向。

先进的芯片封装技术在创新过程中必将起到主要作用。

MulTI-die系统级封装(SiP)具有以下优势:可开发具有更多功能的产品可通过更换裸片快速开发出多个SKU可使用经过验证的裸片,减少开发风险与使用两个独立的芯片相比,mulTI-die吞吐量更高,系统功耗更低可优化系统外形尺寸,降低系统成本与使用两个独立的芯片相比,裸片间的低延迟可以提高系统性能封装行业有一系列技术可支持mulTI-die设计,例如:标准的2D封装、2.5D 先进封装,以及3D堆叠裸片,但没有哪个封装技术是可以适合所有产品的。

选择哪种封装方式将取决于产品的PPA和成本目标。

本文将简单介绍几种最新的多芯片模块(MCM)封装类型,并重点阐述die-to-die(D2D)IP如何通过这些封装来更好地支持设计流程。

四大先进芯片封装类型下一波系统设计浪潮将以先进封装中的小芯片为主导。

这些小芯片本质上也是集成电路,专门用来与其他裸片一起打造更大、更复杂的芯片,且可以被集成到先进的MCM封装中。

小芯片通常由可重复使用的IP块组成。

不同的封装类型在组装、密度和复杂性方面各不相同。

图1介绍了主要的封装类型以及它们在不同应用中的优势和劣势。

▲ 图1:主要的先进封装类型概览有机衬底有机衬底可以支持低密度的IO排布,D2D连接较少。

这种2D类型的标准封装相对便宜,在半导体行业中使用广泛。

与2.5D和3D封装不同,有机衬底封装并不存在脆弱的微凸块,并且由于工艺已十分成熟,所以往往良率更高。

它具有可测试性功能(对已知合格裸片进行低成本晶圆级筛选),但无法对故障连接进行测试和修复。

此外,有机衬底还具有良好的散热性和低翘曲性,支持大规模SiP集成,且无掩模板限制。

重分布层(RDL)扇出相对较新的RDL扇出型(Fan-Out)封装尚未得到广泛使用,其密度与硅中介层相似,但复杂性和成本却更低。

多芯片组件(MCM)技术ppt课件

二、多芯片组件(MCM)分类

• MCM-D

MCM - D是一类在Si、陶瓷或金属基板上采用薄膜工艺 形成高密度互连布线的MCM。MCM - D的基材可以是硅、 铝、氧化铝或氮化铝。典型的线宽25微米,线中心距50微米。 层间通道在10到50微米之间。低介电常数材料二氧化硅、聚 酰亚胺或BCB常用作介质来分隔金属层,介质层要求薄,金 属互连要求细小且保持适当阻抗。

二、多芯片组件(MCM)分类

• MCM-C

共烧陶瓷多芯片组件则以共烧陶瓷混合电路技术发展为基 础。相比于叠层MCM ,陶瓷MCM 需要附加工艺步骤,包括在 介质层上铺设导体图形的薄膜印刷技术。制备足够的布线层数 以实现需要的互连设计,同时还要保证基板的良好机械性能。 介质层打孔形成通孔,通孔会被导体材料填实起到连接上下层 的电学互连。陶瓷上印制电阻材料可获得所需要的电阻值的电 阻,通过微调技术对其进行阻值修正。

一、多芯片组件(MCM)认知

• 基本特点: MCM是高密度组装产品,芯片面积占

基板面积至少20%以上,互连线长度极大缩 短,封装延迟时间缩小,易于实现组件高 速化。

MCM的多层布线基板导体层数应不少 于4层,能把模拟电路、数字电路、功率器 件、光电器件、微波器件及各类片式化元 器件合理而有效地组装在封装体内,形成 单一半导体集成电路不可能完成的多功能 部件、子系统或系统。使线路之间的串扰 噪声减少,阻抗易控,电路性能提高。

多芯片组件(MCM)技术

机电学院 2013.03.21

一、多芯片组件(MCM)认知

• 概念:

多芯片组件,英文缩写 MCM( Multi-Chip Module)—— 是继表面安装技术后,在微电 子领域出现的一项最引人瞩目 的新技术,是将多块半导体裸 芯片组装在一块布线基板上的 一种封装技术。其与混合集成 电路产品并没有本质的区别, 只不过多芯片组件具有更高的 性能、更多的功能和更小的体 积,可以说多芯片组件属于高 级混合集成电路产品。

多芯片封装MCP

MCM(MCP)-Multi Chip Module 是单芯片封装在两维空间里的延伸,也是专用集成电路封装的一种模式。

MCM 具有系统尺寸小、引线框架互连基板芯片、系统功能强、节省PCB 空间、屏蔽和频率特性好、开发风险小、成本低。

上个世纪末,MCM 的应用受到KGD、基板费用高、封装费用高的限制,被戏称为MCMs(Must Cost Millions)-“必须花费几百万”。

如今美国互连与封装学会把MCM按照不同的互连衬底介质分为L、C、D 三种类型:即层压介质高密度印刷线路板模块、陶瓷或玻璃混合电路和共烧陶瓷多层陶瓷模块和在聚合物和介质材料薄膜上淀积金属布线模块。

南通的MCM 属于第三类,采用陶瓷或硅基板,封装外形采用DIP、QFP 封装_薄膜工艺流程:首先在一个200mm(8英寸)晶圆上作4个铝层(两个互连层和两个电源层),中间用苯环丁烯(BCB)绝缘层隔开。

电源层金属溅射厚度为1μm,信号层为3μm,溅射的铝符合半导体规范要求(含0.5%铜),线宽为20μm,线距为25μm,电源层之间介质厚度为3μm,信号层之间为7μm。

BCB的介电常数很低,只有2.65,耗散因子也低至0.0008。

对于速度为10GHz的信号,它的性能有点类似陶瓷,但频率再高上去其性能就开始下降,在95GHz时1cm线上会有3dB衰减。

因为金属层很薄,所以存在一定的直流电阻,约为5Ω/cm,这一点在设计时要考虑到,远端应用应使用较短的布线,但它对改善系统内的耗散噪声有一定帮助。

设计中使用的通孔直接在BCB上作出。

3x 制作使用50μm焊盘和30μm导孔,孔壁略为倾斜,接触点约为20μm。

通孔电阻很小,能通过较大电流,通孔成形过程比目前90%设计工艺都要好。

BCB每层形成后都要经过一次软固化,最后一次固化温度为250℃。

固化使叠层各层相互连接,形成一个中间有引线的固化BCB。

基底材料耐温性使之可用于无铅贴装工艺,包括倒装芯片裸片贴装工艺。

第八章 多芯片组件(MCM)

当一个大而复杂的系统规定了MCM所占的封装 面积时,往往一层 MCM 难以实现,可以设计成立 体化的叠装 MCM ,既减小了所占面积,又充分利 用了空间。由于 CSP 解决了 KGD 问题,所以叠装 MCM的成品率才有保证。 CSP的出现,解决了芯片小,封装大的矛盾,它 既有封装器件的一切便利,又有裸芯片尺寸小,性 能优的特点,这就为 MCM 的迅速发展应用解决了 后顾之忧,因为组装 MCM 的所有芯片都经过老化 筛选、测试,使芯片成为真正的KGD。 另外,由于 CSP 的“外引线”凸点均是 Pb/Sn 焊 料,使用 SMT进行贴装焊接十分方便, MCM 的工 业化规模生产才能得以实现。

(3)MCM 是高密度组装产品,芯片面积占基板面积 减少20%以上,互连线长度极大缩短,封装延迟时间 缩小,易于实现组件高速化。 (4)MCM 避免了单块 IC 封装的热阻、引线及焊接等 一系列问题,使产品的可靠性获得极大提高。 (5)MCM 集中了先进的半导体 IC 的微细加工技术, 厚、薄膜混合集成材料与工艺技术,厚膜、陶瓷与 PCB 的多层基板技术以及 MCM 电路的模拟、仿真、 优化设计、散热和可靠性设计、芯片的高密度互连与 封装等一系列新技术。

多芯片组件(MCM)的组装方式是直接将裸露的 集成电路芯片安装在多层高密度互连衬底上,层与层 的金属导线是用导通孔连接的。 这种组装方式允许芯片与芯片靠得很近,可以降低 互连和布线中所产生的信号延迟、串扰噪声、电感/ 电容耦合等问题;还可提升系统效能与稳定度。 因此,它不仅需要良好的封装技术,在设计规划、 验证与测试上,也必须要有配套的技术和方法,才能 确保质量及优良率。

7.1.3 应用及发展趋势

目前,实现系统集成的技术途径主要有两个:一是半导 体单片集成技术;二是 MCM 技术。前者是通过晶片规模 的集成技术,将高性能数字集成电路(含存储器、微处理器、 图像和信号处理器等 )和模拟集成电路 ( 含各种放大器、变 换器等)集成为单片集成系统;后者是通过三维多芯片组件 技术实现集成的功能。 MCM早在80年代初期就曾以多种形式存在,但由于成 本昂贵,只用于军事、航天及大型计算机上。 近年来,随着技术的进步及成本的降低, MCM 在计算 机、通信、雷达、数据处理、汽车行业、工业设备、仪器 与医疗等电子系统产品上得到越来越广泛的应用,已成为 最有发展前途的高级微组装技术。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

多芯片封装

多芯片封装(Multi Chip Package;MCP)

封装形式的概念

所谓封装形式就是指安装半导体集成电路芯片用的外壳。

它不仅起着安装、固定、密封、保护芯片及增强电热性能等方面的作用,而且还通过芯片上的接点用导线连接到封装外壳的引脚上,这些引脚又通过印刷电路板上的导线与其他器件相连接。

衡量一个芯片封装技术先进与否的重要指标是芯片面积与封装面积之比,这个比值越接近1越好。

一般来说,出现一代新的CPU,就伴随着一种新的封装形式。

随各式便携式信息装置对内存特性需求日益多元化,可将数个芯片封装在一处的多芯片封装(Multi Chip Package;MCP)亦逐渐受到重视,全球包含三星电子、现代电子、英特尔等重量级IC厂商,近期纷纷看好此型内存市场前景,竞推出相关产品。

MCP的优点在于能将2至3种不同特性的芯片封装在一块,可因此减少占据的空间,当前主要为内存所采用。

而利用该封装做出的内存产品适于有复杂内存特性需求的信息装置使用。

目前内存厂商主要利用该技术将闪存(Flash)与SRAM做在一块。

-薄芯片处理是一种特殊的晶圆支持技术,能使芯片被琢磨到只有0.025毫米的厚度。

多重堆叠封装技术能利用无铅锡焊球把安装的芯片的板块堆叠起来。

这种封装在功能上相当于单一封装(single package)。

MCM(Multi Chip Model)多芯片组件-质量

为了解决单一的芯片集成度和功能不够完善的问题,把多个高集成度、高性能、高可靠性的芯片,在高密度多层互联基板上用SMD技术组成多种多样电子组件系统,从而出现了MCM多芯片组件系统

MCM具有以下特点:

封装延迟时间缩小,易于实现组件高速化

缩小整机/组件封装尺寸和重量。

系统可靠性大大提高。

总之,随着CPU和其他超大规模集成电路的进步,集成电路的封装形式也将得到相应的变化,而且封装形式的进步又将反过来促进芯片技术向前发展。

不久以前,高密度薄膜和多芯片封装(MCP)还被认为只是一种用于太空、军事、高端服务器以及大型主机等系统的新型技术,这种技术可以减小最终封装件及系统的尺寸

和重量、减少故障提高可靠性、使用更短和负载更轻的信号线增加速度并使系统具有良好的热性能。

如今,薄膜MCP的各种优点已能够在价格低廉的商用和消费类产品中得以实现,为批量生产而开发的低成本流水线薄膜生产工艺使这项技术由实验室进入到了工厂。

这种新工艺采用硅片覆膜高密度互连基板,对于装配车间来说看上去感觉就像是另一个芯片一样。

它把用不同工艺制造的器件集成在一个封装内,在功能上满足市场快速变化的要求,并在不改变封装引脚尺寸的前提下提高设计的性能。

MCM(MCP)-Multi Chip Module

MCM(MCP)-Multi Chip Module 是单芯片封装在两维空间里的延伸,也是专用集成电路封装的一种模式。

MCM 具有系统尺寸小、引线框架互连基板芯片、系统功能强、节省PCB 空间、屏蔽和频率特性好、开发风险小、成本低。

上个世纪末,MCM 的应用受到KGD、基板费用高、封装费用高的限制,被戏称为MCMs(Must Cost Millions)-“必须花费几百万”。

如今美国互连与封装学会把MCM按照不同的互连衬底介质分为L、C、D 三种类型:即层压介质高密度印刷线路板模块、陶瓷或玻璃混合电路和共烧陶瓷多层陶瓷模块和在聚合物和介质材料薄膜上淀积金属布线模块。

南通的MCM 属于第三类,采用陶瓷或硅基板,封装外形采用DIP、QFP 封装

_

薄膜工艺流程:首先在一个200mm(8英寸)晶圆上作4个铝层(两个互连层和两个电源层),中间用苯环丁烯(BCB)绝缘层隔开。

电源层金属溅射厚度为1μm,信号层为3

μm,溅射的铝符合半导体规范要求(含0.5%铜),线宽为20μm,线距为25μm,电源层之间介质厚度为3μm,信号层之间为7μm。

BCB的介电常数很低,只有2.65,耗散因子也低至0.0008。

对于速度为10GHz的信号,它的性能有点类似陶瓷,但频率再高上去其性能就开始下降,在95GHz时1cm线上会有3dB衰减。

因为金属层很薄,所以存在一定的直流电阻,约为5Ω/cm,这一点在设计时要考虑到,远端应用应使用较短的布线,但它对改善系统内的耗散噪声有一定帮助。

设计中使用的通孔直接在BCB上作出。

3x 制作使用50μm焊盘和30μm导孔,孔壁略为倾斜,接触点约为20μm。

通孔电阻很小,能通过较大电流,通孔成形过程比目前90%设计工艺都要好。

BCB每层形成后都要经过一次软固化,最后一次固化温度为250℃。

固化使叠层各层相互连接,形成一个中间有引线的固化BCB。

基底材料耐温性使之可用于无铅贴装工艺,包括倒装芯片裸片贴装工艺。

另外还有一种热通孔用于直接连接硅晶圆载体,并为大功率元件提供一个低阻热通道。

该项工艺的主要工序为:旋转涂覆、热固化、溅射、掩膜对位和UV曝光、显影、湿法及干法刻蚀。

基片以晶圆形式提供给最终用户。

趋势及未来展望:

六西格玛品质论坛小型MCP的增长需求来自于一些大批量应用消费类产品,如移动电话、掌上电脑和上网记事本、MP3播放机以及其它手持装置,这些产品不仅对价位很敏感,而且要求有较短的产品和改进周期,而这两个要求系统级芯片ASIC技术和嵌入式存储器技术制造工艺却又无法满足。

低成本多芯片封装可作为这些市场所追求的“快速廉价”解决方案,许多来自半导体供应商和OEM的应用都要求将一个快闪

存储器和一个逻辑电路,如微处理器、DSP或ASIC结合在一起。

这些非常简单的MCP设计装配和测试成品率都大于98%,避免了“原本好裸片后来又不好”(KGD)

之类的问题。

今后还将把裸片以倒装芯片形式与硅基底相连,或者与一个重新布线的载体裸片相连用于叠层元件封装中,这种布线技术能在制成的半导体晶圆裸片上提供高密度多层再布线和感应极小的功率分配。

最后,在多芯片封装中将多个倒装芯片贴到硅基底上,这个基底就可以作为封装件,再用大的回流焊球或柱将基底贴到线路板上。

多芯片模块虽然可以提供极高的互连密度,但其高昂的成本一直限制了它的使用。

近年来研究人员又提出了一种和多芯片相对的少芯片封装概念,它克服了以往设计的不足,能满足目前电子产品在成本和功能上的要求。

90年代初期,多芯片模块(MCM)曾被认为是最佳互连封装技术,可以满足不断发展的电子工业的要求。

MCM技术将多个裸片固定在一个基板上连在一起,裸片之间非常接近,可以减少互连延迟。

L

当时一个典型的MCM可能含有二十多个裸片,密封在一块低温共烧陶瓷(LTCC)或沉积基板上。

MCM通常用于军事、航天或高性能计算机设备上,这类应用一般不太计较价格。

虽然IBM和富士通都在他们的大型计算机中使用了MCM并取得成功,但MCM 从未在商业上达到预期的效果。

由于裸片测试和基板返修方面的原因,MCM一直没有能在PC/工作站这个利润非常高的庞大市场中得到广泛采用。

此外只要一个器件失效,基板连带上面好的器件都得扔掉,所以这是一种商用上无法接受的高成本技术。

最近两三年来,MCM技术通过少芯片封装(FCP)的形式获得了新生。

FCP有时也称为多重芯片封装(MCP),已有越来越多的公司出于技术和商业的原因正在接受FCP。

虽然这些FCP看起来与它们的单芯片同类没什么区别,但它们确实完全不同于90年代初期的MCM,今天的FCP不再使用多达二十个的裸片,一般只用2~4个裸片装在球栅阵列封装基板上(图1)。

这一“再生”应部分归功于裸片测试和运送技术的改善以及低成本高性能基板的出现,随着FCP逐渐成为系统级芯片(SoC)的替代方案,进一步还产生了系统级封装(SiP)。