第5章__片内集成外设开发及测试(修改)

第五章系统测试

需求规格说明是功能测试的基本输入。因此先对 需求规格进行分析,明确功能测试的重点。可按照如 下步骤进行:

① 为所有的功能需求(其中包括隐含的功能需求)加 以标识;

② 为所有可能出现的功能异常进行分类分析并加ቤተ መጻሕፍቲ ባይዱ标 识;

③ 对前面表示的功能需求确定优先级。

第五章系统测试

[本章要点]

系统测试的定义; 系统测试的组织与分工; 系统测试的类型; 系统测试的测试用例设计方法; 系统测试的案例分析。

[本章目标]

▪ 进一步理解系统测试和集成测试的区别; ▪ 掌握系统测试的概念; ▪ 熟悉主要的系统测试类型及其特点; ▪ 了解系统测试的过程; ▪ 重点理解如何把黑盒测试技术运用到系统测试中。

14.检查多次使用back键的情况

15. search检查 16.输入信息位置 17.上传下载文件检查 18.必填项检查 19.快捷键检查 20.回车键检查 二、协议一致性测试(Protocol Conformance Testing)

分布式系统中,很多计算功能的完成需要由分布式 系统内的多台计算机相互进行通信、交换信息、协调合 作来完成的,必须遵循一定的规则(协议)。 所以要 进行协议测试。

从网络管理软件获取网络拓扑结构、从现有的流量 监控软件获取流量信息,这样可以得到现有网络的基本 结构,并进行流量分析和冲突检测。

3、应用在服务器上性能的测试

采用工具监控资源使用情况。

实施测试的目的是实现服务器设备、服务器操作系 统、数据库系统、应用在服务器上性能的全面监控,测 试原理如图5-2。

文件 服务器

并发性能测试的过程是一个负载测试和压力测试的 过程,即逐渐增加负载,直到系统的瓶颈或者不能接收 的性能点,通过综合分析交易执行指标和资源监控指标 来确定系统并发性能的过程。

单片机基础知识资料-PPT

第1、3章 单片机应用概述与开发步骤

1. 电子计算机的发展概述

2. 单片机的发展过程及产品近况

3. 单片机的特点 4. 单片机应用系统开发简介

5.1 计算机语言概述

5.2 80C51单片机寻址方式

5.3 80C51单片机指令系统

暂时不讲

5.4 80C51汇编语言程序设计

5.5 80C51单片机C51程序设计语言

5.6 C51的运算符和表达式

5.7 C51的库函数

5.8 C51的应用技巧

第5章 80C51单片机软件基础知识

单片机应用系统

大家有疑问的,可以询问和交流

可以互相讨论下,但要小声点

第1、3章 单片机应用概述与开发步骤

软件系统

• 系统资源分配 • 程序结构 • 数学模型 • 程序流程 • 编制程序

第1、3章 单片机应用概述与开发步骤

程序设计

通常是C语言或者汇编语言,在特定的集成开发环境(IDE)中编程 调试,比如应用最广泛的KEIL uVision3

通过特殊功能寄存器可实现对单片机内部资源的 操作和管理。

常用特殊功能寄存器

第4章 80C51单片机硬件基础知识

常用特殊功能寄存器

第4章 80C51单片机硬件基础知识

常用特殊功能寄存器

端口P0~P3

特殊功能寄存器P0~P3分别是I/O端口P0~P3的锁存 器。80C51单片机是把I/O当作一般的特殊功能寄存器 使用,不专设端口操作指令,使用方便。

•数据缓冲区 30H~7FH是数 据缓冲区,即 用户RAM区, 共80个单元。

【STM32H7教程】第5章STM32H7下载和调试方法(MDK5)

【STM32H7教程】第5章STM32H7下载和调试⽅法(MDK5)第5章 STM32H7下载和调试⽅法(MDK5)本章教程为⼤家介绍如何通过MDK5下载程序到芯⽚⾥⾯以及MDK5的调试和配置⽅法。

5.1 初学者重要提⽰5.2 使⽤MDK调试和下载程序设置(JLINK)5.3 使⽤MDK调试和下载程序设置(STLINK)5.4 MDK调试容易崩溃的解决办法5.5 MDK程序调试5.6 总结5.1 初学者重要提⽰1. 如果使⽤JLINK调试下载STM32H7,务必使⽤JLINK V9或V10,之前的版本已经不⽀持。

2. 如果使⽤STLINK调试下载STM32H7,推荐使⽤最新的电脑端驱动和对应的固件,详情见第2章的2.6⼩节。

3. MDK曾发布的STM32F1,F407,F429和F7的所有调试⽅法的设置细节及其注意事项,同样适⽤于STM32H7:。

4. MDK5调试过程中容易崩溃的问题,请看本章5.4⼩节,⽐较重要。

5. JLINK⽆法下载解决思路以及常见问题整理,适⽤于其它LINK:。

5.2 使⽤MDK调试和下载程序设置(JLINK)调试下载STM32H7,务必使⽤JLINK V9或V10,之前的版本已经不⽀持,JLINK的驱动安装等相关⽂件已经在本教程第2章的2.5章节有说明。

在上个章节⾥⾯,我们已经将Options对话框⾥⾯⼤部分设置选项都做了说明,本章节主要是调试下载的设置。

5.2.1 开发板和JLINK的接线图开发板接上JLINK的效果图如下,JLINK端需要插⼊开发板赠送的JTAG转SWD转接板:注意转接板不要插反了:5.2.2 设置Options⾥⾯的Debug选项Debug选项主要⽤于调试设置。

打开Settings设置选项,设置完毕后别忘了点击确定。

5.2.3 设置Options⾥⾯的Utilities选项Utilities选项主要⽤于程序下载设置。

5.2.4 程序下载前两步设置好之后,JLINK插到电脑端并跟开发板连接好,将板⼦上电,就可以下载了。

第5章_TMS320F2812片内外设模块

华东交通大学电气学院

第5.1节 事件管理器(EV)

F2812提供了2个结构和功能相同的事件管理器EVA和 EVB模块,具有强大的控制功能,特别在运动控制和电机控 制领域。

PDPINTB CMP4/5/6INT CAPINT4/5/6n B T3CINT,T3PINT T3UFINT,T3OFINT

PIE 中断 模块

T3CTRIP PDPINTB

T4CINT,T4PINT

T4C华TR东IP 交通大学电气学院

T4UFINT,T4OFINT

EVA和EVB模块信号引脚

EV模块

通用定时器的寄存器?1通用定时器控制寄存器t1cont2con?选择4种计数模式的一种?使用内部还是外部时钟?确定输入时钟使用的预定标参数?确定比较寄存器重新装载的条件?使能或禁止通用定时器?使能或禁止通用定时器的比较操作?定时器2或1的周期寄存器?定时器4或3的周期寄存器1通用定时器控制寄存器t1cont2confreesoftreservedtmode1tmode0tps2tps1tps0t2swt1t4swt3tenabletclks1tclks0tcld1tcld0tecmprselt1prselt3prd15d14d13d12d11d10d9d8d7d6d5d4d3d2d1d0通用定时器控制寄存器txcon计数模式选择countmodeselection00停止保持01连续增减计数模式10连续增计数模式11定向递增减计数模式定时器使能控制位timerenable0禁止定时器操作1使能定时器操作定时器比较使能位timercompareenable0禁止定时器比较操作1使能定时器比较操作2全局通用定时器控制寄存器gptconab?确定通用定时器实现具体任务需采取的操作方式并明计数方向通用定时器2的状态0递减计数1递增计数reservedt2statt1statt2ctripet1ctripet2toadct1toadcr0r1r1rw1t1toadctcmpoet2cmpoet1cmpoet2pint1pind15d14d13d12d11d10d9d8rw1rw0rw0d7d6d5d4d3d2d1d0rw0rw0rw0通用定时器1比较输出的极性选择位00强制低01低有效10高有效11强制高rw0rw0rw0通用定时器a控制寄存器gptcona通用定时器1的状态0递减计数1递增计数2全局通用定时器控制寄存器gptconabreservedt4statt3statt4ctripet3ctripet4toadct3toadcr0r1r1rw1d7d6d5d4d3d2d1d0t3toadctcmpoet4cmpoet3cmpoet4pint3pind15d14d13d12d11d10d9d8rw1rw0rw0rw0rw0rw0rw0rw0rw0通用定时器b控制寄存器gptconb3通用定时器比较寄存器txcmpr?比较寄存器中的值与通用定时器的计数值进行比较比较匹配时产生

DSP原理与应用2011-第五章TMS320F28335片(精)

DSP 原理与应用The Technology & Applications of DSPs第五章: TMS320F28335片内外设北京交通大学电气工程学院夏明超郝瑞祥万庆祝***************.cn**************.cn**************.cn:TMS320F28335第五讲: TMS320F28335片内外设教学目标:掌握TMS320F28335内核结构,例如A/D转换、串行通信接口、串行外设接口。

外设接重点:TMS320F28335A/DCS308335内部/C 的正确使用,串行通信接口应用。

难点:TMS320F28335的ADC 寄存器操作和串行通信寄存器操作。

教学内容分两部分51§5.1:TMS320F28335内模拟/数字转换§5.2 :TMS320F28335系列串行通信接口SCI 和Modbus 协议介绍DSP 原理与应用2DSP原理与应用3 ADC 有关引脚§5.1 TMS320F28335内模拟/数字转换§5.1 .1Features and functions of ADC module:◆core with built-in dual sample-and-hold◆Simultaneous sampling or sequential sampling modesp g q p g ◆Analog input: ◆Fast conversion time runs at ADC clock orFast conversion time runs at , ADC clock, or 6.25 MSPSmultiplexed inputs◆, multiplexed inputs◆capability provides up to 16 " t i " i i l i E h i "autoconversions" in a single session. Each conversioncan be to select any 1 of 16 input channels.DSP 原理与应用4Sequencer can be operated as two independent 8-state ◆Sequencer can be operated as two independent 8-state sequencers or as one large 16-state sequencer (i.e., two cascaded 8-state sequencerstwo cascaded 8state sequencers.◆(individually addressable to store conversion values store conversion valuesA/DC digital value:DSP 原理与应用2012年9月3日5◆for the start-of-conversion sequence–S/W -software immediate start–ePWM 1-6–GPIO XINT2◆allows interrupt request on every end-of-sequence (EOS or every other EOSy q ( y◆Sequencer can operate in mode, allowing multiple "time-sequenced triggers" to synchronize p q gg yconversions.Sample-and-hold (S/Hacquisition time window has ◆Sample and hold (S/H acquisition time window has separateA/DC模块框图(Block diagram of A/DC Module)§5.1. 2ADC 有关的寄存器控制寄存器通道顺序选择寄存器结果寄存器ADC有关的寄存器(序)控制寄存器状态寄存器参考电压选择寄存器偏移电压调整寄存器§5.1.3 ADC操作模式1 顺序采样模式(Sequential Sampling Mode)根据采样模式划分,包括顺序采样和同步采样2同步采样模式(Simultaneous Sampling Mode)DSP 原理与应用2012年9月3日11根据转换模式划分,包括:级联模式转换和和双序列模式转换1)级联模式转换DSP 原理与应用2012年9月3日122)双序列模式转换DSP 原理与应用2012年9月3日13 单序列模式和级联模式对比DSP 原理与应用2012年9月3日14§5.1.4 ADC电压参考默为使用内部电压参考也以使用外部电压参考允许值为●默认为使用内部电压参考,也可以使用外部电压参考,允许值为2.048V ,1.5V 和1.024V 。

单片机设计及应用知到章节答案智慧树2023年上海电力大学

单片机设计及应用知到章节测试答案智慧树2023年最新上海电力大学绪论单元测试1.本课程的学习目标为()。

参考答案:包括单片机的基本工作原理、单片机的硬件接口技术、汇编语言软件程序设计2.本课程的考试及格率为()。

参考答案:50~75%3.本课程的选修课程为()。

参考答案:计算机基础;电子电路;C语言第一章测试1.微型计算机采用总线结构()。

参考答案:可以简化系统结构、易于系统扩展2.微机的地址总线功能是()。

参考答案:用于传送要访问的存储器单元或I/O端口的地址3.在微机中将各个主要组成部件连接起来,组成一个可扩充基本系统的总线称之为( )。

参考答案:系统总线4.微型计算机的存储系统一般指主存储器和()。

参考答案:辅助存储器5.计算机的工作原理是存储程序控制,所以计算机中的程序都是顺序执行的。

()参考答案:错6.在计算机中,程序和数据都是以二进制形式不加区别存放的。

()参考答案:对7.已知[X]原=11101001,则[X]反=00010110。

()参考答案:错8.800H =2KB。

()参考答案:对9.8位二进制数补码的大小范围是-127∽+127。

()参考答案:错10.-128的补码是10000000。

()参考答案:对11.将十进制(0.825)10转换成二进制数是(0.1101)2。

()参考答案:错12.计算机中负数的反码是把它对应的正数连同符号位按位取反而开形成的。

()参考答案:错13.单片机在调试过程中,通过查表将源程序转换成目标程序的过程叫()。

参考答案:手工汇编14.将十进制数98转换成对应的二进制数是()。

参考答案:110001015.二进制数110110110对应的十六进制数可表示为()。

参考答案:1B6H16.已知[X]补=00000000,则真值X=()。

参考答案:17.计算机中最常用的字符信息编码是()。

参考答案:ASCII18.处理器的内部数据宽度与外部数据宽度可以()参考答案:相同或不同19.中央处理器是由()构成的。

DSP原理与应用2011-第五章 TMS320F28335片内外设_ad转换SCI

掌握TMS320F28335内核结构,例如A/D转换、串行通信接口、 串行 外设接口。

重点:

TMS320F28335内部A/DC的正确使用,串行通信接口应用。

难点:

TMS320F28335的ADC寄存器操作和串行通信寄存器操作。

教学内容分两部分

§5.1:TMS320F28335内模拟/数字转换 §5.2 :TMS320F28335系列串行通信接口SCI和Modbus协议介绍

7

§5.1 .2 ADC有关的寄存器

控制寄存器

通道顺序选 择寄存器

结 果 寄 存 器

DSP原理与应用

2012年9月3日

8

ADC有关的寄存器(序)

控制寄存器 状态寄存器

参考电压选择寄存器 偏移电压调整寄存器

DSP原理与应用

2012年9月3日

9

§5.1.3 ADC 操作模式

根据采样模式划分,包括顺序采样和同步采样 1) 顺序采样模式(Sequential Sampling Mode)

DSP原理与应用

2012年9月3日

10

2) 同步采样模式(Simultaneous Sampling Mode)

DSP原理与应用

2012年9月3日

11

根据转换模式划分,包括: 级联模式转换和和双序列模式转换 1) 级联模式转换

DSP原理与应用

2012年9月3日

12

2) 双序列模式转换

DSP原理与应用

DSP原理与应用

4

Sequencer can be operated as two independent 8-state sequencers or as one large 16-state sequencer (i.e., two cascaded 8-state sequencers).

第五章 通用输入输出端口-TMS320F28335 DSP原理、开发及应用-符晓

0

QUALPRD0

GPIO39-32 GPIO7-0

C2833x GPIO 控制寄存器

寄存器 GPACTRL GPAQSEL1 GPAQSEL2 GPAMUX1 GPAMUX2 GPADIR GPAPUD GPBCTRL GPBQSEL1 GPBQSEL2 GPBMUX1 GPBMUX2 GPBDIR GPBPUD GPCMUX1 GPCMUX2 GPCDIR GPCPUD

输入限定

GPIO Port C 方向寄存器 (GPCDIR) [GPIO 64 到 87]

GPIO Port C

F2833x GPIO管脚示意图

GPxSET GPxCLEAR GPxTOGGLE

I/O DIR Bit 0 = Input 1 = Output

GPxDIR

GPxDAT Out

I/O DAT Bit (R/W) In

C2833x GPIO 数据寄存器

寄存器 GPADAT GPASET GPACLEAR GPA到GGLE GPBDAT GPBSET GPBCLEAR GPB到GGLE GPCDAT GPCSET GPCCLEAR GPC到GGLE

描述 GPIO A Data 寄存器 [GPIO 0 – 31] GPIO A Data 置位寄存器[GPIO 0 – 31] GPIO A Data 清除寄存器[GPIO 0 – 31] GPIO A Data 翻转寄存器[GPIO 0 – 31] GPIO B Data 寄存器 [GPIO 32 – 63] GPIO B Data 置位寄存器[GPIO 32 – 63] GPIO B Data 清除寄存器[GPIO 32 – 63] GPIO B Data 翻转寄存器[GPIO 32 – 63] GPIO C Data 寄存器 [GPIO 64 – 87] GPIO C Data 置位寄存器[GPIO 64 – 87] GPIO C Data 清除寄存器[GPIO 64 – 87] GPIO C Data 翻转寄存器[GPIO 64 – 87]

DSP原理及应用-(修订版)--课后习题答案

第一章:1、数字信号处理的实现方法一般有哪几种?答:数字信号处理的实现是用硬件软件或软硬结合的方法来实现各种算法。

(1) 在通用的计算机上用软件实现;(2) 在通用计算机系统中加上专用的加速处理机实现;(3) 用通用的单片机实现,这种方法可用于一些不太复杂的数字信号处理,如数字控制;(4)用通用的可编程 DSP 芯片实现。

与单片机相比,DSP 芯片具有更加适合于数字信号处理的软件和硬件资源,可用于复杂的数字信号处理算法;(5) 用专用的 DSP 芯片实现。

在一些特殊的场合,要求的信号处理速度极高,用通用 DSP 芯片很难实现( 6)用基于通用 dsp 核的asic 芯片实现。

2、简单的叙述一下 dsp 芯片的发展概况?答:第一阶段, DSP 的雏形阶段( 1980 年前后)。

代表产品: S2811。

主要用途:军事或航空航天部门。

第二阶段, DSP 的成熟阶段( 1990 年前后)。

代表产品: TI 公司的 TMS320C20主要用途:通信、计算机领域。

第三阶段, DSP 的完善阶段( 2000 年以后)。

代表产品:TI 公司的 TMS320C54 主要用途:各个行业领域。

3、可编程 dsp 芯片有哪些特点?答: 1、采用哈佛结构( 1)冯。

诺依曼结构,( 2)哈佛结构( 3)改进型哈佛结构2、采用多总线结构 3.采用流水线技术4、配有专用的硬件乘法-累加器5、具有特殊的 dsp 指令6、快速的指令周期7、硬件配置强8、支持多处理器结构9、省电管理和低功耗4、什么是哈佛结构和冯。

诺依曼结构?它们有什么区别?答:哈佛结构:该结构采用双存储空间,程序存储器和数据存储器分开,有各自独立的程序总线和数据总线,可独立编址和独立访问,可对程序和数据进行独立传输,使取指令操作、指令执行操作、数据吞吐并行完成,大大地提高了数据处理能力和指令的执行速度,非常适合于实时的数字信号处理。

冯。

诺依曼结构:该结构采用单存储空间,即程序指令和数据共用一个存储空间,使用单一的地址和数据总线,取指令和取操作数都是通过一条总线分时进行。

DSP(知识点+思考题)

DSP复习要点第一章绪论1、数的定标:Qn表示。

例如:16进制数2000H=8192,用Q0表示16进制数2000H=0.25,用Q15表示2、‟C54x小数的表示方法:采用2的补码小数;.word 32768 *707/10003、定点算术运算:乘法:解决冗余符号位的办法是在程序中设定状态寄存器STl中的FRCT位为1,让相乘的结果自动左移1位。

第二章CPU结构和存储器设置一、思考题:1、C54x DSP的总线结构有哪些特点?答:TMS320C54x的结构是围绕8组16bit总线建立的。

(1)、一组程序总线(PB):传送从程序存储器的指令代码和立即数。

(2)、三组数据总线(CB,DB和EB):连接各种元器件,(3)、四组地址总线(PAB,CAB,DAB和EAB)传送执行指令所需要的地址。

2、C54x DSP的CPU包括哪些单元?答:'C54X 芯片的CPU包括:(1)、40bit的算术逻辑单元(2)、累加器A和B(3)、桶形移位寄存器(4)、乘法器/加法器单元(5)、比较选择和存储单元(6)、指数编码器(7)、CPU状态和控制寄存器(8)、寻址单元。

1)、累加器A和B分为三部分:保护位、高位字、地位字。

保护位保存多余高位,防止溢出。

2)、桶形移位寄存器:将输入数据进行0~31bits的左移(正值)和0~15bits的右移(负值)3)、乘法器/加法器单元:能够在一个周期内完成一次17*17bit的乘法和一次40位的加法4)、比较选择和存储单元:用维比特算法设计的进行加法/比较/选择运算。

5)、CPU状态和控制寄存器:状态寄存器ST0和ST1,由置位指令SSBX和复位指令RSBX控制、处理器模式状态寄存器PMST2-3、简述’C54x DSP的ST1,ST0,PMST的主要功能。

答:’C54x DSP的ST1,ST0,PMST的主要功能是用于设置和查看CPU的工作状态。

•ST0主要反映处理器的寻址要求和计算机的运行状态。

面向人工智能的嵌入式设计与开发(山东联盟)智慧树知到答案章节测试2023年山东农业工程学院

第一章测试1.嵌入式单片机的处理器()。

A:CPUB:STC:内核D:Inter答案:C2.Cortex-M0系列的工作频率为()A:168MB:72MC:32MD:48M答案:D3.ARM微处理器不包含以下()系列。

A:Cortex-A 系列B:Cortex-M 系列C:Cortex-R 系列D:Cortex-B 系列答案:D4.STM32F103ZET6中103代表()A:闪存存储器容量B:产品子系列C:产品系列D:管脚数目答案:B5.STM32F103ZET6芯片有( )个输入/输出接口。

A:120B:168C:112D:113答案:C6.STM32F10x 芯片工作电压为()A:5VB:3.3VC:6VD:8V答案:B7.程序存储器(ROM)大小是()字节A:64KB:128KC:256K答案:D8.STM32F103ZET6中( )代表封装。

A:ZB:SC:FD:T答案:D9.Cortex-M 系列 M 系列芯片是基于ARM-V7架构的()位设计A:8位B:16位C:32位D:64位答案:C10.以下为嵌入式单片机的输入设备的是()A:按键B:OLEDC:键盘D:鼠标答案:A第二章测试1.GPIO口不可以实现()A:检测外来信号B:模拟全部通信接口通信C:输出D:驱动外部电路答案:C2.STM32F103ZE芯片一共有16个GPIO端口,序号为()A:1-15B:1-16C:0-16D:0-15答案:D3.GPIO端口在输入状态下,不可设置为()A:开漏输入B:模拟输入C:浮空输入、以及D:上拉/下拉输入答案:A4.GPIOB组端口()A:GPIOAC:GPIODD:GPIOC答案:B5.GPIO端口中的浮空输入指()A:GPIO_Mode_IPUB:GPIO_Mode_IPDC:GPIO_Mode_AIND:GPIO_Mode_IN_FLOATING答案:D6.GPIO 端口中的开漏输出指()A:GPIO_Mode_Out_PPB:GPIO_Mode_AF_ODC:GPIO_Mode_AF_PPD:GPIO_Mode_Out_OD答案:D7.GPIO_ReadOutputDataBit函数功能()A:根据“GPIO_InitStruct”中指定的参数初始化GPIO模块B:对指定的 GPIO 端口位输出高电平C:GPIO端口输入数据的读取D:读取指定 GPIO 端口的输出状态答案:D8.函数中选中管脚1的指令为( )A:GPIO_Pin_1B:GPIO_1C:GPIOPin_1D:Pin_1答案:A9.STM32F103ZE 芯片一共有()组 GPIO 端口A:8B:7C:9D:6答案:B10.GPIO端口中的推挽输出()A:GPIO_Mode_Out_ODB:GPIO_Mode_AF_PPC:GPIO_Mode_Out_PPD:GPIO_Mode_AF_OD答案:C第三章测试1.C语言中,输入操作是由库函数( )完成的A:stdioB:scanfC:printfD:math答案:B2.输出操作是由库函数( )完成的A:mathB:scanfC:printfD:stdio答案:C3.以下叙述不正确的是( )。

第5章SOPC技术

图5-7Nios II 存储器和I/O结构

1.指令与数据总线 NiosⅡ结构支持分离的指令和数据总线,属于哈佛 结构。指令和数据总线都作为Avalon主端口实现,遵从 Avalon接口规范。主数据端口连接存储器和外设,指令 主端口仅连接存储器构件。 (1)小端对齐的存储器组织方式 NiosⅡ的存储器问采用小端对齐的方式,在存储器 中,字和半字最高有效位字节存储在较高地址单元中。 (2)存储器与外设访问 NiosⅡ结构提供映射为存储器的I/O访问。数据存储器 和外设都被映射到数据主端口的地址空间。存储器系统 中处理器数据总线低8位分别连接存储器数据线7-0。

(3)指令主端口 NiosⅡ指令总线作为32位Avalon主端口来实现,通 过Avalon交换架构连接到指令存储器的Avalon主端口。 指令主端口只执行一个功能:对处理器将要执行的指令 进行取指。指令主端口是具有流水线属性的Avalon主端 口。它依赖Avalon交换结构中的动态总线对齐逻辑始终 能接收32位数据。NiosⅡ结构支持片内高速缓存还支持 紧耦合存储器,对紧耦合存储器的访问能实现低延迟。 注意:指令主端口不执行任何写操作。动态总线对齐逻 辑不管目标存储器的宽度如何,每次取指都会返回一个 完整的指令字,因而程序员不需要知道NiosⅡ处理器系 统中的存储器宽度。片内高速缓存,用于改善访问较慢 存储器时的平均指令取指性能

Nios II提供3种核不同的内,以满足系统对不同性能 和成本的需求,包括快速内核Nios II/f(性能最优,在 StratixⅡ中,性能超过200DMIPS,仅占用1800个LE)、 标准内核Nios II/s(平衡性能和尺寸)和经济内核Nios II/e(占用逻辑单元最少)。 3种内核的二进制代码完全兼容,具有灵活的性能,当 CPU内核改变时,无须改变软件。

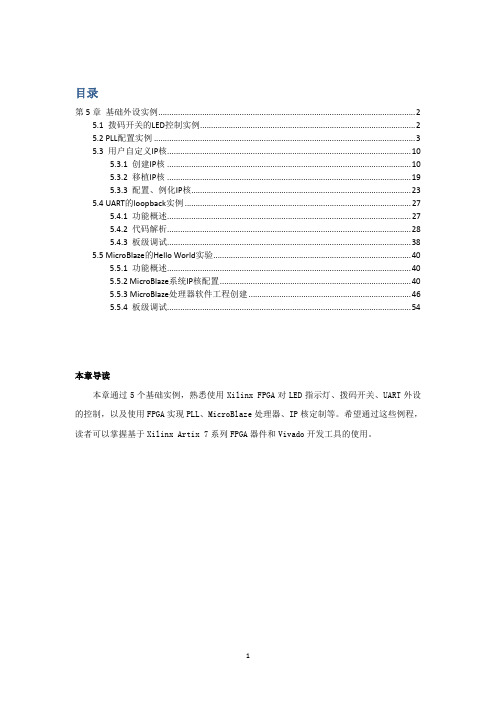

Xilinx FPGA伴你玩转USB3.0与LVDS 第5章 基础外设实例

目录第5章基础外设实例 (2)5.1 拨码开关的LED控制实例 (2)5.2 PLL配置实例 (3)5.3 用户自定义IP核 (10)5.3.1 创建IP核 (10)5.3.2 移植IP核 (19)5.3.3 配置、例化IP核 (23)5.4 UART的loopback实例 (27)5.4.1 功能概述 (27)5.4.2 代码解析 (28)5.4.3 板级调试 (38)5.5 MicroBlaze的Hello World实验 (40)5.5.1 功能概述 (40)5.5.2 MicroBlaze系统IP核配置 (40)5.5.3 MicroBlaze处理器软件工程创建 (46)5.5.4 板级调试 (54)本章导读本章通过5个基础实例,熟悉使用Xilinx FPGA对LED指示灯、拨码开关、UART外设的控制,以及使用FPGA实现PLL、MicroBlaze处理器、IP核定制等。

希望通过这些例程,读者可以掌握基于Xilinx Artix 7系列FPGA器件和Vivado开发工具的使用。

第5章基础外设实例5.1 拨码开关的LED控制实例本实例对应工程at7_ex02,如图5.1所示,AT7板子板载8个LED指示灯和8个拨码开关与FPGA相连。

本实例所要实现的功能很简单,每个拨码开关对应控制一个LED指示灯的亮灭状态。

图5.1 拨码开关与LED原理图本实例功能非常简单,大家直接看代码。

每个时钟周期,将最新的拨码开关输入赋值给LED指示灯。

module at7(input sys_clk_i, //外部输入50MHz时钟信号input ext_rst_n, //外部输入复位信号,低电平有效input[7:0] switch, //8个拨码开关输入,ON -- 低电平;OFF -- 高电平output reg[7:0] led //8个LED指示灯亮灭控制);//-------------------------------------always @(posedge sys_clk_i or negedge ext_rst_n)if(!ext_rst_n) led <= 8'd0;else led <= switch;endmodule如图5.2所示,将at7_ex02工程文件夹下生成的at7.bit文件烧录到AT7开发板中,然后拨动任何一个拨码开关,可以看到对应的LED亮灭状态会相应变化。

单片机原理及接口技术(C51编程)(第2版)-习题答案汇总

单片机答案第1章思考题及习题1参考答案一、填空1. 除了单片机这一名称之外,单片机还可称为或。

答:微控制器,嵌入式控制器。

2。

单片机与普通微型计算机的不同之处在于其将、、和三部分,通过内部连接在一起,集成于一块芯片上。

答:CPU、存储器、I/O 口、总线3. AT89S51单片机工作频率上限为 MHz.答:24MHz。

4。

专用单片机已使系统结构最简化、软硬件资源利用最优化,从而大大降低和提高 .答:成本,可靠性。

二、单选1。

单片机内部数据之所以用二进制形式表示,主要是A.为了编程方便B.受器件的物理性能限制C.为了通用性D.为了提高运算速度答:B2. 在家用电器中使用单片机应属于微计算机的。

A.辅助设计应用B.测量、控制应用C.数值计算应用D.数据处理应用答: B3. 下面的哪一项应用,不属于单片机的应用范围。

A.工业控制 B.家用电器的控制 C.数据库管理 D.汽车电子设备答:C三、判断对错1. STC系列单片机是8051内核的单片机。

对12。

AT89S52与AT89S51相比,片内多出了4KB的Flash程序存储器、128B的RAM、1个中断源、1个定时器(且具有捕捉功能)。

对3. 单片机是一种CPU.错4。

AT89S52单片机是微处理器。

错5. AT89S51片内的Flash程序存储器可在线写入(ISP),而AT89C52则不能。

对6. 为AT89C51单片机设计的应用系统板,可将芯片AT89C51直接用芯片AT89S51替换。

对7. 为AT89S51单片机设计的应用系统板,可将芯片AT89S51直接用芯片AT89S52替换。

对8. 单片机的功能侧重于测量和控制,而复杂的数字信号处理运算及高速的测控功能则是DSP的长处。

对第2章思考题及习题2参考答案一、填空1. 在AT89S51单片机中,如果采用6MHz晶振,一个机器周期为。

答:2µs2. AT89S51单片机的机器周期等于个时钟振荡周期。

单片机原理及接口技术智慧树知到答案章节测试2023年山东第一医科大学

第一章测试1.在MCS-51单片机中,()是程序存储器。

A:ROMB:EPROMC:RAMD:EEPROM答案:ABD2.微型计算机一般由()组成的。

A:输入和输出设备B:存储器C:控制器D:运算器答案:ABCD3.单片机在一块电路芯片上集成了()等主要计算机部件。

A:定时器/计数器B:输入/输出(I/O)接口电路C:中央处理器(CPU)D:数据存储器(RAM)和程序存储器(ROM)答案:ABCD4.我们所说的计算机实质上是计算机的硬件系统与软件系统的总称。

( )A:对B:错答案:A5.单片机的CPU从功能上可分为运算器和存储器。

( )A:错B:对答案:A6.MCS-51单片机是高档16位单片机。

( )A:对B:错答案:B7.MCS-51的产品8051与8031的区别是8031片内无ROM。

( )A:对B:错答案:A8.MCS-51的程序存储器只能用来存放程序。

( )A:错B:对答案:A9.MCS-51是微处理器。

( )A:对B:错答案:B10.MCS-51单片机的片内存储器称为程序存储器。

( )A:对B:错答案:B第二章测试1.下列关于89C51系列单片机的省电方式的说法,错误的是:( )A:在掉电方式中,时钟电路不停止工作。

B:通常掉电方式比空闲方式更省电。

C:分为空闲方式和掉电方式。

D:在空闲方式中,CPU停止工作,许多外设都继续工作。

答案:A2.下列关于89C51系列单片机的存储器寻址指令的说法中正确的是:( )A:MOVC指令可以访问片内RAMB:MOVC指令可以访问片外ROMC:MOV指令可以访问片内ROMD:MOVX指令可以访问片外ROM答案:B3.下列特殊寄存器的复位状态描述中,错误的是:( )A:TL0 00HB:SBUF 不定C:ACC 00HD:SP 70H答案:D4.89C51系列单片机的运算器包括:( )A:ROMB:ALUC:寄存器BD:两个暂存器答案:BCD5.下列关于89C51系列单片机的程序计数器PC的描述正确的是:( )A:内容决定程序执行的流向B:内容是正在执行的指令地址C:可对64KB的ROM直接寻址D:由PCH和PCL组成PC答案:ACD6.89C51单片机拥有片内4kB程序存储器Flash ROM(4KB)用以存放程序、一些原始数据和表格。

STM8S系列单片机原理与应用(潘永雄)第1-5章章 (5)

iret ; 中断入口地址表

segment 'vectit' dc.l {$82000000+main} 入口地址表

; reset [注9]中断

第5章 汇编语言程序设计

dc.l {$82000000+NonHandledInterrupt} dc.l {$82000000+NonHandledInterrupt} dc.l {$82000000+NonHandledInterrupt} dc.l {$82000000+NonHandledInterrupt} dc.l {$82000000+NonHandledInterrupt} dc.l {$82000000+NonHandledInterrupt} dc.l {$82000000+NonHandledInterrupt} dc.l {$82000000+NonHandledInterrupt} dc.l {$82000000+NonHandledInterrupt} dc.l {$82000000+NonHandledInterrupt}

ram0_end.b EQU $ram0_segment_end

ldw X,#ram0_start

clear_ram0.l

clr (X)

incw X

cpw X,#ram0_end

第5章 汇编语言程序设计

jrule clear_ram0

#endif

#ifdef RAM1

; [注6] RAM存储区0100H

在STM8S中,复位后将从复位中断逻辑指示的地址单 元(可以是ROM、EEPROM,甚至是RAM)取出并执行第一 条指令。第一条指令在ROM存储区中的存放位置并没有限 制,将第一条指令所在存储单元的地址填入复位中断入口 地址表中。

知道网课《ARM体系结构与程序设计(齐鲁师范学院)》课后章节测试答案

【单选题】(2分)

下面对CM3中断和异常定义描述正确的是()。

A.

CM3外部中断属于内核范畴

B.

CM3的所有异常和中断的优先级都是可以设置的。

C.

一旦中断请求撤销,其对应的悬起标志也会被撤销

D.

SYSTick定时器捆绑在NVIC中

4

【单选题】(2分)

复位中断的向量名为()。

A.

SVC_Handler

A.

16

B.

4

C.

8

D.

2

6

【判断题】(2分)

开漏模式下,输出寄存器上的0将激活N-MOS,输出1将端口置为高阻态。()

A.

错

B.

对

7

【判断题】(2分)

模拟输入时,施密特触发器被禁止。()

A.

对

B.

错

8

【判断题】(2分)

STM32F107中可以把复用功能重新映射到其他管脚上。()

A.

错

B.

对

第四章测试

A.

对

B.

错

第六章测试

1

【单选题】(2分)

下面不属于IWDG的特点的是()。

A.

专用的低速时钟驱动

B.

寄存器有保护

C.

看门狗被激活后,计数器计数到0产生复位

D.

自由运行的递增计数器

2

【单选题】(2分)

开启IWDG需要向键值寄存器写入()。

A.

0xAAAA

B.

0x1111

C.

0xCCCC

D.

0x0000

A.

对B.Biblioteka 错第二章测试1

【单选题】(2分)

操作系统第5章习题

缺页 缺 缺 缺 缺 缺 缺 缺

21 3 4 41 3 3 24 1 1 02 4 4

缺缺

02 1 3 0

1

02 1 3 3

2

0211

3

022

4

00

缺页 缺 缺 缺 缺

24 0 21 3 4 34 0 21 3 4 13 4 02 1 3 21 3 40 2 1 02 1 34 0 2

缺 缺 缺缺 缺 缺

置换算法的好坏将直接映像到系统的性能,不适当的算法可 能会导致进程发生抖动,即刚被换出的页面很快又被访问 ,需要重新调入,为此,又需要选一页调出;而此刚被换 出的页,很快又要被访问,因而又需要将它调入,如此频 繁的更换页面,进程发生了抖动。

一个好的页面置换算法,应具有较低的页面更换频率。从理 论上讲,应将那些以后不在访问的页面换出,或把哪些在 较长时间内不会再访问的页面调出。

✓ 在动态分区存储管理中采用_移__动____技术可集中分散的

空闲区。

✓ 动、_态最_分_先_区_存__储和管_理_最_中_佳_常_用_。的分配主存的算法有__最__差___

页式管理

【例】分页系统中页面是为( )的。 A 用户所感知 B 操作系统所感知 C 编译系统所感知 D 连接装配程序所感知 【答案】B

【例】在可变式分区管理中,采用拼接技术的目的是()。 A 合并空闲区 B 合并分配区 C 增加主存容量 D 便于地址转换 【答案】A

【例】以动态分区式内存管理中,倾向于优先使用低址部分 空闲区的算法是();

能使内存空间中空闲区分布较均匀的算法是(); 每次分配时把既能满足要求,又是最小的空闲区分配给进程

【例】请求分页系统中一个进程访问页面的次序为:0,2, 1,3,0,2,4,0,2,1,3,4,利用FIFO算法,当 进程使用3个页框时缺页()次,使用4个页框时缺页() 次(缺页次数含初始调入次数)

第5章stm32单片机外部中断ppt课件

5.2.3 中断控制器

ICER[2]:全称Interrupt Clear-Enable Registers,是 一个中断清除使能寄存器组。

该寄存器组与ISER寄存器功能相反,用来清除某个 中断的使能位。由于NVIC的这些寄存器都是写1有 效的,写0是无效的。设置一组ICER 寄存器来清除 相应中断使能位。

5.2.1 中断源

ARM Coetex-M3内核共支持256个中断,其中16 个内部中断,240个外部中断和可编程的256级中断优 先级的设置。STM32目前支持的中断共84个(16个内 部+68个外部),还有16级可编程的中断优先级的设 置,仅使用中断优先级设置8bit中的高4位。

5.2.2 中断向量:表5-1 给出STM32F103中断向量表

5.3.2 中断优先级控制

响应优先级可设置为0到15级。 判断两个中断的优先级时: (1)先看抢占优先级的高低; (2)再看响应优先级的高低; (3)看中断通道向量地址。 一个系统使用一个组别就完全可以满足需要,在使 用一个组别后不要在系统中再改动组别。

5.3.2 中断优先级控制

假定设置中断优先级为组2,然后设置: 中断3(RTC中断)的抢占优先级为2,响应优先级为1。 中断6(外部中断0)的抢占优先级为3,响应优先级为0。 中断7(外部中断1)的抢占优先级为2,响应优先级为0。 求这3个中断的优先级顺序? 上面例子中的中断3和中断7都可以打断中断6 的中断。而中 断7和中断3却不可以相互打断(这是因为他们的抢占优先级 是相同的)。

5.2.3 中断控制器

与NVIC相关的寄存器 在“stm32f10x_map.h” 文件中定义了一个结构 体,结构体的内容如下

STM32F103系列单片机 的中断系统在这些寄存 器的控制下有序执行。 了解这些中断寄存器的 含义,才能更好的理解 STM32单片机中断系统 的工作原理

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

21

2. 主计数寄存器TIM

位 字段 数值 说明

15-0

TIM

0000h主计数寄存器 FFFFh

3. 主周期寄存器PRD

位 15-10 字段 PRD 数值 说明

0000h- 当TIM必须重新装入时,将 FFFFh PRD的内容拷贝到TIM中

22

4. 定时器控制寄存器TCR

位 15 字段 IDLEEN 数值 0 1 0 1 0 1 说明

14

INTEXT

13

ERRTIM

12-11 FUNC 10 TLB 0 1

省电使能位 定时器不能处于省电状态 如果省电状态寄存器中的PERIS=1,定时 器进入省电状态 时钟源从内部切换到外部标志位 定时器没有准备好使用外部时钟源 定时器准备使用外部时钟源 定时器错误标志, 正常 出错 定时器工作模式选择位 定时器装载位, TIM,PSC不重新装载 23

20

ARB

10b

(TDDR 1) ( PRD 1)

1. 定时器预定标寄存器PRSC

位 15-10 9-6

5-4 3-0

字段 Reserved PSC

Reserved TDDR

数值 0h-fh

0h-fh

说明 保留 预定标计数寄存器

保留 当PSC重新装入时,将 TDDR的内容拷贝到PSC中

PLL MULT 输入频率 输出频率 PLL DIV 1

例:外部晶振提供频率:12MHz,要使DSP的CPU工作在 72MHz频率下,则PLL MULT 与PLL DIV如何设置?CLKMD=? PLL MULT=6 PLL DIV=0 CLKMD=2310H PLL MULT=12 PLL DIV=1 CLKMD=2630H PLL MULT=18 PLL DIV=2

● C55x片内外设 ● C55x的芯片支持库

2

5.1 C55x片内外设与芯片支持库简介

C55x的片内外设分为如下几类。

1.时钟与定时器

时钟与定时器包括时钟产生器、通用定时器、实时时钟 以及看门狗定时器等。 2.外部设备连接接口

外部设备连接接口包括外部存储器连接接口、主机接口等。

3

3.信号采集 信号采集类的外设包括采集模拟信号的模/数转换器和提 供数字信号输入、输出功能的通用输入/输出接口。 4.通信接口 C55x处理器为用户提供了多种类型的通信接口,包括多 通道缓冲串口、I2C接口、异步串口、USB接口以及多媒体卡 /SD卡接口等。 5.其他外设 其他外设包括DMA控制器、指令流水线等,这些外设主 要用来辅助CPU工作,提高DSP的工作效率。

9

5.2.4 使用方法

通过对时钟模式寄存器的操作,可以根据需要设定时 钟发生器的工作模式和输出频率,在设置过程中除了工作 模式、分频值和倍频值以外,还要注意其他因素对PLL的 影响。

1.省电(IDLE)

为了降低功耗,可以加载Idle配置,使DSP的时钟发生 器进入Idle模式 当时钟发生器处于Idle模式时,输出时钟停止,引脚被 拉为高电平。 当时钟发生器退出省电状态时,PLL自动切换到旁路模 式,进行跟踪锁定,锁定后返回到锁定模式,时钟模式 寄存器中与省电有关的位是IAI。

4

5.2

时钟发生器

C1

X1 Crystal

X2/CLKIN

5.2.1 时钟模式寄存器

CLKDIV DSP时钟 发生器 CPU 时钟 ÷

C2

CLKIN

CLKOUT

CPU、外设 其他器件 数字锁相环 DPLL 时钟模式寄存 器CLKMD 时钟分 频器

5

5.2.1 时钟模式寄存器

RSV D IAI IO B TEST PLL MUL L PLL DIV PLL BYPASS BREA ENABLE DIV KLN LOCK

取PLL DIV=0,PLL MULT=12,即:

D6D5(PLL DIV)=00b,D11~D7(PLL MULT)=12=01100b。

时钟模式寄存器(CLKMD)的其它位均取为0。 (2)汇编语言实现: mov #0000 01100 00 1 0000b,port(#1c00h) 或 mov #0610h,port(#1c00h) ; 1c00h为时钟模式寄存器(CLKMD)的地址。

11

例,TMS320VC5509A系统的晶体振荡器频率为12MHz。通过 设置DPLL,使系统时钟时钟频率为144MHz。 (1)原理: 使DPLL工作在锁定模式:D4(PLL ENABLE)=1b。

PLL MULT 144MHz= 12MHz PLL DIV 1

PLL MULT =12 即: PLL DIV 1

14

片上外设支持库(CSL)

2.为什么要设计CSL?

DSP片上外设种类及其应用日趋复杂 提供一组标准的方法用于访问和控制片上外设

免除用户编写配置和控制片上外设所必需的定 义和代码

15

片上外设支持库(CSL)

3.CSL的特点

片上外设编程的标准协议:定义一组标准的APIs: 函数、数据类型、宏;

定时器控制寄存器TCR (续) 9 8 SOFT FREE 00 01 10 11 在调试时遇到断点定时器的处理方法

7-6

PWID

5

ARB

4

TSS

0 1 0 1

3

C/P

定时器输出脉冲的宽度 1个CPU时钟周期 2个CPU时钟周期 4个CPU时钟周期 8个CPU时钟周期 自动重装控制位 定时器停止状态位, 启动; 停止 定时器输出时钟/脉冲选择, 输出脉冲; 输出时钟

在C程序(通常在初 始化部分)中执行该 函数,完成对DPLL 的设置

也可利用PLL_setFreq (Uint16 mul, Uint16 div)函数直接设置DPLL

13

片上外设支持库(CSL)

1. 什么是CSL?

已为C6000和C5000系列DSP设计了各自的CSL库 用于配置、控制和管理DSP片上外设 CSL库函数大多数是用C语言编写的,并已对代 码的大小和速度进行了优化 CSL库是可裁剪的:即只有被使用的CSL模块才 会包含进应用程序中 CSL库是可扩展的:每个片上外设的API相互独 立,增加新的API,对其他片上外设没有影响

10

2.DSP复位 在DSP复位期间和复位之后,PLL工作于旁路模式, 输出的时钟频率由CLKMD引脚上的电平确定。 如果CLKMD引脚为低电平,输出频率等于输入频率; 如果CLKMD引脚为高电平,输出频率等于输入频率跟踪锁定之后,由于其他原因使其 输出时钟发生偏移,即失锁。出现失锁现象后,PLL的动 作由时钟模式寄存器中的IOB确定

CLKMD=2950H

8

5.2.3 CLKOUT输出

CPU时钟也可以通过一个时钟分频器提供CLKOUT信号, CLKOUT的频率由系统寄存器(SYSR)中的CLKDIV确定: 如果CLKDIV=000b, CLKOUT的频率等于CPU时钟的频率。 如果CLKDIV=001b, CLKOUT的频率等于CPU时钟的频率的1/2 如果CLKDIV=010b, CLKOUT的频率等于CPU时钟的频率的1/3 如果CLKDIV=011b, CLKOUT的频率等于CPU时钟的频率的1/4 如果CLKDIV=100b, CLKOUT的频率等于CPU时钟的频率的1/5 如果CLKDIV=101b, CLKOUT的频率等于CPU时钟的频率的1/6 如果CLKDIV=110b, CLKOUT的频率等于CPU时钟的频率的1/7 如果CLKDIV=111b, CLKOUT的频率等于CPU时钟的频率的1/8

17

5.2.6 时钟发生器的调试

(3)在没有进行软件设置的情况下,DSP在复位 后CLKOUT的输出直接受CLKMD控制

当CLKMD为高,CLKOUT的输出频率将等于CLKIN的频 率, CLKMD为低,则CLKOUT输出将等于CLKIN的频率的1/2。

(4)如果以上步骤运行正常,则利用软件设置 CLKMD寄存器,使时钟产生器工作于PLL锁相环模 式下,此时再检测CLKOUT信号,查看锁相环是否 正常工作。

第5章 TMS320C55x的片内集成外 设开发及测试 内容提要

C55x外设完成的功能包括采集原始数据、输出 处理结果,还可以通过外设来控制外部其他设备的 工作状态。 C55x的片内外设分为如下几类。 1.时钟与定时器 2.外部设备连接接口 3.信号采集 4.通信接口 5.其他外设

1

第5章 TMS320C55x的片内集成外 设开发及测试 知识要点

– BYPASSDIV=01,输出时钟频率=输入信号频率/2, 即2分频 CLKMD=0004 h

– BYPASSDIV=1x,输出时钟频率=输入信号频率/4, 即4分频 CLKMD=0008 h

7

5.2.2

工作模式

2.锁定模式(LOCK) PLL ENABLE=1,输出的时钟频率由下面公式确定:

18

5.3 通用定时器

要求掌握:

– 定时器的工作原理 – 定时器的设置 – 中断的处理

19

5.3.1 结构框图与工作原理

CPU时钟 MUX 高阻

FUNC位决定 TIN/TOUT引脚功能

4-bit预定标计数器 TDDR PSC 11b 00b TIN/TOUT pin 01b 16-bit主计数器 PRD 向CPU发送的 中断请求 向DMA控制器的 输入时钟频率 同步事件 TINT频率 TIM DATOUT bit TCR

15

14

13

12

11~ 7

6~5

4

3~2

1

0

PLL失锁标志 处理失锁: 旁路下分频值 退出Idle后 PLL 锁定模式 锁定模式 使能或关闭PLL 锁定模式 0:PLL已经失锁 0:不中断PLL, 00 一分频 是否重锁: 下的PLL 下的PLL 关闭PLL 0 标志 1:锁定状态 PLL继续输出时钟 必须为0 01 二分频 0:Idle之前状态 倍频值 分频值,使能PLL 1 0 :旁路 1:切换到旁路模式 10或11 或有对CLKMD 四分频 1: PLL重锁 0~3 ,0~31 1 :锁定 寄存器的写操作 重新开始PLL锁相过程