时钟分频器

分频器

第36卷第2期信息化研究Vo l.36 No. 2 2010年2月I nfo r m a t iza t ion R e s ea r ch Feb. 2010 基于FPGA 的任意数值分频器的设计 周殿凤,康素成,王俊华 (盐城师范学院物理科学与电子技术学院,江苏省盐城市224002 ) 摘要:介绍了基于FPG A 的任意分频系数的分频器的设计,该分频器能实现分频系数和占空比均可以调节的3 类分频:整数分频、小数分频和分数分频。所有分频均通过VHDL 语言进行了编译并且给出了仿真图。本设计中的分频器没有竞争冒险,可移植性强,占用的FPG A资源少。本设计在A l2 te ra 公司的Cyc l o neⅡ系列EP2C35 型FPG A芯片中完全可实现,结果表明设计是正确和可行的。由于分频器应用非常广泛,故本设计具有很强的实用价值。 关键词: FPG A; VHDL;分频器 中图分类号: TP277 0 引言 FPG A 作为未来数字系统的 3 大基石( FPG A、D SP、CPU ) 之一, 成为目前硬件设计研究的重点[ 1 ] 。 在数字系统的设计中,设计人员会遇到各种形式的分频需求,如偶数分频、奇数分频、半整数分频、小数分频率的1 / 10。从图1可看出当j = 5 = m/ 2时输出时钟占空比为50 %。 图110分频器波形图 和分数分频等。在某些设计中,系统不仅对频率有要求,而且对占空比也有严格的要求。由计数器或计数器的级联构成各种形式的偶数分频及非等占空比的奇数分频实现起来较为简单, 但对半整数分频及等占空比的奇数分频实现较为困难,小数分频和分数分频更 占空比为50 %的奇数分频实现起来较为困难,实现的方法较多,文中介绍了一种占用资源较少的方法。假设要实现占空比为50 %的m = 2 n+ 1 分频, 选择两个2 n+ 1进制计数器控制两个中间时钟c lk1 和c l k2 , 1 号计数器在输入时钟c l k的上升沿计数, 2 号在c l k 的 困难[ 2 ] 。为了解决这一问题,本文首先分析了各种分下降沿计数。当计数器1 输出为0 ~n - 1 时c l k1 为 频器的设计方法,然后将其综合起来成为一个通用分频器。通过分析分频器的原理,探索出了一套简单明了的设计方法,设计了一个任意数值通用分频器,该分频器没有毛刺且占用的逻辑资源较少。 1 整数分频器 偶数分频器的设计较为简单,可以利用计数器实1 ,输出为n ~2 n 时c l k1为0 且计数器1 输出为 2 n时计数器1清0 , 如此循环下去; 当计数器2输出为0 ~n - 1 时c l k2为1 ,输出为n ~2 n 时c l k2为0且计数器2输出为 2 n时计数器 2 清0 ,如此循环下去。可见2种计数器实现方法一样,只是翻转的边沿不一样,最终输出的时钟c l kou t = c l k1 + c l k2。占空比为50 %的奇数分频仿真图见图2 ,图中m = 9 ,因此是9 分频电路, 现[ 3 ] 。假设要实现m = 2 n分频, 当计数器的值为0 ~通过预置值m 可以非常方便的对分频系数进行设置 j - 1时,输出时钟为 1 ,计数器的值为j~2 n- 1 时,输出时钟为0 ,在计数器值为2 n - 1 时复位计数器,如此循环下去,即可实现占空比为j/2 n的分频, m 和j都是预置数, j用于调节占空比, m 调节分频系数。m 的值不同,分频系数也就不同, 如果预置数m 是奇数则可实现占空比不等于50 %的奇数分频。图1 中m 取值10,故实现的是10 分频, 输出时钟频率是输入时钟频收稿日期: 2009212 220; 修回日期: 2010201 209。 基金项目:江苏省高校自然科学基金资助项目( 08KJD140005) ;盐城师范学院校级基金资助项目( 09YCK L 016) 。而不需要重新编程。 图29分频器波形图 2小数分频器 小数分频器是通过可变分频和多次平均的方法得到的[ 4 25 ] 。假设要进行m . n分频( m 、n都是整数, 且n < 10 ),因为只有一位小数,所以总共要进行1 0次分 ·59·

电子分频器要注意的几点问题及故障排除

电子分频器要注意的几点问题及故障排除网络摘编 电子分频器: 电子分频器的主要功能当然就是给不同的音箱分配好不同的工作频率了,当然还有保护音箱的功能,下面说下调整电子分频器时需要注意的几点问题及故障排除: 1、分频点: 在一个2分频的音响系统中,一般情况下分频点放在130Hz附近比较合适,但很多情况下,对分频点的调整实际上不是取决于低音音箱,而是要看中高音或全频音箱。因为低音音箱在300Hz以下工作都可以,但有些中高音和全频音箱由于扬声器口径太小,动态范围不够大,必须在200Hz以上工作才能保证它们的安全,如果此时分频点分在130Hz附近,那么这些中高音音箱工作起来就很危险了,因此在效果和安全当中还是要找一个平衡点。我觉得双15寸的全频主音箱最好不要经过电子分频器;单15寸的主音箱可灵活运用;而单12寸以下的主音箱最好要通过电子分频器,至少在180Hz以上工作才安全。 2、音量控制: 不管是输入电平还是输出电平,调整的时候都要有一个度,不要开的太大。如果是电子分频器上的各个音量旋钮都开到很大了,系统的声压还不够,那就要调整电子分频器前面设备的信号电平或者调整电子分频器下面功放的电平和音量开关了。 3、×10按钮: 有一些电子分频器上有一个: ×10的按钮,大家注意不要轻易按下它。 例如我们的分频点调整在200Hz的话,按下此按钮200×10就变成2000Hz 了,因此除非是需要,否则一般不要按下此按钮。

4、低音模式: 有些电子分频器后面板有一个低音模式的选择,它可以把2路立体声信号混合成1路单声道信号,这样可以减少低音音箱之间的声干涉。大家可以适当利用下。 当然要是低音分频点分的较高,那么低音音箱发出的声音就会有一定的指向性了,此时还是要在2路立体声信号的状态下工作较好。 5、立体声工作模式和单声道工作模式: 目前我们使用的大多数电子分频器都是2分频的居多,考虑到灵活性和多功能性,这些电子分频器的后面板一般会有一个立体声和单声道的工作模式转换开关,如果把此开关放在单声道工作模式下,那么此时这台电子分频器就从一台双通道2分频的电子分频器变成了一台单通道3分频的电子分频器了。因此除非必要,否则不要轻易转换此工作开关,要不然电子分频器后面信号输出口所输出的频率信号就会大不一样了!轻者恶化了音质,重者还会损坏设备! 6、系统中低音信号的输出和中高音信号的输出一定不要搞混了,否则高音信号给了低音音箱,低音信号给了高音音箱,那样南辕北辙的做法音响系统中就真的没有声音出来了,因为频率不对呀!搞不好还会烧坏音箱呢! 电子分频器故障例子: 1、05年朋友在长沙做了一个大型的酒吧,音响系统中共使用了单12寸全频主音箱16只,双18寸重低音音箱22只,还有其它20多只辅助音箱。但开业几天后发现主音箱的单12寸的喇叭坏了2只,开始那里的技术人员以为是正常损坏,更换了2只新的喇叭了事,但后来一个星期内陆陆续续的又坏了6只12寸的全频喇叭,这样就很不正常了,而且除了12寸主音箱发生故障外别的音箱都没有问题。后来我去帮忙检查了下系统,发现那里的电子分频器分的频率太低,我把分频器的分频点从130Hz调高到了230Hz,这样问题就解决了,而且低音效果也比以前好了很多。其实道理很简单: 这个系统中由于要兼顾人声演出,所以采用了对人声表现较好的12寸全频主音箱,开始时电子分频器的分频点在130Hz,这是什么概念呢?就是说系统中

分频器设计实验报告

竭诚为您提供优质文档/双击可除分频器设计实验报告 篇一:n分频器分析与设计 一、实验目的 掌握74190/74191计数器的功能,设计可编程计数器和n分频器,设计(n-1/2)计数器、分频器。 二、实验原理 分频是对输入信号频率分频。1、cD4017逻辑功能 2、74190/74191逻辑功能 3、集成计数器级联 当所需计数器模数超过所选计数器最大计数状态时,需要采取多片计数器级联。方法分为异步级联和同步级联。4、集成计数器的编程 在集成计数器的时序基础上,外加逻辑门电路等,反馈集成计数器的附加功能端,达到改变计数器时序的目的。可采用复位编程和置数编程两种。5、多片74190/74191计数器级联 可根据具体计数需求和增减需求,选用74190或74191,

选择不同功能、同步或异步设计等。 6、74190/74191计数器编程 由于没有复位端,因此只能使用置数编程,置数端置为0即可异步置数。可根据需求设计n进制加法或减法计数器。 n与译码逻辑功能如下。 7、74191组成(n-1/2)分频器电路如下图: u3 计数器的两个循环中,一个循环在cp的上升沿翻转;另一个是在cp的下降沿翻转,使计数器的进制减少1/2,达到(n-1/2)分频。 三、实验仪器 1、直流稳压电源1台 2、信号发生器1台 3、数字万用表1台 4、实验箱1台 5、示波器1台 四、仿真过程 1、按照cD4017和74191功能表验证其功能。 2、74191组成可编程计数器 (1)构成8421bcD十进制加法计数器,通过实验验证正确性,列出时序表。设计图如下 仿真波形如下 (2)构成8421bcD十进制减法计数器,通过实验验证正确性,列出时序表。设计图如下: 仿真波形如下

音响分频器原理

音响分频器原理 音箱分频器原理浅释【二分频器样品展示】 首先大家要明白如下道理: 电容器:当电容器两端加载电压的时候,两端就会感应并存储电荷,所以电容器是一个临时的储存电能的器件,当电容器两端电压变化很快的时候【即高频】,由于电压变化太快导致两端感应电荷也同步地变化,也就等效于有电流流过电容器,而当频率很低的时候,电容器两端电压变化很慢,近似没有电流流过。所以说电容器是阻低频通高频的。 线圈:当有电流通过的时候,如果电流的大小和方向发生变化,线圈会产生感应电动势【电压】,它与原来的电压方向相反,即线圈是阻碍变化的电流通过的,当电流变化很快的时候,线圈产生的负电压会很大【根据公式伏电压和频率成正比】,所以线圈是阻高频通低频的。【因为频率很低的时候近似负电压很低或为0,即可以让低频电流顺利通过】

所以音箱分频器采用了上图结构,具体分析: 连接高音喇叭的电路:让电流先流过电容器,阻止低频,让高频通过,并且喇叭与一个线圈并联,让线圈产生负电压,那么这个电压对于高音喇叭来说正好是一个电压补偿,于是可以近似地逼真还原声音电流。 连接低音喇叭电路:电流先流过线圈,这样高频部分被阻止,而低频段由于线圈基本没有阻碍作用而顺利通过,同样,低音喇叭并联了一个电容器,就是利用电容器在高频的时候产生一个电压来补偿损失的电压,道理和高音喇叭端是一样的。 可以看出,分频器充分利用的电容器和线圈的特性达到分频。但是,线圈和电容器在各自阻碍的频率段内终究还是消耗了电压的,所以电路分频器会损失一定的声音,其补偿措施也有很多,由于笔者知识不够,难以说的很清楚。而电子分频就解决了这个问题,当声音输入到功放之前就先分频,然后对不同的频段使用专门的放大电路进行放大,这样的话声音失真小,还原逼真。但是电路复杂,造价昂贵。 下面是一个常用的电路分频器: 下面我们再看两个二分频器:

15分频器

library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity anyodd_div is generic(n:integer:=15); port(clk:in std_logic; clkdiv:out std_logic); end; architecture one of anyodd_div is signal cnt1:integer:=0; signal cnt2:integer:=0; signal clk_temp1:std_logic; signal clk_temp2:std_logic; begin ------------------------------- process(clk) begin if clk'event and clk='1'then if cnt1=n-1 then cnt1<=0; else cnt1<=cnt1+1; end if; end if; end process; --------------------------- process(clk) begin if clk'event and clk='0'then if cnt2=n-1 then cnt2<=0; else cnt2<=cnt2+1; end if; end if; end process; ----------------------------- process(clk) begin if clk'event and clk='1'then if cnt1=0 then clk_temp1<='1'; elsif cnt1<=(n-1)/2 then clk_temp1<='0'; end if; end if;

分频器设计_可控型

现代科技的发展对信号源提出了越来越高的要求,要求信号源的频带宽、频率分辨率高、频率稳定度高、相位噪声和杂散很低、能程控等.频率合成技术是产生大量高精度频率信号的主要技术,频率合成器是一种相位锁定装置,是通讯、雷达、仪器仪表、高速计算机和导航设备中的一个重要组成部分。频率合成器是可由一个工作范围在G地范围的锁相环构成.在高频范围内工作的锁相环是整个系统中功耗最大的部分之一,因此对锁相环的低功耗研究对降低整个系统的功率损耗有着重要的意义.分数分频频率合成器则是近年来出现的一种新技术,它与传统的整数分频频率合成器相比具有频率分辨率高、相位噪声低等优点。前置分频器位于高频锁相环的反馈部分.由于工作频率很高,前置分频器也是锁相环中功耗最大的部分之一。低功耗的前置分频器设计可以很大程度上降低整个锁相环的功率损耗. 目录 摘要 ................................................................................................................ 错误!未定义书签。Abstract ........................................................................................................... 错误!未定义书签。目录 .. (1) 引言 (1) 一、分频器设计 (2) 1.1、分频器的系统介绍 (2) 1.2、前置放大器的设计 (3) 二、前置分频器单元结构 (3) 2.1、TSPC结构 (3) 2.2、传统结构 (4) 2.3、转换器 (5) 三、小数分频器中预分频器的设计 (5) 3.1、小数分频器相位杂散的分析 (5) 3.2、可编程预分频器结构 (6) 结论 (6) 参考文献 (8) 引言 所谓频率合成,又称频率综合,简称频综,是由一个(或几个)具有低相位噪

一文解析主动分频器和被动分频器的优缺点

一文解析主动分频器和被动分频器的优缺点 汽车音响简单的来说区分主动和被动的区别在于分频处理在功率放大之前或之后,分频在功率放大之前的称为主动,而在功放的输出端进行分频处理的称为被动分频。主动和被动都有各自的优点,声音也都有自己的优点和缺点,需要根据自己需要做选择,而不是听别人说主动好就去玩主动。下面是这两种分频的优缺点。 本文首先介绍了分频器的分类及电子分频器的工作原理,其次介绍了主动分频器的优缺点,最后介绍了被动分频器的优缺点,具体的跟随小编一起来了解一下。 分频器的分类分频器有两大类:一类是被动分频器(PassiVe Crossover),亦称功率分频器;另一类是主动分频器(Active Crossover),亦称电子分频器。 主动分频器的工作原理(电子分频器)电子分频器是利用各类有源滤波器(高通、低通、带通)将全频域的音频信号分成不同的频段,有源滤波器是由无源RC滤波网络和由运算放大器接成的跟随器组成,衰减特性随着RC阶数的增加而增强(每增加一阶,衰减斜率增加-6db/out)。 电子分频方式使功率放大器与扬声器之间只有功率传输线。而没有影响音质的其他环节,从而降低了失真,提高了功率放大器对扬声器的阻尼系数,由于电子分频器的负载是功率放大器的输入,阻抗高而且稳定,所以能很容易的调整分频点和控制分频精度,而且由于电子分频器的每一频段的带宽较窄,使非线性畸变引起的高次谐波受到抑制,降低总谐波失真和互调失真,电子分频器克服了功率分频器中存在的缺点,但增加了成本和系统调试的难度,因此多被用于专业场合。 1、二分频电子分频器的工作原理图 7-32所示为采用滤波运算综合法的二分频电子分频器框图,其基本原理是用一组高通或低通滤波器滤除相应频段的信号,然后将此信号反相后,与全屏输入信号相加,得到另一频段的信号。

基于VHDL的分频器设计[开题报告]

开题报告 电子信息工程 基于VHDL的分频器设计

三、课题研究的方法及措施 由于本课题所设计的分频器基于EDA技术,应用VHDL硬件语言设计完成的,因此选择合适的硬件解决原理对分频器性能至关重要的,为了满足不同系统功能需求的分频,本课题将阐述不同原理,不同分频器,同种分频不同原理的设计方案。 占空比可控的整数分设计方案,原理为计数器为带预置数的计数器,其设计的特殊之处在于:可以根据需要,调整数据的位宽,而且计数的初始值是从l开始的,此处计数初始值的设定是设计的一个创新,这样做的目的是为了配合后面比较器的工作,计数器的输出数据作为比较器的输入,比较器的另一输入作为控制端,控制高低电平的比例,从而达到占空比可调的目的。原理图如图1所示。 图1 占空比可控的原理图部分 小数分频的基本原理是采用脉冲吞吐计数器和锁相环技术先设计两个不同分频比的整数分频器,然后通过控制单位时间内两种分频比出现的不同次数来获得所需要的小数分频值。如设计一个分频系数为lO.1的分频器时。可以将分频器设计成9次10分频,1次11分频这样总的分频值为如式1所示。 F=(9×10+lxl 1)/(9+1)=10.1 (式1) 从这种实现方法的特点可以看出,由于分频器的分频值不断改变.因此分频后得到的信号抖动较大。当分频系数为N-0.5(N为整数)时,可控制扣除脉冲的时间,以使输出成为一个稳定的脉冲频率。而不是一次N分频.一次N-1分频。图2给出了通用小数分频器的电路组成。 图2通用小数分频器的电路组成 改进的小数分频设计方案,将两个整数分频器由一个整数分频器和一个半整数分频器代替,结果在如上分析的两个性能方面都有所提高。利用参数化的设计思想和VHDL描述语言与原理图输入方法相结合的方式,设计并实现了一种抖

小数分频器原理

基于CPLD/FPGA的半整数分频器的设计 在数字逻辑电路设计中,分频器是一种基本电路。通常用来对某个给定频率进行分频,以得到所需的频率。整数分频器的实现非常简单,可采用标准的计数器,也可以采用可编程逻辑器件设计实现。但在某些场合下,时钟源与所需的频率不成整数倍关系,此时可采用小数分频器进行分频。比如:分频系数为2.5、3.5、7.5等半整数分频器。笔者在模拟设计频率计脉冲信号时,就用了半整数分频器这样的电路。由于时钟源信号为50MHz,而电路中需要产生一个20MHz的时钟信号,其分频比为2.5,因此整数分频将不能胜任。为了解决这一问题,笔者利用VIDL硬件描述语言和原理图输入方式,通过MAX+plus II开发软件和ALTERA公司的FLEX系列EPF10K10LC84-4型FPGA方便地完成了半整数分频器电路的设计。 2 小数分频的基本原理 小数分频的基本原理是采用脉冲吞吐计数器和锁相环技术先设计两个不同分频比的整数分频器,然后通过控制单位时间内两种分频比出现的不同次数来获得所需要的小数分频值。如设计一个分频系数为10.1的分频器时,可以将分频器设计成9次10分频,1次11分频,这样总的分频值为: F=(9×10+1×11)/(9+1)=10.1 从这种实现方法的特点可以看出,由于分频器的分频值不断改变,因此分频后得到的信号抖动较大。当分频系数为N-0.5(N为整数)时,可控制扣除脉冲的时间,以使输出成为一个稳定的脉冲频率,而不是一次N分频,一次N-1分频。 3 电路组成 分频系数为N-0.5的分频器电路可由一个异或门、一个模N计数器和一个二分频器组成。在实现时,模N计数器可设计成带预置的计数器,这样可以实现任意分频系数为N-0.5的分频器。图1给出了通用半整数分频器的电路组成。

什么是主动和被动汽车音响电子分频器

什么是主动和被动汽车音响电子分频器 所谓电子分频,就是将分频电路提至放大电路之前的电路拓扑设计,就这么简单。 电子分频不是什么新技术,应用于舞台专业音响器材已很普遍。由于电子分频时信号功率很小,很容易把频率精确分开,完全可以根据喇叭单元的特性进行分频,最大限度发挥喇叭单元的特性,得到最平直、最满意的听音曲线 什么是主动和被动汽车音响电子分频器?为了真实地重放各种节目信号,要求喇叭有尽可能宽和平坦的频率响应,即使从HI-FI用是最低低放频响要求来说,喇叭的重放频率范围也必须达到50~12500HZ。事实上,由于受扬场器结构以及制作工艺的客观限制,目前任何一种扬声器都无法在如此宽的频率范围内很好的工作。每一种扬声器都有它的有效频率范围,只能在一个较窄的范围内很好地工作,倘若扬声器的实际工作频率超出它的有效频率范围,扬声器的失真和指向性指标将明显变坏。为此,人们制造出了适用于不同频率范围的扬声器,如低频扬声器、中频扬声器、高频扬声器等等。 这样,人耳能听到的20HZ~20KHZ这个频率范围的声音就是分别通过低频扬声器、中频扬声器、高频扬声器来分别发出。但是并不能直接把这两种扬声器并联在一起,必需要有一种器件来做一个“频率分配工作”,分频器应运而生,分频器的作用就是把20~20KHZ 的全频带信号分割成不同的频段,再分配到相应的喇叭发声。 当我们在安装汽车音响套装喇叭时,经常会接触到一个器件——电子分频器。它时而被我们隐藏在仪表台下方,时而又被我们藏在车门内饰板内。可能有些朋友便会好奇,这个电子分频器到底是干什么用的?没有电子分频器可以吗?对于大家的疑问,结合各方资料,就简单给大家介绍一下电子分频器! 什么是电子分频器: 从字面上理解,电子分频器的意思就是“区分频率的器材”,其实科学原理也是如此,将音频的弱信号进行分频,然后传输给功放,让其放大音频信号,最后传输给各个扬声器。电子分频器的作用:

分频器的设计2014-1-10 10.29.8

武汉理工大学《微机原理与接口技术》课程设计报告书

学

号:

0121105830129

课 程 设 计

题 学 专 班 姓

目 院 业 级 名

分频信号发生器的分析与设计 自动化学院 电气工程及自动化 电气 1107 班 成涛 陈静 教授

指导教师

2014 年

01 月

09 日

武汉理工大学《微机原理与接口技术》课程设计报告书

课程设计任务书

学生姓名: 指导教师: 题 目: 成涛 专业班级: 电气 1107 班 陈静 教授 工作单位: 自动化学院 分频信号发生器的分析与设计

要求完成的主要任务:(包括课程设计工作量及其技术要求,以及说明书撰 写等具体要求) 1. 设:有一输入方波信号 f0(<1MHz) 。要求输出信号:f1=f0/N,N 通过键盘 输入。 2. 画出简要的硬件原理图,编写程序。 3. 撰写课程设计说明书。 内容包括:摘要、 目录、 正文、 参考文献、 附录 (程 序清单) 。正文部分包括:设计任务及要求、方案比较及论证、软件设计说明(软 件思想,流程,源程序设计及说明等) 、程序调试说明和结果分析、课程设计收 获及心得体会。

时间安排: 12 月 26 日----- 12 月 28 日 查阅资料及方案设计 12 月 29 日----- 01 月 0 2 日 编程 01 月 03 日-----0 1 月 07 日 调试程序 01 月 08 日----- 01 月 09 日 撰写课程设计报告

指导教师签名: 系主任(或责任教师)签名:

年 年

月 月

日 日

分频器的设计

分频器的设计 一、课程设计目的 1.学会使用电路设计与仿真软件工具Hspice,熟练地用网表文件来描述模拟电路,并熟悉应用Hspice内部元件库。通过该实验,掌握Hspice的设计方法,加深对课程知识的感性认识,增强电路设计与综合分析能力。 2.分频器大多选用市售成品,但市场上出售的分频器良莠不齐,质量上乘者多在百元以上,非普通用户所能接受。价格在几十元以下的分频器质量难以保证,实际使用表现平庸。自制分频器可以较少的投入换取较大的收获。 二.内容 分频器-概述 分频器是指使输出信号频率为输入信号频率整数分之一的电子电路。在许多电子设备中如电子钟、频率合成器等,需要各种不同频率的信号协同工作,常用的方法是以稳定度高的晶体振荡器为主振源,通过变换得到所需要的各种频率成分,分频器是一种主要变换手段。早期的分频器多为正弦分频器,随着数字集成电路的发展,脉冲分频器(又称数字分频器)逐渐取代了正弦分频器,即使在输入输出信号均为正弦波时也往往采用模数转换-数字分频-数模转换的方法来实现分频。正弦分频器除在输入信噪比低和频率极高的场合已很少使用。

分频器-作用 分频器是音箱中的“大脑”,对音质的好坏至关重要。功放输出的音乐讯号必须经过分频器中的各滤波元件处理,让各单元特定频率的讯号通过。要科学、合理、严谨地设计好音箱之分频器,才能有效地修饰喇叭单元的不同特性,优化组合,使得各单元扬长避短,淋漓尽致地发挥出各自应有的潜能,使各频段的频响变得平滑、声像相位准确,才能使高、中、低音播放出来的音乐层次分明、合拍,明朗、舒适、宽广、自然的音质效果。 在一个扬声器系统里,人们把箱体、分频电路、扬声器单元称为扬声器系统的三大件,而分频电路对扬声器系统能否高质量地还原电声信号起着极其重要的作用。尤其在中、高频部分,分频电路所起到的作用就更为明显。其作用如下: 合理地分割各单元的工作频段; 合理地进行各单元功率分配; 使各单元之间具有恰当的相位关系以减少各单元在工作中出现的声干涉失真; 利用分频电路的特性以弥补单元在某频段里的声缺陷; 将各频段圆滑平顺地对接起来。 分频器-分类 1)功率分频器:位于功率放大器之后,设置在音箱内,通过LC滤波网络,将功率放大器输出的功率音频信号分为低音,中音和高音,分别送至各自扬声器。连接简单,使用方便,但消耗功率,出现音频谷

小数分频频率合成器的理论基础(翻译)

小数分频频率合成器的理论基础(翻译)

小数分频频率合成器的理论基础 A. Marques _, M. Steyaert and W. Sansen ESAT-MICAS, K.U. Leuven, Kard. Mercierlaan 94, B-3001 Heverlee, Belgium 本文提出了一种基于锁相回路(PLL)频率合成器的演变概述。数字PLL的主要限制的描述,以及随之而来的小数N技术使用的必要性是有道理的。合成频率的旁瓣典型的杂散噪声线的起源进行了解释。它通过使用数字?∑调制器来控制分频值展示了如何消除这些杂散噪声线。最后,数字?∑调制器的使用同分数N PLL的输出相位噪声的影响一起进行了分析。 1.介绍 无线通信领域,在过去十年中有了很大的发展。这种快速发展,主要是通过引进强大的数字信号处理技术。这些技术允许执行复杂的调制解调方案,以及先进的数字校正技术,最终产生非常高性能的系统,可以完全或几乎完全集成在一个标准的低成本技术。 典型的接收器/发射器无线系统RF部分如图1所示。可以看出,在无线系统中,一个或多个频率合成器几乎都是必要的,同时在接收和发射部分。此频率合成器必须不仅能够产生感兴趣

的频带内的所有频率,以及产生具有高纯度的,由于不断下降的频道间距。 图1 典型的射频部分,一个无线接收器/ 发射器系统 在无线系统领域,在过去几年中主要重点一直是在一个完整的系统的全面整合,包括发射器/接收器和频率合成器,使用短沟道CMOS或BiCMOS工艺(见[1,13]其引用)。 因此,频率合成精度高,稳定的需求令人难以置信的增长,特别是对需要的操作频率非常高(在千兆赫兹的范围内)的应用,小频率决议(典型的信道间隔几百万赫兹数100千赫),和低相位噪声数字(100dBc的订单数100千赫载波)。此外,同时,在过去几十年,数字可编程的频率合成器的需求也增加了。

电子分频是什么

电子分频是什么 说到电子分频,首先要说分频器是什么。顾名思义,分频器是一种将不同频率的信号进行分割的电路装置。其本质就是信号中的各种滤波器。通常我们指的音频的频率范围在20Hz-20KHz,高音指的是频率较高的声音,低音指的的是频率较低的声音。而在HiFi音响中,分频器的作用就是将高、中、低音,按照需要频率进行分割。因此分频器也常被称为“分音器”。 为什么需要分频器呢?因为不同的喇叭单元各自的特性不同,它们都有最佳表现的频率范围。因此在要求较高的HiFi音响系统中,利用分频器将频率进行分割,再分别交给高、中、低音喇叭,使在它们仅在最佳表现的频率范围内工作,以达到音质更佳的目的。 那么分频器有哪些种类呢?根据分频器在音响系统中所处的位置不同,我们通常又将它们分为功率分频器和电子分频器。 功率分频器: 电子分频器:

功率分频器是家庭HiFi音响中最常见的分频器,它处于功放之后、喇叭之前。正是因为它需要承受功放输出的巨大功率,所以称为功率分频器。功率分频器都是无源滤波器。 电子分频器则用来构成另一种音响系统。它处于音源之后,功放之前。经过它的音频信号较弱,所以通常用有源滤波器来实现。因此电子分频器也常被成为:有源分频器、主动分频器等。

功率分频器由于受元器件所限,所以在阻抗匹配、相位特性、插入损耗等方面和电子分频相比都不具优势。更重要的是,电子分频系统中,以多台功放分工合作的方式代替了功率分频系统中一台功放全力工作的方式,使得对功放的要求明显下降,但表现却能大大提升。 其实在专业音响上,电子分频系统早就被成熟运用。不过略有不同的是,专业音响中更多使用的电子分频器是DSP(数字信号处理器),它的最大特别是集成度高,功能强大,可以对曲线等进行各种调整。而在家用HiFi音响中,特别是对普通用户来说,笔者更推荐使用模拟的电子分频器。模拟的电子分频器没有很多功能和可调整的部分,但也因此能拥有更自然更优质的声音。 当然,不可否认,无论哪种音响系统如果设计合理,都可能发出好声音。 一家之言,仅供参考。

分频器的设计

首先讲一下单元: 一般情况下,我们对单元按频率会划分为超高音,高音,中高音,中音,重低音,低音,超低音 超高音:負責22kHz以上的頻率 高音:負責5000Hz~22kHz頻率、 中音:負責1500~5000Hz頻率 低音:負責1500Hz以下頻率 超低音(增加)負責200Hz以下頻率 也有网友提出其她的划分标准 以A音(C调的“哆来咪法嗦啦西”的“啦”音,频率为440赫兹)为基准音,以倍频的形式向下三个八度向上五个八度,把全音域分为八个八度,一个个八度就就是音响上常说的一个倍频程(1oct)。具体的划分就是这样的: 55-110赫兹,110-220赫兹,220-440赫兹,440-880赫兹,880-1760赫兹,1760-3520赫兹,3520-7040赫兹,7040-14080赫兹,共八段(八个八度)。这样就很清晰的瞧出频段的划分了。110赫兹以下-超低频; 110-220赫兹-低频; 220-440赫兹-中低频; 440-880赫兹-低中频; 880-1760赫兹-中频; 1760-3520赫兹-中高频; 3520-7040赫兹-高频; 7040赫兹以上-超高频。 还有两种频段划分方法 以“E”音划分 -20 次低频 20-40 极低频 40-80 低频下段 80-160 低频上段 160-320 中频下段 320-640 中频中段

640-1280 中频上段 1280-2560 高频下段 2560-5120 高频中段 5120-10240 高频上段 10240- 极高频 以“C”划分 -63 极低频 63-125 低频下段 125-250 低频上段 250-500 中频下段 500-1K 中频中段 1K-2K 中频上段 2K-4K 高频下段 4K-8K 高频上段 8K- 极高频 分频器的主要元件:电阻,电感,电容 电阻在分频器中的作用:调整灵敏度 电感:其特性就是阻挡较高频率,只让较低的频率通过电容:其特性与电感刚好相反,也就就是阻挡频率通过

3分频器的设计

三分频器的设计 时钟输入端(clkin)首先反向和不反向分别接到两个D触发器的时钟输入端,两个D触发器的输出接到一个二输入或非门的输入端,或非门的输出反馈到前面两个D触发器的D输入端,并且或非门的输出后面接一二分频器,得到占空比为50%的三分频波形。 图1:图形设计 VHDL程序: library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; use ieee.std_logic_arith.all; entity fen3 is port (clkin : in std_logic; --时钟输入 qout1 : buffer std_logic; qout2 : buffer std_logic; qout3 : buffer std_logic; clkout : out std_logic --占空比为1/2的三分频输出 ); end fen3; architecture behave of fen3 is begin qout3<=qout1 nor qout2; process(clkin) begin if clkin'event and clkin='1' then --在上升沿触发 qout1<=qout3; end if;

end process; process(clkin) begin if clkin'event and clkin='0' then --在下降沿触发 qout2<=qout3; end if; end process; process(qout3) variable tem:std_logic; begin if qout3'event and qout3='1' then --二分频tem:=not tem; end if; clkout<=tem; end process; end behave; 图3:仿真结果

基于VHDL的小数分频器设计

技术创新 《微计算机信息》(嵌入式与SOC)2010年第26卷第10-2期 360元/年邮局订阅号:82-946 《现场总线技术应用200例》 电子设计 基于VHDL 的小数分频器设计 The design of decimal fraction frequency divider based on the language named VHDL (淮阴工学院) 李慧 LI Hui 摘要:本文主要介绍了一种基于VHDL 语言的双模前置小数分频器的设计,为了测试的需要同时设计了8位数字频率计,在 MAX-PLUS Ⅱ平台下实现分频器的仿真,并下载到EPF10K10LC84-3芯片中实现。关键词:双模;小数分频器;频率计中图分类号:TP386文献标识码:A Abstract:The design of double module decimal fraction frequency divider based on the language named VHDL is mainly presented in this text.8bit digital cymometer is designed for testing at the same time.Simulate is finished on MAX-PLUS Ⅱ,and download is finished in CMOS CHIP named EPF10K10LC84-3. Key words:double module;decimal fraction frequency divider;cymometer 文章编号:1008-0570(2010)10-2-0192-02 1引言 分频器是数字电路中最基础也是最常用的电路,整数分频器的实现比较简单,可采用标准的计数器或可编程逻辑器件设计实现。但在某些特定场合下,时钟源与所需的频率往往不成整数倍关系,此时就需要采用小数分频器对输入的信号进行分频。而同时本系统可以在不降低参考频率的前提下,提高系统输出频率的分辨率。 2双模前置小数分频原理 用来实现小数分频器的方法很多,但其基本原理都基本一样,即在若干个分频周期中采取某种方法使某几个周期多计或少计一个数,从而在整个计数周期的总体平均意义上获得一个小数分频比,设要进行分频比为K 的小数分频,K 可表示为:K=N+10-n ×X 式中:n,N,X 均为正整数;n 为到X 的位数,即K 有n 位小数。另一方面,分频比又可以写成:K=M/P 式中:M 为分频器输入脉冲数;P 为输出脉冲数。 令,则:以上是小数分频器的一种实现方法,即在进行10n 次N 分 频时,设法多输入X 个脉冲。 3系统模块设计部分本系统主要包括两大部分:一部分是可预置分频系数的小 数分频模块设计,另一部分是8位数字频率计的设计(主要是为了验证设计的结果而辅助设计的一个模块)。具体模块框图如下: 图1系统模块图 4VHDL 程序实现 4.1小数分频模块设计1)、 原理分析以实现7.3分频为例,要实现7.3分频,只要在10次分频中做7(即10-3)次除7,3次除8就可以得到:N=(7×7+3×8)/10=7.3,又如,要实现分频系数为7.32的小数分频,只要在每100次分频中做68(100-32)次除7,32次除8即可得到N=(68×7+32×8)/10=7.32。 由上可知,要实现分频比为N.F 的小数分频,只需要对输入信号做N/N+1分频,考虑到该小数分频器要进行多次N 分频和 N+1分频,那么就设法将两种分频混合均匀,这种“均匀”工作是通过计数器来完成的,在这里只讨论一位小数的情况,下面简要介绍这种混合的方法:每进行一次分频,计数值为10减去分频系数的小数部分, 各次计数值累加。若累加结果小于10,则进行N+1分频,若大于10或等于10,则进行N 分频。 2)、VHDL 语言实现(以1位小数为例) 小数分频器主要由N/N+1分频器、计数器以及控制逻辑几 大部分组成。 界面说明部分定义如下: ENTITY sheji_02IS port(clk:in std_logic;--输入信号num_zg,num_zd:in std_logic_vector (3downto 0);--分频系 数高低位输入,最大输入为15.9 err:out std_logic; fout:buffer std_logic);--输出信号end; 分频系数为num_sheding 的分频器设计:process(clk)is begin if clk'event and clk='1'then if num="0000"then 李慧:讲师硕士 (10)áM K P N X P ?=×=+××10á P =10áM N X =×+192--

调音经验4、专业电子分频器的使用技巧

4专业电子分频器的使用技巧 在一套音响系统中提到分频器一般来说是指能将:20Hz--20000Hz频段的音频信号分成合适的、不同的几个频率段,然后分别送给相应功放,用来推动相应音箱的一种音响周边设备。由于它是一种用来处理、分配音频频率信号的电子设备,所以我们通常也叫它:电子分频器。电子分频器的详细功能和工作原理我就不多说了,这里我只是侧重于对一些大家比较重视或经常感到困惑的方面做一些通俗易懂的介绍,希望能对大家有所帮助! 一、我们为什么要使用电子分频器 我们音响师研究电声和现在电声设备与技术的不断发展都是为了一个目的:就是要尽量忠实的再现各种音源,当然要把自然界里千奇百怪、各种各样的声音完全利用现在的电声技术再现是不太现实几乎做不到的。大家知道,声音的频率范围是在20Hz—20000Hz之间,现在大多数前级音频处理设备的频率范围是可以达到这样宽度的,但目前的扬声器却成了一个瓶颈部分,我们奢想使用一种或简单几只扬声器就能放送出接近20Hz--20000Hz这样宽频率的声音是很难做到的,因为现在单只喇叭的有效工作频率范围都不是很宽。鉴于此电声工程师们就设计出了在不同频率段内工作的音箱,如: 1、重低音音箱:让它在大约30-200Hz的频率范围内工作。 2、低中音音箱:让它在大约200-2000Hz的频率范围内工作。 3、高音音箱:让它在大约2000-20000Hz的频率范围内工作。 如此以来我们就可以利用在不同频率段工作的不同种类的音箱配置一套能最大限度接近声音真实频率(20Hz--20000Hz)的音响系统了。当然不同音箱设备的构成和参数是不同的,我上面说的是以一个三分频的系统为例,实际使用上还有其它诸如:2分频或4分频等系统,而且不同音响系统中由于采用的音箱会有区别,因此这些音箱的工作频率也不可能是固定相同的,但大体的原理和思路是一样的。 那么有一个问题就是: 我们如何给这些在不同频率段工作的、不同种类的音箱灵活分配音频频率呢?为了解决这个问题,电子分频器就应运而生了,它可以根据不同音箱工作频率的需要提供合适的频率段,例如: 1、我们可以用电子分频器将高频信号通过功放送到高音扬声器中. 2、可以用电子分频器将中频信号通过功放送到中音扬声器中。 3、可以用电子分频器将低频信号通过功放送到低音扬声器中。 这样高、中、低频信号独立输出、互不干涉,因此可以尽可能发挥不同扬声器的工作频段优势,使音响系统中各频段声音重放显得更加均衡一些,使声音更具层次感,使音色更加完美。

FPGA实验一:简单分频器的设计

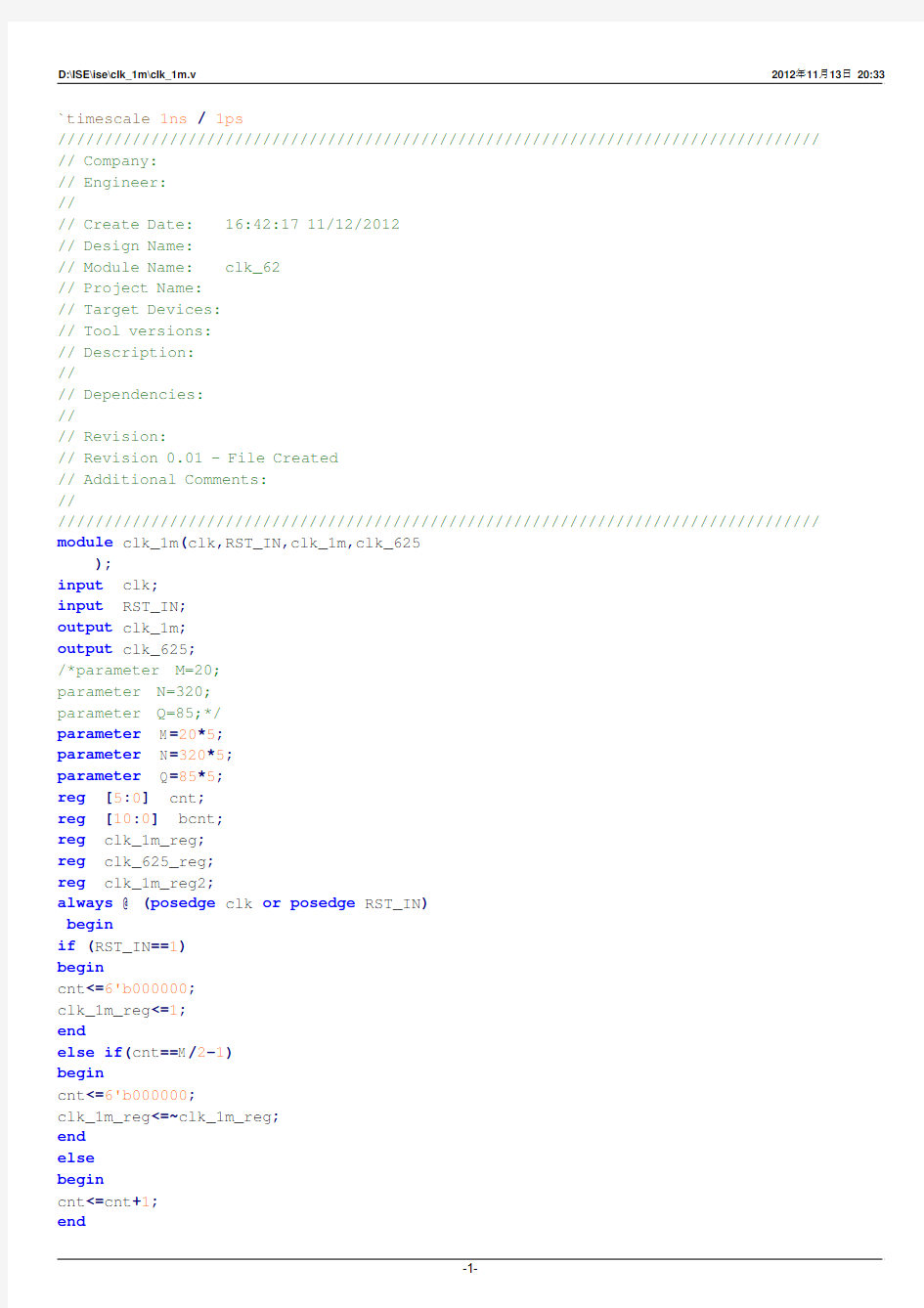

实验报告 课程名称:_____FPGA 实验______指导老师:__竺红卫/陈宏__成绩:__________________ 实验名称:___实验一:简单分频器的设计____实验类型:_FPGA 实验_同组学生姓名:__ 一、实验目的和要求(必填) 1. 熟悉 Xilinx ISE 软件,学会设计、仿真、综合和下载; 2. 熟悉实验板电路设定频率的方法。 二、实验内容和原理(必填) 实验内容: 根据实验板上晶振的输入频率 50MHz ,如果直接用这么高的时钟频率来驱动 LED 的闪烁,人眼将无法分辨。因此本实验着重介绍如何通过分频计数器的方式将 50MHz 的输入频率降低为人眼可分辨的频率(10Hz 以下),并在实验板的 LED0~LED7上显示出来。 LED 照片如下图: 实验原理: 实验板在滑动开关的上面有8 个独立的贴片LED 。 LED 一端接地,另一端通过390 欧的限流电阻接到Spartan-3E 上。要点亮一个LED ,向相应的控制位置输出高电位。 三、主要仪器设备(必填) 1. 电脑一台; 2. 实验板一块,XilinxSpartan-3E ; 3. 实验板电源一只; 4. 实验板连接电脑的下载线一根。 四、实验步骤和现象 1.新建Project 和Verilog Module 打开电脑桌面上的 Xilinx ISE14.1 软件,选择 project →new project 建立新项目,输入 project name 。

核对选择Spartan3E 和XC3S500E 和FG320 的封装形式。 跳出下面的选择框。

选择New Source,并在下面的选择框中选Verilog Module,填写刚才的new project name。 跳出下面的选择框。点击NEXT。