数字电子技术基础简明教程第三版课后习题解答第4章

数字电子技术基础教材第四章答案

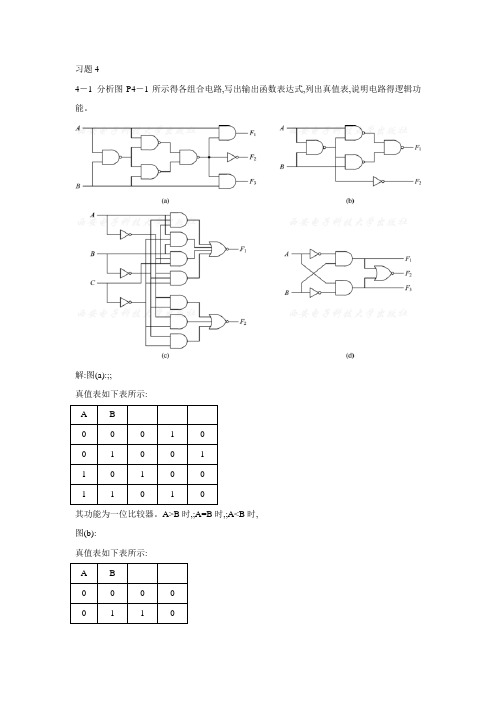

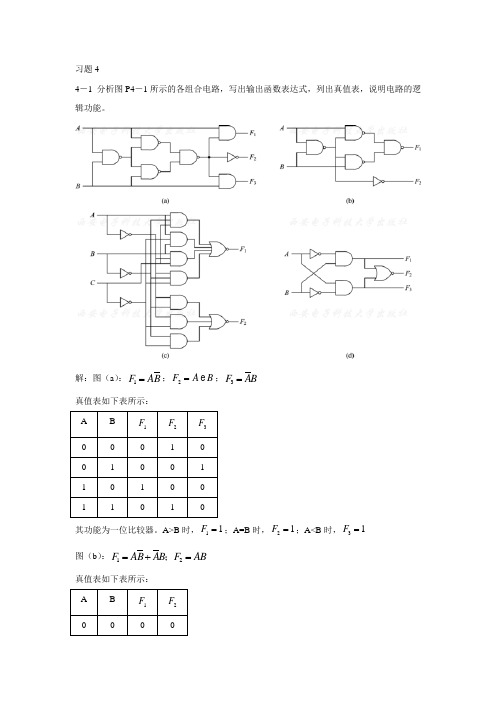

习题44-1 分析图P4-1所示得各组合电路,写出输出函数表达式,列出真值表,说明电路得逻辑功能。

解:图(a):;;真值表如下表所示:其功能为一位比较器。

A>B时,;A=B时,;A<B时,图(b):真值表如下表所示:功能:一位半加器,为本位与,为进位。

图(c):真值表如下表所示:功能:一位全加器,为本位与,为本位向高位得进位。

图(d):;;功能:为一位比较器,A<B时,=1;A=B时,=1;A>B时,=14-2 分析图P4-2所示得组合电路,写出输出函数表达式,列出真值表,指出该电路完成得逻辑功能。

解:该电路得输出逻辑函数表达式为:因此该电路就是一个四选一数据选择器,其真值表如下表所示:,当M=1时,完成4为二进制码至格雷码得转换;当M=0时,完成4为格雷码至二进制得转换。

试分别写出,,,得逻辑函数得表达式,并列出真值表,说明该电路得工作原理。

解:该电路得输入为,输出为。

真值表如下:由此可得:完成二进制至格雷码得转换。

完成格雷码至二进制得转换。

4-4 图P4-4就是一个多功能逻辑运算电路,图中,,,为控制输入端。

试列表说明电路在,,,得各种取值组合下F与A,B得逻辑关系。

解:,功能如下表所示,两个变量有四个最小项,最多可构造种不同得组合,因此该电路就是一个能产生十六种函数得多功能逻辑运算器电路。

4-5 已知某组合电路得输出波形如图P4-5所示,试用最少得或非门实现之。

解:电路图如下:4-6 用逻辑门设计一个受光,声与触摸控制得电灯开关逻辑电路,分别用A,B,C表示光,声与触摸信号,用F表示电灯。

灯亮得条件就是:无论有无光,声信号,只要有人触摸开关,灯就亮;当无人触摸开关时,只有当无关,有声音时灯才亮。

试列出真值表,写出输出函数表达式,并画出最简逻辑电路图。

解:根据题意,列出真值表如下:由真值表可以作出卡诺图,如下图:C AB 00 10 11 100 1由卡诺图得到它得逻辑表达式为: 由此得到逻辑电路为:4-7 用逻辑门设计一个多输出逻辑电路,输入为8421BCD 码,输出为3个检测信号。

数字电子技术基础第四章习题及参考答案

数字电子技术基础第四章习题及参考答案第四章习题1.分析图4-1中所示的同步时序逻辑电路,要求:(1)写出驱动方程、输出方程、状态方程;(2)画出状态转换图,并说出电路功能。

CPY图4-12.由D触发器组成的时序逻辑电路如图4-2所示,在图中所示的CP脉冲及D作用下,画出Q0、Q1的波形。

设触发器的初始状态为Q0=0,Q1=0。

D图4-23.试分析图4-3所示同步时序逻辑电路,要求:写出驱动方程、状态方程,列出状态真值表,画出状态图。

CP图4-34.一同步时序逻辑电路如图4-4所示,设各触发器的起始状态均为0态。

(1)作出电路的状态转换表;(2)画出电路的状态图;(3)画出CP作用下Q0、Q1、Q2的波形图;(4)说明电路的逻辑功能。

图4-45.试画出如图4-5所示电路在CP波形作用下的输出波形Q1及Q0,并说明它的功能(假设初态Q0Q1=00)。

CPQ1Q0CP图4-56.分析如图4-6所示同步时序逻辑电路的功能,写出分析过程。

Y图4-67.分析图4-7所示电路的逻辑功能。

(1)写出驱动方程、状态方程;(2)作出状态转移表、状态转移图;(3)指出电路的逻辑功能,并说明能否自启动;(4)画出在时钟作用下的各触发器输出波形。

CP图4-78.时序逻辑电路分析。

电路如图4-8所示:(1)列出方程式、状态表;(2)画出状态图、时序图。

并说明电路的功能。

1C图4-89.试分析图4-9下面时序逻辑电路:(1)写出该电路的驱动方程,状态方程和输出方程;(2)画出Q1Q0的状态转换图;(3)根据状态图分析其功能;1B图4-910.分析如图4-10所示同步时序逻辑电路,具体要求:写出它的激励方程组、状态方程组和输出方程,画出状态图并描述功能。

1Z图4-1011.已知某同步时序逻辑电路如图4-11所示,试:(1)分析电路的状态转移图,并要求给出详细分析过程。

(2)电路逻辑功能是什么,能否自启动?(3)若计数脉冲f CP频率等于700Hz,从Q2端输出时的脉冲频率是多少?CP图4-1112.分析图4-12所示同步时序逻辑电路,写出它的激励方程组、状态方程组,并画出状态转换图。

数字电子技术基础简明教程第三版4-6章(含答案)

第四章(选择、判断、填空共30题)一、选择题1.N个触发器可以构成能寄存位二进制数码的寄存器。

A.N-1B.NC.N+1D.2N2.在下列触发器中,有约束条件的是。

A.主从J K F/FB.主从D F/FC.同步R S F/FD.边沿D F/F3.一个触发器可记录一位二进制代码,它有个稳态。

A.0B.1C.2D.3E.44.存储8位二进制信息要个触发器。

A.2B.3C.4D.85.对于T触发器,若原态Q n=0,欲使新态Q n+1=1,应使输入T=。

A.0B.1C.QD.Q6.对于T触发器,若原态Q n=1,欲使新态Q n+1=1,应使输入T=。

A.0B.1C.QD.Q7.对于D触发器,欲使Q n+1=Q n,应使输入D=。

A.0B.1C.QD.Q8.对于J K触发器,若J=K,则可完成触发器的逻辑功能。

A.R SB.DC.TD.Tˊ9.欲使J K触发器按Q n+1=Q n工作,可使J K触发器的输入端。

A.J=K=0B.J=Q,K=QC.J=Q,K=QD.J=Q,K=0E.J=0,K=Q10.欲使J K触发器按Q n+1=Q n工作,可使J K触发器的输入端。

A.J=K=1B.J=Q,K=QC.J=Q,K=QD.J=Q,K=1E.J=1,K=Q11.欲使J K触发器按Q n+1=0工作,可使J K触发器的输入端。

A.J=K=1B.J=Q,K=QC.J=Q,K=1D.J=0,K=1E.J=K=112.欲使J K触发器按Q n+1=1工作,可使J K触发器的输入端。

A.J=K=1B.J=1,K=0C.J=K=QD.J=K=0E.J=Q,K=013.欲使D触发器按Q n+1=Q n工作,应使输入D=。

A.0B.1C.QD.Q14.下列触发器中,克服了空翻现象的有。

A.边沿D触发器B.主从R S触发器C.同步R S触发器D.主从J K触发器15.下列触发器中,没有约束条件的是。

A.基本R S触发器B.主从R S触发器C.同步R S触发器D.边沿D触发器16.描述触发器的逻辑功能的方法有。

数字电子技术基础简明教程(第三版) 4-6章

抗干扰0 能1力极0 强;异步置0

只有置1

0

1、00 置不1用0

功能异不。步允置许1

3. T 型触发器

在CP作用下,当T = 0时保持状态不变,T =1 时状态 翻转的电路,叫T 型时钟触发器。

Q

Q

1T C1

T Q n+1 功能 Q n1 T Q n TQ n

0 Q n 保持

T Qn

1 Q n 翻转 CP 下降沿时刻有效

56 引出端 功能 14

VCC

98 7

地

特性表 SD D CP RD

3.C边P 沿D0 DR触1–D 发S–1D器Q主n0+1要特点同步注置0

4 2 3 1 10 12 11 13

–SD1 CP1 – S–D2 CP2 –

D1 RD1 D2 RD2

C1P

的11上升11 沿Q1(正n 边保沿同持)步(或置无下1效降) 沿(负边沿)触发;

2. CP = 1 时跟随。 (Qn1 D) 下降沿到来时锁存 (Qn1 Qn )

三、集成同步 D 触发器

1. TTL 74LS375

Q

G1 >1

R G3 &

Q

>1 G2

S & G4

R

1 S CP

G5 D

D1 CP1、2

D2

D3 CP3、4

D4

74LS375

1 4

1D0 1LE

7 1D1

9 12

换 (2)比较上述特性方程,得出给定触发器中输入

方

信号的接法。

法 (3)画出用给定触发器实现待求触发器的电路。

1. JK D

已有

因此,令J = K = D D

数字电子技术基础简明教程第三版课后练习题含答案

数字电子技术基础简明教程第三版课后练习题含答案1. 十六进制转换1.将十六进制数A6B3转换成十进制数。

答案:42547解析:将十六进制数A6B3转换成十进制数的计算公式为:$A\\times 16^3 + 6\\times 16^2 + B\\times 16 + 3 = 42547$。

2.将十进制数2037转换成十六进制数。

答案:7F5解析:将十进制数2037转换成十六进制数的计算方法如下:•除以16,商为127,余数为5;•再次除以16,商为7,余数为15,即F;•最后商为0,余数为7,即7。

所以十进制数2037转换成十六进制数为7F5。

2. 布尔代数1.A+AB=A答案:真解析:$A+AB = A\\times 1 + A\\times B = A\\times (1+B) = A\\times 1 = A$。

2.AB+BC+CA=AB+AC答案:真解析:AB+BC+CA=AB+AC的推导如下:AB+BC+CA=AB+AC+BC+CA−AC−BD−BD+BD=A(B+C)+B(C+D)−B(D+C)−C(A+D)=A(B+C)−C(A+D)+B(C−D)=AB+AC−BC+BD=AB+AC。

3. 数字逻辑门1.OR 门和 AND 门的输出关系是什么?答案:OR 门输出为真当且仅当其输入中至少有一位为真;AND 门输出为真当且仅当其输入中所有的位都为真。

2.NOT 门的输出关系是什么?答案:NOT 门的输出与输入相反,即若输入为真,则输出为假;若输入为假,则输出为真。

4. 状态分析1.下面是一个简单的计数器状态图,完成以下计数器输出的对应状态表。

计数器状态图计数器状态图答案:状态Q2 Q1 Q0 下一个状态0 0 0 0 11 0 0 1 22 0 1 0 33 0 1 1 44 1 0 0 55 1 0 1 66 1 1 0 77 1 1 1 02.已知一个状态机的状态表,如何画其状态图?答案:画出每个状态和它所连接的下一个状态之间的箭头,用圆圈表示状态,标出每个状态的名称。

数字电子技术基础教材第四章答案

习题44-1 分析图P4-1所示得各组合电路,写出输出函数表达式,列出真值表,说明电路得逻辑功能。

解:图(a):;;真值表如下表所示:A B0 0 0 1 00 1 0 0 11 0 1 0 01 1 0 1 0其功能为一位比较器。

A>B时,;A=B时,;A<B时,图(b):真值表如下表所示:A B0 0 0 00 1 1 0功能:一位半加器,为本位与,为进位。

图(c):真值表如下表所示:功能:一位全加器,为本位与,为本位向高位得进位。

图(d):;;功能:为一位比较器,A<B时,=1;A=B时,=1;A>B时,=14-2 分析图P4-2所示得组合电路,写出输出函数表达式,列出真值表,指出该电路完成得逻辑功能。

解:该电路得输出逻辑函数表达式为:因此该电路就是一个四选一数据选择器,其真值表如下表所示:0 00 11 01 14-3 图P4-3就是一个受M控制得代码转换电路,当M=1时,完成4为二进制码至格雷码得转换;当M=0时,完成4为格雷码至二进制得转换。

试分别写出,,,得逻辑函数得表达式,并列出真值表,说明该电路得工作原理。

解:该电路得输入为,输出为。

真值表如下:M=1 0 0 0 0 0 0 0 00 0 0 1 0 0 0 10 0 1 0 0 0 1 10 0 1 1 0 0 1 00 1 0 0 0 1 1 00 1 0 1 0 1 1 10 1 1 0 0 1 0 10 1 1 0 0 1 0 0 M=0 1 0 0 0 1 1 1 11 0 0 1 1 1 1 01 0 1 0 1 1 0 01 0 1 1 1 1 0 11 1 0 0 1 0 0 01 1 0 1 1 0 0 11 1 1 0 1 0 1 11 1 1 1 1 0 1 0由此可得:完成二进制至格雷码得转换。

完成格雷码至二进制得转换。

4-4 图P4-4就是一个多功能逻辑运算电路,图中,,,为控制输入端。

数字电子技术基础简明教程第三版

注意

置 0 端 RD 和置 1 端 SD 低电平有效。

禁用 RD = SD = 0。

称约束条件

EXIT

[例] 设下图中触发器初始状态为 0,试相应输入波形 画出 Q 和 Q 旳波波形形。分析举例

RD R

Q RD

SD S

Q SD

保持 置 0保持置 1 初态为 0,故保持为 0。

解:

Q

Q

EXIT

(二)基本 RS 触发器旳两种形式

EXIT

一、基本 RS 触发器 Basic Flip - Flop

(一)由与非门互正构补常输工成出 作旳端时基,, 本 RS 触发器

1. 电路构它造们及旳逻输辑出符号 状态相反。

Q

Q

Q

Q

低电平有效

SR

G1

G2

SD

RD

SD 信号输入端 RD

置1端,也 置0端,也 称置位端。 称复位端。 S 即 Set R 即 Reset

触 CP 上升沿(或下降沿)时刻翻转。

发

这种触发方式称为边沿触发式。

器

EXIT

主从触发器和边沿触发器有何异同?

相

只能在 CP 边沿时刻翻转,所以都克服了

同

处 空翻,可靠性和抗干扰能力强,应用范围广。

电路构造和工作原理不同,所以电路功能 相 不同。为确保电路正常工作,要求主从 JK 触 异 处 发器旳 J 和 K 信号在 CP = 1 期间保持不变;而

Q

Q

Q

Q

1S C1 1R

1D C1

CP D CP

同步 D 触发器功能表

D

CP D Qn+1 ❖ 阐

明

称为 D 功能

数字电子技术第四章课后习题答案

第四章组合逻辑电路1. 解: (a)(b)是相同的电路,均为同或电路。

2. 解:分析结果表明图(a)、(b)是相同的电路,均为同或电路。

同或电路的功能:输入相同输出为“1”;输入相异输出为“0”。

因此,输出为“0”(低电平)时,输入状态为AB=01或103. 由真值表可看出,该电路是一位二进制数的全加电路,A为被加数,B为加数,C为低位向本位的进位,F1为本位向高位的进位,F2为本位的和位。

4. 解:函数关系如下:ABSF+⊕=++ABSSSABB将具体的S值代入,求得F 312值,填入表中。

A A FB A B A B A A F B A B A A F A A F AB AB F B B A AB F AB B A B A B A AB F B A A AB F B A B A B A F B A AB AB B A B A F B B A B A B A B A B A B A F AB BA A A B A A B A F F B A B A F B A B A F A A F S S S S =⊕==+==+⊕===+⊕===⊕===⊕===+⊕===+=+⊕===⊕==+==⊕==Θ=+=+⊕===+++=+⊕===+=⊕===⊕==+=+⊕==+=+⊕===⊕==01111111011010110001011101010011000001110110)(01010100101001110010100011000001235. (1)用异或门实现,电路图如图(a)所示。

(2) 用与或门实现,电路图如图(b)所示。

6. 解因为一天24小时,所以需要5个变量。

P变量表示上午或下午,P=0为上午,P=1为下午;ABCD表示时间数值。

真值表如表所示。

利用卡诺图化简如图(a)所示。

化简后的函数表达式为D C A P D B A P C B A P A P DC A PD B A P C B A P A P F =+++=用与非门实现的逻辑图如图(b)所示。

数字电子技术基础教材第四章答案

习题44-1 分析图P4-1所示的各组合电路,写出输出函数表达式,列出真值表,说明电路的逻辑功能。

解:图(a ):1F A B =;2F A B =;3F AB =真值表如下表所示:其功能为一位比较器。

A>B 时,11F =;A=B 时,21F =;A<B 时,31F = 图(b ):12F AB AB F AB =+=; 真值表如下表所示:功能:一位半加器,1F 为本位和,2F 为进位。

图(c ):1(0,35,6)(124,7)F M m==∑∏2(0,1,2,4)(3,5,6,7)F M m ==∑∏真值表如下表所示:功能:一位全加器,1F 为本位和,2F 为本位向高位的进位。

图(d ):1F A B =;2F A B =;3F AB =功能:为一位比较器,A<B 时,1F =1;A=B 时,2F =1;A>B 时,3F =14-2 分析图P4-2所示的组合电路,写出输出函数表达式,列出真值表,指出该电路完成的逻辑功能。

解:该电路的输出逻辑函数表达式为:100101102103F A A x A A x A A x A A x =+++因此该电路是一个四选一数据选择器,其真值表如下表所示:4-3 图P4-3是一个受M 控制的代码转换电路,当M =1时,完成4为二进制码至格雷码的转换;当M =0时,完成4为格雷码至二进制的转换。

试分别写出0Y ,1Y ,2Y ,3Y 的逻辑函数的表达式,并列出真值表,说明该电路的工作原理。

解:该电路的输入为3x 2x 1x 0x ,输出为3Y 2Y 1Y 0Y 。

真值表如下:由此可得:1M =当时,3323212101Y x Y x x Y x x Y x x =⎧⎪=⊕⎪⎨=⊕⎪⎪=⊕⎩ 完成二进制至格雷码的转换。

0M =当时,332321321210321010Y x Y x x Y x x x Y x Y x x x x Y x =⎧⎪=⊕⎪⎨=⊕⊕=⊕⎪⎪=⊕⊕⊕=⊕⎩ 完成格雷码至二进制的转换。