8位ALU(算术逻辑单元)verilog语言

veriloga 二进制加法

veriloga 二进制加法Verilog二进制加法Verilog是一种硬件描述语言,用于描述数字系统的行为与结构。

在数字电路设计中,二进制加法是一项基本的运算操作。

本文将探讨如何使用Verilog语言实现二进制加法,并介绍该过程中的关键步骤和注意事项。

一、概述二进制加法是一种基本的算术操作,用于将两个二进制数相加并生成结果。

在Verilog中,可以通过使用逻辑门和触发器来实现二进制加法。

本文将介绍使用全加器、半加器和多位加法器等组件来实现二进制加法。

二、全加器全加器是二进制加法中的基本组件,用于将两个二进制位和一个进位输入相加,并生成和值和进位输出。

Verilog代码中可以使用if-else语句或case语句来实现全加器的逻辑功能。

三、半加器半加器是一种简化的全加器,只能处理两个二进制位的加法操作。

半加器没有进位输入,只有和值和进位输出。

在Verilog中,可以使用逻辑门来实现半加器的功能。

四、多位加法器多位加法器是由多个全加器和半加器组成的,用于实现多位二进制数的加法操作。

在Verilog中,可以通过级联多个全加器和半加器来构建多位加法器。

根据加法器的位数不同,可以分为4位加法器、8位加法器等。

五、Verilog代码实现通过以上的基本组件,可以使用Verilog语言实现二进制加法。

首先,需要定义输入信号和输出信号的位宽,并声明全加器和半加器的实例。

然后,使用assign语句将输入信号连接到加法器的输入端口,并将输出信号连接到加法器的输出端口。

最后,通过实例化和连接多个加法器,可以实现多位二进制加法。

六、仿真与验证在完成Verilog代码的编写后,可以使用仿真工具来验证二进制加法的正确性。

通过输入不同的二进制数,并观察输出结果是否符合预期,可以检查加法器的功能是否正常。

如果仿真结果与预期一致,则说明二进制加法的Verilog代码实现是正确的。

七、应用领域二进制加法在数字电路设计中广泛应用于各种场景,例如算术运算、逻辑运算、数据传输等。

Verilog实验三原理2:ALU工作原理 (1)

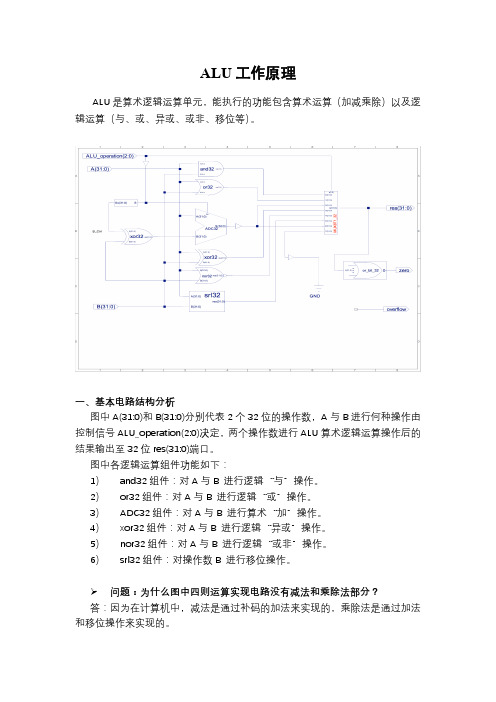

ALU工作原理ALU是算术逻辑运算单元,能执行的功能包含算术运算(加减乘除)以及逻辑运算(与、或、异或、或非、移位等)。

一、基本电路结构分析图中A(31:0)和B(31:0)分别代表2个32位的操作数,A与B进行何种操作由控制信号ALU_operation(2:0)决定,两个操作数进行ALU算术逻辑运算操作后的结果输出至32位res(31:0)端口。

图中各逻辑运算组件功能如下:1)and32组件:对A与B 进行逻辑“与”操作。

2)or32组件:对A与B 进行逻辑“或”操作。

3)ADC32组件:对A与B 进行算术“加”操作。

4)xor32组件:对A与B 进行逻辑“异或”操作。

5)nor32组件:对A与B 进行逻辑“或非”操作。

6)srl32组件:对操作数B 进行移位操作。

Ø问题:为什么图中四则运算实现电路没有减法和乘除法部分?答:因为在计算机中,减法是通过补码的加法来实现的,乘除法是通过加法和移位操作来实现的。

二、如何确定操作数A与B是执行何种运算操作对操作数A与B进行何种操作,由3根控制信号ALU_operation(2:0)决定。

ALU_operation(2:0) 连接至下图8选1多路选择器MUX8T1控制信号线上。

多路选择器原理:左边的8根输入线I0~I7代表输入数据,右边的o线代表输出数据,括号(31:0)代表输入与输出数据为32位。

上面s(2:0)代表3位控制信号:•当s(2:0) = 000时,输出o = I0.•当s(2:0) = 001时,输出o = I1.•当s(2:0) = 010时,输出o = I2.•当s(2:0) = 011时,输出o = I3. 依次类推.由于输入有8根线,因此,控制信号s需要3根选择线。

由于ALU_operation(2:0)连接至多路选择器的控制信号线s(2:0)上,因此,ALU_operation(2:0)的不同取值将决定多路选择器的输出,也即决定ALU电路的最终输出结果res(31:0)。

(完整版)VerilogHDL数字设计与综合(第二版)第七章课后习题答案

1.声明一个名为oscillate的寄存器变量并将它初始化为0。

使其每30个时间单位进行一次取反操作。

不要使用always语句。

提示:使用forever循环。

答:代码如下:reg oscillate;initialbeginoscillate<=0;forever #30 oscillate<=~oscillate;end2.设计一个周期为40个时间单位的时钟信号,其占空比为25%。

使用always和initial块进行设计。

将其在仿真0时刻的值初始化为0。

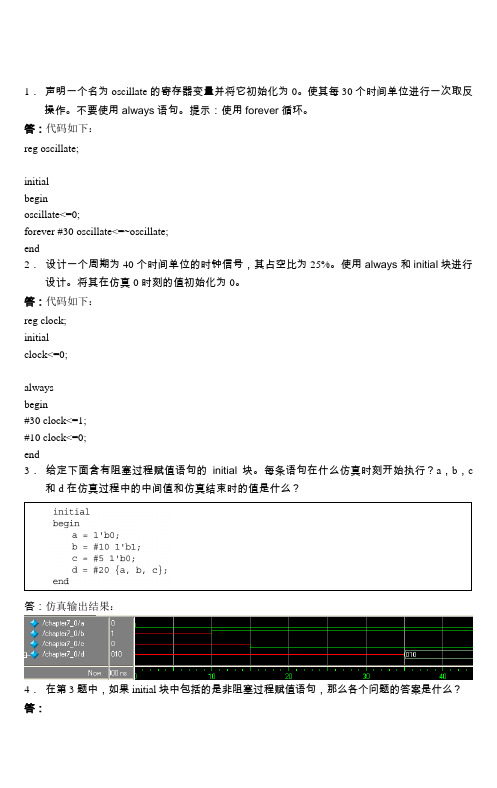

答:代码如下:reg clock;initialclock<=0;alwaysbegin#30 clock<=1;#10 clock<=0;end3.给定下面含有阻塞过程赋值语句的initial块。

每条语句在什么仿真时刻开始执行?a,b,c 和d在仿真过程中的中间值和仿真结束时的值是什么?答:仿真输出结果:4.在第3题中,如果initial块中包括的是非阻塞过程赋值语句,那么各个问题的答案是什么?答:第7章行为级建模79最终d没有输出,因为d<= #20 {a,b,c};语句执行的是先将a,b,c取值存储,在20个时间单位后将存储的值赋给d,因为b,c在初始时刻没有值,所以d值也是不确定的。

5.指出在下面的Verilog代码中各条语句的执行顺序。

其中是否含有不确定的执行顺序?a,b,c和d的最终值是什么?答:先执行a=1’b0,b=1’b1,然后执行#0 c=b,#0 d=a,执行顺序不确定,最终输出结果a=0,b=1,c=1,d=0. 6.在下面的例子中,d的最终值是什么?答:仿真输出波形如下,最终输出结果d=1。

0时刻b|c的值是1,在25个时间刻度后赋给d。

7.使用带有同步清零端的D触发器(清零端高电平有效,在时钟下降沿执行清零操作)设计一个下降沿触发的D触发器,只能使用行为语句。

提示:D触发器的输出q应当声明为寄存器变量。

verilog bit swap 写法

Verilog中的位交换写法一、概述Verilog是一种硬件描述语言,被广泛应用于数字电路设计和验证。

在数字电路设计中,经常需要对数据进行位交换操作。

对于初学者来说,如何利用Verilog语言实现位交换可能会困扰一些人。

本文将介绍Verilog中的位交换写法,希望对初学者有所帮助。

二、位交换的概念位交换是指将一个数据中的某几个位按照特定的顺序重新排列。

对于一个8位的数据,我们可能需要将其中的第2位和第5位进行交换,得到一个新的数据。

这种操作在数字电路设计中是非常常见的。

三、利用assign语句实现位交换在Verilog中,可以利用assign语句实现位交换。

下面是一个简单的例子,说明了如何利用assign语句实现位交换:```verilogmodule bit_swap (input [7:0] in_data,output [7:0] out_data);assign out_data[0] = in_data[7];assign out_data[1] = in_data[6];assign out_data[2] = in_data[5];assign out_data[3] = in_data[4];assign out_data[4] = in_data[3];assign out_data[5] = in_data[2];assign out_data[6] = in_data[1];assign out_data[7] = in_data[0];endmodule```在上面的例子中,我们定义了一个模块bit_swap,输入为8位的数据in_data,输出为8位的数据out_data。

利用assign语句,我们将in_data中的每一位按照特定顺序重新赋值给out_data,从而实现了位交换。

四、利用always语句实现位交换除了利用assign语句,我们还可以利用always语句实现位交换。

实验报告算术逻辑单元

一、实验目的1. 理解算术逻辑单元(ALU)的基本原理和功能。

2. 掌握ALU的设计方法和实现过程。

3. 通过实验加深对计算机组成原理的理解。

二、实验原理算术逻辑单元(ALU)是计算机中执行算术运算和逻辑运算的核心部件。

它主要完成加、减、乘、除等算术运算以及与、或、非、异或等逻辑运算。

ALU的设计和实现是计算机组成原理中的基础内容。

三、实验内容1. 设计一个8位ALU,能够完成加、减、乘、除、与、或、非、异或等运算。

2. 使用Verilog HDL语言实现该ALU。

3. 在FPGA平台上进行测试,验证ALU的功能。

四、实验步骤1. 分析ALU的功能需求,确定输入和输出信号。

2. 设计ALU的内部结构,包括运算单元、控制单元和寄存器。

3. 使用Verilog HDL语言编写ALU的代码。

4. 在FPGA平台上进行测试,验证ALU的功能。

五、实验结果与分析1. 实验结果根据实验要求,我们设计了一个8位ALU,能够完成加、减、乘、除、与、或、非、异或等运算。

以下是部分实验结果:(1)加法运算输入:A = 10101010,B = 11001100输出:10111010(2)减法运算输入:A = 11001100,B = 10101010输出:01010100(3)乘法运算输入:A = 10101010,B = 11001100输出:1111100000(4)除法运算输入:A = 11111111,B = 10000000输出:11111111(5)与运算输入:A = 10101010,B = 11001100输出:10001000(6)或运算输入:A = 10101010,B = 11001100输出:11101110(7)非运算输入:A = 10101010输出:01010101(8)异或运算输入:A = 10101010,B = 11001100输出:011001102. 实验分析通过实验,我们成功设计并实现了8位ALU。

8位ALU设计

8位算术逻辑单元设计电子12-112060401248位算术逻辑单元设计1.概述算术逻辑单元(arithmetic and logic unit) 是能实现多组算术运算和逻辑运算的组合逻辑电路,简称ALU。

算术逻辑单元(Arithmetic&logical Unit)是中央处理器(CPU)的执行单元,是所有中央处理器的核心组成部分,由"And Gate"(与门)和"Or Gate"(或门)构成的算术逻辑单元,主要功能是进行二位元的算术运算,如加减乘(不包括整数除法)。

基本上,在所有现代CPU体系结构中,二进制都以补码的形式来表示。

通常而言,ALU具有对处理器控制器、内存及输入输出设备的直接读入读出权限。

输入输出是通过总线进行的。

输入指令包含一个指令字,有时被称为机器指令字,其中包括操作码,单个或多个操作数,有时还会有格式码;操作码指示ALU机要执行什么操作,在此操作中要执行多少个操作数。

比如,两个操作数可以进行比较,也可以进行加法操作。

格式码可与操作码结合,告知这是一个定点还是浮点指令;输出包括存放在存储寄存器中的结果及显示操作是否成功的设置。

如操作失败,则在机器状态字中会有相应的状态显示。

大部分ALU都可以完成以下运算∶整数算术运算(加、减,有时还包括乘和除),位逻辑运算(与、或、非、异或),移位运算。

2.ALU设计2.1设计目标设计要求该处理器的数据宽度是8bit,可以实现算术加法、算术减法、逻辑与、逻辑或、逻辑非、逻辑与非、逻辑或非和逻辑异或等8种运算。

2.2逻辑分析依照ALU的原理与逻辑结构原理图,用超前进位的方法能实现下面八种功能操作的4位ALU,并对电路进行封装。

设定:输入信号:A4-A1、B4-B1、F3-F1、低位进位端C0、(级联控制端G);输出信号:S4-S1、进位C4 4位ALU的八种功能如下:把低位的进位连接到高一位的本位上,而当F3F2F1的值为001、011、101 时,C0的值为1,其余为0,于是C0应满足:C0=GF1/F1F2F3+C0/G。

八位移位寄存器verilog代码

一、引言在数字电路设计中,移位寄存器是十分常见的电路元件。

它能够对输入的数据按照特定的规则进行位移操作,常见的有左移、右移、循环移位等。

在Verilog语言中,我们可以通过编写代码来实现八位移位寄存器。

本文将从深度和广度方面展开对八位移位寄存器的Verilog代码进行全面评估,并撰写有价值的文章。

二、基本概念在开始编写八位移位寄存器的Verilog代码之前,我们首先要明确其基本概念。

移位寄存器是一种能够在时钟信号的控制下,对输入数据进行位移操作的寄存器。

而八位移位寄存器则是指这个寄存器能够对八位二进制数据进行位移。

这意味着在Verilog代码中,我们需要定义一个八位的寄存器,并编写移位操作的逻辑。

我们还需要考虑如何控制时钟信号和输入数据,以使得移位操作能够按照我们的期望进行。

三、Verilog代码实现```verilogmodule shift_register(input wire clk, // 时钟信号input wire rst, // 复位信号input wire [7:0] data_in, // 输入数据output reg [7:0] data_out // 输出数据);// 初始化寄存器always @(posedge clk or posedge rst)beginif (rst)data_out <= 8'b00000000; // 复位时,将寄存器清零elsedata_out <= data_in; // 否则将输入数据写入寄存器end// 左移操作always @(*)begindata_out = {data_out[6:0], 1'b0}; // 将寄存器中的数据向左移动一位end// 右移操作always @(*)begindata_out = {1'b0, data_out[7:1]}; // 将寄存器中的数据向右移动一位endendmodule```以上是一个简单的八位移位寄存器的Verilog代码实现。

8位ALU设计.doc

8位算术逻辑单元设计电子12-18位算术逻辑单元设计1.概述算术逻辑单元(arithmetic and logic unit) 是能实现多组算术运算和逻辑运算的组合逻辑电路,简称ALU。

算术逻辑单元(Arithmetic&logical Unit)是中央处理器(CPU)的执行单元,是所有中央处理器的核心组成部分,由"And Gate"(与门)和"Or Gate"(或门)构成的算术逻辑单元,主要功能是进行二位元的算术运算,如加减乘(不包括整数除法)。

基本上,在所有现代CPU体系结构中,二进制都以补码的形式来表示。

通常而言,ALU具有对处理器控制器、内存及输入输出设备的直接读入读出权限。

输入输出是通过总线进行的。

输入指令包含一个指令字,有时被称为机器指令字,其中包括操作码,单个或多个操作数,有时还会有格式码;操作码指示ALU机要执行什么操作,在此操作中要执行多少个操作数。

比如,两个操作数可以进行比较,也可以进行加法操作。

格式码可与操作码结合,告知这是一个定点还是浮点指令;输出包括存放在存储寄存器中的结果及显示操作是否成功的设置。

如操作失败,则在机器状态字中会有相应的状态显示。

大部分ALU都可以完成以下运算∶整数算术运算(加、减,有时还包括乘和除),位逻辑运算(与、或、非、异或),移位运算。

2.ALU设计2.1设计目标设计要求该处理器的数据宽度是8bit,可以实现算术加法、算术减法、逻辑与、逻辑或、逻辑非、逻辑与非、逻辑或非和逻辑异或等8种运算。

2.2逻辑分析依照ALU的原理与逻辑结构原理图,用超前进位的方法能实现下面八种功能操作的4位ALU,并对电路进行封装。

设定:输入信号:A4-A1、B4-B1、F3-F1、低位进位端C0、(级联控制端G);输出信号:S4-S1、进位C4 4位ALU的八种功能如下:把低位的进位连接到高一位的本位上,而当F3F2F1的值为001、011、101 时,C0的值为1,其余为0,于是C0应满足:C0=GF1/F1F2F3+C0/G。

8位ALU算术逻辑单元verilog语言

理工大学城市学院FPGA实验报告实验容:8位ALU系别班级:电子1004班学号::日期:2013.4.14一.设计概述:一种基于可编程逻辑器件FPGA和硬件描述语言的8位的ALU的设计方法。

该ALU 采用层次设计方法,有寄存器模块、控制模块和显示模块组成,能实现8位无符号数的取值、加减和4种逻辑运算(与、或、异或、同或)。

该ALU在QuartusII软件环境下进行功能仿真,通过DE2验证。

二.设计功能:1、该处理器的数据宽度为8bit,可以实现算术加法、减法、逻辑与、逻辑或、逻辑非、逻辑与非、逻辑或非和逻辑异或等8种运算。

2、用选择端opcode [2:0] 选择8种运算,2个操作数分别是a_r [7:0]和b_r[7:0],运算结果是alu_out[7:0];并定义选择如下。

3、使用DE2板上的3个拨码开关设置当前ALU的运算功能,再由8个拨码开关给定数据A和数据B,由一个按键key手动提供脉冲。

三.设计方案:本设计共有5个模块。

1)脉冲输出器(key手动脉冲),计数依次产生4个脉冲到各个部件,第一个脉冲启动信号。

2)寄存器A,第二个脉冲来时锁存数据A,并在数码管上显示。

3)寄存器B,第三个脉冲来时锁存数据B,并在数码管上显示。

4)8位ALU,第四个脉冲来时进行运算,并锁存结果alu_out。

5)结果显示器,将结果显示通过DE2上的数码管显示。

四.程序分析:主程序模块:module alu8(clk,clk_r,rst,a,b,alu_out,opcode,sw_ab,HEX1, HEX0, HEX7, HEX6, HEX5, HEX4);input clk,rst,clk_r;input [7:0] sw_ab;input [2:0] opcode;output [6:0] HEX1, HEX0, HEX7, HEX6, HEX5, HEX4;output [7:0] a;output [7:0] b;output [7:0] alu_out;rega U1(.clk(clk),.rst(rst),.sw_ab(sw_ab),.a_r(a),.clk_r(clk_r),.HEX7(HEX7),. HEX6(HEX6)); regb U2(.clk(clk),.rst(rst),.sw_ab(sw_ab),.b_r(b),.clk_r(clk_r),.HEX5(HEX5),. HEX4(HEX4)); alur U3(.clk(clk),.rst(rst),.a_r(a),.b_r(b),.alu_out(alu_out),.opcode(opcode));digital U4(.clk_r(clk_r),.rst(rst),.alu_out(alu_out),.HEX1(HEX1),. HEX0(HEX0)); endmodule第一位数A模块:module rega (clk,clk_r,rst,sw_ab,a_r,HEX7,HEX6);input [7:0] sw_ab;input clk,clk_r,rst;output [7:0] a_r;reg [7:0] a_r;output reg[6:0] HEX7,HEX6;reg [3:0]t;always (posedge clk or negedge rst)if(!rst)t<=1'd0;else if(cnt==5)t<=1'd0;elset<=cnt+1'd1;always (posedge clk or negedge rst)if(!rst) a_r=0;else if(cnt==1) a_r=sw_ab;else a_r=a_r;parameter seg0=7'b1000000,seg1=7'b1111001,seg2=7'b0100100,seg3=7'b0110000,seg4=7'b0011001,seg5=7'b0010010, seg6=7'b0000010,seg7=7'b1111000,seg8=7'b0000000,seg9=7'b0010000,sega=7'b0001000,segb=7'b00000 11,segc=7'b1000110,segd=7'b0100001,sege=7'b0000110,segf=7'b0001110;always (posedge clk_r)case(a_r[3:0])4'h0: HEX6[6:0]=seg0;4'h1: HEX6[6:0]=seg1;4'h2: HEX6[6:0]=seg2;4'h3: HEX6[6:0]=seg3;4'h4: HEX6[6:0]=seg4;4'h5: HEX6[6:0]=seg5;4'h6: HEX6[6:0]=seg6;4'h7: HEX6[6:0]=seg7;4'h8: HEX6[6:0]=seg8;4'h9: HEX6[6:0]=seg9;4'ha: HEX6[6:0]=sega;4'hb: HEX6[6:0]=segb;4'hc: HEX6[6:0]=segc;4'hd: HEX6[6:0]=segd;4'he: HEX6[6:0]=sege;4'hf: HEX6[6:0]=segf;default:HEX6[6:0]=seg0;endcasealways (posedge clk_r)case(a_r[7:4])4'h0: HEX7[6:0]=seg0;4'h1: HEX7[6:0]=seg1;4'h2: HEX7[6:0]=seg2;4'h3: HEX7[6:0]=seg3;4'h4: HEX7[6:0]=seg4;4'h5: HEX7[6:0]=seg5;4'h6: HEX7[6:0]=seg6;4'h7: HEX7[6:0]=seg7;4'h8: HEX7[6:0]=seg8;4'h9: HEX7[6:0]=seg9;4'ha: HEX7[6:0]=sega;4'hb: HEX7[6:0]=segb;4'hc: HEX7[6:0]=segc;4'hd: HEX7[6:0]=segd;4'he: HEX7[6:0]=sege;4'hf: HEX7[6:0]=segf;default:HEX7[6:0]=seg0;endcaseendmodule第二位数B模块:module regb (clk,clk_r,rst,sw_ab,b_r,HEX5,HEX4); input [7:0] sw_ab;input clk,clk_r,rst;output [7:0] b_r;reg [7:0] b_r;output reg[6:0] HEX5,HEX4;reg [3:0]t;always (posedge clk or negedge rst)if(!rst)t<=1'd0;else if(cnt==5)t<=1'd0;elset<=cnt+1'd1;always (posedge clk or negedge rst)if(!rst) b_r=0;else if(cnt==2) b_r=sw_ab;else b_r=b_r;parameter seg0=7'b1000000,seg1=7'b1111001,seg2=7'b0100100,seg3=7'b0110000,seg4=7'b0011001,seg5=7'b0010010,seg6=7'b000001 0,seg7=7'b1111000,seg8=7'b0000000,seg9=7'b0010000,sega=7'b0001000,segb=7'b00000 11,segc=7'b1000110,segd=7'b0100001,sege=7'b0000110,segf=7'b0001110;always (posedge clk_r)case(b_r[3:0])4'h0: HEX4[6:0]=seg0;4'h1: HEX4[6:0]=seg1;4'h2: HEX4[6:0]=seg2;4'h3: HEX4[6:0]=seg3;4'h4: HEX4[6:0]=seg4;4'h5: HEX4[6:0]=seg5;4'h6: HEX4[6:0]=seg6;4'h7: HEX4[6:0]=seg7;4'h8: HEX4[6:0]=seg8;4'h9: HEX4[6:0]=seg9;4'ha: HEX4[6:0]=sega;4'hb: HEX4[6:0]=segb;4'hc: HEX4[6:0]=segc;4'hd: HEX4[6:0]=segd;4'he: HEX4[6:0]=sege;4'hf: HEX4[6:0]=segf;default:HEX4[6:0]=seg0;endcasealways (posedge clk_r)case(b_r[7:4])4'h0: HEX5[6:0]=seg0;4'h1: HEX5[6:0]=seg1;4'h2: HEX5[6:0]=seg2;4'h3: HEX5[6:0]=seg3;4'h4: HEX5[6:0]=seg4;4'h5: HEX5[6:0]=seg5;4'h6: HEX5[6:0]=seg6;4'h7: HEX5[6:0]=seg7;4'h8: HEX5[6:0]=seg8;4'h9: HEX5[6:0]=seg9;4'ha: HEX5[6:0]=sega;4'hb: HEX5[6:0]=segb;4'hc: HEX5[6:0]=segc;4'hd: HEX5[6:0]=segd;4'he: HEX5[6:0]=sege;4'hf: HEX5[6:0]=segf;default:HEX5[6:0]=seg0;endcaseendmodule运算模块:module alur(clk,rst,alu_out,a_r,b_r,opcode,zero);output [7:0] alu_out;output zero;input [7:0] a_r,b_r;input [2:0] opcode;input clk,rst;reg [7:0] alu_out;reg [3:0]t;parameterquA=3'b000,quB=3'b001,ADD=3'b010,DEC=3'b011,ANDD=3'b100,XORR=3'b101,XOR =3'b110,NXOP=3'b111;assign zero=!a_r;always (posedge clk or negedge rst)if(!rst)t<=1'd0;else if(cnt==5)t<=1'd0;elset<=cnt+1'd1;always (posedge clk or negedge rst)if(!rst) alu_out=0;else if(cnt==3) begincasex(opcode)quA: alu_out<=a_r;quB: alu_out<=b_r;ADD: alu_out<=a_r+b_r;DEC: alu_out<=a_r-b_r;ANDD: alu_out<=a_r&b_r;XORR: alu_out<=a_r|b_r;XOR: alu_out<=a_r^b_r;NXOP: alu_out<=a_r^~b_r;default: alu_out<=8'bxxxx_xxxx;endcaseendelse alu_out=0;endmodule结果显示模块:module digital(clk_r,rst,alu_out,HEX1,HEX0);input [7:0] alu_out;input clk_r,rst;output reg[6:0] HEX1,HEX0;parameter seg0=7'b1000000,seg1=7'b1111001,seg2=7'b0100100,seg3=7'b0110000,seg4=7'b0011001,seg5=7'b0010010,seg6=7'b000001 0,seg7=7'b1111000,seg8=7'b0000000,seg9=7'b0010000,sega=7'b0001000,segb=7'b00000 11,segc=7'b1000110,segd=7'b0100001,sege=7'b0000110,segf=7'b0001110;always (posedge clk_r)case(alu_out[3:0])4'h0: HEX0[6:0]=seg0;4'h1: HEX0[6:0]=seg1;4'h2: HEX0[6:0]=seg2;4'h3: HEX0[6:0]=seg3;4'h4: HEX0[6:0]=seg4;4'h5: HEX0[6:0]=seg5;4'h6: HEX0[6:0]=seg6;4'h7: HEX0[6:0]=seg7;4'h8: HEX0[6:0]=seg8;4'h9: HEX0[6:0]=seg9;4'ha: HEX0[6:0]=sega;4'hb: HEX0[6:0]=segb;4'hc: HEX0[6:0]=segc;4'hd: HEX0[6:0]=segd;4'he: HEX0[6:0]=sege;4'hf: HEX0[6:0]=segf;default: HEX0[6:0]=seg0;endcasealways (posedge clk_r)case(alu_out[7:4])4'h0: HEX1[6:0]=seg0;4'h1: HEX1[6:0]=seg1;4'h2: HEX1[6:0]=seg2;4'h3: HEX1[6:0]=seg3;4'h4: HEX1[6:0]=seg4;4'h5: HEX1[6:0]=seg5;4'h6: HEX1[6:0]=seg6;4'h7: HEX1[6:0]=seg7;4'h8: HEX1[6:0]=seg8;4'h9: HEX1[6:0]=seg9;4'ha: HEX1[6:0]=sega;4'hb: HEX1[6:0]=segb;4'hc: HEX1[6:0]=segc;4'hd: HEX1[6:0]=segd;4'he: HEX1[6:0]=sege;4'hf: HEX1[6:0]=segf; default: HEX1[6:0]=seg0; endcaseendmodule五.仿真实现:整体图:波形图:六.硬件实现:1.引脚图:2.分析结果说明:开关0~2是算法选择,具体算法类型见设计功能第2项开关10~17数字输入,用8位二进制数表示两个十六进制数,每四位表示一位按键0是锁存及运算,当开关10~17输入一个数A时,按下按键0,数据就是锁存,再输入数就是数B,而当数据B也锁存后,再次按下按键0,就会显示运算结果按键1是复位键七.总结:通过这次FPGA实验课让我明白了真正的编程不像是那些C语言小程序那么简单,为了这次实验算是绞尽脑汁,最后为了读懂程序,还去专门找了Verilog语言辅导书,不管过程再怎么复杂曲折,总算是顺利的完成了实验任务,到了现在回顾为期6周的学习过程,也有一些时候是因为上课不认真,为后来的程序设计增加了难度,也有一些原因是因为自己本身能力不足导致设计接连失败,不得不说,也有一部分原因是因为学习实验室的器件不足,限制了实验设计的围,也使实验难度增加。

verilog语句讲解

Verilog语句讲解一、Verilog语言简介1.1 什么是Verilog语言Verilog是一种硬件描述语言(HDL),用于描述数字电路和系统的行为和结构。

它是一种高级语言,可以用于设计和验证各种电子系统,从简单的门电路到复杂的处理器和系统芯片。

1.2 Verilog语言的特点•面向事件的建模:Verilog可以描述数字电路中的事件和信号变化,使得设计者可以更好地理解和建模系统的行为。

•层次化建模:Verilog允许设计者使用模块化的方式组织代码,从而实现对复杂系统的分层描述。

•并发性支持:Verilog支持并发执行,可以同时执行多个操作,从而提高了系统的性能和效率。

•灵活性:Verilog可以描述各种类型的电路和系统,包括数字逻辑电路、时序电路、存储器和通信接口等。

二、Verilog语句的基本结构2.1 模块定义语句在Verilog中,一个模块是由输入、输出和内部逻辑组成的。

模块定义语句用于定义一个模块的接口和行为。

module module_name(input_list, output_list);// 内部逻辑endmodule•module_name:模块的名称,用于在其他模块中引用该模块。

•input_list:输入端口列表,用于定义模块的输入信号。

•output_list:输出端口列表,用于定义模块的输出信号。

2.2 信号定义语句Verilog中使用信号来表示数据和控制信号。

信号定义语句用于定义信号的类型和宽度。

reg [width-1:0] signal_name;•reg:表示信号的类型为寄存器,可以存储数据。

•[width-1:0]:表示信号的位宽,从高位到低位。

•signal_name:信号的名称,用于在模块内部引用该信号。

2.3 时钟信号定义语句在时序电路中,时钟信号是非常重要的。

Verilog中使用时钟信号来同步和控制电路的操作。

input wire clk;•input wire:表示时钟信号是一个输入信号。

一个简单的8位处理器完整设计过程及verilog代码

一个简单的8位处理器完整设计过程及verilog代码来源: EETOP BBS 作者:weiboshe一个简单的8位处理器完整设计过程及verilog代码,适合入门学习参考,并含有作者个人写的指令执行过程(点击下方阅读原文到论坛可下载源码)1. CPU定义我们按照应用的需求来定义计算机,本文介绍一个非常简单的CPU的设计,它仅仅用来教学使用的。

我们规定它可以存取的存储器为64byte,其中1byte=8bits。

所以这个CPU就有6位的地址线A[5:0],和8位的数据线D[7:0]。

我们仅定义一个通用寄存器AC(8bits寄存器),它仅仅执行4条指令如下:Instruction Instruction Code OperationADD00AAAAAA AC<—AC+M[AAAAAA]AND01AAAAAA AC<—AC^M[AAAAAA]JMP10AAAAAA GOTO AAAAAAINC11XXXXXX AC<—AC+1除了寄存器AC外,我们还需要以下几个寄存器:地址寄存器 A[5:0],保存6位地址。

程序计数器 PC[5:0],保存下一条指令的地址。

数据寄存器 D[7:0],接受指令和存储器来的数据。

指令寄存器 IR[1:0],存储指令操作码。

2. 取指设计在处理器执行指令之前,必须从存储器取出指令。

其中取指执行以下操作:1〉通过地址端口A[5:0]从地址到存储器2〉等待存储器准备好数据后,读入数据。

由于地址端口数据A[5:0]是从地址寄存器中读出的,所以取指第一个执行的状态是Fetch1: AR<—PC接下来cpu发出read信号,并把数据从存储器M中读入数据寄存器DR中。

同时pc加一。

Fetch2: DR<—M,PC<—PC+1接下来把DR[7:6]送IR,把DR[5:0]送ARFetch3: IR<—DR[7:6],AR<—DR[5:0]3. 指令译码Cpu在取指后进行译码一边知道执行什么指令,对于本文中的CPU来说只有4条指令也就是只有4个执行例程,状态图如下:4. 指令执行对译码中调用的4个例程我们分别讨论:4.1 ADD指令ADD指令需要CPU做以下两件事情:1〉从存储器取一个操作数2〉把这个操作数加到AC上,并把结果存到AC所以需要以下操作:ADD1: DR<—MADD2: AC<—AC+DR4.2 AND指令AND指令执行过程和ADD相似,需要以下操作:AND1: DR<—MAND2: AC<—AC^DR4.3 JMP指令JMP指令把CPU要跳转的指令地址送PC,执行以下操作JMP1: PC<—DR[5:0]4.4INC指令INC指令执行AC+1操作INC1: AC<—AC+1总的状态图如下:5 建立数据路径这一步我们来实现状态图和相应的寄存器传输。

verilog 8bit 数值判断 -回复

verilog 8bit 数值判断-回复Verilog是一种硬件描述语言,通常用于数字电路设计和逻辑仿真。

在数字电路设计中,常常需要对8位数值进行判断,以实现不同的逻辑功能和计算任务。

本文将一步一步地介绍如何使用Verilog语言进行8位数值判断,包括基本概念、语法和实例分析。

第一步:了解Verilog 8位数值判断的基本概念在数值判断中,我们需要根据输入的数值进行不同的逻辑操作,例如等于判断、大于判断、小于判断等。

在Verilog中,我们可以使用比较运算符(如==、>、<等)进行数值判断。

第二步:编写Verilog模块的声明和端口定义Verilog中的数字电路设计通常以模块为单位进行组织。

在编写Verilog 数值判断的模块之前,我们需要声明该模块,并定义其输入和输出端口。

对于8位数值判断的模块来说,我们需要定义两个8位数作为输入,以及一个1位数作为输出。

代码示例如下:verilogmodule number_comparison(input [7:0] num1,input [7:0] num2,output reg output_result);第三步:编写Verilog模块内的逻辑实现在Verilog模块内部,我们可以使用一系列逻辑语句来实现数值的判断部分。

根据具体的需求,我们可以使用if语句、case语句或者其他逻辑结构来实现数值判断的逻辑。

在本例中,我们使用if语句来判断两个8位数是否相等。

代码示例如下:verilogalways @(num1 or num2)beginif(num1 == num2) 判断两个数是否相等output_result = 1'b1; 如果相等,输出结果为1elseoutput_result = 1'b0; 如果不相等,输出结果为0end第四步:编写测试代码并进行仿真验证完成Verilog模块的编写后,我们需要进行仿真验证,以确保模块的正确性。

【FPGA】verilog实现ALU(算数逻辑单元)

【FPGA】verilog实现ALU(算数逻辑单元)算术逻辑单元(arithmetic and logic unit) 是能实现多组算术运算和逻辑运算的组合逻辑电路,简称ALU。

module ALU(A, B, Cin, Sum, Cout, Operate, Mode);input [3:0] A, B; // two operands of ALUinput Cin; //carry in at the LSBinput [3:0] Operate; //determine f(.) of sum = f(a, b)input Mode; //arithmetic(mode = 1'b1) or logic operation(mode = 1'b0)output [3:0] Sum; //result of ALUoutput Cout; //carry produced by ALU operation// carry generation bits and propogation bits.wire [3:0] G, P;// carry bits;reg [2:0] C;reg Cout;// function for carry generation:function gen;input A, B;input [1:0] Oper;begincase(Oper)2'b00: gen = A;2'b01: gen = A & B;2'b10: gen = A & (~B);2'b11: gen = 1'b0;endcaseendendfunction// function for carry propergation:function prop;input A, B;input [1:0] Oper;begincase(Oper)2'b00: prop = 1;2'b01: prop = A | (~B);2'b10: prop = A | B;2'b11: prop = A;endcaseendendfunction// producing carry generation bits;assign G[0] = gen(A[0], B[0], Operate[1:0]);assign G[1] = gen(A[1], B[1], Operate[1:0]);assign G[2] = gen(A[2], B[2], Operate[1:0]);assign G[3] = gen(A[3], B[3], Operate[1:0]);// producing carry propogation bits;assign P[0] = prop(A[0], B[0], Operate[3:2]);assign P[1] = prop(A[1], B[1], Operate[3:2]);assign P[2] = prop(A[2], B[2], Operate[3:2]);assign P[3] = prop(A[3], B[3], Operate[3:2]);// producing carry bits with carry-look-ahead;always @(G or P or Cin, Mode)beginif (Mode) beginC[0] = G[0] | P[0] & Cin;C[0] = G[0] | P[0] & Cin;C[1] = G[1] | P[1] & G[0] | P[1] & P[0] & Cin;C[2] = G[2] | P[2] & G[1] | P[2] & P[1] & G[0] | P[2] & P[1] & P[0] & Cin;Cout = G[3] | P[3] & G[2] | P[3] & P[2] & G[1] | P[3] & P[2] & P[1] & G[0] | P[3] & P[2] & P[1] & P[0] & Cin;endelse beginC[0] = 1'b0;C[1] = 1'b0;C[2] = 1'b0;Cout = 1'b0;endend// calculate the operation results;assign Sum[0] = (~G[0] & P[0]) ^ Cin;assign Sum[1] = (~G[1] & P[1]) ^ C[0];assign Sum[2] = (~G[2] & P[2]) ^ C[1];assign Sum[3] = (~G[3] & P[3]) ^ C[2];endmodulemodule ALU(A, B, Cin, Sum, Cout, Operate, Mode);input [3:0] A, B; //输⼊信号:两个四位的操作对象A、Binput Cin; //输⼊进位信号input [3:0] Operate; //输⼊信号,决定输出sum的操作input Mode; //算数操作(mode = 1'b1) 或者逻辑操作(mode = 1'b0)output [3:0] Sum; //输出ALU计算结果output Cout; //输出ALU操作产⽣的进位信号wire [3:0] G, P; //进位⽣成位和增长位reg [2:0] C;reg Cout;function gen; //进位信号⽣成函数input A, B; //函数输⼊信号A、Binput [1:0] Oper; //函数输⼊操作信号Operbegincase(Oper)2'b00: gen = A; //⽣成A信号2'b01: gen = A & B; //⽣成A和B相与信号2'b10: gen = A & (~B); //⽣成A和~B相与信号2'b11: gen = 1'b0; //⽣成低电平信号endcaseendendfunctionfunction prop; //进位信号增长函数input A, B; //函数输⼊信号A、Binput [1:0] Oper; //函数输⼊操作信号Operbegincase(Oper)2'b00: prop = 1; //返回⾼电平信号2'b01: prop = A | (~B); //返回A和~B相或信号2'b10: prop = A | B; //返回A和B相或信号2'b11: prop = A; //返回A信号endcaseendendfunction//产⽣进位⽣成位信号assign G[0] = gen(A[0], B[0], Operate[1:0]);assign G[1] = gen(A[1], B[1], Operate[1:0]);assign G[1] = gen(A[1], B[1], Operate[1:0]);assign G[2] = gen(A[2], B[2], Operate[1:0]);assign G[3] = gen(A[3], B[3], Operate[1:0]);//产⽣进位增长位信号assign P[0] = prop(A[0], B[0], Operate[3:2]);assign P[1] = prop(A[1], B[1], Operate[3:2]);assign P[2] = prop(A[2], B[2], Operate[3:2]);assign P[3] = prop(A[3], B[3], Operate[3:2]);//产⽣带进位提前的进位always @(G or P or Cin, Mode)beginif (Mode) beginC[0] = G[0] | P[0] & Cin;C[1] = G[1] | P[1] & G[0] | P[1] & P[0] & Cin;C[2] = G[2] | P[2] & G[1] | P[2] & P[1] & G[0] | P[2] & P[1] & P[0] & Cin;Cout = G[3] | P[3] & G[2] | P[3] & P[2] & G[1] | P[3] & P[2] & P[1] & G[0] | P[3] & P[2] & P[1] & P[0] & Cin;endelse beginC[0] = 1'b0;C[1] = 1'b0;C[2] = 1'b0;Cout = 1'b0;endend//计算操作结果assign Sum[0] = (~G[0] & P[0]) ^ Cin;assign Sum[1] = (~G[1] & P[1]) ^ C[0];assign Sum[2] = (~G[2] & P[2]) ^ C[1];assign Sum[3] = (~G[3] & P[3]) ^ C[2];endmodule。

verilog语言编写8位全加器教学文案

v e r i l o g语言编写8位全加器8位全加器一、实验目的用verilog语言编写一个8位全加器,并在modelsim软件上进行仿真。

二、代码1、源代码:module add8(sum,cout,in1,in2,cin);input [7:0] in1,in2;input cin;output [7:0] sum;output cout;assign {cout,sum}=in1+in2+cin;endmodule2、激励:`timescale 1ns/100psmodule add8_tb;reg[7:0] A,B;reg CIN;wire [7:0] SUM;wire COUT;add8 ul(.sum(SUM),.cout(COUT),.in1(A),.in2(B),.cin(CIN));initialbeginA=8'd0;B=8'd0;CIN=1'b0;#10 A=8'd20;B=8'd129;CIN=1'b1;#10 A=8'd27;B=8'd19;CIN=1'b0;#10 A=8'd157;B=8'd29;CIN=1'b0;#10 A=8'd37;B=8'd68;CIN=1'b0;#10 A=8'd11;B=8'd69;CIN=1'b0;#10 A=8'd54;B=8'd67;CIN=1'b1;#10 A=8'd211;B=8'd0;CIN=1'b0;#10 A=8'd87;B=8'd43;CIN=1'b1;#10 A=8'd23;B=8'd171;CIN=1'b0;#10 A=8'd12;B=8'd12;CIN=1'b1;#10 A=8'd112;B=8'd115;CIN=1'b0;endendmodule三、实验过程1、上机过程2、仿真波形3、波形说明波形图中,从上至下依次为:输入加数A、输入加数B、输入进位CIN、输出进位COUT、输出和SUM。

ASIC实验报告(8位CPU的设计)

ASIC设计实验报告学院:电子工程学院学号:2014*******姓名:***指导老师:***2014年11月13日一、实验目的:通过对ASIC实验课的学习,应当学会以下几点:1.熟悉Linux操作系统的应用环境,基本命令行的应用,以及对vi编辑器熟练应用。

2.熟练掌握Verilog编程语言,包括基本组合逻辑电路的实现方法,基本时序逻辑电路的实现方法,怎样使用预定义的库文件,利用always块实现组合逻辑电路的方法已经着重了解assign与always 两种组合逻辑电路实现方法之间的区别,深入了解阻塞赋值与非阻塞赋值的概念以及应用的差别,有限状态机(FSM)实现复杂时序逻辑的方法,以及学会在Linux 系统环境当中应用Synopsys工具VCS进行仿真。

3.熟悉电路设计当中的层次化、结构化的设计方法。

4.熟悉CPU当中有哪些模块组成,模块之间的关系,以及其基本的工作原理。

5.学会利用汇编语言设计程序,注意代码规范性要求。

二、实验要求:按照实验指导书上的要求即:CPU各个模块的Verilog语言代码的编写、编译及仿真正确,并在规定的时间内完成。

要求对CPU进行语言级系统仿真结果正确之后,利用该实验当中采用的八个汇编关键字,编写一个能够实现某种功能的小程序。

然后对其中的控制器电路进行综合,并检查Timing 和Power,进行门级仿真。

三、实验内容:设计一个8位RISC_CPU 系统。

(RISC: Reduced Instruction Set Computer),它是一种八十年代才出现的CPU,与一般的CPU相比,不仅只是简化了指令系统,而且通过简化指令系统使计算机的结构更加简单合理,从而提高了运算速度。

从实现的方法上,它的时序控制信号部件使用了硬布线逻辑,而不是采用微程序控制方式,故产生控制序列的速度要快的多,因为省去了读取微指令的时间。

此CPU所具有的功能有:(1)取指令:当程序已在存储器中时,首先根据程序入口地址取出一条程序,为此要发出指令地址及控制信号。

基于ALU的八位数的加减运算和四位数的乘法和除法的运算

摘要随着半导体技术和系统设计技术的发展,传统单片机由于其尺寸小、功耗低、一些专有特性已经难以满足一些场合的需要。

基于EDA软件的设计方式是借助于计算机来快速准确的完成电路的设计。

设计者提出方案后,利用计算机进行逻辑分析、性能分析、时序测试,如果发现错误或方案不理想,可以重复上述过程直至得到满意的电路,然后进行硬件电路的实现。

这种方法提高了设计质量,缩短了设计周期节省了设计费用,提高了产品的竞争力。

本文对CPU中的ALU的设计,能够完成带进位的八位数的加减运算和四位数的乘法和除法的运算。

在寄存器模块中集成了构成数据路径的所有寄存器和多路选择器,这些多路选择器受控制信号的控制,构成了数据路径中的数据传输部分。

在具体设计时用HLD语言来完成所希望的电路系统,并规定器件的结构特征和电路的行为方式,然后利用综合器和适配器将此程序编程能控制FPGA和CPLD内部结构,并实现相应逻辑功能的的门级或更底层的结构网表文件或下载文件。

关键词:ALU HLD FPGA EDAAbstractWith the development of the semiconductor technology and system design technology, it has been difficult to meet the needs of a number of occasions because of the traditional single chips’ small size, low power consumption and a number of proprietary features. Based on EDA software ,the design uses computer to complete the circuit quickly and accurately. After making a proposal , the Designers do logic analysis, performance analysis and timing test, if they find an error or if the program is not satisfactory, they repeat the process until it become asatisfactory circuit and then implement the hardware circuit .This approach improves design quality and shorten the design cycle ,saves design costs and improves product competitiveness.In this paper, the design of ALU for the CPU can complete the eight-bit number with carry bit into addition and subtraction operations and four-digit number into multiplication and division operations. Register module integrates all registers and multiplexers that constitute the data way .These multiplexers under control of the control signals constitute the data transmission part of data way. In specific design, it completes the expected electrical systems with HLD language and provides the structural characteristics of the device and circuit behavior. Then with this integrated device and the adapter program the program is compiled into FPGA and CPLD to control the internal structure and logic functions to achieve the corresponding gate-level or lower-level structural netlist files or downloading filesKeywords:Arithmetic Logic Unit Field Programmable Gate Array目录1、绪论 (4)1.1EDA技术发展概况 (4)1.1.1 CAD阶段 (5)1.1.2 CAE阶段 (5)1.1.3 EDA阶段 (5)1.2PLD发展概况 (6)1.3课题研究的内容 (8)1.3.1 设计背景介绍 (8)1.3.2 功能要求 (9)2、EDA技术的基础知识 (10)2.1可编程ASIC器件 (10)2.2 EDA设计工具 (11)3、总体方案设计 (12)3.1设计内容 (12)3.2设计方案比较 (13)3.3方案论证 (14)3.4方案选择 (15)4、单元模块设计 (15)4.1有源晶振电路 (15)4.2供电电路 (16)4.3按键输入电路 (17)4.4 LED状态灯输出电路 (18)4.5 最小系统 (19)5、软件实现 (20)5.1软件设计 (20)6、系统仿真及调试 (31)6.1仿真 (31)6.2 调试 (35)7、总结 (35)7.1设计小结 (35)7.2设计收获 (36)7.3设计改进 (36)8、参考文献 (37)1、绪论21世纪人类将全面进入信息化社会,对微电子信息技术和微电子VLSI基础技术将不断提出更高的发展要求,微电子技术仍将继续是21世纪若干年代中最为重要的和最有活力的高科技领域之一。

简单ALU(算术逻辑单元)的verilog实现

简单ALU(算术逻辑单元)的verilog实现2013-06-14 21:39:56简单ALU(算术逻辑单元)的verilog实现,可实现两数相加、相减,或⼀个数的加1、减1操作。

⼩结:要学会看RTL图,能够根据RTL图⼤致判断功能的正确性代码:1module alu_add_sub(2 rst_n,3 clk,4 oper_cmd,5 oper_data,6 dout7 );89parameter DATA_SIZE = 4'd8; //操作数宽度1011input rst_n;12input clk;1314input [1:0] oper_cmd;15input [2*DATA_SIZE - 1:0] oper_data;1617output [DATA_SIZE:0] dout;1819reg [1:0] oper_cmd_r;20reg [2*DATA_SIZE - 1:0] oper_data_r;2122wire [2*DATA_SIZE:0] add_sub_oper;2324reg [DATA_SIZE:0] dout_tmp;25reg [DATA_SIZE:0] dout;2627//输⼊数据打⼀拍28always@(posedge clk)29if(!rst_n)30begin31 oper_cmd_r <= 8'd0;32 oper_data_r <= 16'd0;33end34else35begin36 oper_cmd_r <= oper_cmd;37 oper_data_r <= oper_data;38end3940//根据输⼊数据,求操作码,相当于指令译码41assign add_sub_oper = add_sub_func(oper_cmd_r,oper_data_r);4243//根据译码结果,求输出44always@(posedge clk)45if(!rst_n)46begin47 dout_tmp <= 9'd0;48end49else50begin51if(add_sub_oper[2*DATA_SIZE])52 dout_tmp <= add_sub_oper[2*DATA_SIZE-1 : DATA_SIZE] + add_sub_oper[DATA_SIZE-1 : 0];53else54 dout_tmp <= add_sub_oper[2*DATA_SIZE-1 : DATA_SIZE] - add_sub_oper[DATA_SIZE-1 : 0];55end5657//输出数据打⼀拍58always@(posedge clk)59if(!rst_n)60 dout <= 9'd0;61else62 dout <= dout_tmp;6364//指令译码函数65function [2*DATA_SIZE:0] add_sub_func; //关键字function标志函数开始66input [1:0] oper_cmd;67input [2*DATA_SIZE - 1:0] oper_data;6869reg [1:0] mode;70reg [DATA_SIZE - 1:0] oper1;71reg [DATA_SIZE - 1:0] oper2;7273//always@(oper_cmd or oper_data)74begin//函数体须在过程块中75case(oper_cmd)762'b00 : //两数相加77begin78 mode = 1;79 oper1 = oper_data[2*DATA_SIZE - 1:DATA_SIZE];80 oper2 = oper_data[DATA_SIZE - 1:0];81end822'b01 : //加183begin84 mode = 1;85 oper1 = oper_data[2*DATA_SIZE - 1:DATA_SIZE];86 oper2 = 1'b1;87end882'b10 : //两数相减89begin90 mode = 0;91 oper1 = oper_data[2*DATA_SIZE - 1:DATA_SIZE];92 oper2 = oper_data[DATA_SIZE - 1:0];93end94default : //减195begin96 mode = 0;97 oper1 = oper_data[2*DATA_SIZE - 1:DATA_SIZE];98 oper2 = 1'b1;99end100endcase101 add_sub_func = {mode,oper1,oper2};102end103104endfunction//关键字endfunction标志函数结束105106endmoduletestbench:1module alu_add_sub_tb;23// Inputs4reg rst_n;5reg clk;6reg [1:0] oper_cmd;7reg [15:0] oper_data;89// Outputs10wire [8:0] dout;1112// Instantiate the Unit Under Test (UUT)13 alu_add_sub uut (14 .rst_n(rst_n),15 .clk(clk),16 .oper_cmd(oper_cmd),17 .oper_data(oper_data),18 .dout(dout)19 );2021parameter CLK_PERIOD = 10;2223initial begin24 rst_n = 0;25 clk = 1;26 oper_cmd = 0;27//oper_data = 0;2829 #100;30 rst_n = 1;3132 # (10*CLK_PERIOD) oper_cmd = 2'b00; //两数相加测试3334 # (10*CLK_PERIOD) oper_cmd = 2'b01; //加1测试3536 # (10*CLK_PERIOD) oper_cmd = 2'b10; //两数相减测试3738 # (10*CLK_PERIOD) oper_cmd = 2'b11; //减1测试3940end4142always #(CLK_PERIOD/2) clk = ~clk;4344always@(posedge clk)45if(!rst_n)46begin47 oper_data[15:8] = 0;48 oper_data[7:0] = 0;49end50else51begin52 oper_data[15:8] = oper_data[15:8] + 1;53 oper_data[7:0] = oper_data[7:0] + 1; 54end5556endmodule分析仿真结果,代码满⾜所需功能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

大连理工大学城市学院FPGA实验报告实验内容:8位ALU系别班级:电子1004班学号:姓名:日期:2013.4.14一.设计概述:一种基于可编程逻辑器件FPGA和硬件描述语言的8位的ALU的设计方法。

该ALU采用层次设计方法,有寄存器模块、控制模块和显示模块组成,能实现8位无符号数的取值、加减和4种逻辑运算(与、或、异或、同或)。

该ALU在QuartusII软件环境下进行功能仿真,通过DE2验证。

二.设计功能:1、该处理器的数据宽度为8bit,可以实现算术加法、减法、逻辑与、逻辑或、逻辑非、逻辑与非、逻辑或非和逻辑异或等8种运算。

2、用选择端opcode [2:0] 选择8种运算,2个操作数分别是a_r [7:0]和b_r[7:0],运算结果是alu_out[7:0];并定义选择如下。

3、使用DE2板上的3个拨码开关设置当前ALU的运算功能,再由8个拨码开关给定数据A和数据B,由一个按键key手动提供脉冲。

三.设计方案:本设计共有5个模块。

1)脉冲输出器(key手动脉冲),计数依次产生4个脉冲到各个部件,第一个脉冲启动信号。

2)寄存器A,第二个脉冲来时锁存数据A,并在数码管上显示。

3)寄存器B,第三个脉冲来时锁存数据B,并在数码管上显示。

4)8位ALU,第四个脉冲来时进行运算,并锁存结果alu_out。

5)结果显示器,将结果显示通过DE2上的数码管显示。

四.程序分析:主程序模块:module alu8(clk,clk_r,rst,a,b,alu_out,opcode,sw_ab,HEX1, HEX0, HEX7, HEX6, HEX5, HEX4);input clk,rst,clk_r;input [7:0] sw_ab;input [2:0] opcode;output [6:0] HEX1, HEX0, HEX7, HEX6, HEX5, HEX4;output [7:0] a;output [7:0] b;output [7:0] alu_out;rega U1(.clk(clk),.rst(rst),.sw_ab(sw_ab),.a_r(a),.clk_r(clk_r),.HEX7(HEX7),. HEX6(HEX6));regb U2(.clk(clk),.rst(rst),.sw_ab(sw_ab),.b_r(b),.clk_r(clk_r),.HEX5(HEX5),. HEX4(HEX4));alur U3(.clk(clk),.rst(rst),.a_r(a),.b_r(b),.alu_out(alu_out),.opcode(opcode)); digital U4(.clk_r(clk_r),.rst(rst),.alu_out(alu_out),.HEX1(HEX1),. HEX0(HEX0)); endmodule第一位数A模块:module rega (clk,clk_r,rst,sw_ab,a_r,HEX7,HEX6);input [7:0] sw_ab;input clk,clk_r,rst;output [7:0] a_r;reg [7:0] a_r;output reg[6:0] HEX7,HEX6;reg [3:0] cnt;always @(posedge clk or negedge rst)if(!rst) cnt<=1'd0;else if(cnt==5) cnt<=1'd0;else cnt<=cnt+1'd1;always @(posedge clk or negedge rst)if(!rst) a_r=0;else if(cnt==1) a_r=sw_ab;else a_r=a_r;parameter seg0=7'b1000000,seg1=7'b1111001,seg2=7'b0100100,seg3=7'b0110000,seg4=7'b0011001,seg5=7'b0010010 ,seg6=7'b0000010,seg7=7'b1111000,seg8=7'b0000000,seg9=7'b0010000,sega=7'b0001000,segb=7'b0000011 ,segc=7'b1000110,segd=7'b0100001,sege=7'b0000110,segf=7'b0001110;always @(posedge clk_r)case(a_r[3:0])4'h0: HEX6[6:0]=seg0;4'h1: HEX6[6:0]=seg1;4'h2: HEX6[6:0]=seg2;4'h3: HEX6[6:0]=seg3;4'h4: HEX6[6:0]=seg4;4'h5: HEX6[6:0]=seg5;4'h6: HEX6[6:0]=seg6;4'h7: HEX6[6:0]=seg7;4'h8: HEX6[6:0]=seg8;4'h9: HEX6[6:0]=seg9;4'ha: HEX6[6:0]=sega;4'hb: HEX6[6:0]=segb;4'hc: HEX6[6:0]=segc;4'hd: HEX6[6:0]=segd;4'he: HEX6[6:0]=sege;4'hf: HEX6[6:0]=segf;default:HEX6[6:0]=seg0;endcasealways @(posedge clk_r)case(a_r[7:4])4'h0: HEX7[6:0]=seg0;4'h1: HEX7[6:0]=seg1;4'h2: HEX7[6:0]=seg2;4'h3: HEX7[6:0]=seg3;4'h4: HEX7[6:0]=seg4;4'h5: HEX7[6:0]=seg5;4'h6: HEX7[6:0]=seg6;4'h7: HEX7[6:0]=seg7;4'h8: HEX7[6:0]=seg8;4'h9: HEX7[6:0]=seg9;4'ha: HEX7[6:0]=sega;4'hb: HEX7[6:0]=segb;4'hc: HEX7[6:0]=segc;4'hd: HEX7[6:0]=segd;4'he: HEX7[6:0]=sege;4'hf: HEX7[6:0]=segf;default:HEX7[6:0]=seg0;endcaseendmodule第二位数B模块:module regb (clk,clk_r,rst,sw_ab,b_r,HEX5,HEX4); input [7:0] sw_ab;input clk,clk_r,rst;output [7:0] b_r;reg [7:0] b_r;output reg[6:0] HEX5,HEX4;reg [3:0] cnt;always @(posedge clk or negedge rst)if(!rst) cnt<=1'd0;else if(cnt==5) cnt<=1'd0;else cnt<=cnt+1'd1;always @(posedge clk or negedge rst)if(!rst) b_r=0;else if(cnt==2) b_r=sw_ab;else b_r=b_r;parameter seg0=7'b1000000,seg1=7'b1111001,seg2=7'b0100100,seg3=7'b0110000,seg4=7'b0011001,seg5=7'b0010010,seg6=7'b0000010 ,seg7=7'b1111000,seg8=7'b0000000,seg9=7'b0010000,sega=7'b0001000,segb=7'b0000011 ,segc=7'b1000110,segd=7'b0100001,sege=7'b0000110,segf=7'b0001110;always @(posedge clk_r)case(b_r[3:0])4'h0: HEX4[6:0]=seg0;4'h1: HEX4[6:0]=seg1;4'h2: HEX4[6:0]=seg2;4'h3: HEX4[6:0]=seg3;4'h4: HEX4[6:0]=seg4;4'h5: HEX4[6:0]=seg5;4'h6: HEX4[6:0]=seg6;4'h7: HEX4[6:0]=seg7;4'h8: HEX4[6:0]=seg8;4'h9: HEX4[6:0]=seg9;4'ha: HEX4[6:0]=sega;4'hb: HEX4[6:0]=segb;4'hc: HEX4[6:0]=segc;4'hd: HEX4[6:0]=segd;4'he: HEX4[6:0]=sege;4'hf: HEX4[6:0]=segf;default:HEX4[6:0]=seg0;endcasealways @(posedge clk_r)case(b_r[7:4])4'h0: HEX5[6:0]=seg0;4'h1: HEX5[6:0]=seg1;4'h2: HEX5[6:0]=seg2;4'h3: HEX5[6:0]=seg3;4'h4: HEX5[6:0]=seg4;4'h5: HEX5[6:0]=seg5;4'h6: HEX5[6:0]=seg6;4'h7: HEX5[6:0]=seg7;4'h8: HEX5[6:0]=seg8;4'h9: HEX5[6:0]=seg9;4'ha: HEX5[6:0]=sega;4'hb: HEX5[6:0]=segb;4'hc: HEX5[6:0]=segc;4'hd: HEX5[6:0]=segd;4'he: HEX5[6:0]=sege;4'hf: HEX5[6:0]=segf;default:HEX5[6:0]=seg0;endcaseendmodule运算模块:module alur(clk,rst,alu_out,a_r,b_r,opcode,zero);output [7:0] alu_out;output zero;input [7:0] a_r,b_r;input [2:0] opcode;input clk,rst;reg [7:0] alu_out;reg [3:0] cnt;parameterquA=3'b000,quB=3'b001,ADD=3'b010,DEC=3'b011,ANDD=3'b100,XORR=3'b101,XOR=3'b110, NXOP=3'b111;assign zero=!a_r;always @(posedge clk or negedge rst)if(!rst) cnt<=1'd0;else if(cnt==5) cnt<=1'd0;else cnt<=cnt+1'd1;always @(posedge clk or negedge rst)if(!rst) alu_out=0;else if(cnt==3) begincasex(opcode)quA: alu_out<=a_r;quB: alu_out<=b_r;ADD: alu_out<=a_r+b_r;DEC: alu_out<=a_r-b_r;ANDD: alu_out<=a_r&b_r;XORR: alu_out<=a_r|b_r;XOR: alu_out<=a_r^b_r;NXOP: alu_out<=a_r^~b_r;default: alu_out<=8'bxxxx_xxxx;endcaseendelse alu_out=0;endmodule结果显示模块:module digital(clk_r,rst,alu_out,HEX1,HEX0);input [7:0] alu_out;input clk_r,rst;output reg[6:0] HEX1,HEX0;parameter seg0=7'b1000000,seg1=7'b1111001,seg2=7'b0100100,seg3=7'b0110000,seg4=7'b0011001,seg5=7'b0010010,seg6=7'b0000010 ,seg7=7'b1111000,seg8=7'b0000000,seg9=7'b0010000,sega=7'b0001000,segb=7'b0000011 ,segc=7'b1000110,segd=7'b0100001,sege=7'b0000110,segf=7'b0001110;always @(posedge clk_r)case(alu_out[3:0])4'h0: HEX0[6:0]=seg0;4'h1: HEX0[6:0]=seg1;4'h2: HEX0[6:0]=seg2;4'h3: HEX0[6:0]=seg3;4'h4: HEX0[6:0]=seg4;4'h5: HEX0[6:0]=seg5;4'h6: HEX0[6:0]=seg6;4'h7: HEX0[6:0]=seg7;4'h8: HEX0[6:0]=seg8;4'h9: HEX0[6:0]=seg9;4'ha: HEX0[6:0]=sega;4'hb: HEX0[6:0]=segb;4'hc: HEX0[6:0]=segc;4'hd: HEX0[6:0]=segd;4'he: HEX0[6:0]=sege;4'hf: HEX0[6:0]=segf;default: HEX0[6:0]=seg0;endcasealways @(posedge clk_r)case(alu_out[7:4])4'h0: HEX1[6:0]=seg0;4'h1: HEX1[6:0]=seg1;4'h2: HEX1[6:0]=seg2;4'h3: HEX1[6:0]=seg3;4'h4: HEX1[6:0]=seg4;4'h5: HEX1[6:0]=seg5;4'h6: HEX1[6:0]=seg6;4'h7: HEX1[6:0]=seg7;4'h8: HEX1[6:0]=seg8;4'h9: HEX1[6:0]=seg9;4'ha: HEX1[6:0]=sega;4'hb: HEX1[6:0]=segb;4'hc: HEX1[6:0]=segc;4'hd: HEX1[6:0]=segd;4'he: HEX1[6:0]=sege;4'hf: HEX1[6:0]=segf; default: HEX1[6:0]=seg0; endcaseendmodule五.仿真实现:整体图:波形图:六.硬件实现:1.引脚图:2.分析结果说明:开关0~2是算法选择,具体算法类型见设计功能第2项开关10~17数字输入,用8位二进制数表示两个十六进制数,每四位表示一位按键0是锁存及运算,当开关10~17输入一个数A时,按下按键0,数据就是锁存,再输入数就是数B,而当数据B也锁存后,再次按下按键0,就会显示运算结果按键1是复位键七.总结:通过这次FPGA实验课让我明白了真正的编程不像是那些C语言小程序那么简单,为了这次实验算是绞尽脑汁,最后为了读懂程序,还去专门找了Verilog语言辅导书,不管过程再怎么复杂曲折,总算是顺利的完成了实验任务,到了现在回顾为期6周的学习过程,也有一些时候是因为上课不认真,为后来的程序设计增加了难度,也有一些原因是因为自己本身能力不足导致设计接连失败,不得不说,也有一部分原因是因为学习实验室的器件不足,限制了实验设计的范围,也使实验难度增加。