ALU(算术逻辑运算单元)的设计,南京理工大学紫金学院vhdl实验报告,eda

ALU实验报告

南通大学计算机科学与技术学院上机实验报告课程名称:计算机组成原理实验年级:上机日期:姓名:学号:班级:实验名称:ALU实验教师:成绩:一、目的及要求1、设计一位全加器,并进行封装;2、用封装好的一位全加器做位扩展,实现8位串行进位加法器;3、8位加法器要求具备加减功能和溢出判断能力;4、设计波形文件,进行仿真;4、完成该实验的实验报告。

二、环境(软、硬件平台)软件:Quartus 2.0硬件:pc机三、内容及步骤(包括程序流程及说明)1、一位全加器真值表输入输出Ai Bi Ci Si Ci10 0 0 0 0 1 0 1 00 1 11 0 0 1 0 1 1 1 0 1 1 1 0 01 0 1 00 11 0 0 10 11 1Si=Ai⊕Bi⊕CiCi1=AiBi+BiCi+CiAi=AiBi+﹙Ai⊕Bi﹚Ci2、一位全加器电路3、封装4、用封装好的一位全加器做位扩展,实现8位串行进位加法器,具有加减功能和溢出判断功能。

原理图:5、设计波形文件,进行仿真波形图:四、运行结果加法:减法:溢出:五、问题及心得本学期的第12、13周的周三上午,我们几个班的同学进行了计算机组成原理课程的上机实验,经过两次实验课的上机学习和实验,不仅让我对计算机组成原理这课程有了进一步的了解,同时也让我的动手能力有了很大的提高,在实验的设计与实现中,将书本上的知识进行了运用,巩固和加深了自己的知识结构。

经过前几周的实验的训练,我对Quartus这个软件从原来的茫然、无从下手到有一定的了解,在上机实验开始前我对本次实验进行了初步的预习,对实验的原理和实验的设计也有了初步的了解。

上机开始之前老师为我们仔细讲解了实验的原理及设计过程。

事实证明听讲与自己实际操作是不一样的,自己操作还是存在着难度,需要自己去仔细探究。

在具体的实验操作过程中,主要考验的就是细心和耐心,一旦某个细节忽略了就很容易出现错误,造成大量时间的浪费。

ALU

END PROCESS [进程名];

例 利用PROCESS语句设计与非门电路。

nandx: PROCESS (a, b) BEGIN y<=a NAND b AFTER 10ns; END PROCESS nandx;

敏感信号表所标明的信号是用来启动进程的。敏感信号表中的信号无论哪

一个发生变化(如由’0’变’1’或由’1’变’0’ )都将启动该PROCESS语句。

CASE语句

CASE语句的一般格式为: CASE 条件表达式 IS

顺序描述语句

WHEN 条件表达式的值=>顺序处理语句;

WHEN 条件表达式的值=>顺序处理语句; … END CASE;

CASE语句可以用来描述总线或编码、译码的行为,其功

能是从众多不同语句的序列中选择其中之一执行之。

IF语句也具有类似的功能,但CASE语句具有比IF语句更强

通信则一边通过接口由信号传递,一边并行地同步执行。

当选择表达式的值发生变化,便启动该语句对各子句的选择值(条件) 表达式n WHEN 条件n; 进行测试对比,当发现有满足条件的子句时,就将此子句表达式的值

赋予目标信号。

3.与CASE语句相类似,该语句对子句条件选择值具有同期性(非

顺序性)。 4. 不允许有条件重叠现象,也不允许存在条件涵盖不全的情况。

顺序描述语句

例3-8译码器 LIBRARY ieee; USE ieee.std_logic_1164.ALL; ENTITY decode3_8 IS PORT(a,b,c : IN STD_LOGIC; g1,g2a,g2b : IN STD_LOGIC; y : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); END decode3_8;

ALU实验报告

算术逻辑单元实验报告一、实验目的1、掌握运算器的工作原理。

2、验证运算器的功能。

二、实验原理算术逻辑单元的主要功能是对二进制数据进行定点算术运算、逻辑运算和各种移位操作。

算术运算包括定点加减乘除运算;逻辑运算主要有逻辑与、逻辑或、逻辑异或和逻辑非操作。

ALU通常有两个数据输入端A和B,一个数据输出端Y 以及标志位等。

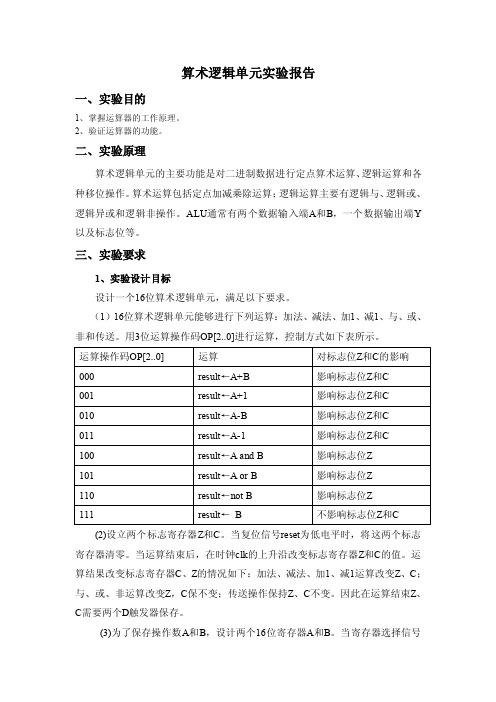

三、实验要求1、实验设计目标设计一个16位算术逻辑单元,满足以下要求。

(1)16位算术逻辑单元能够进行下列运算:加法、减法、加1、减1、与、或、非和传送。

用3位运算操作码OP[2..0]进行运算,控制方式如下表所示。

(2)设立两个标志寄存器Z和C。

当复位信号reset为低电平时,将这两个标志寄存器清零。

当运算结束后,在时钟clk的上升沿改变标志寄存器Z和C的值。

运算结果改变标志寄存器C、Z的情况如下:加法、减法、加1、减1运算改变Z、C;与、或、非运算改变Z,C保不变;传送操作保持Z、C不变。

因此在运算结束Z、C需要两个D触发器保存。

(3)为了保存操作数A和B,设计两个16位寄存器A和B。

当寄存器选择信号sel=0时,如果允许写信号write=1.,则在诗中clk的上升沿将数据输入dinput送入A 寄存器;当寄存器选择信号sel=1时,如果允许写信号write=1.,则在诗中clk的上升沿将数据输入dinput送入B寄存器。

(4)算术逻辑单元用一个设计实体完成。

2.顶层设计实体的引脚要求(1)clk对应试验台上的时钟(单脉冲)。

(2)reset对应实验台上的CPU复位信号CPU-RST。

(3)数据输入dinput对应试验台开关SD15~SD0。

(4)允许写信号write对应试验台开关SA5.(5)OP[2..0]对应试验台开关SA2~SA0.(6)寄存器选择信号sel对应试验台开关SA4.(7)16为运算结果result对应实验台上的指示灯A15~A0.(8)Z、C标志位对应试验台上的Z、C指示灯。

计算机组成原理实验报告_32位ALU设计实验

实验三32位ALU设计实验一、实验目的学生理解算术逻辑运算单元(ALU)的基本构成,掌握Logisim 中各种运算组件的使用方法,熟悉多路选择器的使用,能利用前述实验完成的32位加法器、Logisim 中的运算组件构造指定规格的ALU 单元。

二、实验原理、内容与步骤实验原理、实验内容参考:1、32位加法功能的原理与设计1)设计原理1,被加数A(32位),2,被加数B(32位),3,前一位的进位CIN(1位),4,此位二数相加的和S(32位),5,此位二数相加产生的进位COUT(1位)。

要实现32位的二进制加法,一种自然的想法就是将1位的二进制加法重复32次(即逐位进位加法器)。

这样做无疑是可行且易行的,但由于每一位的CIN都是由前一位的COUT提供的,所以第2位必须在第1位计算出结果后,才能开始计算;第3位必须在第2位计算出结果后,才能开始计算,等等。

而最后的第32位必须在前31位全部计算出结果后,才能开始计算。

这样的方法,使得实现32位的二进制加法所需的时间是实现1位的二进制加法的时间的32倍。

2)电路设计32位加法功能2、32位减法功能的原理与实现1)变减法为加法的原理1.在Y引脚处使用求补器(32位),即可变减法为加法2.用构造好的32位加法器。

Y各位取反,C0取1,即可达到减法变加法。

无符号数的减法溢出,带加减功能的ALU的进位取反后表示,有符号数的减法溢出,仍然用最高位和符号位是否相等来判断2)电路设计32位减法功能3、加减溢出检测的设计(不考虑乘除法)1)有符号数溢出的设计有符号数溢出的设计2)无符号数溢出的设计无符号数溢出的设计4、移位的原理与设计1)逻辑移位逻辑移位2)算术移位算术移位5、逻辑运算功能的原理与设计2)与、或、异或、或非逻辑6、大于、等于、小于功能设计大于、等于、小于功能设计7、AluOP的控制原理与设计1)原理:AluOP的控制原理与设计8、总电路设计图算术逻辑运算单元ALU三、实验结论及分析(实验完成功能情况、存在问题分析或改进思路、自己的心得体会等。

ALU课程设计报告

ALU课程设计报告一、教学目标本课程的教学目标是让学生掌握ALU(算术逻辑单元)的基本原理和操作,能够理解并分析计算机内部的算术和逻辑运算过程。

知识目标要求学生了解ALU的功能、结构和工作原理,能够识别不同的算术和逻辑运算符,理解它们在计算机中的应用。

技能目标则侧重于学生的分析和设计能力,能够运用所学的知识对简单的算术和逻辑运算进行模拟和优化。

情感态度价值观目标则在于培养学生对计算机科学的好奇心和创新精神,提高他们对计算机内部工作原理的兴趣和认识。

二、教学内容本课程的教学内容将围绕ALU展开,首先介绍ALU的功能和重要性,然后详细讲解ALU的结构和工作原理,包括不同的算术和逻辑运算符及其操作过程。

接下来,将通过实例分析,让学生学会如何设计和优化ALU的运算过程。

最后,通过实验操作,让学生亲自动手进行ALU的模拟运算,进一步加深对ALU的理解和掌握。

三、教学方法为了达到上述教学目标,我们将采用多种教学方法进行授课。

首先,通过讲授法,为学生系统地介绍ALU的基本原理和操作。

其次,通过讨论法,让学生在小组内进行交流和探讨,提高他们对ALU的理解和分析能力。

再次,通过案例分析法,让学生通过具体的实例,学会如何设计和优化ALU的运算过程。

最后,通过实验法,让学生亲自动手进行ALU的模拟运算,提高他们的实践能力。

四、教学资源为了支持教学内容和教学方法的实施,我们将准备一系列的教学资源。

主要包括教材、参考书、多媒体资料和实验设备。

教材和参考书将提供丰富的理论知识和实践案例,多媒体资料则可以帮助学生更直观地理解ALU的工作原理,实验设备则是学生进行实际操作的重要工具。

通过这些教学资源的运用,可以有效丰富学生的学习体验,提高他们的学习效果。

五、教学评估为了全面、客观地评估学生在ALU课程中的学习成果,我们将采用多元化的评估方式。

平时表现将占评估总分的30%,包括课堂参与度、提问和回答问题的情况等。

作业将占评估总分的20%,通过布置相关的设计性和分析性作业,让学生能够将所学的理论知识应用到实际问题中。

计算机组成原理-运算器组成实验

南通大学计算机科学与技术学院上机实验报告

课程名称:计算机组成原理年级:上机日期:2014 姓名:学号: 班级:

实验名称:实验二运算器组成实验教师:成绩:

1.设计一个8位补码加/减法运算器

(1)参考图1,在QUARTUS II里输入原理图,设计一个8位补码加/减法运算器。

①一位二进制的加减法器电路图为:

③封装为芯片,设计8位二进制的加减法器,电路图如下

④创建波形文件,对该8位补码加/减法运算器进行功能仿真测试测试通过后,封装成一个芯片。

3.利用仿真波形,测试数据通路的正确性。

设定各控制信号的状态,完成下列操作,要求记录各控制信号的值及时序关系。

(1)在输入数据IN7~IN0上输入数据后,开启输入缓冲三态门,检查总线

时序关系表为:

检查方法,在DR1中存入55H,同时在DR2中存入00H,检测总线输出的数即为存入的数据,波形图如下:

时序关系表为:

方法与上相同,在DR1中存入55H,同时在DR2中存入00H,检测总线输出的数即为存入的数据,波形图如下:

时序关系表为:

(4)完成加法运算,求55H+AAH,检查运算结果是否正确,请说明检查方法。

波形图如下:

(5)完成减法运算,分别求55H-AAH和AAH-55H,检查运算结果是否正确,请说明检查方法。

①计算AA-55,波形图如下:

时序图如下:

②计算

(6)求12H+34H-56H ,将结果存入寄存器R0,检查运算结果是否正确,同时检查数据是否存入,请说明检查方法。

①首先计算结果,波形图,时序图如下:

②检查结果的保存,则把结果存入LDR1,把00H 存入LDR2,通过与0的相加,输出结果就可确定数据已存入。

计算机组成原理实验报告算术逻辑单元ALU实验(源代码全)

计算机组成原理实验报告算术逻辑单元ALU实验(源代码全)算术逻辑单元ALU实验⼀. 实验⽬的1、理解算术逻辑单元ALU的⼯作原理。

2、掌握算术逻辑单元ALU的设计⽅法。

3、验证32位算术逻辑单元ALU的加、减、与、移位等基本功能。

4、选定⼏组数据,完成⼏种算术/逻辑运算。

⼆. 实验设备1、 装有Xilinx Vivado的计算机⼀台。

2、LS-CPU-EXB-002教学系统实验箱⼀套。

三. 实验任务1、学习MIPS指令集,熟知指令类型,了解指令功能和编码,归纳基础的ALU运算指令。

2、归纳确定⾃⼰本次实验中准备实现的ALU运算,要求要求⾄少实现5种ALU运算,包含加减运算,其中减法在内部要转换为加法,见表1-1。

表1-1 ALU的控制信号选择端aluc ALU功能3 2 1 00 0 00 0 10 1 00 1 11 0 01 0 11 1 00 1 1 11 1 1 13、根据如图1-1所⽰的结构框图,设计实验⽅案,并⽤Verilog编写相应代码。

4、 对编写的代码进⾏仿真,得到正确的波形图。

5、将以上设计作为⼀个单独的模块,设计⼀个外围模块去调⽤该模块,如图1-2。

外围模块中需调⽤封装好的LCD触摸屏模块,显⽰ALU 的两个源操作数、操作码和运算结果,并且需要利⽤触摸功能输⼊源操作数。

操作码可以考虑⽤LCD触摸屏输⼊,也可⽤拨码开关输⼊。

6、将编写的代码进⾏综合布局布线,并下载到试验箱中的FPGA板⼦上进⾏演⽰。

四. 实验步骤这⾥给出实验代码,具体的实验步骤请看书alu.vmodule alu(a,b,aluc,r,z);input [31:0] a,b;input [3:0] aluc;output [31:0] r;output z;assign r = cal (a,b,aluc);assign z =~|r;function [31:0] cal;input [31:0] a,b;input [3:0] aluc;casex(aluc)4'b0000: cal = a + b;//加4'b0001: cal = a&b;4'b0010: cal = a^b;4'b0011: cal = b<<a[4:0];4'b0100: cal = a-b;4'b0101: cal = a|b;4'b0110: cal ={b[15:0],16'h0};4'b0111: cal = b>>a[4:0];4'b1111: cal = $signed(b)>>> a[4:0];//算术右移endcaseendfunctionendmodulealu-display.v//************************************************************************* // > ⽂件名: alu_display.v// > 描述:ALU显⽰模块,调⽤FPGA板上的IO接⼝和触摸屏// > 作者 : LOONGSON// > ⽇期 : 2016-04-14//************************************************************************* module alu_display(//时钟与复位信号input clk,input resetn,//后缀"n"代表低电平有效//拨码开关,⽤于选择输⼊数input [1:0] input_sel,//00:输⼊为控制信号(alu_control)//10:输⼊为源操作数1(alu_src1)//11:输⼊为源操作数2(alu_src2)//触摸屏相关接⼝,不需要更改output lcd_rst,output lcd_cs,output lcd_rs,output lcd_wr,output lcd_rd,inout[15:0] lcd_data_io,output lcd_bl_ctr,inout ct_int,inout ct_sda,output ct_scl,output ct_rstn);//-----{调⽤ALU模块}beginreg [3:0] alu_control;// ALU控制信号reg [31:0] alu_src1;// ALU操作数1reg [31:0] alu_src2;// ALU操作数2wire [31:0] alu_result;// ALU结果wire alu_z;alu alu_module(alu alu_module(.aluc(alu_control),.a(alu_src1 ),.b(alu_src2 ),.r(alu_result ),.z(alu_z));//-----{调⽤ALU模块}end//---------------------{调⽤触摸屏模块}begin--------------------// //-----{实例化触摸屏}begin//此⼩节不需要更改reg display_valid;reg [39:0] display_name;reg [31:0] display_value;wire [5:0] display_number;wire input_valid;wire [31:0] input_value;lcd_module lcd_module(.clk(clk ),//10Mhz.resetn(resetn ),//调⽤触摸屏的接⼝.display_valid(display_valid ),.display_name(display_name ),.display_value(display_value ),.display_number(display_number),.input_valid(input_valid ),.input_value(input_value ),//lcd触摸屏相关接⼝,不需要更改.lcd_rst(lcd_rst ),.lcd_cs(lcd_cs ),.lcd_rs(lcd_rs ),.lcd_wr(lcd_wr ),.lcd_rd(lcd_rd ),.lcd_data_io(lcd_data_io ),.lcd_bl_ctr(lcd_bl_ctr ),.ct_int(ct_int ),.ct_sda(ct_sda ),.ct_scl(ct_scl ),.ct_rstn(ct_rstn ));//-----{实例化触摸屏}end//-----{从触摸屏获取输⼊}begin//根据实际需要输⼊的数修改此⼩节,//建议对每⼀个数的输⼊,编写单独⼀个always块//当input_sel为00时,表⽰输⼊数控制信号,即alu_control always @(posedge clk)beginif(!resetn)beginalu_control <=12'd0;endelse if(input_valid && input_sel==2'b00)beginalu_control <= input_value[11:0];endend//当input_sel为10时,表⽰输⼊数为源操作数1,即alu_src1 always @(posedge clk)beginif(!resetn)if(!resetn)beginalu_src1 <=32'd0;endelse if(input_valid && input_sel==2'b10)beginalu_src1 <= input_value;endend//当input_sel为11时,表⽰输⼊数为源操作数2,即alu_src2 always @(posedge clk)beginif(!resetn)beginalu_src2 <=32'd0;endelse if(input_valid && input_sel==2'b11)beginalu_src2 <= input_value;endend//-----{从触摸屏获取输⼊}end//-----{输出到触摸屏显⽰}begin//根据需要显⽰的数修改此⼩节,//触摸屏上共有44块显⽰区域,可显⽰44组32位数据//44块显⽰区域从1开始编号,编号为1~44,always @(posedge clk)begincase(display_number)6'd1 :begindisplay_valid <=1'b1;display_name <="SRC_1";display_value <= alu_src1;end6'd2 :begindisplay_valid <=1'b1;display_name <="SRC_2";display_value <= alu_src2;end6'd3 :begindisplay_valid <=1'b1;display_name <="CONTR";display_value <={20'd0, alu_control};end6'd4 :begindisplay_valid <=1'b1;display_name <="RESUL";display_value <= alu_result;end6'd5 :begindisplay_valid <=1'b1;display_name <="ZF";display_value <= alu_z;enddefault:begindisplay_valid <=1'b0;display_name <=40'd0;display_value <=32'd0;endendcaseend//-----{输出到触摸屏显⽰}end//----------------------{调⽤触摸屏模块}end---------------------//endmodulealu_tb.v代码如下:module testbench;// Inputsreg [31:0] a;reg [31:0] b;reg [3:0] aluc;//outputwire [31:0] r;wire z;//Instantiate the Unit Under Test(UUT)alu uut(.a(a),.b(b),.r(r),.aluc(aluc),.z(z));initial begin// Initialize Inputsa=0;b=0;aluc=0;//Wait 100ns for global reset to finish#100;//Add stimulus hereendalways #10 a=$random;//$random为系统任务,产⽣⼀个随机的32位数always #10 b=$random;//#10表⽰等待10个单位时间(10ns),即每过10ns,赋值⼀个随机的32位数 always #10 aluc={$random}%2;//加了拼接符,{$random}产⽣⼀个⾮负数,除2取余得到0或1 endmodulealu.xdc⽂件如下:set_property PACKAGE_PIN AC19 [get_ports clk]set_property PACKAGE_PIN Y3 [get_ports resetn]set_property PACKAGE_PIN AC22 [get_ports input_sel[0]]set_property PACKAGE_PIN AD24 [get_ports input_sel[1]]set_property IOSTANDARD LVCMOS33 [get_ports clk]set_property IOSTANDARD LVCMOS33 [get_ports resetn]set_property IOSTANDARD LVCMOS33 [get_ports input_sel[1]]set_property IOSTANDARD LVCMOS33 [get_ports input_sel[0]]set_property PACKAGE_PIN J25 [get_ports lcd_rst]set_property PACKAGE_PIN H18 [get_ports lcd_cs]set_property PACKAGE_PIN K16 [get_ports lcd_rs]set_property PACKAGE_PIN L8 [get_ports lcd_wr]set_property PACKAGE_PIN K8 [get_ports lcd_rd]set_property PACKAGE_PIN J15 [get_ports lcd_bl_ctr]set_property PACKAGE_PIN H9 [get_ports {lcd_data_io[0]}]set_property PACKAGE_PIN K17 [get_ports {lcd_data_io[1]}]set_property PACKAGE_PIN J20 [get_ports {lcd_data_io[2]}]set_property PACKAGE_PIN M17 [get_ports {lcd_data_io[3]}]set_property PACKAGE_PIN L17 [get_ports {lcd_data_io[4]}]set_property PACKAGE_PIN L17 [get_ports {lcd_data_io[4]}]set_property PACKAGE_PIN L18 [get_ports {lcd_data_io[5]}]set_property PACKAGE_PIN L15 [get_ports {lcd_data_io[6]}]set_property PACKAGE_PIN M15 [get_ports {lcd_data_io[7]}]set_property PACKAGE_PIN M16 [get_ports {lcd_data_io[8]}]set_property PACKAGE_PIN L14 [get_ports {lcd_data_io[9]}]set_property PACKAGE_PIN M14 [get_ports {lcd_data_io[10]}]set_property PACKAGE_PIN F22 [get_ports {lcd_data_io[11]}]set_property PACKAGE_PIN G22 [get_ports {lcd_data_io[12]}]set_property PACKAGE_PIN G21 [get_ports {lcd_data_io[13]}]set_property PACKAGE_PIN H24 [get_ports {lcd_data_io[14]}]set_property PACKAGE_PIN J16 [get_ports {lcd_data_io[15]}]set_property PACKAGE_PIN L19 [get_ports ct_int]set_property PACKAGE_PIN J24 [get_ports ct_sda]set_property PACKAGE_PIN H21 [get_ports ct_scl]set_property PACKAGE_PIN G24 [get_ports ct_rstn]set_property IOSTANDARD LVCMOS33 [get_ports lcd_rst]set_property IOSTANDARD LVCMOS33 [get_ports lcd_cs]set_property IOSTANDARD LVCMOS33 [get_ports lcd_rs]set_property IOSTANDARD LVCMOS33 [get_ports lcd_wr]set_property IOSTANDARD LVCMOS33 [get_ports lcd_rd]set_property IOSTANDARD LVCMOS33 [get_ports lcd_bl_ctr]set_property IOSTANDARD LVCMOS33 [get_ports {lcd_data_io[0]}]set_property IOSTANDARD LVCMOS33 [get_ports {lcd_data_io[1]}]set_property IOSTANDARD LVCMOS33 [get_ports {lcd_data_io[2]}]set_property IOSTANDARD LVCMOS33 [get_ports {lcd_data_io[3]}]set_property IOSTANDARD LVCMOS33 [get_ports {lcd_data_io[4]}]set_property IOSTANDARD LVCMOS33 [get_ports {lcd_data_io[5]}]set_property IOSTANDARD LVCMOS33 [get_ports {lcd_data_io[6]}]set_property IOSTANDARD LVCMOS33 [get_ports {lcd_data_io[7]}]set_property IOSTANDARD LVCMOS33 [get_ports {lcd_data_io[8]}]set_property IOSTANDARD LVCMOS33 [get_ports {lcd_data_io[9]}]set_property IOSTANDARD LVCMOS33 [get_ports {lcd_data_io[10]}]set_property IOSTANDARD LVCMOS33 [get_ports {lcd_data_io[11]}]set_property IOSTANDARD LVCMOS33 [get_ports {lcd_data_io[12]}]set_property IOSTANDARD LVCMOS33 [get_ports {lcd_data_io[13]}]set_property IOSTANDARD LVCMOS33 [get_ports {lcd_data_io[14]}]set_property IOSTANDARD LVCMOS33 [get_ports {lcd_data_io[15]}]set_property IOSTANDARD LVCMOS33 [get_ports ct_int]set_property IOSTANDARD LVCMOS33 [get_ports ct_sda]set_property IOSTANDARD LVCMOS33 [get_ports ct_scl]set_property IOSTANDARD LVCMOS33 [get_ports ct_rstn]拨码开关的连接,通过AC22、AD24拨码开关来控制输⼊SRC_1,SRC_2,CONTR的值五.结果记录及分析(1) 仿真波形。

实验2 ALU 实验要求

实验2 n位ALU的设计与VHDL实现《计算机组成原理》课程(一)实验类型:简单设计,在理解的基础上修改设计(二)实验类别:基础实验(三)实验学时数:2学时(四)实验目的在加法器的基础上,设计一个简单的ALU,能执行简单的n位(如n=6、7或8)算术/逻辑运算,并实现一些基本的PSW标志位。

(五)实验内容设计一个具有8种操作的ALU,其中逻辑运算和算术运算各4种,并测试其结果。

(六)实验要求(1)按照实验要求设计简单ALU,能执行8种操作,分别为:1)加、减、增1、减1等4种n位算术运算;2)与、或、非、异或等4种n位逻辑运算。

参照教材设计ALU的思路,用一位M 作为进行算术运算或逻辑运算的控制位,M=0 时进行算术运算,M=1 时进行逻辑运算。

另外用2位控制变量来表示4种操作。

(2)实现一些基本的PSW标志位:1)进位/借位的输出标志位C;2) 运算结果为零的输出标志位Z;3) 运算结果为溢出的输出标志位V;4) 运算结果为负数的输出标志位N。

(3)加减必须用最基本的1位全加器fa作为基础,可以采用直接由n次1位运算得到n 位的操作。

当n=8时,可以先构造4位加法器,再进一步实现8位加减运算。

注意:算术运算的两个操作数要求都是带符号数,即1位符号位和n-1位数据位。

(4)在实验平台上实现并测试其正确性。

首先构造实验用例,然后自己用笔算结果,接着再对比试验平台上的实验结果,看两者是否吻合。

(七)实验设备TEC-CA组成原理实验箱。

(八)实验课承担单位:信息学院计算机科学与技术系(九)实验步骤建议为便于大家抓住实验设计的思路,掌握基于VHDL设计的方法,对上述的实验内容,建议采用下列的实验步骤。

这实质上就是一种系统设计的思路和方法,也是自顶向下系统设计的常用技巧,不论是软件还是硬件工程都是类似的。

具体如下。

1. 要完成上述的实验,在理解实验所需功能的基础上,画出ALU的方框图,即画出其输入和输出引脚,并标注输入输出引脚的位数;2. 用VHDL实体描述语句对ALU的输入和输出引脚进行描述;3. 考虑ALU的功能的具体实现,利用VHDL的结构体来实现。

并行乘法器-南京理工大学紫金学院vhdl实验报告-eda

EDA技术与应用实验报告实验名称:并行乘法器姓名:学号:班级:通信时间:2013南京理工大学紫金学院电光系一、实验目的1、学习包集和元件例化语句的使用。

2、学习FLU(全加器单元)电路的设计。

3、学习并行乘法电路的设计。

二、实验原理并行乘法器的电路原理图如下图所示,主要由全加器和与门构成。

并行乘法器原理图三、实验内容1、and_2library ieee;use ieee.std_logic_1164.all;entity and_2 isport (a,b:in std_logic;y:out std_logic);end and_2;architecture and_2 of and_2 isbeginy <= a and b;end and_2;2、faulibrary ieee;use ieee.std_logic_1164.all;entity fau isport (a,b,cin:in std_logic;s,cout:out std_logic);end fau;architecture fau of fau isbegins <= a xor b xor cin;cout <= (a and b)or(a and cin)or(b and cin);end fau;3、top_rowlibrary ieee;use ieee.std_logic_1164.all;use work.my_components.all;entity top_row isport (a:in std_logic;b:in std_logic_vector(3 downto 0);sout,cout:out std_logic_vector(2 downto 0);p:out std_logic);end top_row;architecture structural of top_row isbeginU1: component and_2 port map(a,b(3),sout(2));U2: component and_2 port map(a,b(2),sout(1));U3: component and_2 port map(a,b(1),sout(0));U4: component and_2 port map(a,b(0),p);cout(2) <= '0';cout(1) <= '0';cout(0) <= '0';end structural;4、mid_rowlibrary ieee;use ieee.std_logic_1164.all;use work.my_components.all;entity mid_row isport (a:in std_logic;b:in std_logic_vector(3 downto 0);sin,cin:in std_logic_vector(2 downto 0);sout,cout:out std_logic_vector(2 downto 0);p:out std_logic);end mid_row;architecture structural of mid_row issignal and_out:std_logic_vector(2 downto 0);beginU1: component and_2 port map(a,b(3),sout(2));U2: component and_2 port map(a,b(2),and_out(2));U3: component and_2 port map(a,b(1),and_out(1));U4: component and_2 port map(a,b(0),and_out(0));U5: component fau port map(sin(2),cin(2),and_out(2), sout(1), cout(2));U6: component fau port map(sin(1),cin(1),and_out(1), sout(0), cout(1));U7: component fau port map(sin(0),cin(0),and_out(0), p, cout(0));end structural;5、lower_rowlibrary ieee;use ieee.std_logic_1164.all;use work.my_components.all;entity lower_row isport (sin,cin:in std_logic_vector(2 downto 0);p:out std_logic_vector(3 downto 0));end lower_row;architecture structural of lower_row issignal local:std_logic_vector(2 downto 0);beginlocal(0) <= '0';U1: component fau port map(sin(0),cin(0),local(0), p(0),local(1));U2: component fau port map(sin(1),cin(1),local(1), p(1),local(2));U3: component fau port map(sin(2),cin(2),local(2), p(2),p(3));end structural;6、my_componentslibrary ieee;use ieee.std_logic_1164.all;package my_components iscomponent and_2 isport (a,b:in std_logic; y:out std_logic);end component;component fau isport (a,b,cin:in std_logic; s,cout:out std_logic); end component;component top_row isport (a:in std_logic;b:in std_logic_vector(3 downto 0);sout,cout:out std_logic_vector(2 downto 0);p:out std_logic);end component;component mid_row isport (a:in std_logic;b:in std_logic_vector(3 downto 0);sin,cin:in std_logic_vector(2 downto 0);sout,cout:out std_logic_vector(2 downto 0);p:out std_logic);end component;component lower_row isport (sin,cin:in std_logic_vector(2 downto 0);p:out std_logic_vector(3 downto 0));end component;end my_components;7、multiplierlibrary ieee;use ieee.std_logic_1164.all;use work.my_components.all;entity multiplier isport (a,b:in std_logic_vector(3 downto 0);prod:out std_logic_vector(7 downto 0));end multiplier;architecture structural of multiplier istype matrix is array (0 to 3)ofstd_logic_vector (2 downto 0);signal s,c:matrix;beginU1: component top_row port map (a(0),b,s(0),c(0),prod(0));U2: component mid_row port map (a(1),b,s(0),c(0),s(1), c(1),prod(1));U3: component mid_row port map (a(2),b,s(1),c(1),s(2), c(2),prod(2));U4: component mid_row port map (a(3),b,s(2),c(2),s(3), c(3),prod(3));U5: component lower_row port map(s(3),c(3),prod(7 downto 4));end structural;8、仿真9、把multiplier代码改为百位、十位、个位输出代码如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use work.my_components.all;entity multiplier isport (a,b:in std_logic_vector(3 downto 0);hun,ten,one:out std_logic_vector(3 downto 0)); end multiplier;architecture structural of multiplier istype matrix is array (0 to 3)ofstd_logic_vector (2 downto 0);signal s,c:matrix;signal p:std_logic_vector(7 downto 0);beginU1: component top_row port map (a(0),b,s(0),c(0),p(0));U2: component mid_row port map (a(1),b,s(0),c(0),s(1), c(1),p(1));U3: component mid_row port map (a(2),b,s(1),c(1),s(2), c(2),p(2));U4: component mid_row port map (a(3),b,s(2),c(2),s(3), c(3),p(3));U5: component lower_row port map(s(3),c(3),p(7 downto 4));process(p)variable temp:std_logic_vector(7 downto 0);beginif p >"1100_0111" thenhun <="0010";temp:=p-"1100_1000";elsif p>"0110_0011" thenhun <="0001";temp:=p-"0110_0100";elsehun <="0000";temp:=p;end if;if temp>"0101_1001" thenten <="1001";temp:=temp-"0101_1010"; elsif temp>"0100_1111" then ten <="1000";temp:=temp-"1010_0000"; elsif temp>"0100_0101" then ten <="0111";temp:=temp-"0100_0110"; elsif temp>"0011_1011" then ten <="0110";temp:=temp-"0011_1100"; elsif temp>"0011_0001" then ten <="0101";temp:=temp-"0011_0010"; elsif temp>"0010_0111" then ten <="0100";temp:=temp-"0010_1000"; elsif temp>"0001_1101" then ten <="0011";temp:=temp-"0001_1110"; elsif temp>"0001_0011" then ten <="0010";temp:=temp-"0001_0100"; elsif temp>"0000_1001" then ten <="0001";temp:=temp-"0000_1010"; elseten <="0000";temp:=temp;end if;one <=temp(3 downto 0);end process;end structural;四、小结与体会通过本次实验,我对包集和元件例化语句的使用有了更深刻的了解。

南京理工大学电工电子实验报告(多功能数字计时器设计)

南京理工大学电工电子实验报告(多功能数字计时器设计)1. 电路功能设计要求介绍2. 电路原理简介3. 单元电路设计3.1 脉冲发生电路3.2 计时电路3.3 译码显示电路3.4 清零电路3.5 校分电路3.6 仿电台报时电路4.总电路图5.电路调试和改进意见6.实验中遇到的问题、出现原因及解决方法7.实验体会8.附录8.1 元件清单8.2 芯片引脚图和功能表9.参考文献1.电路功能设计要求1、设计制作一个0分00秒~9分59秒的多功能计时器,设计要求如下:1)设计一个脉冲发生电路,为计时器提供秒脉冲(1HZ),为报时电路提供驱动蜂鸣器的高低脉冲信号(1KHZ、2KHZ);12)设计计时电路:完成0分00秒~9分59秒的计时、译码、显示功能;3)设计清零电路:具有开机自动清零功能,并且在任何时候,按动清零开关,可以对计时器进行手动清零。

4)设计校分电路:在任何时候,拨动校分开关,可进行快速校分。

(校分隔秒)5)设计报时电路:使数字计时器从9分53秒开始报时,每隔一秒发一声,共发三声低音,一声高音;即9分53秒、9分55秒、9分57秒发低音(频率1kHz),9分59秒发高音(频率2kHz);6)系统级联。

将以上电路进行级联完成计时器的所有功能。

7)可以增加数字计时器附加功能:定时、动态显示等。

2. 电路原理简介数字计时器由计时电路、译码显示电路、脉冲发生电路、校分电路、清零电路和报时电路这几部分组成。

其原理框图如下:3. 单元电路设计3.1 脉冲发生电路振荡器是数字钟的核心。

采用石英晶体构成振荡器电路,产生稳定的高频脉冲信号,作为数字钟的时间基准,再经过分频器输出标准秒脉冲(1HZ)。

分频器的功能主要有两个:一是产生标准秒脉冲(1HZ)。

二是提供功能扩展电路所需驱动脉冲信号(1KHZ、2KHZ)。

15 采用晶体的固有频率为32768HZ=2HZ。

2CC4060、74LS74电路图如下所示:2Q5Q4Q143.2 计时电路CC4518(分位、秒个位)、74LS161(秒十位)“0”“1”“o”“0”3.3 译码显示电路译码器 CC4511 显示器共阴LED七段字型数码管 33.4 清零电路3.5 校分电路3.6 仿电台报时电路44.总电路图Q5Q42Q145.电路调试和改进意见先接显示电路,显示电路接完,接入电源,当三个数码管都能正常显示8的时候说明接入正确。

ALU(算术逻辑运算单元)的设计

EDA技术与应用实验报告(四)实验名称:ALU(算术逻辑运算单元)的设计姓名:陈丹学号:100401202班级:电信(2)班时间:2012.12.11南京理工大学紫金学院电光系一、实验目的1、学习包集和元件例化语句的使用。

2、学习ALU电路的设计。

二、实验原理1、ALU原理ALU的电路原理图如图1 所示,主要由算术运算单元、逻辑单元、选择单元构成。

图1ALU功能表如表1 所示。

表12、元件、包集在结构体的层次化设计中,采用结构描述方法就是通过调用库中的元件或者已经设计好的模块来完成相应的设计。

在这种结构体中,功能描述就像网表一样来表示模块和模块之间的互联。

如ALU 是由算术单元、逻辑单元、多路复用器互相连接而构成。

而以上三个模块是由相应的VHDL 代码产生的,在VHDL 输入方式下,如果要将三个模块连接起来,就要用到元件例化语句。

元件例化语句分为元件声明和元件例化。

1、元件声明在VHDL 代码中要引入设计好的模块,首先要在结构体的说明部分对要引入的模块进行说明。

然后使用元件例化语句引入模块。

元件声明语句格式:component 引入的元件(或模块)名port(端口说明);end component;注意:元件说明语句要放在“architecture”和“begin”之间。

2、元件例化语句为将引入的元件正确地嵌入到高一层的结构体描述中,就必须将被引用的元件端口信号与结构体相应端口信号正确地连接起来,元件例化语句可以实现该功能。

元件例化语句格式:标号名:元件名(模块名)port map(端口映射);标号名是元件例化语句的唯一标识,且结构体中的标识必须是唯一的;端口映射分为:位置映射、名称映射。

位置映射指port map 中实际信号的书写顺序与component 中端口说明中的信号书写顺序一致,位置映射对书写顺序要求很严格,不能颠倒;名称映射指port map 中将引用的元件的端口信号名称赋予结构体中要使用元件的各个信号,名称映射的书写顺序要求不严格,顺序可以颠倒。

ALU运算器实验报告

计算机组成与系统结构算术逻辑部件实验报告姓名:同组成员:指导老师:实验时间:2012年3月28日一、实验名称:算术逻辑部件的设计二、实验设备:DE2-70仿真实验板三、实验原理:输入为两个4位操作数A和B,其中,核心部件是能够进行加减运算的加法器,加法器的输出除了和、差的结果Add-Result以外,还有进位标志外,还有进位标志Add-carry、零标志Zero、溢出标志Add-Overflow和标志符号Add-Sign。

在操作控制端ALUctr的控制下,在ALU中执行“加法”、“减法”、“按位或”、“带符号整数比较小于置1”和“无符号数比较小于置1”等运算,Result作为ALU运算的结果被输出,同时,零标志Zero和溢出标志Overflow也被作为ALU的结果标志信息输出。

ALU的操作由一个ALU操作控制信号生成部件产生的控制信号来控制,该控制信号逻辑的输入是ALUctr信号,,输出有4个控制信号:1、SUBctr用来控制ALU执行加法还是减法运算,当SUBctr=1时做减法,当SUBctr=0时做加法;2、OPctr用来控制选择哪种运算的结果作为Result的输出,因为11条目标指令中只有三种运算结果可能:加减,按位或和小于置1,所以OPctr需要两位;3、OVctr用来控制是否要进行溢出判断,当OVctr=1时,需要判断溢出,此时,若结果发生溢出,则溢出标志Overflow为1;当OVctr=0时,无须判断溢出,此时,即使结果发生溢出,溢出标志Overflow也不为1;4、SIGctr信号控制ALU是执行“带符号整数比较小于置于1”还是“无符号数比较小于置1”功能,当SIGctr=0,则执行“无符号数比较小于置1”,当SIGctr=1,则执行“带符号整数比较小于置1”。

ALUctr的三位编码及其对应的操作类型和ALU控制信号ALUctr<2:0> 操作类型SUBctr OVctr SIGctr OPctr<1:0> OPctr的含义0 0 0 addu 0 0 ×0 0 选择加法器的输出结果0 0 1 add 0 1 ×0 0 选择加法器的输出结果0 1 0 or ×0 ×0 1 选择”按位或”结果输出0 1 1 (未用)1 0 0 subu 1 0 ×0 0 选择加法器的输出结果1 0 1 sub 1 1 ×0 0 选择加法器的输出结果1 1 0 sltu 1 0 0 1 0 选择小于置位结果输出1 1 1 slt 1 0 1 1 0 选择小于置位结果输出四、实验结果:通过控制ALUctr、SUBctr、OVctr、SIGctr以及OPctr等控制端来选择需要进行的操作,通过拨动开关来设置我所需要的操作数,通过二极管的发光情况来记录对操作数计算后得到的结果,然后将实际结果与预期结果相匹配,将所有的操作进行过后,比较后发现实际结果均与预期结果全部一致,实验验证成功。

计算机组成原理数据通路实验报告

计算机组成原理数据通路实验报告计算机组成原理实验报告计算机组成原理实验报告实验一基本运算器实验一、实验目的1. 了解运算器的组成结构2. 掌握运算器的工作原理3. 深刻理解运算器的控制信号二、实验设备PC机一台、TD-CMA实验系统一套三、实验原理1. (思考题)运算器的组成包括算数逻辑运算单元ALU(Arithmetic and Logic Unit)、浮点运算单元FPU(Floating Point Unit)、通用寄存器组、专用寄存器组。

①算术逻辑运算单元ALU (Arithmetic and Logic Unit)ALU主要完成对二进制数据的定点算术运算(加减乘除)、逻辑运算(与或非异或)以及移位操作。

在某些CPU中还有专门用于处理移位操作的移位器。

通常ALU由两个输入端和一个输出端。

整数单元有时也称为IEU(IntegerExecution Unit)。

我们通常所说的“CPU 是XX位的”就是指ALU所能处理的数据的位数。

②浮点运算单元FPU(Floating Point Unit)FPU主要负责浮点运算和高精度整数运算。

有些FPU还具有向量运算的功能,另外一些则有专门的向量处理单元。

③通用寄存器组通用寄存器组是一组最快的存储器,用来保存参加运算的操作数和中间结果。

④专用寄存器专用寄存器通常是一些状态寄存器,不能通过程序改变,由CPU自己控制,表明某种状态。

而运算器内部有三个独立运算部件,分别为算术、逻辑和移位运算部件,逻辑运算部件由逻辑门构成,而后面又有专门的算术运算部件设计实验。

下图为运算器内部原理构造图2. 运算器的控制信号实验箱中所有单元的T1、T2、T3、T4都连接至控制总线单元的T1、T2、T3、T4,CLR都连接至CON单元的CLR按钮。

T4由时序单元的TS4提供(脉冲信号),其余控制信号均由CON单元的二进制数据开关模拟给出。

控制信号中除T4为脉冲信号外,其余均为电平信号,其中ALU_B为低有效,其余为高有效。

VHDL实验报告

专用集成电路实验报告13050Z011305024237刘德文实验一开发平台软件安装与认知实验实验内容1、本实验以三线八线译码器(LS74138)为例,在Xilinx ISE 9.2软件平台上完成设计电路的VHDL文本输入、语法检查、编译、仿真、管脚分配和编程下载等操作。

下载芯片选择Xilinx公司的CoolRunner II系列XC2C256-7PQ208作为目标仿真芯片。

2、用1中所设计的的三线八线译码器(LS74138)生成一个LS74138元件,在Xilinx ISE9.2软件原理图设计平台上完成LS74138元件的调用,用原理图的方法设计三线八线译码器(LS74138),实现编译,仿真,管脚分配和编程下载等操作。

源程序:library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;-- Uncomment the following lines to use the declarations that are-- provided for instantiating Xilinx primitive components.--library UNISIM;--use UNISIM.VComponents.all;entity ls74138 isPort ( g1 : in std_logic;g2 : in std_logic;inp : in std_logic_vector(2 downto 0);y : out std_logic_vector(7 downto 0)); end ls74138;architecture Behavioral of ls74138 isbeginprocess(g1,g2,inp)beginif((g1 and g2)='1') thencase inp iswhen "000"=>y<="00000001";when "001"=>y<="00000010";when "010"=>y<="00000100";when "011"=>y<="00001000";when "100"=>y<="00010000";when "101"=>y<="00100000";when "110"=>y<="01000000";when "111"=>y<="10000000";when others=>y<="00000000";end case;elsey<="00000000";end if;end process;end Behavioral;波形文件:生成元器件及连接电路思考:有程序可以看出,定义了三个输入端,一个输出端。

算术逻辑单元alu课程设计

算术逻辑单元alu课程设计一、教学目标本课程的教学目标是让学生掌握算术逻辑单元(ALU)的基本原理和操作,培养学生解决复杂计算问题的能力。

具体目标如下:1.知识目标:–理解ALU的基本组成和功能;–掌握ALU的主要操作,包括加法、减法、乘法和除法;–了解ALU在计算机系统中的应用。

2.技能目标:–能够运用ALU的基本操作解决实际计算问题;–能够设计和实现简单的ALU电路;–能够使用编程语言实现ALU的功能。

3.情感态度价值观目标:–培养学生对计算机科学的兴趣和好奇心;–培养学生的团队合作意识和问题解决能力;–培养学生对算术逻辑单元在现代科技中的重要性的认识。

二、教学内容本课程的教学内容主要包括ALU的基本原理、操作和应用。

具体安排如下:1.第一章:ALU概述–ALU的定义和作用;–ALU的基本组成和功能;–ALU的输入和输出。

2.第二章:加法操作–加法的基本原理;–加法的ALU实现;–加法的应用举例。

3.第三章:减法操作–减法的基本原理;–减法的ALU实现;–减法的应用举例。

4.第四章:乘法操作–乘法的基本原理;–乘法的ALU实现;–乘法的应用举例。

5.第五章:除法操作–除法的基本原理;–除法的ALU实现;–除法的应用举例。

6.第六章:ALU在计算机系统中的应用–ALU在中央处理器(CPU)中的作用;–ALU在计算机图形处理中的作用;–ALU在其他计算机系统中的应用。

三、教学方法为了激发学生的学习兴趣和主动性,本课程将采用多种教学方法,包括讲授法、讨论法、案例分析法和实验法。

1.讲授法:通过教师的讲解和演示,向学生传授ALU的基本原理和操作;2.讨论法:学生进行小组讨论,促进学生之间的交流和合作;3.案例分析法:通过分析实际案例,让学生了解ALU在计算机系统中的应用;4.实验法:安排实验课程,让学生亲自动手设计和实现简单的ALU电路。

四、教学资源为了支持教学内容和教学方法的实施,丰富学生的学习体验,我们将选择和准备以下教学资源:1.教材:选用权威的计算机科学教材,介绍ALU的基本原理和操作;2.参考书:提供相关的参考书籍,供学生进一步深入学习;3.多媒体资料:制作多媒体课件和教学视频,帮助学生形象地理解ALU的功能;4.实验设备:准备实验所需的硬件设备,让学生能够亲身体验ALU的操作。

实验二-算术逻辑单元实验

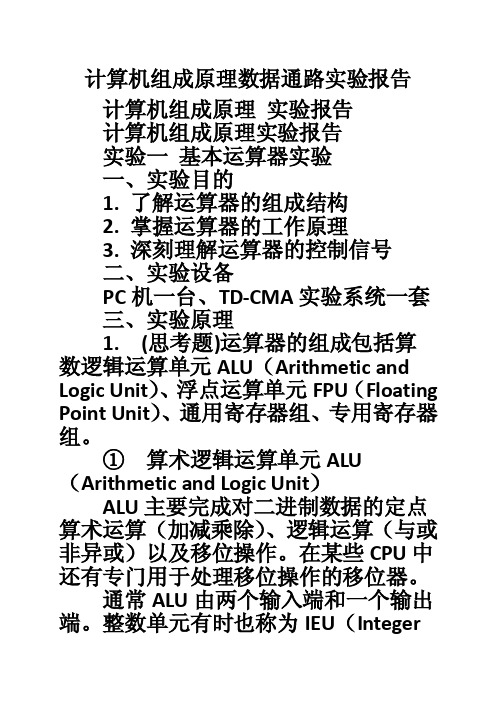

实验二算术逻辑单元(ALU)的设计与实现实验目的1.认识算术逻辑单元的功能及意义2.掌握算术逻辑单元的结构与实现3.进一步熟练Modelsim、Vivado软件和Verilog硬件描述语言的使用4.理解Digilent N4 DDR FPGA开发板上数码管显示原理实验原理1.ALU算术逻辑单元(Arithmetic/Logic Unit , ALU)是现代计算机的核心部件之一。

其内部由算术和逻辑操作部件组合而成,可以实现整数加、减等算术运算和与、或等逻辑运算。

一个典型的算术逻辑单元由两路N位输入、一路N位输出、一组功能选择信号和一些标志位(flag)组成。

两路N位输入数据作为参与运算的两个操作数,输入到ALU中,通过改变功能选择信号,控制ALU对两操作数进行不同的算术或逻辑运算操作,并将N位的结果输出,与结果一同输出的还有运算产生的标志位,例如运算结果为零的标记信号Z(zero)与运算结果溢出的标记信号O(over)、进位标志C(CY)、符号位S(SF)等,如图2-1所示。

图2- 1ALU模块示意图在本次实验中,我们把输入和输出的数据长度定为4位,数据输入命名为A、B,数据输出为F,功能控制信号输入为opcode,进位输入为C n,只产生结果为零的zero标志位。

功能控制信号opcode的定义如表2-1所示。

例如:opcode=0001,运算器实现加法运算。

2.数码管显示关于N4 DDR开发板上数码管的显示原理,参见前面的实验准备部分内容。

实验内容1.基础实验。

用实验调试软件验证ALU的功能,并操作分析、记录结果。

图2- 2 ALU虚拟实验示意图(1)运算功能和控制信号①输入输出对于的开关指示灯分配如下:输入信号A:SW(4-7) B:SW(3-0) Cn:SW8 opcode:SW(12-9)输出信号F:LD(12-15) 标志位S :LD(3) Z LD(2) O: LD(1) C: LD(0)②各种运算对应的控制信号及功能,如下表。

三位计时电路设计,南京理工大学紫金学院vhdl实验报告,eda

EDA技术与应用实验报告实验名称:三位计时电路设计姓名:学号:班级:通信时间:2013南京理工大学紫金学院电光系一、实验目的1、学习利用顺序语句描述电路的方法。

2、学习进程、常用顺序语句的使用。

3、掌握分频电路的设计;掌握利用不完整条件语句构成时序逻辑电路的方法。

二、实验原理1、if语句if语句是具有条件控制功能的语句,它根据指定的条件及其条件是否成立来确定语句的执行顺序,格式如下。

1)格式1if 条件1 then第1组顺序语句;Elsif 条件2 then第2组顺序语句;……elsif 条件 n then第n组顺序语句;else第n+1组顺序语句;end if;在该形式的if语句中,只要满足条件1到条件n中的一个条件就执行一条顺序语句,且最优先的条件为条件1,次要的条件列到后面。

2)格式2(嵌套)if 条件1 thenif 条件2 then……一组顺序语句end if;end if;在该形式的if语句中,只有满足条件1到条件n中的所有条件才能执行相应的顺序语句,且最优先的条件为条件1,次要的条件列到后面。

3)格式3if 条件 then顺序语句;else顺序语句;end if;注意:只有不完整的条件语句才能构成时序逻辑电路,完整的条件语句只能构成组合逻辑电路。

2、进程语句进程主要用于描述顺序语句,其格式如下:标记:process (敏感信号表)声明语句;begin顺序语句end process;声明语句中可以定义一些局部量,可以包括数据类型、常数、变量、属性、子程序等,不能定义信号。

进程语句本为一无限循环语句,进程的启动由敏感信号的变化来启动,否则必须有一个wait语句来激励。

虽然进程中包含了顺序语句,但是进程本身是并行语句,即同一结构体中不同进程是并行运行的。

信号和变量3、信号信号代表电路内部信号传输线路,在元件之间起互连作用,相当于连线,可以通过端口和其他模块相连接。

说明:1)信号时一个全局量,可以在ENTITY和ARCHITECTURE中定义,不可以在进程和子程序的顺序语句中定义信号,但可以在VHDL语句的并行部分和顺序部分同时使用。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

EDA技术与应用实验报告实验名称:ALU(算术逻辑运算单元)的设计姓名:学号:班级:通信时间:2013南京理工大学紫金学院电光系一、实验目的1、学习包集和元件例化语句的使用。

2、学习ALU电路的设计。

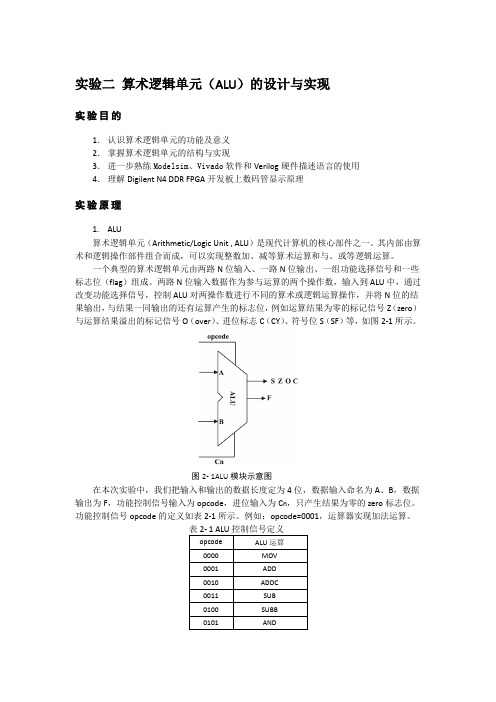

二、实验原理1、ALU原理ALU的电路原理图如图1 所示,主要由算术运算单元、逻辑单元、选择单元构成。

图1ALU功能表如表1 所示。

表12、元件、包集在结构体的层次化设计中,采用结构描述方法就是通过调用库中的元件或者已经设计好的模块来完成相应的设计。

在这种结构体中,功能描述就像网表一样来表示模块和模块之间的互联。

如ALU 是由算术单元、逻辑单元、多路复用器互相连接而构成。

而以上三个模块是由相应的VHDL 代码产生的,在VHDL 输入方式下,如果要将三个模块连接起来,就要用到元件例化语句。

元件例化语句分为元件声明和元件例化。

(1)元件声明在VHDL 代码中要引入设计好的模块,首先要在结构体的说明部分对要引入的模块进行说明。

然后使用元件例化语句引入模块。

元件声明语句格式:component 引入的元件(或模块)名port(端口说明);end component;注意:元件说明语句要放在“architecture”和“begin”之间。

(2)元件例化语句为将引入的元件正确地嵌入到高一层的结构体描述中,就必须将被引用的元件端口信号与结构体相应端口信号正确地连接起来,元件例化语句可以实现该功能。

元件例化语句格式:标号名:元件名(模块名) port map(端口映射);标号名是元件例化语句的唯一标识,且结构体中的标识必须是唯一的;端口映射分为:位置映射、名称映射。

位置映射指 port map 中实际信号的书写顺序与component 中端口说明中的信号书写顺序一致,位置映射对书写顺序要求很严格,不能颠倒;名称映射指port map 中将引用的元件的端口信号名称赋予结构体中要使用元件的各个信号,名称映射的书写顺序要求不严格,顺序可以颠倒。

(3)包集在实体及结构体中定义的对象、数据类型,对另外代码的实体是不能使用的。

但是在同一工程的不同VHDL 文件中,有些对象、数据类型、子程序等常常被重复使用。

为方便VHDL 代码的编写,简化电路设计,故引入包集。

包集也称为程序包。

包集主要由两部分组成:程序包说明和程序包体。

其中,程序包体是可选的,一般程序包说明列出所有项的名称,而程序包体给出各项的细节。

程序包说明中包含的内容很多,只要是通用的全局量,都可以在程序包中加以说明。

主要内容如下:对象(常量、变量、信号)的数据类型说明。

对象(常量、变量、信号)子类型的数值范围说明。

函数与过程说明。

元件语句说明。

程序包说明的书写格式如下:package 程序包名 is说明语句;end 程序包名;程序包名:设计者自定义便于记忆的标识符。

说明语句:包括各种类型的说明语句。

程序包体书写格式如下:package body 程序包名 is顺序语句;end 程序包名;注意:程序包定义的内容不是自动可见的,不是自动被使用。

若某个实体及结构体设计需要使用程序包,可以使用use 语句制定要使用的程序包。

如:use work.程序包名.all;三、实验内容1、建立工程、输入代码(1)算术单元arith_unitlibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity arith_unit isport (a,b:in std_logic_vector(7 downto 0);sel:in std_logic_vector(2 downto 0);cin:in std_logic;x:out std_logic_vector(7 downto 0));end arith_unit;architecture arith_unit of arith_unit isbeginwith sel selectx <=a when "000",a+1 when "001",a-1 when "010",b when "011",b+1 when "100",b-1 when "101",a+b when "110",a+b+cin when "111",null when others;end arith_unit;(2)逻辑单元logic_unitlibrary ieee;use ieee.std_logic_1164.all;entity logic_unit isport (a,b:in std_logic_vector(7 downto 0);sel:in std_logic_vector(2 downto 0);end logic_unit;architecture logic_unit of logic_unit isbeginwith sel selectx <=not a when "000",not b when "001",a andb when "010",a orb when "011",a nandb when "100",a norb when "101",a xorb when "110",a xorb when "111",null when others;end logic_unit;(3)多路复用器sellibrary ieee;use ieee.std_logic_1164.all;entity mux isport (arith,logic:in std_logic_vector(7 downto 0);sel:in std_logic_vector(3 downto 0);x:out std_logic_vector(7 downto 0)); end mux;architecture mux of mux isbeginwith sel(3) selectx <= arith when '0',logic when '1',null when others;end mux;(4)package定义library ieee;use ieee.std_logic_1164.all;package alu iscomponent arith_unit isport (a,b:in std_logic_vector(7 downto 0);sel:in std_logic_vector(2 downto 0);cin:in std_logic;end component;component logic_unit isport (a,b:in std_logic_vector(7 downto 0);sel:in std_logic_vector(2 downto 0);x:out std_logic_vector(7 downto 0)); end component;component mux isport (arith,logic:in std_logic_vector(7 downto 0);sel:in std_logic_vector(3 downto 0);x:out std_logic_vector(7 downto 0)); end component;end alu;(5)alu_unit单元library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use work.alu.all;entity alu_unit isport (a,b:in std_logic_vector(7 downto 0);cin:in std_logic;clk:in std_logic;sel:buffer std_logic_vector(3 downto 0);y:out std_logic_vector(7 downto 0)); end alu_unit;architecture alu_unit of alu_unit issignal x1,x2:std_logic_vector(7 downto 0);beginprocess(clk)variable s:std_logic_vector(3 downto 0);beginif(clk'event and clk='1') thens:=s+1;end if;sel<=s;end process;U1:arith_unit port map(a,b,sel(2 downto 0),cin,x1);U2:logic_unit port map(a,b,sel(2 downto 0),x2);U3:mux port map(x1,x2,sel,y);end alu_unit;2、编译3、仿真4、管脚配置5、下载将文件下载到实验箱,对实验箱进行操作。

四、小结与体会通过本次实验,我们学会了包集和元件例化语句的使用,学会了ALU电路的设计。