基于51单片机的数字秒表设计(最新整理)

基于51单片机的数字秒表课程设计、毕业设计论文

基于51单片机的数字秒表课程设计、毕业设计论文三、课题名称基于51单片的数字秒表设计二、目的和意义1、通过本次课程设计可以灵活运用单片机的基础知识,依据课程设计内容,能够完成从硬件电路图设计,到电路搭建焊接,再到软件编程及系统调试实现系统功能,完成课程设计,加深对单片机基础知识的理解,并灵活运用,将各门知识综合应用。

2、本次课程设计还可以通过上网查询器件资料,培养对新知识新技术的独立的学习能力和应用能力。

3、在这次课程设计中,我们运用到了很多一切所学的知识和一些很有用的软件和工具,如keil4编程软件、Proteus仿真软件、Visio软件、等。

4、通过独立完成一个小的数字秒表系统设计,从硬件设计到软件设计,增强分析问题、解决问题的能力,为日后的毕业设计及科研工作奠定良好的基础。

5、掌握51单片机软件编程知识、实现功能、设计方法,及KEIL软件使用方法;6、应用所学模拟电子线路的知识,掌握电路的设计与应用;7、熟悉PROTEUS的设计与仿真;8、STC——ISP的使用方法;9、掌握焊接电子元器件的方法以及查阅元件功能与参数的方法、步骤。

三、设计目标或任务要求1 、设计目标以单片机为核心,设计数字秒表。

通过硬件电路设计,软件设计,电路搭建,作品调试。

最后完成本次课程设计。

2 、设计要求1、计时范围:0~59分59.59秒,整数四位数和小数两位数显示;2、计时精度10毫秒;3、复位按钮,计时器清零,并做好下次及时准备;4、可以对三个对象(A、B)计时,具有启/停控制;5、设开始、停止A、停止B、显示A、显示B、复位按钮。

四、任务分析、设计方案1、任务分析数字电子秒表具有显示直观、读取方便、精度高等优点,在计时中广泛使用。

本设计用单片机组成数字电子秒表,力求结构简单、精度高为目标。

设计中包括硬件电路的设计和系统程序的设计。

其硬件电路主要有主控制器,计时与显示电路和回零、启动和停表电路等。

主控制器采用单片机89C52显示电路采用共阳极LED数码管显示计时时间。

基于51单片机的数字秒表设计

摘要本设计是基于AT89S51单片机的简易数字秒表设计,主要组成是以51单片机最小系统为核心,通过运用单片机的振荡电路实现计时同时用数码管同步显示。

本秒表最大计时为99秒。

本设计的特点是:大部分功能通过软件实现,使电路简单明了,系统稳定性好。

关键词:AT89S51 振荡电路计时数码管目录1设计概述 (1)1.1AT89S51概述 (1)1.2系统设计功能概述 (1)2系统设计 (2)2.1设计思路 (2)2.2硬件设计 (2)2.2.1单片机最小系统的设计 (2)2.2.2数码管显示电路设计 (3)2.3软件设计 (7)2.3.1软件设计流程图 (7)2.3.2消除开关抖动 (9)2.3.3数码管延时显示程序 (9)2.3.4延时1秒的程序 (10)3软件调试和结果 (10)3.1软件调试与下载 (10)3.2硬件仿真 (11)4心得体会 (12)参考文献 (14)附录 (15)I基于单片机的数字秒表设计主程序 (15)IIPCB电路图 (17)III实物图 (17)11 设计概述1.1 AT89S51概述AT89S51是一个低功耗,高性能CMOS 8位单片机,片内含4k Bytes ISP(In -system programmable)的可反复擦写1000次的Flash 只读程序存储器,器件采用ATMEL 公司的高密度、非易失性存储技术制造,兼容标准MCS -51指令系统及80C51引脚结构,芯片内集成了通用8位中央处理器和ISP Flash 存储单元,功能强大的微型计算机的AT89S51可为许多嵌入式控制应用系统提供高性价比的解决方案。

AT89S51具有如下特点:40个引脚,4k Bytes Flash 片内程序存储器,128 bytes 的随机存取数据存储器(RAM ),32个外部双向输入/输出(I/O )口,5个中断优先级2层中断嵌套中断,2个16位可编程定时计数器,2个全双工串行通信口,看门狗(WDT )电路,片内时钟振荡器。

51单片机实验 秒表设计

实验报告一、实验名称10秒计时的秒表设计二、实验内容精确到0.1秒的秒表三、相关模块led数码管、usb、独立键盘四、实验代码#include "reg52.h"typedef unsigned int u16; //对数据类型进行声明定义typedef unsigned char u8;sbit LSA=P2^2;sbit LSB=P2^3;sbit LSC=P2^4;sbit k1=P3^1;sbit k2=P3^0;sbit k3=P3^2;sbit k4=P3^3;u8 code smgduan[17]={0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d,0x07,0x7f,0x6f,0x77,0x7c,0x39,0x5e,0x79,0x71};u16 s,sec;unsigned int i;unsigned int j;unsigned int a,b,c,d;u8 mb[2];void Timer0Init(){TMOD|=0X01;//选择为定时器0模式,工作方式1,仅用TR0打开启动。

TH0=0XFC; //给定时器赋初值,定时1msTL0=0X18;TR0=0;//打开定时器}void delay(u16 n){while(n--);}void DigDisplay1(u16 i){switch(i){case(0):LSA=0;LSB=0;LSC=0; break;case(1):LSA=1;LSB=0;LSC=0; break;case(2):LSA=0;LSB=1;LSC=0; break;case(3):LSA=1;LSB=1;LSC=0; break;case(4):LSA=0;LSB=0;LSC=1; break;case(5):LSA=1;LSB=0;LSC=1; break;case(6):LSA=0;LSB=1;LSC=1; break;case(7):LSA=1;LSB=1;LSC=1; break;}if (i==1){P0=smgduan[mb[i]]+0x80;//发送段码}else{P0=smgduan[mb[i]];}delay(1); //间隔一段时间扫描P0=0x00;//消隐}void DigDisplay2(u16 i){i=i+3;switch(i){case(0):LSA=0;LSB=0;LSC=0; break;case(1):LSA=1;LSB=0;LSC=0; break;case(2):LSA=0;LSB=1;LSC=0; break;case(3):LSA=1;LSB=1;LSC=0; break;case(4):LSA=0;LSB=0;LSC=1; break;case(5):LSA=1;LSB=0;LSC=1; break;case(6):LSA=0;LSB=1;LSC=1; break;case(7):LSA=1;LSB=1;LSC=1; break;}if (i==4){P0=smgduan[a]+0x80;}else{P0=smgduan[b];}delay(1);P0=0x00;}void DigDisplay3(u16 i){i=i+6;switch(i){case(0):LSA=0;LSB=0;LSC=0; break;case(1):LSA=1;LSB=0;LSC=0; break;case(2):LSA=0;LSB=1;LSC=0; break;case(3):LSA=1;LSB=1;LSC=0; break;case(4):LSA=0;LSB=0;LSC=1; break;case(5):LSA=1;LSB=0;LSC=1; break;case(6):LSA=0;LSB=1;LSC=1; break;case(7):LSA=1;LSB=1;LSC=1; break;}if (i==7){P0=smgduan[c]+0x80;}else{P0=smgduan[d];}delay(1);P0=0x00;}void key1(){delay(10);if(k1==0){TR0=!TR0;while(!k1);}}void key2(){delay(10);if(k2==0){s=0;sec=0;while(!k2);}}void key3(){delay(10);if(k3==0){if (j==0) j=1;else j=0;if (j==1){a=mb[1];b=mb[0];}if (j==0){c=mb[1];d=mb[0];}while(!k3);}}void key4(){delay(10);if(k4==0){s=0;sec=0;a=0;b=0;c=0;d=0;while(!k2);}}void main(){Timer0Init();i=0;j=0;while(1){delay(10);key1();if(TF0==1){TF0=0;TH0=0XFC; //给定时器赋初值,定时1msTL0=0X18;s++;}if(s==60){s=0;sec++;if(sec==100)sec=100;}key2();mb[0]=sec%10;mb[1]=(sec/10)%10;key3();DigDisplay1(i);DigDisplay2(i);DigDisplay3(i);i++;i=i%2;key4();}}五、实验效果K1作用:启动、开始或暂停计时K2作用:计数位清零K3作用:记录当前时间并显示K4作用:清零所有的数码管六、实验遇到的问题经过前几次的实验,0到10秒的计数已经不成问题,本次实验的难点主要在几个按键的功能实现上。

基于51单片机的数字秒表课程设计

电气与自动化工程学院卓越工程师培养计划暑期实训报告题目秒表系统的设计年级11级专业自动化班级卓越班学号*********姓名俞雷地点大学生创新实验室日期2012年8月12日~2012年8月20日目录一、单片机简介............................................................................- 2 -二、设计目标................................................................................- 3 -1、设计目的: (3)2、具体操作: (3)三、硬件设计................................................................................- 4 -原理图:. (4)四、系统的软件设计....................................................................- 5 -1、软件整体设计思路: (5)2、软件流程图: (5)3、程序: (6)(1)数码管秒表显示程序: ...................................................- 6 -(2)1602液晶秒表显示程序:............................................ - 13 -五、系统的调试及设计结果..................................................... - 18 -1602液晶——秒表显示效果图:. (18)LED数码管——秒表显示效果图: (18)六、创新实验室课程设计小结................................................. - 19 -一、单片机简介单片机以其高可靠性、高性价比、低电压、低功耗等一系列优点,近几年得到迅猛发展和大范围推广,广泛应用于工业控制系统,数据采集系统、智能化仪器仪表,及通讯设备、日常消费类产品、玩具等。

单片机课程设计_基于单片机的数字秒表设计

单片机课程设计_基于单片机的数字秒表设计在当今科技迅速发展的时代,电子设备的应用无处不在,其中数字秒表作为一种常见的计时工具,具有广泛的应用场景,如体育比赛、科学实验、工业生产等。

本次课程设计旨在基于单片机技术实现一个数字秒表,通过对硬件电路的设计和软件程序的编写,掌握单片机系统的开发流程和方法,提高实践动手能力和解决问题的能力。

一、设计要求1、能够实现秒表的启动、暂停、复位功能。

2、计时精度达到 001 秒。

3、能够通过数码管显示计时结果。

二、系统方案设计1、硬件设计单片机选型:选用常见的 STC89C52 单片机作为核心控制器,其具有性能稳定、价格低廉、易于编程等优点。

显示模块:采用 8 位共阴极数码管作为显示器件,通过动态扫描的方式实现数字的显示。

按键模块:设置三个独立按键,分别用于启动、暂停和复位操作。

时钟模块:使用单片机内部的定时器/计数器产生精确的时钟信号,实现计时功能。

2、软件设计主程序:负责系统的初始化、按键扫描和计时处理等。

中断服务程序:利用定时器中断实现 001 秒的定时,更新计时数据。

三、硬件电路设计1、单片机最小系统包括单片机芯片、晶振电路和复位电路。

晶振频率选择 12MHz,为单片机提供时钟信号。

复位电路采用上电复位和手动复位相结合的方式,确保系统能够可靠复位。

2、显示电路将 8 位数码管的段选引脚通过限流电阻连接到单片机的 P0 口,位选引脚通过三极管连接到单片机的 P2 口。

通过动态扫描的方式,依次点亮每个数码管,实现数字的显示。

3、按键电路三个按键分别连接到单片机的 P10、P11 和 P12 引脚,采用低电平有效。

当按键按下时,相应引脚的电平被拉低,单片机通过检测引脚电平的变化来判断按键的操作。

四、软件程序设计1、主程序流程系统初始化后,进入主循环。

在主循环中,不断扫描按键状态,如果检测到启动按键按下,则启动计时;如果检测到暂停按键按下,则暂停计时;如果检测到复位按键按下,则将计时数据清零。

基于51单片机的秒表设计报告

课程名称:微机原理课程设计题目:基于51单片机的秒表设计随着社会的发展,单片机已经渗透到我们生活中的各个领域,广泛应用于仪器仪表、家用电器、医用设备、航空航天、专用设备的智能化管理及过程控制等。

本设计就是由单片机STC89C52RC芯片和四位一体LED数码管为核心,辅以必要的电路,构成了一个单片机电子秒表。

秒表是一种常用的测试仪器,它可以用在百米赛跑等需要精确计时的地方,为人们的生活提供了很大的方便。

该单片机电子秒表布置合理,全部器件分布在7*9cm洞洞板上,看起来小巧精简。

采用的是单片机内部定时/计数器计时,走时非常精确而且不易出错。

0.56英寸的四位数码管发出红光,可以直观地显示时间。

一个控制按键就可以控制秒表的计数与停止,按一下控制键,秒表工作状态就由计时变为计时变为停止或停止变为计时,按一下清零键就可以清零,操作非常简单。

由于是四位数码管,它的计时周期为100秒,显示满刻度为99:99秒,从左往右数共四位,前两位显示整数部分,后两位显示小数部分,中间两个个秒闪灯(秒闪灯一直亮)。

关键词:秒表,51单片机,C语言一、设计任务与要求 (18)1.1 设计任务 (18)1.2 设计要求 (18)二、方案总体设计 (19)2.1 方案一 (19)2.2 方案二 (19)2.3 系统采用方案 (19)三、硬件设计 (21)3.1 单片机最小系统 (21)3.2 数码管显示模块 (21)3.3 系统电源 (22)3.4 整体电路 (22)四、软件设计 (24)4.1 keil软件介绍 (24)4.2 系统程序流程 (24)五、仿真与实现 (27)5.1 proteus软件介绍 (27)5.2 仿真过程 (27)5.3 实物制作与调试 (29)5.4 使用说明 (30)六、总结 (32)6.1设计总结 (32)6.2经验总结 (20)七、参考文献 (21)一、设计任务与要求1.1 设计任务1).对更多小器件的了解2).巩固51单片机和C语言的知识,熟悉单片机和C语言的实际操作运用3).掌握仿真软件的运用和原理图的绘制4).加深焊接的技巧,提高焊接的能力5).熟悉调试方法和技巧,提高解决实际问题的能力6).熟悉设计报告的编写过程1.2 设计要求1).清零键进行清零2).一个独立按键进行停止与运行的操作3).秒闪灯一直亮二、方案总体设计设计一个基于51单片机的秒表。

基于51单片机的数字秒表设计

单片机系统课程设计成绩评定表设计课题:数字秒表学院名称:电气工程学院专业班级:自动1204学生:学号:指导教师:王黎设计地点:31-630设计时间:2013-12-29~2013-1-9单片机系统课程设计课程设计名称:数字秒表专业班级:自动1204学生姓名:学号:指导教师:王黎课程设计地点:31-630课程设计时间:2013-12-29~2013-1-9单片机系统课程设计任务书目录1绪论 (3)2系统概述 (4)2.1数字式秒表的设计意义 (4)2.2设计要求与分析 (5)3 硬件电路设计 (6)3.1基准脉冲的获取 (6)3.2键盘及控制电路 (12)3.3计数、译码及显示电路 (14)4 数字秒表系统软件设计 (16)4.1 主程序软件设计 (16)4.2 中断服务程序设计 (16)5调试与仿真 (19)5.1软件调试与烧写 (19)5.2 硬件仿真 (20)6. 结论 (21)参考文献: (23)附录 (24)附录一系统原理图 (24)附录二源程序代码 (25)1绪论21世纪,单片机的发展非常的迅速。

单片机是把主要计算机功能部件都集成在一块芯片上的微型计算机。

它是一种集计数和多种接口于一体的微控制器,被广泛应用在智能产品和工业自动化上,而51单片机是个单片机中最为典型和最有代表性的一种。

51单片机是对所有兼容Intel 8031指令系统的单片机的统称。

该系列单片机的始祖是Intel的8031单片机,后来随着Flash rom技术的发展,8031单片机取得了长足的进展,成为应用最广泛的8位单片机之一,其代表型号是Atmel的AT89系列,它广泛应用于工业测控系统之中。

很多公司都有51系列的兼容机型推出,今后很长的一段时间将占有大量市场。

本次的设计任务是一个数字秒表,而秒表与普通的钟表不同,它的目的是对从某一时刻到另一时刻的时间间隔进行计时。

秒表的数字化常给人们的生活带来极大的方便,它广泛应用于社会的各个领域。

基于51单片机的秒表设计

单片机课程设计课程题目:基于51单片机的秒表设计专业:电子信息工程班级:电信121学号:姓名:1 课题内容要求及目的1.1课题内容用AT89C51设计一个秒表,该秒表课可显示0.0~99.9秒的时间,进行相应的单片机硬件电路的设计并进行软件编程利用单片机定时器/计数器中断设计秒表,从而实现秒、十分之一秒的计时。

综合运用所学的《单片机原理与应用》理论知识,通过实践加强对所学知识的理解,具备设计单片机应用系统的能力。

通过本次系统设计加深对单片机掌握定时器、外部中断的设置和编程原理的全面认识复习和掌握。

本系统利用单片机的定时器/计数器定时和记数的原理,通过采用proteus仿真软件来模拟实现。

模拟利用AT89C51单片机、LED 数码管以及控件来控制秒表的计数以及计位!其中有三位数码管用来显示数据,显示秒(两位)和十分之一秒,十分之一秒的数码管计数从0~9,满十进一后显示秒的数码管的数字加一,并且十分之一秒显示清零重新从零计数。

计秒数码管采用三位的数码管,当计数超过范围是所有数码管全部清零重新计数。

1.2课题要求本课题是基于单片机的秒表系统设计,它的具体要求有以下几点:(1)用单片机AT89C51实现;(2)以0.1秒为最小单位进行显示;(3)秒表量程为0.0-99.9秒,用LED显示;(4)有清零、开始、停止功能。

1.3课题目的通过课程设计,进一步熟悉和掌握AT89C51单片机的结构及工作原理,掌握以单片机核心的电路设计的基本方法和技术,了解表关电路参数的计算方法。

通过完成一个包括电路设计和程序开发的完整过程,进一步了解开发一单片机应用系统的全过程,通过此综合训练,为以后毕业设计打下一定的基础。

(1)利用单片机定时器计数器中断设计秒表,从而实现秒、十分之一秒的计时。

(2)综合运用所学的《单片机原理与应用》理论知识,通过实践加强对所学知识的理解,具备设计单片机应用系统的能力,加深对单片机课程的全面认识。

51单片机数字秒表设计报告论文

51单片机数字秒表设计报告目录摘要 (I)ABSTRACT (II)第一章引言 (1)1.1秒表的概述 (1)1.2本设计任务 (1)1.3系统主要功能 (2)第二章硬件设计 (3)2.1总体方案的设计 (3)2.2单片机的选择 (4)2.3各部分电路设计 (5)2.3.1系统时钟电路的设计 (5)2.3.2系统复位电路的设计 (6)2.3.3 按键与按钮电路设计 (7)2.4显示电路的选择与设计 (7)2.4.1数码管的内部结构 (8)2.4.2 数码管的外部结构 (8)2.5系统总体电路的设计 (9)第三章软件设计 (11)3.1主程序设计 (11)3.2中断程序设计 (12)第四章系统调试 (16)第五章总结 (17)参考文献 (18)摘要近年来随着科学技术的发展,单片机的应用正在不断发展。

本文阐述了基于51单片机的数字秒表的设计。

计时秒表是一种先进的电子计数器,较多的应用在教学器材、比赛计时等,而且采用数字显示,具有直观、读取方便、功能方便等诸多优点。

本设计是由硬件电路和软件程序两部分组成,硬件电路由AT89C51单片机、按键控制电路、数码显示电路、晶振电路以及复位电路组成,它使用元件少,电路结构简单,功能强大;软件采用C语言程序设计,使用keil编译源程序,产生的可执行性文件能够让单片机快速执行。

该设计充分利用单片机内部资源,通过程序利用定时器中断服务程序对计时秒表开始、暂停、清零等操作进行处理,提高单片机的工作效率,使得系统能实现0~99秒的计时。

关键字:51单片机;秒表;定时器;中断服务程序ABSTRACTadvanced electronic counter, more application in teaching equipment, timing, etc., and adopts digital display, intuitive, easy to read, convenient features, and many other advantages. This design is consists of two parts, hardware circuit and software program, the hardware circuit is controlled by AT89C51, key circuit, digital display circuit, crystals circuit and reset circuit, it USES less component, the circuit structure is simple, powerful; Software using C language program design, use the keil compiler source code, can let the enforceability file microcontroller rapid execution. This design make full use of the single chip microcomputer internal resources, through the application using the timer interrupt service routine for timing stopwatch start, pause, reset operations such as processing, improve the work efficiency of the single chip microcomputer system can realize the timing of 0 ~ 99 seconds.Key words:51 single chip,microcomputer A stopwatch,The timer,Interrupt service routin第一章引言20世纪末,电子技术获得了飞速的发展,在其推动下,现代电子产品几乎渗透了社会的各个领域,有力地推动了社会生产力的发展和社会信息化程度的提高,同时也使现代电子产品性能进一步提高,产品更新换代的节奏也越来越快。

51单片机秒表程序设计

51单片机秒表程序设计1. 简介秒表是一种用于测量时间间隔的计时器,常见于体育比赛、实验室实验等场合。

本文将介绍如何使用51单片机设计一个简单的秒表程序。

2. 硬件准备•51单片机开发板•LCD液晶显示屏•按键开关•连接线3. 程序流程3.1 初始化设置1.设置LCD液晶显示屏为8位数据总线模式。

2.初始化LCD液晶显示屏。

3.设置按键开关为输入模式。

3.2 主程序循环1.显示初始界面,包括“00:00:00”表示计时器初始值。

2.等待用户按下开始/暂停按钮。

3.如果用户按下开始按钮,则开始计时,进入计时状态。

4.如果用户按下暂停按钮,则暂停计时,进入暂停状态。

5.在计时状态下,每隔1毫秒更新计时器的数值,并在LCD液晶显示屏上显示出来。

6.在暂停状态下,不更新计时器的数值,并保持显示当前数值。

3.3 计时器控制1.定义一个变量time用于存储当前的计时器数值,单位为毫秒。

2.定义一个变量running用于标记计时器的状态,0表示暂停,1表示运行。

3.定义一个变量start_time用于存储计时器开始的时间点。

4.定义一个变量pause_time用于存储计时器暂停的时间点。

5.在计时状态下,每隔1毫秒更新time的值为当前时间与start_time的差值,并将其转换为小时、分钟、秒的表示形式。

6.在暂停状态下,保持time的值不变。

3.4 按键检测1.检测按键开关是否被按下。

2.如果按键被按下,判断是开始/暂停按钮还是复位按钮。

3.如果是开始/暂停按钮,并且当前处于计时状态,则将计时状态设置为暂停状态,并记录暂停时间点为pause_time;如果当前处于暂停状态,则将计时状态设置为运行状态,并记录开始时间点为当前时间减去暂停时间的差值。

4.如果是复位按钮,则将计时器数值重置为0,并将计时状态设置为暂停。

4. 程序代码示例#include <reg51.h>// 定义LCD控制端口和数据端口sbit LCD_RS = P1^0;sbit LCD_RW = P1^1;sbit LCD_EN = P1^2;sbit LCD_D4 = P1^3;sbit LCD_D5 = P1^4;sbit LCD_D6 = P1^5;sbit LCD_D7 = P1^6;// 定义按键开关端口sbit START_PAUSE_BTN = P2^0;sbit RESET_BTN = P2^1;// 定义全局变量unsigned int time = 0; // 计时器数值,单位为毫秒bit running = 0; // 计时器状态,0表示暂停,1表示运行unsigned long start_time = 0; // 开始时间点unsigned long pause_time = 0; // 暂停时间点// 函数声明void delay(unsigned int ms);void lcd_init();void lcd_command(unsigned char cmd);void lcd_data(unsigned char dat);void lcd_string(unsigned char *str);void lcd_clear();void lcd_gotoxy(unsigned char x, unsigned char y);// 主函数void main() {// 初始化设置lcd_init();while (1) {// 显示初始界面lcd_clear();lcd_gotoxy(0, 0);lcd_string("00:00:00");// 等待用户按下开始/暂停按钮while (!START_PAUSE_BTN && !RESET_BTN);// 判断按钮类型并处理计时器状态if (START_PAUSE_BTN) {if (running) { // 当前处于计时状态,按下按钮将进入暂停状态 running = 0;pause_time = time;} else { // 当前处于暂停状态,按下按钮将进入计时状态running = 1;start_time = get_current_time() - pause_time;}} else if (RESET_BTN) { // 复位按钮按下,重置计时器time = 0;running = 0;}}}// 毫秒级延时函数void delay(unsigned int ms) {unsigned int i, j;for (i = ms; i > 0; i--) {for (j = 110; j > 0; j--);}}// LCD初始化函数void lcd_init() {lcd_command(0x38); // 设置8位数据总线模式lcd_command(0x0C); // 显示开,光标关闭lcd_command(0x06); // 光标右移,不移动显示器lcd_command(0x01); // 清屏}// 向LCD发送指令函数void lcd_command(unsigned char cmd) {LCD_RS = 0;LCD_RW = 0;LCD_EN = 1;LCD_D4 = cmd >> 4 & 1;LCD_D5 = cmd >> 5 & 1;LCD_D6 = cmd >> 6 & 1;LCD_D7 = cmd >> 7 & 1;delay(1);LCD_EN = 0;LCD_D4 = cmd >> 0 & 1;LCD_D5 = cmd >> 1 & 1;LCD_D6 = cmd >> 2 & 1;LCD_D7 = cmd >> 3 & 1;delay(1);LCD_EN = 0;}// 向LCD发送数据函数void lcd_data(unsigned char dat) { LCD_RS = 1;LCD_RW = 0;LCD_EN = 1;LCD_D4 = dat >> 4 & 1;LCD_D5 = dat >> 5 & 1;LCD_D6 = dat >> 6 & 1;LCD_D7 = dat >> 7 & 1;delay(1);LCD_EN = 0;LCD_D4 = dat >> 0 & 1;LCD_D5 = dat >> 1 & 1;LCD_D6 = dat >> 2 & 1;LCD_D7 = dat >> 3 & 1;delay(1);LCD_EN = 0;}// 向LCD发送字符串函数void lcd_string(unsigned char *str) {while (*str) {lcd_data(*str++);delay(5);}}// 清屏函数void lcd_clear() {lcd_command(0x01);}// 设置光标位置函数void lcd_gotoxy(unsigned char x, unsigned char y) {unsigned char addr;if (y == 0)addr = x | (0x80 + y);else if (y == 1)addr = x | (0xC0 + y);lcd_command(addr);}5. 总结本文介绍了使用51单片机设计一个简单的秒表程序。

基于51单片机的数字时钟,带秒表和时间设置

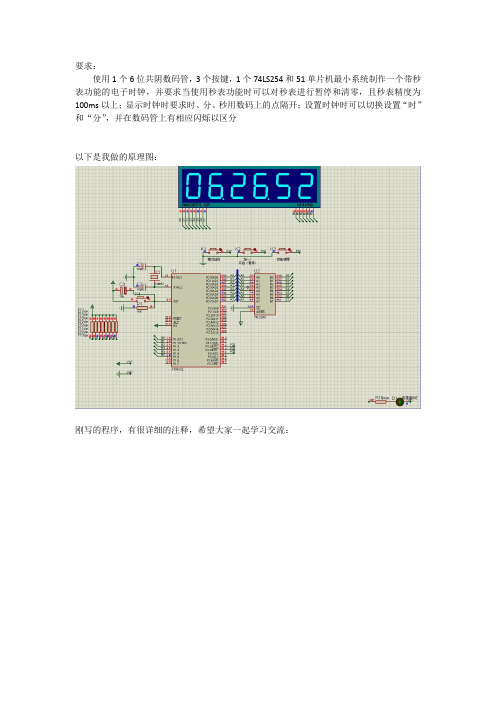

要求:

使用1个6位共阴数码管,3个按键,1个74LS254和51单片机最小系统制作一个带秒表功能的电子时钟,并要求当使用秒表功能时可以对秒表进行暂停和清零,且秒表精度为100ms以上;显示时钟时要求时、分、秒用数码上的点隔开;设置时钟时可以切换设置“时”和“分”,并在数码管上有相应闪烁以区分

以下是我做的原理图:

刚写的程序,有很详细的注释,希望大家一起学习交流:

以下是仿真文件和C程序,网盘分享给大家:

/share/link?shareid=3375444058&uk=453592216 /share/link?shareid=3375444058&uk=453592216 /share/link?shareid=3375444058&uk=453592216

(上面3个是一样的,怕有些吧友没看到)

希望吧友们一起分享自己的作品。

51单片机秒表程序设计报告

单片机程序设计报告题目: 秒表设计班级:姓名:学号:指导老师:时间:一、课题任务要求用AT89C51设计一个2位LED数码显示“秒表”,显示时间为00~99秒,每秒自动加一。

即数码显示管在原先的计数上快速加一。

二、设计思路1、使用单片机,设计秒表,能显示分分秒秒;2、使用三个按键停止,开始,复位,其中“开始”按键当开关由上向下拨时开始计时,此时若再拨“开始”按键则数码管暂停;“清零”按键当开关由上向下拨时数码管清零,此时若再拨“开始”按键则又可重新开始计时;3、使用液晶或数码管显示;4、使用定时器中断。

三、硬件设计3.1、单片机介绍单片机:AT89C51是一种带4K字节闪存可编程可擦除只读存储器的低电压、高性能CMOS 8位微处理器。

单片机的可擦除只读存储器可以反复擦除1000次。

该器件采用ATMEL高密度非易失存储器制造技术制造,与工业标准的MCS-51指令集和输出管脚相兼容。

AT89C51主要特性:·与MCS-51 兼容·低功耗的闲置和掉电模式·4K字节可编程闪烁存储器·全静态工作:0Hz-24MHz·寿命:1000写/擦循环·数据保留时间:10年·三级程序存储器锁定·128×8位内部RAM·片内振荡器和时钟电路·32可编程I/O线·两个16位定时器/计数器·5个中断源·可编程串行通道3.2管脚说明:VCC:供电电压。

GND:接地。

P0口:P0口为一个8位漏级开路双向I/O口,每脚可吸收8TTL门电流。

当P1口的管脚第一次写1时,被定义为高阻输入。

P0能够用于外部程序数据存储器,它可以被定义为数据/地址的第八位。

在FIASH编程时,P0 口作为原码输入口,当FIASH进行校验时,P0输出原码,此时P0外部必须被拉高。

P1口:P1口是一个内部提供上拉电阻的8位双向I/O口,P1口缓冲器能接收输出4TTL门电流。

基于C51单片机控制的数码管秒表

基于C51单片机控制的数码管秒表基于C51单片机控制的数码管秒表/************************************************************** ***************/说明:下面是通过c语言编写的程序,数码管为共阴数码管使用的芯片有74h138译码器器74HCT573PW芯片。

显示效果为:00-00-00分别是分--秒--百分之一秒可用一个键控制:按一下开始计时,再按暂停,再按清零。

本代码经测试可以使用/************************************************************** ***************/ #include#define ENABLE 0#define DISABLE 1#define DATA P0unsigned n=0;unsigned char a,b,count=0, i, j = 0,x,u[8];sbit hc138s_enable = P1^3;sbit hc138s_a = P1^0;sbit hc138s_b = P1^1;sbit hc138s_c = P1^2;sbit k1=P3^4;unsigned char code table[]=//共阴极0~f数码管编码{0x3f,0x06,0x5b,0x4f, //0~30x66,0x6d,0x7d,0x07, //4~70x7f,0x6f//8~9};voiddelay_ms(unsigned intnms);void chose7s(unsigned char num);void chose7ss(unsigned char numm);void timer0_init(void){TMOD = 0X01;TH0 = (65536-10000)/256;TL0 = (65536-10000)%256;ET0 = 1;EA = 1;TR0 = 1;}/************************************************************** *******//* 用作数码管最初显示状态*//************************************************************** *******/ void s1(){for(j=0;j<8;j++){if(j==2||j==5){chose7s(j);//使能某位数码管DATA=0x40;delay_ms(2);}else{chose7s(j);DATA=0x3f;delay_ms(2);}}}void s2(){// timer0_init();for(i=0;i<10;i++)//扫描{for(j=0;j<8;j++){if(j==2||j==5){chose7s(j);DATA=0x40;delay_ms(2);}else{chose7s(j);x=u[j];DATA=table[x];delay_ms(2);}}}}/**************************开关*************************************/void key1(){if (k1==0){delay_ms(20);if(k1==0){n++;if(n==3){n=0;count=0;b=0;a=0;}while(!k1);}}}/************************************************************** **************** ** 函数名: main** 函数功能: 主函数** 输入: 无** 输出: 无**************************************************************** **************** /void main(void){while(1){key1();switch(n){case 0:s1();break;case 1:timer0_init();s2();break;case 2:TR0=0;s2();break;}}}/************************************************************** **************** ** 函数名: chose7s** 函数功能: 使能某个数码管** 输入: 数码管编号** 输出: 无**************************************************************** **************** /void chose7s(unsigned char num){hc138s_enable = ENABLE;switch(num){case 0://第1个数码管hc138s_a = 0;hc138s_b = 0;hc138s_c = 0;break;case 1://第2个数码管hc138s_a = 1;hc138s_b = 0;hc138s_c = 0;//P0=0x3f; break;case 2://第3个数码管hc138s_a = 0;hc138s_b = 1;hc138s_c = 0;//P0=0x40; break;case 3://第4个数码管hc138s_a = 1;hc138s_b = 1;hc138s_c = 0;//P0=0x3f; break;case 4://第5个数码管hc138s_a = 0;hc138s_b = 0;hc138s_c = 1;//P0=0x3f; break;case 5://第6个数码管hc138s_a = 1;hc138s_b = 0;hc138s_c = 1;break;case 6://第7个数码管hc138s_a = 0;hc138s_b = 1;hc138s_c = 1;//P0=0x3f;break;case 7://第8个数码管hc138s_a = 1;hc138s_b = 1;hc138s_c = 1;//P0=0x3f;break;default:hc138s_enable = DISABLE;break;}hc138s_enable = DISABLE;}/************************************************************** **************** ** 函数名: delay_ms* 函数功能: 延时* 输入: n* 输出: 无*************************************************************** **************** /voiddelay_ms(unsigned intnms){unsignedinti, j;for(i = nms; i > 0; i--)for(j = 55; j > 0; j--);}/************************************************************** ***************/ /*1/100秒计时*//************************************************************** ***************/ void T0_time() interrupt 1{TH0 = (65536-10000)/256;TL0 = (65536-10000)%256;count++;if(count==100){count=0;a++;if(a==60){a=0;b++;if(b==60){b=0;a=0;count=0;}}}u[7]=count%10;u[6]=count/10;u[4]=a%10;u[3]=a/10;u[1]=b%10;u[0]=b/10;}/*如果显示亮度不够可以改一下延时*/ //后面我会发设计报告。

基于51单片机的时钟秒表

摘要 (1)1 设计目的及要求 (2)1.1 设计目的 (2)1.2 设计要求 (2)2 设计方案选择 (3)2.1 芯片简介 (3)2.2 总体设计思路 (3)2.3 单元电路设计 (4)2.3.1 时钟模块 (4)2.3.2 复位电路模块 (4)2.3.3 控制模块 (5)2.3.4 显示模块 (5)3 软件设计 (6)3.1整体程序设计思路 (6)3.2 程序流图 (6)3.3 主要程序代码 (8)4 仿真调试 (11)4.1 keil简介 (12)4.1 keil与protues联调 (11)4.2仿真实现 (12)5 硬件实现 (13)5.1 程序下载步骤 (13)5.1 硬件调试 (14)6 拓展 (14)6.1 设计原理 (14)6.2 主要程序清单 (14)6.3 仿真实现 (15)7 心得体会 (16)参考文献 (17)本设计的数字秒表系统采用STC89C52单片机为中心器件,利用其定时器/计数器原理,结合LED数码管以及按键电路来设计计时器。

将软、硬件有机地结合起来,使得系统能够实现四位LED显示,显示时间为00.00~99.99秒,计时精度为0.01秒,能正确地进行计时。

同时,我在此基础上,又设计了时钟秒表定时器,可以显示年、月、日、星期、时间进制、时、分、秒、、以及闹钟启/停状态,可以实现时间的调整,时钟/秒表功能的转换,闹钟的启/停。

其中软件系统采用C语言编写程序,包括显示程序,定时中断服务,延时程序等,并在keil中调试运行,硬件系统利用PROTEUS强大的功能来实现,简单切易于观察,在仿真中就可以观察到实际的工作状态,利用单片机开发板可下载程序,实现硬件实现。

关键词:秒表,时钟,定时/计数器1 设计目的及要求1.1 设计目的本设计主要是应用Proteus软件和嵌入式C语言编程工具,结合单片机原理及应用、微机原理与接口技术等专业课程,强化和巩固专业理论基础,掌握Proteus仿真的技巧和嵌入式C语言编程工具,提高单片机开发能力,并为嵌入式开发打下基础。

51单片机时钟秒表课程设计

51单片机时钟秒表课程设计

这个是我写的作业的方案,单片机课程结课作业,以下是我写的设计方案,写的不咋滴欢迎拍砖。

一、详细功能设计

1、基于51 单片机倒计时秒表,最大值为9999 秒,计时单位为0.1 秒;

2、计时的初始值为组员学号后4 位,键盘启动/停止计时;

3、设计多个按键,使用键盘选择不同成员的学号作为初始值。

二、8031 最小系统设计

1、最小系统设计原理图如图1.0 所示:

2、8031 最小系统概述;

8031 最小系统包含晶振电路与复位电路。

晶振选择12MHZ 晶振,晶振电容使用30pf 电容瓷片电容。

复位电路选择上电复位。

三、硬件设计

1、数码管电路

在本设计中,使用7 段共阴极数码管,选择数码管的型号为7SEG-MPX6- CC;

2、数码管片选电路;

由于本设计需要显示五位数字,同时为了驱动数码管,使用了74HC154 芯片。

与此同时,使用74HC154 芯片还可以扩展数码管显示数字的个数。

三、软件设计

1、程序流程图如图3.0 所示:

图3.0 程序流程图

2、程序流程说明

数码管显示和扫描键盘子函数放在0.1 秒的定时器中断里,而主函数的while(1)函数向数码管显示数据变量送数据。

数码管显示函数接受键盘状态,根。

51单片机秒表课程设计

51单片机秒表课程设计一、课程目标知识目标:1. 学生能理解51单片机的基本原理,掌握其编程方法。

2. 学生能掌握秒表功能的基本组成部分,如计时、暂停、复位等。

3. 学生能理解并应用中断、定时器等51单片机的相关知识。

技能目标:1. 学生能运用C语言编写51单片机程序,实现秒表功能。

2. 学生能通过实验操作,调试并优化程序,解决实际问题。

3. 学生能熟练使用相关开发工具和调试设备,如编译器、仿真器等。

情感态度价值观目标:1. 学生培养对单片机编程的兴趣,激发创新意识和实践欲望。

2. 学生培养良好的团队合作意识,学会互相交流、协作解决问题。

3. 学生培养严谨的科学态度,注重实验数据的真实性,勇于面对和克服困难。

课程性质:本课程为实践性课程,以项目为导向,结合理论知识与实际操作,培养学生的动手能力和编程思维。

学生特点:学生具备一定的电子基础和编程基础,对51单片机有一定了解,但对中断、定时器等高级功能尚不熟悉。

教学要求:教师需引导学生运用已学知识,通过实际操作,逐步掌握51单片机的编程和应用。

在教学过程中,注重培养学生的实际操作能力、问题解决能力和团队协作能力。

课程目标的设定旨在使学生在完成本项目后,能够独立设计并实现简单的单片机应用系统。

二、教学内容1. 理论知识:- 51单片机结构及工作原理- C语言编程基础:数据类型、运算符、控制语句等- 中断和定时器的原理与应用- 键盘输入与数码管显示原理2. 实践操作:- 使用Keil软件编写和编译程序- 使用STC89C52RC单片机进行程序下载和调试- 设计并实现秒表功能,包括计时、暂停、复位等3. 教学大纲:- 第一周:回顾51单片机基本原理,学习C语言编程基础- 第二周:学习中断和定时器知识,分析秒表功能需求- 第三周:设计程序框架,编写中断处理程序和定时器程序- 第四周:编写键盘输入和数码管显示程序,实现秒表功能- 第五周:项目调试、优化和展示4. 教材章节及内容:- 第一章:51单片机概述,了解单片机的发展及其应用- 第二章:C语言编程基础,掌握基本语法和数据类型- 第三章:中断和定时器,学习中断处理和定时器编程方法- 第四章:输入输出接口,学习键盘输入和数码管显示技术教学内容的选择和组织旨在保证学生能够系统地掌握51单片机编程及应用,注重理论与实践相结合,培养学生的实际操作能力。

基于51单片机的秒表设计

单片机课程设计课程题目:基于51单片机的秒表设计专业:电子信息工程班级:电信121学号:姓名:1 课题内容要求及目的1.1课题内容用AT89C51设计一个秒表,该秒表课可显示0.0~99.9秒的时间,进行相应的单片机硬件电路的设计并进行软件编程利用单片机定时器/计数器中断设计秒表,从而实现秒、十分之一秒的计时。

综合运用所学的《单片机原理与应用》理论知识,通过实践加强对所学知识的理解,具备设计单片机应用系统的能力。

通过本次系统设计加深对单片机掌握定时器、外部中断的设置和编程原理的全面认识复习和掌握。

本系统利用单片机的定时器/计数器定时和记数的原理,通过采用proteus仿真软件来模拟实现。

模拟利用AT89C51单片机、LED 数码管以及控件来控制秒表的计数以及计位!其中有三位数码管用来显示数据,显示秒(两位)和十分之一秒,十分之一秒的数码管计数从0~9,满十进一后显示秒的数码管的数字加一,并且十分之一秒显示清零重新从零计数。

计秒数码管采用三位的数码管,当计数超过范围是所有数码管全部清零重新计数。

1.2课题要求本课题是基于单片机的秒表系统设计,它的具体要求有以下几点:(1)用单片机AT89C51实现;(2)以0.1秒为最小单位进行显示;(3)秒表量程为0.0-99.9秒,用 LED显示;(4)有清零、开始、停止功能。

1.3课题目的通过课程设计,进一步熟悉和掌握AT89C51单片机的结构及工作原理,掌握以单片机核心的电路设计的基本方法和技术,了解表关电路参数的计算方法。

通过完成一个包括电路设计和程序开发的完整过程,进一步了解开发一单片机应用系统的全过程,通过此综合训练,为以后毕业设计打下一定的基础。

(1)利用单片机定时器计数器中断设计秒表,从而实现秒、十分之一秒的计时。

(2)综合运用所学的《单片机原理与应用》理论知识,通过实践加强对所学知识的理解,具备设计单片机应用系统的能力,加深对单片机课程的全面认识。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ATMEL 公司的 89 系列单片机以其卓越的性能、完善的兼容性、 快 捷 便 利 的 电 擦 写 操 作 、 低 廉 的 价 格 完 全 替 代 了 87C51/62 和 8751/52,低电压、低功耗,有 DIP、PLCC、QFP 封装,是目前性 能最好、价格最低、最受欢迎的单片机之一。

P1.0 P1.1 P1.2 P1.3 P1.4 P1.5 P1.6 P1.7 RST/VPD P3.0 P3.1 P3.2 P3.3 P3.4 P3.5 P3.6 P3.7

XTAL2 XTAL1

VSS

VCC P0.0 P0.1 P0.2 P0.3 P0.4 P0.5 P0.6 P0.7 VPP ALE PSEN P2.7 P2.6 P2.5 P2.4 P2.3

AT89S52 为 40 脚双列直插封装的 8 位通用微处理器,采用工业 标准的 C51 内核,在内部功能及管脚排布上与通用的 8XC52 相同, 其主要用于汇聚调整时的功能控制。功能包括对汇聚主 IC 内部寄存 器、数据 RAM 及外部接口等功能部件的初始化,汇聚调整控制,汇 聚测试图控制等。 单片机外部结构 AT89S52 单片机采用 40 脚的 DIP 封装,如下所示。

数码管显示可以分为静态显示和动态显示两种。由于本设计需要 采用四位数码管显示时间,如果静态显示则占用的口线多,硬件电路 复杂,所以采用动态显示。

动态显示是一位一位地轮流点亮各位数码管,这种逐位点亮显示

器的方式称为位扫描。通常各位数码管的段选线相应并联在一起,由 一个 8 位的 I/O 口控制;各位的公共阴极位选线由另外的 I/O 口线控 制。动态方式显示时,各数码管轮流选通,要使其稳定显示必须采用 扫描方式,即在某一时刻只选通一位数码管并送出相应的段码,在另 一时刻选通另一数码管,并送出相应的段码,依次规律循环,即可以 使各位数码管显示将要显示的字符,虽然这些字符是在不同时刻分别 显示,但由于人眼存在视觉暂留效应,只要每位显示间隔足够短就可 以给人同时显示的感觉。

0.1 秒位到 10 吗 0.1 秒位清零,1 秒位加一

1 秒位到 10 吗 1 秒位清零,10 秒位加一

10 秒位到 10 吗 10 秒位清零

中断返回

2.3 程序清单

#include<reg52.h>

unsigned int data table[]={0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d,0x07,0x7f,0x6f}; //显示码值

a、P0 口(P0.0~P0.7)是一个 8 位漏极开路型双向 I/O 口,在访问外

部存储器时,它是分时传送的低字节地址和数据总线,P0 口能以吸 收电流的方式驱动八个 LSTTL 负载。 b、P1 口(P1.0~P1.7)是一个带有内部上拉电阻的 8 位准双向 I/O 口。 能驱动四个 LSTTL 负载。 c、P2 口(P2.0~P2.7)是一个带有内部上拉电阻的 8 位准双向 I/O 口, 在访问外部存储器时,它输出高 8 位地址。P2 口可以驱动四个 LSTTL 负载。 d、P3 口(P3.0~P3.7)是一个带有内部上拉电阻的 8 位准双向 I/O 口。 能驱动四个 LSTTL 负载。 1.3 显示电路的选择与设计

39 38 37 36 35 34 33 32

P2.0/A8 P2.1/A9 P2.2/A10 P2.3/A11 P2.4/A12 P2.5/A13 P2.6/A14 P2.7/A15

21 22 23 24 25 26 27 28

P3.0/RXD P3.1/TXD P3.2/INT0 P3.3/INT1

摘要

近年来随着科学技术的发展,单片机的应用正在不断走下面还深 入。本文简单阐述了基于单片机的数字秒表的的设计。本设计的主要 特点是计时精度达到 0.01 秒,是各种体育竞赛的必要设备之一。

本设计的数字秒表采用 AT89S52 单片机为主要器件,利用其定时 器的原理,结合显示电路、LED 数码管以及外部外部中断电路来设 计计时器。将软硬件结合起来,使得系统能实现 0~99.99 秒的计时, 计时精度位 0.01 秒。硬件系统利用 proteus 仿真,在仿真中就能观察 到系统的实际运行情况。 关键字:单片机 数字秒表 仿真

P3.4/T0 P3.5/T1 P3.6/WR P3.7/RD

10 11 12 13 14 15 16 17

RP1

1

2 3 4 5 6 7 8 9

U2:A

2 3

A B

Y0 Y1

1E

Y2 Y3

74LS139

RESPACK-8

4 5 6 7

二 软件设计

2.1 主程序设计 本系统程序主要模块由主程序、定时中断服务程序、外部中断 0

对于数字显示电路,通常采用液晶显示或数码管显示。对于一般 的段式液晶屏,需要专门的驱动电路,而且液晶显示作为一种被动显 示,可视性差,不适合远距离观看;对于具有驱动电路和单片机接口 的液晶显示模块,一般多采用并行接口,对单片机的接口要求较高, 占用资源多;另外,AT89S52 单片机本身没有专门的液晶驱动接口。 而数码管作为一种主动显示器件,具有亮度高、响应速度快、价格便 宜、易于购买等优点,而且有远距离视觉效果,很适合夜间或者远距 离操作。因此在本设计中,我们采用 7 段数码管作为显示介质。

//给定时器赋定时初值

TL0=(65536-1000)%256;

EA=1;

//开中断

EX0=1;

EX1=1;

ET0=1;

IT0=1;

//设置外部中断位脉冲边沿触发方式

IT1=1;

while(1)

// 数码显示

{

P2=0x03;

P0=table[i];

一端。当采用外部振荡时,此引脚接外部振荡源。

(2)控制或与其他电源复用引脚

a、RST/VPD 当振荡器运行是,在此引脚上出现两个机器周期的

高电平(由低到高跳变),将使单片机复位在 Vcc 掉电期间,此引脚

可接上备用电源,由 VPD 向内部提供备用电源,

以保持内部 RAM 中的数据。

b、ALE/PROG

U1

19 XTAL1 18 XTAL2

9 RST

29 30 31

PSEN ALE EA

1 2 3 4 5 6 7 8

P1.0/T2 P1.1/T2EX P1.2 P1.3 P1.4 P1.5 P1.6 P1.7

AT89S52

P0.0/AD0 P0.1/AD1 P0.2/AD2 P0.3/AD3 P0.4/AD4 P0.5/AD5 P0.6/AD6 P0.7/AD7

四位数码管 位控制

计时器采用 T0 中断实现,定时溢出中断周期为 1ms,当溢出中 断后向 CPU 发出溢出中断请求,每发出 10 次中断请求就对 10ms 位

(即最后一位)加一,达到 100 次就对 100ms 位加一,以此类推, 直到 99.99s 为止。

再看按键的处理。两个按键采用中断的方法,设置外部中断 0 和 外部中断 1 位脉冲边沿触发方式,这样一来每当按键按下时便会触发 中断,从而实现启动和暂停。 1.2 单片机的选择

(1)外部中断 0 服务程序

外部中断 0 服务程序结合外部 P3.2 键实现数字秒表的启动功能。流 程如下图所示。

外部中断 0 入口

启动定时器 T0 TR0=1

中断返回

(2)外部中断 1 服务程序 外部中断 1 服务程序结合外部 P3.3 键实现数字秒表的停止功能。 流程图如下所示。

外部中断 1 入口

本设计利用 AT89S52 单片机的定时器,使其能精确计时。利用 中断系统使其实现启动和暂停的功能,P0 口输出段码数据,P2.0~P22. 连上译码器作为位选,P3.2 和 P3.3 接口的两个按钮分别实现启动和 暂停功能。设计的基本要求是正确性。硬件电路按下图进行设计。

控制开关

AT89S52 单片机

一 硬件设计

1、1 总体方案的设计 数字秒表具有显示直观、读取方便、精度高等优点,在计时中

广泛应用。本设计中用单片机和数码管组成数字秒表力求结构简单。 设计中包括硬件电路的设计和系统程序的设计。硬件电路主要

有主控制器、控制按钮与显示电路组成。主控制器采用单片机 AT89S52,显示电路采用四位共阴极数码管显示计时时间。

服务程序和外部中断 1 服务程序组成。其中主程序是整个程序的主 体。可以对各个中断程序进行调用。协调各个子程序之间的关系。

主程序主要是设置定时器大的工作模式,对定时器赋初值,开总 中断、两个外部中断以及定时器溢出中断。并设置外部中断为脉冲边 沿触发方式。 2.2 中断程序设计

本方案中用到了三个中断:外部中断 0、外部中断 1 和定时器 T0 溢出中断。CPU 在响应中断时,先处理高级中断,后处理低级中断, 若有多个同级中断时,则应按自然优先顺序处理。例如当 CPU 正在 处理一个中断申请时,又出现了另一个优先级比它高的中断请求,这 时,CPU 就暂停对当前优先级较低的中断源的服务,转去响应优先 级比它高的中断请求,并为其服务。待服务结束,再继续执行原来较 低级的中断服务程序。而当 CPU 为级别高的中断服务程序服务时, 如果级别低的中断发出中断请求,此时 CPU 是不会响应的,所以为 了避免开始和暂停两个按键中的一个出现没有响应的情况,在进行编 程是要注意中断的使用,避免出现中断的嵌套。合理分配中断对本设 计是很重要的。

d、EA/Vpp 内部程序存储器和外部程序存储器选择端。当 EA/Vpp

位高电平时,访问内部程序存储器,当 EA/Vpp 为低电平时,则访问

外部程序存储器。对于 EPROM 编程期间,此引脚上加 21VEPROM

编程电源(Vpp)。