项目二一位十进制加法计算器的逻辑电路设计与制作100页PPT

设计一个一位十进制加减法++数字电路课程设计报告

设计一个一位十进制加减法++数字电路课程设计报告一位十进制加减法++数字电路课程设计报告摘要:本文介绍了一位十进制加减法++数字电路课程设计的具体实现步骤。

通过串行和并行方式,使用ALU模块实现对数字的加减法运算,并模拟真实的计算机系统。

最后,将实现的电路连接到FPGA上,并在XilinxISE环境中进行调试和测试。

关键词:十进制加减法; ALU; FPGA; XilinxISE1 绪论随着信息技术的发展,数字电路处理能力也越来越强大。

在数字电路设计中,加减法运算是最基本的运算,因此如何实现十进制加减法++数字电路设计成为研究的重点。

本文将介绍一位十进制加减法++数字电路设计的具体实现步骤,并将实现的电路连接到FPGA上,并在XilinxISE环境中进行调试和测试,以便快速实现和调试。

2 原理说明十进制加减法++数字电路设计是一种实现数字加减法运算的电路,它可以通过串行或并行的方式来实现,主要包括以下几部分:(1) 数据输入:数字输入的格式一般为二进制、八进制、十进制或十六进制,可以使用输入设备(如键盘、指针装置等)输入;(2) ALU模块:ALU模块(算术逻辑单元)是实现加减法运算的最主要组成部分,它包括算术逻辑和控制逻辑;(3) 数据输出:数据输出的格式一般为二进制、八进制、十进制或十六进制,可以使用输出设备(如显示器、打印机等)进行输出;(4) 控制逻辑:控制逻辑主要由指令和控制状态机构成,控制状态机负责控制ALU模块的加减法运算,而指令则控制整个系统的运行状态。

3 电路设计(1)ALU模块设计:由于加减法运算是ALU模块的主要功能,因此该模块必须具备加减法运算的能力,同时应具备移位、带符号处理、移位定位、逻辑运算等功能。

(2)控制逻辑设计:为了控制ALU的加减法运算,必须设计一套控制逻辑,该控制逻辑主要由指令和控制状态机构成,指令用于控制系统的运行状态,而控制状态机则控制ALU模块的加减法运算,实现真实的计算机系统。

项目2一位加法计算器的设计与制作

根据编码的概念,编码器的输入端子数N和输出端子数n应满足 如下关系:

N

≤

2

n

编码器按编码方式不同,可分为普通编码器和优先编码器。按 输出代码的种类不同,又可分为二进制编码器和二-十进制编码器等。

图2-3 三位二进制普通编码器的逻辑图

1.普通编码器 普通编码器的特点是在任一时刻,只允许输入一个编码信号, 否则输出发生混乱。如图2-3所示的电路是用与非门及非门组成的 三位二进制普通编码器的逻辑图。该电路的输入端子数为7,输出 端子数为3。

[项目实施]

工作任务 名称一位加法Biblioteka 算器的设计与制作元器件选择

仪器设备 1.直流稳电源 2.万用表 3.面包板(或者印制电路板和电烙 铁) 4.集成电路测试装置(配16脚和14脚的集成电路插座) 5.示波 器

序 号

型号规 个 序号 名称 型号规格 个数 格 数 6×6×1 2套, 显示译码 按键S1~ 0mm 1 18 5 74LS48 2 器IC6、 S9 (标注 IC7 个 1~9) LED显示 LG5011A 编码器IC1、 2 74LS147 2 6 2 器IC8、 IC2 H IC9 名称 3 六反相器 IC3、IC4 74LS04 2 7 编码器限 流电阻R 1kΩ 18

74LS147的功能见表2-3所示。 表2-3 74LS147的功能表

3.编码器的应用 74LS148优先编码器的功能扩展。 【例2-1】 用两片74LS148优先编码器扩展成为16线-4线优先 译码器。 解设16线-4线优先编码器的编码输入端为 I15 ~ I 0 ,二进制代码 的输出端为 Y ~ Y 0 。

该编码器任何时刻都不允许有两个或两个以上输入信号同时 请求编码,否则输出将发生混乱。

加法计算器电路

各数位的权是8的幂

4、十六进制

数码为:0—9、A—F;基数是16。 运算规律:逢十六进一,即:F+1=10。 十六进制数的权展开式: 如:(D8.A)2= 13×161 +8×160+10 ×16-1=(216.625)10

各数位的权是16的幂

返回

二、不同数制之间的转换 1、二进制数与八进制数的相互转换

Y0 I1 I 3 I 5 I 7

返回

I 1 I 2I 3 I 4 I 5 I 6 I 7 ≥1

逻辑电路图:

≥1

Y2

Y1

≥1

Y0

想一想

如何用与非门实现?

返回

(2)集成8线-3线优先编码器74LS148

I0 & G2 YS

I1 I2 I3 I4 I5 I6 I7

1 1 1 1 1 1 1 G1 1 1

返回

1、十进制

数码为:0—9;基数是10。 十进制数的权展开式: 运算规律:逢十进一,即:9+1=10。

103、102、101、100称为十进 制的权。各数位的权是10的 幂。

5× 103=5000 5× 102= 500

5× 101= 50

5×

5 5 5 5

100=

任意一个十进制数都可以 5 表示为各个数位上的数码 + 与其对应的权的乘积之和, =5555 称权展开式。

返回

[知识链接2] 编码器

实现编码功能的逻辑电路,称为编码器。编码器又分 为普通编码器和优先编码器两类。

1.二进制编码器

(1)三位二进制普通编码器 输入:I0~I7 8个高电平信号,

I0 I1 I2 I3 I4 I5 I6 I7

输出:3位二进制代码Y2Y1Y0。

十进制加法器

十进制加法器十进制加法器可由BCD码(二-十进制码)来设计,它可以在二进制加法器的基础上加上适当的“校正”逻辑来实现,该校正逻辑可将二进制的“和”改变成所要求的十进制格式。

n位BCD码行波式进位加法器的一般结构如图2.3(a)所示,它由n级组成,每一级将一对4位的BCD数字相加,并通过一位进位线与其相邻级连接。

而每一位十进制数字的BCD 加法器单元的逻辑结构示于图2.3(b)。

图2.3 十进制加法器在十进制运算时,当相加二数之和大于9时,便产生进位。

可是用BCD码完成十进制数运算时,当和数大于9时,必须对和数进行加6修正。

这是因为,采用BCD码后,在二数相加的和数小于等于9时,十进制运算的结果是正确的;而当相加的和数大于9时,结果不正确,必须加6修正后才能得出正确的结果。

因此,当第一次近似求值时,可将它看成每一级是一个4位二进制加法器来执行,就好像xi 和yi是普通4位二进制数一样。

设S'i代表这样得到的4位二进制数和,C'i+1为输出进位,而Si 代表正确的BCD和,Ci+1代表正确的进位,那么当xi+yi+Ci<10时,Si=S'i当Xi +Yi+Ci≥10时,Si=S'i+6显然,当C'i+1=1或S'i≥10时,输出进位C i+1=1。

因此,可利用C i+1的状态来产生所要求的校正因子:Ci+1=1时校正因子为6;Ci+1=0时校正因子为0。

在图2.3(b)中,4位行波式进位的二进制加法器计算出和S'i ,然后S'i经过第二级二进制加法器加上0或6,则产生最终结果Si。

8.8 《项目6加法计算器的设计与制作》课件

1100

8421 码:又称 BCD 码,是最常用的十进制编码。其 每位的权为 8、 4、 2、 1,按公式展开,即可得对应的十 进制数,如(0111)2=1×22+1 ×21+1×20=7 5421 码 也 是 有 权 码 , 其 每 位 的 权 为 5 、 4 、 2 、 1 , 如 (1010)2=1×5+1×2=7。 2421 码 是 有 权 码 , 其 每 位 的 权 为 2 、 4 、 2 、 1 , 如 (1100)2=1×2 + 1×4 = 6 ,与余 3 码相同 0 和 9 、 1 和 8 、 2 和 7…是互为反码。另外当任何两个这样的编码值相加等于 9时,结果的4个二进制码一定都是1111。 格雷码:也叫循环码,特点是任何相邻的两个码组中, 仅有一位代码不同,抗干扰能力强。 余 3 码不是有权码,由于它按二进制展开后十进制数 比所表示的对应的十进制数大 3 。如 0101 表示的是 2 ,其 展开十进制数为5,故称为余3码。

逻辑电路图如图6.2所示。

图6-2 8线-3线二进制普通编码器

2.优先编码器

前面讨论的普通编码器中,输入信号之间是相互排斥 的,每次只能输入一个信号,而优先编码器可以同时输 入几个信号,但在设计时已经将各输入信号的优先顺序 排好。当几个信号同时输入时,优先权最高的信号优先 编码,这种电路称为优先编码器。 图6-3所示为三—八线优先 I9 I8 I7 I6 I5 I4 I3 I2 I1 I0 编码器CT74LS147的逻辑功 74LS147 能示意图,其功能表如表6-4 Y3 Y2 Y1 Y0 所示。下面根据表6-4所示的 CT74LS147的功能表对其逻 辑功能说明如下。

若以 N 代替( 6.1.1 )中的 10 ,就可以得到任意进制 (N进制)数展开式的形式 D=∑ki×Ni (6-2) 式中的ki是第i位的系数,N称为计数的基数,Ni 称为 第i位的权,i的取值与式(6-1)中的规定相同。

十进制位加法计数器设计

洛阳理工学院十进制4位加法计数器系别:电气工程与自动化系姓名:李奇杰学号:B10041016十进制4位加法计数器设计设计要求:设计一个十进制4位加法计数器设计设计目的:1.掌握EDA设计流程2.熟练VHDL语法3.理解层次化设计的内在含义和实现设计原理通过数电知识了解到十进制异步加法器的逻辑电路图如下则可以通过对JK触发器以及与门的例化连接实现十进制异步加法器的设计设计内容JKJK触发器的VHDL文本描述实现:--JK触发器描述library ieee;use ieee.std_logic_1164.all; entity jk_ff isport(j,k,clk: in std_logic;q,qn:out std_logic);end jk_ff;architecture one of jk_ff is signal q_s: std_logic;beginprocess(j,k,clk)beginif clk'event and clk='0' thenif j='0' and k='0' thenq_s <= q_s;elsif j='0' and k='1' thenq_s <= '0';elsif j='1' and k='0' thenq_s <= '1';elsif j='1' and k='1' thenq_s <= not q_s;end if;end if;end process;q <= q_s;qn <= not q_s;end one;元件门级电路:与门VHDL文本描述实现:--与门描述library ieee;use ieee.std_logic_1164.all;entity yumen2 isport(a,b:in std_logic;co:out std_logic);end entity yumen2;architecture one of yumen2 isbeginco<= (a and b );end architecture one;门级电路:十进制异步加法器例化元件文本实现:library ieee; --JK触发器描述use ieee.std_logic_1164.all;entity jk_ff isport(j,k,clk: in std_logic;q,qn:out std_logic);end jk_ff;architecture one of jk_ff issignal q_s: std_logic;beginprocess(j,k,clk)beginif clk'event and clk='0' thenif j='0' and k='0' thenq_s <= q_s;elsif j='0' and k='1' thenq_s <= '0';elsif j='1' and k='0' thenq_s <= '1';elsif j='1' and k='1' thenq_s <= not q_s;end if;end if;end process;q <= q_s;qn <= not q_s;end one;--与门描述library ieee;use ieee.std_logic_1164.all;entity yumen2 isport(a,b:in std_logic;co:out std_logic);end entity yumen2;architecture one of yumen2 isbeginco<= (a and b );end architecture one;library ieee; --十进制加法计数器描述use ieee.std_logic_1164.all;entity count10 isport(cp: in std_logic;c:out std_logic;q:out std_logic_vector(3 downto 0));end entity count10;architecture count of count10 is--例化元件JK触发器component jk_ffport(j,k,clk: in std_logic;q,qn:out std_logic);end component;--例化元件与门component yumen2port(a,b:in std_logic;co:out std_logic);end component;signal d,e,f,g,h,i,v,l,z:std_logic;signal ou:std_logic_vector(3 downto 0);beginjk1:jk_ff port map(j=>'1',k=>'1',clk=>cp,q=>e);jk2:jk_ff port map(j=>f,k=>'1',clk=>e,q=>h);jk3:jk_ff port map(j=>'1',k=>'1',clk=>h,q=>i);jk4:jk_ff port map(j=>l,k=>'1',clk=>e,q=>z,qn=>f); ym1:yumen2 port map(a=>e,b=>z,co=>c);ym2:yumen2 port map(a=>h,b=>i,co=>l);q<=z&i&h&e; -- 信号输出end architecture count;门级电路:波形仿真:展开二进制显示:无符十进制显示:思考与改进:该设计中可以直接把使用与门的地方改用and语法代替。

项目二一位十进制加法计算器的逻辑电路设计与制作课件.ppt

任务二 译码器逻辑电路设计与制 作

【知识链接2:LED数码管及其驱动电路】

LED数码管(也称发光二极管数码管)是用显示数字、文字 和符号的常用器件。如图2-8所示。

LED数码管根据管内PN结的连接方式不同,可分为共阴数码 管和共阳数码管两种。共阴数码管就是管内所有PN结的阴极 都连在一起,如图2-9(a)所示。使用时应将共阴端接低电 平,阳极接显示译码器的哥哥输出端。共阳数码管就是管内 所有PN结的阳极都连在一起,如图2-9(b)所示。使用时应 将共阳端接高电平,阴极接显示译码器的各个输出端。

Li Ai Bi

Gi Ai Bi AiBi Ai Bi AiBi Mi AiBi

根据上面的表达式可画出如图2-21所示的逻辑电路图。

上一页 返 回

仿真演练一 七段数码管显示电路

【技能目标】 (1)学会用字信号发生器。 (2)学会编码七段数码管。 (3)进一步会用逻辑分析仪。 【知识目标】 (1)掌握数码管的编码方法。 (2)掌握字信号发生器的使用方法。

4.活动提示

(1)为保证课堂效率,建议学生将前两次任务中制作的电路 保留并在此次任务中直接使用。

(2)此设计为组合逻辑,用集成逻辑门实现,设计方法可见 后面的知识链接。

上一页 下一页

任务三 一位十进制加法器的逻辑 电路设计与制作

【知识链接1:半加器与全加器的基本知识 】

1.一位加法器 (1)半加器。 半加器的真值表如表2-7所示。表中的A和B分别表示两个相

3.实践活动要求

要求每人用逻辑门设计BCD编码器的控制电路,并在焊接板( 或面包板)上将设计的电路搭建起来,然后调试并实现所要求 的功能。

4.实践仪器与元件

万用表、电烙铁、按钮开关10只,红色LED4只,集成逻辑门 若干,电阻、电容若干,导线,焊接板(或面包板),焊锡丝

项目:计数器的设计与制作PPT课件

(a) 状态图; (b) 时序图

17

三、计数器

•

(4) 归纳分析结果, 确定该时序电路的逻辑功能。从时

• 钟方程可知该电路是同步时序电路。从状态图可知随着CP脉

• 冲的递增, 触发器输出Q2Q1Q0值是递减的, 且经过八个CP脉冲 • 完成一个循环过程。

•

综上所述,此电路是同步三位二进制(或一位八进制)

(3) ① 列状态表。 列出电路输入信号和触发器原态的所有 取值组合,代入相应的状态方程,求得相应的触发器次态及 输出, 列表得到状态表, 如表5.4所示。

21

三、计数器

表5.4

cp

Q2n Q1n

00

Q Q0n

Q Q n1 n1 n1

2

1

0

00 0

1

00

10 1

0

01

00 1

1

01

11 0

0

10

3.1 同步计数器 1. 同步二进制计数器 同步二进制计数器电路如图所示。

12

三、计数器

Q2

Q J&

F2 C K

Q RD &

Q1

Q0

Q J&

F三1 、C计数器

Q RD K

Q J& F0 C

Q RD K

清零 CP

13

三、计数器

分析过程:

(1) 时钟方程

CP0=CP1=CP2=CP↓

驱动方程: J0=1

同一个时钟脉冲源,因而,所有触发器的状态变化都与所加时钟信号同步。 异步时序逻辑电路

异步时序逻辑电路中,没有统一的时钟脉ห้องสมุดไป่ตู้,有些触发器的时钟输入端 与时钟脉冲源相连,而有些触发器的时钟输入端不与时钟脉冲源相连。

8.8 《项目6加法计算器的设计与制作》课件.

然后讨论小数的转换。 假设十进制小数为(D)10,对应的等值二进制数为(0.k-1k-21k-3…k-n)2,则依式(6-3)可知 (D)10=k-1×2-1+ k-2×2-2+ k-3×2-3+……+ k-n×2-n 将上式两边同乘以2可得 2(D)10=k-1+(k-2×2-1+ k-3×2-2+……+ k-n×2-n+1)(6-6)

项目6 加法计算器的分析与制作

任务一 计算器数字显示电路分析与制作

任务二 一位加法计算器的设计与制作

计算器是我们经常使用的一种电子产品,能够实现 加减乘除。计算器中的加减乘除运算用电路如何实现 呢?通过本项目内容的学习,我们来一起学习如何制 作一个一位十进制加法计算器。

【知识目标】

1.掌握常用数制的表示及其相互转换; 2.理解编码的含义,掌握常用的BCD码; 3.掌握编码器、译码器、数据选择器、数据分配器 、 寄存器、加法器的逻辑功能和主要用途; 4.初步掌握用中规模集成组合逻辑电路设计电路的方 法; 5.了解组合逻辑电路的应用。

若以 N 代替( 6.1.1 )中的 10 ,就可以得到任意进制 (N进制)数展开式的形式 D=∑ki×Ni (6-2) 式中的ki是第i位的系数,N称为计数的基数,Ni 称为 第i位的权,i的取值与式(6-1)中的规定相同。

(2)二进制

在数字电路中应用最广泛的的是二进制。二进制的基 数是 2 ,每一位数仅有 0 和 1 两个数码表示,数字中低位 和相邻高位之间的关系是“逢二进一”,所以称为二进 制。根据式(6-2),任何一个二进制数均可展开为 D=∑ki×2i (6-3) 并计算出它所对应的十进制数的大小。例 (111101.11)2=1×25+1×24+1×23+1×22×0×21+1×20+ 1×2-1+1×2-2=(61.75)10

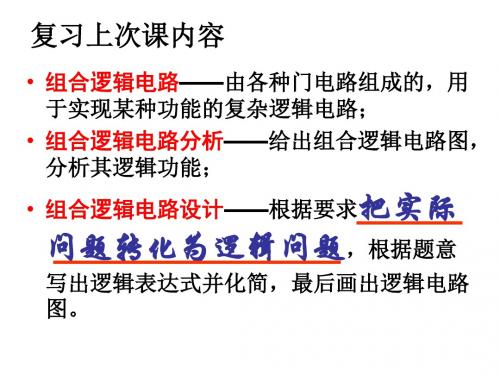

计算机中常用组合逻辑电路(共87张PPT)

三、译码器和编码器

二 进制译码器

译 码 二-十进制译码器 器

显示译码器

二进制编码器

编 码 器

二-十进制编码器

1、译码器

把代码状态的特定含义翻译出来的过程称 为译码,实现译码操作的电路称为译码器。

译码器就是把一种代码转换为另一种代码的电路。

1)二进制译码器

设二进制译码器的输入端为n个,则输出端为2n个,且 对应于输入代码的每一种状态,2n个输出中只有一

用两片74LS85比较八位数时,高四位的输出就是八位 数比较结果的输出。

低四位片输出接到高四位片的级联输入,从而高四 位相等时,高四位的输出取决于级联输入—低四位 的比较结果。

实现逻辑图

A3

A2

A1 74LS85

A0 (1) A>B

B3

A=B

B2

A<B

B1

B0 a>b a=b a<b

A3

A2 A1 74LS85 A0 (2) A>B

CO

Ci

Ci AiBi

半加器符号

2)全加器

能对两个1位二进制数进行相加并考虑低位来的进位,即相当于3 个1位二进制数相加,求得和及进位的逻辑电路称为全加器。

A i B i C i-1 000 001 010

Si Ci 00 10 10

AiBi

Ci-1

00 01 11 10

00 1 0 1

11 0 1 0

(Ai Bi)AiBi

(Ai Bi)AiBi

逻辑图:

(Ai<Bi) (Ai=Bi) (Ai>Bi)

&

≥1

&

&&

1

十进制加法计数器

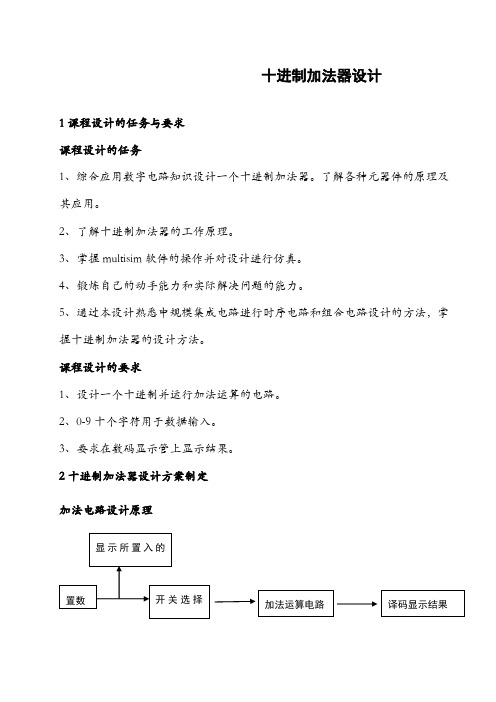

十进制加法器设计1课程设计的任务与要求 课程设计的任务1、综合应用数字电路知识设计一个十进制加法器。

了解各种元器件的原理及其应用。

2、了解十进制加法器的工作原理。

3、掌握multisim 软件的操作并对设计进行仿真。

4、锻炼自己的动手能力和实际解决问题的能力。

5、通过本设计熟悉中规模集成电路进行时序电路和组合电路设计的方法,掌握十进制加法器的设计方法。

课程设计的要求1、设计一个十进制并运行加法运算的电路。

2、0-9十个字符用于数据输入。

3、要求在数码显示管上显示结果。

2十进制加法器设计方案制定 加法电路设计原理图1加法运算原理框图如图1所示第一步置入两个四位二进制数。

例如(1001)2,(0011)2和(0101)2,(1000),同时在两个七段译码显示器上显示出对应的十进制数9,3和5,8。

2第二步将置入的数运用加法电路进行加法运算。

第三步前面所得结果通过另外两个七段译码器显示。

即:加法运算方式,则(1000)2+(0110)2=(1110)2 十进制8+6=14 并在七段译码显示出14。

运算方案通过开关S1——S8接不同的高低电平来控制输入端所置的两个一位十进制数,译码显示器U8和U9分别显示所置入的两个数。

数A直接置入四位超前进位加法器74LS283的A4——A1端,74LS283的B4——B1端接四个2输入异或门。

四个2输入异或门的一输入端同时接到开关S1上,另一输入端分别接开关S5——S8,通过开关S5——S8控制数B的输入,通过加法器74LS283完成两个数A和B的相加。

由于译码显示器只能显示0——9,所以当A+B>9时不能显示,我们在此用另一片芯片74LS283完成二进制码与8421BCD码的转换,即S>9(1001)2时加上3(0011)2,产生的进位信号送入译码器U10来显示结果的十位,U11显示结果的个位。

3十进制加法器电路设计加法电路的实现用两片4位全加器74LS283和门电路设计一位8421BCD码加法器。

逻辑电路的设计加法器PPT课件

请同学们思考以下两个问题:

1、各位上的运算有何不同之处?

2、只考虑某一位数相加,用逻辑电路实现,分别有几个 输入端和输出端?

——加法器

加法器

加法运算的基本规则:

(1)逢二进一。 (2)最低位是两个数最低位的叠加,不需

考虑进位。 (3)其余各位都是三个数相加,包括加数

例2:利用四位全加器实现四位全减器。

两个多位数相减,可以用补码相加来实现。

A-B=A+B补=A+B反+1

差

A4A3A2A1 N4N3N2N1

借位 1

S4

S3

S2

C4

S1 C0

A4A3A2A1 N4N3N2N1 1 “1”

A4 A3 A2 A1 B4 B3 B2 B1

被减数

1 1 11

• 由于4位二进制数相加是逢十六进一,而 8421码相加是逢十进一,用4位全加器构成 8421码加法器时,必须解决“逢十六进一 变成逢十进一”的问题。

“逢十六进一变成逢十进一”

6+7=13

加

6修正

非法码

8+9=17

加6

需要加6修正情况:①:和在10—15之间,② :有进位Co。

•BCD(8421)码加法器电路设计

Bn

Cn

Cn-1

F3

F2

F1

F0

加法器

C3

C0

B3 A3 B2 A2

B1 A1 B0 A0

74LS83

加法器(5)

多位加法器

串行进位加法器 并行进位加法器

例:四位串行进位加法器

一位十进制加法器设计报告

一位十进制加法器设计报告成员:一位十进制加法器一、实验目的:1、进一步学习组合逻辑电路的设计方法;2、学习相关芯片的使用;3、学一位十进制加法器的原理,并设计一个一位十进制加法电路。

二、设计原理:利用74HC283芯片,可以实现4为二进制数的相加运算,因此,对两个一位十进制数进行加运算时,应先把十进制数转化成二进制数,即进行编码,然后进行加运算,编码采用了两个8线-3线编码器串联组成的16线-4线编码器。

对求和结果进行输出时,当结果是一位十进制数时,可以直接输出,而求和结果为二位十进制数时,需要将结果分成十位数字和个位数字,分别显示在两个七段数码显示器上,这就需要对输出结果进行处理,设计时用对要输出结果加六,并取后四位作为个位输出,十位输出为1。

下面分介绍电路各个部分的设计方法与功能。

1、译码部分:电路设计如图一,CD4532为8线-3线译码器,输入和输出端均为高电平有效,即可以把0~7的十进制数转化为相应的二进制数输出。

设计时用两片CD4532组成16线-4线译码器,当要是入一个十进制数时,在相应的输入端加高电平即可。

图一2、求和部分:求和部分电路设计如图二,74HC283为四位二进制加法器,输入和输出端均为高电平有效,可以对输入的两个十进制数转化为的二进制数进行求和,其中,C4为进位输出端,当输出结果超过15时,输出高电平。

图二3、结果处理输出部分:结果处理输出部分电路设计如图三,CD4585为四位二进制比较电路,输入和输出端均为高电平有效,用两片CD4585组成8位二进制比较电路,将求和结果与9比较。

当结果小于9时,输出端输出为低电平,即输出为零,利用74HC283,将结果直接输出;当大于9时输出为1,对输出结果加6,并取后四位作为个位输出。

当输出结果为10~15时,用作加六运算的74HC283的C4端输出为1;当结果为16~18时,用作求和的电路C4端输出为1;当结果为0~9时,二者输出均为0;以此可以控制十位输出1还是0。

项目二一位十进制加法计算器的逻辑电路设计与制作资料共100页

31、只有永远躺在泥坑里的人,才不会再掉进坑里。——黑格尔 32、希望的灯一旦熄灭,生活刹那间变成了一片黑暗。——普列姆昌德 33、希望是人生的乳母。——科学到很多东西的诀窍,就是一下子不要学很多。——洛克

项目二一位十进制加法计算器的逻辑 电路设计与制作资料

36、如果我们国家的法律中只有某种 神灵, 而不是 殚精竭 虑将神 灵揉进 宪法, 总体上 来说, 法律就 会更好 。—— 马克·吐 温 37、纲纪废弃之日,便是暴政兴起之 时。— —威·皮 物特

38、若是没有公众舆论的支持,法律 是丝毫 没有力 量的。 ——菲 力普斯 39、一个判例造出另一个判例,它们 迅速累 聚,进 而变成 法律。 ——朱 尼厄斯

电子应用技术项目教程项目10一位十进制加法计算器的设计与制作共67页文档

计算器的设计与制作

6、纪律是自由的第一条件。——黑格 尔 7、纪律是集体的面貌,集体的声音, 集体的 动作, 集体的 表情, 集体的 信念。 ——马 卡连柯

8、我们现在必须完全保持党的纪律, 否则一 切都会 陷入污 泥中。 ——马 克思 9、学校没有纪律便如磨坊没有水。— —夸美 纽斯

10、一个人应该:活泼而守纪律,天 真而不 幼稚, 勇敢而 鲁莽, 倔强而 有原则 ,热情 而不冲 动,乐 观而不 盲目。 ——马 克思

1、最灵繁的人也看不见自己的背脊。——非洲 2、最困难的事情就是认识自己。——希腊 3、有勇气承担命运这才是英雄好汉。——黑塞 4、与肝胆人共事,无字句处读书。——周恩来 5、阅读使人充实,会谈使人敏捷,写作使人精确。——培根

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

46、我们若已接受最坏的,就再没有什么损失。——卡耐基 47、书到用时方恨少、事非经过不知难。——陆游 48、书籍把我们引入最美好的社会,使我们认识各个时代的伟大智者。——史美尔斯 49、熟读唐诗三百首,不会作诗也会吟。——孙洙 50、谁和我一样用功,谁就会和我一样成功。—自己选择的路、跪着也要把它走 完。 17、一般情况下)不想三年以后的事, 只想现 在的事 。现在 有成就 ,以后 才能更 辉煌。

18、敢于向黑暗宣战的人,心里必须 充满光 明。 19、学习的关键--重复。

20、懦弱的人只会裹足不前,莽撞的 人只能 引为烧 身,只 有真正 勇敢的 人才能 所向披 靡。