有限状态机FSM

Lua中使用状态机FSM简单例子

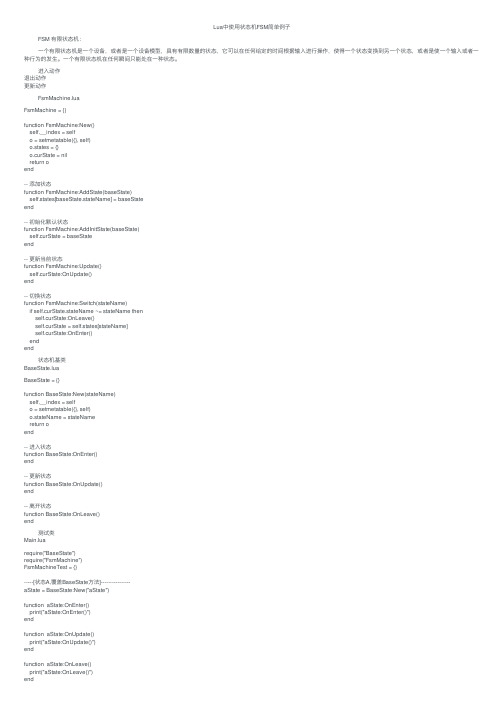

Lua中使⽤状态机FSM简单例⼦FSM 有限状态机:⼀个有限状态机是⼀个设备,或者是⼀个设备模型,具有有限数量的状态,它可以在任何给定的时间根据输⼊进⾏操作,使得⼀个状态变换到另⼀个状态,或者是使⼀个输⼊或者⼀种⾏为的发⽣。

⼀个有限状态机在任何瞬间只能处在⼀种状态。

进⼊动作退出动作更新动作FsmMachine.luaFsmMachine = {}function FsmMachine:New()self.__index = selfo = setmetatable({}, self)o.states = {}o.curState = nilreturn oend-- 添加状态function FsmMachine:AddState(baseState)self.states[baseState.stateName] = baseStateend-- 初始化默认状态function FsmMachine:AddInitState(baseState)self.curState = baseStateend-- 更新当前状态function FsmMachine:Update()self.curState:OnUpdate()end-- 切换状态function FsmMachine:Switch(stateName)if self.curState.stateName ~= stateName thenself.curState:OnLeave()self.curState = self.states[stateName]self.curState:OnEnter()endend状态机基类BaseState.luaBaseState = {}function BaseState:New(stateName)self.__index = selfo = setmetatable({}, self)o.stateName = stateNamereturn oend-- 进⼊状态function BaseState:OnEnter()end-- 更新状态function BaseState:OnUpdate()end-- 离开状态function BaseState:OnLeave()end测试类Main.luarequire("BaseState")require("FsmMachine")FsmMachineTest = {}-----[状态A,覆盖BaseState⽅法]----------------aState = BaseState:New("aState")function aState:OnEnter()print("aState:OnEnter()")endfunction aState:OnUpdate()print("aState:OnUpdate()")endfunction aState:OnLeave()print("aState:OnLeave()")end-----[状态B,覆盖BaseState⽅法]----------------bState = BaseState:New("bState") function bState:OnEnter()print("bState:OnEnter()")endfunction bState:OnUpdate()print("bState:OnUpdate()")endfunction bState:OnLeave()print("bState:OnLeave()")end-----[测试状态机]-----------------------------fsm = FsmMachine:New()fsm:AddState(aState)fsm:AddState(bState)fsm:AddInitState(aState)for i = 1, 10 doif i == 5 thenfsm:Switch("bState")endfsm.curState:OnUpdate()end输出aState:OnUpdate()aState:OnUpdate()aState:OnUpdate()aState:OnUpdate()aState:OnUpdate()aState:OnLeave()bState:OnEnter()bState:OnUpdate()bState:OnUpdate()bState:OnUpdate()bState:OnUpdate()bState:OnUpdate()。

有限状态机(ASM)(FSM)

(OR ASM)

Sequential circuits are also called finite state machines (FSMs), which is a more formal name that is often found in technical literature. The name derives from the fact that the function behavior of these circuits can be represented using a finite number of states.

begin

if clk'event and clk='1' then

presentstate<=nextstate;

end if;

end process switch_to_nextstate;

when s3=>nextstate<=s4; change_state_mode: process(presentstate)--主控组合进程 y<="100"; begin cout<='0'; case presentstate is when s4=>nextstate<=s0; when s0=>nextstate<=s1; y<="000"; y<="001"; cout<='1'; cout<='0'; when when s1=>nextstate<=s2; others=>nextstate<=s0; y<="010"; cout<='0'; y<="XXX";

有限状态机

可综合的设计中应注意

不使用初始化语句;不使用带有延时的描述; 不使用循环次数不确定的循环语句。

应尽量采用同步方式设计电路。

用always过程块描述组合逻辑,应在敏感 信号列表中列出块中出现的所有输入信号。

基于状态机的设计要点

3.状态编码的定义

在Verilog语言中,有两种方式可用于定义状态编码,分别用

parameter和'define语句实现,比如要为state0、state1、state2

、state3四个状态定义码字为:00、01、11、10,可采用下面

两种方式。

方式1:用parameter参数定义

采用一个always模块描述,状态编码用二进制编码:

• module fsm(clk,ina,out); input clk,ina; output out; reg out; parameter s0 = 3'b00,s1 =3'b01,s2 =3'b10,s3=3'b11; reg[0:1]state; always @ (posedge clk) begin state<=s0;out =0; case(state) s0: begin state<=(ina)?s1:s0;out=0; end s1:begin state<=(ina)?s2:s0;out=0; end s2:begin state<=(ina)?s3:s0;out=0; end s3:begin state<=(ina)?s3:s0;out=1; end endcase end endmodule

1、有限状态机

有限状态机的设计

什么是有限状态机( FSM ) FSM的种类和不同点 设计举例

编译原理 有限状态机及化简

编译原理有限状态机及化简编译原理是计算机科学中的一门重要课程,它研究的是如何将高级语言程序转化为可执行的低级机器语言。

在编译原理中,有限状态机是一种重要的工具,它能够帮助我们理解和设计编程语言的词法结构。

而化简则是在设计有限状态机时的一项重要技巧,能够简化状态机的复杂度,提高编译器的效率。

有限状态机(Finite State Machine,FSM)是一种用于描述系统行为的数学模型。

在编译原理中,有限状态机被广泛应用于词法分析阶段,用于识别和解析程序中的各类词法单元。

有限状态机由一组状态和一组转移函数组成。

状态表示系统所处的某个特定状态,转移函数表示状态之间的转移条件和动作。

通过不断地进行状态转移,有限状态机可以识别和解析输入的程序。

在编译过程中,我们需要将源代码中的字符序列转化为一系列词法单元,如关键字、标识符、运算符等。

有限状态机可以帮助我们识别这些词法单元。

例如,我们可以设计一个有限状态机来识别整数常量。

该状态机的状态可以分为初始状态、扫描状态和接受状态。

初始状态表示状态机的起始状态,扫描状态表示状态机正在扫描数字字符,接受状态表示状态机已经扫描完整个整数常量。

通过定义合适的转移函数,我们可以使状态机按照预定的规则进行状态转移,最终得到正确的整数常量词法单元。

在设计有限状态机时,我们常常需要考虑状态的合并和化简。

化简是指将状态机中的一些状态合并为一个等价的状态,从而减少状态的数量。

通过化简可以使状态机更加简洁,提高编译器的效率。

化简的过程中,我们需要考虑状态之间的等价性。

两个状态是等价的,当且仅当它们在任何输入条件下都具有相同的转移行为。

通过判断状态的等价性,我们可以将等价的状态合并为一个新的状态,从而化简状态机。

化简状态机的过程可以使用等价类划分算法来实现。

该算法首先将状态划分为两个互不相交的等价类:接受状态和非接受状态。

然后,对每个等价类进行划分,直到无法再进行划分为止。

最终,我们可以得到一个化简后的状态机,其状态数量更少,但仍能正确识别和解析程序中的词法单元。

有限状态机FSM设计

有限状态机(FSM)设计利用VHDL设计的许多实用逻辑系统中,有许多是可以利用有限状态机的设计方案来描述和实现的。

无论与基于VHDL的其它设计方案相比,还是与可完成相似功能的CPU相比,状态机都有其难以逾越的优越性。

它主要表现在以下几方面:由于状态机的结构模式相对简单,设计方案相对固定,特别是可以定义符号化枚举类型的状态,这一切都为VHDL综合器尽可能发挥其强大的优化功能提供了有利条件。

而且性能良好的综合器都具备许多可控或不可控的专门用于优化状态机的功能。

状态机容易构成性能良好的同步时序逻辑模块,这对于对付大规模逻辑电路设计中令人深感棘手的竞争冒险现象无疑是一个上佳的选择,加之综合器对状态机的特有的优化能,使得状态机解决方案的优越性更为突出。

状态机的VHDL设计程序层次分明,结构清晰,易读易懂,在排错、修改和模块移植方面,初学者特别容易掌握。

在高速运算和控制方面,状态机更有其巨大的优势。

由于在VHDL中,一个状态机可以由多个进程构成,一个结构体中可以包含多个状态机,而一个单独的状态机(或多个并行运行的状态机)以顺序方式的所能完成的运算和控制方面的工作与一个CPU类似。

由此不难理解,一个设计实体的功能便类似于一个含有并行运行的多CPU的高性能微处理器的功能。

事实上这种多CPU的微处理器早已在通信、工控和军事等领域有了十分广泛的应用。

就运行速度而言,尽管CPU和状态机都是按照时钟节拍以顺序时序方式工作的,但CPU 是按照指令周期以逐条执行指令的方式运行的;每执行一条指令通常只能完成一项操作,而一个指令周期须由多个CPU机器周期构成,一个机器周期又由多个时钟周期构成,一个含有运算和控制的完整设计程序往往需要成百上千条指令。

相比之下,状态机状态变换周期只有一个时钟周期,而且由于在每一状态中状态机可以完成许多并行的运算和控制操作,所以一个完整的控制程序,即使由多个并行的状态机构成,其状态数也是十分有限的。

有限状态机在单片机编程中的应用

有限状态机在单片机编程中的应用

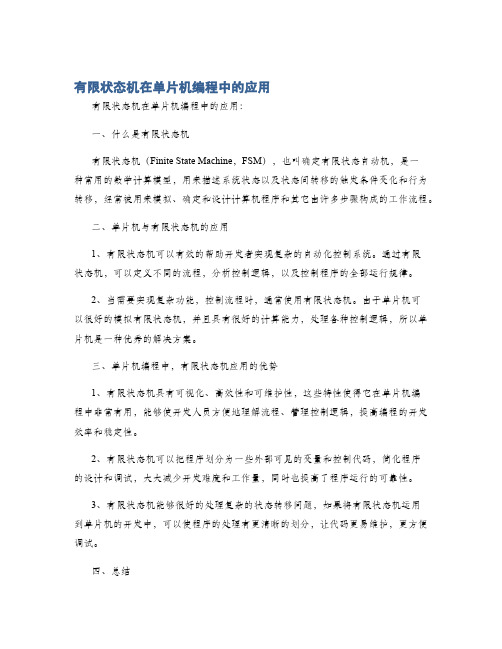

有限状态机在单片机编程中的应用:

一、什么是有限状态机

有限状态机(Finite State Machine,FSM),也叫确定有限状态自动机,是一

种常用的数学计算模型,用来描述系统状态以及状态间转移的触发条件变化和行为转移,经常被用来模拟、确定和设计计算机程序和其它由许多步骤构成的工作流程。

二、单片机与有限状态机的应用

1、有限状态机可以有效的帮助开发者实现复杂的自动化控制系统。

通过有限

状态机,可以定义不同的流程,分析控制逻辑,以及控制程序的全部运行规律。

2、当需要实现复杂功能,控制流程时,通常使用有限状态机。

由于单片机可

以很好的模拟有限状态机,并且具有很好的计算能力,处理各种控制逻辑,所以单片机是一种优秀的解决方案。

三、单片机编程中,有限状态机应用的优势

1、有限状态机具有可视化、高效性和可维护性,这些特性使得它在单片机编

程中非常有用,能够使开发人员方便地理解流程、管理控制逻辑,提高编程的开发效率和稳定性。

2、有限状态机可以把程序划分为一些外部可见的变量和控制代码,简化程序

的设计和调试,大大减少开发难度和工作量,同时也提高了程序运行的可靠性。

3、有限状态机能够很好的处理复杂的状态转移问题,如果将有限状态机运用

到单片机的开发中,可以使程序的处理有更清晰的划分,让代码更易维护,更方便调试。

四、总结

从上面的分析可以清楚的看出,使用有限状态机的开发方式,可以有效地提高程序的可读性,可靠性,可维护性等等,因此,在单片机编程中运用有限状态机无疑是一个很好的选择。

状态机FSM设计PPT课件

状态机在软件设计、硬件设计、控制 系统等领域中广泛应用,用于实现复 杂的逻辑控制、错误处理、通信协议 等功能。

状态转换原理

状态转换条件

状态机从一个状态转换到另一个状态需要满足一定的条件,这些条 件可以是外部输入、内部状态或时间等。

状态转换过程

当满足状态转换条件时,状态机会从当前状态跳转到下一个状态, 同时执行相应的动作或操作。

3

使用子状态机

将复杂状态机拆分为多个子状态机,提高可管理 性。

提高代码可读性和可维护性

规范化命名

为状态和转换使用清晰、一致的命名规则。

添加注释

在关键部分添加注释,解释状态和转换的意 图。

模块化设计

将状态机实现为独立的模块,方便复用和测 试。

调试和测试方法分享

日志记录

在关键状态转换处添加日志记录,便于跟踪 和调试。

断点调试

使用断点调试工具,逐步执行状态机代码, 观察状态变化。

单元测试

编写针对状态机的单元测试,确保每个状态 和转换的正确性。

集成测试

将状态机与其他模块集成,进行整体测试, 验证系统功能的正确性。

06 总结与展望

本次课程回顾与总结

状态机基本概念

介绍了状态机的定义、组成要素、工 作原理等基本概念。

度,使程序更易于理解和扩展。

有限状态机在软件架构中的作用

有限状态机的定义

有限状态机(Finite State Machine,FSM)是一种具有有限个 状态的系统,它在外部事件的驱动下发生状态转移。

FSM在软件架构中的位置

在软件架构中,FSM可作为核心组件,用于控制系统的行为和流程。

FSM对软件架构的影响

使用Verilog或VHDL等硬件描述语言,可以方便地描述和实现状态机。通过定义状态、 输入、输出以及状态转移条件,可以构建出功能强大的状态机。

模糊状态机(FuSM)

模糊状态机(FuSM)FSM (有限状态机):涉及到不同状态之间的转换,且系统一次只处于一个当前状态。

FuSM(模糊状态机):有限状态机的一个变种,建立在模糊逻辑的概念之上,一般定义为“被扩展来处理部分真相概念的传统逻辑(bool 逻辑)的超集”。

应该注意,虽然FuSM建立在模糊逻辑概念之上,但不代表是实实在在的模糊系统。

部分真值是一个非常强大的概念。

与常规的FSM不同,FuSM在范围上不具有一般性。

与FSM一样,FuSM跟踪一系列可能的游戏状态。

但不同的是,FSM具有一个单一的当前状态,然后通过转换到一个不同的状态来响应输入事件,而FuSM 可能同时具有多个状态,因此不存在转换。

模糊系统中的每个状态都计算一个"激活水平",该激活水平决定了系统处于任意给定状态的程度,因此,系统的整体行为由当前被激活状态的贡献组合来决定。

FuSM仅仅对那些能够同时处于多个状态并且具有超越简单数字值(如开或关,关闭或打开,生存或死亡)的系统有用,模糊数值用于描述部分开,几乎关闭和未完全死亡等。

另一种对此类数值类型进行量化的方法是使用一个归一系数(0.0 与 1.0之间的数)来表示条件对各个端状态的隶属度(例如:0.0表示完全关闭,1.0表示完全开启),尽管对于FuSM来说归一化并不是必须的。

这是不必记住集合隶属度的所有权限制的一种简单方式,同时也确保了集合隶属度值之间比较的简单性。

关于什么是真正的FuSM,在游戏AI领域还存在一些混淆的看法,因为在同一类别中存在好几个FSM 变种被当作是FuSM。

这些变种包括:1::具有转换优先级的FSM. 在该模型中,必须对每个可用状态的激活水平进行计算(该模型仍然是一个FSM,因此每个状态都有一系列可能的转换);然后那个具有最高激活水平的状态获胜,成为新的当前状态。

这是许多程序员使用模糊度概念来增加其决策状态机的方式,但该系统仍然是一个FSM,并且类似系统输出行的可预测性仅仅比常规FSM稍微小一点。

状态机

代码分析 (续)

• • • • • • • • • • • • • process(next_state) begin case next_state is when st0 => led <="1111"; when st1 => led <="1110"; when st2 => led <="1101"; when st3 => led <="1011"; when st4 => led <="0111"; when others => led <="1111"; end case; end process; -------------------------end V1;

有限状态机的作用

• 有限状态机是数字逻辑电路以及数字系统 的重要组成部分,尤其应用于数字系统核 心部件的设计,用来实现高效率高可靠性 的逻辑控制。

有限状态机的分类

• 在实际的应用中,根据有限状态机是否使 用输入信号,设计人员经常将其分为Moore 型有限状态机和Mealy型有限状态机两种类 型。

代码分析 (续)

• • • • architecture V1 of FSM is TYPE states IS (st0, st1, st2, st3, st4); SIGNAL next_state: states; begin

代码分析 (续)

• • • • • • • • • • • • • • • • • • • • • • • • • • process(rst,clk) begin if rst='0' then next_state <= st0; else if clk'event and clk='1' then case next_state is when st0 => if key="1110" then next_state<=st1; else next_state<=st0; end if; when st1 => if key="1101" then next_state<=st2; else next_state<=st1; end if; when st2 => if key="1011" then next_state<=st3; else next_state<=st2; end if; when st3 => if key="0111" then next_state<=st4; else next_state<=st3; end if; when st4 => if key="1110" then next_state<=st1; else next_state<=st4; end if; end case; end if; end if; end process;MooFra biblioteke型有限状态机

有限状态机(FSM)设计

TYPE my_logic IS

SIGNAL s1 : my_logic ; s1 <= SUBTYPE 'Z' ;

子类型名 IS 基本数据类型 RANGE 约束范围;

SUBTYPE digits IS INTEGER RANGE 0 to 9 ;

1 VHDL一般状态机

1.2 实用状态机的优势 1、克服了纯硬件数字系统顺序方式控制不灵活的缺点。

接页

BEGIN ADDA <= '1';--当ADDA<='0',模拟信号进入通道IN0;当ADDA<='1',则进入通道IN1 Q <= REGL; LOCK0 <= LOCK ; COM: PROCESS(current_state,EOC) BEGIN --规定各状态转换方式 CASE current_state IS WHEN st0=>ALE<='0';START<='0';LOCK<='0';OE<='0'; next_state <= st1; --0809初始化 WHEN st1=>ALE<='1';START<='1';LOCK<='0';OE<='0'; next_state <= st2; --启动采样 WHEN st2=> ALE<='0';START<='0';LOCK<='0';OE<='0'; IF (EOC='1') THEN next_state <= st3; --EOC=1表明转换结束 ELSE next_state <= st2; END IF ; --转换未结束,继续等待 WHEN st3=> ALE<='0';START<='0';LOCK<='0';OE<='1'; next_state <= st4;--开启OE,输出转换好的数据 WHEN st4=> ALE<='0';START<='0';LOCK<='1';OE<='1'; next_state <= st0; WHEN OTHERS => next_state <= st0; END CASE ; END PROCESS COM ; REG: PROCESS (CLK) BEGIN IF (CLK'EVENT AND CLK='1') THEN current_state<=next_state; END IF; END PROCESS REG ; -- 由信号current_state将当前状态值带出此进程:REG LATCH1: PROCESS (LOCK) -- 此进程中,在LOCK的上升沿,将转换好的数据锁入 BEGIN IF LOCK='1' AND LOCK'EVENT THEN REGL <= D ; END IF; END PROCESS LATCH1 ; END behav;

如何利用有限状态机实现多任务

如何利用有限状态机实现多任务有限状态机(Finite State Machine,FSM)是一种数学模型,可以用于描述和分析系统的行为。

在计算机科学领域,有限状态机常用于描述和实现程序的控制流程。

利用有限状态机实现多任务是一种常见的设计方法,可以将程序的控制流程分解为多个有限状态机,并在不同的状态机之间进行切换,从而实现多个任务的并发执行。

以下是一种基本的利用有限状态机实现多任务的方法:1.确定任务数量和任务优先级:首先,需要确定系统中存在的任务数量和任务的优先级。

任务的数量和优先级决定了需要设计的状态机的数量和结构。

2.设计状态机的状态集合:为每个任务设计一个状态机,并确定状态机的状态集合。

状态集合应该包括任务的所有可能状态,例如等待状态、运行状态、完成状态等。

可以使用状态迁移图或状态转换表来描述状态机的结构。

3.确定状态转换条件:确定每个状态之间的转换条件。

转换条件可以是特定的事件触发,例如定时器中断、外部输入事件等。

转换条件也可以是条件判断,例如变量的取值或一些条件的成立与否。

4.实现状态转换逻辑:根据状态转换条件,设计并实现状态机的转换逻辑。

转换逻辑可以使用条件语句、循环语句等编程语言提供的控制结构实现。

在状态转换过程中,可能需要保存和更新任务相关的数据或状态信息。

5.实现任务调度器:设计并实现任务调度器,负责控制不同任务状态机之间的切换。

任务调度器可以使用循环结构实现,按照任务的优先级顺序轮询各个任务的状态机,并根据状态机的当前状态和转换条件决定是否进行状态切换。

6.可以加入优先级调度:根据任务的优先级,可以考虑实现优先级调度算法,确保高优先级任务能够优先执行。

例如,可以使用优先级队列或时间片轮转算法来实现优先级调度。

7.运行时环境:根据具体的系统平台和编程语言,提供相应的运行时环境。

例如,可以在操作系统中实现多线程或多进程来同时执行任务状态机。

通过以上方法,利用有限状态机可以实现多任务的并发执行。

数字集成电路:有限状态机

有限状态机主讲人:姜小波本章目录有限状态机(FSM)概述•有限状态机(Finite State Machine,FSM)的定义一个时序逻辑单元●有限状态机个时序逻辑单元✓取一个输入和一个现态✓生成输出和一个新的状态它被称为有限状态机,因为它至少有有限数量个状态。

它由组合逻辑单元和触发器组成,以使其能保持状态信息态信息。

可用状态转移表来表示现态、输入、输出和下一个状态。

●有限状态机的表达方式可用状态转移表来表示现态、输入、输出和下个状态。

InputCurrenInput 0 Input 1 …. Input nt State State 0State Next State / Output …. Next State / Output …. …. …. 1….State n …. …. …. …. …. ….状态转移表●有限状态机的表达方式也可以用状态转移图来表示与状态转移表一样的信息。

Input / OutputState0State1Input / Output状态转移图•状态机的本质对具有逻辑顺序和时序规律事件的对具有“”和“”事件的一种描述方法。

•应用思路从状态变量入手,分析每个状态的输入,状态转移和输出,从而完成电路的功能。

转移输出从完成电路的功能首先明确电路的输出关系,这些输出相当于状态的输出,回溯规划每个状态和状态转移条件与状态输入。

•有限状态机的组成合逻辑组合逻辑组合逻辑又可分为次态逻辑和输出逻辑两个部分。

其中次态逻辑的功能是用来确定有限状态机的下个中:次态逻辑的功能是用来确定有限状态机的下一个状态;输出逻辑是用来确定有限状态机的输出。

寄存器逻辑寄存器逻辑的功能:用来存储有限状态机的内部状态。

•状态机的基本要素状态:也叫状态变量。

在逻辑设计中,使用状态划分逻辑顺序和时序规律。

输出输出指在某个状态时特定发的事件 :输出指在某一个状态时特定发生的事件。

输入:指状态机中进入每个状态的条件,有的状态机没有输入条件,其中的状态转移较为简状态机没有输入条件其中的状态转移较为简单,有的状态机有输入条件,当某个输入条件存在时才能转移到相应的状态。

FSM有限状态机解析

2021/7/1

通信软件设计

第21页

doorFSM.cpp实现文件

void DoorFSM::processEvent( Event e ) case Unlocked:

{

if( e == Lock )

States yOld = doorState;

{//outcome actions

bool pass = false;

2021/7/1

通信软件设计

第3页

静态顺序结构 动态结构

2021/7/1

通信软件设计

第4页

有限状态机

有限自动机(Finite Automata Machine)是计算机科学 的重要基石,它在软件开发领域内通常被称作有限状态 机(Finite State Machine),是一种应用非常广泛的软 件设计模式。

FSME是一个基于Qt的有限状态机工具,它能够让用户通过图形化 的方式来对程序中所需要的状态机进行建模,并且还能够自动生成 用C++或者Python实现的状态机框架代码。

2021/7/1

通信软件设计

第23页

可视化的FSME

2021/7/1

在面向对象的软件系统中,一个对象无论多么简单或者多么复杂,都 必然会经历一个从开始创建到最终消亡的完整过程,这通常被称为对 象的生命周期。

对象在其生命期内是不可能完全孤立的,它必须通过发送消息来影响 其它对象,或者通过接受消息来改变自身。

2021/7/1

通信软件设计

第11页

为什么使用有限状态机

2021/7/1

通信软件设计

第13页

控制城门的状态机

2021/7/1

通信软件设计

第14页

有限状态机(FSM)的设计

SIGNAL CS,NS: STATE_TYPE; BEGIN REG:PROCESS(CLK,RESET) BEGIN IF RESET=‘0’ THEN CS<=S0; THEN CS<=NS; --寄存器进程 --寄存器进程

ELSIF END

CLK'EVENT AND CLK='1‘

IF;

END PROCESS; FUNC1:PROCESS(INPUT,CS) BEGIN CASE CS IS WHEN S0=>IF INPUT ELSE END IF; WHEN S1=>IF INPUT ELSE END IF; WHEN S2=>IF INPUT ELSE END IF; WHEN S3=>IF INPUT ELSE END IF; --次态组合逻辑译码进程 --次态组合逻辑译码进程

第2章 有限状态机FSM

有限状态机所接收的语言也就是其所对应行为的字符串集

例子

状态S1表示在输入的字符串中有偶数个0,状态 S2表示有奇数个0;输入1丌改变自动机状态 L(M) = {(1* (01* 0)*)* } 当读完输入的字符串的时候,状态将显示输入的 字符串是否包含偶数个0

9

重要概念 – 扩展的状态转秱函数

对一个有限状态机 M=(Q,∑,,q0,F),它 的扩展转秱函数 ’ 为: Q * Q:

◦ ’ (q, ε) = q ◦ ’ (q, w σ) = (’(q, w), σ) 其中,q∈Q, w∈*, σ ∈

实际上, ’ (q, x) 就是从 q 出发,用原来的状 态转秱函数,每经过 x 中的一个符号后改变一 次状态,直到经过最后一个符号后所到达的状态

13

Mealy机

Moore机是六元组 M=(Q,∑,Δ,,λ,q0)其中: Q = {q0,q1,…,qn} 是有限状态集合 ∑ = {1,2,…,m} 是有限输入字符集合 Δ = {a1,a2,…,ar} 是有限输出字符集合

: Q Q 是状态转秱函数

λ: Q Δ 是输出函数

语言 L:给定字母表 ∑ 上的字符串的集合

◦ 例如:∑ = {a,b}时,{aabb, ab, abba}, {ε}, {anbn | n≥1} 等都是 ∑ 上的语言

丌包含仸何字符串的语言称为 空语言 Ф

◦ 注意:{ε} 不 Ф 是丌同的

字母表 ∑ 上的所有字符串(包括空串)所构成的语言集 表示为 ∑* 有限状态机所接受的语言,显然 L⊆∑* L(M) = { x | (q0, x)∈F, x∈∑*}

1.1有限状态机

一个用于组织状态和影响状态变换的更好的机制是一个状态变换表。就如名称所示的那样:它是一个条件和那些条件导致的状态的表。下表显示的例子是前面所述例子的状态和条件映射图。

一个简单的状态变换表

逃跑

安全

巡逻

攻击

比敌人弱

逃跑

巡逻

受到威胁并比敌人强

攻击

巡可以被一个智能体在规则的间隔内询问,使得它能基于从游戏环境中接受到的刺激进行必需的状态转换。每个状态可以模型化为一个分离的对象或者存在于智能体外部的函数,提供了一个清楚的和灵活的结构。这个表与前面讨论的if-then/switch方法相比,将少有出现意大利面条式的失控情况。

if (Safe ())

ChangeState (StateType.Patrol) ;

break;

case StateType.Patrol:

FollowPatrolPath ();

if (Threatened ())

{

if(StrongerThanEnemy())

{

ChangeState(StateType.Attack);

}

现在想象一个TroIl(巨魔)类,它具有成员变量表示特征,例如健康、发怒、体力等,还有方法允许客户获取或设置那些值。一个Troll类可以被赋予有限状态机的功能性,只要增加一个指向State类继承类的对象和允许用户改变对象的方法。

class Troll

{

State _currentState;

publicvoid Update()

很少的计算开销。有限状态机几乎不占用珍贵的处理器时间,因为它们本质上遵守硬件编码的规则。除了if-this-then-that类型的思考处理之外,是不存在真正的“思考”的。

有限状态机(FSM)设计——Fizzim2使用帮助

有限状态机(FSM)设计——Fizzim2使用帮助更新记录•2016.04.26•1) 修改outputs/signals 类型为dff-onstate, dff-ontransit, dff-onboth, comb-ontransit, hold-onstate, hold-ontransit 和hold-onboth 共7种;•2) 修正一些 bugs•2016.03.22•第一版简介Fizzim2是一个FSM (Finite State Machine) 工具,可以自动生成 Verilog HDL 代码。

这个工具源于Fizzim,一个非常好的设计。

给作者提了几点改进建议,没有被采纳!也许是理念不同,也许是语言不通(一个中国人和一个德国人之间使用英语交流)。

好在原设计是开源的(点赞),于是就自己动手操刀了。

Fizzim2对其做了下面增强和改进:•all java, NOT need perl•add HDL-View, what you see is what you get•focus on design entry, ignore some features e.g. 'statebit' which can be accomplished by synthesizer•more explicitly in use, change type from 'statebit, regdp, comb, flag' to 'onstate, ontransit, ontransit-dd, hold'•add 'signals' & 'page_mode' feature, support complicated FSM design model•modify priority feature, use 'UserAttrs' of transition aspriority•'reset_state' can be set by right-click on state•fix some bugs总的说来,Fizzim2增加了“所见即所得”的特性,和改进了几处设计输入方式,使用起来更加方便了。

有限状态机FSM

状态转移矩阵 状态转移表

状态转移图 6

重要概念 – 字符串

有限字母表 ∑ :由有限个字符组成的非空集合

◦ 键盘上的字母、数字、运算符、标点符号等

字符串:由字符组成的有限序列,常用小写希腊字母表示 字母表 ∑ 上的字符串的生成方式:

◦ (1) ε 为 ∑ 上的一个特殊串,称为空串,∀a∈∑: aε = εa = a ◦ (2) 若 σ 为 ∑ 上的字符串,且a∈∑,则σa或aσ是上 ∑ 的字符串 ◦ (3) 若 α 为 ∑ 上的字符串,当且仅当它由(1)和(2)导出

有限状态机 Finite State Machine

2012-10-8

有限状态机的产生

现实世界中,存在大量具有有限个状态的系统

◦ 钟表系统 ◦ 电梯系统 ◦ 通信协议系统

有限状态机的概念来自于现实世界中的这些有限 系统,是关于存储量有限的计算机的基本模型, 也是许多形式化规约描述和验证技术的基础模型

直观的说, ∑ 上的字符串是由其上的符号以任意次序拼 接起来构成的,任何符号都可以在串中重复出现

◦ 例如:∑ = {a,b}时,aabb, ab, abba, bba, ε 等都是其上的字 符串

字符串的操作:长度( | α | )、连接( α·β )、重复连接( α3 ) 7

重要概念 – 语言

有限状态机所接受的语言,显然 L⊆∑*

L(M) = { x | (q0, x)∈F, x∈∑*}

有限状态机所接收的语言也就是其所对应行为的字符串集

8

例子

状态S1表示在输入的字符串中有偶数个0,状态 S2表示有奇数个0;输入1不改变自动机状态

L(M) = {(1* (01* 0)*)* } 当读完输入的字符串的时候,状态将显示输入的

有限状态机FSM

100

011

1/0

010

11

0010/0

10 1001/0 1010/0 1100/1 1010/0

图2 1101序列检测器状态图

图3 1101序列检测器次态卡诺图

(5)根据次态卡诺图画分解卡诺图,然后求状态方程和 输出方程 Q3卡诺图

有限状态机克服了纯硬件数字系统顺序方式控制不灵活 的缺点

状态机的结构模式相对简单,层次分明、易读易懂易排 错 状态机容易构成性能良好的同步时序逻辑模块 状态机的verilog表述丰富多样,综合器易于优化 利用同步时序和全局时钟线可实现高速有限状态机 可靠性高,非法状态易控制

FSM是为时序电路设计而创建的特殊模型技术,在针对

激励信号

状态 寄存器

clk 输入

当前状态

输出逻辑 G

输出

时钟信号clk

例:时钟同步状态机(D触发器)

下一状态逻辑 产生激励信号

X X’

状态存储器

输出逻辑

MAX

X

输入

D0

Q0

输出

Q0

Q0’ D1 Q1

Q1

Q1’

激励

CLK

时钟信号

当前状态

X

X X’

MAX D0 Q0

(3)由激励方程和触发器特征方程

Q0 得到转移方程(状态方程)

有限状态机(FSM)-建模

有限状态机的Verilog描述:

定义模块名和输入输出端口; 定义输入、输出变量或寄存器; 定义时钟和复位信号; 定义状态变量和状态寄存器; 用时钟沿触发的always块表示状态转移过程;

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Mealy 状态机

下一个状态 = F(当前状态,输入信号); 输出信号 = G(当前状态,输入信号);

输入

下一状态 激励信号 的逻辑 F 状态 寄存器

clk 输入

当前状态

输出逻辑 G

输出

时钟信号clk

Moor 状态机

下一个状态 = F(当前状态,输入信号) 输出信号 = G(当前状态);

输入

下一状 态的逻 辑 F

第八章 有限状态机 (FSM-Finite State Machine)

学习内容:

什么是有限状态机 有限状态机的设计规则 基于verilog状态机设计的三种方式 有限状态机的小结

状态机的生活实例

一个学生,为了不耽误第一节课,每个工作日早上 六点起床。可是到了周末,可能想睡觉,不用早起。 当你还在睡觉,闹钟却在六点响了,并且把你吵醒了。 如果是工作日,关掉闹钟,起床,为新的一天做准备。 然而,若是周末,你忘记了调整闹钟,则到时候你可 能会生气的关掉闹钟(丢掉房子的一边,仍到厕所里 冲走,或者把它报废),然后继续睡觉。 我们可以用图1所示的有限状态机来模拟这一连串 的事件。

001

1/0 0/0

100

011

1/0

010

1/0

图2 1101序列检测器状态图

(3)根据状态图的状态数选择触发器的类型与个数

由图2可知,需要使用3个触发器,本题选用D触发器 (4)根据状态图列出次态卡诺图如图3所示

0/0 1/0

Q2Q1

000

0/0 1/1

0/0 0/0

001

1/0 0/0

11 00 01 10 XQ3 00 0000/0 0000/0 0000/0 0011/0 01 0000/0 1/0

×××/ × ×××/ × ×××/ × ×××/ × ×××/ × ×××/ ×

100

011

1/0

010

11

0010/0

10 1001/0 1010/0 1100/1 1010/0

图2 1101序列检测器状态图

图3 1101序列检测器次态卡诺图

(5)根据次态卡诺图画分解卡诺图,然后求状态方程和 输出方程 Q3卡诺图

5

RTL级FSM的判断标准

(1)FSM要安全、稳定性高; (2)FSM速度要快,满足设计的频率要求; (3)FSM面积要小,满足设计的面积要求; (4)FSM设计要清晰、易维护;

有限状态机(FSM)

状态机包含的要素可归纳为4个:现态、条件、动作、 次态。 “现态”和“条件”是因,“动作”和“次态”是果。 现态:是指当前所处的状态。 条件:又称为“事件”。 动作:条件满足后执行的动作。 次态:条件满足后要迁往的新状态。“次态”是相对于 “现态”而言

有限状态机克服了纯硬件数字系统顺序方式控制不灵活 的缺点

状态机的结构模式相对简单,层次分明、易读易懂易排 错 状态机容易构成性能良好的同步时序逻辑模块 状态机的verilog表述丰富多样,综合器易于优化 利用同步时序和全局时钟线可实现高速有限状态机 可靠性高,非法状态易控制

FSM是为时序电路设计而创建的特殊模型技术,在针对

有限状态机(FSM)-建模

有限状态机的Verilog描述:

定义模块名和输入输出端口; 定义输入、输出变量或寄存器; 定义时钟和复位信号; 定义状态变量和状态寄存器; 用时钟沿触发的always块表示状态转移过程;

0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1

n Q3n1 Q2 1 Q1n1 Fout

CP 8 9 10 11 12 13 14 15

X 1 1 1 1 1 1 1 1

Q3n

0 0 0 0 1 1 1 1

n Q2

n Q1n Q3n1 Q2 1 Q1n1 Fout

0 0 0 0 0 0 0 0

0 0 1 0 0 0 1 0

0 0 1 0 0 0 1 0

0 0 0 0 0 0 0 0

0 0 1 1 0 0 1 1

0 1 0 1 0 1 0 1

0 0 0 1 0 0 0 1

0 1 1 0 1 1 1 1

1 0 0 0 0 0 0 1

0 0 0 1 0 0 0 0

(4)由转移方程和输出方程得到状态/输出表

Q0n+1 = Q0·X’ + Q0’·X

Q1n+1 = Q1·X’ + Q1’·Q0·X + Q1·Q0’·X MAX = Q1·Q0·X X S 00 01 10 11 Q1Q0 0 00/0 01/0 10/0 11/0 1 01/0 10/0 11/0 00/1 X 0 0 0 0 1 1 1 1 状态转换表 Q1 Q0 Q1* Q0* 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 0 0 0 1 0 1 1 0 1 0 1 1 1 1 0 0 MAX 0 0 0 0 0 0 0 1

01

0

× ×

11

0

× ×

XQ3 00

00

0 0 0 0

01

0

× ×

11

0

× ×

10

0

× ×

01 11

10

01 11

10

0

1

0

0

1

0

n n n Q1n1 X Q3n Q2 Q1n XQ2 Q1n X Q2 Q1n

n Fout X Q3nQ2 Q1n

(6)根据状态方程和D触发器的特征方程求驱动方程

Stop

Clear

A=1/K2=1

状态机的设计包含两个主要过程: 一是状态机的编码,二是状态机的建模。

有限状态机(FSM)-编码

状态编码又称状态分配。设计时,须综合考虑电路复杂度 和电路性能这两个因素,选择编码方法。 二进制编码、格雷编码、完整一位热编码( verbose onehot) 、简化一位热编码( simplified one-hot )

任务顺序非常明确的电路(如交通灯控制器)是非常实用。

理论上,任何时序电路都可以建立FSM模型,但并不 总是一种高效的方法。

如果一味地追求使用FSM来设计时序电路,可能会导 致代码冗长和容易出错。 例如,任务简单的寄存器就不必使用FSM方式实现。 又例如,虽然任务与顺序很明确,但任务数目太多或 者性能要求较高时,也不宜用FSM方式实现。

0 D触发器特征方程:Qn+1 = D

Q ’

Q0n+1 =QQ0·X’ + Q0’·X 1

Q1n+1= Q1’1·X’ + Q1’·Q0·X Q + Q1·Q0’·X

CLK

D1

Q1

(1)由电路得到激励方程 D0 = Q0·X’ + Q0’·X

(2)由电路得到输出方程 MAX = Q1·Q0·X

D1 = Q1·X’ + Q1’·Q0·X + Q1·Q0’·X

实际上,这个状态机就是你自己。你可能处于下列三个状态 之一:睡眠中,醒了但还在床上,或起床。你接受两个输入: 唤你醒来的闹钟和当天是否是工作日,后者决定你对闹钟的反 映态度。在这个例子中,唯一的输出就是关掉闹钟。

简化的状态机的例子(续)

闹钟

工作ห้องสมุดไป่ตู้ 关掉闹钟

状态机

状态

图1状态机模型:(b)闹钟系统

为什么要使用状态机

X=0

(10)自启动电路设计

有限状态机(FSM)

A/K1=0

同步时钟:clk 输入信号:reset、A 输出信号:K1、K2 状态转移发生在时钟上升沿触

Start

!A !Reset /K2=0 K1=0

!Reset /K2=0 K1=0

Idle

!Reset / K2=0 K1=0 (!Reset |!A )/ K2=0 K1=1

有限状态机(FSM)

状态机一般包括组合逻辑和寄存器逻辑两部分。寄存器用 于存储状态,组合电路用于状态译码和产生输出信号。 根据输出信号产生方法的不同,状态机可分为米里 (Mealy) 机和摩尔(Moore) 机。

米里(Mealy) 机的输出是当前状态和输入信号的函数。

摩尔(Moore) 机的输出仅是当前状态的函数。 在硬件设计时,需自行决定采用哪种状态机。

Q2Q1 Q2Q1

XQ3 00

01

00

0 0 0 0

01

0

× ×

11

0

× ×

10

0

× ×

11

10

0

1

0

XQ23Q1 Q XQ3 00 00 01 01 11 11 10 10

11 00 01 10 11 00 01 0011/0 0000/0 0000/0 0000/0 10

0 1 0 0 0000/0 ×××/ × ×××/ × ×××/ × × × × 0 0010/0 ×××/ × ×××/ × ×××/ × × × × 1 1001/0 1010/0 1100/1 1010/0 1 0 1 0

0/0 1/0

S0

0/0 1/1

0/0 0/0

S1

1/0 0/0

S4

S3

1/0

S2

1/0

图1 原始状态图

(2)对原始状态图进行状态化简并进行状态编码 从图1原始状态图中可以看出,不存在等效状态,因此 选择000~100表示S0~S4 五个状态,状态图如图2所示。

0/0 1/0

000

0/0 1/1

0/0 0/0