Encounter 快速入门教程

SOC_encounter使用说明

上述设置如下图所示:

具体的电源条 参数值需根据 设计特点如功 耗值,设计面 积等信息进行 设定。

设置完成后,8条垂直电源条如下分布:

上述若发现存在Stripes未连接上,则点击菜单栏Route Special Route, 只选择‘Stripes(unconnected)‟选项,如下 图:

2011.01.09

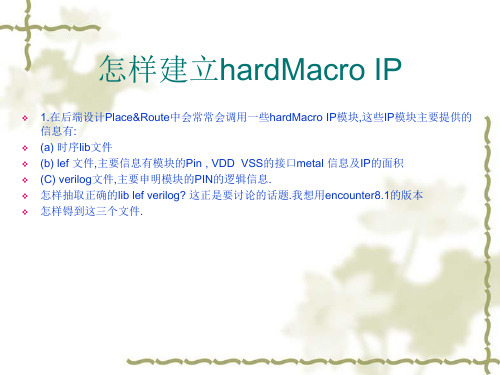

概要

在本篇ppt中,主要以一个32位的流水线加法 器设计为例,介绍SOC Encounter V7.1版本 自动布局布线工具的主要使用方法及步骤。

目录

以加法器为例,将综合后的结果导入SOC Encounter, 生成 GDSII版图分为以下几个步骤:

根据设计特点不同,这些选 项可灵活调整。

• 点击‘Attribute‟键,设置一些Net的属性,如下:

选中‘Net Type‟,选择‘Clock Nets‟, 即对时钟Nets的布线作一些 特殊设置。

Skip Antenna: 选择FALSE; Skip Rouing: 选择FALSE; Avoid Detour: 选择TRUE; SI Prevention: 选择TRUE; SI Post Route Fix: 选择 TRUE; Weight: 10; Spacing: 1。设置如下,然后点击‘OK‟。

(5)给’Advanced‘中SI Analysis项填入如下噪声库.cdB文件:

上述各项填好后,点‟save‟将此次的设置保存成.conf文件,然后 点击’OK„键即可导入设计,如下图:

Floorplan

点击菜单栏Floorplan Specify Floorplan,如下:

• 指定Core/Die的面积或者Core的利用率,如本例中指定了Die的 宽高分别为3200,3200um。具体的大小值可通过预估,试验几 次等方法进行估算。 • 指定Core到IO/Die边界的距离,以给电源环留下足够的空间,本 例中设定Core到IO边界上下左右的距离都为100um。如下图:

Eclipse快捷键和一些用法

Eclipse快捷键:Ctrl+1 助手键(定位到某元素提供最可能的帮助)Ctrl+3 万能键(可以锁定工具栏中任意工具以及其它的工具都可以锁定)Ctrl+D: 删除当前行Ctrl+J 正向增量查找(跟ctrl+f相比,优点显而意见,操作简单,也不挡着视线)Ctrl+Shift+ K 向上查找(ctrl+shift+k 向上查找跟上面的一样好使)Ctrl+shift+j 反向查找Alt+Enter 显示当前选择资源(工程,or 文件or文件)的属性Ctrl+Shift+L抽取本地变量( 可以直接把一些魔法数字和字符串抽取成一个变量,尤其是多处调用的时候)Alt+↓当前行和下面一行交互位置(可以省去先剪切,再粘贴了)Alt+↑当前行和上面一行交互位置(同上)Ctrl+K 快速定位到下一个Ctrl+Shift+X 把当前选中的文本全部变大写Ctrl+Shift+Y 把当前选中的文本全部变为小写Ctrl+Shift+F 格式化当前代码Ctrl+Shift+P 定位到对于的匹配符(譬如{})Alt+Shift+z (if(),whlie(),for(),…包围选中的代码)Alt+Enter 显示当前选择资源(工程,or 文件or文件)的属性Shift+Enter 在当前行的下一行插入空行(这时鼠标可以在当前行的任一位置,不一定是最后)Shift+Ctrl+Enter 在当前行插入空行(原理同上条)Ctrl+Q 定位到最后编辑的地方Ctrl+L 定位在某行(对于程序超过100的人就有福音了)Ctrl+M 最大化当前的Edit或View (再按则反之)Ctrl+/ 注释当前行,再按则取消注释Ctrl+O 快速显示OutLine二.Eclipse应用:代码片段:主要把那些比较通用的代码保存成一个片段。

选中一块代码然后右键点击Add to Snippets....就出现一个对话框,填写此代码片段的类型,也可以使用已经有了的代码片段类型,然后再出现一个Customize palette 的对话框,里面可以在Variables 里面增加变量,然后在下面的代码中引用就可以了。

Carbide 3D BitRunner V2快速入门指南说明书

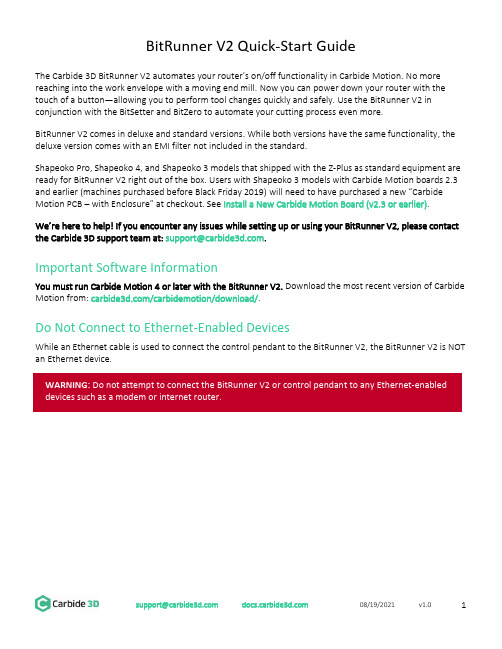

BitRunner V2 Quick-Start GuideThe Carbide 3D BitRunner V2 automates your router’s on/off functionality in Carbide Motion. No more reaching into the work envelope with a moving end mill. Now you can power down your router with the touch of a button—allowing you to perform tool changes quickly and safely. Use the BitRunner V2 in conjunction with the BitSetter and BitZero to automate your cutting process even more.BitRunner V2 comes in deluxe and standard versions. While both versions have the same functionality, the deluxe version comes with an EMI filter not included in the standard.Shapeoko Pro, Shapeoko 4, and Shapeoko 3 models that shipped with the Z-Plus as standard equipment are ready for BitRunner V2 right out of the box. Users with Shapeoko 3 models with Carbide Motion boards 2.3 and earlier (machines purchased before Black Friday 2019) will need to have pu rchased a new “Carbide Motion PCB –with Enclosure” at checkout. See Install a New Carbide Motion Board (v2.3 or earlier).We’re here to help! If you encounter any issues while setting up or using your BitRunner V2, please contact the Carbide 3D support team at: *********************.Important Software InformationYou must run Carbide Motion 4 or later with the BitRunner V2. Download the most recent version of Carbide Motion from: /carbidemotion/download/.Do Not Connect to Ethernet-Enabled DevicesWhile an Ethernet cable is used to connect the control pendant to the BitRunner V2, the BitRunner V2 is NOT an Ethernet device.Setting Up the BitRunner V21.1 Review BitRunner V2 Kit ContentsFigure 1Item Description Qty NoteA BitRunner V2 (Deluxe or Standard) 1 BitRunner V2 enclosure and attached power cordsB Control Pendant 1 Enable/disable the BitRunner V2C Logic Cable 1 Connects the BitRunner V2 to the controllerD Ethernet Cable 1 Connects the BitRunner V2 to the control pendantE Grounding Cable 1 Attaches to spindle mount to ground the spindle1.2 Install a New Carbide Motion Board (v2.3 or earlier)If you have an older Carbide Motion board (2.3 or earlier), you should have purchased a new Carbide Motion PCB and enclosure with your BitRunner V2. Before setting up the BitRunner V2, you will need to install the new controller:1.Power off the machine.2.Disconnect the power and USB cables, and all of the motor cables and homing switches from theboard.3.Remove your old controller from the machine.4.Install the new controller. The USB and power ports face the back of the machine.5.Reconnect the motor, homing switch, power, and USB cables.1.3 Connect the BitRunner V2 to the ControllerThe BitRunner V2 is designed to lay flat on the ground near your work table and electrical outlet.The 6-pin male-to-female logic cable connects the BitRunner V2 to the Shapeoko controller. The male end of the cable plugs into the BitRunner V2 and the female end plugs into the controller.1.Plug the male end of the logic cable into the 6-pin female port on the top of the BitRunner V2. SeeFigure 2.a.The black plastic latch on the side of the connector faces RIGHT.b.Make sure the connector is fully seated. You will hear the latch click into place.Figure 21.Plug the cable’s female end into the 6-pin male BitRunner V2 connector protruding from the front-end of the controller. See Figure 3.a.The small triangular peg faces OUT (away from the rail).b.The connector fits tightly. Press in and down to get it to seat fully.Figure 31.4 Connect the BitRunner V2 to the Control PendantUse the flat black Ethernet cable to connect the BitRunner V2 to the control pendant. The two ends of the cable are interchangeable. See Figure 4.1.Plug one end of the Ethernet cable into the Ethernet jack on the control pendant.a.The clear latch and black strain-relief boot face up.b.Press firmly to fully seat the connector. You will hear the latch click into place.Figure 42.Plug the other end of the Ethernet cable into the jack on the top of the BitRunner V2. See Figure 5.a.The clear latch and black strain-relief boot face LEFT.b. Press firmly to fully seat the connector. You will hear the latch click into place.Figure 51.5 Connect the BitRunner V2 to the Router and Power1.Plug the spindle/router power cord into the short female power cable on the left side of theBitRunner V2.2.Plug the longer male power cable into a wall outlet.1.6 Attach the Grounding Cable to the Spindle Mount (Optional)To attach the grounding cable:1.Insert the banana plug into the round port on the top of the BitRunner V2. See Figure 6.Figure 6e an M5 screw to secure the ring terminal end of the grounding cable to one of the two M5 holeson the left side of the spindle mount. See Figure 7.e a couple of zip ties to secure the grounding cable. Make sure the cable is secured where it willnot get in the way of the machine’s movements.Figure 71.7 Upgrade Carbide MotionThe BitRunner V2 requires at least Carbide Motion 4.1.Check for the build number in the bottom-left corner of Carbide Motion. Build numbers higher than400 do not need to be upgraded.2.If you have an older version, download the most recent version of Carbide Motion from/carbidemotion/download and install it to your computer.Using the BitRunner V22.1 Enable/Disable the BitRunner V2The BitRunner V2 is enabled and disabled via the control pendant.To enable the BitRunner V2:1.Press the control pendant button to supply power to the router. The red button LED will turn ON. SeeFigure 8.Figure 8To disable the BitRunner V2:2.Press the control pendant button again to cut power to the router. The button LED will turn OFF.2.2 Install an End Mill1.Press the control pendant button to disable the BitRunner V2 (button LED will be OFF).2.Flip the power switch on the router to the OFF position.3.Install the end mill.2.3 Run the Project G-code1.Flip the power switch on the router to the ON position.2.Press the button on the control pendant to enable the BitRunner V2.3.Load the G-code (.nc file) in Carbide Motion.The G-code (or absence thereof) determines when BitRunner V2 cuts or supplies power to the router. If there is no G-code/.nc file being executed in Carbide Motion, then no power is supplied to the router. TheG-code also triggers alert boxes to open in Carbide Motion which let you know when it’s time to change the end mill, what RPM to set the spindle to, etc.When G-code is executed in Carbide Motion, specific commands will determine if power is on or off: •An M3 S command of 1000 or greater (1000 is the RPM) automatically turns the router on. M3 S2800 is an example M3 S command. Alternately, you might see commands written like this: M3S2800.•An M5 command turns the router off.•An M6 command indicates a tool change.2.4 Perform Tool Changes1.When the G-code reaches a tool-change command (M6) Carbide Motion will pause the job, cutpower to the router, and alert you that it’s time to change the tool.2.Press the control pendant button to disable the BitRunner V2 (button LED will turn off).3.Flip the power switch on the router to the OFF position.4.Change the end mill.5.Flip the power switch on the router to the ON position.6.Press the control pendant button again to re-enable the BitRunner V2 (button LED will turn on).7.In Carbide Motion, click the Resume button to resume cutting. Carbide Motion will continue cuttinguntil it’s time to perform another tool change, load the next G-code file, or until the project is done.See Figure 9.Figure 9Troubleshooting and Maintenance 3.1 Troubleshooting Guide3.2 MaintenanceCheck the top of the BitRunner V2 for dust accumulation periodically, and vacuum when necessary.3.3 Replacing the FuseThe fuse may have blown if you know the G-code is good and the control pendant LED still lights up, but the BitRunner V2 has stopped working.1.Unplug the BitRunner V2 from the power source and unplug all cables on the top of the device.e a 2.5mm hex key to remove the four FHS securing the back panel.e a 2.5 mm hex key to remove the six BHCS securing the metal EMI shield. See Figure 10.Figure 10e a small flathead screwdriver to carefully pry open the lid of the small black fuse box. SeeFigure 11.a.Pry from the left side of the fuse box, near the “B” embossed on the lid.Figure 11NOTE: Figure 11 shows the deluxe BitRunner V2. The standard version will not have the large coils under the metal EMI shield.e your finger or a small flathead screwdriver to carefully remove the fuse. See Figure 12.Figure 126.Insert a new 15A 250V 5×20mm fuse.7.Replace the metal EMI shield.8.Replace the back panel of the BitRunner V2.。

ABAP新手资料-[SAP Script 编程指南-DOC]

![ABAP新手资料-[SAP Script 编程指南-DOC]](https://img.taocdn.com/s3/m/61cfab00eefdc8d377ee3225.png)

1 SAPscript Forms31.1 SAPscript的组成 (3)1.2 Forms: 组件和技术 (3)1.2.1 概念 (3)1.2.1.1修改SAP Forms (3)1.2.1.2 Forms:概念 (4)1.2.1.3 Client和语言版本:概念 (4)1.2.2 组件 (5)1.2.2.1 Header Data (5)1.2.2.2 Paragraph Formats and Attributes (6)1.2.2.3 Character Formats and Attributes (8)1.2.2.4 Windows (8)1.2.2.5 Pages(页面) (10)1.2.2.6 Pages window(页面窗口) (11)1.2.2.7 Text Elements (文本元素) (12)1.2.3 技术 (15)1.2.3.1在Form中包含图形 (15)1.2.3.2在FORM中包含公司logo (17)1.2.3.3在form中打印条形码 (24)1.2.3.4 Using Boxes, Lines, and Shading (27)2.SAPscript Control Commands (30)2.1 Control Commands语法 (30)2.2 Control Commands 种类 (30)2.2.1 显示分页:NEW-PAGE (30)2.2.2 限制分页:PROTECT (31)2.2.3 下一个main window命令:NEW-WINDOW (31)2.2.4 给文本symbol分配值:DEFINE (32)2.2.5 格式化日期字段:SET DATE MASK (32)2.2.6 格式化Time字段:SET TIME MASK (33)2.2.7 设置与国家相关的格式:SET COUNTRY (33)2.2.8 设置symbol位:SET SIGN (34)2.2.9 Initializing Numbered Paragraphs:RESET (34)2.2.10包含其他文本:INCLUDE (35)2.2.11改变样式:STYLE (35)2.2.12格式化地址:ADDRESS (36)2.2.13在main window中设置Header Text:TOP (37)2.2.14在main window中设置Footer Text:BOTTOM (37)2.2.15条件文本:IF (37)2.2.16条件文本:CASE (38)2.2.17调用ABAP子程序:PERFORM (38)2.2.18合计:SUMMING (40)3.SAPscript Symbols (40)3.1Syntax of Symbols (41)3.2System Symbols (41)3.3Program Symbols (42)3.4Standard Symbols (43)3.5Text Symbols (43)4.Formatting Options (44)4.1Offset(偏移量) (44)4.2Output Length (44)4.3 Omitting the Leading Sign (45)4.3 Omitting Leading Zeros (45)4.4 Space Compression (45)4.5 Number of Decimal Places (46)4.6 Omitting the Separator for ‘Thousands’ (46)4.7 Specifying an Exponent for Floating Point Numbers (46)4.8 Right-Justified Output (47)4.9 Fill Characters (47)4.10 Suppressing Output of Initial Values (47)4.11Local Dates(Currently Only for Japan) (48)4.12Changing the Value of a Counter (48)4.13Preceding and Subsequent Texts(Pre-Text/Post-Text) (48)5.SAPscript Function Modules (49)5.1OPEN_FORM (51)5.2CLOSE_FORM (53)5.3WRITE_FORM (53)6一个完整的例子 (54)1 SAPscript Forms1.1 SAPscript的组成SAPscript由下面五个部分组成:1)编辑器用来编辑一行文本。

encounter很好的辅导资料

Invoke Cadence On-Line Document

1. 在terminal里执行 unix% /usr/cad/cadence/SOC/cur/tools/bin/cdnshelp & 如 果不输入完整路径而真接输入cdsdoc,则根据PATH设定的顺序不同可能会执 行到其它cadence软件的On-Line document。 2. 在Language上連点兩下,底下窗口列出LEF和DEF的文件, 再在LEF/DEF 5.6 Language Reference 上連点兩下,右边出现这份文件的内容。 在LEF Syntax上点兩下,应可看到所有LEF的语法說明,你可以再往下点找到详细的 LEF语法。 3. 回到Products页(现在可能被收起來了, 按一下Products展开),展开 SoC

Start SOC Encounter

5. 进入Lab-A lab unix% cd Lab-A 6. 这个Lab的设计档放在design_data目錄里, cell library的档案放在library目 錄里, 如果你是在学校里做这个design, 你必须从CIC提供tsmc.13 design kit 里找到这些档案. 7. 进入Lab2 unix% cd Lab2

Page 1 of 32

z

Lab1 On-Line Document { Logging in { Invoke Cadence On-Line Document { Lab2 System Startup Logging in Copy lab material Start SOC Encounter { Lab3 Design Import, floorplan Prepare Data Design Import Global Net Connect Specify Scan Chang Floorplan { Lab4 Powerplan Powerplan

Sporter Ballistic Chronograph 快速入门指南说明书

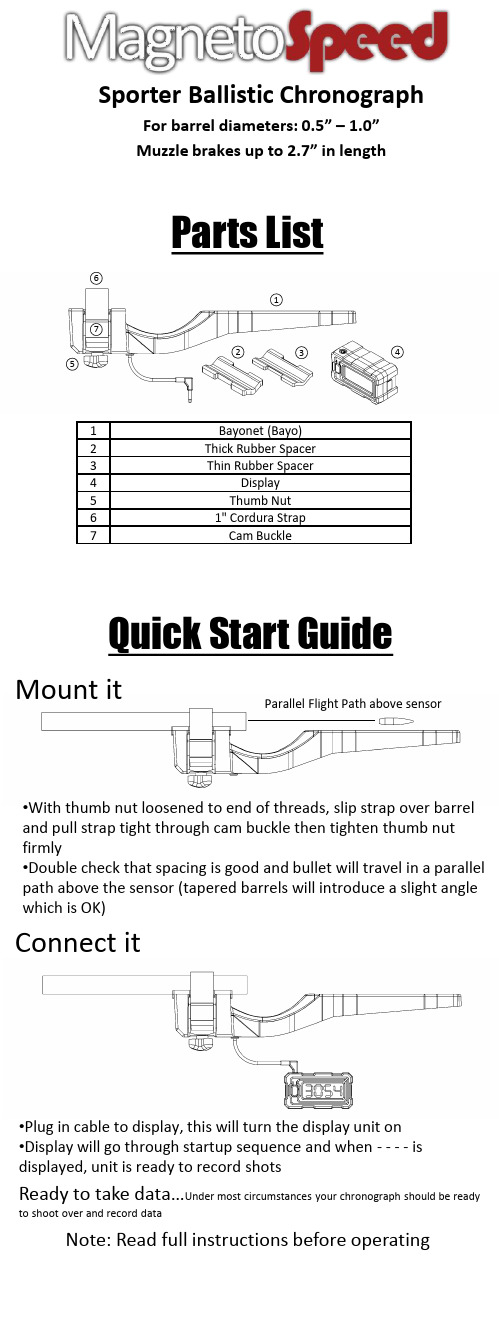

Sporter Ballistic ChronographFor barrel diameters: 0.5” –1.0”Muzzle brakes up to 2.7” in length Quick Start Guide Mount it Parallel Flight Path above sensor •With thumb nut loosened to end of threads, slip strap over barrel and pull strap tight through cam buckle then tighten thumb nut firmly•Double check that spacing is good and bullet will travel in a parallel path above the sensor (tapered barrels will introduce a slight angle which is OK)Connect it•Plug in cable to display, this will turn the display unit on •Display will go through startup sequence and when ----is displayed, unit is ready to record shotsNote: Read full instructions before operating Ready to take data…Under most circumstances your chronograph should be ready to shoot over and record data Parts List12345671Bayonet (Bayo)2Thick Rubber Spacer 3Thin Rubber Spacer 4Display 5Thumb Nut 61" Cordura Strap 7Cam BuckleStrapping the Bayonet (Bayo)•Seat muzzle end of barrel in V-block groove under strap. Use thicker rubber pad for thin-walled barrels•Make sure sensor deck is down-range from muzzle.•Make sure muzzle is 0.25-2.0 inches down-range from front of V-block (overhanging into blast zone).•Make sure Thumb Nut is "unscrewed" almost all the way but still attached to end of Strap Screw.•Pull cinch strap up through strap adjuster until ALL slack is taken up around barrel.•Tighten Thumb Nut against Screw Frame until tight.•Test grip of strap by tugging on the bayo; if unmovable then proceed. If not, continue tightening Thumb Screw.•Remove bolt from gun (if possible) and look down the barrel towards the muzzle; make sure the bayo sensor deck cannot be seen through barrel to ensure bullet will not encounter bayo. MAKE SURE BAYO SENSOR DECK IS NOT IN THE PATH OF THE BULLET!•Plug data cord into display unit jack. Continue to check muzzle location with reference to the V-block. If bayo is creeping off, retighten strap with muzzle in proper position.•To remove, simply unscrew Thumb Nut to let off tension, pull back strap adjuster, slide off muzzle.•Note: Loose strap end can be placed in strap collector slot in Screw Frame during storage/use.•Loose strap. Thumbscrew at bottom of threads.•Thumbscrew tightened, with strap tucked in strap keeper.Disclaimer: The bayo is designed to fit tapered and bull barrel muzzles between 0.50 and 1.00 inches in diameter. It is the responsibility of the user to make sure that the bayo is mounted correctly with the sensor deck away from the bullet path.DimensionsDisplay Operation•To turn display on, plug cable into the jack on top of the display •This display is a 7 segment display, so refer to the guide word key •The display will cycle through a startup sequence that displays the following, and the current settings•Firmware version•Battery voltage (ex. 8.8)•Sensitivity: -(Regular), (High 1) or (High 2)•Units: (Feet per sec) or (Meters per sec)•The unit will then arrive at the Home ScreenHome Screen with no shotsReady to record new shotsHome Screen with 13 shotsReady to record, will add to current shot string •To change sensitivity, from the Home Screen hold down the button until “Conf” flashes. Release the button. The current sensitivity setting will be displayed. Hold down the button again, until “done” is displayed. The sensitivity settings will change in the order of Reg, HI 1, then HI 2. To go from Reg to HI 2, you would have to cycle the sensitivity setting twice. After a change of sensitivity the display will flash the new setting. At any point if the button is not pressed for 20 seconds, the display will return to the home screen.•To change units of measure, hold down the button while plugging unit in. After “Conf” flashes, release button. Current units will be displayed. Hold down button until “done” is displayed to cycle between FPS and MPS. Display will return to home screen after 20 seconds.TroubleshootingCheck Sensor SpacingUse a cleaning rod to check the spacing of sensor 1 and sensor 2 from bottom bullet edge Distances should be between 1/8” and 0.375” and they should be within 1/16” of each ot Common Issues•Lean inBayo damageReduced velocity accuracy•Lean outShot pickup errorReduced velocity accuracy•Thick muzzle/barrelLow signalReduced velocity accuracyShot pickup error•Muzzle too close to Sensor 1Signal gets noisyReduced velocity accuracyShot pickup error•V-block overlaps muzzleBayo/strapping damageMagnetospeed, LLC 9206 Rod Rd, Suite CAustin, Texas 78736(512) 284-8161********************* Made in USAPatent Pending4。

SoC Encounter设计流程ppt

1.Initial_design

MMMC:

生成并更新RC corner,指明每个RC corner对应的cap table file,供进 行RC参数提取时使用,并指明每个RC corner对应的MMMC view:

create_rc_corner -name rc_worst -cap_table \ ../../techfile/soce_captable/smic_logic065_7lm_max.captbl

2.Floorplan

Floorplan set:

Specify floorplan:

指明floorplan坐标原点,确定floorplan面积(包括die size and core size,反复调 整,直到满足要求)及标准单元排列方式等。 命令:specify floorplan;

Add IO cells and filler:

$DEF_CAP \ -detailed_clock_cap_factor $DET_CLK_CAP -xcap_factor $X_CAP

update_delay_corner -name normal_func1_max_dcw_view_dc -rc_corner rc_worst

09.03.2020

Design_import:

第一次设计时,需要详细填写上述文件,填写完成以后,可以保存(save)为.conf 文件,以备下次调用。设计中也可以调用(load)现成的配置文件(.conf)。如: 命令: loadConfig $conf_file 0

commitConfig

上述内容包括详细的工艺库信息和设计数据、约束信息等。

-clockGatingCheck true \

Pearson English门户快速入门指南说明书

Quick Start Guidefor Students Pearson English Portal Pearson JapanSystem requirementsFor Computers:●OS:Windows7+,Mac OS10.13+●Browsers:Chrome,Firefox,Edge,Safari(in thelatest version)●Processor:Intel Core™Duo2.0GHz or fasterprocessor●Screen resolution:minimum1366x768px●Memory:2GB or higher RAM●Adobe Flash Player:latest version(for IslandAdventure Game only)●Cookies:must be enabledFor Offline App(Pearson Practice English app):●iOS:10.0+&32MB●Android:5.0+&26.5MB For Tablets:●iPad iOS11.2+,Android OS5.0+orWindows8.1,10●Supported browsers(in latest versions):Chrome,Safari●IAG game is accessed using app available in StoreFor iPhones:●iOS11.2+●Safari in latest versionFor Android devices:●Android OS5.0+●Chrome in latestversionNote:Some types of activities(e.g.drag&drop)may not work correctly on mobile devices.The presentation tool and admin toolBefore you begin using the Pearson English Portal,please see the list of system requirements and take a moment to ensure you have the correct equipment:Click here to check your computer now.Click here to check your Internet browserspeed. 1Before the student begins a journey with the Pearson English Portal we recommend checking if their device meets the system requirements .To start using the Pearson English Portal a student needs:●an e-mail address and ●a student access code.The access code might come with your textbook,from your school,or in a separate kit.You can also contact your local Pearson Representative or distributor by visiting our website .Registering anaccount 2A B C DTo register an account:1.Go to:pearson /register2.Choose your preferred language [A] and click Create an account .If you encounter any issues,click on the Help [B]icon to access the help site.3.Select Create adult account [C]orCreate c hild account [D].Note:If you are a young learner,please ask your parent or a teacher to create an account for you.4. Enter your Email address, Username, Password, First name and Last name. Choose Japan in Country if you live in Japan.Read the Terms of Use and thePrivacy Policy and check the box[A]. If you wish to get information from Pearson, check the box[B].Click “Create account ”[C] andyou will be directed to your Dashboard.Note s :●Your lastname must be at least twoLatin characters long.If you register using differentwriting system,e.g.Chinese,one character/symbol isenough.●Your username can contain onlylowercase letters,numbers,dots [.],underscores [_],dashes [-]and atsigns [@].●Your password must have 8 or more characters, at least one uppercaseRegisteringan account,cont.2A B CTo sign in to the Pearson English Portal student account:1.Go to /login2.Enter student Username and Password .3.Click on the Sign in buttonNote:If you forget your password,click on theForgot your password?link or click here for instructions.Signingin323Students need to add a product to their account to be able to fully use the Pearson English Portal.To add a product to an account:1.On your Dashboard,click on either the Add New Product buttonor add a new product link [A].2.Enter your Access Code and click the Activate button.If you use a devicewith a camera,you will also see the option to add a product by scanningthe QR code[B].You may also return to the Dashboard[C].3.Click the Go to Productsbutton.4Adding aproductTo join a teacher’s class:1.Go to the Classes tab.2.Click on the Join Class buttonor join a class link [A].3.Enter the Class Code you shouldget from your teacher.4.Click on the Joinbutton.5Joining a classThe teacher is able to track students’progress and provide feedback on their work after they have joined the class.。

Encounter使用方法

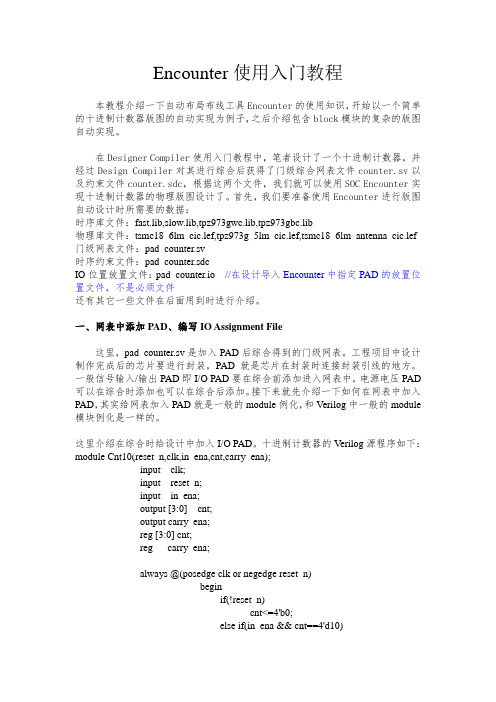

Encounter使用入门教程本教程介绍一下自动布局布线工具Encounter的使用知识,开始以一个简单的十进制计数器版图的自动实现为例子,之后介绍包含block模块的复杂的版图自动实现。

在Designer Compiler使用入门教程中,笔者设计了一个十进制计数器,并经过Design Compiler对其进行综合后获得了门级综合网表文件counter.sv以及约束文件counter.sdc,根据这两个文件,我们就可以使用SOC Encounter实现十进制计数器的物理版图设计了。

首先,我们要准备使用Encounter进行版图自动设计时所需要的数据:时序库文件:fast.lib,slow.lib,tpz973gwc.lib,tpz973gbc.lib物理库文件:tsmc18_6lm_cic.lef,tpz973g_5lm_cic.lef,tsmc18_6lm_antenna_cic.lef 门级网表文件:pad_counter.sv时序约束文件:pad_counter.sdcIO位置放置文件:pad_counter.io //在设计导入Encounter中指定PAD的放置位置文件,不是必须文件还有其它一些文件在后面用到时进行介绍。

一、网表中添加PAD、编写IO Assignment File这里,pad_counter.sv是加入PAD后综合得到的门级网表。

工程项目中设计制作完成后的芯片要进行封装,PAD就是芯片在封装时连接封装引线的地方。

一般信号输入/输出PAD即I/O PAD要在综合前添加进入网表中,电源电压PAD 可以在综合时添加也可以在综合后添加。

接下来就先介绍一下如何在网表中加入PAD,其实给网表加入PAD就是一般的module例化,和Verilog中一般的module 模块例化是一样的。

这里介绍在综合时给设计中加入I/O PAD。

十进制计数器的Verilog源程序如下:module Cnt10(reset_n,clk,in_ena,cnt,carry_ena);input clk;input reset_n;input in_ena;output [3:0] cnt;output carry_ena;reg [3:0] cnt;reg carry_ena;always @(posedge clk or negedge reset_n)beginif(!reset_n)cnt<=4'b0;else if(in_ena && cnt==4'd10)cnt<=4'b0;else if(in_ena && cnt<4'd10)cnt<=cnt+1'b1;endalways @(posedge clk or negedge reset_n)beginif(!reset_n)carry_ena<=1'b0;else if(in_ena && cnt==4'd10)carry_ena<=1'b1;elsecarry_ena<=1'b0;endendmodule加入PAD后的十进制计数器Verilog网表如下:module Cnt10_PAD(reset_n,clk,in_ena,cnt,carry_ena); //顶层模块input reset_n;input clk;input in_ena;output [3:0] cnt;output carry_ena;wire top_clk,top_reset,top_in_ena;wire top_carry_ena;wire [3:0] top_cnt;Cnt10CNT10(.reset_n(top_reset),.clk(top_clk),.in_ena(top_in_ena),.cnt(top_cnt),.carry_ena (top_carry_ena)); //这里是对Cnt10 module的例化//下面是I/O PAD module的例化PDIDGZ PAD_CLK(.PAD(clk),.C(top_clk));PDIDGZ PAD_RESET(.PAD(reset_n),.C(top_reset));PDIDGZ PAD_IN_ENA(.PAD(in_ena),.C(top_in_ena));PDO02CDG PAD_CARRY_ENA(.I(top_carry_ena),.PAD(carry_ena));PDO02CDG PAD_CNT_0(.I(top_cnt[0]),.PAD(cnt[0]));PDO02CDG PAD_CNT_1(.I(top_cnt[1]),.PAD(cnt[1]));PDO02CDG PAD_CNT_2(.I(top_cnt[2]),.PAD(cnt[2]));PDO02CDG PAD_CNT_3(.I(top_cnt[3]),.PAD(cnt[3]));endmodule说明:关于PAD如何例化,首先要查看厂家提供的工艺库中的关于PAD的verilog 文件,如本例子中使用tsmc18工艺库,描述PAD的verilog文件为tpz973g.v,这个文件是PAD文件的verilog描述,包括输入输出的端口等信息。

STARCCM基础培训教程

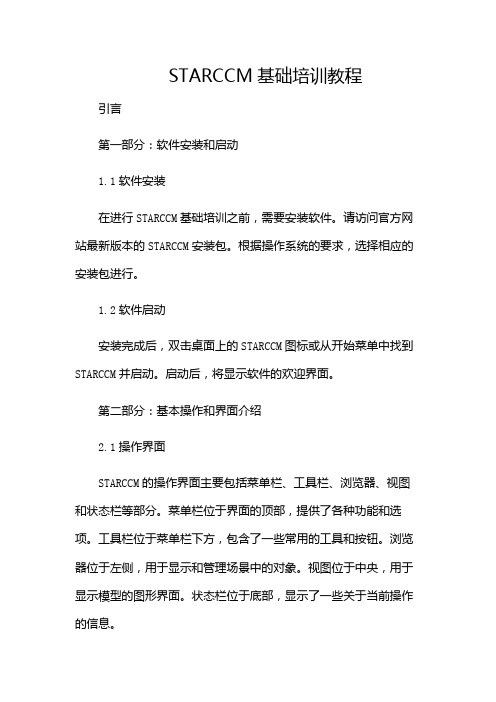

STARCCM基础培训教程引言第一部分:软件安装和启动1.1软件安装在进行STARCCM基础培训之前,需要安装软件。

请访问官方网站最新版本的STARCCM安装包。

根据操作系统的要求,选择相应的安装包进行。

1.2软件启动安装完成后,双击桌面上的STARCCM图标或从开始菜单中找到STARCCM并启动。

启动后,将显示软件的欢迎界面。

第二部分:基本操作和界面介绍2.1操作界面STARCCM的操作界面主要包括菜单栏、工具栏、浏览器、视图和状态栏等部分。

菜单栏位于界面的顶部,提供了各种功能和选项。

工具栏位于菜单栏下方,包含了一些常用的工具和按钮。

浏览器位于左侧,用于显示和管理场景中的对象。

视图位于中央,用于显示模型的图形界面。

状态栏位于底部,显示了一些关于当前操作的信息。

2.2基本操作在STARCCM中,基本操作包括创建模型、设置边界条件、划分网格、求解和后处理等。

下面将简要介绍这些操作的基本步骤。

2.2.1创建模型在菜单栏中选择“File”->“New”创建一个新的模型。

在弹出的对话框中,可以选择模型的类型和单位制。

然后,根据需要创建几何形状,可以使用内置的几何创建工具或导入外部CAD模型。

2.2.2设置边界条件创建模型后,需要设置边界条件。

在浏览器中,找到相应的边界条件选项,并进行设置。

例如,可以设置进口速度、出口压力、壁面粗糙度等。

2.2.3划分网格设置边界条件后,需要对模型进行网格划分。

在菜单栏中选择“Mesh”->“CreateMesh”进行网格划分。

在弹出的对话框中,可以选择网格类型和网格参数。

然后,“Generate”按钮网格。

2.2.4求解网格划分完成后,可以进行求解。

在菜单栏中选择“Simulation”->“Run”进行求解。

在弹出的对话框中,可以选择求解器类型和求解参数。

然后,“Start”按钮开始求解。

2.2.5后处理求解完成后,可以进行后处理。

在菜单栏中选择“Results”->“Post-processing”进行后处理。

Encounter快速入门教程

Encounter 能够与各种其他工具集成,如 Microsoft Office、Teams、 OneDrive 等。

encounter的特点和优势

优势

提高工作效率:通过 Encounter,团队成员可以更快速地协作、沟通和 完成任务。

减少沟通成本:Encounter 提供了直观、易于使用的沟通工具,可以降 低沟通成本。

网络架构

encounter采用去中心化的分布式网络架 构,由多个节点组成,节点之间通过P2P 协议进行通信。

VS

通信协议

encounter使用自定义的通信协议,以确 保节点之间的安全通信。通信协议包括消 息的格式、加密方式、认证机制等。

04

encounter实践案例分 享

使用encounter进行网络分析的案例

encounter与其他安全工具的对比和优势分析

对比

与其他安全工具相比,encounter具有高效、准确、易 用等优点,同时能够与其他安全工具进行集成和交互 ,形成更加完善的安全解决方案。

优势分析

encounter的优势在于其先进的技术和算法,能够快速 准确地检测和防御网络安全威胁,同时其良好的扩展 性和兼容性也能够满足不同用户的需求。

使用encounter进行安全事件处理的案例

要点一

总结词

要点二

详细描述

安全事件处理是encounter的重要应用之一,通过自动 化和智能化手段,可以帮助企业快速响应和处理安全 事件。

当encounter检测到安全事件时,会自动进行事件分析 、分类和优先级判断,并生成详细的报告和警报信息 。同时,encounter还支持自动化响应措施,如隔离网 络、阻止IP等,帮助企业快速处理安全事件,减少损失 。

Encounter使用入门教程

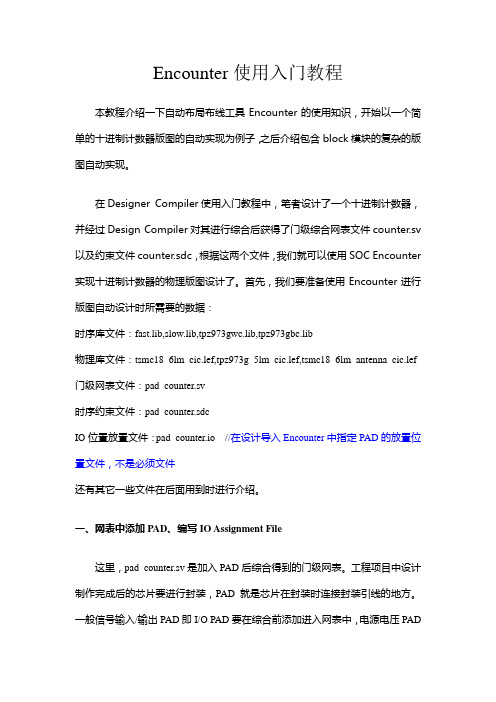

Encounter使用入门教程本教程介绍一下自动布局布线工具Encounter的使用知识,开始以一个简单的十进制计数器版图的自动实现为例子,之后介绍包含block模块的复杂的版图自动实现。

在Designer Compiler使用入门教程中,笔者设计了一个十进制计数器,并经过Design Compiler对其进行综合后获得了门级综合网表文件counter.sv 以及约束文件counter.sdc,根据这两个文件,我们就可以使用SOC Encounter 实现十进制计数器的物理版图设计了。

首先,我们要准备使用Encounter进行版图自动设计时所需要的数据:时序库文件:fast.lib,slow.lib,tpz973gwc.lib,tpz973gbc.lib物理库文件:tsmc18_6lm_cic.lef,tpz973g_5lm_cic.lef,tsmc18_6lm_antenna_cic.lef 门级网表文件:pad_counter.sv时序约束文件:pad_counter.sdcIO位置放置文件:pad_counter.io //在设计导入Encounter中指定PAD的放置位置文件,不是必须文件还有其它一些文件在后面用到时进行介绍。

一、网表中添加PAD、编写IO Assignment File这里,pad_counter.sv是加入PAD后综合得到的门级网表。

工程项目中设计制作完成后的芯片要进行封装,PAD就是芯片在封装时连接封装引线的地方。

一般信号输入/输出PAD即I/O PAD要在综合前添加进入网表中,电源电压PAD可以在综合时添加也可以在综合后添加。

接下来就先介绍一下如何在网表中加入PAD,其实给网表加入PAD就是一般的module例化,和Verilog中一般的module 模块例化是一样的。

这里介绍在综合时给设计中加入I/O PAD。

十进制计数器的Verilog源程序如下:module Cnt10(reset_n,clk,in_ena,cnt,carry_ena);input clk;input reset_n;input in_ena;output [3:0] cnt;output carry_ena;reg [3:0] cnt;reg carry_ena;always @(posedge clk or negedge reset_n)beginif(!reset_n)cnt<=4'b0;else if(in_ena && cnt==4'd10)cnt<=4'b0;else if(in_ena && cnt<4'd10)cnt<=cnt+1'b1;endalways @(posedge clk or negedge reset_n)beginif(!reset_n)carry_ena<=1'b0;else if(in_ena && cnt==4'd10)carry_ena<=1'b1;elsecarry_ena<=1'b0;endendmodule加入PAD后的十进制计数器Verilog网表如下:module Cnt10_PAD(reset_n,clk,in_ena,cnt,carry_ena); //顶层模块input reset_n;input clk;input in_ena;output [3:0] cnt;output carry_ena;wire top_clk,top_reset,top_in_ena;wire top_carry_ena;wire [3:0] top_cnt;Cnt10CNT10(.reset_n(top_reset),.clk(top_clk),.in_ena(top_in_ena),.cnt(top_cnt),.carry_ena (top_carry_ena)); //这里是对Cnt10 module的例化//下面是I/O PAD module的例化PDIDGZ PAD_CLK(.PAD(clk),.C(top_clk));PDIDGZ PAD_RESET(.PAD(reset_n),.C(top_reset));PDIDGZ PAD_IN_ENA(.PAD(in_ena),.C(top_in_ena));PDO02CDG PAD_CARRY_ENA(.I(top_carry_ena),.PAD(carry_ena));PDO02CDG PAD_CNT_0(.I(top_cnt[0]),.PAD(cnt[0]));PDO02CDG PAD_CNT_1(.I(top_cnt[1]),.PAD(cnt[1]));PDO02CDG PAD_CNT_2(.I(top_cnt[2]),.PAD(cnt[2]));PDO02CDG PAD_CNT_3(.I(top_cnt[3]),.PAD(cnt[3]));endmodule说明:关于PAD如何例化,首先要查看厂家提供的工艺库中的关于PAD的verilog 文件,如本例子中使用tsmc18工艺库,描述PAD的verilog文件为tpz973g.v,这个文件是PAD文件的verilog描述,包括输入输出的端口等信息。

Encounter

1.import设计之后需要 对综合后的网表、约束文件 进行check, 使用checkDesign –all

Floorplan

在工具菜单中FloorPlan specify Floorplan 弹出如图右边的界面。 如果要定义一个IP的面积选择 Die Size by: Width 500 (定义IP的宽度) Height 500 (定义IP的高度)

Import design

1. Yield 这项主要是 用在65ns 工艺及以下,主要用来提高芯片的良率的一些约束文件. 2. Timing主要用来做partition 3.MMMC主要是低功耗设计设计的约束文件.. 把所有的输入文件加载后,点击OK

Import design

Placement

Cell padding的功能告诉工具 在placement cell时,需要在 Reg 、latch 的单元附近 预先留指定buffer单元的定 倍数个单元的空间,目的是 在做时钟树时,需要大量buf或者 是inv单元,而这些单元则能 尽可能近的接近这时序单元, 减少时钟net的长度。

Powerplan

在调整好Floorplan之后,下一个阶段是规划IP模块的电源、地线的规划, 如果工艺选的是4层metal布线,最好选择metal3 和metal4做VDD VSS的stripes, Stripes的间隔值的大小与芯片消耗的峰值有关,如果峰值比较大,那么stripes尽ห้องสมุดไป่ตู้的做得 比较密些,间距少一些。反之则stripes要做稀疏些,间距大一些。那么怎样估算总的VDD VSS stripes 的宽度值 假如IP的做powerAnalysis得出的峰值180 mw,根据厂家给的PCM参数,metal1的电迁 移值为1um/1ma,那么总的 Stipes’s width=180mw/1.8v * 1ma=180um 如果IP做成2000X2000平方微米,如果做成水平和垂直方向的电源网格 建议做成水平的stripes 的width 为9um 做十条,space 200um. 建议做成垂直的stripes 的width 为9um 做十条, space 200um. 这样做能保证电流比较均匀的分布到芯片每一个区域,减少IRdrop.

快速入门指南 ELE-L09 ELE-L29 ELE-L04说明书

Quick Start Guide ELE-L09ELE-L29Know Your DeviceBefore using the device, familiarize yourself with its basic operations.To power on your device, press and hold the power button until the screen turns on.To power off your device, press and hold the power button, and then touch .To restart your device, press and hold the power button, and then touch .Press and hold the power button for 10 or more seconds to forcibly restart your device.objects while using the NFC function.Check out the pre-installed Tips app and master all thegreat features on your device.Getting StartedDo not insert or remove the SIM card when your device is powered on.Ensure that the card is correctly aligned and that the card tray is level when you insert it into your device.Be careful not to scratch your device or hurt yourselfwhen using the eject pin.Store the eject pin out of the reach of children to prevent accidental swallowing or injury.Do not use cut or modified SIM or NM cards (nanomemory cards) with your device as these may not be recognized and could damage the card tray (slot).If your SIM card does not match your device, pleasecontact your carrier.Follow the instructions in the following figures to set up your device. Please use the eject pin included.Single-SIM:3nano-SIM 1NM Card21Dual-SIM:321nano-SIM 1nano-SIM 2NM Cardnano-SIM 1Dual SIM Card Management (dual-SIM devices only)Your device supports dual card dual standby. Under Settings > Wireless & networks > Dual SIM settings, select the default mobile data card and calling card as needed.Dual 4GIf both of your SIM cards support 4G services, when one of them is active on a 4G voice call, you will be prompted to handle any new call to the other SIM card. Answering the new call will automatically end the active call.The default mobile data SIM card can still be used for Internet surfing on a 4G network when the other card is on a 4G voice call.Some of the aforementioned features may beunavailable in certain areas due to networkinterference.4G voice services require the support of your carrier'snetwork and the deployment of relevant services.Contact your carrier to activate 4G services.If this guide is inconsistent with the description on theofficial website, the latter prevails.For More InformationIf you encounter any problems while using your device, you can obtain help from the following resources:Visit /en to view device information, frequently asked questions and other information.Visit /en/support for the most up-to-date contact information for your country or region. Go to Settings and touch System > About phone > Legal to view legal information for your product.Go to Settings and touch System > About phone > Legal > Safety information to view safety information for your product.Go to Settings and touch System > About phone > Authentication info to view regulatory information for your product.Go to Settings and touch System > Certification logos to view more information on certification logos for your product.All pictures and illustrations in this guide, including butnot limited to the device color, size, and display content,are for your reference only. The actual device may vary.Nothing in this guide constitutes a warranty of any kind,express or implied.Safety InformationPlease read all of the safety information carefully before using your device to ensure its safe and proper operation and to learn how to dispose of your device properly.Operation and safetyTo prevent possible hearing damage, do not listen at high volume levels for long periods.Using an unapproved or incompatible power adapter, charger, or battery may damage your device, shorten its lifespan, or cause a fire, explosion, or other hazards.Ideal operating temperatures are 0 °C to 35 °C. Ideal storage temperatures are -20 °C to +45 °C.Pacemaker manufacturers recommend that a minimum distance of 15 cm be maintained between a device and a pacemaker to prevent potential interference with the pacemaker. If using a pacemaker, hold the device on the side opposite the pacemaker and do not carry the device in your front pocket.Keep the device and the battery away from excessive heat and direct sunlight. Do not place them on or in heating devices, such as microwave ovens, stoves, or radiators.Observe local laws and regulations while using the device. To reduce the risk of accidents, do not use your wireless device while driving.While flying in an aircraft or immediately before boarding, only use your device according to instructions provided. Use of a wireless device in an aircraft may disrupt wireless networks, present a hazard to aircraft operation, or be illegal.To prevent damage to your device's parts or internal circuits, do not use it in dusty, smoky, damp, or dirty environments or near magnetic fields.When charging the device, make sure the power adapter is plugged into a socket near the devices and is easily accessible.Unplug the charger from electrical outlets and the device when not in use.Do not use, store or transport the device where flammables or explosives are stored (in a gas station, oil depot, orchemical plant, for example). Using your device in these environments increases the risk of explosion or fire.Dispose of this device, the battery, and accessories according to local regulations. They should not be disposed of in normal household waste. Improper battery use may lead to fire, explosion, or other hazards.This device contains a built-in battery. Do not attempt to replace the battery by yourself. Otherwise, the device may not run properly or it may damage the battery. For your personal safety and to ensure that your device runs properly, you are strongly advised to contact a Huawei authorized service center for a replacement.Disposal and recycling informationThe crossed-out wheeled-bin symbol on your product, battery, literature or packaging reminds you that all electronic products and batteries must be taken to separate waste collection points at the end of their working lives; they must not be disposed of in the normal waste stream with household garbage. It is the responsibility of the user to dispose of the equipment using a designated collection point or service for separate recycling of waste electrical and electronic equipment (WEEE) and batteries according to local laws.Proper collection and recycling of your equipment helps ensure electrical and electronic equipment (EEE) waste is recycled in a manner that conserves valuable materials and protects human health and the environment, improper handling, accidental breakage, damage, and/or improper recycling at the end of its life may be harmful for health and environment. For more information about where and how to drop off your EEE waste, please contact your local authorities, retailer or household waste disposal service or visit the website http:// /en/.Reduction of hazardous substancesThis device and its electrical accessories are compliant with local applicable rules on the restriction of the use of certain hazardous substances in electrical and electronic equipment, such as EU REACH, RoHS and Batteries (where included) regulations. For declarations of conformity about REACH andRoHS, please visit our web site / certification.EU regulatory conformance (only applies to ELE-L09 / ELE-L29)Body worn operationThe device complies with RF specifications when used near your ear or at a distance of 0.50 cm from your body. Ensure that the device accessories, such as a device case and device holster, are not composed of metal components. Keep the device away from your body to meet the distance requirement. The highest SAR value reported for this device type when tested at the ear isELE-L090.33 W/kgELE-L290.33 W/kgAnd when properly worn on the body isELE-L090.85 W/kgELE-L290.85 W/kgStatementHereby, Huawei Technologies Co., Ltd. declares that this device ELE-L09 / ELE-L29 is in compliance with the essential requirements and other relevant provisions of Directive2014/53/EU.The most recent and valid version of the DoC (Declaration of Conformity) can be viewed at / certification.This device may be operated in all member states of the EU. Observe national and local regulations where the device is used.This device may be restricted for use, depending on the local network.Restrictions in the 2.4 GHz band:Norway: This subsection does not apply for the geographical area within a radius of 20 km from the centre of Ny-Ålesund. Restrictions in the 5 GHz band:According to Article 10 (10) of Directive 2014/53/EU, the packaging shows that this radio equipment will be subject to some restrictions when placed on the market in Belgium (BE), Bulgaria (BG), the Czech Republic (CZ), Denmark (DK), Germany (DE), Estonia (EE), Ireland (IE), Greece (EL), Spain (ES), France (FR), Croatia (HR), Italy (IT), Cyprus (CY), Latvia (LV), Lithuania (LT), Luxembourg (LU), Hungary (HU), Malta (MT), Netherlands (NL), Austria (AT), Poland (PL), Portugal (PT),Romania (RO), Slovenia (SI), Slovakia (SK), Finland (FI), Sweden (SE), the United Kingdom (UK), Turkey (TR), Norway (NO), Switzerland (CH), Iceland (IS), and Liechtenstein (LI).The WLAN function for this device is restricted to indoor use only when operating in the 5150 to 5350 MHz frequency range.Frequency Bands and Power(a) Frequency bands in which the radio equipment operates: Some bands may not be available in all countries or all areas. Please contact the local carrier for more details.(b) Maximum radio-frequency power transmitted in the frequency bands in which the radio equipment operates: The maximum power for all bands is less than the highest limit value specified in the related Harmonized Standard.The frequency bands and transmitting power (radiated and/or conducted) nominal limits applicable to this radio equipment are as follows:ELE-L09GSM900: 35 dBm, GSM1800: 32 dBm,WCDMA900/ 2100: 25.7 dBm, LTE Band1/3/7/8/20/28/34/38/40: 25.7 dBm, Wi-Fi 2.4G:20 dBm, Bluetooth: 20 dBm, Wi-Fi 5G:5150-5250 MHz: 23 dBm, 5250-5350 MHz: 20dBm,5470-5725 MHz: 20 dBm, 5725-5850MHz: 13 dBm, NFC: 42 dBuA/m at 10mELE-L29GSM900: 35 dBm, GSM1800: 32 dBm,WCDMA900/ 2100: 25.7 dBm, LTE Band1/3/7/8/20/28/34/38/40: 25.7 dBm, Wi-Fi 2.4G:20 dBm, Bluetooth: 20 dBm, Wi-Fi 5G:5150-5250 MHz: 23 dBm, 5250-5350 MHz: 20dBm,5470-5725 MHz: 20 dBm, 5725-5850MHz: 13 dBm, NFC: 42 dBuA/m at 10m Accessories and Software InformationSome accessories are optional in certain countries or regions. Optional accessories can be purchased from a licensed vendor as required. The following accessories are recommended: Adapters: HW-050450X00,HW-050450X01 (X represents the different plug types used, which can be either C, U, J, E, B, A, I, R, Z or K, depending on your region)Batteries: HB436380ECWEarphones: MEMD1632B580C00, 1311-3291-3.5mm-229, EMC309-001The product software version is ELE-L09: 5.0.1.78(C432E78R1P6log) / ELE-L29: 5.0.1.78 (C432E78R1P6log). Software updates will be released by the manufacturer to fixbugs or enhance functions after the product has been released. All software versions released by the manufacturer have been verified and are still compliant with the related rules.All RF parameters (for example, frequency range and output power) are not accessible to the user, and cannot be changed by the user.For the most recent information about accessories and software, please see the DoC (Declaration of Conformity) at /certification.FCC Regulatory ComplianceBody worn operationThe device complies with RF specifications when used near your ear or at a distance of 1.50 cm from your body. Ensure that the device accessories, such as a device case and device holster, are not composed of metal components. Keep the device away from your body to meet the distance requirement. Certification information (SAR)This device is also designed to meet the requirements for exposure to radio waves established by the Federal Communications Commission (USA).The SAR limit adopted by the USA is 1.6 W/kg averaged over one gram of tissue. The highest SAR value reported to the FCC for this device type complies with this limit.The highest SAR value reported to the FCC for this device type when using it at the ear isELE-L090.53 W/kgELE-L290.53 W/kgELE-L040.53 W/kgAnd when properly worn on the body isELE-L090.54 W/kgELE-L290.54 W/kgELE-L040.56 W/kgAnd when using the Wi-Fi hotspot function isELE-L090.68 W/kgELE-L290.68 W/kgELE-L040.68 W/kgFCC statementThis equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonableprotection against harmful interference in a residential installation. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:--Reorient or relocate the receiving antenna.--Increase the separation between the equipment and receiver. --Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.--Consult the dealer or an experienced radio/TV technician for help.This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions: (1) this device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation.Caution: Any changes or modifications to this device not expressly approved by Huawei Technologies Co., Ltd. for compliance could void the user's authority to operate the equipment.Industry Canada compliance (only applies to ELE-L04)Body worn operationThe device complies with RF specifications when used near your ear or at a distance of 1.50 cm from your body. Ensure that the device accessories, such as a device case and device holster, are not composed of metal components. Keep the device away from your body to meet the distance requirement. The highest SAR value reported to the IC for this device type when using it at the ear isELE-L040.53 W/kgAnd when properly worn on the body isELE-L040.56 W/kgIC StatementThis device complies with CAN ICES-3 (B)/NMB-3(B).This device complies with Industry Canada licence-exempt RSS standard(s). Operation is subject to the following two conditions: (1) this device may not cause interference, and (2) this device must accept any interference, including interference that may cause undesired operation of the device. Restrictions in the 5 GHz band:Within the 5.15 to 5.25 GHz band, UNII devices will be restricted to indoor operations to reduce any potential for harmful interference to co-channel Mobile Satellite System (MSS) operations.Legal NoticeTrademarks and Permissions, , and are trademarks or registered trademarks of Huawei Technologies Co., Ltd. Manufactured under license from Dolby Laboratories. Dolby, Dolby Atmos, and the double-D symbol are trademarks of Dolby Laboratories.Android™ is a trademark of Google Inc.LTE is a trademark of ETSI.The Bluetooth® word mark and logos are registered trademarks owned by Bluetooth SIG, Inc. and any use of such marks by Huawei Technologies Co., Ltd. is under license.Wi-Fi®, the Wi-Fi CERTIFIED logo, and the Wi-Fi logo arePrivacy PolicyTo better understand how we protect your personal information, please see the privacy policy at http:// /privacy-policy.Copyright © Huawei Technologies Co., Ltd. 2019. All rights reserved.THIS DOCUMENT IS FOR INFORMATION PURPOSE ONLY, AND DOES NOT CONSTITUTE ANY KIND OF WARRANTIES.。

MOVE! 教练应用程序安卓快速入门指南说明书

MOVE!® Coach App Android Quick Start GuideOverviewMOVE!® Coach is a 19-week Department of Veterans Affairs (VA) weight management mobile application (app) for Veterans. It combines self-management tools and information from VA’s MOVE! Weight Management Program with guidance from the VA MOVE! team.The app was designed with Veterans in mind and addresses Veterans’ most common weight-loss challenges, but the educational resources and tracking features available on the app can be used by anyone. Veterans can use the app independently, or if they are receiving health care from VA, they can partner with their clinicians during MOVE! program participation.Setting Up and Logging Into Your AppBefore you can use the MOVE! Coach App, you must “accept” the End User License Agreement (EULA). The app then will take you to a screen where you will complete basic information about yourself (age, gender, etc.). Once you save your basic information, you will be able to begin using the app. All the information you enter will be safely stored on your device and will not be shared.Information Included in the MOVE! Coach AppThe MOVE! Coach App provides:•Self-Management Guides – Focus areas for all 19 weeks of MOVE!•Diary Entries – Daily tracking of weight, diet and physical activity.•My Goals & Progress – Resources for self-monitoring, setting goals, graphing change, calculating your health statistics and reviewing progress summaries and reports.•How To Solve Problems – Tips and ideas for coping with challenging situations.In addition, you can share your progress on social media or with friends and supporters.Using the Self-Management GuidesEach self-management guide includes the following sections:•Objectives – Goals for how each guide can help you manage your weight.•Coursework – Activities to help you achieve each week’s goals.•Chapters – Topics covered in each guide.•Summary – Puts everything you have learned together.•Get Ready for the Next Guide – A questionnaire to prepare you for the next guide.•Related Handouts – Links to supplemental materials that support your week’s focus.To access the guides, tap Self-Management Guides from the MOVE! Coach home screen.If this is your fist time accessing this feature, you will see a blinking icon (blue key in a yellow circle). Tap the icon to proceed. Youwill be presented with four screens of important introductory information about the app and the use of self-management guides.(NOTE: in the future, if you would like to re-read the four intro pages, access is under the options menu (three- vertical stacked dots)on the upper right area of the self-management guide main screen). After tapping Done at the end of those four pages, you will be taken to the list of 11 self-management guide topics. Guide 1 “Getting Started” will be open for you to begin (shown by > symbol).All other guides (2-11) will be locked as indicated by the lock icon after the guide title. You should complete the previous guide inorder to unlock the next guide. Guides 2 and 3 will unlock a week after completing the previous guide and guides 4 thru 11 willunlock two weeks after completing the previous guide. Once you have completed all sections of a guide, a check-mark will appearafter the guide title. All check-marks must be present in order to open the next guide. You will always be able to go back to any self-management guide you have completed.MOVE! recommends completing the guides in order and over the allotted time (e.g., Guide 1 over one week, Guide 4 over two weeks).This time is needed for you to learn weight-management concepts, use the Weight, Physical Activity, and Diet Diaries, and buildweight management skills in a progressive fashion. However, if you wish to unlock a guide sooner, you can ‘tap and hold’ or ‘longpress’ on the guide to unlock it. NOTE: Unlocking a guide early will also turn off ‘Guide Notifications.’ To turn notifications back on, tapthe options menu (three-vertical stacked dots in the upper right corner), tap Settings, and tap the circle next to Guide Notifications.Making Diary EntriesWith the MOVE! Coach App, you can enter your weight and information about what you eat and how you exercise. Making regular entries is important because the app relies on the data you enter to graph results and run reports. To use the app most effectively – and achieve the best results with your MOVE! Weight Management Program – make sure you add entries routinely. To create an entry, tap the + icon that appears on most MOVE! Coach screens, and enter information about your weight, diet, activity, steps and water intake. For more detailed diary entry information see the Diary Entries section of the MOVE! Coach App for Android User Manual.My Goals & ProgressSetting goals, recording your behavior and tracking your outcomes will increase your chances of weight-loss success. To access tools for setting goals and tracking progress, tap My Goals & Progress from the MOVE! Coach home screen, and then tap the tool you would like to use.The app includes six categories of tools: My Diaries, My Goals, Graphs, Calculation Tools, My Summaries and My Reports. To return to the My Goals & Progress screen, tap the back arrow ç in the upper left corner.Graphing Your ProgressYou can see your progress by graphing the information you entered in the app. Although you can find basic graphs on the MOVE! Coach home screen, more details and graphing options are available in the Goals & Progress section.Tap My Goals & Progress, then under the Graphs section, tap on one of the types of graphs listed: Weight Graph, Physical Activity Graph or Diet Graph. To change the date range when on the graph screen, tap the options menu (three-vertical stacked dots in the upper right corner). Tap Graph, and adjust the date by tapping the circle next to the desired time period or by entering a date range. Tap Graph to view the updated graph.How to Solve ProblemsCertain days, specific circumstances or phases of MOVE! can be challenging. Avoid setbacks, stay motivated and keep making progress by using resources that can help you overcome obstacles.To access these resources, tap How To Solve Problems from the MOVE! Coach home screen, and then tap one of the 10 available categories. Most of these categories explain how the topic affects your health and include a list of helpful handouts and resources. Tap on the name of a resource you would like to view to access a document with more information.。

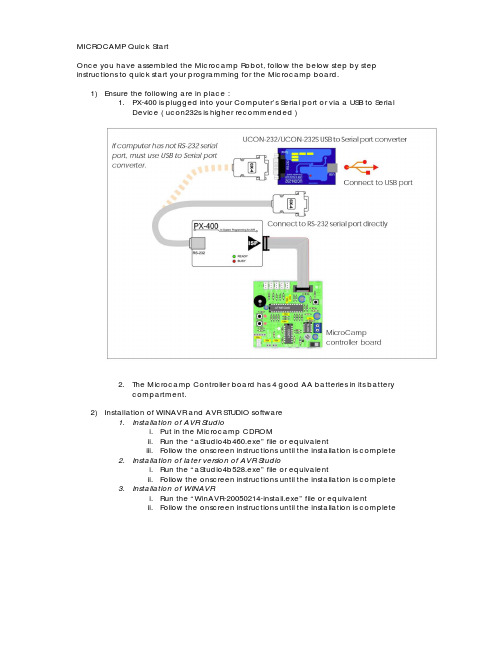

Microcamp快速入门指南说明书

MICROCAMP Quick StartOnce you have assembled the Microcamp Robot, follow the below step by step instructions to quick start your programming for the Microcamp board.1)Ensure the following are in place :1.PX-400 is plugged into your Computer’s Serial port or via a USB to SerialDevice ( ucon232s is higher recommended )2.The Microcamp Controller board has 4 good AA batteries in its batterycompartment.2)Installation of WINAVR and AVR STUDIO software1.Installation of AVR Studioi.Put in the Microcamp CDROMii.Run the “aStudio4b460.exe” file or equivalentiii.Follow the onscreen instructions until the installation is complete2.Installation of later version of AVR Studioi.Run the “aStudio4b528.exe” file or equivalentii.Follow the onscreen instructions until the installation is complete3.Installation of WINAVRi.Run the “WinAVR-20050214-install.exe” file or equivalentii.Follow the onscreen instructions until the installation is complete3)COPY all required library files1.Copy the whole “MicroCamp_include” folder located in the CDROM intothe C:\WinAVR-20070525 directory or the directory that WINAVR wasinstalled into.4)Starting AVR Studio1.Double click on the “AVR Studio 4” program icon.2.After the AVR Studio software starts, you will see this window3.Click on the “New Project” Button4.Choose AVR GCC and type in the project name as “testcode”5.Click on the “…” to chose your project folder6.Click on the “Create New Folder” icon to create a new folder.7.Type in “testproject” as the folder8.Double Click on it9.Click on the Select button10.Click on the “Finish” Button11.Click on “Project” tab, followed by the “Configuration Options”12.Choose the Device as “atmega8”13.Put “16000000” in the hz box14.Choose the “Include Directories” ICON15.Click on the “New (Insert)” button16.Choose the following 2 directories :17.Choose the “Include Directories” ICON18.Select the “libm.a” file on the left “Available Link Objects”19.Click on the “Add Library” button20.“libm.a” will then be added into the “Link with These Objects”21.Click on the “OK” button.5)Entering your Program Code:1.2.Press the “F7” key to compile.3.You should see something like “Build Succeeded with 3 warning ….”4.It is ok to have some warning after your build but if you encounter anyerrors, you will need to recheck your code or if all your include directoriesare correct.6)Programming your Microcontroller Board1.Make sure that your Microcamp Controller board is plugged into the PX-400 and the PX-400 to your computer.2.Turn on the Microcamp controller board.3.Click on the “Tools” and then AVR Prog tab4.Click on the Browse button and select the HEX file, which is the compiledfile from your project folder’s default directory.5.Choose ATmega8 under the Device Selectionstly Click on the “Program” button under the Flash section.7. A Progress bar will show the downloading of the code to the MicrocampController Board.8.Run the Microcamp board to confirm that the code is successfullydownloaded.。

Encounter使用入门教程

Encounter使用入门教程本教程介绍一下自动布局布线工具Encounter的使用知识,开始以一个简单的十进制计数器版图的自动实现为例子,之后介绍包含block模块的复杂的版图自动实现。

在Designer Compiler使用入门教程中,笔者设计了一个十进制计数器,并经过Design Compiler对其进行综合后获得了门级综合网表文件以及约束文件,根据这两个文件,我们就可以使用SOC Encounter实现十进制计数器的物理版图设计了。

首先,我们要准备使用Encounter进行版图自动设计时所需要的数据:时序库文件:,,,物理库文件:,,门级网表文件:时序约束文件:IO位置放置文件:eset_n(top_reset),.clk(top_clk),.in_ena(top_in_ena),t(top_cnt),.carry _ena(top_carry_ena)); AD(clk),.C(top_clk));PDIDGZ PAD_RESET(.PAD(reset_n),.C(top_reset));PDIDGZ PAD_IN_ENA(.PAD(in_ena),.C(top_in_ena));(PDO02CDG PAD_CARRY_ENA(.I(top_carry_ena),.PAD(carry_ena));PDO02CDG PAD_CNT_0(.I(top_cnt[0]),.PAD(cnt[0]));PDO02CDG PAD_CNT_1(.I(top_cnt[1]),.PAD(cnt[1]));PDO02CDG PAD_CNT_2(.I(top_cnt[2]),.PAD(cnt[2]));PDO02CDG PAD_CNT_3(.I(top_cnt[3]),.PAD(cnt[3]));endmodule说明:关于PAD如何例化,首先要查看厂家提供的工艺库中的关于PAD的verilog 文件,如本例子中使用tsmc18工艺库,描述PAD的verilog文件为973g,这个文件是PAD文件的verilog描述,包括输入输出的端口等信息。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Add Filler 也可以在Place完成

之后添加

9. 导出数据

选择输出的数据类型 填写输出数据的名称 Layer map 文件,对应到 PDK的layer层次

输出数据的库名称

数据Top cell name

Map File 范例:

## layer name A1 A1 A1 A1 A1 A1 NAME W2 T2 T2 T2 T2 T2 T2 NAME DIEAREA layer 属性 NET SPNET PIN FILL VIA VIAFILL A1/PIN ALL NET SPNET PIN FILL VIA VIAFILL T2/PIN ALL stream layer number 7 7 7 7 7 7 7 8 84 84 84 84 84 84 9 230 data type number 0 0 0 0 0 0 253 0 0 0 0 0 0 0 253 0

2. 启动Encounter

工作目录管理: 假设项目名称为project, 在project下新建lib、work文件夹 xxx/project/lib (存放各种库文件) xxx/project/work (工作数据区) 在work下打开打开终端: 输入encounter 不能加“&” , 回车

5. Floorplan规划

设置Die的面积、长宽、利用率等 建立一个初始化的Floorplan

5.1 Specify Floorplan:Basic

Size:指定大小 Die/IO/Core Coordinates: 通过Die/IO/Core Coordinate来指 定大小。 有两种方式来设定die的大小: ◆ Core size by Aspect Ratio ◆ Core Size by Width and Height Core Margins也是有两种方式 ◆ Core to Die Boundary ◆ Core to IO Boundary Core边界一般都是需要的,用来 放置Power Ring,与其他模块的 隔离区

Special Route

选择需要布线的节点 和端口

选择布线层次

最后确认

8.3 勾选 Global Route Detail Route

设置CPU核心数, 增加布线速度

布线结果

在终端下可看到布线的结果, 如果有违反,需重复 Place—Route 过程,直到 violation为零,如果错误较 少,也可以手工修改, 打开: Tools—Violation Browser 查看详细情况。

By:jfchen

1. 数据准备

必要数据:

A. 综合后Verilog网表,通常以.v结尾; B. 标准单元LEF库文件; 可选数据: A. IO/Pin位置配置文件; B. MMMC等。。。

Encounter标准流程

极简流程

Design Import Create Floorplan Power Plan Place Route END

1 选择要设置 的Pin 2. 设定放置边界,层次

3. 设置起始位置、间距

6.2 导出IO配置文件

File—Save—I/O File 保存为.io文件,方便下次导入使用,或 者添加在Import Design中IO设置中

Note: Encounter的每一步操作都可以保存到 一个记录文件中,如果要恢复只需load 这个文件就可以: File—Load File—Save 所以每一个关键操作后都要单独保存, 如Specify Floorplan、Power Plan、 Place、Route等

3. 菜单简介

File :各种数据文件保存、导入 Edit :各种数据属性编辑修改 Floorplan:布局设置 Power:配置电源/地 Place:放置标准单元 Route:布线器 Option:配置Encounter各项属性

4.Import Design

File – Import Design

5.2 Specify—Floorplan:Advanced

设置标准单元阵列排布方式 A. 选择Site; B. 改变Rows设置 C. 改变Rows spacing D. 改变Row height E. 改变底部IO的排列方向

6. 设置IO的位置

启动Pin Editor:Edit—Pin Editor

Include Pre-Place Optimization:放置前优化netlist Include In-Place Optimization: 在放置优化Timing constraints

Place之后(无 Stripe和Top/Bottom Ring)

8.2 Route

Special Route: 连接Cell、block、Pad的电源和地到全局电源地。 Trial Route: 快速的布线,提取参数用于时序分析; 用于分析布线阻塞情况; 不完全布线,DRC&LVS不一定会通过; NanoRoute: 精细完整的布线 Mixed Signal: 基于图形的布线器 适用于小型的定制block;

8.4 添加Filler

在Rows的空白处添加Nwell/Ntap、Ptap,保证Rows的 DRC&LVS通过。Filler一般为纵向布线Pitch的整数倍 Place—Add Phycical Cell—Add Filler

选择Filler cell

如果有DRC Violation导致不能添 加,需把Mode选项里面的 Perform DRC Violation Checking 去掉

添加verilog网表文件 和Top cell name

添加标准单元LEF库 添加IO配置文件, 可选项

强大的帮助文档,一 切不懂都可以从help 中找到答案

File – Import Design

Advanced页: 选择Power项,添加 Power Nets: Ground Nets:

保存设置: Save可将本次的设置 保存到一个文件中, 下次再Load的这个文 件即可。

7. 配置电源、地

Power 菜单

添加外围供电环路 添加StdCell Rows的 供电线路

7.1 Add Ring:Basic

添加电源/地的节点名称 设置Ring的类型

设置纵向、横向的layer、width、 spacing等

7.2 Add Ring:Advanced

选择Die的哪一边需要添加Ring

最后OK确认

7.3 Add Stripe:

添加电源/地节点名称,配置线 宽、间距以及层次使用 设置每一组Stripe的pitch

设置Stripe的起始和结束位置

最后OK确认

完成后

Ring

Stripe

8. Place & Route

8.1 放置标准单元

Place—Place Standard Cell Run Full Placement:放置全部 Run Incremental Placement:放置增加的 设置CPU个数 以增加place的 速度