pld应用程序举例

PLD应用1-1

PLD应用1-1简介PLD〔Programmable Logic Device〕可编程逻辑器件是一种广泛应用于电子电路设计的器件。

它允许设计人员通过编程来实现各种逻辑功能,而无需进行物理连接和布线。

本文将介绍PLD的根本概念、工作原理以及它在电子电路设计中的应用。

PLD的根本概念PLD是一种以逻辑门为根底的可编程器件。

它由可编程逻辑阵列〔PLA〕和输入输出〔IO〕模块组成。

可编程逻辑阵列中包含了大量的与门、或门和非门等逻辑门,它们的连接方式可以通过编程进行定制,从而实现各种逻辑功能。

输入输出模块用于与外部电路进行连接,使得PLD能够接收输入信号并输出处理后的信号。

PLD的工作原理PLD的工作原理可以简单的描述为以下几个步骤:1.确定逻辑功能:首先,设计人员需要确定所需的逻辑功能,例如实现一个加法器或一个多功能计数器等。

2.编程:接下来,设计人员通过编程将逻辑功能描述转化为PLD可以理解的形式。

这通常是通过一种硬件描述语言〔HDL〕来完成的,例如VHDL或Verilog。

3.下载:编程完成后,设计人员将程序下载到PLD中。

下载过程通常通过调试工具或专用的下载器进行。

4.验证:一旦程序下载成功,PLD即可开始执行所需的逻辑功能。

设计人员可以通过输入信号来验证PLD的工作是否符合预期,并对必要的调整进行修改。

PLD的应用PLD在电子电路设计中有着广泛的应用。

下面将列举几个常见的应用场景:逻辑电路设计PLD可以用于设计各种逻辑电路,例如加法器、乘法器、多功能计数器等。

通过编程,设计人员可以灵巧地调整逻辑功能,根据需求进行定制。

工业自动化PLD可以用于工业自动化系统中的逻辑控制。

例如,设计一个用于控制机器人操作的逻辑控制器,可以通过编程PLD来实现各种自动化操作,提高生产效率和质量。

数字信号处理PLD可用于实现数字信号处理算法,如滤波、FFT等。

通过编程PLD,设计人员可以将算法转化为硬件逻辑,从而加速数字信号处理的速度和效率。

pid实际应用

pid实际应用PID(Proportional-Integral-Derivative,比例积分微分)控制器是一种经典的自动控制系统,也是目前工业控制中应用最广泛的一种控制器。

它通过不断地测量被控对象的实际输出值与期望输出值的差距,并依照一定的比例、积分、微分系数计算出控制信号,对被控对象进行调节,最终使其输出达到期望值并保持稳定。

PID控制器的实际应用非常广泛,涵盖了各个领域的自动控制系统。

下面就以几个实际的例子来说明PID控制器的应用。

1. 温度控制系统温度控制系统是PID控制器的经典应用。

制造业中的许多工艺都需要对温度进行控制,例如冶金、化工、生物制药、食品加工等行业。

PID 控制器可以根据传感器提供的温度数值计算出控制信号,通过调节加热器或制冷器的功率,实现对温度的精确控制。

2. 电机转速控制电机的转速直接影响着机械设备的性能和工作效率,因此需要对电机转速进行准确控制。

PID控制器可以通过对电机转速的反馈信号不断调整电机的输出功率,使得电机转速稳定在期望值或者在受到扰动时能够快速恢复到期望转速。

3. 液位控制系统液位控制系统在化工、石油、食品饮料等行业中应用较为广泛。

PID 控制器可以通过对液位的反馈信号进行测量和处理,精确地调节阀门开度和出口流量,从而实现液位的准确控制。

4. 飞行控制在无人机、飞机、火箭等航空器的飞行控制中,PID控制器是必不可少的关键组件之一。

通过对陀螺仪、加速度计等测量装置的反馈信号不断计算控制信号,实现对飞行器姿态、高度、速度等方面的精确控制。

总之,PID控制器是自动控制领域中非常重要的一种控制器,其实际应用广泛涵盖了各个领域。

在未来,随着人类技术的不断进步和应用场景的不断拓展,PID控制器的应用也将变得越来越广泛和深入。

可编程逻辑器件及应用 丝路

可编程逻辑器件及应用丝路可编程逻辑器件(Programmable Logic Device,PLD)是一种数字电路集成电路,它可以通过编程来实现特定的功能。

PLD通常包括可编程逻辑阵列(Programmable Logic Array,PLA)、可编程阵列逻辑器件(Programmable Array Logic,PAL)和复杂可编程逻辑器件(Complex Programmable Logic Device,CPLD)等。

PLD的应用非常广泛,它可以被用于数字信号处理、计算机网络、通信系统、工业控制等领域。

下面将介绍几个PLD的应用案例。

1. 数字信号处理数字信号处理是指将模拟信号转换为数字信号,并对其进行处理的过程。

在数字信号处理中,PLD可以被用于实现滤波器、快速傅里叶变换(Fast Fourier Transform,FFT)等算法。

例如,在音频处理中,PLD可以被用于实现音频滤波器以及降噪算法。

2. 计算机网络计算机网络是指多台计算机通过通信线路相互连接起来形成的一个系统。

在计算机网络中,PLD可以被用于实现交换机、路由器等网络设备。

例如,在以太网中,交换机需要对数据包进行转发和过滤操作。

这些操作可以通过使用PLD来实现。

3. 通信系统通信系统是指将信息从一个地方传输到另一个地方的系统。

在通信系统中,PLD可以被用于实现调制解调器、编码器、解码器等电路。

例如,在数字电视中,PLD可以被用于实现视频编解码器以及数字信号处理算法。

4. 工业控制工业控制是指对工业生产过程进行自动化控制的过程。

在工业控制中,PLD可以被用于实现逻辑控制器(Programmable Logic Controller,PLC)、传感器接口电路、运动控制器等设备。

例如,在自动化生产线上,PLC需要对各个设备进行监控和控制。

这些操作可以通过使用PLD来实现。

丝路是一条连接东西方的古代贸易路线。

在丝路上,商人们通过沟通交流来促进贸易和文化交流。

pld应用程序举例

PLD应用程序举例PLD〔可编程逻辑器件〕是一种集成电路,它具有重要的应用领域。

在本文档中,我们将介绍几个常见的PLD应用程序的例子,包括数字逻辑电路、数据通信系统和图像处理。

数字逻辑电路数字逻辑电路是PLD应用程序的一种常见形式。

它们由逻辑门和触发器组成,用于实现各种逻辑功能。

下面是一些常见的数字逻辑电路应用程序:1. 门电路门电路由逻辑门组成,逻辑门有与门、或门、非门等。

门电路可以用于实现布尔逻辑操作,如逻辑与、逻辑或、逻辑非等。

PLD可以程序化配置,实现各种不同的逻辑电路。

2. 计数器和时序电路计数器是数字电路中常见的一个组件,可以用来计数和分频。

PLD 可以用来实现各种不同类型的计数器,如二进制计数器、BCD计数器等。

时序电路用于控制信号的时序和时钟分频,也可以通过PLD来实现。

3. 十进制解码器十进制解码器是将BCD码或二进制编码转换为七段显示器所需的信号的电路。

PLD可以用来实现十进制解码器,从而实现数字显示。

数据通信系统PLD在数据通信系统中也有广泛的应用。

它们可以用于实现各种不同的通信协议和接口。

下面是一些常见的数据通信系统应用程序:1. UARTUART〔通用异步收发器〕是一种常见的串行通信接口。

PLD可以用来实现UART接口,使设备能够进行串行通信。

2. SPISPI〔串行外设接口〕是一种用于连接多个外设的通信协议。

PLD 可以用来实现SPI接口,使设备能够与其他外设进行通信。

3. I2CI2C〔串行总线接口〕是一种用于连接多个设备的通信协议。

PLD 可以用来实现I2C接口,使设备能够进行多设备通信。

图像处理PLD也可以在图像处理领域发挥重要作用。

它们可以用于实现各种图像处理算法和滤波器。

下面是一些常见的图像处理应用程序:1. 图像滤波器图像滤波器可以用于平滑、锐化或增强图像。

PLD可以用来实现各种滤波器,如均值滤波器、中值滤波器等。

2. 图像压缩图像压缩是减少图像文件大小的过程。

PID算法实例

signed int uk1; //对u[k]四舍五入取整

signed int adjust; //调节器输出调整量

//变量初始化

Kp=4;

Ti=0.005;

T=0.001;

// Ki=KpT/Ti=0.8,微分系数Kd=KpTd/T=0.8,Td=0.0002,根据实验调得的结果确定这些参数

ek=0;

ek1=0;

ek2=0;

uk=0;

uk1=0;

adjust=0;

intpiadjust(float ek) //PI调节算法

{

if( gabs(ek)<0.1 )

adjust=0;

else

{

uk=Kp*(ek-ek1)+Ki*ek; //计算控制增量

ek1=ek;

uk1=(signed int)uk;

{

EvaRegs.CMPR3=EvaRegs.CMPR3+piadjust(ek);//误差较小PID调节稳住

if(EvaRegs.CMPR3>=890)

{

EvaRegs.CMPR3=890; //限制PWM占空比

}

}

PID 算法应用实例

一、PID算法:

比例、积分、微分控制,简称PID控制,又称PID调节;

二、应用环境:

当被控对象的结构和参数不能完全掌握,或得不到精确的数学模型时,控制理论的其它技术难以采用时,系统控制器的结构和参数必须依靠经验和现场调试来确定;

三、PID算法应用实例

四、参数调整

PID控制器参数选择的方法很多,例如试凑法、临界比例度法、扩充临界比例度法等。但是,对于PID控制而言,参数的选择始终是一件非常烦杂的工作,需要经过不断的调整才能得到较为满意的控制效果。依据经验,一般PID参数确定的步骤如下:

第12章PLD技术及其应用

➢ BIT 位类型,取值0、1,由STANDARD程序包定义; ➢ BIT_VECTOR 位向量类型,是BIT的组合,该端口的取值可能是

一组二进制位的值; ➢ STD_LOGIC 工业标准的逻辑类型,取值0、1、X、Z,由

STD_LOGIC_1164程序包定义; ➢ INTEGER 整数类型,可用作循环的指针或常数,通常不用作I/O信号; ➢ STD_LOGIC_VECTOR 工业标准的逻辑向量类型,是STD_LOGIC的组; ➢ BOOLEAN 布尔类型,取值FALSE,TRUE。

(2) 可移植性好。对于设计和仿真工具采用相同的描述,对 于不同的平台也采用相同的描述。

(3) 研制周期短,成本低。由于VHDL支持大规模设计的分 解和对已有设备的利用,因此加快了设计流程。

(4) 可以延长设计的生命周期。因为VHDL的硬件描述与工 艺技术无关,不会因工艺变化而使描述过时。

硬件描述语言 库

创建一个默认的图形符号

第12章 12.2.1

第12章 12.2.1

创建一个默认的图形符号

文本设计输入方法

第12章 12.2.1

文本设计输入方法

第12章 12.2.1

文本设计输入方法

第12章 12.2.1 文本输入

文本设计输入方法 保存文件

第12章 12.2.1

顶层图形设计方法

第12章 12.2.1

CPLD的编程工艺

第12章 12.1.2

✓ EPROM(Erasable Programmable ROM)工艺 ✓ E2ROM(Electrical Erasable ROM)工艺 ✓ Flash工艺

FPGA的结构特点

VCC

GND &

第12章 12.1.2

可编程逻辑器件及应用 滴管

可编程逻辑器件及应用滴管一、可编程逻辑器件概述可编程逻辑器件(Programmable Logic Device,PLD)是一种能够根据用户的需求自行配置的数字电路,具有灵活性和可重构性等特点。

常见的PLD包括可编程门阵列(Programmable Array Logic,PAL)、可编程逻辑阵列(Programmable Logic Array,PLA)、复杂可编程逻辑器件(Complex Programmable Logic Device,CPLD)和现场可编程门阵列(Field Programmable Gate Array,FPGA)等。

二、PLD应用领域1.数字信号处理PLD在数字信号处理领域有着广泛的应用。

例如,在音频处理中可以使用FPGA实现数字滤波器、音频混响、均衡器等功能;在视频处理中可以使用FPGA实现图像压缩、图像增强、运动检测等功能。

2.计算机硬件设计计算机硬件设计中也广泛使用了PLD技术。

例如,在CPU设计中可以使用FPGA实现指令集模拟器、调试接口等功能;在存储控制器设计中可以使用CPLD实现数据缓存控制、时序控制等功能。

3.通信系统通信系统也是PLD应用的重要领域之一。

例如,在无线通信系统中可以使用FPGA实现信号调制解调器、信号处理器等功能;在有线通信系统中可以使用CPLD实现时钟同步、数据转换等功能。

4.工业控制工业控制也是PLD应用的重要领域之一。

例如,在自动化生产线中可以使用FPGA实现逻辑控制器、运动控制器等功能;在机器人控制中可以使用CPLD实现运动规划、传感器数据采集等功能。

三、滴管应用案例滴管是一种常见的液体分配装置,广泛应用于医疗、化学实验和生命科学研究等领域。

PLD技术可以为滴管的精确控制提供支持。

1.滴定仪滴定仪是一种常见的化学分析仪器,用于测定溶液中某种物质的浓度。

滴定仪通常由自动滴定装置和计量装置组成,其中自动滴定装置通过PLD技术实现对液体流量的精确控制。

PLD可编程逻辑器件-pld应用程序举例 精品

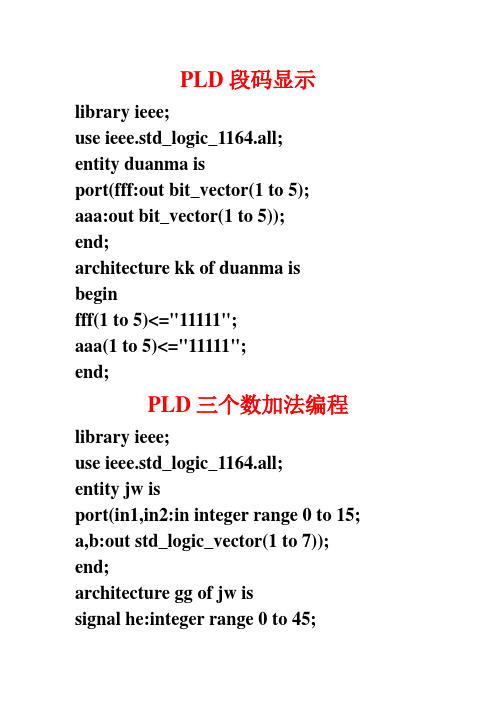

PLD段码显示library ieee;use ieee.std_logic_1164.all;entity duanma isport(fff:out bit_vector(1 to 5); aaa:out bit_vector(1 to 5));end;architecture kk of duanma isbeginfff(1 to 5)<="11111";aaa(1 to 5)<="11111";end;PLD三个数加法编程library ieee;use ieee.std_logic_1164.all;entity jw isport(in1,in2:in integer range 0 to 15; a,b:out std_logic_vector(1 to 7)); end;architecture gg of jw issignal he:integer range 0 to 45;beginhe<=in1+in2;with he selecta<="1111110" when 0|10|20|30|40, "0110000" when 1|11|21|31|41, "1101101" when 2|12|22|32|42, "1111001" when 3|13|23|33|43, "0110011" when 4|14|24|34|44, "1011011" when 5|15|25|35|45, "1011111" when 6|16|26|36, "1110000" when 7|17|27|37, "1111111" when 8|18|28|38, "1111011" when 9|19|29|39, "0000000" when others;with he selectb<="0000000" when 0<=he and he<=9,else "0110000" when 10<=he andhe<=19,else"1101101" when 20<=he andhe<=29,else"1111001" when 30<=he andhe<=39,else"0110011" when 40<=he andhe<=39,else"0000000" when others;end;PLD八个按键两个灯library ieee;use ieee.std_logic_1164.all;entity guozi3 isport(in1,in2:in std_logic_vector(1 to 4); a,b:out std_logic_vector(1 to 8)); end;architecture gg of guozi3 isbeginwith in1 select"0110000" when "0001", "1101101" when "0010", "1111001" when "0011", "0110011" when "0100", "1011011" when "0101", "1011111" when "0110", "1110000" when "0111","1111111" when "1000", "1111011" when "1001", "0000000" when others;with in2 selectb<="0110000"when "0001", "1101101" when "0010", "1111001" when "0011", "0110011" when "0100", "1011011" when "0101", "1011111" when "0110", "1110000" when "0111", "1111111" when "1000", "1111011" when "1001", "0000000" when others;end;PLD顺序语句编程(0加到9) library ieee;use ieee.std_logic_1164.all;entity jinchen isport(in1:in std_logic;a:out std_logic_vector(1 to 7));end;architecture gg of jinchen is signal ss:integer range 0 to 9; beginprocessbeginwait until in1='1';ss<=ss+1;if ss=10 thenss<=0;end if;end process;with ss selecta<="1111110" when 0,"0110000" when 1,"1101101" when 2,"1111001" when 3,"0110011" when 4,"1011011" when 5,"1011111" when 6,"1110000" when 7,"1111111" when 8,"1111011" when 9,"0000000" when others;end;PLD矢量10个控制2个数码管library ieee;use ieee.std_logic_1164.all;entity kongzhi2 isport (a:out bit_vector(1 to 7);b:in bit_vector(1 to 10));end;architecture ff of kongzhi2 is begina<="1111110"when b="1000000000"else"0110000"when b="010*******"else"1101101"when b="0010000000"else"1111001"when b="1001000000"else"0110011"when b="1000100000"else"1011011"when b="1000010000"else"1011111"when b="1000001000"else"1110000"when b="1000000100"else"1111111"when b="1000000010"else"1110011"when b="1000000001"else"0000000";end;PLD晶振50M控制数码管library ieee;use ieee.std_logic_1164.all; entity jinzheng isport(in50m:in std_logic;a:out std_logic_vector(1 to 7)); end;architecture gg of jinzheng is signal in1:std_logic;signal ss:integer range 0 to 9;signal count:integer range 0 to 25000000;beginprocessbeginwait until in50m='1';count<=count+1;if count=25000000 thencount<=0;in1<=not in1;end if;end process;processbeginwait until in1='1';ss<=ss+1;if ss=10 thenss<=0;end if;end process;with ss selecta<="1111110" when 0,"0110000" when 1,"1101101" when 2,"1111001" when 3,"0110011" when 4,"1011011" when 5,"1011111" when 6,"1110000" when 7,"1111111" when 8,"1111011" when 9,"0000000" when others;end;PLD晶振50M自动跳变程序(0到59)library ieee;use ieee.std_logic_1164.all;entity jiadxx isport(in50m:in std_logic;a,b:out std_logic_vector(1 to 7)); end;architecture gg of jiadxx issignal in1:std_logic;signal t,g:integer range 0 to 9;signal count:integer range 0 to 59 25000000;beginprocessbeginwait until in50m='1';count<=count+1;if count=25000000 thencount<=0;in1<=not in1;end if;end process;processbeginwait until in1='1';g<=g+1;if g=9 then if g=5 then 改变变量g<=0;t<=t+1;if t=5 thent<=0;end if;end if;end process;with g selecta<="1111110" when 0,"0110000" when 1,"1101101" when 2,"1111001" when 3,"0110011" when 4,"1011011" when 5,"1011111" when 6,"1110000" when 7,"1111111" when 8,"1111011" when 9,"0000000" when others; with t selectb<="1111110" when 0,"0110000" when 1,"1101101" when 2,"1111001" when 3,"0110011" when 4,"1011011" when 5,"1011111" when 6,"1110000" when 7,"1111111" when 8,"1111011" when 9,"0000000" when others;end;PLD(1-8数码管显示)第六个显示0 library ieee;use ieee.std_logic_1164.all;entity jiadxx isport(a:out std_logic_vector(1 to 7);b:out std_logic_vector(1 to 3)); end;architecture kk of jiadxx isbegina<="1111110"; --显示的数“0”b<="010"; --显示的位“第6位”end;PLD动态间隔1秒闪烁library ieee;use ieee.std_logic_1164.all;entity jiadxx isport(in50m:in std_logic;b:out std_logic_vector(1 to 3);a:out std_logic_vector(1 to 7)); end;architecture gg of jiadxx issignal count:integer range 0 to 25000000;signal count_one:integer range 0 to 1; signal one_hz:std_logic;beginprocessbeginwait until in50m='1';count<=count+1;if count=25000000 thencount<=0;one_hz<=not one_hz;end if;end process;processbeginwait until one_hz='1';count_one<=count_one+1;if count_one=0 thenb<="000";elseb<="001";end if;end process;a<="1111110";end;PLD动态显示0 1 library ieee;use ieee.std_logic_1164.all;entity dz1121 isport(in50m:in std_logic;a:out std_logic_vector(1 to 7);b:out std_logic_vector(1 to 3));end;architecture gg of ningyi issignal in1:std_logic;signal count_c:integer range 0 to 3; signal count:integer range 0 to 2500; beginprocessbeginwait until in50m='1';count<=count+1;if count=2500 thencount<=0;in1<=not in1;end if;end process;processbeginwait until in1='1';count_c<=count_c+1;if count_c=1 thencount_c<=0;end if;end process;with count_c selecta<="1111110"when 0,"0110000"when 1,"0000000"when others;with count_c selectb<="000" when 0,"001" when 1,"111" when others;end;PLD数码管显示0-7 library ieee;use ieee.std_logic_1164.all;entity xian0-7 isport(in50m:in std_logic;a:out std_logic_vector(1 to 7);b:out std_logic_vector(1 to 3));end;architecture gg of xian0-7 issignal in1:std_logic;signal count_c:integer range 0 to 7; signal count:integer range 0 to 2500; beginprocessbeginwait until in50m='1';count<=count+1;if count=2500 thencount<=0;in1<=not in1;end if;end process;processbeginwait until in1='1';count_c<=count_c+1;case count_c iswhen 0=>b<="000"; --a<="1111110"; when 1=>b<="001";a<="0110000"; when 2=>b<="010";a<="1101101"; when 3=>b<="011";a<="1111001"; when 4=>b<="100";a<="0110011"; when 5=>b<="101";a<="1011011"; when 6=>b<="110";a<="1011111"; when 7=>b<="111";a<="1110000";if count_c=7 thencount_c<=0;end if;end case;end process;end;PLD时钟显示library ieee;use ieee.std_logic_1164.all;entity shizon isport(in50m: std_logic;a:out std_logic_vector(1 to 7);--段码b:out std_logic_vector(1 to 3));--位码end;architecture ff of shizon issignal count:integer range 0 to 250;--整数定义signal count_s:integer range 0 to25000;--半秒定义signalg1,g2,s1,s2,b1,b2:std_logic_vector(1 to 7);--变量范围signal one_hz:std_logic;--定义1赫兹信号signal one_s:std_logic;signal x:integer range 0 to 7;--signal gg1,gg2,ss1,ss2,bb1,bb2:integer range 0 to 9;beginprocessbeginwait until in50m='1';count<=count+1;if count=250 thencount<=0;one_hz<=not one_hz;end if;end process;processbeginwait until in50m='1'; count_s<=count_s+1; if count_s=25000 then count_s<=0;one_s<=not one_s; end if;end process;processbeginwait until one_hz='1'; x<=x+1;case x iswhen 0=>b<="000";a<=g1;when 1=>b<="001";a<=g2;when 2=>b<="010";a<="0000001"; when 3=>b<="011";a<=s1;when 4=>b<="100";a<=s2 ;when 5=>b<="101";a<="0000001"; when 6=>b<="110";a<=b1;when 7=>b<="111";a<=b2;x<=0;end case;end process;processbeginwait until one_s='1';gg1<=gg1+1;if gg1=9 thengg1<=0;gg2<=gg2+1;if gg2=5 thengg2<=0;ss1<=ss1+1;if ss1=9 thenss1<=0;ss2<=ss2+1;if ss2=5 thenss2<=0;bb1<=bb1+1;if bb1=9 thenbb1<=0;bb2<=bb2+1;end if;if bb1=3 and bb2=2 then bb1<=0;bb2<=0;end if;end if;end if;end if;end if;end process;with gg1 selectg1<="1111110" when 0,"0110000" when 1,"1101101" when 2,"1111001" when 3,"0110011" when 4,"1011011" when 5,"1011111" when 6,"1110000" when 7,"1111111" when 8,"1111011" when 9,"0000000" when others; with gg2 selectg2<="1111110" when 0,"0110000" when 1,"1101101" when 2,"1111001" when 3,"0110011" when 4,"1011011" when 5,"0000000" when others; with ss1 selects1<="1111110" when 0,"0110000" when 1,"1111001" when 3,"0110011" when 4,"1011011" when 5,"1011111" when 6,"1110000" when 7,"1111111" when 8,"1111011" when 9,"0000000" when others; with ss2 selects2<="1111110" when 0,"0110000" when 1,"1101101" when 2,"1111001" when 3,"0110011" when 4,"1011011" when 5,"0000000" when others; with bb1 selectb1<="1111110" when 0,"0110000" when 1,"1101101" when 2,"1111001" when 3,"1011011" when 5,"1011111" when 6,"1110000" when 7,"1111111" when 8,"1111011" when 9,"0000000" when others; with bb2 selectb2<="1111110" when 0,"0110000" when 1,"1101101" when 2,"0000000" when others; end;PLD单个音符编程低2音library ieee;use ieee.std_logic_1164.all;entity ypyy isport(in50m:in std_logic;a:out std_logic);end;architecture gg of ypyy is signal in1:std_logic;signal count:integer range 0 to 25000000;beginprocessbeginwait until in50m='1';count<=count+1;if count=85034 thencount<=0;in1<=not in1;end if;end process;a<=in1;END;PLD双音符编程library ieee;use ieee.std_logic_1164.all;entity ypyy isport(in50m:in std_logic;a:out std_logic);end;architecture gg of ypyy issignal in1:std_logic;signal in2:std_logic;signal count:integer range 0 to 25000000;signal count_1:integer range 0 to 25000000;signal ys1s:integer range 0 to 50000000;signal jia1:integer range 0 to 1; beginprocessbeginwait until in50m='1';count<=count+1;if count=85034 then count<=0;in1<=not in1;end if;end process;processbeginwait until in50m='1'; count_1<=count_1+1; if count_1=63775 then count_1<=0;in2<=not in2;end if;end process;processbeginwait until in50m='1'; ys1s<=ys1s+1;if ys1s=50000000 then ys1s<=0;jia1<=jia1+1;end if;if jia1=0 thena<=in1;elsea<=in2;end if;end process;end;PLD 1-7音符编程(if语句)library ieee;use ieee.std_logic_1164.all;entity ypyy isport(in50m:in std_logic;a:out std_logic);end;architecture gg of ypyy issignal in1:std_logic;signal in2:std_logic;signal in3:std_logic;signal in4:std_logic;signal in5:std_logic;signal in6:std_logic;signal in7:std_logic;signal count:integer range 0 to 25000000;signal count_1:integer range 0 to 25000000;signal count_2:integer range 0 to 25000000;signal count_3:integer range 0 to 25000000;signal count_4:integer range 0 to 25000000;signal count_5:integer range 0 to 25000000;signal count_6:integer range 0 to 25000000;signal ys1s:integer range 0 to 50000000;signal jia1:integer range 0 to 7; beginprocessbeginwait until in50m='1';count<=count+1;if count=95419 thencount<=0;in1<=not in1;end if;end process;processbeginwait until in50m='1';count_1<=count_1+1;if count_1=85034 thencount_1<=0;in2<=not in2;end if;end process;processbeginwait until in50m='1'; count_2<=count_2+1; if count_2=75757 then count_2<=0;in3<=not in3;end if;end process;processbeginwait until in50m='1'; count_3<=count_3+1; if count_3=71633 then count_3<=0;in4<=not in4;end if;end process;processbeginwait until in50m='1'; count_4<=count_4+1; if count_4=63775 then count_4<=0;in5<=not in5;end if;end process;processbeginwait until in50m='1'; count_5<=count_5+1; if count_5=56818 then count_5<=0;in6<=not in6;end if;end process;processbeginwait until in50m='1';count_6<=count_6+1; if count_6=50607 then count_6<=0;in7<=not in7;end if;end process;processbeginwait until in50m='1'; ys1s<=ys1s+1;if ys1s=50000000 then ys1s<=0;jia1<=jia1+1;end if;if jia1=0 thena<=in1;end if;if jia1=1 thena<=in2;end if;if jia1=2 thena<=in3;end if;if jia1=3 then a<=in4;end if;if jia1=4 then a<=in5;end if;if jia1=5 then a<=in6;end if;if jia1=6 then a<=in7;end if;end process; end;。

可编程逻辑器件及应用 社会主义

可编程逻辑器件及应用社会主义可编程逻辑器件(PLD)是一种数字电路设备,它可以在不改变硬件设计的情况下重新编程以实现不同的功能。

PLD通常由可编程逻辑阵列(PLA)、可编程数组逻辑器件(PAL)和复杂可编程逻辑器件(CPLD)组成。

PLD有许多应用,从简单的控制电路到复杂的计算机系统。

以下是几个常见的应用:1. 控制电路:PLD可以用于控制各种设备和机器,例如机械臂、自动售货机、智能家居等。

通过重新编程PLD,可以改变设备的工作方式和行为。

2. 数据传输:PLD可以用于数据传输和通信系统。

例如,在网络交换机中使用PLD来实现数据包转发和路由选择。

3. 数字信号处理:PLD可以用于数字信号处理,例如音频处理、图像处理和视频压缩等。

通过重新编程PLD,可以实现各种算法和信号处理技术。

4. 计算机系统:CPLD是一种专门设计用于计算机系统中的可编程逻辑器件。

它们通常用于控制总线接口、时钟管理、存储器控制等方面。

5. 测试和测量:PLD可以用于测试和测量设备,例如数字万用表、示波器和频谱分析仪等。

通过重新编程PLD,可以实现不同的测试和测量功能。

PLD在现代社会中的应用越来越广泛。

它们可以用于各种领域,包括工业控制、通信、医疗、航空航天和军事等。

PLD的优点是灵活性高、可重复使用性好、设计周期短等。

在社会主义建设中,PLD也有着重要的应用。

例如,在工厂自动化生产线中,PLD可以用于控制机器人和生产设备,提高生产效率和质量。

在交通运输领域,PLD可以用于控制交通信号灯和智能交通系统,提高道路安全和交通流畅度。

总之,PLD是一种非常有用的数字电路设备,在现代社会中具有广泛的应用前景。

随着技术的不断发展和创新,PLD将继续发挥重要作用。

PID控制及其应用

1. 简介PID控制指的是一种闭环控制方式,将输入输出偏差的比例(P)、积分(I)和微分(D)通过线性组合构成控制量,对被控制对象进行控制。

2.PID控制原理在模拟控制系统中,控制器最常用的控制规律是PID控制。

模拟PID控制系统原理框图如图1-1所示。

系统由模拟PID控制器和被控对象组成。

PID控制器是一种线性控制器,它根据给定值rin(t)与实际输出值yout(t)构成控制偏差PID的控制规律为或写成传递函数的形式式中,Kp---比例系数;Ti--积分时间常数;Td---微分时间常数。

简单说来,PID控制器各校正环节的作用如下:(1)比例环节:成比例地反映控制系统的偏差信号error(t),偏差一旦产生,控制器立即产生控制作用,以减少偏差。

(2)积分环节:主要用于消除静差,提高系统的无差度。

积分作用的强弱取决于积分时间常数TI,TI越大,积分作用越弱,反之则越强。

(3)微分环节:反映偏差信号的变化趋势(变化速率),并能在偏差信号变得太大之前,在系统中引入一个有效的早期修正信号,从而加快系统的动作速度,减少调节时间。

3.数字PID算法原理在计算控制系统中,使用的是数字PID控制器,数字PID控制算法通常又分为位置式PID 控制算法和增量式PID控制算法。

位置式算法输出的是执行机构的实际位置,如有干扰的话,会导致大幅度变化。

而增量式PID是指数字控制器的输出只是控制量的增量,所以电机控制一般都采用增量式PID算法。

增量式PID算法公式:----△u( k ) = K p△e(k)+Kie(k)+Kd[△e(k)-△e(k-1)]----△e(k) = e(k) – e(k-1)-----△e(k-1) = e(k-1) – e(k-2)-----e(k) = r(k) – c(k) (因在速度控制导通角上开始是从大变小,所以该公式须变成c(k)-r(k))参数说明:k--------------采样序号, k = 0, 1, 2----;r(t)-----------速度给定值;c(t)-----------速度实际输出值;△u( k )------第K次采样时刻的计算机输出增量值;e(k)----------第K次采样时刻输入的偏差值;e(k-1)--------第(k-1)次采样时刻输入的偏差值;K I-------------积分系数,K I = K P*T/T I;K D------------微分系数,K D = K P*T D/T;T--------------采样调期;Kp------------比例系数;T I-------------积分时间常数T D------------微分时间常数4.PID 控制参数整定方法PID 控制参数的自动整定分两步进行,第一步是初始确定PID 控制参数;第二步是在初定的PID 控制参数基础上,根据直线电机控制系统的响应过程和控制目标期望值,修正初定的PID 参数,直至电机系统的控制指标符合所需求为止.在数字控制系统中,采样周期T 是一个比较重要的因素,采样周期的选取,应与PID 参数的整定综合考虑,选取采样周期时,一般应考虑下列几个因素: (1) 采样周期应远小于对象的扰动信号的周期。

可编程逻辑器件及应用 分式

可编程逻辑器件及应用分式

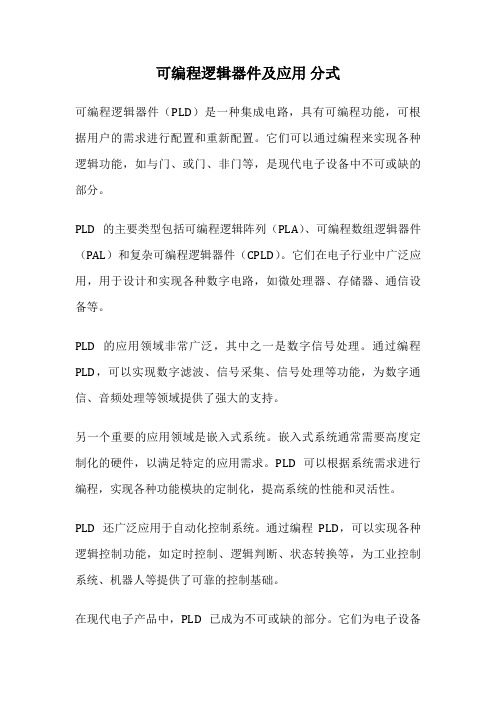

可编程逻辑器件(PLD)是一种集成电路,具有可编程功能,可根据用户的需求进行配置和重新配置。

它们可以通过编程来实现各种逻辑功能,如与门、或门、非门等,是现代电子设备中不可或缺的部分。

PLD的主要类型包括可编程逻辑阵列(PLA)、可编程数组逻辑器件(PAL)和复杂可编程逻辑器件(CPLD)。

它们在电子行业中广泛应用,用于设计和实现各种数字电路,如微处理器、存储器、通信设备等。

PLD的应用领域非常广泛,其中之一是数字信号处理。

通过编程PLD,可以实现数字滤波、信号采集、信号处理等功能,为数字通信、音频处理等领域提供了强大的支持。

另一个重要的应用领域是嵌入式系统。

嵌入式系统通常需要高度定制化的硬件,以满足特定的应用需求。

PLD可以根据系统需求进行编程,实现各种功能模块的定制化,提高系统的性能和灵活性。

PLD还广泛应用于自动化控制系统。

通过编程PLD,可以实现各种逻辑控制功能,如定时控制、逻辑判断、状态转换等,为工业控制系统、机器人等提供了可靠的控制基础。

在现代电子产品中,PLD已成为不可或缺的部分。

它们为电子设备

的设计和开发提供了灵活性和可定制性,大大缩短了产品的开发周期和成本,促进了电子科技的发展。

总的来说,可编程逻辑器件在各个领域都发挥着重要作用,推动了数字电路技术的发展,促进了电子产品的创新。

随着科技的不断进步和发展,PLD的应用领域将会越来越广泛,为人类生活带来更多便利和可能。

PID控制原理详解及实例说明

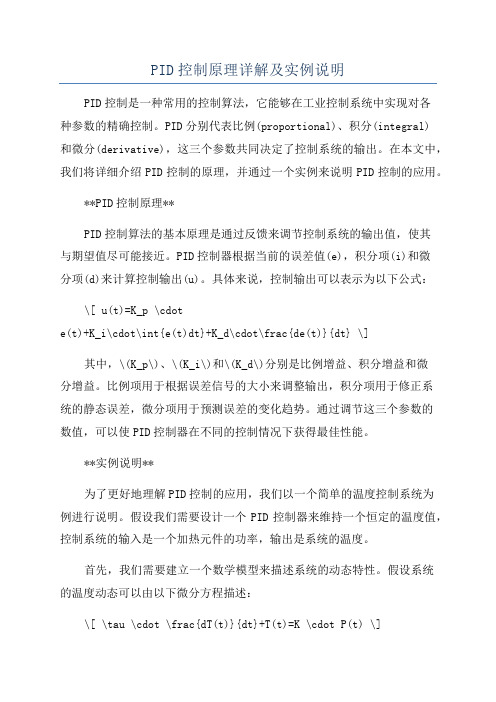

PID控制原理详解及实例说明PID控制是一种常用的控制算法,它能够在工业控制系统中实现对各种参数的精确控制。

PID分别代表比例(proportional)、积分(integral)和微分(derivative),这三个参数共同决定了控制系统的输出。

在本文中,我们将详细介绍PID控制的原理,并通过一个实例来说明PID控制的应用。

**PID控制原理**PID控制算法的基本原理是通过反馈来调节控制系统的输出值,使其与期望值尽可能接近。

PID控制器根据当前的误差值(e),积分项(i)和微分项(d)来计算控制输出(u)。

具体来说,控制输出可以表示为以下公式:\[ u(t)=K_p \cdote(t)+K_i\cdot\int{e(t)dt}+K_d\cdot\frac{de(t)}{dt} \]其中,\(K_p\)、\(K_i\)和\(K_d\)分别是比例增益、积分增益和微分增益。

比例项用于根据误差信号的大小来调整输出,积分项用于修正系统的静态误差,微分项用于预测误差的变化趋势。

通过调节这三个参数的数值,可以使PID控制器在不同的控制情况下获得最佳性能。

**实例说明**为了更好地理解PID控制的应用,我们以一个简单的温度控制系统为例进行说明。

假设我们需要设计一个PID控制器来维持一个恒定的温度值,控制系统的输入是一个加热元件的功率,输出是系统的温度。

首先,我们需要建立一个数学模型来描述系统的动态特性。

假设系统的温度动态可以由以下微分方程描述:\[ \tau \cdot \frac{dT(t)}{dt}+T(t)=K \cdot P(t) \]其中,\(T(t)\)代表系统的温度,\(P(t)\)代表加热元件的功率,\(\tau\)代表系统的时间常数,\(K\)代表系统的传递函数。

接下来,我们可以根据这个数学模型来设计PID控制器。

首先,我们需要对系统进行参数调试,确定合适的比例增益\(K_p\)、积分增益\(K_i\)和微分增益\(K_d\)。

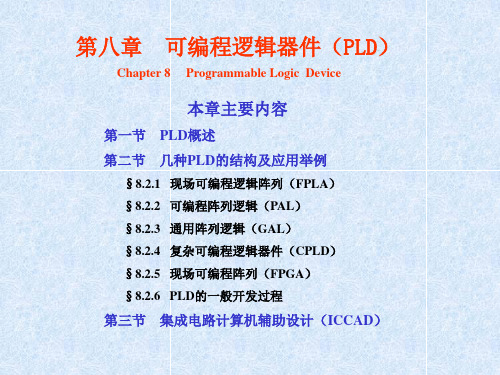

可编程逻辑器件(PLD)

据表8-2-3化简可得各个触发器的状态方程为: 驱动方程为:

用PAL16R4实现四 位循环码计数器

四、PAL的特点: 1)“与”阵列可编程方法能提供较高的性能和最有效的结构,

每个输出所需的乘积项的数量由“或”阵列固定; 2)灵活性强,在现代电子行业中仍大量使用。 3)PAL的缺点是采用熔丝工艺,一旦编程后就不能修改。

图8.2.9 GAL16V8结构控制字的组成

图8.2.8中的或门有8个输入端,来自与逻辑阵列的输出;异或门用于 控制输出函数的极性。当XOR(n)为0时,异或门的输出与或门的输出 同相,否则反相。

列的第一乘积项当中选择一个作为输出三态缓冲器的控制信号,如表8-2-4 所示。

表8-2-4 TSMUX的控制功能表

PLD的基本结构图:

一、PLD的表示方法: 描述PLD器件基本结构的逻辑图形符号如下:

二、PLD的优点:

PLD综合了标准通用型逻辑器件和半定制逻辑器件的许 多优点,再加上它的可编程性,为数字系统的设计带来了很 多方便。其优点如下:

1、设计灵活、方便

2、高性能和高可靠性

3、费用较低

三、PLD的分类:

8-2-5所示。

表8-2-5 FMUX的控制功能表

OLMC的工作模式表8-2-6所列的5种,它们由结构控制字 SYN、AC1(n)、XOR(n)的状态指定。

表8-2-6 OLMC的5种工作模式

三、OLMC的特点: 1)OLMC的输入可以独立的设定为高或低有效 2)可采用组合逻辑(异步)输出或寄存器逻辑(同步)输出; 3)器件有一个公用的输出使能端,对于每个输出使能端可以由

三、PAL应用举例:

[例8-2-1] 用PAL器件设计一个数值判别电路。要求判断4位二进 制数DCBA的大小属于0-5、6-10、11-15三个区间的哪一个之内。

第七章PLD及其应用

ROM的分类

按构成存储单 ROM存入 元的元件分类 数据的过程 称为编程 掩模式ROM

晶体管ROM

MOS管ROM

一次编程ROM(PROM)

按编程方式 多次改写编程ROM 分类 闪速存储器FLASH

光擦编程ROM(EPROM) 电擦编程ROM(EEPROM) 电改写ROM(EAROM)

ROM的应用(2)

{end}

PLD的结构与特点(5)

PLD器件的电路表示方法 基本逻辑单元的表示 输入/反馈缓冲器

B A A

CA

采用互补 ABC

“或”门

ABC

F

F A B C

PLD的结构与特点(6)

PLD器件的电路表示方法 阵列交叉点的逻辑表示

硬性连接

编程连接

第7章 可编程逻辑器件及其应用

§7.1 PLD的结构与特点

基本结构与分类

PLD器件的电路表示方法

§7.2 ROM的工作原理与应用

ROM的组成与原理

ROM的应用

第7章 可编程逻辑器件及其应用

§7.3 通用阵列逻辑器件GAL

GAL器件的基本结构 GAL器件的应用与开发

{end}

PLD的结构与特点(1)

地址译码器

ROM的基本结构

地址 线

A0 A1

存贮矩阵 输出缓冲器

字线

存贮容量

W0 W 地址 1 译码 存贮矩阵 器 An 1 W2 n 1

2 m

210 m 1K m

n

输出缓冲器

位线

Dm 1

D1 D0

地址 ROM 字线 数据 (位线) 3) 的应用(

pld应用程序举例.doc

PLD段码显示library ieee;use ieee.std_logic_1164.all;entity duanma isport(fff:out bit_vector(1 to 5); aaa:out bit_vector(1 to 5));end;architecture kk of duanma isbeginfff(1 to 5)<="11111";aaa(1 to 5)<="11111";end;PLD三个数加法编程library ieee;use ieee.std_logic_1164.all;entity jw isport(in1,in2:in integer range 0 to 15; a,b:out std_logic_vector(1 to 7)); end;architecture gg of jw issignal he:integer range 0 to 45;beginhe<=in1+in2;with he selecta<="1111110" when 0|10|20|30|40, "0110000" when 1|11|21|31|41, "1101101" when 2|12|22|32|42, "1111001" when 3|13|23|33|43, "0110011" when 4|14|24|34|44, "1011011" when 5|15|25|35|45, "1011111" when 6|16|26|36, "1110000" when 7|17|27|37, "1111111" when 8|18|28|38, "1111011" when 9|19|29|39, "0000000" when others;with he selectb<="0000000" when 0<=he and he<=9,else "0110000" when 10<=he andhe<=19,else"1101101" when 20<=he andhe<=29,else"1111001" when 30<=he andhe<=39,else"0110011" when 40<=he andhe<=39,else"0000000" when others;end;PLD八个按键两个灯library ieee;use ieee.std_logic_1164.all;entity guozi3 isport(in1,in2:in std_logic_vector(1 to 4); a,b:out std_logic_vector(1 to 8)); end;architecture gg of guozi3 isbeginwith in1 select"0110000" when "0001", "1101101" when "0010", "1111001" when "0011", "0110011" when "0100", "1011011" when "0101", "1011111" when "0110", "1110000" when "0111","1111111" when "1000", "1111011" when "1001", "0000000" when others;with in2 selectb<="0110000"when "0001", "1101101" when "0010", "1111001" when "0011", "0110011" when "0100", "1011011" when "0101", "1011111" when "0110", "1110000" when "0111", "1111111" when "1000", "1111011" when "1001", "0000000" when others;end;PLD顺序语句编程(0加到9) library ieee;use ieee.std_logic_1164.all;entity jinchen isport(in1:in std_logic;a:out std_logic_vector(1 to 7));end;architecture gg of jinchen is signal ss:integer range 0 to 9; beginprocessbeginwait until in1='1';ss<=ss+1;if ss=10 thenss<=0;end if;end process;with ss selecta<="1111110" when 0,"0110000" when 1,"1101101" when 2,"1111001" when 3,"0110011" when 4,"1011011" when 5,"1011111" when 6,"1110000" when 7,"1111111" when 8,"1111011" when 9,"0000000" when others;end;PLD矢量10个控制2个数码管library ieee;use ieee.std_logic_1164.all;entity kongzhi2 isport (a:out bit_vector(1 to 7);b:in bit_vector(1 to 10));end;architecture ff of kongzhi2 is begina<="1111110"when b="1000000000"else"0110000"when b="010*******"else"1101101"when b="0010000000"else"1111001"when b="1001000000"else"0110011"when b="1000100000"else"1011011"when b="1000010000"else"1011111"when b="1000001000"else"1110000"when b="1000000100"else"1111111"when b="1000000010"else"1110011"when b="1000000001"else"0000000";end;PLD晶振50M控制数码管library ieee;use ieee.std_logic_1164.all; entity jinzheng isport(in50m:in std_logic;a:out std_logic_vector(1 to 7)); end;architecture gg of jinzheng is signal in1:std_logic;signal ss:integer range 0 to 9;signal count:integer range 0 to 25000000;beginprocessbeginwait until in50m='1';count<=count+1;if count=25000000 thencount<=0;in1<=not in1;end if;end process;processbeginwait until in1='1';ss<=ss+1;if ss=10 thenss<=0;end if;end process;with ss selecta<="1111110" when 0,"0110000" when 1,"1101101" when 2,"1111001" when 3,"0110011" when 4,"1011011" when 5,"1011111" when 6,"1110000" when 7,"1111111" when 8,"1111011" when 9,"0000000" when others;end;PLD晶振50M自动跳变程序(0到59)library ieee;use ieee.std_logic_1164.all;entity jiadxx isport(in50m:in std_logic;a,b:out std_logic_vector(1 to 7)); end;architecture gg of jiadxx issignal in1:std_logic;signal t,g:integer range 0 to 9;signal count:integer range 0 to 59 25000000;beginprocessbeginwait until in50m='1';count<=count+1;if count=25000000 thencount<=0;in1<=not in1;end if;end process;processbeginwait until in1='1';g<=g+1;if g=9 then if g=5 then 改变变量g<=0;t<=t+1;if t=5 thent<=0;end if;end if;end process;with g selecta<="1111110" when 0,"0110000" when 1,"1101101" when 2,"1111001" when 3,"0110011" when 4,"1011011" when 5,"1011111" when 6,"1110000" when 7,"1111111" when 8,"1111011" when 9,"0000000" when others; with t selectb<="1111110" when 0,"0110000" when 1,"1101101" when 2,"1111001" when 3,"0110011" when 4,"1011011" when 5,"1011111" when 6,"1110000" when 7,"1111111" when 8,"1111011" when 9,"0000000" when others;end;PLD(1-8数码管显示)第六个显示0 library ieee;use ieee.std_logic_1164.all;entity jiadxx isport(a:out std_logic_vector(1 to 7);b:out std_logic_vector(1 to 3)); end;architecture kk of jiadxx isbegina<="1111110"; --显示的数“0”b<="010"; --显示的位“第6位”end;PLD动态间隔1秒闪烁library ieee;use ieee.std_logic_1164.all;entity jiadxx isport(in50m:in std_logic;b:out std_logic_vector(1 to 3);a:out std_logic_vector(1 to 7)); end;architecture gg of jiadxx issignal count:integer range 0 to 25000000;signal count_one:integer range 0 to 1; signal one_hz:std_logic;beginprocessbeginwait until in50m='1';count<=count+1;if count=25000000 thencount<=0;one_hz<=not one_hz;end if;end process;processbeginwait until one_hz='1';count_one<=count_one+1;if count_one=0 thenb<="000";elseb<="001";end if;end process;a<="1111110";end;PLD动态显示0 1 library ieee;use ieee.std_logic_1164.all;entity dz1121 isport(in50m:in std_logic;a:out std_logic_vector(1 to 7);b:out std_logic_vector(1 to 3));end;architecture gg of ningyi issignal in1:std_logic;signal count_c:integer range 0 to 3; signal count:integer range 0 to 2500; beginprocessbeginwait until in50m='1';count<=count+1;if count=2500 thencount<=0;in1<=not in1;end if;end process;processbeginwait until in1='1';count_c<=count_c+1;if count_c=1 thencount_c<=0;end if;end process;with count_c selecta<="1111110"when 0,"0110000"when 1,"0000000"when others;with count_c selectb<="000" when 0,"001" when 1,"111" when others;end;PLD数码管显示0-7 library ieee;use ieee.std_logic_1164.all;entity xian0-7 isport(in50m:in std_logic;a:out std_logic_vector(1 to 7);b:out std_logic_vector(1 to 3));end;architecture gg of xian0-7 issignal in1:std_logic;signal count_c:integer range 0 to 7; signal count:integer range 0 to 2500; beginprocessbeginwait until in50m='1';count<=count+1;if count=2500 thencount<=0;in1<=not in1;end if;end process;processbeginwait until in1='1';count_c<=count_c+1;case count_c iswhen 0=>b<="000"; --a<="1111110"; when 1=>b<="001";a<="0110000"; when 2=>b<="010";a<="1101101"; when 3=>b<="011";a<="1111001"; when 4=>b<="100";a<="0110011"; when 5=>b<="101";a<="1011011"; when 6=>b<="110";a<="1011111"; when 7=>b<="111";a<="1110000";if count_c=7 thencount_c<=0;end if;end case;end process;end;PLD时钟显示library ieee;use ieee.std_logic_1164.all;entity shizon isport(in50m: std_logic;a:out std_logic_vector(1 to 7);--段码b:out std_logic_vector(1 to 3));--位码end;architecture ff of shizon issignal count:integer range 0 to 250;--整数定义signal count_s:integer range 0 to25000;--半秒定义signalg1,g2,s1,s2,b1,b2:std_logic_vector(1 to 7);--变量范围signal one_hz:std_logic;--定义1赫兹信号signal one_s:std_logic;signal x:integer range 0 to 7;--signal gg1,gg2,ss1,ss2,bb1,bb2:integer range 0 to 9;beginprocessbeginwait until in50m='1';count<=count+1;if count=250 thencount<=0;one_hz<=not one_hz;end if;end process;processbeginwait until in50m='1'; count_s<=count_s+1; if count_s=25000 then count_s<=0;one_s<=not one_s; end if;end process;processbeginwait until one_hz='1'; x<=x+1;case x iswhen 0=>b<="000";a<=g1;when 1=>b<="001";a<=g2;when 2=>b<="010";a<="0000001"; when 3=>b<="011";a<=s1;when 4=>b<="100";a<=s2 ;when 5=>b<="101";a<="0000001"; when 6=>b<="110";a<=b1;when 7=>b<="111";a<=b2;x<=0;end case;end process;processbeginwait until one_s='1';gg1<=gg1+1;if gg1=9 thengg1<=0;gg2<=gg2+1;if gg2=5 thengg2<=0;ss1<=ss1+1;if ss1=9 thenss1<=0;ss2<=ss2+1;if ss2=5 thenss2<=0;bb1<=bb1+1;if bb1=9 thenbb1<=0;bb2<=bb2+1;end if;if bb1=3 and bb2=2 then bb1<=0;bb2<=0;end if;end if;end if;end if;end if;end process;with gg1 selectg1<="1111110" when 0,"0110000" when 1,"1101101" when 2,"1111001" when 3,"0110011" when 4,"1011011" when 5,"1011111" when 6,"1110000" when 7,"1111111" when 8,"1111011" when 9,"0000000" when others; with gg2 selectg2<="1111110" when 0,"0110000" when 1,"1101101" when 2,"1111001" when 3,"0110011" when 4,"1011011" when 5,"0000000" when others; with ss1 selects1<="1111110" when 0,"0110000" when 1,"1111001" when 3,"0110011" when 4,"1011011" when 5,"1011111" when 6,"1110000" when 7,"1111111" when 8,"1111011" when 9,"0000000" when others; with ss2 selects2<="1111110" when 0,"0110000" when 1,"1101101" when 2,"1111001" when 3,"0110011" when 4,"1011011" when 5,"0000000" when others; with bb1 selectb1<="1111110" when 0,"0110000" when 1,"1101101" when 2,"1111001" when 3,"1011011" when 5,"1011111" when 6,"1110000" when 7,"1111111" when 8,"1111011" when 9,"0000000" when others; with bb2 selectb2<="1111110" when 0,"0110000" when 1,"1101101" when 2,"0000000" when others; end;PLD单个音符编程低2音library ieee;use ieee.std_logic_1164.all;entity ypyy isport(in50m:in std_logic;a:out std_logic);end;architecture gg of ypyy is signal in1:std_logic;signal count:integer range 0 to 25000000;beginprocessbeginwait until in50m='1';count<=count+1;if count=85034 thencount<=0;in1<=not in1;end if;end process;a<=in1;END;PLD双音符编程library ieee;use ieee.std_logic_1164.all;entity ypyy isport(in50m:in std_logic;a:out std_logic);end;architecture gg of ypyy issignal in1:std_logic;signal in2:std_logic;signal count:integer range 0 to 25000000;signal count_1:integer range 0 to 25000000;signal ys1s:integer range 0 to 50000000;signal jia1:integer range 0 to 1; beginprocessbeginwait until in50m='1';count<=count+1;if count=85034 then count<=0;in1<=not in1;end if;end process;processbeginwait until in50m='1'; count_1<=count_1+1; if count_1=63775 then count_1<=0;in2<=not in2;end if;end process;processbeginwait until in50m='1'; ys1s<=ys1s+1;if ys1s=50000000 then ys1s<=0;jia1<=jia1+1;end if;if jia1=0 thena<=in1;elsea<=in2;end if;end process;end;PLD 1-7音符编程(if语句)library ieee;use ieee.std_logic_1164.all;entity ypyy isport(in50m:in std_logic;a:out std_logic);end;architecture gg of ypyy issignal in1:std_logic;signal in2:std_logic;signal in3:std_logic;signal in4:std_logic;signal in5:std_logic;signal in6:std_logic;signal in7:std_logic;signal count:integer range 0 to 25000000;signal count_1:integer range 0 to 25000000;signal count_2:integer range 0 to 25000000;signal count_3:integer range 0 to 25000000;signal count_4:integer range 0 to 25000000;signal count_5:integer range 0 to 25000000;signal count_6:integer range 0 to 25000000;signal ys1s:integer range 0 to 50000000;signal jia1:integer range 0 to 7; beginprocessbeginwait until in50m='1';count<=count+1;if count=95419 thencount<=0;in1<=not in1;end if;end process;processbeginwait until in50m='1';count_1<=count_1+1;if count_1=85034 thencount_1<=0;in2<=not in2;end if;end process;processbeginwait until in50m='1'; count_2<=count_2+1; if count_2=75757 then count_2<=0;in3<=not in3;end if;end process;processbeginwait until in50m='1'; count_3<=count_3+1; if count_3=71633 then count_3<=0;in4<=not in4;end if;end process;processbeginwait until in50m='1'; count_4<=count_4+1; if count_4=63775 then count_4<=0;in5<=not in5;end if;end process;processbeginwait until in50m='1'; count_5<=count_5+1; if count_5=56818 then count_5<=0;in6<=not in6;end if;end process;processbeginwait until in50m='1';count_6<=count_6+1; if count_6=50607 then count_6<=0;in7<=not in7;end if;end process;processbeginwait until in50m='1'; ys1s<=ys1s+1;if ys1s=50000000 then ys1s<=0;jia1<=jia1+1;end if;if jia1=0 thena<=in1;end if;if jia1=1 thena<=in2;end if;if jia1=2 thena<=in3;end if;if jia1=3 then a<=in4;end if;if jia1=4 then a<=in5;end if;if jia1=5 then a<=in6;end if;if jia1=6 then a<=in7;end if;end process; end;。

可编程逻辑器件及应用 话语

可编程逻辑器件及应用话语可编程逻辑器件(PLD)是一种集成电路,可以根据用户的需求进行编程,实现不同的逻辑功能。

它们被广泛应用于数字电子设备中,例如计算机、通信设备、工业自动化系统等。

PLD的出现极大地推动了数字电子技术的发展,为人们的生活带来了诸多便利。

PLD通常包括可编程逻辑阵列(PLA)和可编程输入/输出(PIO)两部分。

PLA是PLD的核心部件,由一系列可编程逻辑单元(PLU)组成,每个PLU可以实现一个逻辑门或一组逻辑门的功能。

PIO则用于与外部设备进行通信,实现数据的输入和输出。

通过编程,用户可以将不同的逻辑功能映射到PLD的逻辑单元上,从而实现自己想要的功能。

PLD的应用非常广泛。

在计算机领域,PLD常用于实现各种逻辑控制功能,例如地址译码、时序控制、状态机设计等。

在通信设备中,PLD可以用于实现信号处理、协议转换、时钟管理等功能。

在工业自动化系统中,PLD则可以实现各种控制逻辑,提高生产效率和产品质量。

除了以上领域,PLD还被广泛应用于航天航空、汽车电子、医疗设备等领域。

例如,在航天航空领域,PLD可以用于实现导航系统、飞行控制系统等;在汽车电子领域,PLD可以用于实现车辆控制系统、车载娱乐系统等;在医疗设备领域,PLD可以用于实现医疗影像处理、生命参数监测等。

随着科技的不断发展,PLD的功能和性能也在不断提升。

新型的PLD产品不仅集成度更高、功耗更低,而且支持更复杂的逻辑功能和算法。

例如,现在的PLD产品可以支持高速数据处理、人工智能算法等,为各种应用场景提供更强大的计算能力。

总的来说,可编程逻辑器件在数字电子技术领域扮演着至关重要的角色。

它们不仅为我们的生活带来了便利,而且推动了数字化进程的发展。

随着科技的不断进步,相信PLD的应用领域会越来越广泛,功能也会越来越强大。

让我们拭目以待,见证PLD的未来发展!。

pld设计实例

PLD设计实例引言可编程逻辑器件〔PLD〕是一种数字电路设备,可以根据用户的需要来重新配置其逻辑功能。

PLD在数字系统设计中起着重要的作用,能够提高设计效率和可重用性。

本文将介绍一个PLD设计实例,详细说明设计过程和实现步骤。

设计目标在本实例中,我们的设计目标是实现一个4位全加器电路。

全加器是一种常用的组合逻辑电路,用于将两个输入位和一个进位输入位相加,同时产生和位和进位输出位。

设计过程1. 确定输入输出首先,我们需要确定设计的输入和输出。

在这个实例中,我们的输入是两个4位的二进制数和一个进位输入位,输出是一个4位的二进制和结果和一个进位输出位。

2. 确定逻辑方程根据全加器的功能,我们可以确定其逻辑方程。

全加器的和输出位可以通过对两个输入位和进位位进行异或操作得到,进位输出位可以通过对两个输入位和进位位进行与操作得到。

因此,全加器的逻辑方程如下:和输出位 = 输入位1 ⊕ 输入位2 ⊕ 进位输入位进位输出位 = (输入位1 ∧ 输入位2) ∨ (输入位1 ∧ 进位输入位) ∨ (输入位2 ∧ 进位输入位)3. 确定逻辑电路图根据全加器的逻辑方程,我们可以绘制其逻辑电路图。

在这个实例中,我们需要实现4个全加器来组成4位的全加器电路。

每个全加器的输入和输出如下:输入:输入位1、输入位2、进位输入位输出:和输出位、进位输出位将4个全加器依次连接,形成4位的全加器电路。

4. PLD实现利用PLD来实现我们的设计。

PLD可以通过配置其内部的逻辑功能块来实现不同的数字电路设计。

在本实例中,我们可以使用PLD的可编程逻辑阵列〔PLA〕功能块来实现全加器电路。

首先,我们需要将全加器的逻辑方程转换成与、或、非逻辑块的组合。

然后,根据PLD的可编程特性,我们可以将这些逻辑块配置到PLD的PLA功能块中。

5. 配置PLD根据全加器的逻辑电路图,我们可以将对应的逻辑块配置到PLD的PLA功能块中,以实现全加器电路。

配置PLD的具体方法可以参考PLD芯片的技术手册。

可编程逻辑器件及应用 弹球

可编程逻辑器件及应用弹球

可编程逻辑器件在弹球游戏中的应用

弹球游戏一直以来都备受玩家们的喜爱,其简单而有趣的玩法吸引了无数人的参与。

而在现代科技的飞速发展下,弹球游戏也逐渐融入了更多的高科技元素,其中可编程逻辑器件的应用就是一个典型的例子。

可编程逻辑器件,简称PLD,是一种集成电路芯片,可以根据用户的需求和设计来进行编程,实现不同的逻辑功能。

在弹球游戏中,PLD可以被用来控制弹球的运动轨迹、速度、反弹角度等参数,从而增加游戏的趣味性和挑战性。

PLD可以用来控制弹球的运动轨迹。

通过编程设置不同的逻辑条件和算法,可以让弹球在桌面上来回移动,避开障碍物或者击中目标。

这样一来,玩家在游戏中就需要通过操作来控制弹球的运动方向,增加了游戏的难度和挑战性。

PLD还可以控制弹球的速度。

通过编程设置不同的速度参数,可以让弹球在游戏中快速移动或者缓慢前行,从而让玩家在游戏中需要更快的反应速度和更精准的操作来控制弹球,增加了游戏的刺激感和紧张感。

PLD还可以控制弹球的反弹角度。

通过编程设置不同的反弹条件和算法,可以让弹球在撞到障碍物或者墙壁时以不同的角度反弹,从

而让玩家在游戏中需要更准确的预判和操作来控制弹球的轨迹,增加了游戏的策略性和技巧性。

总的来说,可编程逻辑器件在弹球游戏中的应用,可以让游戏变得更加有趣、刺激和具有挑战性。

通过编程设置不同的参数和逻辑条件,可以让弹球的运动变得更加多变和精彩,吸引更多的玩家参与其中。

希望未来能有更多的创新技术被应用到弹球游戏中,让这个经典的游戏焕发出新的活力和魅力。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

PLD 段码显示library ieee;use ieee.std_logic_1164.all; entity duanma is port(fff:out bit_vector(1 to 5); aaa:outbit_vector(1 to 5)); end;architecture kk of duanma isbeginfff(1 to 5)<="11111";aaa(1 to 5)<="11111"; end;PLD 三个数加法编程library ieee;use ieee.std_logic_1164.all;entity jw is port(in1,in2:in integer range 0 to 15; a,b:out std_logic_vector(1 to 7));end;architecture gg of jw is signal he:integer range 0 to 45;beginhe<=in1+in2;with he selecta<="1111110" when 0|10|20|30|40,"0110000" when 1|11|21|31|41,"1101101" when 2|12|22|32|42,"1111001" when 3|13|23|33|43,"0110011" when 4|14|24|34|44,"1011011" when 5|15|25|35|45,"1011111" when 6|16|26|36,"1110000" when 7|17|27|37,"1111111" when 8|18|28|38,"1111011" when 9|19|29|39,"0000000" when others;with he selectb<="0000000" when 0<=he and he<=9,else "0110000" when 10<=he andhe<=19,else"1101101" when 20<=he andhe<=29,else"1111001" when 30<=he andhe<=39,else"0110011" when 40<=he andhe<=39,else"0000000" when others;end;PLD 八个按键两个灯library ieee;use ieee.std_logic_1164.all;entity guozi3 isport(in1,in2:in std_logic_vector(1 to 4);a,b:out std_logic_vector(1 to 8)); end; architecture gg of guozi3 isbeginwith in1 select"0110000" when "0001","1101101" when "0010","1111001" when "0011","0110011" when "0100","1011011" when "0101","1011111" when "0110","1110000" when "0111","1111111" when "1000","1111011" when "1001","0000000" when others;with in2 select b<="0110000"when "0001", "1101101" when "0010", "1111001" when "0011", "0110011" when "0100", "1011011" when "0101", "1011111" when "0110", "1110000" when "0111", "1111111" when"1000", "1111011" when "1001", "0000000" when others; end;PLD 顺序语句编程(0 加到9) library ieee;use ieee.std_logic_1164.all;entity jinchen is port(in1:in std_logic;a:out std_logic_vector(1 to 7));end;architecture gg of jinchen is signal ss:integer range 0 to 9; begin process beginwait until in1='1'; ss<=ss+1;if ss=10 then ss<=0;end if; end process;with ss select a<="1111110" when 0, "0110000" when 1, "1101101" when 2, "1111001" when 3, "0110011" when 4, "1011011" when 5, "1011111" when 6, "1110000" when 7, "1111111" when 8, "1111011" whe n 9,"0000000" whe n others;end;PLD矢量10个控制2个数码管library ieee;use ieee .std」o gic_1164 .all;en tity kon gzhi2 isport (a:out bit vector(1 to 7);b:in bit vector(1 to 10));end;architecture ff of kon gzhi2 isbeg ina<="1111110"when b="1000000000"else"0110000"whe n b="010*******"else"1101101"when b="0010000000"else"1111001"whe n b="1001000000"else"0110011"whe n b="1000100000"else"1011011"whe n b="1000010000"else whe nb="1000001000"else"1110000"whe n b="1000000100"else whe nb="1000000010"else"1110011"when b="1000000001"else "0000000"; end;PLD晶振50M控制数码管library ieee;use ieee .std」o gic_1164 .all;en tity jin zhe ng isport(i n50m:i n std_logic;a:out std_logic_vector(1 to 7));end;architecture gg of ji nzhe ng issignal in 1:std_logic;sig nal ss:i nteger range 0 to 9;sig nal coun t:i nteger range 0 to 25000000; beg inprocessbeg in wait un til in 50m='1';coun t<=co un t+1;if cou nt=25000000 thencoun t<=0;in1v=not in1;end if;end process;processbeg inwait un til in 1='1';ss<=ss+1;if ss=10 thenss<=0;end if;end process;with ss selecta<="1111110" whe n 0, "0110000" when 1,"1101101" whe n 2,"1111001" whe n 3,"0110011" whe n 4,"1011011" whe n 5,"1011111" whe n 6,"1110000" when 7,"1111111" whe n 8,"1111011" whe n 9,"0000000" whe n others;end;PLD晶振50M自动跳变程序(0到59) library ieee;use ieee .std」o gic_1164 .all;en tity jiadxx isport(i n50m:i n std_logic;a,b:out std」o gic_vector(1 to 7));end;architecture gg of jiadxx issignal in 1:std_logic;sig nal t,g:i nteger range 0 to 9;signal count:integer range 0 to 59 25000000; begin process begin wait until in50m='1'; count<=count+1;if count=25000000 then count<=0;in1<=not in1; end if; end process;processbegin wait until in1='1';g<=g+1;if g=9 then if g=5 then 改变变量g<=0;t<=t+1;if t=5 then t<=0;end if;end if;end process;with g select a<="1111110" when 0, "0110000" when 1,"1101101" when 2,"1111001" when 3,"0110011" when 4,"1011011" when 5,"1011111" when 6,"1110000" when 7,"1111111" when 8,"1111011" when 9,"0000000" when others; with t select b<="1111110" when 0,"0110000" when 1,"1101101" when 2,"1111001" when 3,"0110011" when 4,"1011011" when 5,"1011111" when 6,"1110000" when 7,"1111111" when 8,"1111011" when 9,"0000000" when others;end;PLD ( 1-8 数码管显示)第六个显示0 library ieee;use ieee.std_logic_1164.all;entity jiadxx isport(a:out std_logic_vector(1 to 7); b:out std_logic_vector(1 to 3));end;architecture kk of jiadxx isbegina<="1111110"; -- 显示的数“ 0” b<="010"; --显示的位“第6 位” end;PLD 动态间隔1 秒闪烁library ieee;use ieee.std_logic_1164.all;entity jiadxx is port(in50m:in std_logic;b:out std_logic_vector(1 to 3); a:out std_logic_vector(1 to 7)); end;architecture gg of jiadxx is signalcount:integer range 0 to 25000000;signal count_one:integer range 0 to 1; signal one_hz:std_logic;begin process begin wait until in50m='1'; count<=count+1;if count=25000000 then count<=0;one_hz<=not one_hz; end if; end process; processbeginwait until one_hz='1';count_one<=count_one+1;if count_one=0 thenb<="000";elseb<="001";end if;end process;a<="1111110";end;PLD 动态显示0 1library ieee;use ieee.std_logic_1164.all;entity dz1121 isport(in50m:in std_logic;a:out std_logic_vector(1 to 7); b:outstd_logic_vector(1 to 3));end;architecture gg of ningyi is signalin1:std_logic;signal count_c:integer range 0 to 3;signal count:integer range 0 to 2500; beginprocessbegin wait until in50m='1'; count<=count+1; if count=2500 then count<=0;in1<=not in1;end if;end process;process begin wait until in1='1';count_c<=count_c+1;if count_c=1 thencount_c<=0;end if;end process;with count_c select a<="1111110"when 0, "0110000"when 1 ,"0000000"when others;with count_c selectb<="000" when 0,"001" when 1,"111" when others;end;PLD 数码管显示0-7 library ieee;use ieee.std_logic_1164.all;entity xian0-7 isport(in50m:in std_logic;a:out std_logic_vector(1 to 7);b:out std_logic_vector(1 to 3));end;architecture gg of xian0-7 issignal in1:std_logic;signal count_c:integer range 0 to 7; signal count:integer range 0 to 2500; beginprocessbeginwait until in50m='1'; count<=count+1;if count=2500 thencount<=0;in1<=not in1;end if;end process;processbeginwait until in1='1'; count_c<=count_c+1;case count_c is when 0=>b<="000";a<="1111110"; when 1=>b<="001";a<="0110000"; when 2=>b<="010";a<="1101101"; when 3=>b<="011";a<="1111001"; when 4=>b<="100";a<="0110011"; when 5=>b<="101";a<="1011011"; when 6=>b<="110";a<="1011111"; when 7=>b<="111";a<="1110000";if count_c=7 thencount_c<=0;end if;end case;end process;end;PLD 时钟显示library ieee;use ieee.std_logic_1164.all;entity shizon is port(in50m: std_logic;a:out std_logic_vector(1 to 7);-- 码b:out std_logic_vector(1 to 3));-- 码end;architecture ff of shizon is signal count:integer range 0 to 250;-- 数定义signal count_s:integer range 0 to25000;-- 半秒定义signalg1,g2,s1,s2,b1,b2:std_logic_vector(1 to 7);-- 变量范围signal one_hz:std_logic;-- 定义1 赫兹信号signal one_s:std_logic;signal x:integer range 0 to 7;--signal gg1,gg2,ss1,ss2,bb1,bb2:integer range 0 to 9;begin process begin wait until in50m='1'; count<=count+1;if count=250 then count<=0; one_hz<=not one_hz;end if; end process;processbeginwait until in50m='1'; count_s<=count_s+1; if count_s=25000 then count_s<=0;one_s<=not one_s; end if;end process;processbeginwait until one_hz='1'; x<=x+1;case x iswhen 0=>b<="000"; a<=g1;when 1=>b<="001"; a<=g2;when 2=>b<="010"; a<="0000001"; when 3=>b<="011";a<=s1;when 4=>b<="100";a<=s2 ;when 5=>b<="101"; a<="0000001"; when 6=>b<="110"; a<=b1;when 7=>b<="111"; a<=b2; x<=0; end case;end process;processbeginwait until one_s='1'; gg1<=gg1+1; if gg1=9 thengg1<=0; gg2<=gg2+1; if gg2=5 then gg2<=0;ss1<=ss1+1;if ss1=9 thenss1<=0;ss2<=ss2+1;if ss2=5 thenss2<=0; bb1<=bb1+1; if bb1=9 then bb1<=0; bb2<=bb2+1;end if;if bb1=3 and bb2=2 thenbb1<=0;bb2<=0;end if;end if;end if;end if;end if;end process;with gg1 select g1<="1111110" when 0,"0110000" when 1, "1101101" when 2, "1111001" when 3, "0110011" when 4, "1011011" when 5, "1011111" when 6, "1110000" when 7, "1111111" when 8, "1111011" when 9, "0000000" when others; with gg2 select g2<="1111110" when 0,"0110000" when 1, "1101101" when 2, "1111001" when 3, "0110011" when 4, "1011011" when 5, "0000000" when others; with ss1 select s1<="1111110" when 0,"0110000" when 1,"1101101" when 2, "1111001" when 3,"0110011" when 4, "1011011" when 5,"1011111" when 6, "1110000" when 7,"1111111" when 8, "1111011" when 9,"0000000" when others; with ss2 select s2<="1111110" when 0,"0110000" when 1, "1101101" when 2, "1111001" when 3, "0110011" when 4, "1011011" when 5, "0000000" when others; with bb1 select b1<="1111110" when 0,"0110000" when 1, "1101101" when 2,"1111001" when 3,"0110011" when 4,"1011011" when 5,"1011111" when 6,"1110000" when 7,"1111111" when 8,"1111011" when 9,"0000000" when others; with bb2 select b2<="1111110" when 0,"0110000" when 1,"1101101" when 2,"0000000" when others; end;PLD 单个音符编程低2音library ieee; use ieee.std_logic_1164.all; entity ypyy is port(in50m:in std_logic;a:out std_logic);end; architecture gg of ypyy is signalin1:std_logic; signal count:integer range 0 to 25000000;beginprocessbeginwait until in50m='1'; count<=count+1;if count=85034 then count<=0;in1<=not in1;end if;end process;a<=in1;END;PLD 双音符编程library ieee;use ieee.std_logic_1164.all;entity ypyy isport(in50m:in std_logic;a:out std_logic);end;architecture gg of ypyy issignal in1:std_logic;signal in2:std_logic;signal count:integer range 0 to 25000000;signal count_1:integer range 0 to 25000000;signal ys1s:integer range 0 to 50000000;signal jia1:integer range 0 to 1; beginprocessbeginwait until in50m='1';count<=count+1;if count=85034 then count<=0;in1<=not in1;end if;end process;processbeginwait until in50m='1'; count_1<=count_1+1; if count_1=63775 then count_1<=0;in2<=not in2;end if;end process;processbeginwait until in50m='1'; ys1s<=ys1s+1;if ys1s=50000000 then ys1s<=0;jia1<=jia1+1; end if;if jia1=0 then a<=in1;else a<=in2;end if;end process; end;PLD 1-7 音符编程( if 语句) library ieee;use ieee.std_logic_1164.all;entity ypyy is port(in50m:in std_logic;a:out std_logic); end;architecture gg of ypyy is signal in1:std_logic; signal in2:std_logic;signal in3:std_logic;signal in4:std_logic;signal in5:std_logic;signal in6:std_logic;signal in7:std_logic;signal count:integer range 0 to25000000;signal count_1:integer range 0 to 25000000;signal count_2:integer range 0 to 25000000;signal count_3:integer range 0 to 25000000;signal count_4:integer range 0 to 25000000;signal count_5:integer range 0 to 25000000;signal count_6:integer range 0 to 25000000;signal ys1s:integer range 0 to 50000000;signal jia1:integer range 0 to 7; beginprocessbeginwait until in50m='1'; count<=count+1;if count=95419 then count<=0;in1<=not in1;end if;end process;processbeginwait until in50m='1'; count_1<=count_1+1; if count_1=85034 then count_1<=0;in2<=not in2;end process;processbeginwait until in50m='1'; count_2<=count_2+1; if count_2=75757 then count_2<=0;in3<=not in3;end if;end process;processbeginwait until in50m='1'; count_3<=count_3+1; if count_3=71633 then count_3<=0;in4<=not in4; end if;end process;process beginwait until in50m='1'; count_4<=count_4+1; if count_4=63775 then count_4<=0;in5<=not in5;end process;processbeginwait until in50m='1'; count_5<=count_5+1;if count_5=56818 then count_5<=0;in6<=not in6;end if;end process;processbeginwait until in50m='1';count_6<=count_6+1; if count_6=50607 then count_6<=0;in7<=not in7;end if;end process;processbeginwait until in50m='1'; ys1s<=ys1s+1; if ys1s=50000000 then ys1s<=0; jia1<=jia1+1;end if;if jia1=0 thena<=in1;end if;if jia1=1 thena<=in2;end if;if jia1=2 thena<=in3; end if;if jia1=3 then a<=in4;end if;if jia1=4 then a<=in5;end if;if jia1=5 then a<=in6;end if;if jia1=6 then a<=in7;end if;end process; end;。