Cadence下原理图的检查,网表的生成处理

原理图电气检查及报表的生成

1 产生ERC表

2 网络表 3 元件列表

4 工程层次结构列表

报表

SCH除了可生成原理图以外,将原理

图转化成各种报表文件也是它的一个重要

内容。报表相当于原理图的档案,它存放

的是原引脚之间的连接

情况等。

1 ERC表

一、ERC表的作用

3

元件列表

元件列表主要用于整理一个电路或一个项目文件中的所有

元件。它主要包括元件的名称、标注、封装等内容。 生成原理图元件列表的基本步骤为: 方法一:

( 1 ) 打 开 原 理 图 文 件 , 执 行 菜 单 命 令 “ Report\Bill of Materials”。

(2)执行菜单命令后,会出现如下图1所示的对话框。用鼠标 左键单击图中的Report按钮,系统又将弹出如图2所示的对话 框。

后面的Report Mode栏中列出了对应的报告类型,共有 一下4种报告类型: Fatal error:重大错误; Error:错误;

Warning:警告;

No Report:不报告(即无错误)。

2、Connection Matrix标签页如下图所示,主要用 于设置检测规则。

三、检查结果报告 当设置好检查规则后就可以对原理图进行检查。Protel 中的电气检查是通过编译项目实现的。 编译项目的操作步骤如下: (1)打开需要编译的项目,然后选择Project\compile PCB Project命令。 (2)当项目被编译时,任何已经启动的错误均将显示在设计 窗口的message面板中,如下图所示。 (3)若电路绘制正确,message面板应该是空白的。如果有错 误报告,则可根据给出的错误检查电路并修正。

5、总线标号格式错误:

【免费下载】cadence生成网络表时出现如下错误解决办法

U(ZE0B5L5b%X;n4g Allegro对一些字符[例如"空格","小数点"等等]很在意,可以参阅相关文档的描述.(3)Error Illegal character "Dot(.)" found in "PCB Footprint"#1 Error [ALG0081] Illegal character "Dot(.)" found in "PCB Footprint" property for componen t instance C255: PG16_AC97, PG16_AC97 (226.06, 132.08) .封装命名不能包含“.”(4)Error Illegal character "Forward Slash(/)" found in "PCB Footprint" property#1 Error [ALG0081] Illegal character "Forward Slash(/)" found in "PCB Footprint" property for component instance C255: PG16_AC97, PG16_AC97 (226.06, 132.08) .#2 Error [ALG0081] Illegal character "Forward Slash(/)" found in "PCB Footprint" property for component instance D3: PG01_LED&Switch&7-Segment Disp, PG01_LED&Switch&7-Segment Disp (93.98, 33.02) .#3 Error [ALG0081] Illegal character "Forward Slash(/)" found in "PCB Footprint" property for component instance C245: PG16_AC97, PG16_AC97 (205.74, 35.56) .封装命名不能包含“/”(5)比较隐藏的排除法Loading... E:\FPGA\SCH\allegro/pstchip.dat#34 WARNING(SPCODD-34): Expected ';' character on line 5308.Check the name and value syntax for invalid characters in theprimitive definition before the line number.ERROR(SPCODD-47): File ./allegro/pstchip.dat could not be loaded, and the pac kaging operation did not complete. Check the pxl.log file for the errors causing this situ ation and package the design again.#53 ERROR(SPCODD-53): Packaging cannot be completed because packaging has enc ountered a null object ID. The design may not have been saved correctly. Save the sc hematic and rerun packaging.#187 Error [ALG0036] Unable to read logical netlist data.Exiting... "D:\Cadence\SPB_16.2\tools\capture\pstswp.exe" -pst -d "E:\FPGA\SCH\motherb oard.dsn" -n "E:\FPGA\SCH\allegro" -c "D:\Cadence\SPB_16.2\tools\capture\allegro.cfg" -v 3 -j "PCB Footprint"*** Done*******掌握排错方法,查找文件pstchip.dat,第on line 5308 看看错误,便可以解决(6)封装命名中不能包含“小数点”、“/”、“空格”,把空格换成下划线或删除,可以解决********************************************************************************** Netlisting the design*********************************************************************************Design Name:E:\FPGA\SCH\basicboard.dsnNetlist Directory:E:\FPGA\SCH\allegroConfiguration File:D:\Cadence\SPB_16.2\tools\capture\allegro.cfgSpawning... "D:\Cadence\SPB_16.2\tools\capture\pstswp.exe" -pst -d "E:\FPGA\SCH\basic board.dsn" -n "E:\FPGA\SCH\allegro" -c "D:\Cadence\SPB_16.2\tools\capture\allegro.cfg" -v 3 -j "PCB Footprint"#1 Error [ALG0081] Illegal character "White space" found in "PCB Footprint" property f or component instance MG2: Basic, PG06_Stepmotor (180.34, 83.82) .#2 Error [ALG0081] Illegal character "White space" found in "PCB Footprint" property f or component instance ISO1: Basic, PG05_DC Motor (134.62, 40.64) .#3 Info: PCB Editor does not support Dots(.), Forward Slash(/) and White space in foot print names. The supported characters include Alphabets, Numerics, Underscore(_) and Hyphen(-).#4 Aborting Netlisting... Please correct the above errors and retry.Exiting... "D:\Cadence\SPB_16.2\tools\capture\pstswp.exe" -pst -d "E:\FPGA\SCH\basicboa rd.dsn" -n "E:\FPGA\SCH\allegro" -c "D:\Cadence\SPB_16.2\tools\capture\allegro.cfg" -v 3 -j "PCB Footprint"*** Done ***封装命名中不能包含“小数点”、“/”、“空格”,把空格换成下划线或删除,可以解决(7)Warning#11 Warning [ALG0051] Pin "GND" is renamed to "GND#A6" after substituting illegal ch aracters in Package XC3S1400A-4FG676-C_0FF , U1A: SCHEMATIC1, PG01_FPGACO NFIG (2.40, 3.10).#12 Warning [ALG0051] Pin "GND" is renamed to "GND#A11" after substituting illegal c haracters in Package XC3S1400A-4FG676-C_0FF , U1A: SCHEMATIC1, PG01_FPGAC ONFIG (2.40, 3.10).#13 Warning [ALG0051] Pin "GND" is renamed to "GND#A1" after substituting illegal ch aracters in Package XC3S1400A-4FG676-C_0FF , U1A: SCHEMATIC1, PG01_FPGACO NFIG (2.40, 3.10).#14 Warning [ALG0051] Pin "GND" is renamed to "GND#W8" after substituting illegal c haracters in Package XC3S1400A-4FG676-C_0FF , U1A: SCHEMATIC1, PG01_FPGAC ONFIG (2.40, 3.10).这条警告信息,在命名规范的前提下就不考虑这个警告了。

cadence生成网络表时出现如下错误解决办法

U(ZE0B5L5b%X;n4g Allegro对一些字符[例如"空格","小数点"等等]很在意,可以参阅相关文档的描述.(3)Error Illegal character "Dot(.)" found in "PCB Footprint"#1 Error [ALG0081] Illegal character "Dot(.)" found in "PCB Footprint" property for componen t instance C255: PG16_AC97, PG16_AC97 (226.06, 132.08) .封装命名不能包含“.”(4)Error Illegal character "Forward Slash(/)" found in "PCB Footprint" property#1 Error [ALG0081] Illegal character "Forward Slash(/)" found in "PCB Footprint" property for component instance C255: PG16_AC97, PG16_AC97 (226.06, 132.08) .#2 Error [ALG0081] Illegal character "Forward Slash(/)" found in "PCB Footprint" property for component instance D3: PG01_LED&Switch&7-Segment Disp, PG01_LED&Switch&7-Segment Dis p (93.98, 33.02) .#3 Error [ALG0081] Illegal character "Forward Slash(/)" found in "PCB Footprint" property for component instance C245: PG16_AC97, PG16_AC97 (205.74, 35.56) .封装命名不能包含“/”(5)比较隐藏的排除法Loading... E:\FPGA\SCH\allegro/pstchip.dat#34 WARNING(SPCODD-34): Expected ';' character on line 5308.Check the name and value syntax for invalid characters in theprimitive definition before the line number.ERROR(SPCODD-47): File ./allegro/pstchip.dat could not be loaded, and the pac kaging operation did not complete. Check the pxl.log file for the errors causing this situ ation and package the design again.#53 ERROR(SPCODD-53): Packaging cannot be completed because packaging has enc ountered a null object ID. The design may not have been saved correctly. Save the sc hematic and rerun packaging.#187 Error [ALG0036] Unable to read logical netlist data.Exiting... "D:\Cadence\SPB_16.2\tools\capture\pstswp.exe" -pst -d "E:\FPGA\SCH\motherb oard.dsn" -n "E:\FPGA\SCH\allegro" -c "D:\Cadence\SPB_16.2\tools\capture\allegro.cfg" -v 3 -j "PCB Footprint"*** Done*******掌握排错方法,查找文件pstchip.dat,第on line 5308 看看错误,便可以解决(6)封装命名中不能包含“小数点”、“/”、“空格”,把空格换成下划线或删除,可以解决********************************************************************************** Netlisting the design*********************************************************************************Design Name:E:\FPGA\SCH\basicboard.dsnNetlist Directory:E:\FPGA\SCH\allegroConfiguration File:D:\Cadence\SPB_16.2\tools\capture\allegro.cfgSpawning... "D:\Cadence\SPB_16.2\tools\capture\pstswp.exe" -pst -d "E:\FPGA\SCH\basic board.dsn" -n "E:\FPGA\SCH\allegro" -c "D:\Cadence\SPB_16.2\tools\capture\allegro.cfg" -v 3 -j "PCB Footprint"#1 Error [ALG0081] Illegal character "White space" found in "PCB Footprint" property f or component instance MG2: Basic, PG06_Stepmotor (180.34, 83.82) .#2 Error [ALG0081] Illegal character "White space" found in "PCB Footprint" property f or component instance ISO1: Basic, PG05_DC Motor (134.62, 40.64) .#3 Info: PCB Editor does not support Dots(.), Forward Slash(/) and White space in foot print names. The supported characters include Alphabets, Numerics, Underscore(_) and Hyphen(-).#4 Aborting Netlisting... Please correct the above errors and retry.Exiting... "D:\Cadence\SPB_16.2\tools\capture\pstswp.exe" -pst -d "E:\FPGA\SCH\basicboa rd.dsn" -n "E:\FPGA\SCH\allegro" -c "D:\Cadence\SPB_16.2\tools\capture\allegro.cfg" -v 3 -j "PCB Footprint"*** Done ***封装命名中不能包含“小数点”、“/”、“空格”,把空格换成下划线或删除,可以解决(7)Warning#11 Warning [ALG0051] Pin "GND" is renamed to "GND#A6" after substituting illegal ch aracters in Package XC3S1400A-4FG676-C_0FF , U1A: SCHEMATIC1, PG01_FPGACO NFIG (2.40, 3.10).#12 Warning [ALG0051] Pin "GND" is renamed to "GND#A11" after substituting illegal c haracters in Package XC3S1400A-4FG676-C_0FF , U1A: SCHEMATIC1, PG01_FPGAC ONFIG (2.40, 3.10).#13 Warning [ALG0051] Pin "GND" is renamed to "GND#A1" after substituting illegal ch aracters in Package XC3S1400A-4FG676-C_0FF , U1A: SCHEMATIC1, PG01_FPGACO NFIG (2.40, 3.10).#14 Warning [ALG0051] Pin "GND" is renamed to "GND#W8" after substituting illegal c haracters in Package XC3S1400A-4FG676-C_0FF , U1A: SCHEMATIC1, PG01_FPGAC ONFIG (2.40, 3.10).这条警告信息,在命名规范的前提下就不考虑这个警告了。

cadence allegro pcb layout详细教程

cadence allegro pcb layout详细教程

本文为大家带来cadence allegro pcb layout详细教程。

一、用Design Entry CIS(Capture)设计原理图1、创建工程file--》new--》project ;输入工程名称,指定工程放置路径;

2、设置操作环境OpTIons--》Preferencses:颜色:colors/Print

格子:Grid Display

杂项:Miscellaneous

常取默认值

3、配置设计图纸:设定模板:OpTIons--》Design Template:(应用于新图)

设定当前图纸OpTIons--》SchemaTIc Page Properities

4、创建元件及元件库File--》New Library --》选择要添加到的工程

Design --》New Part.(或者在Library处右击选择New Part)

(1)Homogeneous:复合封装元件中(多个元件图组成时)每个元件图都一样(default 适用于标准逻辑)

(2)Heterogeneous:复合封装元件(多个元件图组成时)中使用不一样的元件图(较适用于大元件)

一个封装下多个元件图,以View ext part(previous part)切换视图元器件封装:

(1)place --》line画线,用来画封装外形;

(2)place--》pin放置管脚;放单个或多个;

不同类型的管脚选择的type不同;

5、绘制原理图(1)放置电器。

protel原理图检查及网络表、报告文件生成

第三单元原理图检查及网络表、报告文件生成3.1 第1题【操作要求】1.检查原理图打开C:\信息产业部\Unit3\Y3-01.sch原理图文件,按表3-01设置电气规则校验(检查),对该原理图进行电气规则检查。

表3-01选项是否选中网络名重复选中未连接的网络标号选中未连接的电源符号选中零件标号重复选中总线标号格式错误选中产生报告文件选中添加错误标记选中●将电气规则检查文件保存到考生文件夹中,命名为JG3-01.erc。

●根据错误标记和生成的报告文件改正原理图中的错误(不能删除元件、网络标号、端口等),直到无错误为止。

●重新标注(标注模式任意)修改后的无错的原理图文件。

●将标注后的原理图文件保存到考生文件夹中,命名为JG3-01.sch。

2.生成网络表依据原理图JG3-01.sch生成格式为protel的网络表,将生成的网络表文件保存到考生文件夹中,命名为。

3.生成材料清单文件依据原理图JG3-01.sch生成材料清单文件,将生成的材料清单文件保存到考生文件夹中,命名为JG3-01.BOM。

3.2 第2题【操作要求】1.检查原理图打开C:\信息产业部\Unit3\Y3-02.sch原理图文件,按表3-02设置电气规则校验(检查),对该原理图进行电气规则检查。

表3-02选项是否选中网络名重复选中未连接的网络标号选中未连接的电源符号选中零件标号重复选中总线标号格式错误选中产生报告文件选中添加错误标记选中●将电气规则检查文件保存到考生文件夹中,命名为JG3-02.erc。

●根据错误标记和生成的报告文件改正原理图中的错误(不能删除元件、网络标号、端口等),直到无错误为止。

●重新标注(标注模式任意)修改后的无错的原理图文件。

●将标注后的原理图文件保存到考生文件夹中,命名为JG3-02.sch。

2.生成网络表依据原理图JG3-02.sch生成格式为protel的网络表,将生成的网络表文件保存到考生文件夹中,命名为。

学习笔记-candence16.6-原理图部分

学习笔记目录一、原理图设计部分1.针对原理图界面的操作2.对原理图进行编辑3.对制作原件的编辑4.生成网表5.生成清单和打印设置针对原理图界面的操作Design entry CIS:进行板级设计时用来画原理图的。

PCB Editor:cadence进行布局布线的软件。

Cadence product choices-----OrCAD capture CIS进行原理图页面个性化设置(整体设置)Options-->design template..(即原理图页面模板). 进行原理图页面个性化设置(单页设置)Options-->schematic page propertise..5. .drn文件是建立的工程的数据库文件,包括电路原理图(schematic)、元件库(design cache)、输出文件(outputs)。

6.工具栏的显示、隐藏和自定义View-->toolbar7.更改原理图背景颜色Option-->Preferences..8.原理图的放大、缩小快捷键i、o。

View-->zoom-->in/out按住ctrl,滚动鼠标。

对原理图进行编辑旋转元器件:快捷键R画线:places -->wire快捷键W任意角度画线:画线时按住shift网络节点:junction删除网络节点:按住“s”键,鼠标左键单击节点,此时出现一个方框,这时按“delete”键,即可删除。

浏览命令browse整体浏览:选中.drn文件Edit-->browse-->parts/nets......点击原件标号可以直接定位到该原件。

对制作原件的编辑1.批量放置管脚:place--pin array2.批量修改管教:选中需要修改的管脚---右键---editproperties..3.查看元件的属性:options-->part propertise..Options-->edit part propertise..(可以改写footprint)相同的不同的4.查看一个package里的几个部分:View--packageView--package propertisesCtrl+B:package的上一级Ctrl+N:package的下一级5.画线时任意起点和终点画线:options--->prefences..-->grid display---取消pointer snap to grid6.按组编号:Tool-->annotate..四、生成网表Netlist---PCB Editor生成清单和打印设置TOOLS---Bill OF materials针对allegro原理图界面的操作allegro的5种应用模式(application mode)general edit 普通模式Placement edit 排零件模式。

Cadence常用技巧、网表导入PADS、CAD板框导入PADS

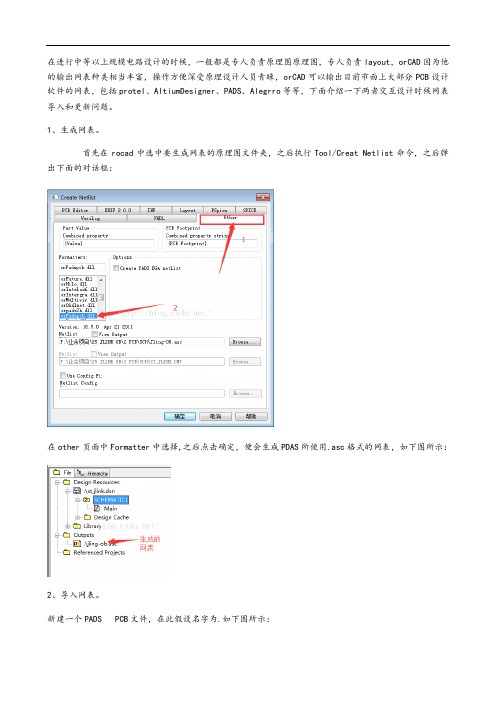

在进行中等以上规模电路设计的时候,一般都是专人负责原理图原理图,专人负责layout,orCAD因为他的输出网表种类相当丰富,操作方便深受原理设计人员青睐,orCAD可以输出目前市面上大部分PCB设计软件的网表,包括protel、AltiumDesigner、PADS、Alegrro等等,下面介绍一下两者交互设计时候网表导入和更新问题。

1、生成网表。

首先在rocad中选中要生成网表的原理图文件夹,之后执行Tool/Creat Netlist命令,之后弹出下面的对话框:在other页面中Formatter中选择,之后点击确定,便会生成PDAS所使用.asc格式的网表,如下图所示:2、导入网表。

新建一个PADS PCB文件,在此假设名字为.如下图所示:新建文件之后,首先要有自己的PCB封装库,并且设置好自己的PCB封装库路径,设置PCB封装库路径发方法如下:工具/选项之后弹出来如下界面:点击右侧的库列表文件夹,如下图所示,之后选择自己的PCB封装库所在位置:这样自己的封装库路径设置完成了。

之后可以在PADS layout软件中导入网表了。

打开刚才创建的文件,执行"文件/导入"命令,打开刚才用orcad生成的.asc文件。

之后会弹出一个检验文本,提示所有的错误和警告,如下图所示:之后还会弹出一个警告对话框,可以忽略之。

之后所有的原件就导入进来了,如下图所示,此时元件是堆放在一起的:执行命令:“工具/分散元器件”,之后元器件被分散开来,如下图所示:这样,就完成了PCB的导入,之后可以进行布线工作。

3、更新原理图中修改的网表。

在PCB布线的时候可能会修改原理图中的部分器件或者连线,这时候就要进行网表更新。

步骤如下:a、更改好原理图之后,重新生成网表,然后新建一个空的PCB文件,给这个pcb文件起一个名字(名字随便起),这里就叫做.b、打开文件,执行"文件/导入"命令,导入新生成的.asc网表,之后关闭。

Capture CIS原理图设计后处理

1. Tools

Design Rules check,打开如下对话框:

Scope:针对设计中的全部还是选择的部分做DRC。 Mode:针对样本原型还是引用部分做DRC Action:

① DRC检查,在做运行DRC前,会把DRC Mark删除, 再运行DRC,并重新生DRC MARK及报表。

Page 2

主要内容:

1. 元器件编号(Annotate、Back-annotate)。 2. 设计规则检查(DRC)。 3. 元器件属性参数更新。 4. 生成网表。 5. 元器件信息统计、BOM输出。

Page 3

1.元器件编号

元器件编号的原则:

为了减少PCB布

局的工作量,不能对

是新设计吗?

1.元器件编号

元器件编号反标:Back Annotate:

这个功能是通过swap文件对元件编号或引线编号进行重排。 Swap文件可以手工按一定格式编辑或者由第三方面软件生成, 我们目前用到的是allegro软件,其中有在做管脚交换的时候要用 到这个功能,这里不详细叙述,有兴趣可以查看, 《OrCAD Capture CIS 9 实用教程》及相关资料。

Cadence原理图设计后处理

摘要:

原理图绘制好之后,最终要生成网表,以便能顺利导入PCB设计软件, 绘制电路板。那么如何保证生成的网表是正确的呢,网络连接是否有遗漏 呢,封装信是否正确认呢,因此我们非常有必要在原理图绘制好之后做一 些处理,这就是本文接下来要讲的内容,结合公司情况,有些步骤原理图 绘制人员是必需要做的,本文引用了《OrCAD Capture CIS 9 实用教程》 里的一些内容,所用软件是CADENCE16.3,部分检查项将归到 CADENCE原理图设计规范中去。

cadence原理图设计实例教程

器件放置

• 也可以按下步骤放置uA741:

➢ 执行P1ace/Part命令 ➢ 在 Part中输“ *741* ” , ➢ 点击Part Search, ➢ 点击Begin Search, ➢ 在Library 库中寻找到

uA741/opamp.olb ➢ 单击“OK” ➢ 执行前面的步骤,单击

“OK”,放置器件,断开放 置

放置电容符号

➢ 执行P1ace/Part命令 ➢ 在 “Libraries”列表框中选

择“ANALOG” ➢ 在 “Part”列表框中选择

“ C” ➢ 单击“OK” ➢ 将电阻C移至合适位置,

(按键盘中的R键,器件旋 转)按鼠标左键放置 ➢ 按ESC键(或鼠标右键点 end mode)结束绘制元器

器件封装调用

在Link Footprint to Component 栏内点OK,对于没有 定义的管脚封装图,出现MAXECO提示说明,确定

器件封装调用

在Link Footprint to Component 栏内点OK,对于没有定义的管脚封 装图, 点Link existing footprint to component来查找连接封装。

Place net name

放置分页图纸间的接口

原理图绘制

(二) 原理图绘制

以声控开关为例(电源是直流12V,负载为发光二极管)见下 图:

放置集成块运放uA741

• 执行P1ace/Part命令 • 在 “Libraries”列表

框中选择“OPAMP” 库 • 在 “Part”列表框中 选择“uA741” • 单击“OK” • 将集成块移至合适位 置,按鼠标左键 • 按ESC键或鼠标右键点 end mode以结束绘 制元器件状态

Cadence原理图绘制流程

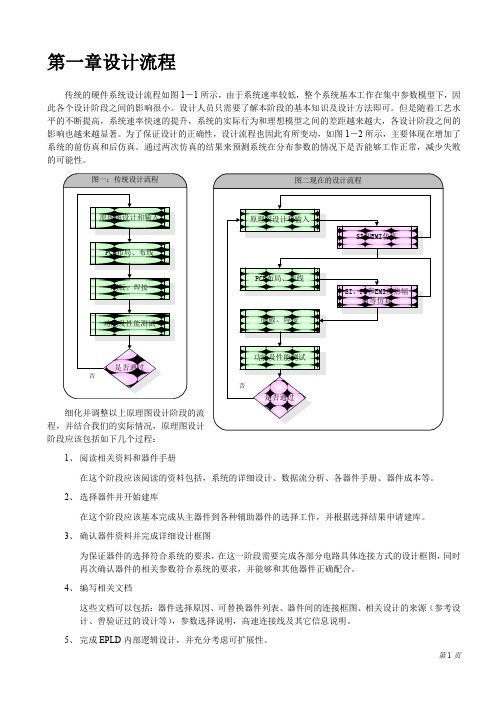

第一章设计流程传统的硬件系统设计流程如图1-1所示,由于系统速率较低,整个系统基本工作在集中参数模型下,因此各个设计阶段之间的影响很小。

设计人员只需要了解本阶段的基本知识及设计方法即可。

但是随着工艺水平的不断提高,系统速率快速的提升,系统的实际行为和理想模型之间的差距越来越大,各设计阶段之间的影响也越来越显著。

为了保证设计的正确性,设计流程也因此有所变动,如图1-2所示,主要体现在增加了系统的前仿真和后仿真。

通过两次仿真的结果来预测系统在分布参数的情况下是否能够工作正常,减少失败的可能性。

细化并调整以上原理图设计阶段的流程,并结合我们的实际情况,原理图设计阶段应该包括如下几个过程:1、 阅读相关资料和器件手册在这个阶段应该阅读的资料包括,系统的详细设计、数据流分析、各器件手册、器件成本等。

2、 选择器件并开始建库在这个阶段应该基本完成从主器件到各种辅助器件的选择工作,并根据选择结果申请建库。

3、 确认器件资料并完成详细设计框图为保证器件的选择符合系统的要求,在这一阶段需要完成各部分电路具体连接方式的设计框图,同时再次确认器件的相关参数符合系统的要求,并能够和其他器件正确配合。

4、 编写相关文档这些文档可以包括:器件选择原因、可替换器件列表、器件间的连接框图、相关设计的来源(参考设计、曾验证过的设计等),参数选择说明,高速连接线及其它信息说明。

5、 完成EPLD 内部逻辑设计,并充分考虑可扩展性。

在编写相关文档的的同时需要完成EPLD内部逻辑的设计,确定器件容量及连接方式可行。

6、使用Concept-HDL绘制原理图7、检查原理图及相关文档确保其一致性。

以上流程中并未包括前仿真的相关内容,在设计中可以根据实际情况,有选择的对部分重要连线作相关仿真,也可以根据I/O的阻抗,上升下降沿变化规律等信息简单分析判断。

此流程中的各部分具体要求、注意事项、相关经验和技巧有待进一步完善。

第二章Concept-HDL的使用运行Concept-HDL后将会出现类似如下界面。

Cadence网络表总结

Cadence 网络表总结用Capture CIS 画原理图后结果发现工程文件丢失。

不知道是我误删除了还是由于Capture CIS 的bug 问题。

但此时我已将网络表导入了Allegro ,并摆放了一部分元件。

如果重新画原理图重新布局PCB 比较麻烦,于是就按照以前打印的PDF 原理图布线。

可是当布到最后却发现了问题,我想修改原理图的设计时却没有办法了。

比如像下面这图里我想把接地引脚换成数字地(Dgnd ),以前接的是模拟地(Agnd )平时更改一下原理图就可以了,但原理图丢失,这时候就只能去修改cadence 网络表来实现目标。

cadence 网络表包括三个文件:pstchip.dat ,pstxprt.dat ,pstxnet.dat打开之后就知道pstchip.dat 是描述元件的引脚等信息的。

pstxprt.dat 是描述封装信息的,就是指该封装长什么样。

pstxnet.dat 就是描述各个元件之间的网络联系,即把所有的网络表和元件都给列了出来。

想将上面的元件地从Agnd 改到Dgnd ,需要将pstxnet.dat 打开,在里面的NET_NAME'AGND''@ODDETECT.ODDETECT(SCH_1):AGND':C_SIGNAL='@oddetect.oddetect(sch_1):agnd';里找到对应的C46 ,C47,C45 ,C48 的NODE_NAME C47 2'@ODDETECT.ODDETECT(SCH_1):INS229657@DISCR ETE.CAP NP.NORMAL(CHIPS)':'2':;厶・,NODE_NAME C46 2'@ODDETECT.ODDETECT(SCH_1):INS229641@DISCRETE.CAP.NORMAL(CHIPS)':IQI.・厶・,NODE_NAME C48 2'@ODDETECT.ODDETECT(SCH_1):INS546266@DISCRETE.CAP.NORMAL(CHIPS)':'2':;厶・,NODE_NAME C45 2'@ODDETECT.ODDETECT(SCH_1):INS551150@DISCRETE.CAP.NORMAL(CHIPS)':'2':;厶・,剪切至'DGND''@ODDETECT.ODDETECT(SCH_1):DGND':C_SIGNAL='@oddetect.oddetect(sch_1):dgnd'; ................... 这时再重新导入网络表,就就会发现在PCB 里已经更改过了电气的连接关系。

cadence生成网络表时出现如下错误解决办法

U(ZE0B5L5b%X;n4g Allegro对一些字符[例如"空格","小数点"等等]很在意,可以参阅相关文档的描述.(3)Error Illegal character "Dot(.)" found in "PCB Footprint"#1 Error [ALG0081] Illegal character "Dot(.)" found in "PCB Footprint" property for componen t instance C255: PG16_AC97, PG16_AC97 (226.06, 132.08) .封装命名不能包含“.”(4)Error Illegal character "Forward Slash(/)" found in "PCB Footprint" property#1 Error [ALG0081] Illegal character "Forward Slash(/)" found in "PCB Footprint" property for component instance C255: PG16_AC97, PG16_AC97 (226.06, 132.08) .#2 Error [ALG0081] Illegal character "Forward Slash(/)" found in "PCB Footprint" property for component instance D3: PG01_LED&Switch&7-Segment Disp, PG01_LED&Switch&7-Segment Dis p (93.98, 33.02) .#3 Error [ALG0081] Illegal character "Forward Slash(/)" found in "PCB Footprint" property for component instance C245: PG16_AC97, PG16_AC97 (205.74, 35.56) .封装命名不能包含“/”(5)比较隐藏的排除法Loading... E:\FPGA\SCH\allegro/pstchip.dat#34 WARNING(SPCODD-34): Expected ';' character on line 5308.Check the name and value syntax for invalid characters in theprimitive definition before the line number.ERROR(SPCODD-47): File ./allegro/pstchip.dat could not be loaded, and the pac kaging operation did not complete. Check the pxl.log file for the errors causing this situ ation and package the design again.#53 ERROR(SPCODD-53): Packaging cannot be completed because packaging has enc ountered a null object ID. The design may not have been saved correctly. Save the sc hematic and rerun packaging.#187 Error [ALG0036] Unable to read logical netlist data.Exiting... "D:\Cadence\SPB_16.2\tools\capture\pstswp.exe" -pst -d "E:\FPGA\SCH\motherb oard.dsn" -n "E:\FPGA\SCH\allegro" -c "D:\Cadence\SPB_16.2\tools\capture\allegro.cfg" -v 3 -j "PCB Footprint"*** Done*******掌握排错方法,查找文件pstchip.dat,第on line 5308 看看错误,便可以解决(6)封装命名中不能包含“小数点”、“/”、“空格”,把空格换成下划线或删除,可以解决********************************************************************************** Netlisting the design*********************************************************************************Design Name:E:\FPGA\SCH\basicboard.dsnNetlist Directory:E:\FPGA\SCH\allegroConfiguration File:D:\Cadence\SPB_16.2\tools\capture\allegro.cfgSpawning... "D:\Cadence\SPB_16.2\tools\capture\pstswp.exe" -pst -d "E:\FPGA\SCH\basic board.dsn" -n "E:\FPGA\SCH\allegro" -c "D:\Cadence\SPB_16.2\tools\capture\allegro.cfg" -v 3 -j "PCB Footprint"#1 Error [ALG0081] Illegal character "White space" found in "PCB Footprint" property f or component instance MG2: Basic, PG06_Stepmotor (180.34, 83.82) .#2 Error [ALG0081] Illegal character "White space" found in "PCB Footprint" property f or component instance ISO1: Basic, PG05_DC Motor (134.62, 40.64) .#3 Info: PCB Editor does not support Dots(.), Forward Slash(/) and White space in foot print names. The supported characters include Alphabets, Numerics, Underscore(_) and Hyphen(-).#4 Aborting Netlisting... Please correct the above errors and retry.Exiting... "D:\Cadence\SPB_16.2\tools\capture\pstswp.exe" -pst -d "E:\FPGA\SCH\basicboa rd.dsn" -n "E:\FPGA\SCH\allegro" -c "D:\Cadence\SPB_16.2\tools\capture\allegro.cfg" -v 3 -j "PCB Footprint"*** Done ***封装命名中不能包含“小数点”、“/”、“空格”,把空格换成下划线或删除,可以解决(7)Warning#11 Warning [ALG0051] Pin "GND" is renamed to "GND#A6" after substituting illegal ch aracters in Package XC3S1400A-4FG676-C_0FF , U1A: SCHEMATIC1, PG01_FPGACO NFIG (2.40, 3.10).#12 Warning [ALG0051] Pin "GND" is renamed to "GND#A11" after substituting illegal c haracters in Package XC3S1400A-4FG676-C_0FF , U1A: SCHEMATIC1, PG01_FPGAC ONFIG (2.40, 3.10).#13 Warning [ALG0051] Pin "GND" is renamed to "GND#A1" after substituting illegal ch aracters in Package XC3S1400A-4FG676-C_0FF , U1A: SCHEMATIC1, PG01_FPGACO NFIG (2.40, 3.10).#14 Warning [ALG0051] Pin "GND" is renamed to "GND#W8" after substituting illegal c haracters in Package XC3S1400A-4FG676-C_0FF , U1A: SCHEMATIC1, PG01_FPGAC ONFIG (2.40, 3.10).这条警告信息,在命名规范的前提下就不考虑这个警告了。

原理图电气规则检查及报表

2.“Rule Matrix(电气法则测试矩阵)”标签页 用鼠标左键单击“Setup Electrical Rule Check”对话框的“Rule Matrix”标签,即可进入“Rule Matrix”标签页,如下图所示。

可以设置“Connected Pin/Sheet Entry/Port Rule Matrix”(有连接关系的管脚、方块电路的I/O端口和电路的I/O端口)的矩阵规则。

8.2.3 生成交叉参考元件列表 1)执行“File\ Open”命令,打开需要生成交叉参考元件列表的项目文件。 2)执行“Reports\Cross Reference”菜单命令。 3)执行上一步操作后,系统将自动进入到文本编辑器,并产生后缀为.XRF的交叉参考元件列表。下图所示为“振荡器和积分器.sch”生成的交叉参考元件列表。 4)执行“File\Save”命令,将生成的交叉参考元件列表文件存盘。

网络表的格式 ⑴ 元件的声明格式 元件的声明主要有以下几个特点: ●元件的声明以“[”开始,以“]”结束,其内容包括在两个方括号之间。 ●网络经过的每一个元件都要有相应的声明。 ●元件声明的内容主要有元件的标号、元件的封装名称和元件的注释文字三部分。 下面是一个元件的声明的例子: [ 元件声明开始 C3 元件的标号 RAD0.1 元件的封装名称 0.01 元件的注释 ] 元件声明结束 ⑵ 网络的定义格式 网络的定义有以下几个要求: ●网络的定义以“(”开始,以“)”结尾,将其内容包括在两个圆括号之间。 ●网络定义中,定义该网络的名称。 ●网络名称定义后,列出连接该网络的各个端点。

完成参数设置后,系统自动进入表格编辑器,同时形成后缀为.XLS的元件列表,下图表示电路原理图“zdq.sch”生成的元件材料表文件。 选择“File”菜单,然后在弹出了下拉菜单中选择“Save”选项,将生成的元件材料表文件存盘保存。

《电子线路CAD实用教程》第4章 原理图的检查和常用报表的生成

课 堂 演 示

电子线路CAD实用教程

邓

奕 主编

华中科技大学出版社

4.3 生成层次表

层次表记录由多张绘图页组成的层次原理图的 层次结构数据,其输出的结果为ASCLL文件,文件 的存盘名为(*.rep),生成原理图的层次表操作步 骤如下: (1)打开已经绘制的原理图; ( 2 ) 然 后 执 行 Report 报 告 中 的 Design Hierarchy命令,系统将会生成该原理图的层次关系 表。 在层次表文件中,可以看到原理图的层次关系。

电子线路CAD实用教程 邓 奕 主编 华中科技大学出版社

4.1 检查电路原理图

1、检查元件序号 电路图绘制完成后,元件的序号一般较为混乱,尤 其在原理图很复杂的情况下,需要对元件序号进行一定 的编排和检查,以免元件序号出现重复或遗漏的现象。 元件的重新排序有以下两种方法: (1)手工修正。首先仔细检查电路图,查出不规范的 标志,然后逐一修改。这种方法虽然简单,但是效率很 低。 ( 2 ) 自 动 修 正 。 可 以 通 过 菜 单 命 令 【Tools】/ 【Annotate】来实现。此时系统自动弹注释设计对话框。

电子线路CAD实用教程

邓

奕 主编

华中科技大学出版社

【实例4-4】生成元件采购列表(P77)

课 堂 演 示

电子线路CAD实用教程 邓 奕 主编 华中科技大学出版社

4.5 生成元件引脚列表

元件引脚列表用于列出所选元件的引脚信息, 如元件的引脚数、元件引脚名称以及元件引脚的相 关网络等信息。 生成元件引脚列表的方法: (1)用鼠标选取某元件,此时被选取元件出现 黄色的边框,说明元件被选中。 (2)选择Reports报告中的Selected Pins 命令, 系统将生成该元件的引脚列表,出现该元件的所有 引脚相关信息。

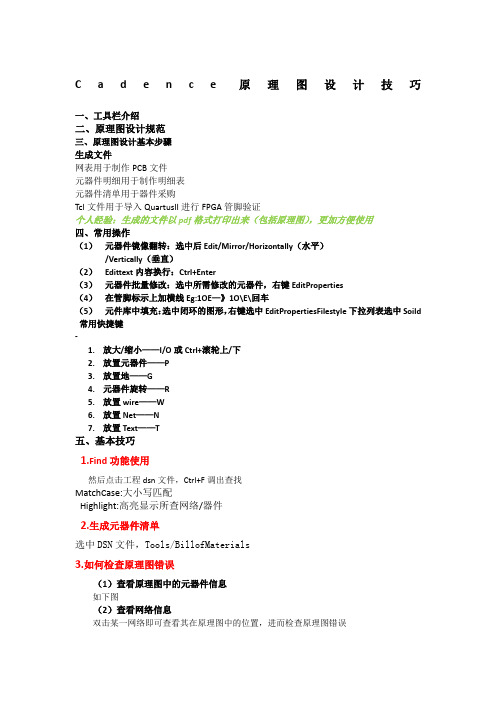

Cadence原理图设计技巧

C a d e n c e原理图设计技巧一、工具栏介绍二、原理图设计规范三、原理图设计基本步骤生成文件网表用于制作PCB文件元器件明细用于制作明细表元器件清单用于器件采购Tcl文件用于导入QuartusII进行FPGA管脚验证个人经验:生成的文件以pdf格式打印出来(包括原理图),更加方便使用四、常用操作(1)元器件镜像翻转:选中后Edit/Mirror/Horizontally(水平)/Vertically(垂直)(2)Edittext内容换行:Ctrl+Enter(3)元器件批量修改:选中所需修改的元器件,右键EditProperties(4)在管脚标示上加横线Eg:1OE—》1O\E\回车(5)元件库中填充:选中闭环的图形,右键选中EditPropertiesFilestyle下拉列表选中Soild 常用快捷键-1.放大/缩小——I/O或Ctrl+滚轮上/下2.放置元器件——P3.放置地——G4.元器件旋转——R5.放置wire——W6.放置Net——N7.放置Text——T五、基本技巧1.Find功能使用然后点击工程dsn文件,Ctrl+F调出查找MatchCase:大小写匹配Highlight:高亮显示所查网络/器件2.生成元器件清单选中DSN文件,Tools/BillofMaterials3.如何检查原理图错误(1)查看原理图中的元器件信息如下图(2)查看网络信息双击某一网络即可查看其在原理图中的位置,进而检查原理图错误(3)DRC检查选中工程DSN文件,Tools/DesignRulesCheck4.从原理图中导出网表设置完毕之后,会在指定路径下产生pstchip.dat,pstxnet.dat,patxprt.dat文件pstchip.dat:记录的是各个封装的相关参数pstxnet.dat:记录各个器件引脚的电气连接关系patxprt.dat:记录的是各个器件对应的封装类型5.关于输出文件的打印File/Print,选中Setup进行打印设置,选中虚拟打印机,这里安装的是AdobePDF(Acrobat9.0Pro) 然后选择纸张大小、方向,确定即可。

Cadence16.3原理图输出篇

Cadence allegro 16.3原理图设计教程(输出篇)厦门大学电子实训基地严新金2011年4月26日一:添加footprint 属性1.1 单个元件添加 Footprint 属性第一种方法:直接修改1双击元件,弹出property editor 对话框2在左上角空白处右键->pivot,改变视图3修改PCB Footprint 属性第二种方法:在元件库中添加footprint 属性,更新到原理图1 打开元件库2 打开元件编辑页面3 菜单option->package property4弹出编辑属性对话框5 修改 PCB Footprint 属性,保存。

回到原理图,打开 cache 选中要编辑Footprint 的元件,右键replace cache6:弹出 replace cache 对话框,Action 中选择replace schematic part properties 复选框以及preserve Refdef 复选框。

如图1.2 批量添加Footprint 属性1 工程管理窗口中,选择某一页2 右键->Edit object properties3 打开属性编辑窗口4 用 Pivot 命令改变视图显示方式页面放大:CTRL+鼠标滚轮上推。

页面缩小:CTRL+鼠标滚轮下拉。

左键框选 Footprint 空白处5 右键单击任意一个待编辑的方框,选择 Edit6 修改属性值,OK。

单击 Property Editor 中的Apply 按钮,信息被添加到原理图中。

二自动生成位号1 对原理图通篇检查,确认电气连接正确,逻辑功能正确,电源连接正确。

2 重新进行索引编号,选.dsn 文件,tool->annotate3 弹出 annotate 对话框,各种选项如图所示,各项意义很明确。

4 确定,取消所有索引编号。

重新编号,这步 annotate 对话框中Action 中选择incremental reference update。

Cence原理图设计技巧

C e n c e原理图设计技巧集团企业公司编码:(LL3698-KKI1269-TM2483-LUI12689-ITT289-C a d e n c e原理图设计技巧一、工具栏介绍二、原理图设计规范三、原理图设计基本步骤生成文件网表用于制作PCB文件元器件明细用于制作明细表元器件清单用于器件采购Tcl文件用于导入QuartusII进行FPGA管脚验证个人经验:生成的文件以pdf格式打印出来(包括原理图),更加方便使用四、常用操作(1)元器件镜像翻转:选中后Edit/Mirror/Horizontally(水平)/Vertically(垂直)(2)Edittext内容换行:Ctrl+Enter(3)元器件批量修改:选中所需修改的元器件,右键EditProperties (4)在管脚标示上加横线Eg:1OE—》1O\E\回车(5)元件库中填充:选中闭环的图形,右键选中EditPropertiesFilestyle下拉列表选中Soild常用快捷键-1.放大/缩小——I/O或Ctrl+滚轮上/下2.放置元器件——P3.放置地——G4.元器件旋转——R5.放置wire——W6.放置Net——N7.放置Text——T五、基本技巧1.Find功能使用然后点击工程dsn文件,Ctrl+F调出查找MatchCase:大小写匹配Highlight:高亮显示所查网络/器件2.生成元器件清单选中DSN文件,Tools/BillofMaterials3.如何检查原理图错误(1)查看原理图中的元器件信息如下图(2)查看网络信息双击某一网络即可查看其在原理图中的位置,进而检查原理图错误(3)DRC检查选中工程DSN文件,Tools/DesignRulesCheck4.从原理图中导出网表设置完毕之后,会在指定路径下产生pstchip.dat,pstxnet.dat,patxprt.dat文件pstchip.dat:记录的是各个封装的相关参数pstxnet.dat:记录各个器件引脚的电气连接关系patxprt.dat:记录的是各个器件对应的封装类型5.关于输出文件的打印File/Print,选中Setup进行打印设置,选中虚拟打印机,这里安装的是AdobePDF(Acrobat9.0Pro)然后选择纸张大小、方向,确定即可。

Cadence常用技巧、网表导入PADS、CAD板框导入PADS

在进行中等以上规模电路设计的时候,一般都是专人负责原理图原理图,专人负责layout,orCAD因为他的输出网表种类相当丰富,操作方便深受原理设计人员青睐,orCAD可以输出目前市面上大部分PCB设计软件的网表,包括protel、AltiumDesigner、PADS、Alegrro等等,下面介绍一下两者交互设计时候网表导入和更新问题。

1、生成网表。

首先在rocad中选中要生成网表的原理图文件夹,之后执行Tool/Creat Netlist命令,之后弹出下面的对话框:在other页面中Formatter中选择orPadspc.dll,之后点击确定,便会生成PDAS所使用.asc格式的网表,如下图所示:2、导入网表。

新建一个PADS PCB文件,在此假设名字为Demo.pcb.如下图所示:新建文件之后,首先要有自己的PCB封装库,并且设置好自己的PCB封装库路径,设置PCB封装库路径发方法如下:工具/选项之后弹出来如下界面:点击右侧的库列表文件夹,如下图所示,之后选择自己的PCB封装库所在位置:这样自己的封装库路径设置完成了。

之后可以在PADS layout软件中导入网表了。

打开刚才创建的Demo.pcb文件,执行"文件/导入"命令,打开刚才用orcad生成的.asc文件。

之后会弹出一个检验文本,提示所有的错误和警告,如下图所示:之后还会弹出一个警告对话框,可以忽略之。

之后所有的原件就导入进来了,如下图所示,此时元件是堆放在一起的:执行命令:“工具/分散元器件”,之后元器件被分散开来,如下图所示:这样,就完成了PCB的导入,之后可以进行布线工作。

3、更新原理图中修改的网表。

在PCB布线的时候可能会修改原理图中的部分器件或者连线,这时候就要进行网表更新。

步骤如下:a、更改好原理图之后,重新生成网表,然后新建一个空的PCB文件,给这个pcb文件起一个名字(名字随便起),这里就叫做temp.pcb.b、打开temp.pcb文件,执行"文件/导入"命令,导入新生成的.asc网表,之后关闭temp.pcb。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

更改标题栏

用FileOpenProject打开上 节所建立工程。注意每页图右 下角的标题栏,右上图中是三 幅图相同的标题栏,注意图中 的红圈部分。我们做相应的修 改。 只要点击红圈中的部分我们就 可以修改该参数。 第一页修改后的情况如右下图 所示。 第二、三页在与第一页做相同 修改的情况下,还要修改右下 图中画兰圈的部分。就是所属 三页图中的第几页。

更新元件标号(一)

用FileOpenProject打开上节所建立工程。 在工程页面上用ToolsAnnotate菜单命令或用下图中红圈中的工 具栏命令来实现元件的重新编号。

更新元件标号(二)

左图是弹出的更新网络 标号菜单。注意图中的 红圈和兰圈。 要想更新元件的编号, 要先复位元件的编号到 R?或C?或U?等。即先进 行红圈操作。确定后会 在图中看到,所有的编 号都被复位。 然后再点击兰圈所圈定 的选项确定后就可以看 出器件编号被重新编过 了。

更新编号前后的对比

其中U7 U6 C150 C26 P3 P1 R141 R14

添加PCB封装(一)

左图是我们所打开工程样例的第 一页图中的部分,按住Ctrl可以 选择多个器件,然后点击鼠标右 键弹出菜单,注意左图中反色的 部分,选择此即可编辑元件的属 性。 在下面弹出的图面中,拖动下面 的滚动条,找到红圈所圈定的PCB Footprint部分,就可以添加PCB 封装了 添加方法,是选中这几个电容的 栏,然后依次输入0603,也可选 中这几栏,然后用点击鼠标右侧, 在弹出的菜单中选择Edit,再在 弹出的对话框中输入封装值。

第四讲

Cadence下原理图的检查,网 表的生成

课程简介

课程内容:.Cadence下原理图的检查,网表的生 成及其它后处理工作。 课程目的:掌握原理图检查方法,掌握网表的生 成方法及其它后处理方法。 讲座时间:30分钟

本节主要内容

后处理事宜

更改标题栏。 更新元件标号。 添加PCB封装。 DRC检查。 网表生成。 元件清按右图进行设定就可 生成元件报表清单。 下图中反色的部分就 是新生成的器件清单

元件清单的生成

右图是元件清单的 列表,以第1项为例, 第二个列的21代表 元件的数量,接下 的所属同一值的电 容编号,最后这些 电容的统一电容值。

本讲结束

画原理图的最简单方法。

原理图上元件网络线的最终确定还要 看PCB的布局,主要是看接插件、总线 驱动器件、CPLD等网络线可灵活变动 的器件在走线时的情况。

添加PCB封装(二)

添加PCB封装(三)

逐个修改,完成添加PCB封装工作。 对于不确定的封装,可先命名,最后去对应 PCB的封装库。

DRC的检查(一)

在工程图面下用Tools工具菜单下的反色的命令或用 上图中红圈中红色对号上的DRC工具按钮,进行DRC检 查。

DRC的检查(二)

右图是常用的拼接 式电路图的DRC检查 设置。如果是层次 图的话还要选择相 应的与层次图有关 的部分。 确定后即可查看输 入结果。

网络表的生成(二)

在右图中,要生成PADS 能识别的PCB网表,一 定要注意选择,首先要 选择最上面按钮的最后 一个,红色圈定的部分 Other。 然后拖动该图面中的滚 动条,如红色圈定的。 找到padspcb.dll这个 选项,点中即可。 确定后即可生成网表。

网络表的生成(三)

左图中红色所圈 定的部分就是所 产生的网表文件。 左图中兰色所圈 定的部分是以上 所做DRC检查时生 成的DRC检查文件。

DRC的检查(三)

依上图Session Log中的报错 情况,找到原理图的相应部分, 从右图可以看出,出错的部分 已经被绿圈圈住。图中ADDR24 的确没有连接网络。图中的 nOE也的确没有连接到其它图 页上。再次进行相应处理图后 DRC检查正确。

网络表的生成(一)

用Tools工具菜单下的反色部分Create Netlist命令来实现网表的生成,也可以用 上图中红圈中的图标工具按钮来生成网表。