第6章 6-3赋值语句

人教版必修3 赋值语句

思考:

x=10

y=x z=y 则x,y,z的值分别为多少?

注意(4): 辗转赋值,即先将一个数值赋给一个变量, 再将第一个变量的值赋给第二个变量…一直继续下去。

探究交流:

①:下面的程序A的输出值是多少? A=10 A=A+15 PRINT “A=” ; A END

X=Y,表示用Y的值替代变量X原先的取值。

所以“Y=X与 X=Y”的含义运行结果是不同的。 注意:⑵赋值号左右不能对换。赋值语句是将赋值 需要更完整的资源请到 新世纪教育网 号右边的表达式的值赋给赋值号左边的变量。

注意:⑶不能利用赋值语句进行代数的演算(如化简、 因式分解、解方程等)

(1)、赋值语句中的“=”的作用及应用

(2)、编程的一般步骤:先写算法,再进 行编程。 我们要养成良好的习惯,也有助于数学逻辑 思维的形成。

需要更完整的资源请到 新世纪教 育网 -

例1:交换两个变量A和B的值,并输出交 换前后的值。 程序:

INPUT A

INPUT B PRINT A,B X=A A=B B=X PRINT A,B

需要更完整的资源请到 新世纪教 育网 -

END

课堂练习:

1、写出鸡兔同笼问题的一个算法并编程。 程序框图如下: 编程如下: 开始

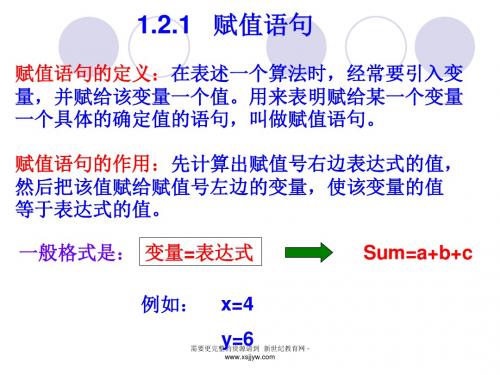

1.2.1 赋值语句

赋值语句的定义:在表述一个算法时,经常要引入变 量,并赋给该变量一个值。用来表明赋给某一个变量 一个具体的确定值的语句,叫做赋值语句。 赋值语句的作用:先计算出赋值号右边表达式的值, 然后把该值赋给赋值号左边的变量,使该变量的值 等于表达式的值。 一般格式是: 变量=表达式 例如: x=4 y=6 Sum=a+b+c

第6章-循环

{…

{…

{

while( )

do

for(;;)

{…}

{… }

{… }

}

while( );

}

} while( );

6.5 循环的嵌套

(4) while( ) (5) for(;;)

{…

{…

do{…}

while( )

while( )

{}

{…}

…

}

}

(6) do {… for(;;){ } … } while( )

第六章

本章要点

循环的基本概念 不同形式的循环控制 多重循环问题

主要内容

6.1 概述 6.2 goto语句以及用goto语句构成循环 6.3 用while语句实现循环 6.4 用do-while语句实现循环 6.5 用for 语句实现循环 6.6 循环的嵌套 6.7 几种循环的比较 6.8 break语句continue和语句 6.9 程 序 举 例

}

的值为} “真”时,两种循环得到的结

果相同。否则,二者结果不相同。

6.4 用for 语句实现循环

❖ C语言中的for语句使用最为灵活,不仅可以用于循环次数已经确 定的情况,而且可以用于循环次数不确定而只给出循环结束条件 的情况,它完全可以代替while语句。

❖ 一般形式: for(表达式1;表达式2;表达式3) 语句

以赋初值,使循环变量自动增值等。

6.4 用for 语句实现循环

说明: (5) 3个表达式都可省略,如:

for(; ;) 语句 相当于

while(1) 语句 即不设初值,不判断条件(认为表达式2为真值), 循环变量不增值。无终止地执行循环体。

6.4 用for 语句实现循环

EDA技术与Verilog_HDL(潘松)第6章习题答案

6-1 在Verilog设计中,给时序电路清零(复位)有两种不同方法,它们是什么,如何实现?答:同步清零、异步清零,在过程语句敏感信号表中的逻辑表述posedge CLK用于指明正向跳变,或negedge用于指明负向跳变实现6-2 哪一种复位方法必须将复位信号放在敏感信号表中?给出这两种电路的Verilog 描述。

答:异步复位必须将复位信号放在敏感信号表中。

同步清零:always @(posedge CLK) //CLK上升沿启动Q<=D; //当CLK有升沿时D被锁入Q异步清零:always @(posedge CLK or negedge RST) begin //块开始if(!RST)Q<=0; //如果RST=0条件成立,Q被清0else if(EN) Q<=D;//在CLK上升沿处,EN=1,则执行赋值语句end//块结束6-3 用不同循环语句分别设计一个逻辑电路模块,用以统计一8位二进制数中含1的数量。

module Statistics8(sum,A); output[3:0]sum;input[7:0] A;reg[3:0] sum;integer i;always @(A)beginsum=0;for(i=0;i<=8;i=i+1) //for 语句if(A[i]) sum=sum+1;else sum=sum;endendmodule module Statistics8(sum,A); parameter S=4;output[3:0]sum;input[7:0] A;reg[3:0] sum;reg[2*S:1]TA;integer i;always @(A)beginTA=A; sum=0;repeat(2*S)beginif(TA[1])sum=sum+1;TA=TA>>1;endendendmodulerepeat循环语句for循环语句module Statistics8(sum,A);parameter S=8;output[3:0]sum;input[7:0] A;reg[S:1] AT;reg[3:0] sum;reg[S:0] CT;always @(A) beginAT={{S{1'b0}},A}; sum=0; CT=S;while(CT>0) beginif(AT[1])sum=sum+1;else sum=sum;begin CT= CT-1; AT=AT>>1; end end endendmodule6-3 用不同循环语句分别设计一个逻辑电路模块,用以统计一8位二进制数中含1的数量。

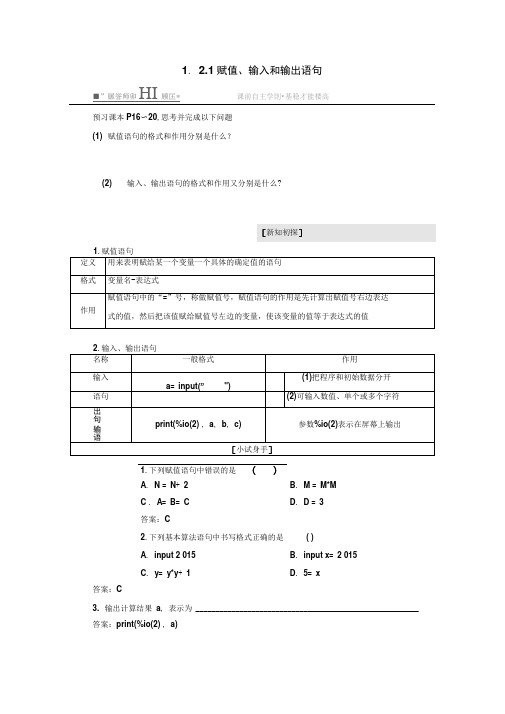

高中数学新人教B版必修3赋值、输入和输出语句

1. 2.1赋值、输入和输出语句■”脈誉师卯HI顾匡* 课前自主学則•基稳才能楼高预习课本P16〜20,思考并完成以下问题(1) 赋值语句的格式和作用分别是什么?(2) 输入、输出语句的格式和作用又分别是什么?1.下列赋值语句中错误的是()A. N = N+ 2B. M = M*MC . A= B= C D.D = 3答案:C2.下列基本算法语句中书写格式正确的是( )A. input 2 015B. input x= 2 015C. y= y*y+ 1D. 5= x答案:C3. 输出计算结果a, 表示为 ________________________________________________________ 答案:print(%io(2) , a)课堂讲輻设计■举一能通类题输入、输出语句及赋值语句的功能[典例]写出下列语句描述的算法的输出结果.a = 1;b = 2; c= a+ b;(2)b = a + c—b;print %io 2 , c, b, a ;a +b 2[解](1)因为a= 5, b= 3, c=-= 4, d= c= 16,所以输出结果为16.(2)因为a= 1, b= 2, c= a + b= 3,所以b= a+ c—b= 1 + 3—2 = 2.故输出结果依次为 a = 1, b= 2, c= 3.(1) 根据给出的算法语句写结果,应抓住输入、输出语句和赋值语句的特点,按语句的计算、赋值功能依次执行.⑵注意在Scilab语言中常见运算符号的书写方式,明确它们的运算规则:先乘除,后加减;乘幕优先于乘除;函数优先于乘幕;同级运算从左向右按顺序进行;括号内的运算最优先.[活学活用]如果输入“82,92,90下面程序的功能是____________,输出结果为_________ .x= input(” 成绩1 =” );y= input(” 成绩2 = ” );z= input(”成绩3 = ”);t= x + y+ z;s= t/3 ;print(%io(2) , s, t);解析:输入考试成绩,输出三科总分和平均分.答案:输出总分和平均分264,88用赋值、输入、输出语句写算法程序[典例]如图,已知圆的半径为R,其内接正方形如图,试设计程序求图中阴影部分的面积.[解]程序如下:R = input(”输入圆的半径R” 丫a = sqrt(2 *R ;S1 = %pi*R*R ;S2= a*a;S= S1 —S2;print (%io (2 , S ;1 •编写程序解决具体问题的一般步骤(1) 设计并用自然语言写出解决问题的算法.(2) 用程序框图表示算法.(3) 将程序框图转化为算法语句即得程序.2. 由程序框图写出程序的方法顺序结构的程序框图只需利用输入语句、输出语句和赋值语句即可完成•其中输入、输出框对应输入语句和输出语句,处理框对应赋值语句.[活学活用]根据程序框图,写出程序.(W)~rx=x+11r=r-iI/输出解:程序如下:x=input(,F x=");y= input]"y= M);print(%io(2),x/2.3 *y)?x=x+l |y=y—11print( %io(2) i y f x) v赋值、输入、输出语句在现实生活中的应用1 ----------- *v_ ------------------------------------------------------------------------------------------------------------------------------- 1现统计错了•小亮的成绩记在了小明的名下,小强的成绩记在了小亮的名下,而小明的成绩记在小强的名下了•设计程序更正成绩单,并输出.[解]程序如下:a = input( a= ;b= input(” b= ” ;c= input( c= ;x = a;a = c;c= b;b= x;print(% io(2 , c , b, a ;编写程序解决实际应用题的步骤(1) 审清题意,恰当设未知数.(2) 建立数学模型,把实际问题转化为数学问题.(3) 根据数学模型,设计算法分析.(4) 根据算法分析,画出程序框图.(5) 根据程序框图,利用输入、输出语句及赋值语句等编写程序.[活学活用]经过市场调查分析,2016年第一季度内,某地区对某件商品的需求量为12 000件,为保证商品不脱销,商家在月初时将商品按相同的量投入市场,已知年初商品的库存量为50 000件,用S表示商品的库存量,设计一个程序,求出第一季度结束时商品的库存量.解:列出如下列所示每月库存量的变化情况:库存f■-月份一月二月三月S46 00042 00038 000程序如下:S= 50 000; S= S—4 000;S= S—4 000;S= S—4 000; print % io 2 , S ;[层级一学业水平达标]1. 下列输入、输出、赋值语句中正确的是()A. a= input(” a=” )B. print(% io(2), a; b; c)课匠艮级训练,歩步提升隧力C. 10= BD . A= B=—5解析:选A A正确;B错误,print语句中变量之间用“,”隔开,而不是“;”;C 错误,赋值语句中“=”号左边只能是变量名,不能是数值;D错误,一个赋值语句只能给一个变量赋值,不能出现两个或两个以上的赋值号.2. 执行下面的程序后,输出的a, b的值是()a = 1 ;b= 3;a = a+ b;b= a—b;print(% io(2 , a, b ;A. 1,3B. 4,1C. 4,—2D. 1,4解析:选B 由赋值语句的意义知,执行 a = a + b后,a的值变为1 + 3 = 4,执行b = a —b 后,b= 4 —3 = 1,故选B.3. 下列程序若输出的结果为_______________________________ 4,则输入的x值可能是.解析:由题意可得x2+ 2x+ 1 = 4,解得x= 1或x=—3. 答案:1或—34. 读如下两个程序,完成下列题目.程序甲:x = 1 ;x = x*2 ;x = x*3 ;print (%io (2 , x ;程序乙:(1)程序甲的运行结果为_________⑵若程序甲、乙运行结果相同,则程序乙输入的值为_____________ .解析:赋值语句给变量赋值时,变量的值总是最后一次所赋的值,故程序甲中x的值最后为6.要使程序乙中y 的值为6,即x 2 + 6= 6,故x = 0,即输入的x 的值为0. 答案:(1)6 (2)0 [层级二应试能力达标] 1. “ x=3*5,” ( ) ① “ x=3*5 ② x=3*5 ③ “ x=3*5 ④ “ x=x+1”A .①③ C .①④语句在执行时“='右边 解析:选B的是 "的意思是 “ x=3*5=15 是将数值15赋给 x ; ”可以写为“ 3*5= x ”; “x=x+1 ”是某一程序中的先后相邻的两个语句,那么下列说法中,正确 ”此式与算术中的式子是一样的;x 的值是15,执行后左边 x 的值是16. B.②④ D .② 程序中的等号与算术中的不一样,且在给变量赋值时,赋值号的左边是变量,右边是数值或表达式,左右两边不能交换位置,故①③错. 2•以下程序运行后输出结果是 x = 5弘 *= 】(打 b= modulo (X' 10); x — 10 * b+a : print(^io(2)-x); A . 58B . 88C . 13D . 85解析:选D •/ x = 58, a 为58除以10的整数商,.a = 5.又T b 为58除以10的余数, b = 8.x = 10 X 8+ 5= 85. 3•以下程序的含义是( )A .求 x 3+ 3x 2— 24x + 30= 0 的根B .输入x 后,输出y = x 3 + 3x 2- 24x + 30的值C .求一般三次函数值的程序D . y = x 3+ 3x 2— 24x + 30 的作图程序解析:选B 本题考查对输入语句 x = input(” x = ”),赋值语句y = x A 3 + 3] 4.给出下列程序:x1 = input (” x1=” ;y1 = input (” y1=";x2= input(” x2=” ;y2= input(” y2=” ;a = x1 —x2;m = a A2;b = y1 —y2;n = bA2;s= m + n;d = sqrt(s ;print (%io (2 , d ;此程序的功能为()A .求点到直线的距离B.求两点之间的距离C .求一个多项式函数的值D .求输入的值的平方和解析:选B输入的四个实数可作为两个点的坐标,程序中的a, b分别表示两个点的横、纵坐标之差,而m, n分别表示两点横纵坐标之差的平方;s是横、纵坐标之差的平方和,d是平方和的算术平方根,即两点之间的距离,最后输出此距离.5. 运行程序:A = 2;A = A*5 ;A = A + 8;print (%io (2 , A ;输出结果为 _________ .解析:首先将2赋给变量A,然后将2X 5的结果再赋给A,最后这个新的数10加上8, 就得到输出的A的值18.答案:186. 已知A(X1,浙),B(X2,『2)是平面上的两点,试设计一个程序,输入A, B两点的坐标,输出其中点的坐标,现已给出程序的一部分,试在横线上填上适当的语句,把程序补充完整.x1 = input (” x1 = ”;y1 = input (” y1 = ” ;x2= input j” x2=”;y2= input j” y2=”;________ ;_ ;xy解析:根据题意可知程序中缺中点坐标,由中点坐标公式x= ~~2~ , y=2 "可得中点坐标.答案:x= (x1 + x2)/2 ; y = (y1 + y2)/ 27•已知一段程序如下:M-input ("M-");M = 2 * 6:P=(M * N)/2;Q=3 * P;pritu(%ic(2}・网若输入的是3,则运行结果是____________ .解析:由"Z H M",得N=3 ;由" M=2*6 ",得M=12 ;由" P=(M*N)/2 ",得P=18 ;由”Q=3*P ",得Q=54.答案:54,18,3,128.根据下列程序框图写出程序./输山y/解:程序如下:x = inpui(tr x=1t);xl = x/100:x2 = (x—xl * 100)/10;x3=x—x I s 100—x2 * 10?y=x3 * 100+x2 * 104 xl ;print(%io(2):9.某工种按工时计算工资,每月总工资=每月劳动时间(小时)x每小时工资,从总工资中扣除10%作公积金,剩余的为应发工资,请编写一个输入劳动时间和每小时工资数就能输出应发工资的程序,并画出程序框图.解:算法分析.程序框图如图所示.输入毎小时工蟄4程序如下:i = input(H t = ,,)i a= inpul (Ir a —"): 2 = 0* 9 * y : print( %ic(2).x):S 1 输入每月劳动时间t 和每小时工资a. S2 求每月总工资y =每月劳动时间t x 每小时工资 a.S3 求应发工资z =每月总工资y x (1 — 10%).S4 输出应发工资 z.。

第6章 Verilog HDL设计进阶习题

1CLK7476N 1K ~1Q ~1CLR 14

U3A 7400N

3

V1 100 Hz 5V J1

10 9 2 7 6 5 4 3

74194N

9 QD QC QB QA 12 13 14 15 11 13 14 15 16 17 18 19 20 21 22 23 1 2 3 4 5 6 7 8 G D C B A

//Verilog设计一个4位4输入最大数值检测电路 module Maximum_value_detection(Mostlarge,a,b,c,d);//4位 4输入最大数值检测电路 output [3:0] Mostlarge; input [3:0] a,b,c,d; wire[3:0]sum1,sum2,sum3;

习

CP 1 2 3 4 5 6 QD(A2) QC(D4、~D5) 0 0 0 1 1 1 1 1 1 0 ~0 0 QB(A1) 0 1 1 0 0 1

题

QA(A0、D7) 1 0 1 0 1 0 D D1 D2 D3 D4 D5 D6 F 0 1 0 0 1 0

7

8 9 10 11

1

1 1 1 1

U1

74150N

Key = Space

XSC1

Ext Trig + _ A + _ + B _

U5A 7404N

E15 E14 E13 E12 E11 E10 E9 E8 E7 E6 E5 E4 E3 E2 E1 E0

0

1 ~1 1 1

1

0 0 1 1

1

0 1 0 1

D7

D4 D5 D6 D7

1

1 0 0 1

VDD 5V U2 U1A 74S04D

LabVIEW编程与项目开发实用教程 第6章 LabVIEW高级编程

图6-4 公式节点输入/输出端子对应,左图正确/右图错误

6.1.2 公式

在函数数学公式与脚本选板中公式节点 ,见图6-5。

当把公式节点放置到程序框图上时,系统会自动弹出“配置公式”对 话框,见图6-6。在对话框中输入公式后,若对话框右上方的方块显示为 绿色时,则表明系统识别了输入的函数。当出现错误或非法公式时,对 话框右上方的方块显示为灰色,表明系统不识别。

图 6-1 公式节点选板

图 6-5 脚本与公式选板

与创建循环的方法类似,用户从结构选板中选择公式节点,用鼠标 在程序框图上任意位置拖放任意大小的公式节点。公式节点是一个大小 可变的方框,利用它可直接在程序框图中输入数学公式,如图6-3所示。

在程序框图上输入数学公式或类似于C语言的表达式,可以使用的函 数如下:abs、acos、acosh、asin、asinh、atan、atan2、atanh、ceil、cos 、cosh、cot、csc、exp、expm1、floor、getexp、getman、int、intrz、ln、 lnp1、log、log2、max、min、mod、pow、rand、rem、sec、sign、sin、 sinc、sinh、sqrt、tan和tanh等。

LabVIEW通过对象标签将局部变量和 前面板对象相关联,因此必须用描述性 的自带标签对前面板控件和显示件进行 标注,如图6-11中对象标签“字符串”、 “数值”等。

2.局部变量使用方法

(1)使用局部变量可对前面板控件进行 读/写。 局部变量有读和写两种属性。当一个局部 变量为读属性时,说明可以从该局部变量 中读取数据。相反,当其为写属性时则可 以给该变量赋值。右键单击从弹出菜单上 选 转换为写入 或 转换为读取。

1.全局变量创建

06 VB程序设计语句

说明: ⑴语句执行过程。

【例6.15】从键盘输入字符并统计字符个数,当输入字符为“?”时,停止计数。 【例6.16】用Do语句编写程序,求1到100的累加和。

退出

第23页

⑵ Do循环需要有能够改变循环条件表达式值的语句,否则循环永远不会 结束,即死循环。

⑶ Exit Do语句用于强制跳出循环。 ⑷ Do...Loop 语句的另一种形式格式:

退出

第16页

3 .当程序中依赖某个单独的关键变量或表达式作判断条件时,Select Case语句效率更高,可读性好。

4.如果测试表达式的值能与多个Case子句表达式的值相匹配,只执行第一 个匹配的Case子句下面的语句块。

【例6-10】用Case语句改写例6.7,将输入成绩转换为相应学分。 注意值列表顺序的合理性。

退出

3.If 语句的嵌套 格式:

If<条件1>Then <语句块1>

ElseIf<条件2>Then <语句块2> …

[Else 语句块n+1]

End If

第11页

退出

第12页

If语句多分支结构流程图

真 语句块1

假 条件

1真

条件 假

语句块2

2

真

语句块n

条件 n

假 语句块n+1

退出

第13页

If语句的嵌套可以用于条件比较复杂的多分支情况。 【例6-6】已知分段函数: 编写程序,输入自变量x的值,计算并输出函数y的值。

退出

For…Next语句 第19页

格式:

For <循环变量> = <初值> To <终值> [Step步长]

[计算机软件及应用]计算机基础2C语言第6章循环结构

![[计算机软件及应用]计算机基础2C语言第6章循环结构](https://img.taocdn.com/s3/m/f45143d1bcd126fff6050bd4.png)

2021/8/26

2

while语句

(1)一般格式 while(循环继续条件) { 循环体语句组;}

while语句的语义是:计算表达式的值,当值为真(非 0)时, 执行循环体语句。

2021/8/26

3

#include <stdio.h>

main()

{ int n=0; printf("input a string:\n"); while(getchar()!='\n') n++; printf("%d",n); }

重循环

2021/8/26

5

当输入a的值为5时,分析以下程序 的结果

main() {

int a,n=0; scanf(“%d”,&a); while(a=5)

printf("%d ",n++); }

2021/8/26

6

以下程序的输出结果是2 0。

#include <stdio.h> void main() {

char c; c=getchar( ); while((getchar())!='?')

putchar(++c); }

jhiu

2021/8/26

9

#include <stdio.h> void main() {

输入:2473<CR>(<CR>代表回车符), 程序的输出结果是

int c;

while((c=getchar())!='\n')

for(n=7;n<=100;n+=7)

《计算机科学概论》第6章 程序设计语言

传统的程序设计概念

2.数据结构

抽象的描述:数据的概念形态或布局。 通俗的理解:

当相同类型或不同类型的一组数据结合在一起使用时,可以使 用某种方式将它们组织起来,这种数据的组织方式就叫做数据结构。

一种常用的数据结构----数组,数组有: 同构数组(homogeneous array) 异构数组(heterogeneous array)

字符(character)类型 用来指称符号组成的数据 比较、查找、连接等运算

布尔(Boolean)类型 指称只有真和假两种值的数据项

传统的程序设计概念

1.变量和数据类型-说明变量的一般形式:

数据类型 变量名; 例如: int Height;

int Height, Width; int height = 100;

例如:Z = X + Y; Z := X + Y;

运算符优先(operator precedence) 赋值语句中的表达式的运算次序是借助运算符的优先级实现的 例如:2*4+6/2

重载(overloading):一个运算符的多重使用称为运算符的重载 例如: “abc” + “ok” 结果是:“abcok”

历史回顾

程序设计范型

程序设计范型代表了在构建问题的解决方法时的不同方法。 范型影响了整个软件的开发过程。我们应该称为软件开发范型。

历史回顾

程序设计范型

历史回顾

程序设计范型- 命令型范型 (过程型)

是一种传统的程序设计方法 这种范型告诉我们的程序设计方法是:先找到解决问题的算法,

然后用命令序列表示这个算法。 C、Pascal、BASIC…

过程的目的是要产生一个值,而不是一个动作。 例如:

高级语言程序设计第6章参考答案

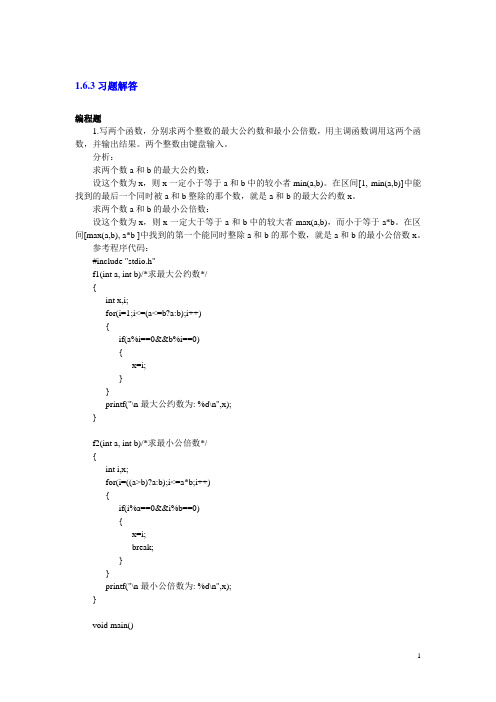

1.6.3习题解答编程题1.写两个函数,分别求两个整数的最大公约数和最小公倍数,用主调函数调用这两个函数,并输出结果。

两个整数由键盘输入。

分析:求两个数a和b的最大公约数:设这个数为x,则x一定小于等于a和b中的较小者min(a,b)。

在区间[1, min(a,b)]中能找到的最后一个同时被a和b整除的那个数,就是a和b的最大公约数x。

求两个数a和b的最小公倍数:设这个数为x,则x一定大于等于a和b中的较大者max(a,b),而小于等于a*b。

在区间[max(a,b), a*b ]中找到的第一个能同时整除a和b的那个数,就是a和b的最小公倍数x。

参考程序代码:#include "stdio.h"f1(int a, int b)/*求最大公约数*/{int x,i;for(i=1;i<=(a<=b?a:b);i++){if(a%i==0&&b%i==0){x=i;}}printf("\n最大公约数为: %d\n",x);}f2(int a, int b)/*求最小公倍数*/{int i,x;for(i=((a>b)?a:b);i<=a*b;i++){if(i%a==0&&i%b==0){x=i;break;}}printf("\n最小公倍数为: %d\n",x);}void main(){int a,b;printf("\n请输入两个数:\n");printf("a=");scanf("%d", &a);printf("b=");scanf("%d", &b);f1(a, b);f2(a, b);}运行结果:请输入两个数:a=4b=16最大公约数为:4最小公倍数为:162.编写一个函数,其功能是对于给定的一个时间数(秒为单位),以“时:分:秒”的格式输出。

第6章 VHDL时间控制和赋值语句

第6章 行为描述(二):时间控制和赋值语句

1. 第一种形式的延时控制语句 在上面给出的第一种延时控制格式中,<延迟时间>的后面跟 着一条行为语句。在这种情况下,仿真进程在遇到这条带有延时 控制的行为语句后并不立即执行行为语句指定的操作,而是要延 迟等待到“<延迟时间>”所指定的时间量过去后才真正开始执行行 为语句指定的操作,如例6-1所示的程序。

则不会触发语句的执行。

所要触发执行的具体操作

边沿触发事件控制的语法格式可以为如下几种:

第一种:@ (<事件表达式>) 行为语句;

第二种:@ (<事件表达式>) ;

第三种:@ (<事件表达式1> or <事件表达式2> or ……or<事

件表达式n >) 行为语句;

第四种:@ (<事件表达式1> or <事件表达式2> or ……or<事

4

第6章 行为描述(二):时间控制和赋值语句

【例6-1】第一种形式的延时控制语句。

module clk_gen(clk); output clk; reg clk; initial

串行块内共有四条赋值语句, 其中语句S1没有时间控制部 分,而语句S2、S3和S4带有

延时控制。

begin

clk=0;

begin #10 ; a=b ;

end 将等价于下面这一条语句:

#10 a=b; 下面我们给出另一个例子来说明第二种形式的延时控制语句 在并行块中使用的情况。

10

第6章 行为描述(二):时间控制和赋值语句

【例6-3】第二种形式的延时控制语句使用于并行块。 module clk_gen(clk);

C语言程序设计 第6章

#include <stdio.h> #include <stdlib.h> main( ) { int a[10]; /*定义数组*/ int k,j; float ave,s; k=0;s=0.0; for(j=0;j<10;j++) /*用数组存放10个随机整数*/ a[j]=rand()%50; printf("数组中的值:"); for(j=0;j<10;j++) /*输出10个随机整数*/ printf("%6d",a[j]); printf("\n"); for(j=0;j<10;j++) { if(a[j]%2==0) /*如果数组元素的值为偶数*/ {s+=a[j];k++;} /*累加及偶数个数计数*/ } if(k!=0) {ave=s/k; printf("偶数的个数:%d\n偶数的平均植:%f\n",k,ave);} }

(2)定义一个二维数组a[N][5],数组每行存放一名 学生的数据,每行前4列存放学生4门单科成绩,第5列 存放学生的总分。 (3)输入N个学生的单科成绩,存入二维数组a中。 (4)通过变量sum累加计算每位学生的总分,然后 赋值给每行的最后一个元素。 (5)输出数组第5列上的值,即为每个学生的总分。

for(i=0;i<N;i++) { sum=0; for(j=0;j<4;j++) /*计算当前学生的总分*/ sum+=a[i][j]; a[i][4]=sum; } for(i=0;i<N;i++) /*输出每个学生的总分*/ printf("第%d个学生的总分为:%d\n",i+1,a[i][4]); }

Java语言程序设计第6章_数组与字符串

6.3.3 正则表达式中的限定符

▪ 在使用正则表达式时,如果需要某一类型的元字符多次输出, 逐个输入就相当麻烦,这时可以使用正则表达式的限定元字 符来重复次数。

例如:

regex=”hello[246]?” 那么”hello”、”hello2”、 ”hello4”、 ”hello6”都是与 regex匹配的字符串。

以上构造方法中,使用最多的是第2个,如:

String s = new String(“Hello World“);

字符数组要转化为字符串可以利用第3个构造方法。例如:

Char[] helloArray={‘h’,’e’,’l’,’l’,’o’}; String s = new String(helloArray);

▪ 二维数组的元素是一维数组,因此,初始化时也可允许各行单 独进行。Java的二维数组允许各行有不同的元素个数。例如:

▪ double score[][]; ▪ score = new double[3][]; ▪ score[0] = new double[3]; ▪ score[1] = new double[2]; ▪ score[2] = new double[4];

▪ public String (String s); //用已有字符串创建新的String。

▪ public String (StringBuffer buf) ; //用StringBuffer对 象的内容初始化新String。

▪ public String (char value[]); //用已有字符数组初始 化新String。

double score [] []={{56.8,42.5,96.8};{100,78},{99,63,78,45}}

C++第六章课后习题

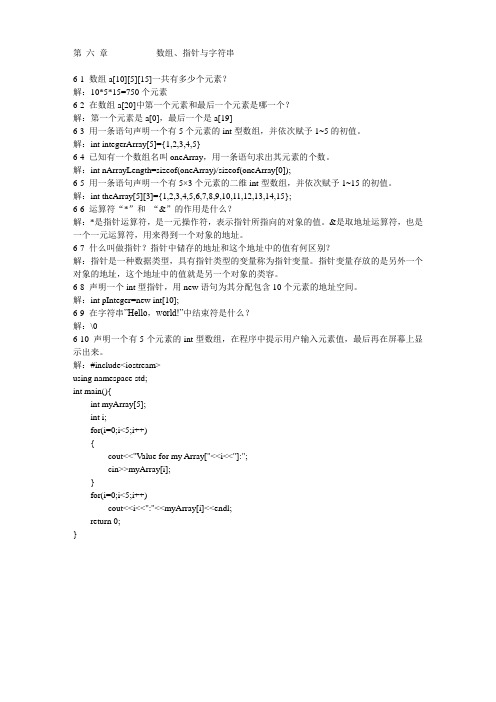

第六章数组、指针与字符串6-1 数组a[10][5][15]一共有多少个元素?解:10*5*15=750个元素6-2 在数组a[20]中第一个元素和最后一个元素是哪一个?解:第一个元素是a[0],最后一个是a[19]6-3 用一条语句声明一个有5个元素的int型数组,并依次赋予1~5的初值。

解:int integerArray[5]={1,2,3,4,5}6-4 已知有一个数组名叫oneArray,用一条语句求出其元素的个数。

解:int nArrayLength=sizeof(oneArray)/sizeof(oneArray[0]);6-5 用一条语句声明一个有5×3个元素的二维int型数组,并依次赋予1~15的初值。

解:int theArray[5][3]={1,2,3,4,5,6,7,8,9,10,11,12,13,14,15};6-6 运算符“*”和“&”的作用是什么?解:*是指针运算符,是一元操作符,表示指针所指向的对象的值。

&是取地址运算符,也是一个一元运算符,用来得到一个对象的地址。

6-7 什么叫做指针?指针中储存的地址和这个地址中的值有何区别?解:指针是一种数据类型,具有指针类型的变量称为指针变量。

指针变量存放的是另外一个对象的地址,这个地址中的值就是另一个对象的类容。

6-8 声明一个int型指针,用new语句为其分配包含10个元素的地址空间。

解:int pInteger=new int[10];6-9 在字符串”Hello,world!”中结束符是什么?解:\06-10 声明一个有5个元素的int型数组,在程序中提示用户输入元素值,最后再在屏幕上显示出来。

解:#include<iostream>using namespace std;int main(){int myArray[5];int i;for(i=0;i<5;i++){cout<<"Value for my Array["<<i<<"]:";cin>>myArray[i];}for(i=0;i<5;i++)cout<<i<<":"<<myArray[i]<<endl;return 0;}6-11 引用和指针有何区别?何时只能使用指针而不能使用引用?解:引用是一个别名,不能为NULL值,不能被重新分配;指针是一个存放地址的变量。

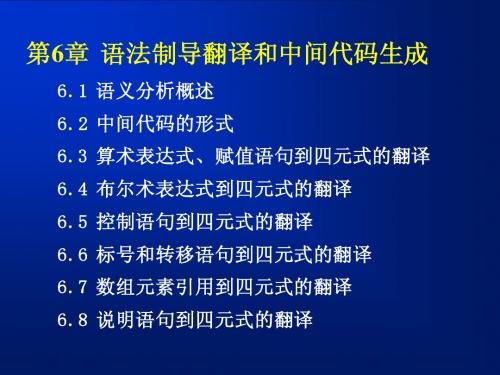

6-第六章_语义分析-1-2-3节

2.语义分析程序 2.语义分析程序

为每个产生式,构造一个语义子程序Subi , 为每个产生式,构造一个语义子程序Sub 语义程序包括: 针对每一条产生式) 语义程序包括:⑴ Subi (针对每一条产生式) 公共子程序) ⑵ Comj (公共子程序)

语法分析程序 Par1,Par2…Park 语义 分析 程序 Sub1 Sub2 Ret1,Ret2…Reth

L.in= real L.in= real , , id2 id3

L.in= real id1

语 义 规 则 L.in:=T.type T.type=integer T.type:=real L1.in:=L.in;addtype(id.entry,L.in) ; addtype(id.entry,L.in)

…

Subn 中间代码Leabharlann Com1… Com m

例:E→E1 + E2 入口参数(Par) (Par): .PLACE, 入口参数(Par): E1.PLACE, E2.PLACE (存放E1 、E2 的值的单元地址) 存放E 的值的单元地址) 返回参数(Ret): E.PLACE (存放E值的单元地址) 返回参数(Ret): (存放E值的单元地址) (Ret) 存放 生成中间代码 ( +, E1.PLACE, E2.PLACE, E.PLACE)

例: E → E1 + E2 E .code —— E的中间代码序列 E .val —— E的值 存放E E .PLACE —— 存放E的值的单元地址

说明: 不同的中间代码形式、不同的语言成份, 说明: 不同的中间代码形式、不同的语言成份, 使用的属性不同。 使用的属性不同。

属性 • 综合属性(synthesized attribute) 综合属性(synthesized

《C程序设计》课件第6章

数组是由相同类型的数据组成的有序集合, 集合中的每 一个数据称为数组的元素, 每个数组元素用数组名和下标唯 一标识访问, 在程序中可方便地按下标组织循环来访问数组 元素。 下面用数组来改写例6.1, 请读者体会数组的作用。

#include <stdio.h> void main() {

float s[5]; int i; printf("Enter five scores:"); for(i=1; i<=5; i++)

1 2 3 4 5 6

这种初始化的方式也可以只为数组的部分元素赋值,例 如:

int a[3][2]={{1},{2,3},{4}}; 这样,数组的前几个元素的值为:

a[0][0]=1,a[1][0]=2,a[1][1]=3, a[2][0]=4 而其余元素的初值将自动设为0。 在初始化时,也可将所有数据写在一个花括号内,按数 组的排列顺序对各元素赋初值。如: int a[3][2]={1,2,3,4}; 其结果是:a[0][0]=1,a[0][1]=2,a[1][0] =3,a[1][1]=4,其余元素的值自动设为0。

需要强调指出的是,在程序设计中, C语言的编译系统对 数组下标越界(即引用a[5], a[6],…),并不给出错误提示, 因此用户在编程时应格外注意,以免影响系统的正常运行。

电气控制与S7-300 PLC编程技术第6章 位逻辑指令

= Q4.1

7.逻辑块的操作

2. 串并联组合表示法

当逻辑串是复杂组合时,CPU的扫描顺序是先“与”后 “或”。图6.16 (a)给出的梯形逻辑是触点先并后串的例子,与 其对应的语句表为: I0.0 M10.0 M10.1 Q4.0 A( ( ) I0.2 M0.3 O I0.0 O I0.2 ) (a) A( I0.0 M10.0 M10.1 Q4.0 O M10.0 ( ) O M0.3 I0.2 M0.3 ) A M10.1 (b ) = Q6.0

一个RLO可被用来驱动几个输出元件。在LAD中,输出 线圈是上下依次排列的。在STL中,与输出信号有关的指令被 一个接一个地连续编程,这些输出具有相同的优先级。图6.8是 多重输出梯形图,与之对应的语句表如下: A A I0.0 I0.1

I0.0 I0.2 I0.1 Q4.0 ( ) I0.3 Q4.1 ( )

网络 1 A A R I0.3 T1 (R) C1 (R) 网络 2 A R 网络 3 A R I0.4 C1 I0.3 T1 I0.0 I0.1 I0.0 I0.2 I0.1 Q4.0 Q4.0 (S) A A S I0.0 I0.1 Q4.0

图6.16 串并联组合逻辑梯形图

图6.16(b)是先串后并的例子,与其对应的语句表如下: A( A I0.0 A M10.0 O A I0.2 A M0.3 ) A M10.1 = Q4.0

5.逻辑 “异或”指令பைடு நூலகம்

6.逻辑 “异或非”指令

3. “异或”和“异或非”(X,XN)指令 图6.7是“异或”逻辑梯形图,下面是与梯形图对应的语句 表。在的语句表中,使用了“异或”和“异或非”指令,分别 用助记符“X”和“XN”来标识。它类似“或”和“或非”指令, 用于扫描并联回路能否“通电”。 X X = I 0.0 I 0.1 Q 4.0

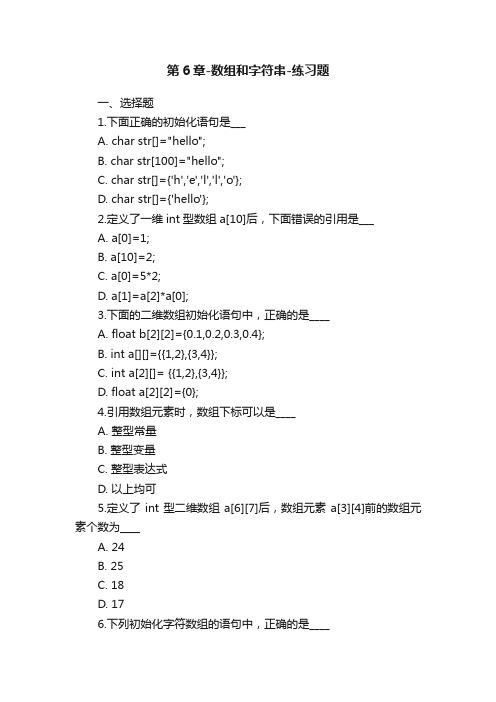

第6章-数组和字符串-练习题

第6章-数组和字符串-练习题一、选择题1.下面正确的初始化语句是___A. char str[]="hello";B. char str[100]="hello";C. char str[]={'h','e','l','l','o'};D. char str[]={'hello'};2.定义了一维int型数组a[10]后,下面错误的引用是___A. a[0]=1;B. a[10]=2;C. a[0]=5*2;D. a[1]=a[2]*a[0];3.下面的二维数组初始化语句中,正确的是____A. float b[2][2]={0.1,0.2,0.3,0.4};B. int a[][]={{1,2},{3,4}};C. int a[2][]= {{1,2},{3,4}};D. float a[2][2]={0};4.引用数组元素时,数组下标可以是____A. 整型常量B. 整型变量C. 整型表达式D. 以上均可5.定义了int型二维数组a[6][7]后,数组元素a[3][4]前的数组元素个数为____A. 24B. 25C. 18D. 176.下列初始化字符数组的语句中,正确的是____A. char str[5]="hello";B. char str[]={'h','e','l','l','o','\0'};C. char str[5]={"hi"};D. char str[100]="";7.给出下列代码,则数组初始化中哪项是不正确的?byte[]array1,array2[];byte array3[][];byte [][]array4;A.array2 = array1 B.array2=array3C.array2=array4 D.array3=array48.下面程序的运行结果是____main() {int x=30;int[] numbers=new int[x];x=60;System.out.println(numbers.length);}A. 60B. 20C. 30D. 509.下面不是创建数组的正确语句A.float f[][]=new float[6][6];B.float f[]=new float[6];C.float f[][]=new float[][6];D.float[][]f=new float[6][];10.下列关于Java语言的数组描述中,错误的是()。

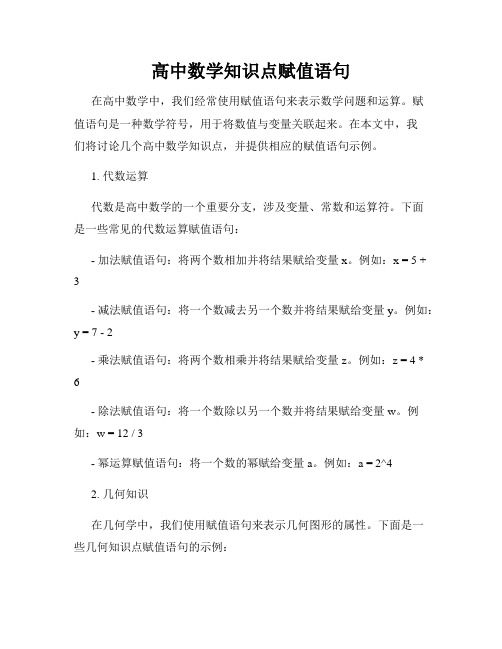

高中数学知识点赋值语句

高中数学知识点赋值语句在高中数学中,我们经常使用赋值语句来表示数学问题和运算。

赋值语句是一种数学符号,用于将数值与变量关联起来。

在本文中,我们将讨论几个高中数学知识点,并提供相应的赋值语句示例。

1. 代数运算代数是高中数学的一个重要分支,涉及变量、常数和运算符。

下面是一些常见的代数运算赋值语句:- 加法赋值语句:将两个数相加并将结果赋给变量x。

例如:x = 5 + 3- 减法赋值语句:将一个数减去另一个数并将结果赋给变量y。

例如:y = 7 - 2- 乘法赋值语句:将两个数相乘并将结果赋给变量z。

例如:z = 4 * 6- 除法赋值语句:将一个数除以另一个数并将结果赋给变量w。

例如:w = 12 / 3- 幂运算赋值语句:将一个数的幂赋给变量a。

例如:a = 2^42. 几何知识在几何学中,我们使用赋值语句来表示几何图形的属性。

下面是一些几何知识点赋值语句的示例:- 长方形面积赋值语句:将长方形的长和宽相乘并将结果赋给变量A。

例如:A = l * w- 圆的周长赋值语句:将圆的直径乘以π并将结果赋给变量C。

例如:C = d * π- 三角形面积赋值语句:将三角形的底边乘以高并除以2,并将结果赋给变量S。

例如:S = (b * h) / 23. 概率与统计在概率与统计学中,我们使用赋值语句来表示概率和统计量。

下面是一些与概率和统计相关的赋值语句示例:- 事件概率赋值语句:将事件的发生次数除以总次数并将结果赋给变量P。

例如:P = n / N- 样本均值赋值语句:将样本的所有观测值相加并除以样本容量,并将结果赋给变量μ。

例如:μ = (x₁ + x₂ + ... + xₙ) / n- 样本方差赋值语句:将每个观测值与样本均值的差的平方相加并除以样本容量减1,并将结果赋给变量σ²。

例如:σ² = ((x₁ - μ)² + (x₂- μ)² + ... + (xₙ - μ)²) / (n - 1)4. 数列和数列求和在数列和数列求和中,我们使用赋值语句来表示数列的通项和求和公式。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

例6-11 不要在不同的always块内为同一个变量赋值

module correct_assign( clk, //时钟输入信号 sel , //选择信号,sel==1时输出din1的值,当sel=0时输出 din2的值 din1, din2, dout ); input clk; input sel; input din1; input din2; output dout; wire wire wire reg clk; sel; din1, din2; dout;

always @ (din) begin dout = temp[1]; temp[1] = temp[0]; temp[0] = din; end

由于阻塞赋值语句是一个接一个执行的,因此首先执行 了dout=temp[1],将temp[1]的值赋予了dout,然后才执 行temp[1]=temp[0],此时temp[1]的值才被更新,也就是 说dout获得的是上次更新的temp[1]的值。

reg x,y,z; reg [15:0] reg_a, reg_b; integer count; initial //所有行为语句必须放在initial或always 块内部 begin 在仿真0时刻执行 x= 0; y=1;z=1; //标量赋值 count=0; //整型变量赋值 reg_a=16’b0; reg_b=reg_a; //向量的初始化

例6-10 在不同的always块内为相同的变量赋值

module wrong_assign( clk, //时钟输入信号 sel , //选择信号,sel==1时输出din1的值,当sel=0时输出 din2的值 din1, din2, dout ); input clk; input sel; input din1; input din2; output dout; wire wire wire reg clk; sel; din1, din2; dout;

∥定义两个1位的输人信号 ∥outl输出了a和b的与值 ∥out2输出了a和b的或值 //out3输出了a和b的异或值

wire

out1,out2,out3; ∥定义3个1位的输出信号

assign outl=a&b: assign out2=a|b: assign out3=a^b;

连续赋值语句的特点:

#10 reg_b[15:13] = {x,y,z} 在仿真时刻25执行 //把拼接操作的结果赋值给向量的部分位 count=count+1; end //给整型变量赋值(递增) 在仿真时刻25执行

结论1:由于阻塞赋值语句是按顺序执行的,因此 如果在一个begin_end块中使用阻塞式赋值语句,那 么这个块表现为串行行为。

1、连续赋值语句的左值必须是一个标量或向量线网,或者 是标量或向量线网的拼接,不能是标量或向量寄存器。 2、连续赋值语句总是处于激活状态,只要任意一个操作

数发生变化,表达式就会被立即重新计算,并且将结果赋给 等号左边的线网。

3、操作数(赋值符右端)可以是标量或向量的线网或寄存 器,也可以是函数调用。 4、赋值延迟用于控制对线网赋予新值的时间,根据仿真时 间单位进行说明。这对于描述实际电路中的时序非常有用。

阻塞赋值 (Blocking Assignment)

非阻塞赋值 (Nonblocking Assignment)

6.3.1 连续赋值

•连续赋值用于对线网 型的变量进行赋值;

线网型变量必须用连 续赋值的方法赋值

它只能为线网型变量赋值

•表达方式是以关键字assign开头,后面跟“=” 赋值 wire a , b;

在仿真时刻15执行 reg_a[2] <= #15 1’b1; //带延迟的位选赋值 reg_b[15:13] <= #10 {x,y,z}; 在仿真时刻10执行 //把拼接操作的结果赋值给向量的部分位 count <= count+1; //给整型变量赋值(递增) 在仿真时刻0执行

end

多条阻塞语句与多条非阻塞语句的区别: 多条阻塞语句是顺序执行的,而多条非阻塞语句是 并行执行的 阻塞赋值和非阻塞赋值在使用上的一些注意事项: (1)在使用always块描述组合逻辑时,使用阻塞赋 值;在使用always块描述时序逻辑时,使用非阻塞 赋值 (2)不要在同一个always块内同时使用阻塞赋值和 非阻塞赋值 (3)无论是使用阻塞赋值或者非阻塞赋值,不要在 不同的always块内为同一个变量赋值 (4)在程序中不要使用0延时

wire out =in1 & in2;

隐式线网声明:

•若一个信号被用在连续赋值语句左端,则Verilog编 译器认为该信号是一个隐式声明的线网。 •若线网被连接到模块的端口上,则Verilog编译器 认为隐式声明线网的宽度等于模块端口的宽度。 wire i1, i2;

∥连续赋值语句,out为线网类型

reg x,y,z; reg [15:0] reg_a, reg_b; integer count; //所有行为语句必须放在initial或always 块内部 initial begin 在仿真0时刻执行 x= 0; y=1;z=1; //标量赋值 count=0; //整型变量赋值 reg_a=16’b0; reg_b=reg_a; //向量的初始化 在仿真时刻15执行 #15 reg_a[2] =1’b1; //带延迟的位选赋值

§ 6.3 赋值语句

本节重点:

•掌握两种赋值语句:连续赋值和过程赋值语句 •掌握过程赋值的两种类型:阻塞赋值和非阻塞赋值

本节难点:

•阻塞赋值和非阻塞赋值的使用

§ 6.3 赋值语句

Verilog HDL有两种为变量赋值的方法: 连续赋值 (Continuous Assignment) 过程赋值 (Procedural Assignment)

注意:在对寄存器类型变量进行赋值时,如果赋值

符两侧宽度不相等,则采用以下原则: 1、如果右边表达式的位宽较宽,则将保留从最低 位开始的右侧值,把超过左侧位宽的高位丢弃; 2、如果左侧位宽大于右侧位宽,则不足的高位补0;

非阻塞赋值

module blocking(

非阻塞赋值使用“ 为变量赋值,在执行到赋值语 // 时钟输入信号 clk, <=” rst , 句时,仅仅对“ <=”右边的表达式的值进行评估,但并 //复位信号,用于给寄存器赋初值,低电平有效 不马上执行赋值,然后继续执行后面的操作。连续的 out1, 非阻塞赋值操作是同时完成的。

endmodule

if(!rst)

else

begin out1 <= 1; out2 <= 0; end

begin

out1<= out2; out2<= out1; end

图6-3 例6-9的仿真波形

当rst异步复位信号 变低时,为outl和 out2赋初值1和0

当clk时钟信号的上升沿到来时执行 always块内的内容。由于使用了非阻 塞赋值,outl<=out2和out2<=outl这两 条语句是同时完成的

例6-8连续的阻塞赋值

module blocking(

din, //数据输入信号 dou //数据输出信号 ); din; dout; din; dout; temp; //数据缓冲

input output wire reg reg [1:0] always @ (din) begin dout = temp[1]; temp[1] = temp[0]; temp[0] = din; end endmodule

过程赋值语句 的两种类型:

一、阻塞赋值语句

阻塞赋值使用“=”为变量赋值,在赋值结束以前不可以进 module blocking( din, //数据输入信号 行其他操作,在赋值结束后继续后面的操作。 dout //数据输出信号 ); input din; output dout; wire din; reg dout; reg [1:0] temp; //数据缓冲 always @ (din) begin temp[0] = din; temp[1] = temp[0]; dout = temp[1]; end endmodule

• 过程赋值语句的更新对象是寄存器、整数、实数

或时间变量,位置在各种块结构中。

• 这些类型的变量在被赋值后,其值将保持不变, 直到被其他过程赋值语句赋予新值。

连续赋值语句

总是处于活动状态,任意一个 操作数的变化都会导致表达式 的重新计算以及重新赋值

过程赋值语句

只有在执行到的时候才 会起作用,且一旦赋值 将保持值不变

过程赋值语句左侧值的可选类型:

• reg、整型数、实型数、时间寄存器变量或存储

器单元。

• 上述个中类型的位选(例如,addr[0] )。 • 上述各种类型的域选(例如,addr[31:16] )。 • 上述三种类型的拼接。

阻塞赋值语句 (Blocking Assignment) 非阻塞赋值语句 (Nonblocking Assignment)

assign out =i1 & i2;

∥注意,out并未声明为线网,但Verilog仿真器会推断出 ∥out是一个隐式声明的线网

连续赋值延迟:

•用于控制任一操作数发生变化后语句左值被赋予新值 之间的时间间隔。 assign #10 out =in1 & in2; wire #10 out =in1 & in2;

例:连续赋值语句举例

assign outl= i1& i2;

∥连续赋值语句,out是线网,i1和i2也是线网

assign addr[15:0]=addr1_bit[15:0]^addr2_bit[15:0];

∥向量线网的连续赋值语句。addr是16位的向量线网 ∥addr1_bits和addr2_bits是16位的向量寄存器