6.1.2 段寄存器的说明语句

龙芯 3C5000L 处理器寄存器使用手册说明书

龙芯3C5000L处理器寄存器使用手册多核处理器架构、寄存器描述与系统软件编程指南V1.1龙芯中科技术股份有限公司版权声明本文档版权归龙芯中科技术股份有限公司所有,并保留一切权利。

未经书面许可,任何公司和个人不得将此文档中的任何部分公开、转载或以其他方式散发给第三方。

否则,必将追究其法律责任。

免责声明本文档仅提供阶段性信息,所含内容可根据产品的实际情况随时更新,恕不另行通知。

如因文档使用不当造成的直接或间接损失,本公司不承担任何责任。

龙芯中科技术股份有限公司Loongson Technology Corporation Limited地址:北京市海淀区中关村环保科技示范园龙芯产业园2号楼Building No.2, Loongson Industrial Park,Zhongguancun Environmental Protection Park, Haidian District, Beijing电话(Tel):************传真(Fax):************阅读指南《龙芯3C5000L处理器寄存器使用手册》介绍龙芯3C5000L多核处理器架构与寄存器描述,对芯片系统架构、主要模块的功能与配置、寄存器列表及位域进行详细说明。

修订历史手册信息反馈:*******************也可通过问题反馈网站/ 向我司提交芯片产品使用过程中的问题,并获取技术支持。

I 目录1 概述 (1)1.1 龙芯系列处理器介绍 (1)1.2 龙芯3C5000L简介 (2)2 系统配置与控制 (5)2.1 芯片工作模式 (5)2.2 控制引脚说明 (5)3 物理地址空间分布 (7)3.1 结点间的物理地址空间分布 (7)3.2 结点内的物理地址空间分布 (8)3.3 地址路由分布与配置 (9)4 芯片配置寄存器 (17)4.1 版本寄存器(0x0000) (17)4.2 芯片特性寄存器(0x0008) (17)4.3 厂商名称(0x0010) (18)4.4 芯片名称(0x0020) (18)4.5 功能设置寄存器(0x0180) (18)4.6 引脚驱动设置寄存器(0x0188) (19)4.7 功能采样寄存器(0x0190) (19)4.8 温度采样寄存器(0x0198) (20)4.9 频率配置寄存器(0x01B0) (20)4.10 处理器核分频设置寄存器(0x01D0) (23)4.11 处理器核复位控制寄存器(0x01D8) (23)4.12 路由设置寄存器(0x0400) (24)4.13 其它功能设置寄存器(0x0420) (24)4.14 摄氏温度寄存器(0x0428) (26)4.15 SRAM调节寄存器(0x0430) (26)4.16 FUSE0观测寄存器(0x0460) (26)4.17 FUSE1观测寄存器(0x0470) (27)5 芯片时钟分频及使能控制 (28)II 5.1 芯片模块时钟介绍 (28)5.2 处理器核分频及使能控制 (29)5.2.1 按地址访问 (29)5.2.2 配置寄存器指令访问 (30)5.3 结点时钟分频及使能控制 (30)5.3.1 软件设置 (31)5.3.2 硬件自动设置 (31)5.4 HT控制器分频及使能控制 (32)5.5 Stable Counter分频及使能控制 (33)6 软件时钟系统 (35)6.1 Stable Counter (35)6.1.1 Stable Timer的配置地址 (35)6.1.2 Stable Counter的时钟控制 (36)6.1.3 Stable Counter的校准 (37)6.2 Node Counter (38)6.2.1 按地址访问 (38)6.3 时钟系统小结 (38)7 GPIO控制 (39)7.1 输出使能寄存器(0x0500) (39)7.2 输入输出寄存器(0x0508) (39)7.3 中断控制寄存器(0x0510) (39)7.4 GPIO引脚功能复用表 (40)7.5 GPIO中断控制 (41)8 LA464处理器核 (43)8.1 3C5000L实现的指令集特性 (43)8.2 3C5000L配置状态寄存器访问 (47)9 共享Cache(SCache) (48)10 处理器核间中断与通信 (51)10.1 按地址访问模式 (51)10.2 配置寄存器指令访问 (53)10.3 配置寄存器指令调试支持 (54)11 I/O中断 (56)11.1 传统I/O中断 (56)11.1.1 按地址访问 (58)11.1.2 配置寄存器指令访问 (59)11.2 扩展I/O中断 (59)11.2.1 按地址访问 (60)11.2.2 配置寄存器指令访问 (63)11.2.3 扩展IO中断触发寄存器 (63)11.2.4 扩展IO中断与传统HT中断处理的区别 (64)12 温度传感器 (65)12.1 实时温度采样 (65)12.2 高低温中断触发 (65)12.3 高温自动降频设置 (67)12.4 温度状态检测与控制 (68)12.5 温度传感器的控制 (69)13 DDR4 SDRAM控制器配置 (71)13.1 DDR4 SDRAM控制器功能概述 (71)13.2 DDR4 SDRAM读操作协议 (72)13.3 DDR4 SDRAM写操作协议 (72)13.4 DDR4 SDRAM参数配置格式 (72)13.4.1 内存控制器的参数列表 (72)13.5 软件编程指南 (84)13.5.1 初始化操作 (84)13.5.2 复位引脚的控制 (84)13.5.3 Leveling (86)13.5.4 功耗控制配置流程 (88)13.5.5 单独发起MRS命令 (88)13.5.6 任意操作控制总线 (89)13.5.7 自循环测试模式控制 (89)13.5.8 ECC功能使用控制 (90)13.5.9 出错状态观测 (90)III14 HyperTransport控制器 (94)14.1 HyperTransport硬件设置及初始化 (94)14.2 HyperTransport协议支持 (96)14.3 HyperTransport中断支持 (97)14.3.1 PIC中断 (97)14.3.2 本地中断处理 (98)14.3.3 扩展中断处理 (98)14.4 HyperTransport地址窗口 (99)14.4.1 HyperTransport空间 (99)14.4.2 HyperTransport控制器内部窗口配置 (99)14.5 配置寄存器 (100)14.5.1 Bridge Control (104)14.5.2 Capability Registers (105)14.5.3 Error Retry 控制寄存器 (107)14.5.4 Retry Count 寄存器 (108)14.5.5 Revision ID 寄存器 (108)14.5.6 Interrupt Discovery & Configuration (109)14.5.7 中断向量寄存器 (110)14.5.8 中断使能寄存器 (113)14.5.9 Link Train 寄存器 (115)14.5.10 接收地址窗口配置寄存器 (116)14.5.11 配置空间转换寄存器 (120)14.5.12 POST地址窗口配置寄存器 (121)14.5.13 可预取地址窗口配置寄存器 (122)14.5.14 UNCACHE地址窗口配置寄存器 (123)14.5.15 P2P地址窗口配置寄存器 (126)14.5.16 控制器参数配置寄存器 (128)14.5.17 接收诊断寄存器 (130)14.5.18 PHY 状态寄存器 (131)14.5.19 命令发送缓存大小寄存器 (131)14.5.20 数据发送缓存大小寄存器 (132)IVV14.5.22 接收缓冲区初始寄存器 (133)14.5.23 Training 0 超时短计时寄存器 (134)14.5.24 Training 0 超时长计时寄存器 (134)14.5.25 Training 1 计数寄存器 (135)14.5.26 Training 2 计数寄存器 (135)14.5.27 Training 3 计数寄存器 (135)14.5.28 软件频率配置寄存器 (136)14.5.29 PHY阻抗匹配控制寄存器 (137)14.5.30 PHY 配置寄存器 (138)14.5.31 链路初始化调试寄存器 (139)14.5.32 LDT调试寄存器 (139)14.5.33 HT TX POST ID窗口配置寄存器 (141)14.5.34 外部中断转换配置 (142)14.6 HyperTransport总线配置空间的访问方法 (143)15 低速IO控制器配置 (144)15.1 UART控制器 (144)15.1.1 数据寄存器(DAT) (144)15.1.2 中断使能寄存器(IER) (145)15.1.3 中断标识寄存器(IIR) (145)15.1.4 FIFO控制寄存器(FCR) (146)15.1.5 线路控制寄存器(LCR) (147)15.1.6 MODEM控制寄存器(MCR) (148)15.1.7 线路状态寄存器(LSR) (149)15.1.8 MODEM状态寄存器(MSR) (151)15.1.9 接收FIFO计数值(RFC) (151)15.1.10 发送FIFO计数值(TFC) (152)15.1.11 分频锁存器 (152)15.1.12 新增寄存器的使用 (153)15.2 SPI控制器 (153)15.2.1 控制寄存器(SPCR) (154)VI15.2.3 数据寄存器(TxFIFO) (155)15.2.4 外部寄存器(SPER) (156)15.2.5 参数控制寄存器(SFC_PARAM) (156)15.2.6 片选控制寄存器(SFC_SOFTCS) (157)15.2.7 时序控制寄存器(SFC_TIMING) (157)15.2.8 自定义控制寄存器(CTRL) (158)15.2.9 自定义命令寄存器(CMD) (158)15.2.10 自定义数据寄存器0(BUF0) (158)15.2.11 自定义数据寄存器1(BUF1) (159)15.2.12 自定义时序寄存器0(TIMER0) (159)15.2.13 自定义时序寄存器1(TIMER1) (159)15.2.14 自定义时序寄存器2(TIMER2) (159)15.2.15 SPI双线四线使用指南 (160)15.3 I2C控制器 (161)15.3.1 分频锁存器低字节寄存器(PRERlo) (161)15.3.2 分频锁存器高字节寄存器(PRERhi) (161)15.3.3 控制寄存器(CTR) (162)15.3.4 发送数据寄存器(TXR) (162)15.3.5 接收数据寄存器(RXR) (163)15.3.6 命令控制寄存器(CR) (163)15.3.7 状态寄存器(SR) (163)15.3.8 从设备控制寄存器(SLV_CTRL) (164)龙芯3C5000L处理器寄存器使用手册图目录VII 图目录图1-1龙芯3号系统结构 (1)图1-2龙芯3号结点结构 (2)图1-3龙芯3C5000L芯片互连结构 (3)图1-4龙芯3C5000L每硅片结构 (4)图6-1多片互连时的Stable复位控制 (38)图11-1龙芯3C5000L处理器中断路由示意图 (56)图13-1 DDR4 SDRAM读操作协议 (72)图13-2 DDR4 SDRAM写操作协议 (72)图14-1龙芯3C5000L中HT协议的配置访问 (143)表目录表2-1 控制引脚说明 (5)表3-1 结点级的系统全局地址分布 (7)表3-2 结点内的地址分布 (8)表3-3 SCID_SEL地址位设置 (8)表3-4 结点内44位物理地址分布 (9)表3-5 MMAP字段对应的该空间访问属性 (9)表3-6地址窗口寄存器表 (10)表3-7MMAP寄存器位域说明 (15)表3-8从设备号与所述模块的对应关系 (15)表3-9 MMAP字段对应的该空间访问属性 (16)表4-1 版本寄存器 (17)表4-2 芯片特性寄存器 (17)表4-3 厂商名称寄存器 (18)表4-4 芯片名称寄存器 (18)表4-5 功能设置寄存器 (18)表4-6 引脚驱动设置寄存器 (19)表4-7 功能采样寄存器 (19)表4-8 温度采样寄存器 (20)表4-9 结点时钟软件倍频设置寄存器 (21)表4-10 内存时钟软件倍频设置寄存器 (22)表4-11 处理器核软件分频设置寄存器 (23)表4-12 处理器核软件分频设置寄存器 (23)表4-13 芯片路由设置寄存器 (24)表4-14 其它功能设置寄存器 (24)表4-15 温度观测寄存器 (26)表4-16 处理器核SRAM调节寄存器 (26)表4-17 FUSE观测寄存器 (26)表4-18 FUSE观测寄存器 (27)表5-1 处理器内部时钟说明 (28)VIIIIX表5-2 处理器核软件分频设置寄存器 (29)表5-3 其它功能设置寄存器 (29)表5-4 其它功能设置寄存器 (30)表5-5 处理器核私有分频寄存器 (30)表5-6 功能设置寄存器 (31)表5-7 其它功能设置寄存器 (31)表5-8高温降频控制寄存器说明 (32)表5-9 功能设置寄存器 (32)表5-10 其它功能设置寄存器 (33)表5-11 其它功能设置寄存器 (33)表5-12 GPIO 输出使能寄存器 (34)表6-1地址访问方式 (35)表6-2 配置寄存器指令访问方式 (36)表6-3 寄存器含义 (36)表6-4其它功能设置寄存器 (36)表6-5 Node counter 寄存器 (38)表7-1 输出使能寄存器 (39)表7-2 输入输出寄存器 (39)表7-3 中断控制寄存器 (39)表7-4 GPIO 功能复用表 (40)表7-5 中断控制寄存器 (41)表8-1 3C5000L 实现的指令集功能配置信息列表 (44)表9-1 共享Cache 锁窗口寄存器配置 (48)表10-1处理器核间中断相关的寄存器及其功能描述 (51)表10-2 0号处理器核的核间中断与通信寄存器列表 (51)表10-3 1号处理器核的核间中断与通信寄存器列表 (52)表10-4 2号处理器核的核间中断与通信寄存器列表 (52)表10-5 3号处理器核的核间中断与通信寄存器列表 (52)表10-6 当前处理器核核间中断与通信寄存器列表 (53)表10-7 处理器核核间通信寄存器 (53)表10-8 处理器核核间通信寄存器 (55)X表11-1中断控制寄存器 (57)表11-2 IO 控制寄存器地址 (58)表11-3中断路由寄存器的说明 (58)表11-4中断路由寄存器地址 (58)表11-5 处理器核私有中断状态寄存器 (59)表11-6 其它功能设置寄存器 (60)表11-7 扩展IO 中断使能寄存器 (60)表11-8 扩展IO 中断自动轮转使能寄存器 (60)表11-9 扩展IO 中断状态寄存器 (60)表11-10 各处理器核的扩展IO 中断状态寄存器 (61)表11-11中断引脚路由寄存器的说明 (61)表11-12中断路由寄存器地址 (62)表11-13 中断目标处理器核路由寄存器的说明 (62)表11-14 中断目标处理器核路由寄存器地址 (62)表11-15中断目标结点映射方式配置 (63)表11-16当前处理器核的扩展IO 中断状态寄存器 (63)表11-17扩展IO 中断触发寄存器 (63)表12-1温度采样寄存器说明 (65)表12-2扩展IO 中断触发寄存器 (65)表12-3高低温中断寄存器说明 (66)表12-4高温降频控制寄存器说明 (67)表12-5温度状态检测与控制寄存器说明 (69)表12-6温度传感器配置寄存器说明 (69)表12-7温度传感器监测点说明 (70)表13-1 内存控制器软件可见参数列表 (72)表13-2 0号内存控制器出错状态观测寄存器 (90)表13-3 1号内存控制器出错状态观测寄存器 (92)表14-1 HyperTransport 总线相关引脚信号 (94)表14-2 HyperTransport 接收端可接收的命令 (96)表14-3 两种模式下会向外发送的命令 (97)表14-4 其它功能设置寄存器 (98)XI表14-5 默认的4个HyperTransport 接口的地址窗口分布 (99)表14-6 龙芯3号处理器HyperTransport 接口内部的地址窗口分布 (99)表14-7 龙芯3C5000L 处理器HyperTransport 接口中提供的地址窗口 (100)表14-8 Bus Reset Control 寄存器定义 (104)表14-9 Command ,Capabilities Pointer ,Capability ID 寄存器定义 (105)表14-10 Link Config ,Link Control 寄存器定义 (105)表14-11 Revision ID ,Link Freq ,Link Error ,Link Freq Cap 寄存器定义 (106)表14-12 Feature Capability 寄存器定义 (107)表14-13 Error Retry 控制寄存器 (107)表14-14 Retry Count 寄存器 (108)表14-15 Revision ID 寄存器 (108)表14-16 Interrupt Capability 寄存器定义 (109)表14-17 Dataport 寄存器定义 (109)表14-18 IntrInfo 寄存器定义(1) (109)表14-19 IntrInfo 寄存器定义(2) (109)表14-20 HT 总线中断向量寄存器定义(1) (111)表14-21 HT 总线中断向量寄存器定义(2) (111)表14-22 HT 总线中断向量寄存器定义(3) (112)表14-23 HT 总线中断向量寄存器定义(4) (112)表14-24 HT 总线中断向量寄存器定义(6) (112)表14-25 HT 总线中断向量寄存器定义(7) (112)表14-26 HT 总线中断向量寄存器定义(8) (113)表14-27 HT 总线中断使能寄存器定义(1) (114)表14-28 HT 总线中断使能寄存器定义(2) (114)表14-29 HT 总线中断使能寄存器定义(3) (114)表14-30 HT 总线中断使能寄存器定义(4) (114)表14-31 HT 总线中断使能寄存器定义(5) (115)表14-32 HT 总线中断使能寄存器定义(6) (115)表14-33 HT 总线中断使能寄存器定义(7) (115)表14-34 HT 总线中断使能寄存器定义(8) (115)表14-35 Link Train 寄存器 (116)表14-37 HT总线接收地址窗口0基址(外部访问)寄存器定义 (117)表14-38 HT总线接收地址窗口1使能(外部访问)寄存器定义 (117)表14-39 HT总线接收地址窗口1基址(外部访问)寄存器定义 (118)表14-40 HT总线接收地址窗口2使能(外部访问)寄存器定义 (118)表14-41 HT总线接收地址窗口2基址(外部访问)寄存器定义 (118)表14-42 HT总线接收地址窗口3使能(外部访问)寄存器定义 (119)表14-43 HT总线接收地址窗口3基址(外部访问)寄存器定义 (119)表14-44 HT总线接收地址窗口4使能(外部访问)寄存器定义 (119)表14-45 HT总线接收地址窗口4基址(外部访问)寄存器定义 (120)表14-46配置空间扩展地址转换寄存器定义 (120)表14-47扩展地址转换寄存器定义 (121)表14-48 HT总线POST地址窗口0使能(内部访问) (121)表14-49 HT总线POST地址窗口0基址(内部访问) (121)表14-50 HT总线POST地址窗口1使能(内部访问) (122)表14-51 HT总线POST地址窗口1基址(内部访问) (122)表14-52 HT总线可预取地址窗口0使能(内部访问) (122)表14-53 HT总线可预取地址窗口0基址(内部访问) (123)表14-54 HT总线可预取地址窗口1使能(内部访问) (123)表14-55 HT总线可预取地址窗口1基址(内部访问) (123)表14-56 HT总线Uncache地址窗口0使能(内部访问) (124)表14-57 HT总线Uncache地址窗口0基址(内部访问) (124)表14-58 HT总线Uncache地址窗口1使能(内部访问) (124)表14-59 HT总线Uncache地址窗口1基址(内部访问) (125)表14-60 HT总线Uncache地址窗口2使能(内部访问) (125)表14-61 HT总线Uncache地址窗口2基址(内部访问) (126)表14-62 HT总线Uncache地址窗口3使能(内部访问) (126)表14-63 HT总线Uncache地址窗口3基址(内部访问) (126)表14-64 HT总线P2P地址窗口0使能(外部访问)寄存器定义 (127)表14-65 HT总线P2P地址窗口0基址(外部访问)寄存器定义 (127)表14-66 HT总线P2P地址窗口1使能(外部访问)寄存器定义 (127)XII表14-68 控制器参数配置寄存器0定义 (128)表14-69 控制器参数配置寄存器1定义 (129)表14-70接收诊断寄存器 (130)表14-71 PHY状态寄存器 (131)表14-72 命令发送缓存大小寄存器 (131)表14-73 数据发送缓存大小寄存器 (132)表14-74发送缓存调试寄存器 (132)表14-75接收缓冲区初始寄存器 (134)表14-76 Training 0 超时短计时寄存器 (134)表14-77 Training 0 超时长计数寄存器 (134)表14-78 Training 1 计数寄存器 (135)表14-79 Training 2 计数寄存器 (135)表14-80 Training 3 计数寄存器 (135)表14-81 软件频率配置寄存器 (137)表14-82 阻抗匹配控制寄存器 (137)表14-83 PHY 配置寄存器 (138)表14-84 链路初始化调试寄存器 (139)表14-85 LDT调试寄存器1 (139)表14-86 LDT调试寄存器2 (140)表14-87 LDT调试寄存器3 (140)表14-88 LDT调试寄存器4 (140)表14-89 LDT调试寄存器5 (140)表14-90 LDT调试寄存器5 (141)表14-91 HT TX POST ID WIN0 (141)表14-92 HT TX POST ID WIN1 (141)表14-93 HT TX POST ID WIN2 (141)表14-94 HT TX POST ID WIN3 (142)表14-95 HT RX INT TRANS LO (142)表14-96 HT RX INT TRANS Hi (142)表15-1 SPI控制器地址空间分布 (154)XIIIXIV11 概述1.1 龙芯系列处理器介绍龙芯处理器主要包括三个系列。

第6章 8086指令系统与汇编基础

第13页

2013年8月1日星期四

第6章

8086指令系统与汇编基础 3.段地址寄存器

有 CS、DS、ES、SS 四 个 , 分 别 表 示 程 序 码 ( code segment register)、 数 据 ( data segment register)、附加(extra segment register)、堆栈 (stack segment register)段地址用。在 DOS 系统 中,每一个段地址容量只有 64KBytes。 当数据段地址不够用时,就可以用附加数据段地址 来补足,例如想要将一个段地址的某些内容复制到 另一段地址中,就可以同时指定 DS、ES 分别表示 这两个段地址。

第17页 2013年8月1日星期四

第6章

6.2.4

8086指令系统与汇编基础

寄存器间接寻址(Register Indirect Addressing) 寄存器间接寻址方式中,操作数存放在存储器 中,但操作数的有效地址EA在基址寄存器BX、BP或 变址寄存器SI、DI中。操作数的物理地址为: 物理地址=16(段寄存器)+(寄存器)

执行结果为:(AX)=8060H 指令中也可指定段跨越前缀以取得其它段中的 数据。如:MOV AX,ES:[BX]指令,则从附加段中 取得数据。

操作码

DS 3000 0 BX + 200 0

代 码

段

30000 32000 AH AL

60 80

3200 0

数 据

段

图 6- 2- 2

例 6 - 5 的执行过程

第3页 2013年8月1日星期四

第6章

8086指令系统与汇编基础

计算机只能识别二进制代码,因此计算机能执行 的指令必须以二进制代码的形式表示,这种以二进制 代码形式表示的指令称为指令的机器码(Machine Code)。 2.汇编指令格式 一条指令一般包含操作码和操作数两部分。

微机原理与接口技术-六章-程序设计

汇编语言程序设计步骤:

开始

处理

处理

结束

处理

Y

N

6.2 简单程序(1)

例:将内存单元10050H的内容拆成两段,每段4位,分别存 入10051H(低4位)和10052H(高4位)单元。即 10051H和10052H单元的高4位都为0。

⑥静态检查程序是否有错

6.3 分支程序(1)

N 条件满足? 语句系列1 语句系列2 N

例:编一个程序。从外设71H取一个数M,判断其值是否在10和 20之间,即10≤M<20。如果M≥20,则送0FFH给外设73H; 如果M<10,则送00H给外设73H;如果10≤M<20, 则送88H给外设73H。

子程序中对堆栈的压入和弹出操作要成对使用,保持堆栈的平衡。

子程序要利用过程定义伪指令声明。

一、子程序编写注意事项

二、举例

例:

code segment main proc far ...... call subr1 ...... ret main endp subr1 proc near ...... ret subr1 endp code ends

DP5 PROC NEAR MOV AL,CL SAL AL,1 SAL AL,1 ADD AL,CL MOV CL,AL RET DP5 ENDP MY ENDS END START AL=? BL=? CL=?

汇编语言中,子程序要用一对过程伪指令PROC和ENDP声明,格式如下: 过程名 PROC [NEAR/FAR] …… ;过程体 …… 过程名 ENDP NEAR属性(段内近调用) FAR属性(段间远调用)

提供必要的子程序说明信息。

处理好子程序与主程序间的参数传递问题。

汇编语言寄存器详解

汇编语言寄存器详解汇编语言是一种底层程序设计语言,与高级语言相比,汇编语言更接近于计算机硬件层面。

在汇编语言中,寄存器是一种非常重要的概念,它们用于存储数据和指令,以及进行计算和操作。

在本文中,我们将详细介绍汇编语言中常用的寄存器及其作用。

1. 通用寄存器通用寄存器是汇编语言中最基本的寄存器,它们可以用于存储数据、指针和地址等信息。

在x86架构中,通用寄存器有8个,分别为:AX,BX,CX,DX,SI,DI,BP和SP。

其中,AX,BX,CX和DX是16位寄存器,也就是说它们可以存储16位的数据。

SI和DI是用于存储指针和地址的寄存器,BP和SP 则是用于存储栈指针的寄存器。

2. 段寄存器在汇编语言中,除了通用寄存器以外,还有一种特殊的寄存器,叫做段寄存器。

段寄存器用于存储内存中某个段的起始地址,它们可以帮助程序员在内存中定位某个数据或指令。

在x86架构中,有4个段寄存器,分别为:CS,DS,SS和ES。

其中,CS用于存储代码段的地址,DS用于存储数据段的地址,SS用于存储堆栈段的地址,ES则可以用作附加段寄存器。

3. 标志寄存器标志寄存器是一种特殊的寄存器,它们用于存储程序运行中的各种状态信息。

在x86架构中,有一个标志寄存器,叫做FLAGS寄存器,它包含了各种标志位,用于表示程序运行中的各种状态信息。

其中,比较常用的标志位有:ZF(零标志位),CF(进位标志位),OF(溢出标志位)等。

这些标志位可以帮助程序员判断程序运行中的各种状态,从而进行相应的处理。

总的来说,寄存器是汇编语言中非常重要的概念,程序员需要熟练掌握各种寄存器的作用和用法,才能够编写出高效、正确的汇编程序。

Verilog语言基础知识

在Verilog HDL中,用parameter来定义常量,即用parameter来定义一个标志符,代表一个常量,称为符号常量。其定义格式如下:

parameter 参数名1=表达式,参数名2=表达式,参数名3=表达式……;

例如:

parameter sel=8,code=8'ha3;

//分别定义参数sel为常数8(十进制),参数code为常数a3(十六进制)

Verilog HDL中共有19种数据类型。数据类型是用来表示数字电路中的数据存储和传送单元的。在此介绍4个最基本的数据类型:integer型、parameter型、reg型和wire型。

Verilog HDL中也有常量和变量之分,他们分属以上这些类型。

6.2.1 常量

在程序运行过程中,其值不能被改变的量称为常量。

assign {cout,sum}=ina+inb+cin;//全加

endmodule

【例6.2】一个8位计数器的Verilog HDL源代码

module counter8(out,cout,data,load,cin,clk);

output[7:0]out;

output cout;

input[7:0] data;

6.1.2 Verilog HDL模块的结构

Verilog HDL的基本设计单元是"模块(block)"。一个模块是由两部分组成的,一部分描述接口;另一部分描述逻辑功能,即定义输入是如何影响输出的。下面举例说明,图6.1示出了一个"与-或-非"门电路。

图6.1"与-或-非"电路

该电路表示的逻辑函数可以写为:

6.2.2 变量

【汇编】各种寄存器介绍

【汇编】各种寄存器介绍计算机寄存器分类简介:32位CPU所含有的寄存器有:4个数据寄存器(EAX、EBX、ECX和EDX)2个变址和指针寄存器(ESI和EDI) 2个指针寄存器(ESP和EBP)6个段寄存器(ES、CS、SS、DS、FS和GS)1个指令指针寄存器(EIP) 1个标志寄存器(EFlags)1、数据寄存器数据寄存器主要⽤来保存操作数和运算结果等信息,从⽽节省读取操作数所需占⽤总线和访问存储器的时间。

32位CPU有4个32位的通⽤寄存器EAX、EBX、ECX和EDX。

对低16位数据的存取,不会影响⾼16位的数据。

这些低16位寄存器分别命名为:AX、BX、CX和DX,它和先前的CPU中的寄存器相⼀致。

4个16位寄存器⼜可分割成8个独⽴的8位寄存器(AX:AH-AL、BX:BH-BL、CX:CH-CL、DX:DH-DL),每个寄存器都有⾃⼰的名称,可独⽴存取。

程序员可利⽤数据寄存器的这种“可分可合”的特性,灵活地处理字/字节的信息。

寄存器EAX通常称为累加器(Accumulator),⽤累加器进⾏的操作可能需要更少时间。

可⽤于乘、除、输⼊/输出等操作,使⽤频率很⾼;寄存器EBX称为基地址寄存器(Base Register)。

它可作为存储器指针来使⽤;寄存器ECX称为计数寄存器(Count Register)。

在循环和字符串操作时,要⽤它来控制循环次数;在位操作中,当移多位时,要⽤CL来指明移位的位数;寄存器EDX称为数据寄存器(Data Register)。

在进⾏乘、除运算时,它可作为默认的操作数参与运算,也可⽤于存放I/O的端⼝地址。

在16位CPU中,AX、BX、CX和DX不能作为基址和变址寄存器来存放存储单元的地址,在32位CPU中,其32位寄存器EAX、EBX、ECX和EDX不仅可传送数据、暂存数据保存算术逻辑运算结果,⽽且也可作为指针寄存器,所以,这些32位寄存器更具有通⽤性。

2、变址寄存器32位CPU有2个32位通⽤寄存器ESI和EDI。

MCS51的串行口PPT

6.1.2 特殊功能寄存器PCON

字节地址为87H,没有位寻址功能。

SMOD:波特率选择位。 例如:方式1旳波特率旳计算公式为: 方式1波特率=(2SMOD/32)×定时器T1旳溢出率

图6-14 流水灯显示电路图

ORG 0000H LJMP MAIN ORG 2023H MAIN: MOV SCON,#00H ;置串行口工作方式0 MOV A,#80H :最高位灯先亮 CLR P1.1 ;关闭并行输出(避象传播过程中,各 LED旳“暗红”现象) OUT0: MOV SBUF,A ;开始串行输出 OUT1: JNB TI,OUT1 ;输出完否? CLR TI ;完了,清TI标志,以备下次发送 SETB P1.1 ;打开并行口输出 ACALL DELAY ;延时一段时间 RR A ;循环右移 CLR P1.1;关闭并行输出 SJMP OUT0;循环 DELAY: …………;延时子程序,不再反复

假如SM2=0,则不论第9位数据是“1”还是“0”,都 将 前8位数据送入SBUF中,并置“1” RI,产生 中断祈求。

在方式1时,假如SM2=1,则只有收到停止位时才会激 活RI。

在方式0时,SM2必须为0。

(3)REN——允许串行接受位

由软件置“1”或清“0”。

REN=1 允许串行口接受数据。 REN=0 禁止串行口接受数据。 (4)TB8——发送旳第9位数据 方式2和3时,TB8是要发送旳第9位数据,可作为奇偶 校验位使用,也可作为地址帧或数据帧旳标志。 =1为地址帧, =0为数据帧 (5)RB8——接受到旳第9位数据 方式2和3时,RB8存储接受到旳第9位数据。在方式1 ,假如SM2=0,RB8是接受到旳停止位。在方式0, 不使用RB8。 (6)TI——发送中断标志位

汇编语言中寄存器介绍

汇编语言中寄存器介绍寄存器是汇编语言中非常重要的概念,它们用于存储和操作数据。

在本文中,将介绍汇编语言中常用的寄存器,并详细解释它们的功能和用途。

1. 通用寄存器通用寄存器是最常用的寄存器,在汇编语言中使用频率较高。

通常有四个通用寄存器,分别是AX、BX、CX和DX。

这些寄存器既可用于存储数据,也可用于进行算术运算。

例如,将数据从内存加载到通用寄存器中,进行加法或减法运算,然后将结果存回内存。

2. 累加器寄存器累加器寄存器是AX寄存器的别名。

AX寄存器在处理循环和计数时非常有用。

它还可以用于存储需要频繁访问的数据,例如需要进行累加或累减的数值。

3. 基址寄存器基址寄存器是BX寄存器的别名。

它与偏移量配合使用,用于计算内存地址。

通常在存储大量数据的数组或缓冲区中使用。

4. 计数器寄存器计数器寄存器是CX寄存器的别名。

CX寄存器在处理循环时非常有用。

它可以作为循环计数器,用于控制循环的次数。

5. 数据寄存器数据寄存器是DX寄存器的别名。

它可以存储需要进行输入/输出操作的数据,例如从键盘读取的字符或向屏幕输出的字符。

数据寄存器还可以用于存放在算术运算中需要使用的常数。

6. 标志寄存器标志寄存器用于存储处理器运行过程中的状态信息,例如进位标志、零标志、符号标志等。

它们对于程序的条件分支非常重要,可以根据不同的标志位执行相应的操作。

7. 段寄存器段寄存器用于指示在内存中的位置。

在实模式下,由于地址总线的限制,内存地址仅能表示64KB。

因此,通过使用段寄存器,可以将内存地址拓展到1MB甚至更大。

常用的段寄存器有CS(代码段寄存器)、DS(数据段寄存器)、SS(堆栈段寄存器)和ES(附加段寄存器)。

8. 指令寄存器指令寄存器(IP)用于存储当前执行的指令在内存中的地址。

它是程序执行的关键寄存器之一,能够实现指令的顺序执行。

在汇编语言中,寄存器是程序设计中不可或缺的组成部分。

通过合理地使用和操作寄存器,能够提高程序的执行效率和性能。

(整理)寄存器说明图表.

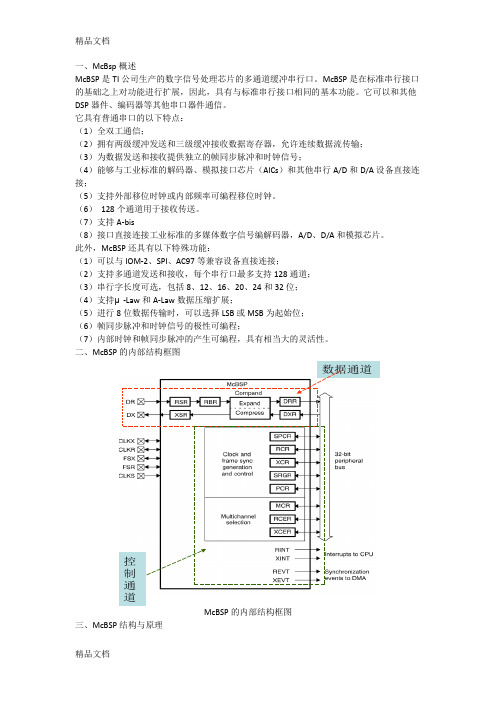

一、McBsp概述McBSP是TI公司生产的数字信号处理芯片的多通道缓冲串行口。

McBSP是在标准串行接口的基础之上对功能进行扩展,因此,具有与标准串行接口相同的基本功能。

它可以和其他DSP器件、编码器等其他串口器件通信。

它具有普通串口的以下特点:(1)全双工通信;(2)拥有两级缓冲发送和三级缓冲接收数据寄存器,允许连续数据流传输;(3)为数据发送和接收提供独立的帧同步脉冲和时钟信号;(4)能够与工业标准的解码器、模拟接口芯片(AICs)和其他串行A/D和D/A设备直接连接;(5)支持外部移位时钟或内部频率可编程移位时钟。

(6)128个通道用于接收传送。

(7)支持A-bis(8)接口直接连接工业标准的多媒体数字信号编解码器,A/D、D/A和模拟芯片。

此外,McBSP还具有以下特殊功能:(1)可以与IOM-2、SPI、AC97等兼容设备直接连接;(2)支持多通道发送和接收,每个串行口最多支持128通道;(3)串行字长度可选,包括8、12、16、20、24和32位;(4)支持μ-Law和A-Law数据压缩扩展;(5)进行8位数据传输时,可以选择LSB或MSB为起始位;(6)帧同步脉冲和时钟信号的极性可编程;(7)内部时钟和帧同步脉冲的产生可编程,具有相当大的灵活性。

二、McBSP的内部结构框图McBSP的内部结构框图三、McBSP结构与原理数据通道控制通道四、McBsp数据压缩功能。

图1-1 DXR数据发送寄存器图1-2 XSR数据发送移位寄存器表1-2 数据发送移位寄存器(XSR)位段说明图1-3 DRR数据接收寄存器表1-3 数据接收寄存器(DRR)位段说明图1-4 RBR数据接收缓存寄存器表1-4 数据接收缓存寄存器(RBR)位段说明图1-5 RSR数据接收移位寄存器表1-5 数据接收移位寄存器(RSR)位段说明图1-6 SPCR串口控制寄存器表1-6 串口控制寄存器(SPCR)位段说明图1-7 RCR接收控制寄存器表1-7 接收控制寄存器(RCR)位段说明图1-8 XCR发送控制寄存器表1-8 发送控制寄存器(XCR)位段说明图1-9 SRGR采样率发生控制寄存器表1-9采样率发生控制寄存器(SRGR)位段说明图1-10 MCR多通道控制寄存器表1-10多通道控制寄存器(MCR)位段说明图1-11 RCER接收通道使能寄存器表1-11 接收通道使能寄存器(RCER)位段说明图1-12 XCER发送通道使能寄存器表1-12 发送通道使能寄存器(XCER)位段说明图1-13 RCERE增强的接收通道使能寄存器0-3表1-13 增强的接收通道使能寄存器(RCERE)位段说明图1-14 XCERE增强的发送通道使能寄存器0-3 表1-14 增强的发送通道使能寄存器(RCERE)位段说明图1-15 PCR引脚控制寄存器表1-15 引脚控制寄存器(PCR)位段说明自定义数据结构1.数据接收三级缓存寄存器状态表1-16数据接收三级缓存寄存器状态段说明2.PC串口使能表1-16 PC串口使能段说明***********************华丽的分割线***********************************。

第6章 应用指令

• 6.3 比较、传送与数据变换指令

• 6.3.1 比较指令

• 比较指令包括CMP(比较)和ZCP(区间比较), 比较结果用目标元件的状态来表示。 • (1)比较指令CMP • (2)区间比较指令ZCP • 如下图

图6.9 比较指令

图6.10 区间比较指令

(3)触点型比较指令触点型比较指令相当于一 个触点,执行时比较源操作数[ S1· ]和 [S2· ],满足比较条件则触点闭合,源操作 数 可 以 取 所 有 的 数 据 类 型 。

图6.44 绝对值式凸轮顺控指令

(2) 增量式凸轮顺控指令 INCD :源操作数 和 目 标 操 作 数 与 ABSD 指 令 的 相 同 , 1≤n≤64,该指令只能使用一次。

图6.45 增量式凸轮顺控指令

6.8.2 定时器指令 • (1)示教定时器指令TTMR:目标操作数[D· ] 为D,n=0~2。使用TTMR指令可以用一 只按钮调整定时器的设定时间。

图6.25 字右移

图6.26 字左移

• 6.5.3 先入先出写入与读出指令 • (1)先入先出写入指令 • FIFO(first in first out,先入先出)写入指令 SFWR • (2)先入先出读出指令 • FIFO读出指令SFRD

图6.27 移位寄存器写入指令

图6.28 移位寄存器读出指令

图6.3 CJ指令的使用

图6.4 跳转指令的应用

• 6.2.2 子程序调用与子程序返回指令 • FX1S 的子程序调用指令 CALL 的操作数为 P0 ~ P62 , 其 他 系 列 的 操 作 数 为 P0 ~ P127( 不包括 P63) ,子程序返回指令 SRET 无操作数。

图6.5 子程序的嵌套调用

图6.39 高速计数器比较置位与比较复位指令

7指令系统1

一方面,会影响处理器执行指令的速度和效率 另一方面,对程序设计也很重要

MOV指令

6.1.3.1 立即数寻址方式

指令中的操作数直接存放在机器代码中,紧跟 在操作码之后(操作数作为指令的一部分存放 在操作码之后的主存单元中) 这种操作数被称为立即数imm 可以是8位数值i8(00H~FFH) 也可以是16位数值i16(0000H~FFFFH) 立即数寻址方式常用来给寄存器和存储单元赋 值,多以常量形式出现

6.1.3 8088/8086的寻址方式

寻址方式 : CPU在执行指令时确定操作数地址的方法。 四种基本寻址方式:

立即数寻址

寄存器寻址 直接寻址 寄存器间接寻址

Hale Waihona Puke 对存储器寻址操作数的寻址方式

指令系统设计了多种操作数的来源 寻找操作数的过程就是操作数的寻址 把寻找操作数的方式叫做(操作数)寻址方式 理解操作数的寻址方式是理解指令功能的前提 操作数采取哪一种寻址方式

;AX←DS:[BX+SI]

演示

MOV AX, [BX][SI]

;AX←DS:[BX+SI]

基址加变址寻址

操作数的地址为基址寄存器内容加上变址寄存器内容

当用BX做基址寄存器,则默认段地址寄存器为DS 当用BP做基址寄存器,则默认段地址寄存器为SS 例:MOV AX,[BX+DI] MOV [BP+SI],DX MOV BX, [BP][DI]

MOV AX, 0102H

;AX←0102H

演示

立即数寻址

例:MOV AL,5

MOV BX,3064H

5 和3064H为立即数

• 立即数寻址方式主要用在对寄存器赋值,运

寄存器表示方法

寄存器表示方法

一。

寄存器是计算机硬件中的重要组成部分,就像人的大脑中的记忆细胞一样,负责存储各种关键的数据和指令。

1.1 寄存器的种类繁多,比如通用寄存器,它就像一个多面手,能处理各种各样的数据。

还有专用寄存器,那可是有着特定任务的高手,专门负责特定的操作。

1.2 寄存器的大小也是有讲究的。

有的寄存器可能只有几个比特,而有的能达到几十个比特。

这就好比不同大小的容器,装的东西多少不一样。

二。

寄存器的工作速度那可是相当快的,简直是风驰电掣。

2.1 它能够在极短的时间内完成数据的读取和写入,一点都不拖泥带水。

2.2 而且寄存器的准确性也是没得说,真可谓是“分毫不差”,保证了计算机运行的稳定和可靠。

2.3 寄存器的存在让计算机的运行效率大大提高,就像给汽车装上了超强的引擎。

三。

在实际应用中,寄存器发挥着巨大的作用。

3.1 比如说在处理器的运算过程中,寄存器充当着临时存储数据的角色,让计算能够快速进行。

3.2 再比如在控制指令的执行时,寄存器准确地传递着各种信息,确保每一个指令都能被正确执行,真可谓是“指哪打哪”。

寄存器虽然看似不起眼,但却是计算机运行中不可或缺的重要角色,没有它,计算机可就没法高效、准确地工作啦!。

汇编语言第六章

三.中断向量表

3. 设置或取出中断向量指令 (1) 设置中断向量指令 功能:把由AL指定的中断类型的中断向量DS:DX放入中

断向量表中。

(AH)= 25H

(AL)= 中断类型号

DS:DX = 中断向量 INT 21H

三.中断向量表

(2) 取出中断向量指令

功能:把AL中指定的中断类型的中断向量从中断

一、 WIN32编程基础

(2) 循环控制伪指令

格式:.WHILE 条件表达式 循环体 .ENDW 格式:.REPEAT 循环体 .UNTIL 条件表达式 格式:.CONTINUE 功能:终止本次循环, 开始下一次循环 格式:.BREAK 功能:退出当前循环

功能:实现循环结构

一、 WIN32编程基础

内中断的处理特点: ①中断类型号一般在指令中; ② 不受中断允许标志位IF的影响。

二、 中断源

2. 外中断 由外设控制器、协处理器等CPU以外的事件引起的中断, 称为外中断。 外中断的处理特点: ① 中断类型号由8259A提供,或由自制电路来提供;

② 受中断允许标志位IF的影响(IF=1,响应中断)。

个字节。

三.中断向量表

如:INT 4AH

中断向量地址 = 4AH*4 = 128H

DEBUG执行后, 用D命令查看: ―D0:0↙ … 执行INT 4AH时: IP=1805H CS=F000H IP F000: 1805 中断处理

0:128H

0:129H

05 18

0:12AH

0:12BH

00

F0 …

外设

二、 外设与主机传送的接口与信息

接口的组成:设备状态寄存器、设备控制寄存 器、数据寄存器。 I/O端口的地址空间:允许设置64K个8位端口 或32K个16位端口。 如:40H~43H时钟/定时器,60H~63H为 8255通讯芯片的接口。

第六章子程序结构

6.4.3、堆栈传递参数 子程序可以利用堆栈传递参数。例如C语言中,函数的参数传递就是利用堆栈。 首先要了解堆栈的构造和工作原理: 堆栈段使用段寄存器SS。在CALL指令、RET指令、PUSH指令、POP指令中, 按照“后进先出”的原则工作,并使用SP寄存器内容为堆栈顶偏移量指令。 使用BP为指针存取数据,默认的段寄存器也是SS,因此,BP也常常用来作存 取堆栈中数据的偏移量指针。 堆栈顶是变化的,随着压栈操作,堆栈顶向低地址方向生长。 压栈操作,堆栈顶向低地址方向生长 压栈操作 对堆栈的压栈操作和弹出堆栈操作必须平衡。

例:在数据串STR1中有20个字数据,数据串STR2中有5个字数据,编程。在 STR1中查找子串STR2,找到则把BL置为1,否则把BL置为0。 先编一个比较字数据串的子程序CMPSTR。 子程序名:CMPSTR 功能:把STR2与SI指到的字数据串比较(只比较前5个元素),相同则返回ZF= 1,否则返回ZF=0。 入口参数:SI指到一个数据串。 出口参数:两个串相同则返回ZF=1,否则返回ZF=0 程序: CMPSTR: LEA DI,STR2 MOV CX ,5 CLD REPZ CMPSW RET

SP

×× ×× ## ## %% SP %% ◎◎ ◎◎

ARY 地址 COUNT 地址 SUM 地址

×× ×× ## ## %% %% ◎◎ ◎◎

低地址

问题:取堆栈中的数据能否使用BX、SI、DI作指针? 答:可以,但是必须用段超越。如: PROADD PROC NEAR

MOV SI,SP MOV MOV SUB LP: ADD INC INC LOOP MOV MOV RET PROADD ENDP BX,SS:[SI +6] ;取ARY首地址 C X,SS:[SI+4] ;取数据个数 AX ,AX AX,[BX ] BX BX LP BX,SS:[SI+2] ;取SUM地址 [BX] ,AX 6 ;存和数 ;返回,并且使SP=SP+6

汇编语言程序设计(第二版)课后题答案

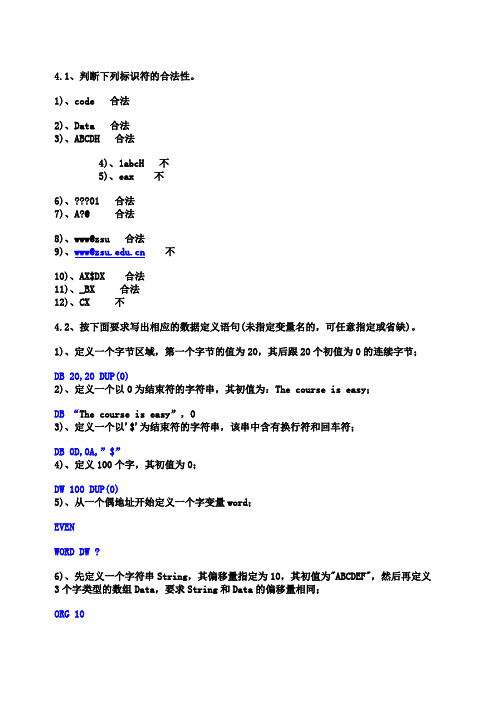

4.1、判断下列标识符的合法性。

1)、code 合法2)、Data 合法3)、ABCDH 合法4)、1abcH 不5)、eax 不6)、01 合法7)、A?@ 合法8)、www@zsu 合法9)、***********.cn不10)、AX$DX 合法11)、_BX 合法12)、CX 不4.2、按下面要求写出相应的数据定义语句(未指定变量名的,可任意指定或省缺)。

1)、定义一个字节区域,第一个字节的值为20,其后跟20个初值为0的连续字节;DB 20,20 DUP(0)2)、定义一个以0为结束符的字符串,其初值为:The course is easy;DB “The course is easy”,03)、定义一个以'$'为结束符的字符串,该串中含有换行符和回车符;DB 0D,0A,”$”4)、定义100个字,其初值为0;DW 100 DUP(0)5)、从一个偶地址开始定义一个字变量word;EVENWORD DW ?6)、先定义一个字符串String,其偏移量指定为10,其初值为"ABCDEF",然后再定义3个字类型的数组Data,要求String和Data的偏移量相同;ORG 10STRING DB "ABCDEF"ORG 10DATA DW 3 DUP(?)7)、定义一个字符串String,其初值为"12345678",再定义4个字类型的数组Data,要求String和Data共享同一片内存单元;STRING DB "12345678"ORG $-8DATA DW 4 DUP (?)4.3、把下列C语言的变量定义语句改写成与之等价的汇编语言语句。

1)、char ch1, ch2[3], ch3[]="Are you ready?", ch4='Q';CH1 DB ?CH2 DB 3 DUP (?)CH3 DB "Are you ready?",0CH4 DB “Q”2)、int w1, w2[5], w3=0x1234, w4[]={90, 89, 432, 344};W1 DW ?W2 DW 5 DUP (?)W3 DW 1234HW4 DW 90,89,432,3443)、long int d1=1234, d2, d3[10], d4[]={1, 2, 3, 4, 5, 6};D1 DD 1234D2 DD ?D3 DD 10 DUP(?)D3 DD 1,2,3,4,5,64.4、假设4.3题中三组变量在内存中是连续存放的,且变量ch1的偏移量是20H,试求出其它每个变量的偏移量。

寄存器

寄存器(Register)是CPU内部的元件,所以在寄存器之间的数据传送非常快。

用途:1.可将寄存器内的数据执行算术及逻辑运算。

2.存于寄存器内的地址可用来指向内存的某个位置,即寻址。

3.可以用来读写数据到电脑的周边设备。

8086 有8个8位数据寄存器,这些8位寄存器可分别组成16位寄存器:AH&AL=AX:累加寄存器,常用于运算;BH&BL=BX:基址寄存器,常用于地址索引;CH&CL=CX:计数寄存器,常用于计数;DH&DL=DX:数据寄存器,常用于数据传递。

为了运用所有的内存空间,8086设定了四个段寄存器,专门用来保存段地址:CS(Code Segment):代码段寄存器;DS(Data Segment):数据段寄存器;SS(Stack Segment):堆栈段寄存器;ES(Extra Segment):附加段寄存器。

当一个程序要执行时,就要决定程序代码、数据和堆栈各要用到内存的哪些位置,通过设定段寄存器CS,DS,SS 来指向这些起始位置。

通常是将DS固定,而根据需要修改CS。

所以,程序可以在可寻址空间小于64K 的情况下被写成任意大小。

所以,程序和其数据组合起来的大小,限制在DS 所指的64K内,这就是COM文件不得大于64K的原因。

8086以内存做为战场,用寄存器做为军事基地,以加速工作。

除了前面所提的寄存器外,还有一些特殊功能的寄存器:IP(Intruction Pointer):指令指针寄存器,与CS配合使用,可跟踪程序的执行过程;SP(Stack Pointer):堆栈指针,与SS配合使用,可指向目前的堆栈位置。

BP(Base Pointer):基址指针寄存器,可用作SS的一个相对基址位置;SI(Source Index):源变址寄存器可用来存放相对于DS 段之源变址指针;DI(Destination Index):目的变址寄存器,可用来存放相对于ES 段之目的变址指针。

PLC的地址寄存器指令说明

PLC的地址寄存器指令说明地址寄存器指令说明见表。

表地址寄存器指令说明1.+AR1加累加器1至地址寄存器1(+AR1、+AR1P#Byte. Bit)使用该指令是将地址寄存器AR1的内容加上作为地址偏移量的累加器1中低字的内容,或加上指令中的16位常数,结果在AR1( AR2)中。

首先将整数(16位)扩展为符号正确的24位,然后将其加到AR1的最低有效的24位(AR1中的相对地址的部分)。

在AR1( AR2)中,区域ID的部分(第24~ 26位)保持不变。

要加到AR1、AR2的内容中的整数(16位)由ACCU 1的低字中的值指定。

允许值的范围为-32768~+32767。

参数P#Byte. Bit(被加到AR1或AR2上的地址)的数据类型为指针常数。

要加到AR1、AR2的内容中的偏移量由参数P#Byte,Bit地址指定。

指令的执行与状态位无关,而且对状态位没有影响。

+AR1:加地址寄存器1中内容的整数(16位)通过累加器1低字中的数值定义,允许范围为-32768~+32767。

+AR1P#Byte. Bit:要加上的偏移量通过P#Byte. Bit地址定义。

编程示例1:L +300 说明:将数值装入累加器1低字中+AR1 将累加器1低字中的内容(整数,16位)加到地址寄存器1编程示例2:+ AR1 P#300.0 说明:将偏移量300.0加到地址寄存器12.+AR2加累加器1至地址寄存器2*(+AR2、+LAR2P#Byte. Bit)使用该指令,可以将语句中或累加器1低字中定义的偏移量加至地址寄存器2。

首先将整数(16位)扩展为带有其正确符号的2位数,然后加到地址寄存器2的最低有效24位(地址寄存器2中部分相关地址)。

地址寄存器2中ID区部分(位24、25和26)保持不变。

指令的执行与状态位无关,而且对状态位没有影响。

+AR2:加地址寄存器2中内容的整数(16位)通过累加器1低字中的数值定义,允许范围为-32768~+32767。

第6章 S7-200系列PLC的

END、STOP、WDR指令应用举例

☆ STOP与END指令通常在程序中用来处理突发应急事件,可以有 效避免实际生产中的重大损失。

6.3.4 跳转及标号指令

◆跳转指令(JMP)与标号(LBL)指 令可以在相同的代码段中(主程序、子 程序或中断程序)完成分支操作,将程 序流程跳转到标号(n)目的地。 ◆不能从主程序跳转至子程序或中断例 行程序中的标号,也不能从子程序或中 断例行程序跳转至该子程序或中断例行 程序之外的标号。 ◆可以在顺序控制SCR段中使用“跳转” 指令,但对应的“标号”指令必须位于 相同的SCR段内。

6.2.1 位逻辑指令

1.基本位操作指令

基本位操作指令操作数寻址范围:I,Q,M,SM,T,C,V, S,L等。指令助记符: LD(Load)、LDN(Load Not)、A(And)、 AN(And Not)、O(Or)、 ON(Or Not)、=(Out)。 【例题】位操作指令的程序应用,如图6-5所示。

3.间接寻址

● 间接寻址使用指针存取存储单元中的数据。可以用作指针的存储 器有变量存储器(V)、局部变量存储器(L)、累加器(A C)。 ● S7-200允许指针存取以下内存区:I、Q、V、M、S、T(仅限当前值) 和C(仅限当前值),但不能对独立的位(BIT)值或模拟量进行间接 寻址。 ● 用间接寻址方式存取数据需要作的工作有3种:建立指针、指针存 取数据和修改指针。 1)建立指针

【例题1】块操作指令程序应用,如图6-10所示。

6.2.2 逻辑堆栈指令

【例题2】栈操作指令应用程序,如图6-11所示。

想一想 练一练

将梯形图转换成语句表指令编程。

6.2.3 定时器指令

◆ S7-200 PLC 的 定 时器在程序中用于延 时 ◆有T0~T255共256 个定时器 ◆分为TON、TOF和 TONR 定 时 器 等 3 个 类型

汇编语言之程序的基本结构

第6章程序的基本结构在前面几章,我们分别介绍了用汇编语言进行程序设计所需要的几个最基本的知识:内存单元的寻址方式,变量定义和各种汇编指令格式。

在掌握了这些基本内容之后,就需要学习如何把它们组成一个完整的汇编语言程序。

6.1 源程序的基本组成汇编语言源程序的组成部分有:模块、段、子程序和宏等。

一个模块对应一个目标文件,当开发较大型的应用程序时,该程序可能由若干个目标文件或库结合而成的。

有关模块和子程序的知识和宏在第7章介绍,有关宏的知识将在第9章中叙述。

6.1.1 段的定义微机系统的内存是分段管理的,为了及之相对应,汇编语言源程序也分若干个段来构成。

8086CPU有四个段寄存器,在该系统环境下运行的程序在某个时刻最多可访问四个段,而80386及其以后的CPU 都含有六个段寄存器,于是,在这些系统环境下开发的运行程序在某个时刻最多可访问六个段。

不论程序在某个时刻最多能访问多少个段,在编程序时,程序员都可以定义比该段数更多的段。

在通常情况下,一个段的长度不能超过64K,在80386及其以后系统的保护方式下,段基地址是32位,段的最大长度可达4G。

段的长度是指该段所占的字节数:、如果段是数据段,则其长度是其所有变量所占字节数的总和;、如果段是代码段,则其长度是其所有指令所占字节数的总和。

在定义段时,每个段都有一个段名。

在取段名时,要取一个具有一定含义的段名。

段定义的一般格式如下:段名SEGMENT[对齐类型] [组合类型] [类别]…;段内的具体内容…段名ENDS其中:“段名”必须是一个合法的标识符,前后二个段名要相同。

可选项“对齐类型”、“组合类型”和“类别”的说明作用请见6.3节中的叙述。

一个数据段的定义例子:DATA1S EGMENTword1D W1, 9078H, ?byte1D B21, 'World'DD12345678HDATA1E NDS一个代码段的例子:CODE1S EGMENTAX,MOV;把数据段DATA1的段值送AXDATA1;把AX的值送给DS,即:DS存储数据段的段MOVDS, AX值…MOV AX, 4C00HINT21H;调用DOS功能,结束程序的运行CODE1E NDS6.1.2 段寄存器的说明语句在汇编语言源程序中可以定义多个段,每个段都要及一个段寄存器建立一种对应关系。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ASSUME CS:CODE1, DS:DATA1

上面的语句说明了:CS对应于代码段CODE1,DS对应于数据段DATA1。

在ASSUME语句中,还可以用关键字NOTHING来说明某个段寄存器不与任何段相对应。下面语句说明了段寄存器ES不与某段相对应。

…

MOVAX, 4C00H;(7)

INT21H;(8)

CODE1 ENDS

语句(1)和(6)分别说明了段和段寄存器之间的对应关系,其中语句(6)重新说明语句(1)所指定的对应关系。

二组语句(2)和(3)、(4)和(5)实现对段寄存器DS和ES赋初值。ASSUME说明语句只起说明作用,它不会对段寄存器赋值,所以,必须对有关段寄存器赋值。在以后的其它源程序中也都是用此方法来实现对数据段寄存器赋值的。

6.1.2 段寄存器的说明语句

在汇编语言源程序中可以定义多个段,每个段都要与一个段寄存器建立一种对应关系。建立这种对应关系的说明语句格式如下:

ASSUME 段寄存器名:段名[, 段寄存器名:段名, ……]

其中:段寄存器是CS、DS、ES、SS、FS和GS,段名是在段定义语句说明时的段名。

6.1.2 段寄存器的说明语句

→ 源程序的基本组成 → 段寄存器的说明语句 课件章节 网络课件目录 第1章 预备知识 第2章 CPU资源和存储器 第3章 操作数的寻址方式 第4章 标识符和表达式 第5章 微机CPU的指令系统 第6章 程序的基本结构 第7章 子程序和库 第8章 输入输出和中断 第9章 宏 第10章 应用程序的设计 第11章 数值运算协处理器 第12章 汇编语言和C语言

例6.1 汇编语言段及其段说明语句的作用。

DATA1SEGMENT;定义数据段DATA1

word1DW 5678h

byte1DB "ABCDEFG"

DATA1ENDS

DATA2SEGMENT;定义数据段DATA2

word2DW 1234h

word3DW 9876h

DATA2ENDS

ASSUME ES:NOTHING

在通常情况下,代码段的第一条语句就是用ASSUME语句来说明段寄存器与段之间的对应关系。在代码段的其它位置,还可以用另一个ASSUME语句来改变前面ASSUME语句所说明的对应关系,这样,代码段中的指令就用最近的ASSUME语句所建立的对应关系来确定指令中的有关信息。

MOVES, AX;(5)

…

MOVAX, word1;访问段DATA1中的字变量word1

MOVword2, AX;访问段DATA2中的字变量word2

…

ASSUMEDS:DATA3, ES:NOTHING;(6)

MOVAX, DATAห้องสมุดไป่ตู้

MOVDS, AX

MOVBL, byte2;访问段DATA3中的字节变量byte2

DATA3SEGMENT;定义数据段DATA3

byte2DB ?

DATA3ENDS

CODE1SEGMENT;编写代码段CODE1

ASSUMECS:CODE1, DS:DATA1, ES:DATA2;(1)

MOVAX, DATA1;(2)

MOVDS, AX;(3)

MOVAX, DATA2;(4)

语句(7)和(8)是调用中断21H的4CH号功能来结束本程序的执行,程序的返回代码由寄存器AL来确定。结束本程序执行的指令是所有主模块必须书写的语句。

注意:代码段寄存器不能由程序员在源程序中对其赋值,其值是由操作系统在装入它进入系统运行时自动赋值的。

课件章节 课件目录 第1章 预备知识 第2章 CPU资源和存储器 第3章 操作数的寻址方式 第4章 标识符和表达式 第5章 微机CPU的指令系统 第6章 程序的基本结构 第7章 子程序和库 第8章 输入输出和中断 第9章 宏 第10章 应用程序的设计 第11章 数值运算协处理器 第12章 汇编语言和C语言