FAN7393A_半桥栅极驱动IC

ad7399原理

ad7399原理

AD7399是一款10位分辨率的多通道电压输出数模转换器,采用±5 V双

电源供电。

其工作原理基于模数转换技术,将数字信号转换为模拟电压信号。

在AD7399中,数字信号通过SPI兼容型串行接口输入,经过内部逻辑电

路的处理,转换为相应的模拟电压信号输出。

该数模转换器具有可编程关断功能,能够实现低功耗待机模式。

同时,内部上电复位电路能够确保设备在上电或复位时处于已知状态。

此外,AD7399还具有双缓冲寄存器,可以同时更新多通道DAC,使得在

多通道应用中能够快速切换通道,提高系统的响应速度。

其4个单独的轨到轨基准电压输入能够提供高精度的模拟输出电压。

AD7399具有低温度系数和低噪声性能,使其在温度变化较大的环境中仍能保持稳定的输出。

此外,它还通过了汽车应用认证,能够满足汽车电子系统的严格要求。

总体而言,AD7399是一款高性能的数模转换器,适用于需要高精度、多通道、低功耗的电压输出应用场景。

如需更多信息,建议访问ADI官网或咨

询相关业内人士。

恩智浦半导体TEA2093TS GreenChip同步整流控制器产品数据手册说明书

GreenChip同步整流控制器第1版——2022年6月7日产品数据手册1 简介TEA2093TS是针对开关电源的新一代同步整流器(SR)控制器IC系列中的一员。

它包含自适应栅极驱动器,以便在任意负载下达到最高效率。

TEA2093TS是一款专门用于非对称半桥反激式和标准反激式转换器次级侧同步整流的控制器IC。

它内置用于驱动SR MOSFET的检测级和驱动器级,对次级变压器绕组的输出进行整流。

TEA2093TS可以为具有低输出电压的电池充电应用或具有高侧整流的应用生成自己的供电电压。

TEA2093TS采用绝缘硅片(SOI)工艺制成。

2 特性和优势2.1 能效特性●自适应栅极驱动器,在任意负载下达到最高效率●空载运行时的典型电源电流低于200 μA2.2 应用特性●在低至0 V的宽输出电压范围内工作●能够处理高达120 V输入电压的漏检测引脚●对低输出电压工作自供电●对不使用辅助绕组的高侧整流自供电●使用标准和逻辑电平SR MOSFET●支持USB BC、USB PD和快充应用●TSOP6封装2.3 控制特性●自适应栅极驱动器,实现导通终止时的快速关闭●带有源栅极下拉的欠压锁定(UVLO)3 应用TEA2093TS适用于反激式电源。

在此类应用中,它可以驱动外部同步整流器MOSFET,这些MOSFET取代用于对变压器次级绕组上的电压进行整流的二极管。

它可用于所有需要高效率的电源,如:●充电器●电源适配器●非对称半桥反激式电源●具有极低和/或可变输出电压的反激式电源4 订购信息表1.订购信息型号封装名称说明版本TEA2093TS/1 TSOP6 塑料小型封装;6引脚SOT4575 标示表2.标记代码型号标记代码TEA2093TS/1 TEA20936 功能框图图1. TEA2093TS 功能框图导通调节关断调节V 和I参考欠压锁定 驱动器供电节能控制使能逻辑关闭7 引脚分布信息7.1 引脚分布图2.TEA2093TS引脚分布(SOT457)7.2 引脚说明表3.引脚说明符号引脚说明CAP 1 内部供电电压的电容输入GND 2 接地XV 3 外部电源输入GATE 4 SR MOSFET的栅极驱动器输出SOURCE 5 SR MOSFET的源极检测输入DRAIN 6 SR MOSFET的漏极检测输入8 功能说明8.1 简介TEA2093TS是一款用于非对称半桥反激式和标准反激式应用中的同步整流(SR)的控制器IC。

三个独立的半桥栅极驱动集成电路芯片

三个独立的半桥栅极驱动集成电路芯片引言随着电子技术的发展,集成电路芯片在各个领域得到广泛应用。

半桥栅极驱动集成电路芯片是一种常见的电源管理芯片,用于控制电源与负载之间的电流流动。

本文将对三个独立的半桥栅极驱动集成电路芯片进行详细介绍。

1. 半桥栅极驱动集成电路芯片的基本原理半桥栅极驱动集成电路芯片是一种用于控制半桥电路的驱动器。

半桥电路由两个功率晶体管组成,一个用于负载的正向通路,另一个用于负载的反向通路。

半桥栅极驱动集成电路芯片通过控制两个功率晶体管的栅极电压,实现对半桥电路的控制。

半桥栅极驱动集成电路芯片的基本原理如下:1.输入信号:半桥栅极驱动集成电路芯片接收来自控制器的输入信号,通常是一个PWM信号。

2.信号处理:半桥栅极驱动集成电路芯片对输入信号进行处理,生成对应的栅极驱动信号。

3.驱动信号输出:半桥栅极驱动集成电路芯片将栅极驱动信号输出给半桥电路的两个功率晶体管,控制它们的导通与截止。

4.电源管理:半桥栅极驱动集成电路芯片通常还包含电源管理功能,如过流保护、过温保护等,以确保系统的安全运行。

2. 三个独立的半桥栅极驱动集成电路芯片介绍2.1 半桥栅极驱动芯片A半桥栅极驱动芯片A是一款高性能的半桥栅极驱动集成电路芯片。

它具有以下特点:•高速驱动:半桥栅极驱动芯片A能够提供高频率的栅极驱动信号,适用于高速开关应用。

•低功耗:半桥栅极驱动芯片A采用先进的功耗优化技术,能够在工作时保持低功耗,提高系统效率。

•多种保护功能:半桥栅极驱动芯片A内置了多种保护功能,如过流保护、过温保护等,能够有效保护系统的安全运行。

2.2 半桥栅极驱动芯片B半桥栅极驱动芯片B是一款高集成度的半桥栅极驱动集成电路芯片。

它具有以下特点:•高集成度:半桥栅极驱动芯片B集成了多个功能模块,如电源管理、PWM信号生成等,减少了外部器件的使用,降低了系统成本。

•丰富的接口:半桥栅极驱动芯片B提供了多种接口,如SPI接口、I2C接口等,方便与外部控制器进行通信。

FAN78883半桥式栅极驱动IC

半桥式栅极驱动IC3 半桥式栅极驱动IC产品特性自举工作通道浮动电压达到+200V所有通道的拉电流和灌电流驱动能力为350mA/650mA 3 半桥式栅极驱动器V BS =15V 时,信号传播允许的负向电压V S 摆幅扩展到-9.8V 。

匹配的最大传播延迟时间:50ns 兼容3.3V 和5V 输入逻辑所有通道内置直通保护电路,典型死区时间为270ns 内置共模dv/dt 噪音消除电路所有通道内置UVLO 功能适用范围三相电机变频驱动器说明该FAN7888是一款集成了三个半桥式栅极驱动器集成电路的芯片,专为高压,高速驱动MOSFET 和IGBT 设计,可在高达+200V 电压下工作。

飞兆半导体的高电压处理和共模噪声消除技术可以保证高端驱动器在高dv/dt 噪声环境下稳定工作。

先进的电平转换电路允许高端驱动器在V BS =15V 时运行在V S =-9.8V (典型值)。

当V DD 和V BS 低于指定的阈值电压时,UVLO 电路能够预防故障。

输出驱动器的拉电流/灌电流通常为350mA/650mA ,它适用于电机驱动系统中的三相半桥式电路。

订货信息关于飞兆半导体绿色生态定义,请访问:/company/green/rohs_green.html .20-SOIC器件型号封装工作温度范围Eco 状态包装方法FAN7888M 20-SOIC-40°C 至 +125°CRoHS 塑料管FAN7888MXRoHS胶带&卷盘半桥式栅极驱动IC图1 三相无刷直流(BLDC)电动机驱动器的应用内部模块图UVWUU ULVU VL WU WLQ4Q6Q2Q1Q3Q5Q1Q3Q5Q4Q6Q23 Ⳍ䗚GND LO3LIN1V DD V S1HO1V B1HIN1V S2HO2V B2V S3HO3V B3HIN2HIN3LIN2LIN3LO2LO120191817161514131212345678910V S1V S3V S2V S2V S3V S1FAN78883 ⳌBLDC ⬉I UI VI W11FAN7888 Rev.00UVLOR R SQ偅偅W Ⳍ偅V Ⳍ偅U Ⳍ偅LO2V S2HO2V B2HO3V B3UHINULIN V DDVHIN V DD VDD_UVLOHIN1HIN2HIN3LIN1LIN2LIN3VLINⳈ䗮䘏䕥UVLOVDDV DDLO1GNDV S1HO1V B1⍜䰸㛝 ⫳⡍㾺 䕧半桥式栅极驱动IC图3 引脚布局(顶视图)引脚定义引脚编号名称说明1HIN1高端栅极1驱动器的逻辑输入12LIN1低端栅极1驱动器的逻辑输入13HIN2高端栅极2驱动器的逻辑输入24LIN2低端栅极2驱动器的逻辑输入25HIN3高端栅极3驱动器的逻辑输入36LIN3低端栅极3驱动器的逻辑输入37LO3低端栅极驱动器3的输出8V S3高端驱动器3的浮动电源偏置电压9HO3高端驱动器3的栅极驱动输出10V B3高端驱动器3的浮动电源电压11GND 地端12V DD 逻辑的和所有低端栅极驱动器的电源电压13LO2低端栅极驱动器2的输出14V S2高端驱动器2的浮动电源偏置电压15HO2高端驱动器2的栅极驱动输出16V B2高端驱动器2的浮动电源电压17LO1低端栅极驱动器1的输出GNDLO3FAN7888V DD V S1HIN2HIN3LIN2LIN3LO2LO11817161514131211345678910V S2HO2V B2V S3HO3V B3FAN7888 Rev.00半桥式栅极驱动IC注意:1. 安装到76.2 x 114.3 x 1.6mm PCB 板(FR-4还氧玻璃材料)2. 参考以下标准:JESD51-2:集成电路热测试方法环境条件-自然对流 JESD51-3:含铅表面贴装封装的低有效导热系数测试板3. 在任何情况下,不要超过P D 。

半桥栅极驱动器FD2103P说明书

FD2103PFD2103P180V 半桥栅极驱动器概述FD2103P 是一款半桥栅极驱动电路芯片,设计用于高压、高速驱动N 型功率MOSFET 。

FD2103P 内置欠压(UVLO )保护功能,防止功率管在过低的电源电压下工作而对功率管产生损坏。

FD2103P 内置直通防止保护和死区时间,防止功率管发生直通,有效防止半桥功率器件损坏。

封装产品特点⚫ 悬浮绝对电压+180V ⚫ 电源工作电压范围:10~20V ⚫ 输出电流+0.3A/-0.6A ⚫ 3.3V/5V 输入逻辑兼容 ⚫ VCC 欠压保护(UVLO ) ⚫ 高端输出与高端输入同相 ⚫ 低端输出与低端输入反相 ⚫ 内置直通防止功能⚫ 内置100ns 死区时间应用电机驱动DC-DC 转换器P r el i mi n a ry1. 绝对最大额定值(除非特殊说明,所有管脚均以COM 为参考点)参数符号 范围 单位 高侧浮动绝对电压 V B -0.3~205 V 高侧浮动偏移电压 V S V B -25~V B +0.3 V 高侧输出电压 V HO V S -0.3~V B +0.3V 低侧供电电压 V CC -0.3~25 V 低侧输出电压V LO -0.3~V CC +0.3 V 逻辑输入电压(HIN, LIN*) V IN -0.3~6.5 V 偏移电压压摆率范围 dV S /dt ≤50 V/ns 功率耗散@T A ≤25︒C SOIC-8 P D ≤0.625 W 结对环境的热阻 SOIC-8R thJA ≤200 ︒C/W 结温范围 T j ≤150︒C 储存温度范围T stg-55~150︒C注1:在任何情况下,不要超过P D 。

注2:电压超过绝对最大额定值,可能会损坏芯片。

2. 推荐工作条件(所有电压均以COM 为参考点)参数符号 最小值 最大值 单位 高侧浮动绝对电压 V B V S +10V S +20V 高侧浮动偏移电压 V S-5 180 V 高侧输出电压 V HO V S V B V 低侧供电电压 V CC 10 20 V 低侧输出电压 V LO 0 V CC V 逻辑输入电压(HIN, LIN*)V IN0 5.5V环境温度T A -40 125 ︒C注1:芯片长久工作在推荐工作条件外,可能会影响其可靠性。

TDA7393, 规格书,Datasheet 资料

TDA7393 2x32W DUAL BRIDGE CAR RADIO AMPLIFIER HIGH OUTPUT POWER CAPABILITY:2x35W max./4Ω2x32W EIAJ/4Ω2x22W typ./4Ω@14.4V,1KHz,10%2x19W typ./4Ω@13.2V,1KHz,10%2x28W typ./2Ω@14.4V,1KHz,10%2x25W typ./2Ω@13.2V,1KHz,10%LOW DISTORTIONLOW OUTPUT NOISEST-BY FUNCTIONMUTE FUNCTIONAUTO-MUTE AT MIN.SUPPLY VOLTAGE DETECTIONLOW EXTERNAL COMPONENT COUNT–INTERNALLY FIXED GAIN(32dB)–NO EXTERNAL COMPENSATION–NO BOOTSTRAP CAPACITORSADDITIONAL MONO INPUT PROTECTIONS:OUTPUT AC/DC SHORT CIRCUIT TO GND AND TO V SVERY INDUCTIVE LOADSOVERRATING CHIP TEMPERATURE WITH SOFT THERMAL LIMITERLOAD DUMP VOLTAGEFORTUITOUS OPEN GNDREVERSE BATTERYESD PROTECTIONDESCRIPTIONThe TDA7393is a new technology class AB Audio Power Amplifier in Multiwatt15package de-signed for high end car radio applications.Thanks to the fully complementary PNP/NPN output con-figuration the high power performances of the TDA7393are obtained without bootstrap capaci-tors.The extremely reduced components countOctober1998®MULTIWATT15ORDERING NUMBER:TDA7393BLOCK DIAGRAM1/9allows very compact sets.PIN CONNECTION (Top view)ABSOLUTE MAXIMUM RATINGSSymbol ParameterValue Unit V CC Operating Supply Voltage 18V V CC (DC)DC Supply Voltage28V V CC (pk)Peak Supply Voltage (t =50ms)50V I OOutput Peak Current:Repetitive (Duty Cycle 10%at f =10Hz)Non Repetitive (t =100µs)4.55.5A A P tot Power dissipation,Tcase =75°C (see derating curve)50W T j Junction Temperature150°C T op Operating Ambient Temperature –40to 85°C T stgStorage Temperature–55to 150°CTHERMAL DATASymbol ParameterValue Unit R th j-caseThermal Resistance Junction to CaseMax.1.5°C/WTDA73932/9ELECTRICAL CHARACTERISTICS(V S=13.2V;f=1KHz;R g=600Ω;R L=4Ω;T amb=25°C;Refer to the application circuit,unless otherwise specified.)Symbol Parameter Test Condition Min.Typ.Max.UnitI q1Quiescent Current90180mAV OS Output Offset Voltage150mVG v Voltage Gain30.53233.5dBP o Output Power THD=10%;V S=14.4VTHD=10%THD=1%THD=10%;R L=2ΩTHD=10%;V S=14.4V; R L=2Ω172219162528WWWWWP o max Max.Output Power EIAJ RULES;V S=13.7V30W THD Distortion P o=0.1to8W0.080.3%e No Output Noise Bw=20Hz to20KHz0.3mVrms SVR Supply Voltage Rejection f=100Hz(stereo)60dBf L Low Cut-Off Frequency10Hz f H High Cut-Off Frequency300KHz R i Input Impedance101520KΩC T Cross Talk f=1KHz5065dB I SB St-By Current Consumption100µA V SB out St-By OUT Threshold Voltage Amp.ON 3.5VV SB IN St-By IN Threshold Voltage Amp.OFF 1.5VV SB Supply Dependent St-ByThreshold St-By=H,V S reducing/increasing7.58.3VA M Mute Attenuation V O=1Vrms75dB V M out Mute OUT Threshold Voltage Amp.Play 3.5V V M in Mute IN Threshold Voltage Amp.Mute 1.5VV M Supply Dependent MuteThreshold Mute=IN,V S reducing/increasing8.59.3VI m(L)Muting Pin Current V MUTE=1.5V(Sourced Current)61014µAI m(H)Muting Pin Current VMUTE=3.5V(Sourced Current)61014µA Figure1:Quiescent Current vs.Supply Voltage Figure2:Output Power vs.Supply VoltageR L=4ΩR L=4Ωf=1KHzTDA73933/9Figure 5:Cross-Talk vs.FrequencyFigure 6:SVR vs.FrequencyFigure 7:Distortion vs.Frequency Figure 8:Distortion vs.FrequencyFigure 3:Output Power vs Supply VoltageFigure 4:EIAJ Power vs.Supply VoltageR L =2Ωf =1KHzf =1KHz V i =2.5VrmsV S =13.2V R L =4ΩV O =1VrmsV S =13.2V R L =4ΩV r =1Vrms R g =600ΩMute 1,2=OFFV S =13.2V R L =2ΩV S =13.2V R L =4ΩBoth channelsTDA73934/9TDA7393 Figure9:Block Diagram of Mute CircuitFigure10:ExplanatoryWaveforms Of Mute Circuit5/9TDA7393Figure11:Application CircuitFigure12:P.C.Board and Component Layout of the fig.11(1:1scale) 6/9TDA7393 Figure13:Power Dissipation Derating Curve7/9Multiwatt15VDIM.mm inch MIN.TYP.MAX.MIN.TYP.MAX.A 50.197 B 2.650.104C 1.60.063D 10.039E 0.490.550.0190.022F 0.660.750.0260.030G 1.02 1.27 1.520.0400.0500.060G117.5317.7818.030.6900.7000.710H119.60.772H220.20.795L 21.922.222.50.8620.8740.886L121.722.122.50.8540.8700.886 L217.6518.10.6950.713 L317.2517.517.750.6790.6890.699L410.310.710.90.4060.4210.429L7 2.65 2.90.1040.114M 4.25 4.55 4.850.1670.1790.191M1 4.63 5.085.530.1820.2000.218S 1.9 2.60.0750.102S1 1.9 2.60.0750.102Dia13.653.850.1440.152OUTLINE AND MECHANICAL DATAMULTIWATT15PACKAGE MECHANICAL DATATDA73938/9TDA7393 Informationfurnished is believed to be accurate and reliable.However,STMicroelectronics assumes no responsibility for the consequencesof use of such information nor for any infringement of patents or other rights of third parties which may res ult from its use.No license isgranted by implication or otherwise under any patent or patent rights of STMicroelectronics.Specification mentioned in this publication are subject to change withoutnotice.This publicationsupersedes and replaces all information previously supplied.STMicroelectronics products are notauthorizedfor use as critical components in life support devices or systems without express writtenapproval of STMicroelec tronics.The ST logois a registered trademark of STMicroelec tronics©1998STMicroelectronics–Printed in Italy–All Rights ReservedMULTIWATT®is a Registered Trademark ofthe STMicroelectronicsSTMicroelectronics GROUP OF COMPANIESAustralia-Brazil-Canada-China-France-Germany-Italy-Japan-Korea-Malaysia-Malta-Mexico-Morocco-The Netherlands-Singapore-Spain-Sweden-Switzerland-Taiwan-Thailand-United Kingdom-U.S.A.9/9。

屹晶微电子 EG2153 自振荡半桥驱动芯片 数据手册说明书

版本变更记录目录1. 特性 (1)2. 描述 (1)3. 应用领域 (1)4. 引脚 (2)4.1 引脚定义 (2)4.2 引脚描述 (2)5. 结构框图 (3)6. 典型应用电路 (3)7. 电气特性 (4)7.1 极限参数 (4)7.2 推荐参数 (4)7.3 典型参数 (5)7.4 时序图 (7)7.5 开关时间特性 (7)8. 应用设计 (8)8.1 Vcc端电源电压 (8)8.2 欠压锁定模式 (8)8.3 自举电路 (9)8.4 关闭模式 (10)9. 封装尺寸 (11)9.1 SOP8封装尺寸 (11)EG2153芯片数据手册V1.01. 特性◼高端悬浮自举电源设计,耐压可达600V◼ C T , R T 可编程振荡器◼VCC电源12V 齐纳钳位◼微小启动电流◼CT脚带使能关闭功能◼VCC和VB端电源带欠压保护◼输出电流能力IO+/- 0.2 A/0.3A◼内部自带死区◼低压输出端信号逻辑和RT 端相同◼外围器件少◼封装形式:SOP8◼无铅无卤符合ROHS标准2. 描述EG2153是一种高压、高速功率MOSFET和IGBT栅极驱动器,内部集成了高压半桥驱动电路和一个振荡器,形成一款多功能,更加安全的功率驱动芯片。

CT管脚具有保护关断功能,可以用一个电压信号使驱动器停止输出。

VDD上电低于开启电压时,输出低电平,超过开启阈值,驱动器就能稳定的频率振荡。

3. 应用领域◼荧光灯◼开关电源4. 引脚4.1 引脚定义VS图4-1. EG2153管脚定义4.2 引脚描述5. 结构框图RTCTGNDVCC VB HO VS LO图5-1. EG2153内部电路图6. 典型应用电路EG2153图6-1. EG2153典型应用电路图7. 电气特性7.1 极限参数无另外说明,在T A=25℃条件下注:超出所列的极限参数可能导致芯片内部永久性损坏,在极限的条件长时间运行会影响芯片的可靠性。

7.2 推荐参数无另外说明,在T A=25℃条件下,VCC=VB=12V,负载电容C L=1nF条件下7.3 典型参数无另外说明,在T A=25℃,VCC=12V,负载电容CT=C L=1nF条件下7.4 时序图图7-1.输出开关波形7.5 开关时间特性图7-2.输出开关波形7-3. 死区时间波形图8. 应用设计8.1 Vcc端电源电压由于芯片内部有稳压管,芯片电源电压会钳为在大约12V。

EG2124A 芯片数据手册说明书

版本变更记录目录1. 特性 (1)2. 描述 (1)3. 应用领域 (1)4. 引脚 (2)4.1 引脚定义 (2)4.2 引脚描述 (3)5. 结构框图 (4)6. 典型应用电路 (5)7. 电气特性 (5)7.1 极限参数 (5)7.2 典型参数 (6)7.3 开关时间特性及死区时间波形图 (8)8. 应用设计 (8)8.1 VCC端电源电压 (8)8.2 输入逻辑信号要求和输出驱动器特性 (8)8.3 自举电路 (10)9. 封装尺寸 (11)9.1 TSSOP20封装尺寸 (11)9.2 QFN24封装尺寸 (12)EG2124A芯片数据手册V1.01. 特性◼高端悬浮自举电源设计,耐压可达260V◼集成三路独立半桥驱动◼适应5V、3.3V输入电压◼最高频率支持500KHZ◼低端VCC电压范围7V-20V◼输出电流能力IO +0.8A/-1.2A◼VCC和VB带欠压保护◼内建死区控制电路◼自带闭锁功能,彻底杜绝上、下管输出同时导通◼HIN输入通道高电平有效,控制高端HO输出◼LIN输入通道高电平有效,控制低端LO输出◼封装形式:TSSOP20和QFN24◼无铅无卤符合RHOS标准2. 描述EG2124A是一款高性价比的大功率MOS管、IGBT管栅极驱动专用芯片,内部集成了逻辑信号输入处理电路、死区时控制电路、欠压保护电路、闭锁电路、电平位移电路、脉冲滤波电路及输出驱动电路。

EG2124A高端的工作电压可达260V,低端VCC的电源电压范围宽7V~20V。

该芯片具有闭锁功能防止输出功率管同时导通,输入通道HIN和LIN 内建了下拉电阻,在输入悬空时使上、下功率MOS管处于关闭状态,输出电流能力IO +0.8A/-1.2A,采用TSSOP20和QFN24封装。

3. 应用领域◼三相直流无刷电机驱动器4. 引脚4.1 引脚定义图4-1. EG2124A管脚定义图4-2. EG2124管脚定义4.2 引脚描述5. 结构框图VB1HO1VS1VCCLO1VB2HO2VS2LO2VB3HO3VS3LO3GND图5-1. EG2124A内部电路图6. 典型应用电路图6-1. EG2124A典型应用电路图7. 电气特性7.1 极限参数7.2 典型参数无另外说明,在T A=25℃,Vcc=12V,负载电容C L=1nF条件下7.3 开关时间特性及死区时间波形图图7-1. 低端输出LO 开关时间波形图图7-2. 高端输出HO 开关时间波形图50%50%LOH INLINHO 50%50%图7-3. 死区时间波形图8. 应用设计8.1 VCC 端电源电压针对不同的MOS 管,选择不同的驱动电压,开启MOS 管推荐电源VCC 工作电压典型值为7V-15V 。

三个独立的半桥栅极驱动集成电路芯片

三个独立的半桥栅极驱动集成电路芯片1. 引言在现代电子技术中,半桥栅极驱动集成电路芯片是一种常见且重要的电子元件。

它能够有效地控制和驱动功率半导体器件,如MOSFET和IGBT等。

本文将介绍三个独立的半桥栅极驱动集成电路芯片,包括其原理、特点、应用等方面的内容。

2. 半桥栅极驱动集成电路芯片原理半桥栅极驱动集成电路芯片是一种专门用于控制和驱动功率半导体器件的集成电路。

它通常由输入端、输出端、逻辑控制单元和驱动单元等部分组成。

输入端通常接收来自控制信号源的信号,用于指示开关状态。

输出端则连接到功率半导体器件的栅极,通过改变栅极信号来控制功率器件的导通与截止状态。

逻辑控制单元负责接收输入信号,并进行逻辑判断。

它可以根据输入信号的不同组合来产生相应的控制信号,用于驱动驱动单元的工作。

驱动单元是半桥栅极驱动集成电路芯片的核心部分。

它通常由多个逻辑门电路、电流源和电压源等组成。

驱动单元根据逻辑控制单元产生的信号,通过改变栅极信号的电平和波形来控制功率半导体器件的导通与截止状态。

3. 三个独立的半桥栅极驱动集成电路芯片3.1 半桥栅极驱动集成电路芯片A半桥栅极驱动集成电路芯片A是一款高性能的半桥栅极驱动芯片。

它采用了先进的CMOS工艺,具有低功耗、高响应速度和抗干扰能力强等特点。

该芯片具有多种保护功能,如过温保护、过流保护和过压保护等。

它还支持多种工作模式选择,包括PWM模式、脉冲模式和直流模式等。

半桥栅极驱动集成电路芯片A广泛应用于各种领域,如工业自动化、新能源汽车和消费电子等。

它能够有效地控制和驱动功率半导体器件,提高系统的可靠性和稳定性。

3.2 半桥栅极驱动集成电路芯片B半桥栅极驱动集成电路芯片B是一款高集成度的半桥栅极驱动芯片。

它采用了先进的BICMOS工艺,具有低功耗、高效率和小尺寸等特点。

该芯片内部集成了多个逻辑门电路和驱动单元,能够实现多种控制功能。

它支持多种输入信号格式,如PWM信号、脉冲信号和模拟信号等。

半桥栅极驱动芯片

半桥栅极驱动芯片半桥栅极驱动芯片(Half-Bridge Gate Driver Chip)半桥栅极驱动芯片是一种用于驱动半桥功率器件(例如电力MOSFET、IGBT 等)的关键组件。

它主要负责控制功率器件的开关,以实现对电力系统的有效控制和保护。

半桥栅极驱动芯片的基本原理是通过输出控制信号来控制半桥功率器件的开关状态。

它通常具有两个栅极驱动输出引脚,分别对应 N 沟道和 P 沟道功率器件。

通过精确控制输入信号的脉冲宽度和频率,可以实现功率器件的开关和切换。

半桥栅极驱动芯片的主要功能包括以下几个方面:1. 开关控制:根据输入信号的脉冲宽度和频率,控制功率器件的开关状态。

这样可以实现对电力系统的有效控制,如变换电压、调整电流等。

2. 防过流保护:通过监测电流的大小,当电流超过设定值时,自动切断功率器件的开关以保护电路和设备的安全运行。

3. 短路保护:在系统短路发生时,自动切断功率器件的开关,以防止进一步损坏电路和设备。

4. 温度保护:监测功率器件的温度,当温度过高时,自动切断开关以防止功率器件过热,从而保护电路和设备的安全运行。

5. 看门狗功能:监测系统的工作状态,当系统处于异常状态时,自动切断开关以保护电路和设备。

半桥栅极驱动芯片的优势主要体现在以下几个方面:1. 高效性能:半桥栅极驱动芯片采用先进的驱动技术和高性能材料,具有较低的功耗和高的效率,可以更好地满足功率器件的控制需求。

2. 可靠性:半桥栅极驱动芯片具有良好的抗干扰能力和稳定的工作性能,能够在恶劣的工作环境下长时间稳定运行。

3. 安全性:半桥栅极驱动芯片具有多种保护功能,可以有效地防止电路和设备的损坏,提高系统的可靠性和安全性。

4. 节省空间:半桥栅极驱动芯片体积小巧,集成度高,可以有效地节省系统的空间,提高系统的紧凑性。

总之,半桥栅极驱动芯片是控制和保护半桥功率器件的重要组成部分。

它具有高效性能、可靠性、安全性和节省空间的优势,广泛应用于工业控制、电力系统等领域。

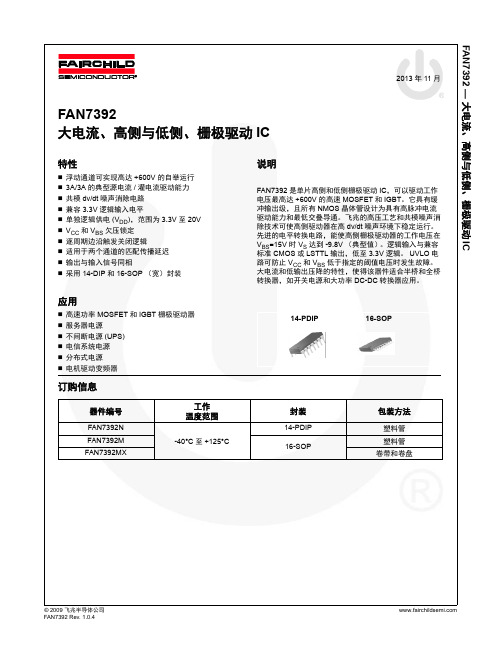

大电流、高侧与低侧、栅极驱动 IC

14-PDIP

16-SOP

封装 14-PDIP 16-SOP

包装方法

塑料管 塑料管 卷带和卷盘

© 2009 飞兆半导体公司 FAN7392 Rev. 1.0.4

FAN7392 — 大电流、高侧与低侧、栅极驱动 IC

典型应用电路图

15V

HIN

Controller SD

VBSUV-

VBS 电源欠压 负向阈值电压

VIN=0V, VBS= 扫描

7.3

8.4

9.5 V

VBSUVH VBS 电源欠压锁定滞回电压回差

ILK

偏置漏电流

输入逻辑部分 (HIN、 LIN 和 SD)

VIN=0V, VBS= 扫描 VB=VS=600V

0.4

V

50 μA

VDD=3V

2.4

V

VIH

逻辑 “1” 输入阈值电压

应用

高速功率 MOSFET 和 IGBT 栅极驱动器 服务器电源 不间断电源 (UPS) 电信系统电源 分布式电源 电机驱动变频器

订购信息

器件编号

FAN7392N FAN7392M FAN7392MX

工作 温度范围

-40°C 至 +125°C

说明

FAN7392 是单片高侧和低侧栅极驱动 IC,可以驱动工作 电压最高达 +600V 的高速 MOSFET 和 IGBT。它具有缓 冲输出级,且所有 NMOS 晶体管设计为具有高脉冲电流 驱动能力和最低交叠导通。飞兆的高压工艺和共模噪声消 除技术可使高侧驱动器在高 dv/dt 噪声环境下稳定运行。 先进的电平转换电路,能使高侧栅极驱动器的工作电压在 VBS=15V 时 VS 达到 -9.8V (典型值)。逻辑输入与兼容 标准 CMOS 或 LSTTL 输出,低至 3.3V 逻辑。 UVLO 电 路可防止 VCC 和 VBS 低于指定的阈值电压时发生故障。 大电流和低输出压降的特性,使得该器件适合半桥和全桥 转换器,如开关电源和大功率 DC-DC 转换器应用。

原边反馈ACDC控制芯片CX73XX系列IC

Tst =−R1×C1×ln(1−

VCC−ON

)

2×Vac−Ist×R1

其中:VCC-ON 是芯片启动电压;

Ist 是芯片启动电流。

(2)

深圳市尚亿微科技有限公司

图 12:启动电路 正因为很小的启动电流,所以 R1 的值可 以取得很大,如 1.2MΩ。如果 VCC 的电容是 4.7uF,启动延迟在 90V 交流输入时可以做到 1 秒以内。 VCC 欠压锁定 图 13 所示,这款原边反馈控制芯片的开 启和关断门槛固定在 12V 和 5V。在启动时, VCC 电容必须通过启动电阻 R1 充电至 12V 从 而来启动控制芯片。在能量不能从辅助绕组中 得到时,VCC 电容将一直对控制芯片供电,直 到辅助绕组开始对 VCC 供应大于 5V 的电压。 如果 VCC 电压低于 5V,芯片将进入 VCC 欠 压锁定状态,关闭芯片内部的一些电路,此时, Vbus 通过 R1 给电容 C1 充电,直到 VCC 电 压达到 12V,芯片再次启动,打开所有的内部 电路。这个欠压锁定的滞环将保证在启动时 VCC 电容足够对控制芯片供电。

CABLE

GND

图 7:CX732A内部模块

VCC

VDD

Ibias

150uA Ifb_open

OTP

4.65V Vovp

FB_open

COMP

Ovp

FB

Ifb EA

3 x (1+Kcab)V

0.1V Vcp

COMP

CV Controller

CCM Protection

3V Vfb

CS

CX732B

Vline

图 10:主要波形

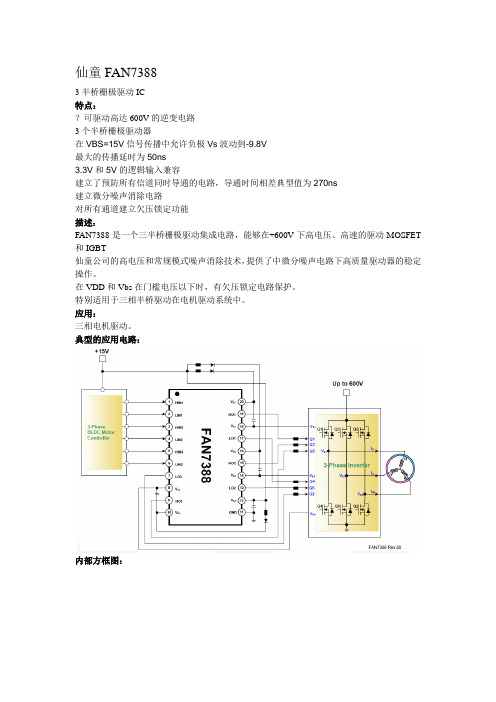

仙童FAN7388

仙童FAN7388

3半桥栅极驱动IC

特点:

?可驱动高达600V的逆变电路

3个半桥栅极驱动器

在VBS=15V信号传播中允许负极Vs波动到-9.8V

最大的传播延时为50ns

3.3V和5V的逻辑输入兼容

建立了预防所有信道同时导通的电路,导通时间相差典型值为270ns

建立微分噪声消除电路

对所有通道建立欠压锁定功能

描述:

FAN7388是一个三半桥栅极驱动集成电路,能够在+600V下高电压、高速的驱动MOSFET 和IGBT

仙童公司的高电压和常规模式噪声消除技术,提供了中微分噪声电路下高质量驱动器的稳定操作。

在VDD和Vbs在门槛电压以下时,有欠压锁定电路保护。

特别适用于三相半桥驱动在电机驱动系统中。

应用:

三相电机驱动。

典型的应用电路:

内部方框图:

引脚图:

最大额定参数:

注意:

安装在76.2×114.3×1.6mmPCB上

有关的规则:

JESD51-2:集成电路热力测验环境-自然环境JESD51-3:低效热力传导测试

在任何情况下不要超过功耗。

各种电脑块超级单片及各种集成电路IC的代换收集

创维东芝超级单片机使用的微处理器的代用关系创维东芝超级单片机心有:3T30、4T30、5T30、3T36、4T36、5T36等机心,是创维公司与日本东芝公司联合开发的新一代超级单片集成电路彩电机心。

该机心采用了东芝公司最新推出的超大规模集成心片,有:TMPA8803CSN、TMPA8823CSN、TMPA8808CSN、TMPA8809CSN、TMPA8829CSN等。

在创维东芝超级单片机心中,3T30、3T36、4T36是同一种机心,使用的软件基本相同,对应的超级单片型号是’rMPA8803CSN或者TMPA8823CSN。

TMPA8823CSN是TMPA8803CSN软件升级后的版本,但二者配套使用的存储器不同,不能互换使用。

4T30、5T36、5T30是同一种机心,使用的软件基本相同(电源电路不同),对应的超级单片型号是TMPA8808CSN、TMPA8809CSN或者TMPA8829CSN。

TPMA8829C8N是TMPA8809CSN软件升级后的版本,其存储器的代换原则配套使用的存储器不同,不能互换使用。

创维的83703可代8370183735可代83702和837325P30的83731没有可代换的。

83703还能带83702,但是会出现无声或者白屏把OP2调成28即可。

创维T系列机型CPU的代换目前T系列机芯共有5种CPU,其分别为:1、87CM38N-3856,在3T01、4T01机芯上使用,其可存储100个频道。

2、87CM38N-1N86,在21寸9000系列机芯上使用,可存储256个频道,并带有游戏功能。

3、87CM38N-1N10,在25寸5T10机芯上使用,可存储228个频道。

4、87CM38N-1R02,在29寸5T10、5T20机芯一使用,可存储256个频道,带有游戏功能。

5、87TPS38N,此种为OTP产品,为T系列最早使用的CPU,在25寸5T10机芯上使用,有两种,其分别为可存储228和256个频道。

ADV7390-datasheet芯片资料

Advanced power management

Macrovision® Rev 7.1.L1 (SD) and Rev 1.2 (ED) compliant Programmable features

Power Supply Specifications........................................................ 5 Input Clock Specifications .......................................................... 5 Analog Output Specifications..................................................... 5 Digital Input/Output Specifications........................................... 6 MPU Port Timing Specifications ............................................... 6 Digital Timing Specifications ..................................................... 7 Video Performance Specifications ............................................. 8 Power Specifications .................................................................... 8 Timing Diagrams.............................................................................. 9 Absolute Maximum Ratings.......................................................... 15 Thermal Resistance .................................................................... 15 ESD Caution................................................................................ 15 Pin Configurations and Function Descriptions ......................... 16 Typical Performance Characteristics ........................................... 18 MPU Port Description................................................................... 23 I2C Operation.............................................................................. 23 SPI Operation.............................................................................. 24 Register Map.................................................................................... 25 Register Programming............................................................... 25 Subaddress Register (SR7 to SR0) ............................................ 25 ADV7390/ADV7391 Input Configuration ................................. 41 Standard Definition.................................................................... 41 Enhanced Definition/High Definition .................................... 41 Enhanced Definition (At 54 MHz) .......................................... 41 ADV7392/ADV7393 Input Configuration ................................. 42 Standard Definition.................................................................... 42 Enhanced Definition/High Definition .................................... 43 Enhanced Definition (At 54 MHz) .......................................... 43 Output Configuration .................................................................... 44 Features ............................................................................................ 45 Output Oversampling ................................................................ 45 ED/HD Nonstandard Timing Mode........................................ 45 ED/HD Timing Reset ................................................................ 46

QED9320 LED控制芯片说明书

V V V V V V

承受功耗

PDMAX 0.625

W

PN结到环境的热阻

θJA

℃ 145

/W

工作结温范围

~ ℃ TJ -40 150

储存结温范围

~ ℃ TSTG -55 150

注 1:最大极限值是指超出该工作范围,芯片有可能损坏。推荐工作范围是指在该范围内,器件功能正常,但并不完全保证 满足个别性能指标。电气参数定义了器件在工作范围内并且在保证特定性能指标的测试条件下的直流和交流电参数规范。对

若在启动中发现故障,内部控制电路停止工作, VCC充电电路关断并锁定;当 VCC电压降至欠压保护

阈值 7V后,VCC充电电路解除锁定重新充电,芯片重新启动。

2.恒流控制,输出电流设置

QED9320采用初级线圈电流采样控制 LED输出电流。

输出电流计算公式: ≈ LED

IOUT 0.5*N*V /RCS

QED9320

集成有源 PFC可控硅调光,原边反馈 LED控制芯片

QED9320_demo 板说明书_0.1

深圳质能达微电子科技有限公司

QED MicroElectronics Inc. 电话:86-755-2691-5113 传真:86-755-2691-5113

QED9320

集成有源 PFC可控硅调光,原边反馈 LED控制芯片

0

3

V

乘法器增益

VCOMP=1.7V, VASN=0.5V

K

VCOMP=1.7V, VASN=1.5V

0.82 1.04 1.24 1/V 0.86 1.05 1.20 1/V

误差放大器 参考电压 跨导

COMP低钳位电压 最大输出电流 电流采样 前沿消隐时间 过流保护阈值电压 CS高钳位电压 CS低钳位电压 FB反馈 零电流检测阈值 零电流检测迟滞 过压保护 FB阈值 最小关断时间 最大关断时间 功率 MOS 功率 MOS导通阻抗 功率 MOS击穿电压 TRIAC调光下拉管 MOS导通阻抗 MOS击穿电压 过热保护

常用开关电源芯片大全之欧阳美创编

常用开关电源芯片大全第1章DC-DC电源转换器/基准电压源1.1 DC-DC电源转换器1.低噪声电荷泵DC-DC电源转换器AAT3113/AAT31142.低功耗开关型DC-DC电源转换器ADP30003.高效3A开关稳压器AP15014.高效率无电感DC-DC电源转换器FAN56605.小功率极性反转电源转换器ICL76606.高效率DC-DC电源转换控制器IRU30377.高性能降压式DC-DC电源转换器ISL64208.单片降压式开关稳压器L49609.大功率开关稳压器L4970A10.1.5A降压式开关稳压器L497111.2A高效率单片开关稳压器L497812.1A高效率升压/降压式DC-DC电源转换器L597013.1.5A降压式DC-DC电源转换器LM157214.高效率1A降压单片开关稳压器LM1575/LM2575/LM2575HV15.3A降压单片开关稳压器LM2576/LM2576HV16.可调升压开关稳压器LM257717.3A降压开关稳压器LM259618.高效率5A开关稳压器LM267819.升压式DC-DC电源转换器LM2703/LM270420.电流模式升压式电源转换器LM273321.低噪声升压式电源转换器LM275022.小型75V降压式稳压器LM500723.低功耗升/降压式DC-DC电源转换器LT107324.升压式DC-DC电源转换器LT161525.隔离式开关稳压器LT172526.低功耗升压电荷泵LT175127.大电流高频降压式DC-DC电源转换器LT176528.大电流升压转换器LT193529.高效升压式电荷泵LT193730.高压输入降压式电源转换器LT195631.1.5A升压式电源转换器LT196132.高压升/降压式电源转换器LT343333.单片3A升压式DC-DC电源转换器LT343634.通用升压式DC-DC电源转换器LT346035.高效率低功耗升压式电源转换器LT346436.1.1A升压式DC-DC电源转换器LT346737.大电流高效率升压式DC-DC电源转换器LT378238.微型低功耗电源转换器LTC175439.1.5A单片同步降压式稳压器LTC187540.低噪声高效率降压式电荷泵LTC191141.低噪声电荷泵LTC3200/LTC3200-542.无电感的降压式DC-DC电源转换器LTC325143.双输出/低噪声/降压式电荷泵LTC325244.同步整流/升压式DC-DC电源转换器LTC340145.低功耗同步整流升压式DC-DC电源转换器LTC340246.同步整流降压式DC-DC电源转换器LTC340547.双路同步降压式DC-DC电源转换器LTC340748.高效率同步降压式DC-DC电源转换器LTC341649.微型2A升压式DC-DC电源转换器LTC342650.2A两相电流升压式DC-DC电源转换器LTC342851.单电感升/降压式DC-DC电源转换器LTC344052.大电流升/降压式DC-DC电源转换器LTC344253.1.4A同步升压式DC-DC电源转换器LTC345854.直流同步降压式DC-DC电源转换器LTC370355.双输出降压式同步DC-DC电源转换控制器LTC373656.降压式同步DC-DC电源转换控制器LTC377057.双2相DC-DC电源同步控制器LTC380258.高性能升压式DC-DC电源转换器MAX1513/MAX151459.精简型升压式DC-DC电源转换器MAX1522/MAX1523/MAX152460.高效率40V升压式DC-DC电源转换器MAX1553/MAX155461.高效率升压式LED电压调节器MAX1561/MAX159962.高效率5路输出DC-DC电源转换器MAX156563.双输出升压式DC-DC电源转换器MAX1582/MAX1582Y64.驱动白光LED的升压式DC-DC电源转换器MAX158365.高效率升压式DC-DC电源转换器MAX1642/MAX164366.2A降压式开关稳压器MAX164467.高效率升压式DC-DC电源转换器MAX1674/MAX1675/MAX167668.高效率双输出DC-DC电源转换器MAX167769.低噪声1A降压式DC-DC电源转换器MAX1684/MAX168570.高效率升压式DC-DC电源转换器MAX169871.高效率双输出降压式DC-DC电源转换器MAX171572.小体积升压式DC-DC电源转换器MAX1722/MAX1723/MAX172473.输出电流为50mA的降压式电荷泵MAX173074.升/降压式电荷泵MAX175975.高效率多路输出DC-DC电源转换器MAX180076.3A同步整流降压式稳压型MAX1830/MAX183177.双输出开关式LCD电源控制器MAX187878.电流模式升压式DC-DC电源转换器MAX189679.具有复位功能的升压式DC-DC电源转换器MAX194780.高效率PWM降压式稳压器MAX1992/MAX199381.大电流输出升压式DC-DC电源转换器MAX61882.低功耗升压或降压式DC-DC电源转换器MAX62983.PWM升压式DC-DC电源转换器MAX668/MAX66984.大电流PWM降压式开关稳压器MAX724/MAX72685.高效率升压式DC-DC电源转换器MAX756/MAX75786.高效率大电流DC-DC电源转换器MAX761/MAX76287.隔离式DC-DC电源转换器MAX8515/MAX8515A88.高性能24V升压式DC-DC电源转换器MAX872789.升/降压式DC-DC电源转换器MC33063A/MC34063A90.5A升压/降压/反向DC-DC电源转换器MC33167/MC3416791.低噪声无电感电荷泵MCP1252/MCP125392.高频脉宽调制降压稳压器MIC220393.大功率DC-DC升压电源转换器MIC229594.单片微型高压开关稳压器NCP1030/NCP103195.低功耗升压式DC-DC电源转换器NCP1400A96.高压DC-DC电源转换器NCP140397.单片微功率高频升压式DC-DC电源转换器NCP141098.同步整流PFM步进式DC-DC电源转换器NCP142199.高效率大电流开关电压调整器NCP1442/NCP1443/NCP1444/NCP1445100.新型双模式开关稳压器NCP1501101.高效率大电流输出DC-DC电源转换器NCP1550102.同步降压式DC-DC电源转换器NCP1570103.高效率升压式DC-DC电源转换器NCP5008/NCP5009 104.大电流高速稳压器RT9173/RT9173A105.高效率升压式DC-DC电源转换器RT9262/RT9262A 106.升压式DC-DC电源转换器SP6644/SP6645107.低功耗升压式DC-DC电源转换器SP6691108.新型高效率DC-DC电源转换器TPS54350109.无电感降压式电荷泵TPS6050x110.高效率升压式电源转换器TPS6101x111.28V恒流白色LED驱动器TPS61042112.具有LDO输出的升压式DC-DC电源转换器TPS6112x 113.低噪声同步降压式DC-DC电源转换器TPS6200x114.三路高效率大功率DC-DC电源转换器TPS75003115.高效率DC-DC电源转换器UCC39421/UCC39422116.PWM控制升压式DC-DC电源转换器XC6371117.白光LED驱动专用DC-DC电源转换器XC9116118.500mA同步整流降压式DC-DC电源转换器XC9215/XC9216/XC9217119.稳压输出电荷泵XC9801/XC9802120.高效率升压式电源转换器ZXLB16001.2 线性/低压差稳压器121.具有可关断功能的多端稳压器BAXXX122.高压线性稳压器HIP5600123.多路输出稳压器KA7630/KA7631124.三端低压差稳压器LM2937125.可调输出低压差稳压器LM2991126.三端可调稳压器LM117/LM317127.低压降CMOS500mA线性稳压器LP38691/LP38693128.输入电压从12V到450V的可调线性稳压器LR8129.300mA非常低压降稳压器(VLDO)LTC3025130.大电流低压差线性稳压器LX8610131.200mA负输出低压差线性稳压器MAX1735132.150mA低压差线性稳压器MAX8875133.带开关控制的低压差稳压器MC33375134.带有线性调节器的稳压器MC33998135.1.0A低压差固定及可调正稳压器NCP1117136.低静态电流低压差稳压器NCP562/NCP563137.具有使能控制功能的多端稳压器PQxx138.五端可调稳压器SI-3025B/SI-3157B139.400mA低压差线性稳压器SPX2975140.五端线性稳压器STR20xx141.五端线性稳压器STR90xx142.具有复位信号输出的双路输出稳压器TDA8133143.具有复位信号输出的双路输出稳压器TDA8138/TDA8138A144.带线性稳压器的升压式电源转换器TPS6110x145.低功耗50mA低压降线性稳压器TPS760xx146.高输入电压低压差线性稳压器XC6202147.高速低压差线性稳压器XC6204148.高速低压差线性稳压器XC6209F149.双路高速低压差线性稳压器XC64011.3 基准电压源150.新型XFET基准电压源ADR290/ADR291/ADR292/ADR293 151.低功耗低压差大输出电流基准电压源MAX610x152.低功耗1.2V基准电压源MAX6120153.2.5V精密基准电压源MC1403154.2.5V/4.096V基准电压源MCP1525/MCP1541155.低功耗精密低压降基准电压源REF30xx/REF31xx156.精密基准电压源TL431/KA431/TLV431A第2章AC-DC转换器及控制器1.厚膜开关电源控制器DP104C2.厚膜开关电源控制器DP308P3.DPA-Switch系列高电压功率转换控制器DPA423/DPA424/DPA425/DPA4264.电流型开关电源控制器FA13842/FA13843/FA13844/FA138455.开关电源控制器FA5310/FA53116.PWM开关电源控制器FAN75567.绿色环保的PWM开关电源控制器FAN76018.FPS型开关电源控制器FS6M07652R9.开关电源功率转换器FS6Sxx10.降压型单片AC-DC转换器HV-2405E11.新型反激准谐振变换控制器ICE1QS0112.PWM电源功率转换器KA1M088013.开关电源功率转换器KA2S0680/KA2S088014.电流型开关电源控制器KA38xx15.FPS型开关电源功率转换器KA5H0165R16.FPS型开关电源功率转换器KA5Qxx17.FPS型开关电源功率转换器KA5Sxx18.电流型高速PWM控制器L499019.具有待机功能的PWM初级控制器L599120.低功耗离线式开关电源控制器L659021.LINK SWITCH TN系列电源功率转换器LNK304/LNK305/LNK30622.LINK SWITCH系列电源功率转换器LNK500/LNK501/LNK52023.离线式开关电源控制器M51995A24.PWM电源控制器M62281P/M62281FP25.高频率电流模式PWM控制器MAX5021/MAX502226.新型PWM开关电源控制器MC4460427.电流模式开关电源控制器MC4460528.低功耗开关电源控制器MC4460829.具有PFC功能的PWM电源控制器ML482430.液晶显示器背光灯电源控制器ML487631.离线式电流模式控制器NCP120032.电流模式脉宽调制控制器NCP120533.准谐振式PWM控制器NCP120734.低成本离线式开关电源控制电路NCP121535.低待机能耗开关电源PWM控制器NCP123036.STR系列自动电压切换控制开关STR8xxxx37.大功率厚膜开关电源功率转换器STR-F665438.大功率厚膜开关电源功率转换器STR-G865639.开关电源功率转换器STR-M6511/STR-M652940.离线式开关电源功率转换器STR-S5703/STR-S5707/STR-S570841.离线式开关电源功率转换器STR-S6401/STR-S6401F/STR-S6411/STR-S6411F 442.开关电源功率转换器STR-S651343.离线式开关电源功率转换器TC33369~TC3337444.高性能PFC与PWM组合控制集成电路TDA16846/TDA1684745.新型开关电源控制器TDA1685046.“绿色”电源控制器TEA150447.第二代“绿色”电源控制器TEA150748.新型低功耗“绿色”电源控制器TEA153349.开关电源控制器TL494/KA7500/MB375950.Tiny SwitchⅠ系列功率转换器TNY253、TNY254、TNY25551.Tiny SwitchⅡ系列功率转换器TNY264P~TNY268G52.TOP Switch(Ⅱ)系列离线式功率转换器TOP209~TOP22753.TOP Switch-FX系列功率转换器TOP232/TOP233/TOP23454.TOP Switch-GX系列功率转换器TOP242~TOP25055.开关电源控制器UCX84X56.离线式开关电源功率转换器VIPer12AS/VIPer12ADIP57.新一代高度集成离线式开关电源功率转换器VIPer53第3章功率因数校正控制/节能灯电源控制器1.电子镇流器专用驱动电路BL83012.零电压开关功率因数控制器FAN48223.功率因数校正控制器FAN75274.高电压型EL背光驱动器HV8265.EL场致发光背光驱动器IMP525/IMP5606.高电压型EL背光驱动器/反相器IMP8037.电子镇流器自振荡半桥驱动器IR21568.单片荧光灯镇流器IR21579.调光电子镇流器自振荡半桥驱动器IR215910.卤素灯电子变压器智能控制电路IR216111.具有功率因数校正电路的镇流器电路IR216612.单片荧光灯镇流器IR216713.自适应电子镇流器控制器IR252014.电子镇流器专用控制器KA754115.功率因数校正控制器L656116.过渡模式功率因数校正控制器L656217.集成背景光控制器MAX8709/MAX8709A18.功率因数校正控制器MC33262/MC3426219.固定频率电流模式功率因数校正控制器NCP165320.EL场致发光灯高压驱动器SP440321.功率因数校正控制器TDA4862/TDA486322.有源功率因数校正控制器UC385423.高频自振荡节能灯驱动器电路VK05CFL24.大功率高频自振荡节能灯驱动器电路VK06TL第4章充电控制器1.多功能锂电池线性充电控制器AAT36802.可编程快速电池充电控制器BQ20003.可进行充电速率补偿的锂电池充电管理器BQ20574.锂电池充电管理电路BQ2400x5.单片锂电池线性充电控制器BQ2401xB接口单节锂电池充电控制器BQ2402x7.2A同步开关模式锂电池充电控制器BQ241008.集成PWM开关控制器的快速充电管理器BQ29549.具有电池电量计量功能的充电控制器DS277010.锂电池充电控制器FAN7563/FAN756411.2A线性锂/锂聚合物电池充电控制器ISL629212.锂电池充电控制器LA5621M/LA5621V13.1.5A通用充电控制器LT157114.2A恒流/恒压电池充电控制器LT176915.线性锂电池充电控制器LTC173216.带热调节功能的1A线性锂电池充电控制器LTC173317.线性锂电池充电控制器LTC173418.新型开关电源充电控制器LTC198019.开关模式锂电池充电控制器LTC400220.4A锂电池充电器LTC400621.多用途恒压/恒流充电控制器LTC400822.4.2V锂离子/锂聚合物电池充电控制器LTC405223.可由USB端口供电的锂电池充电控制器LTC405324.小型150mA锂电池充电控制器LTC405425.线性锂电池充电控制器LTC405826.单节锂电池线性充电控制器LTC405927.独立线性锂电池充电控制器LTC406128.镍镉/镍氢电池充电控制器M62256FP29.大电流锂/镍镉/镍氢电池充电控制器MAX150130.锂电池线性充电控制器MAX150731.双输入单节锂电池充电控制器MAX1551/MAX155532.单节锂电池充电控制器MAX167933.小体积锂电池充电控制器MAX1736B接口单节锂电池充电控制器MAX181135.多节锂电池充电控制器MAX187336.双路输入锂电池充电控制器MAX187437.单节锂电池线性充电控制器MAX189838.低成本/多种电池充电控制器MAX190839.开关模式单节锂电池充电控制器MAX1925/MAX192640.快速镍镉/镍氢充电控制器MAX2003A/MAX200341.可编程快速充电控制器MAX712/MAX71342.开关式锂电池充电控制器MAX74543.多功能低成本充电控制器MAX846A44.具有温度调节功能的单节锂电池充电控制器MAX8600/MAX860145.锂电池充电控制器MCP73826/MCP73827/MCP7382846.高精度恒压/恒流充电器控制器MCP73841/MCP73842/MCP73843/MCP73844 647.锂电池充电控制器MCP73861/MCP7386248.单节锂电池充电控制器MIC7905049.单节锂电池充电控制器NCP180050.高精度线性锂电池充电控制器VM7205。

FAN7313参数

^ 背光电路的核心FAN7313 2011-3-28 23:03:02 上传下载附件(66.75 KB) " R0 I: a+ r+ h" z FAN7313的优势:1 宽电源供电2 具有模拟电压及PMW 两种亮度控制方式,也适应不同的控制电路。

3 亮度控制平滑4 外围元件少 5 具有两路相位相反的激励信号输出,不适宜作为全桥功率放大电路的激励控制,但适合作为半桥架构的功率放大驱动。

6 具有输出过压保护,短路保护,背光灯管断路等保护功能。

引脚定义:1 OLP1 灯管断路保护1 (阈值为1V,低于1V 进入保护) openlamp protection 2 OLP2 灯管短路保护2 , s$ x# Z8 t9 g1 O2 S, J& O3 COMP 误差放大器输出4 FB 误差放大器输入5 BDIM PWM 亮度调节输入端6 AMD 模拟亮度调整输入端7 ENA 背光使能控制8 GND9 OUTL 激励输出(低)10 VREF 基准电压输出11 VCC 芯片供电12 VB 基准电压输入13 OUTH 激励输出(高)14 VS 激励输出接低端15 SCP 短路保护端16 RT 振荡频率控制(背光灯管工作频率),由外接电阻和电容的时间常数决定。

17 BCT PWM 频率控制,外接时间常数电容(亮度控制输入,PWM 时,此引脚接地)18 OLR 过压保护控制端(电压大于2V 时保护)19 OLP4 CCFL 灯管断路保护4(阈值为1V,低于1V 时保护)20 OLP3 CCFL 灯管短路保护3 (阈值为1V,低于1V 时保护)内部框图: 2011-3-28 23:04:42 上传下载附件(62.41 KB) 2 y: Z) ]- `, Y, y. Y9 x' e* n2 V4 Y( V; p, r/ P+ y# g 对内部框图的理解&以及芯片如何实现各种功能:ENA:背光灯开启的使能输入,输入电压要高于 1.25V。

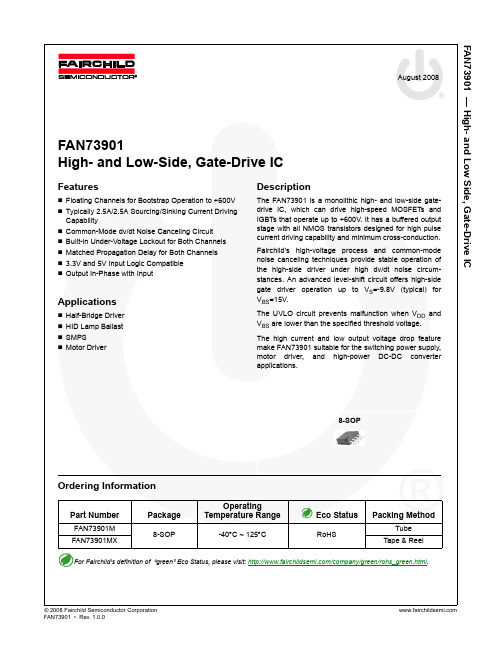

FAN73901中文资料

VB 8 HO 7

3 COM

VS 6

4 LO

VDD 5

RBOOT DBOOT

Up to 600V

R1 CBOOT

Q1 R2

OUTPUT

C1

R3

Q2

R4

Load

FAN73901 Rev.01

Figure 1. Application Circuit for Half-Bridge

Internal Block Diagram

Min. VS+10 6-VDD

VS 10 COM COM -40

Max. VS+20

600 VB 20 VDD VDD +125

Unit V V V V V V °C

© 2008 Fairchild Semiconductor Corporation

FAN73901 • Rev. 1.0.0

4

Symbol

VB VS VHO VDD VLO VIN TA

Parameter High-Side Floating Supply Voltage High-Side Floating Supply Offset Voltage High-Side Output Voltage Low-Side and Logic Supply Voltage Low-Side Output Voltage Logic Input Voltage (HIN and LIN) Operating Ambient Temperature

Name HIN LIN COM LO VDD VS HO VB

Description Logic Input for High-Side Gate Driver Output Logic Input for Low-Side Gate Driver Output Low-Side Driver Return Low-Side Driver Output Low-Side and Logic Part Supply Voltage High-Voltage Floating Supply Return High-Side Driver Output High-Side Floating Supply

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

© 2012 飞兆半导体公司

FAN7393A • Rev. 1.0.1

3

FAN7393A — 半桥栅极驱动 IC

绝对最大额定值

应力超过绝对最大额定值,可能会损坏器件。在超出推荐的工作条件的情况下,该器件可能无法正常工作,所以不建议 让器件在这些条件下长期工作。此外,长期工作在高压推荐的工作条件下工作,会影响器件的可靠性。绝对最大额定值 仅是应力规格值。除非另有说明, TA = 25°C。

IO+

输出高电平、短路脉冲电流 (5)

IO-

输出低电平、短路脉冲电流 (5)

VSS/COM VSS-COM/COM-VSS 电压承受 (5)

VS

IN 信号传播到 HO 时允许的 VS 引脚负电压

注:

5 这些参数由设计保证。

空载 (IO=0A) 空载 (IO=0A) VHO=0V, VIN=5V, PW ≤10µs VHO=15V, VIN=0V, PW ≤10µs

图 1. 典型应用电路

IN 1

250K

SD 2 DT 4

5V 250K

SCHMITT TRIGGER INPUT

RDTINT

SHOOT-THROUGH PREVENTION

DEAD-TIME { DTMIN=400ns }

HS(ON/OFF)

UVLO

LS(ON/OFF)

VSS 3

Pin 8, 9, 10 and 14 are no connection

PULSE GENERATOR

UVLO

NOISE CANCELLER

RR SQ

VSS/COM LEVEL SHIFT

图 2. 功能框图

DELAY

DRIVER

DRIVER

13 VB 12 HO 11 VS 7 VDD 6 LO 5 COM

© 2012 飞兆半导体公司

FAN7393A • Rev. 1.0.1

FAN7393A — 半桥栅极驱动 IC

2013 年 11 月

FAN7393A 半桥栅极驱动 IC

特性

浮动通道可实现高达 +600V 的自举运行 2.5A/2.5A 的典型源电流 / 灌电流驱动能力 将容许负VS摆幅扩展到-9.8V,用于VBS=15V时的信号

传播 高侧输出与 IN 输入信号同相 兼容 3.3V 和 5V 逻辑输入电平 适用于两个通道的匹配传播延迟 内置关断功能 两个通道均内置欠压锁定 (UVLO) 功能 内置共模 dv/dt 噪声消除电路 RDT=0W 时,内部最小死区时间为 400ns 可编程导通延迟控制 (死区时间)

-40 -20

High-Side Low-Side

0 20 40 60 80 100 120 Temperature [°C]

图 4. 导通传播延时 与温度的关系

tR [ns]

50 High-Side Low-Side

40

30

20

10

0 -40 -20

0 20 40 60 80 100 120 Temperature [°C]

55

100 μA

1.0

1.6 mA

450 800 μA 650 1000 μA

10 μA

VIN=0V, VDD=VBS= 扫描 7.8

8.8

9.8 V

VIN=0V, VDD=VBS= 扫描 7.3

8.3

9.3 V

VIN=0V, VDD=VBS= 扫描

0.5

V

VSHUNT VBS 电压调节器箝位电压 输入逻辑部分

最小值 VS+10 6-VDD

VS 10

COM

VSS VSS VSS -5

-40

最大值 VS+20

600 VB 20 VDD VDD 5 VDD +5 +125

单位 V V V V V V V V V °C

© 2012 飞兆半导体公司

FAN7393A • Rev. 1.0.1

4

符号 tON tOFF tSD MtON MtOFF tR tF

DT

MDT

参数 导通传播延迟 (6) 关断传播延时 关闭传播延迟 延迟匹配, HO 和 LO 开启 延迟匹配, HO 和 LO 关断 导通上升时间 关断下降时间

死区时间:LO 关断至 HO 开启 HO 关断至 LO 开启

死区时间匹配 =|DTLO-HO - DTHO-LO|

工作条件 VS=0V, RDT=0Ω VS=0V

VS=0V VS=0V RDT=0Ω RDT=200KΩ RDT=0Ω RDT=200KΩ

最小值 典型值 最大值 单位

530 730 ns

130 250 ns

140 210 ns

0

90

ns

0

40

ns

25

50

ns

15

35

ns

300 400 5002.0

2.5

A

2.0

2.5

A

-5.0

5.0 V

-9.8 -7.0 V

© 2012 飞兆半导体公司

FAN7393A • Rev. 1.0.1

5

FAN7393A — 半桥栅极驱动 IC

动态电气特性

除非另有说明, VBIAS(VDD, VBS)=15.0V, VSS=COM=0V, CL=1000pF, DT=VSS, TA=25°C。

符号

特性

测试条件

最小值 典型值 最大值 单位

电源部分

IQDD VDD 静态电源电流

IQBS VBS 静态电源电流

IPDD VDD 工作电源电流

IPBS ISD ILK

VBS 工作电源电流 关闭模式电源电流 偏置漏电流

自举电源部分

VDDUV+ VBSUV+ VDDUVVBSUVVDDUVH VBSUVH

注意:

1. 本 IC 的 VBS 端含有电压调节器。该电源引脚不应使用超过 “ 电气特性 ” 部分指定的 VSHUNT 低阻抗电压源驱动。 2. 安装到 76.2 x 114.3 x 1.6mm PCB 板 (FR-4 环氧玻璃材料 )。

3. 参考下列标准: JESD51-2:集成电路热测试方法环境条件 – 自然通风和 JESD51-3:含铅表面贴装封装的低有效导热系数测试板。

2

FAN7393A — 半桥栅极驱动 IC FAN7393A

引脚布局

引脚定义

引脚号 1 2 3 4 5 6 7 8 9 10 11 12 13 14

IN 1 SD 2 VSS 3 DT 4 COM 5 LO 6 VDD 7

14 NC 13 VB 12 HO 11 VS 10 NC 9 NC 8 NC

14-SOP

订购信息

器件编号 FAN7393AMX

封装 14-SOIC

工作温度 -40°C 至 +125°C

包装方法 卷带和卷盘

© 2012 飞兆半导体公司 FAN7393A • Rev. 1.0.1

FAN7393A — 半桥栅极驱动 IC

典型应用电路图

+15V

飞兆的高压工艺和共模噪声消除技术可使高侧驱动器在高 dv/dt 噪声环境下稳定运行。先进的电平转换电路,能使 高侧栅极驱动器的工作电压在 VBS=15V 时 VS 达到 -9.8V (典型值)。

UVLO 电路可防止 VDD 和 VBS 低于指定的阈值电压时发 生故障。

大电流和低输出压降的特性,使得该器件适合于不同的半 桥和全桥逆变器、电机驱动变频器、开关电源、感应加 热,以及大功率 DC-DC 转换器等应用。

图 3. 引脚布局 (俯视图)

名称 IN SD VSS DT

COM LO VDD NC NC NC VS HO VB NC

说明 高侧和低侧栅极驱动器输出的逻辑输入,与 HO 同相 关断逻辑输入 逻辑地 通过外接电阻实现死区时间控制 (参考 VSS) 接地 低侧栅极返回 电源电压 无连接 无连接 无连接 高侧浮动电源电压返回 高侧驱动输出 高侧浮动电源 无连接

VDD 和 VBS 电源欠压 正向阈值电压 VDD 和 VBS 电源欠压 负向阈值电压

VDD 和 VBS 电源欠压锁定滞回电压回差

电压调节器部分

VIN=0V 或 5V VIN=0V 或 5V fIN=20KHz,空载 CL=1nF, fIN=20KHz, RMS SD=VSS VB=VS=600V

600 1000 μA

-0.3 VB-VSHUNT

VS-0.3 -0.3 -0.3 -0.3 VSS -0.3

VDD-25

-55

625.0 VB+0.3 VB+0.3 VDD+0.3

25.0 VDD+0.3

5.5 VDD+0.3 VDD+0.3

± 50 1

110 +150 +150

V V V V V V V V V V/ns W °C/W °C °C

5

6

µs

0

40

ns

0

500 ns

注: 6 导通传播延迟包括死区时间。

© 2012 飞兆半导体公司

FAN7393A • Rev. 1.0.1

6

FAN7393A — 半桥栅极驱动 IC

典型特性

tON [ns]

750 700 650 600 550 500 450 400 350

4. 在任何情况下,都不要超过 PD 最大值。

推荐工作条件

推荐的操作条件表明确了器件的真实工作条件。指定推荐的工作条件,以确保器件的最佳性能达到数据表中的规格。 飞兆不建议超出额定或依照绝对最大额定值进行设计。