基于FPGA的计数器设计

基于FPGA的计数器的程序的设计方案

基于FPGA的计数器的程序设计方案1.1 FPGA简介FPGA(Field-Progrmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。

它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

自1985 年Xilinx 公司推出第一片中大规模现场可编程逻辑器件(FP2GA) 至今,FPGA 已经历了十几年的历。

在这十几年的过程中,可编程器件有了惊人的发展:从最初的1200 个可利用门,到今天的25 万可利用门,规模增大了200 多倍; FPGA 供应商也从Xilinx 的一枝独秀,到今天近20 个厂商的分庭抗争;FPGA 从单一的基于SRAM结构到今天各种结构类型的出现,都充分体现了可编程器件这一巨大市场的吸引力。

FPGA 不仅可以解决电子系统小型化、低功耗、高可靠性等问题,而且其开发周期短、开发软件投入少、芯片价格不断降低。

由于目前电子产品生命周期相对缩短,相近功能产品的派生设计增多等特点,促使FPGA 越来越多地取代了ASIC 的市场,特别是对国内众多的科研单位来说,小批量、多品种的产品需求,使得FPGA 成为首选。

1.2 硬件描述语言VHDL特点功能强大、设计灵活。

VHDL具有功能强大的语言结构,可以用简洁明确的源代码来描述复杂的逻辑控制。

它具有多层次的设计描述功能,层层细化,最后可直接生成电路级描述。

VHDL支持同步电路、异步电路和随机电路的设计,这是其他硬件描述语言所不能比拟的。

VHDL还支持各种设计方法,既支持自底向上的设计,又支持自顶向下的设计;既支持模块化设计,又支持层次化设计。

支持广泛、易于修改。

由于VHDL已经成为IEEE标准所规范的硬件描述语言,目前大多数EDA工具几乎都支持VHDL,这为VHDL的进一步推广和广泛应用奠定了基础。

基于fpga的计数器设计代码

基于fpga的计数器设计代码基于FPGA的计数器设计代码介绍:来自电子系统设计实验课程的一个项目,要求编写一段基于FPGA 的计数器设计代码,但是考虑到本实验课程源自一门免费的开源课程,因此无法提供实际的设备来验证此设计代码,但是可以通过模拟环境进行测试以确保实现正确设计功能,本文将介绍如何利用FPGA对计数器进行设计。

实现方法:1.首先需要确定将用哪种FPGA芯片来实现计数器功能,例如Xilinx Spartan-6的FPGA。

2.然后确定使用哪种电路来实现计数器功能,可以使用逻辑器件来实现,例如可以使用多路触发器、多变量单位、或是查找表等电路。

3.接下来就是根据前面两步的确定,开始编写实现计数器设计的代码,例如VHDL语言或Verilog语言。

4.最后进行代码仿真,使用设计的代码来仿真计数器的功能,以确保代码完全正确。

示例代码:下面是一段可以实现计数器设计的代码,采用的是VHDL语言:--计数器设计代码LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY COUNTER ISPORT (reset : IN STD_LOGIC;clk : IN STD_LOGIC;count : OUT STD_LOGIC_VECTOR (7 DOWNTO 0));END COUNTER;ARCHITECTURE RTL OF COUNTER ISBEGINPROCESS(clk, reset)BEGINIF (reset='1') THENcount <= '00000000'; --初始值为0ELSIF (clk='1' and clk'EVENT) THENcount <= count + 1; --正常的计数END IF;END PROCESS;END RTL;以上代码可以实现一个八位的计数器,当reset为高电平时,计数器初始值为0,每次当clk上升沿时,计数器递增1,当计数器到达最大值255时,再次上升时从0开始重复计数。

基于FPGA的定时器计数器的设计与实现

基于FPGA的定时器/计数器的设计与实现摘要本课题旨在用EDA工具与硬件描述语言设计一个基于Altera公司的FPGA 16位计数器\定时器,可对连续和非连续脉冲进行计数,并且计数器在具有计数定时功能基础上,实现简单脉宽调制功能和捕获比较功能。

本设计采用QuartusII编译开发工具使用VerilogHDL 设计语言进行设计,并采用了由上而下的设计方法对计数器进行设计,体现了VerilogHDL 在系统级设计上自上而下设计风格的优点。

本设计中采用了三总线的设计方案,使设计更加简洁与规范。

本设计所有模块与功能均在Quartus II 7.0_1.4G_Liwz版本下通过编译与仿真,实现了定时器/计数器的设计功能。

关键词:VerilogHDL硬件描述语言;QuartusII;FPGA;定时器/计数器FPGA-based timer / counter design and implementationThis topic aims to use EDA tools to design a 16 bit counter \ timer based on Altera's FPGA by hardware descripe language, which can count continuous and discontinuous pulset, and the counter with the function of capture and PWM. This design uses VerilogHDL language and top-down design method to design the counter on QuartusII compile tool, the design reflect the advantages of VerilogHDL top-down design in system-level design. The design uses a three-bus design, which make design much more specifications and concise. The design and function of all modules are compiled and simulationed on the Quartus II 7.0_1.4G_Liwz versions, and achieve the timer / counter’s features.Key words: VerilogHDL hardware description language; QuartusII; FPGA; timer / counter河北大学2011届本科生毕业论文(设计)目录引言 (1)1 计数器设计方式选择与论证 (4)1.1 计数器实现方案论证 (4)1.2 设计方式选择认证 (4)1.2.1 自下而上的设计方法 (4)1.2.2 自上而下的设计方法 (4)1.2.3 混合的设计方法 (5)2 计数器整体设计方案 (6)3 计数器/定时器各种工作方式的设计 (8)3.1 计数模块 (8)3.1.1 位加计数器模块 (8)3.1.2 位减计数器 (9)3.2 顶层模块设计 (11)4 总结 (19)谢辞........................................ 错误!未定义书签。

基于fpga的计数器的程序设计

基于FPGA的计数器的程序设计摘要本文介绍了一种基于FPGA的,由顶层到底层设计的数字计数器。

本文主要包括该计数器的设计基础和实现方法以及译码与显示等内容,描述了它的设计平台、工作原理和软硬件实现。

本设计主要有分频器、四位计数器、16位锁存器以及数码管显示电路四个模块组成。

计数器各模块设计采用VHDL硬件描述语言编程,极大地减少了硬件资源的占用,仿真与分析结果表明,该数字计数器性能优异,软件设计语言灵活,硬件简单,速度快。

关键词FPGA计数器VHDL分频器目录基于FPGA的计数器的程序设计 (1)摘要 (1)1 绪论 (3)1.1 FPGA简介 (3)1.2硬件描述语言VHDL简介 (3)1.3开发工具Quartus II简介 (4)2整体设计方案 (4)3各功能模块设计及仿真 (5)3.1分频器的设计 (5)3.1.1分频器设计原理 (5)3.1.2源程序及波形仿真 (6)3.1.3分频器RTL 电路图 (7)3.2计数器的设计 (7)3.2.1分频器设计原理 (7)3.2.2源程序及波形仿真 (8)3.2.3 RTL 电路图 (11)3.3锁存器的设计 (11)3.3.1锁存器设计原理 (11)3.3.2锁存器源程序及波形仿真 (12)3.3.3锁存器RTL电路图 (13)3.4显示部分的设计 (13)3.4.1七段数码管显示原理 (13)3.4.2七段数码管显示源程序及波形仿真 (15)3.4.3七段数码管显示RTL 电路图 (16)4系统顶层设计 (17)4.1.1自顶向下的设计方法 (17)4.1.2 顶层设计源程序及其仿真波形 (17)4.1.3系统顶层RTL 电路图 (20)5总结 (21)参考文献 (22)1 绪论1.1 FPGA简介FPGA 是现场可编程门阵列(Field Programmable Gate Array)的简称。

FPGA 器件及其开发系统是开发大规模数字集成电路的新技术。

基于FPGA的计算器设计

基于FPGA的计算器设计基于FPGA(可编程逻辑门阵列)的计算器设计是一种使用FPGA开发板和硬件描述语言来实现的计算器。

它可以进行基本的数学运算,如加法、减法、乘法和除法等。

FPGA计算器不仅具有快速的运算速度和高度的可靠性,还具有较小的体积和低功耗。

FPGA计算器通常由输入、控制单元、运算单元和输出组成。

输入可以通过按钮、键盘或其他输入设备来实现。

控制单元负责解析输入并发出相应的控制信号。

运算单元是FPGA计算器的核心组件,它负责接收控制信号,并执行相应的运算操作。

输出单元将运算结果显示在计算器的屏幕上。

使用硬件描述语言(HDL)来实现FPGA计算器的设计可以提供高度的灵活性和可扩展性。

HDL允许开发人员通过编程方式定义逻辑门和电路功能,而不是通过物理硬件组件来实现。

这意味着开发人员可以根据需要添加新的运算功能,并且可以很容易地在FPGA计算器上进行修改和更新。

FPGA计算器可以通过对数据进行二进制表示来实现各种数学运算。

例如,加法可以通过将两个二进制数相加来实现。

具体实现可以使用查找表(Look-up Table)或全加器等组合逻辑电路来完成。

除法则比较复杂,通常需要使用除法算法来实现。

除了基本的数学运算,FPGA计算器还可以实现其他功能,如逻辑运算、位操作和存储器操作等。

逻辑运算可以用于实现条件语句和循环语句等流程控制功能。

位操作可以用于提取和修改数据的特定位。

存储器操作可以用于存储和读取数据。

基于FPGA的计算器设计有许多优点。

首先,FPGA计算器具有非常快的运算速度,比软件计算器更加高效。

其次,FPGA计算器具有较小的体积和低功耗,适合嵌入式系统或低功耗应用场景。

此外,由于FPGA计算器的硬件实现,它也具有较高的稳定性和可靠性。

然而,基于FPGA的计算器设计也存在一些挑战。

首先,硬件描述语言的学习成本较高,需要开发人员具备一定的硬件设计知识。

其次,FPGA 计算器的开发过程相对复杂,需要编写和调试大量的HDL代码。

【设计】基于FPGA的计算器设计毕业论文

【关键字】设计毕业设计(论文)题目: 基于FPGA 的计算器设计The design of calculator based on FPGA基于FPGA的计算器设计研究生:XX 指导老师:XX摘要本文介绍了一个简单计算器的设计,基于硬件描述语言VHDL采用了现场可编程逻辑器件FPGA进行设计,并在Altera公司的Quartus Ⅱ软件上实现仿真。

系统由键控模块、运算、保存模块和译码显示模块四个部分组成,计算部分为加法器、减法器、乘法器和除法器,保存部分需要3个保存器来实现:内部累加器(acc)、输入寄存器(reg)以及结果暂存器(ans)。

显示部分由四个七段译码管组成,分别来显示输入数字,输入部分采用外接键盘,外部的8个按键他们能以单键和组合键的形式完成0~9999之内的‘加’、‘减’、‘乘’、‘除’、‘符号变换’、‘保存数据’和‘读取数据’等七种功能运算其结构简单,易于实现。

关键词:FPGA;VHDL;计算器;设计The design of calculator based on FPGAGraduate Student: Dongdong Fan Supervisor: Shuxiang SongAbstractThis article describes the design of a simple calculator, the design uses Field Programmable Gate Array FPGA based on VHDL hardware description language to design and Altera's Quartus Ⅱ in software for emulation. This system is componented by the key control module, computing, storage and decoding display module of the four parts, the computing part include adder, subtractor, multiplier and divider,Storage part needs three memory to help achieved: internal accumulator (acc), input register (reg) as well as the results of registers (ans). Display part is made up four decoder of 7 sections, respectively to show the number of input. The 8 keys they can by single combined key forms to be completed addition, multiplication, division arithmetic operator and symbol transform,stored data and read seven function of operation within 0 to 9999 numbers.its structure is simple and easy to implement.Key words:FPGA; VHDL; calclute ; design目录第1章引言1.1 课程设计的目的与意义在人类学会交易的时候,计算也随之产生,而算盘作为计算最实用的工具存在了几千年。

基于FPGA的计时器设计(最终)

本科毕业设计(论文)基于FPGA的计时器的设计学院自动化学院专业电子信息科学与技术年级班别2009级(1)班学号3109001158学生姓名刘健忠指导教师谭北海2013年4月基于F P G A 的计时器设计刘健忠自动化学院摘要随着电子设计自动化技术和可编程逻辑器件的出现和飞速发展,在设计周期得到大大的缩短的同时系统成本也有了大幅度的降低,显然标准逻辑器件的组装已远不能满足这方面的要求。

而Verilog HDL能提供高阶电路描述语言的方式,让复杂的电路可以通过Verilog HDL编辑器的电路合成方式,轻易而且快速的达到设计的规格。

由于Verilog HDL电路描述语言能涵盖的范围相当广,能适用于各种不同阶层的设计工程师的需要,所以Verilog HDL电路设计毫无疑问的成为硬件设计工程师的必备工具。

本系统是用Verilog编写的基于Altera DE2的电话计费器。

该设计采用了现场可编程逻辑器件FPGA设计,并基于硬件描述语言Verilog HDL在Altera公司的Quartus Ⅱ软件上实现仿真。

根据电话局反馈回来的信号,此信号是提前预设的,数码管显示通话类型、用户余额以及通话时长(包括秒数和分钟数)。

根据每种通话类型的计费价格不同,当系统所设置的余额数不够,用户将无法拨通电话,当用户余额小于指定金额时,系统发出警告信号,提醒用户。

当告警时间过长(超过1分钟)时自动切断通话信号。

当用户结束通话,系统清零。

关键词:Verilog ,FPGA,通话信号,计时器AbstractWith the rapid development of electronic design automation technology and programmable logic devices which greatly shorten the design period and reduced the cost of the system at the same time. Apparently, the assembly of standard logic devices can not meet the requirements in this regard. Verilog HDL can provide high-level circuit description language, which allows complex circuit by the Verilog HDL Editor circuit synthesis method as well by meeting the design specification appropriately. Verilog HDL circuit description language covers a very wide range,which can be applied to a variety of different sectors of the needs of design engineers, the circuit design of Verilog HDL without a doubt to become an essential tool for hardware design engineers.The system is based on Altera DE2 written by Verilog phone devices. It is used by Field Programmable Gate Array FPGA based on Verilog HDL hardware description language to design and Altera's Quartus Ⅱin software for emulation. According to the feedback of the telephone office back signal which is actually pre-designed, digital pipe display type, user balance and phone call duration (including the number of seconds or minutes). Depending on the billing price of each call type is different,when a began to balance the set is not enough, the user will not be able to dial the phone, and when the balance is less than the specified money, issuing a warning signal system, reminding to users. When the alarm time is too long (more than 1 minutes), the conversation signal will be automatically cut off . When the user end the call, the system will be reseted.Key words:Verilog ,FPGA,Calling signal,calculagraph目录1绪论 (1)1.1 课题研究的目的 (1)1.2 国内外发展现状 (1)1.3课题的主要技术路线 (2)2FPGA技术及硬件描述语言 (3)2.1 FPGA的介绍 (3)2.1.1可编程逻辑器件发展简史 (3)2.1.2可编程逻辑器件的基本结构 (3)2.1.3可编程逻辑器件分类 (4)2.1.4 Altera Cyclone Ⅱ系列器件介绍 (5)2.1.5 FPGA的开发流程 (5)2.2 FPGA设计方法 (6)2.3 利用硬件描述语言(HDL)的硬件电路设计方法 (7)2.4 Verilog HDL语言的设计流程 (8)2.5 Quartus Ⅱ概述及其设计流程 (11)2.5.1 Quartus Ⅱ概述 (11)2.5.2 Quartus Ⅱ设计流程 (12)3系统总体设计 (14)3.1 计费模块介绍 (14)3.2 预设模块介绍 (15)3.3 时钟分频模块介绍 (15)3.4 分拆模块介绍 (15)3.5 数码管显示模块介绍 (16)3.6 警告模块介绍 (17)3.7 逻辑资源使用情况 (17)4系统的操作与分析 (18)4.1系统功能介绍 (18)4.2 选择通话类型和设置余额 (20)4.3通话开始 (21)4.4通话结束 (22)结论 (23)参考文献 (24)致谢 (25)附录A (26)附录B (27)附录C (31)附录D (32)附录E (33)附录F (35)附录G (36)1绪论1.1课题研究的目的时钟计时器在现在应用场合非常的广泛,近年来,随着科学技术的进步和时代的发展,人们对时钟的功能和精度提出了越来越高的要求,各种时钟的设计也越来越重要。

华中科技大学基于FPGA的十进制加减可逆计数器

实验名称:十进制加减可逆计数器实验组别:⑨实验人:XJY 班级:光信1102 学号:U201114XXX目标要求:利用实验板实现十进制加减可逆计数器设计,具体要求为:拨码开关键SW1为自动可逆加减功能键,当SW1为HIGH时,计数器实现自动可逆模十加减计数功能,即4个七段数码管上几乎同步显示0—1—2—3—4—…9—8—7—…0—1…的模十自动可逆加减计数结果;当SW1为LOW时,计数器按拨码开关键SW0的选择分别执行加减计数功能。

即当SW0为HIGH时,计数器实现模十加计数功能,即4个七段数码管上几乎同步显示0—1—2—3—4—…9——0—1…的模十加计数结果;当SW0为LOW时,8—7…的模十减计数结果。

实现原理:源码清单:`timescale 1ns / 1ps////////////////////////////////////////////////////////////////////////////////// // Company:// Engineer://// Create Date: 14:24:13 12/09/2013// Design Name:// Module Name: xjy// Project Name:// Target Devices:// Tool versions:// Description://// Dependencies://// Revision:// Revision 0.01 - File Created// Additional Comments://////////////////////////////////////////////////////////////////////////////////// module xjy(input clk,input SW1,input SW0,input clear,input reset,output reg[3:0] sl_reg,output reg [6:0]segdat_reg);reg [26:0] count;reg [3:0] q;reg x;always@(posedge clk)beginif(clear) beginsl_reg<=0;count<=0;endelsecount<=count+1;endalways@(posedge count[24]) //程序运行时用//always@(posedge count[4]) 程序模拟时使用beginif (reset) begin q<=0; x<=0; endelse begincase(SW1)1'd1:begincase(x)1'd0: beginif(q==4'd8) x<=1;q<=q+1;end1'd1: beginif(q==4'd1) x<=0;q<=q-1;endendcaseend1'd0:begincase(SW0)1'd0:beginif(q==4'd0) q<=4'd9;else q<=q-1;end1'd1:beginif(q==4'd9) q<=4'd0;else q<=q+1;endendcaseendendcaseendendalways@(q) // 数码管显示处理begincase(q)4'h0: segdat_reg = 7'b0000001; //04'h1: segdat_reg = 7'b1001111; //14'h2: segdat_reg = 7'b0010010; //24'h3: segdat_reg = 7'b0000110; //34'h4: segdat_reg = 7'b1001100; //44'h5: segdat_reg = 7'b0100100; //54'h6: segdat_reg = 7'b0100000; //64'h7: segdat_reg = 7'b0001111; //74'h8: segdat_reg = 7'b0000000; //84'h9: segdat_reg = 7'b0000100; //9default: segdat_reg = 7'b0111000; //Fendcaseendendmodule测试文件清单:`timescale 1ns / 1ps//////////////////////////////////////////////////////////////////////////////// // Company:// Engineer://// Create Date: 17:46:25 12/09/2013// Design Name: XJY// Module Name: D:/ISE/XJY/xjy/xjy_test.v// Project Name: xjy// Target Device:// Tool versions:// Description://// Verilog Test Fixture created by ISE for module: XJY //// Dependencies://// Revision:// Revision 0.01 - File Created// Additional Comments:////////////////////////////////////////////////////////////////////////////////// module xjy_test;// Inputsreg clk;reg SW1;reg clear;reg reset;// Outputswire [3:0] sl_reg;wire [6:0] segdat_reg;// Instantiate the Unit Under Test (UUT)XJY uut (.clk(clk),.SW1(SW1),.clear(clear),.reset(reset),.sl_reg(sl_reg),.segdat_reg(segdat_reg));always begin#10; clk=~clk;endinitial begin// Initialize Inputsclk = 0;SW1 = 0;SW0=1;clear =1;reset = 1;// Wait 60 ns for global cleat to finish#60;clear =0;// Wait 60 ns for global reset to finish#60;reset = 0;// Add stimulus hereendEndmodule管脚定义文件:#Created by Constraints Editor (xc3s100e-cp132-4) - 2013/12/10 NET "clk" TNM_NET = clk;TIMESPEC TS_clk = PERIOD "clk" 20 ns HIGH 50%;NET "segdat_reg[6]" LOC = L14;NET "segdat_reg[5]" LOC = H12;NET "segdat_reg[4]" LOC = N14;NET "segdat_reg[3]" LOC = N11;NET "segdat_reg[2]" LOC = P12;NET "segdat_reg[1]" LOC = L13;NET "segdat_reg[0]" LOC = M12;NET "sl_reg[0]" LOC = F12;NET "sl_reg[1]" LOC = J12;NET "sl_reg[2]" LOC = M13;NET "sl_reg[3]" LOC = K14;NET "clear" LOC = K3;NET "clk" LOC = B8;NET "SW1" LOC = L3;NET "clk" SLEW=FAST;NET "reset" LOC=B4;NET "SW0" LOC=P11;NET "SW1" LOC=L3;系统使用说明:clear 为程序开始按钮,定义为开发板的拨码开关SW3reset 为程序清零按钮,拨至低电位后显示清零,定义为拨码开关SW2SW1 为程序功能控制按钮,定义为拨码开关SW1SW0 为程序功能控制按钮,定义为拨码开关SW0系统功能与性能测试结果:实验开始之前将SW3,SW2,SW1,SW0,均调至HIGH实验开始调SW3(clear),SW2(reset)为LOW当SW1为HIGH时,计数器实现自动可逆模十加减计数功能,即4个七段数码管上几乎同步显示0—1—2—3—4—…9—8—7—…0—1…的模十自动可逆加减计数结果;当SW1为LOW时,计数器按拨码开关键SW0的选择分别执行加减计数功能。

基于FPGA的PLC并行计数器的设计_张炜

第4期

张 炜 , 等 : 基于 F P G A的P L C 并行计数器的设计

· 1 0 4 5·

至 0 时计数完成 。 采用 F P GA 设 计 的 计 数 器 : 数 量 为 2 5 6 个, 计数频率在 1 0k H z 以 上 , 计 数 范 围 为 1~6 7 1 0 8 8 6 4。A RM 向F P GA 写入的计数器数据格式如表 1 所示 。

用A RM 作为 P L C 控制系统的控制器 ,F P GA 协同完成各种并 行运算 ,A RM 与 F P GA 功 能 互 补 , 可 以 充 分 发 挥 A RM 处 理

[ ] 器的高速低功耗和 F P GA 可编程逻辑灵活并行的特点 3-4 。

1 A RM-F P G A 通信方式与协议

A RM 与 F P GA 通信的方式和 A RM 访问外部存储器类似 , 当A RM 需要将数据发送或读回时 , 只需按 照 一 定 的 数 据 格 式 与通信时序 访 问 F P GA。 而 采 用 快 速 G P I O 端口来实现 A RM [ 5] , 与F P GA 的通信 比使用传统 G P I O 端口要快将近 3 . 5倍 。

图 1 计数器数据读写时序图

图中 :c l k 4 8M 为系统时钟输入线 ; r s t为复位控制线 ; r w 为读 写控制线 ;e n 为 片 选 控 制 线 ;a d d r 为 地 址 总 线 ;d a t a为 数 据 总线 。

; 。 收稿日期 : 2 0 1 2 0 7 1 3 2 0 1 2 0 8 1 5 - - 修回日期 : - - ; ( 基金项目 : 广西 科 学 基 金( 桂科自2 桂科自 0 1 1 G XN S F A 0 1 8 1 5 3) ) 。 0 9 9 1 0 6 7 , 作者简介 : 张 炜( 男, 湖 北 黄 冈 人, 硕 士 研 究 生, 主要从事 1 9 8 7 -) 过程控制与自动化装置的研究 。 , 李克俭 ( 女, 湖北 武 汉 人 , 副 教 授, 高 级 工 程 师, 主要从事电 1 9 6 2 -) 力电子技术与自动化装置的研究 。

基于FPGA的计算器设计

基于FPGA的计算器设计引言:FPGA(Field-Programmable Gate Array)是一种现场可编程门阵列,它能够被重新编程以适应不同的电路设计需求。

基于FPGA的计算器设计具有很大的灵活性和可扩展性,可以实现不同类型的计算功能。

本文将介绍基于FPGA的计算器设计的原理、实现方法和一些相关应用。

一、基本原理1.输入部分:用于输入待计算的数字和操作符。

2.各种算术和逻辑运算电路:根据输入的操作符和数字,进行相应的计算操作。

3.结果显示部分:用于显示计算的结果。

二、实现方法1.设计算术和逻辑运算电路:根据计算器的需求,设计加法、减法、乘法、除法等算术运算电路,同时还要设计逻辑运算电路,如与门、或门、非门等。

2.设计输入模块:通过按键或其他输入方式输入待计算的数字和操作符。

3.设计控制模块:根据输入的操作符,控制算术和逻辑运算电路的工作顺序和时序。

4.设计结果显示模块:将计算结果显示在数码管或LCD屏幕上。

三、设计思路及具体实现方法1.输入模块设计:可以采用按键输入方式,数字键用于输入待计算的数字,功能键用于输入操作符。

2.算术与逻辑运算电路设计:通过组合逻辑电路设计实现各种算术和逻辑运算,如加法电路、乘法电路等。

将输入信号与操作符信号传入相应的运算电路,经过计算后得到结果。

3.控制模块设计:根据输入的操作符,控制算术和逻辑运算电路的工作顺序和时序。

可以使用状态机或者组合逻辑电路实现。

4.结果显示模块设计:将计算结果显示在数码管或LCD屏幕上。

根据计算结果的位数设计相应的显示模块。

四、应用领域基于FPGA的计算器设计可以用于各种计算任务,包括科学计算、金融计算、矩阵计算等。

除了基本的四则运算,还可以实现复杂函数的计算,如三角函数、指数函数等。

FPGA计算器还可以应用于数字信号处理、图像处理等领域,用于实时计算和数据处理。

五、设计优势与局限性1.优势:(1)灵活性高:FPGA可编程性强,可以根据需要重新编程,实现各种不同类型的计算功能。

基于FPGA和单片机的多功能计数器设计

基于FPGA和单片机的多功能计数器设计

一、系统方案

方案1:采用中小规模数字电路构成系统,由计数器构成主要的测量模块。

用定时器组成主要的控制电路。

此方案软件设计简单,但外围芯片过多,且频带窄,实现起来较复杂,功能不强,而且不能程控和扩展。

方案2:采用单片机实现。

被测信号经调理后送入单片机,利用其内部的计数器完成计数,然后再进行数据处理和显示,但单片机在处理高速信号时略显吃力。

方案3:利用FPGA对调理后的被测信号实现高速计数,单片机软件执行高精度浮点数运算并显示。

单片机完成系统的数据处理、逻辑控制和人机交互功能;大规模现场可编程器件(FPGA)实现外围计数功能。

电路框图如图1所示。

基于FPGA的计数器的设计

3)为225计数分频电路建立元件符号。

方法:先设置要建立原件符号的文件为顶层文件(project——set as top),然后生成符号文件(File——create< update——create symbol file for current file),然后在当前工程下元件库中就有所产生的元器件了

实验操作要点及总结(记录实验过程中的重点、难点及遇到的问题、实验结果):

实验成绩

指导老师签字

2、用多个D触发器级联构成多位的二进制计数器,将板载的50MHz时钟225分频,产生周期约1秒的分频时钟,编程下载,用LED灯观察输出的分频信号。

四、实验过程及结果记录

1、D触发器构成的一位二进制计数器

1)原理图

2)记录实验过程和仿真波形

2、D触发器级联构成的225计数电路

1)完成原理图输入编译;

实验报告九

基于FPGA的计数器的设计

一、实验目的

1、学习QuartusII软件的使用;

2、掌握计数器的工作原理和设计方法;

3、掌握用原理图输入设计计数器的全过程。

二、实验设备与器件

Altera公司的CycloneIII系列器件及相应的FPGA开发板,QuartusII软件等。

三、实验内容

1、以D触发器构成的一位二进制计数器(二分频器)为例,熟悉QuartusII软件设计过程;

fpga多通道脉冲计数器的设计与实现

fpga多通道脉冲计数器的设计与实现在数字电路设计领域中,FPGA(现场可编程门阵列)被广泛应用于各种应用,其中包括多通道脉冲计数器。

本文将从FPGA多通道脉冲计数器的设计与实现展开讨论,深入探讨其原理、技术和应用。

1. 引言FPGA多通道脉冲计数器是一种基于FPGA技术的高性能计数器,可同时对多个输入通道的脉冲信号进行计数和分析。

其设计与实现涉及到数字电路设计、时序控制、信号处理等多个方面,具有很高的工程价值和学术研究意义。

2. FPGA技术概述FPGA是一种可编程逻辑器件,具有灵活可编程、并行处理能力强、资源丰富等特点,广泛用于数字信号处理、通信、图像处理等领域。

在多通道脉冲计数器设计中,FPGA的并行计算和资源复用能力将发挥重要作用。

3. 多通道脉冲计数器原理多通道脉冲计数器是指能够同时对多个输入通道的脉冲信号进行计数和统计的计数器。

其原理是通过FPGA多通道输入模块对输入信号进行采样和处理,然后将处理后的数据传输至计数模块进行计数和存储,最终实现对多通道脉冲信号的精确计数和分析。

4. 设计与实现在实际设计中,多通道脉冲计数器的FPGA实现需要考虑到输入通道数、时钟频率、计数精度、数据存储等多个方面的问题。

通过适当的电路设计和FPGA编程,可以实现高性能、高稳定性的多通道脉冲计数器。

5. 应用与展望多通道脉冲计数器在核物理实验、粒子物理研究、医学影像等领域有着广泛的应用前景,其FPGA实现技术将成为未来研究的热点之一。

6. 总结与展望通过本文的讨论,我们全面了解了FPGA多通道脉冲计数器的设计与实现,明确了其原理、技术特点和应用前景。

随着FPGA技术的不断发展和应用,多通道脉冲计数器将在更多领域展现出其重要作用。

个人观点:FPGA多通道脉冲计数器的设计与实现是一个充满挑战和机遇的领域,需要对数字电路、信号处理、FPGA编程等多个方面有深入的理解和应用。

随着科学技术的发展,多通道脉冲计数器将在更多领域得到应用,为相关领域的研究和应用带来新的机遇和突破。

基于FPGA的计算器设计说明

研究生课程论文课程名称 FPGA及片上系统SOPC应用授课学期学年第一学期学院 X专业 C学号 C1C任课教师 C论文题目基于FPGA的计算器设计交稿日期 2014年01月09日成绩X基于FPGA的计算器设计研究生:XX 指导老师:XX摘要本文介绍了一个简单计算器的设计,基于硬件描述语言VHDL采用了现场可编程逻辑器件FPGA进行设计,并在Altera公司的Quartus Ⅱ软件上实现仿真。

系统由键控模块、运算、存储模块和译码显示模块四个部分组成,计算部分为加法器、减法器、乘法器和除法器,存储部分需要3个存储器来实现:部累加器(acc)、输入寄存器(reg)以及结果暂存器(ans)。

显示部分由四个七段译码管组成,分别来显示输入数字,输入部分采用外接键盘,外部的8个按键他们能以单键和组合键的形式完成0~9999之的‘加’、‘减’、‘乘’、‘除’、‘符号变换’、‘存储数据’和‘读取数据’等七种功能运算其结构简单,易于实现。

关键词:FPGA;VHDL;计算器;设计The design of calculator based on FPGA Graduate Student: Dongdong Fan Supervisor: Shuxiang SongAbstractThis article describes the design of a simple calculator, the design uses Field Programmable Gate Array FPGA based on VHDL hardware description language to design and Altera's Quartus Ⅱ in software for emulation. This system is componented by the key control module, computing, storage and decoding display module of the four parts, the computing part include adder, subtractor, multiplier and divider,Storage part needs three memory to help achieved: internal accumulator (acc), input register (reg) as well as the results of registers (ans). Display part is made up four decoder of 7 sections, respectively to show the number of input. The 8 keys they can by single combined key forms to be completed addition, multiplication, division arithmetic operator and symbol transform,stored data and read seven function of operation within 0 to 9999 numbers.its structure is simple and easy to implement.Key words:FPGA; VHDL; calclute ; design目录摘要 (I)目录 (II)第1章引言 (1)1.1 课程设计的目的与意义 (1)1.2 国外发展现状 (1)第2章FPGA技术及硬件描述语言 (2)2.1 EDA技术及其发展 (2)2.2 FPGA技术 (2)2.3硬件描述语言VHDL (3)第3章系统总体设计 (4)3.1 计算器的计算部分 (4)3.2 计算器的存储部分 (4)3.3 计算器的显示部分 (5)3.4 计算器的输入部分 (6)第4章计算器的VHDL设计 (7)4.1加法器的设计与仿真 (7)4.2减法器的设计与仿真 (8)4.3乘法器的设计与仿真 (9)4.4 除法器的设计与仿真 (10)第5章结束语 (11)参考文献: (11)基于FPGA的计算器设计第1章引言1.1 课程设计的目的与意义在人类学会交易的时候,计算也随之产生,而算盘作为计算最实用的工具存在了几千年。

基于FPGA的计算器设计

基于FPGA的计算器设计引言:随着数字电子技术的不断发展,计算器已经成为人们生活中不可或缺的工具之一、计算器设计是数字电子技术的经典应用之一,也是许多电子工程、计算机科学等专业学科的必修课程。

随着FPGA(Field Programmable Gate Array)技术的快速发展,基于FPGA的计算器设计在教育和工程领域得到了广泛应用。

本文将介绍基于FPGA的计算器的设计思路、硬件架构和关键模块的设计。

一、设计思路:二、硬件架构:1.输入模块:负责接收用户输入的数字和操作符,并将其转化为计算器能够处理的格式。

2.运算模块:负责对输入的数字和操作符进行运算,并生成计算结果。

3.显示模块:负责将计算结果显示在计算器的显示屏上。

4.控制模块:负责控制计算器的各个模块之间的数据流和操作。

三、关键模块的设计:1.输入模块设计:输入模块主要包括键盘和输入转换电路。

键盘用于接收用户输入,输入转换电路负责将键盘输入转化为计算器可以处理的格式(比如将键盘输入的字符转化为二进制数)。

2.运算模块设计:运算模块设计的关键是将不同的操作符映射到不同的算法和电路实现。

比如,加法操作可以通过加法器电路实现,减法操作可以通过加法器和取反器电路实现。

3.显示模块设计:显示模块主要包括显示屏和显示驱动电路。

显示驱动电路负责将计算结果转化为显示屏可以显示的格式(比如将二进制数转化为十进制数)。

4.控制模块设计:控制模块负责协调各个模块的数据流和操作流程。

控制模块可以通过有限状态机(FSM)的方式来实现,根据用户输入的操作符和状态转移条件来决定下一步的操作。

四、实验结果和分析:通过基于FPGA的计算器设计,我们可以实现一个功能强大、灵活易用的计算器。

在实验中,我们可以通过按键输入数字和操作符,计算器会将输入转化为正确的结果并在显示屏上显示出来。

1.灵活性:FPGA芯片的可编程逻辑单元可以根据需求进行更改和扩展,使得计算器可以具有更多的功能和特性。

基于FPGA十进制计时器设计

十进制计时器设计一、实验目的:熟悉Quartus II的开发环境和开发流程,掌握Verilog文本设计流程,并使用Verilog编写一个十进制计时器,在Altera-Modelsim软件上仿真,验证十进制计时器的功能是否正确。

二、实验原理:十进制计数器的CLK为计数的信号,上升沿有效;RST为计数器复位信号;EN为时钟使能信号,当EN处于高电平时,计数器在CLK有效时开始计数;DATA为4位并行的数据输入端;DOUT为4位并行的数据输出端;Load为计数器的数据加载控制信号,当Load处于低电平时,数据输入端DATA 的数据被加载至数据输出端DOUT;Cout为计数器的进位输出。

三、实验步骤:3.1创建项目(1)新建一个文件夹存放EDA项目设计的相关文件。

本项设计的内容为十进制计数器,并且文件名不能使用中文,因此文件夹取名为CNT10,存放的路径为C:\Users\pp\Desktop\CNT10。

其次,项目的顶层文件名设置必须与编辑代码中的顶层模块名一致。

(2)将设计文件加入工程中。

单击File name栏后的控件,将与工程相关的Verilog文件加入工程;若没有编写相关Verilog文件,便单击Next进入下一步。

(3)选择目标芯片。

根据项目开发的硬件平台,选择与之相应的FPGA芯片。

首先在Device Family下拉列表中选择Cyclone系列,在引脚数目pin count中选择144,可快速筛选出符合条件得芯片型号。

(4)EDA工具设置。

此窗口中有三项选择:Design Entry/Synthesis用于选择输入的HDL类型和综合工具;Simulation用于选择仿真工具;Timing Analysis用于选择时序分析工具。

若不作选择,则默认选择Quartus II自含的EDA设计工具。

3.2 Verilog文本输入选择File->New命令,在New窗口中选择Verilog HDL File命令建立Verilog 文本,设置文件名为cnt10.v并存放在C:\Users\pp\Desktop\CNT10文件夹的根目录下。

基于FPGA的多功能计数器的设计_毕业设计

摘要本文介绍了一种以大规模可编程逻辑芯片为设计载体,由顶层到底层设计的多功能数字频率计。

该频率计采用单片机与频率测量技术相结合,大大提高了测量的精度。

本文主要包括该频率计的设计基础和实现方法两部分内容,描述了它的设计平台、工作原理和软硬件实现。

在硬件上,利用Altera 公司的FPGA器件为主控器;在软件上,采用VHDL硬件描述语言编程,极大地减少了硬件资源的占用。

该数字频率计具有频率测量、周期测量、脉宽测量和占空比测量等多种功能。

仿真与分析结果表明,该数字频率计性能优异,软件设计语言灵活,硬件简单,速度快。

关键词 FPGA 等精度频率计 VHDLAbstractThis article introduced one kind as designs the carrier take the large-scale programmable logic chip, the multi-purpose digital frequency meters which designs from the top layer to the first floor. This frequency meter uses the monolithic integrated circuit and the frequency measurement technology unifies, increased the survey precision greatly. This article mainly includes this frequency meter's design basis and realizes the method two partial contents, described its design platform, the principle of work and the software and hardware realizes. On the hardware, uses Altera Corporation's FPGA componentis the master controller; On the software, uses the VHDL hardware description language programming, reduced hardware source occupancy enormously. This digital frequency meter has the frequency measurement, the cyclical survey, the pulse width survey and the dutyfactor survey and so on many kinds of functions. The simulation and the analysis result indicated that this digital frequency meter performance is outstanding, the software design language is flexible, the hardware is simple, the speed is quick.Keywords FPGA Equal Precision Measurement Frequency meter VHDL目录第一章概述 (1)1.1多功能计数器现状 (1)1.2频率测量方法简介 (2)第二章软件开发平台VHDL简介 (5)2.1VHDL的发展 (5)2.2VHDL的特点 (5)2.3VHDL语言结构 (7)2.3.1 实体(ENTITY) (7)2.3.2 结构体(ARCHITECTURE) (8)2.4VHDL软件设计简介 (10)第三章硬件开发平台现场可编程门阵列(FPGA)简介 (12)3.1可编程逻辑器件 (12)3.2现场可编程门阵列(FPGA) (13)3.2.1 FPGA的器件结构与工作原理 (14)3.2.2 基于EDA平台的FPGA开发流程 (18)第四章多功能计数器的理论基础和总体设计方案 (21)4.1常用频率测量方法及其误差分析 (21)4.1.1 直接测频法 (21)4.1.2 测周法原理 (23)4.1.3 等精度测频原理 (25)4.2脉冲宽度和占空比测量原理 (28)4.3总体设计 (29)第五章多功能计数器的软件设计和硬件设计 (32)5.1软件设计 (32)5.1.1 测频专用模块工作功能描述及VHDL程序 (33)5.1.2 脉冲宽度和占空比测量模块 (37)5.1.3 GATE (41)5.1.4 测频/测周期实现 (42)5.2硬件设计 (43)5.2.1 程控放大电路 (44)5.2.2 过零比较电路 (45)5.2.3 测频主系统实现 (46)总结 (48)谢辞 (49)参考文献 (50)第一章概述在信息技术高速发展的今天,电子系统数字化已成为有目共睹的趋势。

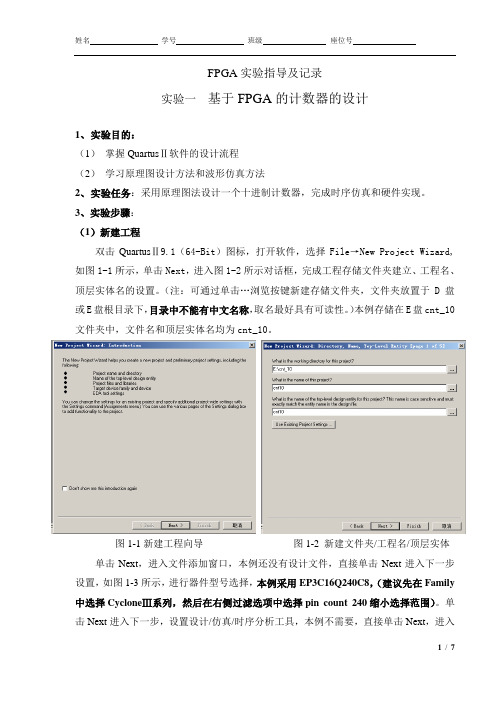

EDA实验指导 基于FPGA的计数器设计

FPGA实验指导及记录实验一基于FPGA的计数器的设计1、实验目的:(1)掌握QuartusⅡ软件的设计流程(2)学习原理图设计方法和波形仿真方法2、实验任务:采用原理图法设计一个十进制计数器,完成时序仿真和硬件实现。

3、实验步骤:(1)新建工程双击QuartusⅡ9.1(64-Bit)图标,打开软件,选择File→New Project Wizard,如图1-1所示,单击Next,进入图1-2所示对话框,完成工程存储文件夹建立、工程名、顶层实体名的设置。

(注:可通过单击…浏览按键新建存储文件夹,文件夹放置于D盘或E盘根目录下,目录中不能有中文名称,取名最好具有可读性。

)本例存储在E盘cnt_10文件夹中,文件名和顶层实体名均为cnt_10。

图1-1新建工程向导图1-2 新建文件夹/工程名/顶层实体单击Next,进入文件添加窗口,本例还没有设计文件,直接单击Next进入下一步设置,如图1-3所示,进行器件型号选择,本例采用EP3C16Q240C8,(建议先在Family 中选择CycloneⅢ系列,然后在右侧过滤选项中选择pin count 240缩小选择范围)。

单击Next进入下一步,设置设计/仿真/时序分析工具,本例不需要,直接单击Next,进入下一步。

观察设置细节,单击Finish完成设计。

图1-3 器件型号选择图1-4 完成工程设置(2)新建设计文件选择File→New,打开如图1-5所示对话框,选择Block Diagrom原理图设计文件,打开原理图设计文件。

双击空白处,打开symbol对话框,选择74390,单击OK后,拖动鼠标可放置于原理图任意空白处。

进一步添加输入端input/输出端output,添加完成后如图1-8所示。

图1-5 新建原理图文件图1-6 选择74390图1-7添加输入/输出端 图1-8 放置所需元器件将鼠标放置于器件端口处,鼠标即会变为“+”字型,此时可拖动鼠标进行连线。

基于FPGA的计数器设计说明

EDA课程设计项目名称基于FPGA的计数器的设计专业班级通信102班学生青瓜指导教师2013年 5 月28 日摘要本课程设计要完成一个 1 位十进制计数器的设计。

计数器是大规模集成电路中运用最广泛的结构之一。

在模拟与数字集成电路设计当中, 灵活地选择与使用计数器可以实现很多复杂的功能, 可以大量减少电路设计的复杂度和工作量。

讨论了一种可预置加减计数器的设计, 运用Ver ilog H DL 语言设计出了一种同步的可预置加减计数器, 该计数器可以根据控制信号分别实现加法计数和减法计数, 从给定的预置位开始计数, 并给出详细的 VerilogHDL 源代码。

最后, 设计出了激励代码对其进行仿真验证, 实验结果证明该设计符合功能要求, 可以实现预定的功能。

关键词:计数器;VerilogHDL;QuartusⅡ;FPGA;AbstractThis course is designed to complete a one decimal counter design. The counter is LSI structure in one of the most widely used. In the analog and digital IC designs, the flexibility to select the counter can achieve a lot with the use of complex functions, can significantly reduce the complexity of circuit design and workload. Discusses a presettable down counter design, using Ver ilog H DL language designed a synchronous presettable down counter, the counter can be implemented according to the control signals are counted Addition and subtraction counting from a given the preset starts counting, and gives detailed VerilogHDL source code. Finally, the design of the incentive code its simulation, experimental results show that the design meets the functional requirements, you can achieve the intended function.Key words:Decimal counter; VerilogHDL; Quartus Ⅱ; FPGA;目录摘要IAbstractII第1章绪论11.1计数器的种类11.2计数器的发展1第2章设计环境22.1 Quartus II22.1.1 软件简介22.1.2 功能22.2 Verilog HDL硬件描述语言42.2.1 语言简介42.2.2 主要能力42.2.3 语言用途62.2.4 Verilog HDL的发展历史62.2.5 主要应用72.3 Electronic Design Automation8第3章设计思路103.1输入模块103.2 寄存器模块103.3 输出模块113.4 计数模块11第4章程序设计124.1 主程序124.3 always语句134.4 if-else语句13第5章波形仿真13结论14参考文献15附录116致16第1章绪论1.1计数器的种类1、如果按照计数器中的触发器是否同时翻转分类,可将计数器分为同步计数器和异步计数器两种。

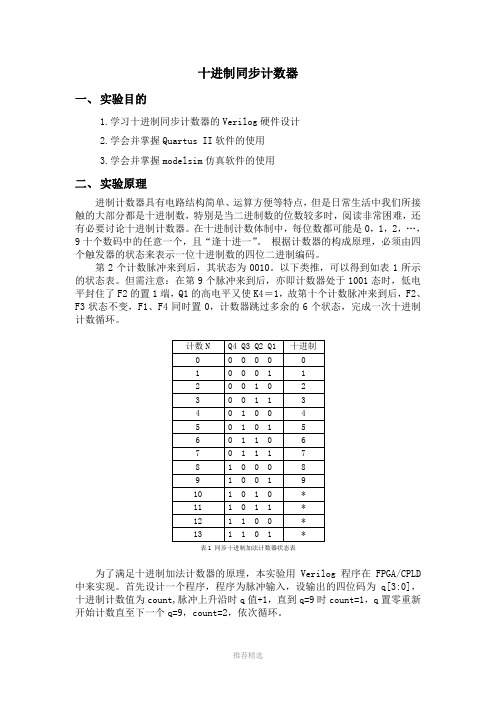

基于FPGA十进制同步计数器

十进制同步计数器一、实验目的1.学习十进制同步计数器的Verilog硬件设计2.学会并掌握Quartus II软件的使用3.学会并掌握modelsim仿真软件的使用二、实验原理进制计数器具有电路结构简单、运算方便等特点,但是日常生活中我们所接触的大部分都是十进制数,特别是当二进制数的位数较多时,阅读非常困难,还有必要讨论十进制计数器。

在十进制计数体制中,每位数都可能是0,1,2,…,9十个数码中的任意一个,且“逢十进一”。

根据计数器的构成原理,必须由四个触发器的状态来表示一位十进制数的四位二进制编码。

第2个计数脉冲来到后,其状态为0010。

以下类推,可以得到如表1所示的状态表。

但需注意:在第9个脉冲来到后,亦即计数器处于1001态时,低电平封住了F2的置1端,Q1的高电平又使K4=1,故第十个计数脉冲来到后,F2、F3状态不变,F1、F4同时置0,计数器跳过多余的6个状态,完成一次十进制计数循环。

表1 同步十进制加法计数器状态表为了满足十进制加法计数器的原理,本实验用Verilog程序在FPGA/CPLD 中来实现。

首先设计一个程序,程序为脉冲输入,设输出的四位码为q[3:0],十进制计数值为count,脉冲上升沿时q值+1,直到q=9时count=1,q置零重新开始计数直至下一个q=9,count=2,依次循环。

三、实验任务1.根据实验目的编写verilog程序2.将设计好的Verilog译码器程序在Quartus II上进行编译3.对程序进行适配、仿真,给出其所有信号的时序仿真波形图(注意仿真波形输入激励信号的设置)。

本实验要求自己设置clr值,理解清零的意义四、实验步骤:1.建立工作库文件和编辑设计文文件任何一项设计都是一项Project(工程),而把一个工程下的所有文件放在一个文件夹内是一个非常好的习惯,以便于我们整理,利用和提取不同工程下的文件,而此文件夹将被EDA软件默认为Work Library(工作库),所以第一步先根据自己的习惯,建立个新的文件夹。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一级建造师工程经济模拟题100道得分规则:备选答案为ABCD四项的为单项选择题,每题1分,每题的备选项中,只有1个最符合题意:备选答案为ABCDE五项的为多项选择题,每题2分,每题的备选项中,有2个或2个以上符合题意,至少有1个错项。

错选,本题不得分;少选,所选的每个选项得0.5分。

1、在工程经济学中,作为衡量资金时间价值的绝对尺度,利息是指( )。

P2A.占用资金所付出的代价B.放弃使用资金所得的补偿C.考虑通货膨胀所得的补偿D.资金的一种机会成本E.投资者的一种收益2、利率是各国调整国民经济的杠杆之一。

其高低首先取决于( )。

P2A.金融市场借贷资本的供求状况B.借贷资本的期限C.通货膨胀的波动影响D.社会平均利润率的高低3、下列关于利息和利率的说法中,正确的有( )。

P2-3A.利息是占用资金所付出的代价B.利息能够促进企业加强经济核算C.利率的高低取决于平均投资利润率的高低D.利息是衡量资金时间价值的绝对尺度E.利息和利率是以信用方式动员和筹集资金的动力4、在工程经济分析中,通常采用( )计算资金的时间价值。

P5A、连续复利B、间断复利C、连续单利D、瞬时单利5、关于现金流量图绘制规则的说法,正确的有( )。

P5A.横轴为时间轴,整个横轴表示经济系统寿命期B.横轴的起点表示时间序列第一期期末C.横轴上每一间隔代表一个计息周期D.与横轴相连的垂直箭线代表现金流量E.垂直箭线的长短应体现各时点现金流量的大小6、要正确绘制现金流量图,必须把握好现金流量的要素主要包括( )。

P6A.现金流量的时间点B.现金流量的大小C.现金流量的运动状态D.现金流量的方向E.现金流量的作用点7、现金流量的分布情况,说明( )。

P8A.从收益方面来看,获得时间越早,数额越多,其现值越大B.从收益方面来看,获得时间越早,数额越少,其现值越大C.建设项目早投产,早获收益,多获收益,才能达到最佳经济效益D.在投资额一定的情况下,投资支出的时间越晚,数额越少,现值越小E.在投资额一定的情况下,投资支出的时间越晚,数额越少,现值越大8、影响资金等值的因素有( )。

P11A.资金数额的多少B.资金发生的时间长短C.折现率D.利息E.国家政策9、下列关于名义利率和有效利率的说法中,正确的有( )。

P12-13A.名义利率是计息周期利率与一个利率周期内计息周期数的乘积B.有效利率包括计息周期有效利率和利率周期有效利率C.当计息周期与利率周期相同时,名义利率等于有效利率D.当计息周期小于利率周期时,名义利率大于有效利率E.当名义利率一定时,有效利率随计息周期变化而变化10、对于经营性建设项目,财务分析应主要分析项目的( )。

P15A.盈利能力B.偿债能力C.财务生存能力D.经济费用效益E.投资效果分析11、在经济效果评价方法中,对同一个技术方案必须同时进行( )。

P15A.融资前分析和融资后分析B.定量分析和定性分析C.动态分析和静态分析D.确定性评价和不确定性评价12、在经济效果评价方法中,( )是指对无法精确度量的重要因素实行的估量分析方法。

P17A.定量分析B.动态分析C.定性分析D.静态分析13、下列财务评价指标中,属于分析项目偿债能力的是( )。

P19A.投资回收期B.总投资收益率C.项目资本金净利润率D.利息备付率14、在下列投资方案评价指标中,不考虑资金时间价值的指标是( )。

P19A.利息备付率和内部收益率B.资金利润率和净现值率C.利息备付率和借款偿还期D.净现值和内部收益率15、在下列投资方案经济效果评价指标中,属于投资方案盈利能力动态评价指标的是( )。

P19 A.内部收益率和投资收益率B.净现值和利息备付率C.净现值和内部收益率D.净现值和总投资利润率16、在评价投资方案经济效果时,与静态评价方法相比,动态评价方法的最大特点是( )。

P19 A.考虑了资金的时间价值B.适用于投资方案的粗略评价C.适用于逐年收益不同的投资方案D.反映了短期投资效果17、总投资收益率指标中的收益是指项目建成后( )。

P19A.正常生产年份的年税前利润或运营期年平均税前利润B.正常生产年份的年税后利润或运营期年平均税后利润C.正常生产年份的年息税前利润或运营期年平均息税前利润D.投产期和达产期的盈利总和18、在投资方案评价中,投资回收期只能作为辅助评价指标的主要原因是( )。

P23A.只考虑投资回收前的效果,不能准确反映投资方案在整个计算期内的经济效果B.忽视资金具有时间价值的重要性,在回收期内未能考虑投资收益的时间点C.只考虑投资回收的时间点,不能系统反映投资回收之前的现金流量D.基准投资回收期的确定比较困难,从而使方案选择的评价准则不可靠19、净现值作为评价投资方案经济效果的指标,其优点是( )。

P24A.全面考虑了项目在整个计算期内的经济状况B.能够直接说明项目在整个运营期内各年的经营成果C.能够明确反映项目投资中单位投资的使用效率D.不需要确定基准收益率而直接进行互斥方案的比选20、若已知某技术方案各年的净现金流量,则该技术方案的财务净现值就完全取决于所选用的( )。

P24A.生产能力利用率B.基准收益率C.折现率D.投资收益率21、采用内部收益率指标评价投资方案经济效果的优越性在于( )。

P26A.能够反映项目在整个计算期内的经济状况B.能够直接衡量项目未回收投资的收益率C.能够直接反映项目运营期各年的利润率D.只需确定基准收益率的大致范围E.不需要与投资方案相关的大量数据22、净现值和内部收益率作为评价投资方案经济效果的主要指标,二者的共同特点有( )。

P26 A.均考虑了项目在整个计算期内的经济状况B.均取决于投资过程的现金流量而不受外部参数影响C.均可用于独立方案的评价,并且结论是一致的D.均能反映投资过程的收益程度E.均能直接反映项目在运营期间各年的经营成果23、企业或行业投资者以动态的观点所确定的、可接受的技术方案最低标准的收益水平指的是( )。

P26A.财务内部收益率B.基准收益率C.增量投资收益率D.净资产收益率24、对非国家投资项目而言,投资者在确定基准收益率时应以( )为基础。

P26A.资金限制和投资风险B.资金成本和目标利润C.目标利润和投资风险D.资金成本和通货膨胀25、为了限制对风险大、盈利低的项目进行投资,在进行项目经济评价时,可以采取提高( )的方法。

P27A.基准收益率B.投资收益率C.投资报酬率D.内部收益事26、建设工程项目的现金流量按当年价格预测时,确定基准收益率需要考虑的因素包括( )。

P28A.投资周期B.通货膨胀C.投资风险D.经营规模E.机会成本27、按基准年不变价格预测建设工程项目的现金流量,确定基准收益率需要考虑的因素有( )。

P28A.资金成本B.经营成本C.机会成本D.通货膨胀E.投资风险28、根据现行财税制度,偿还贷款的资金来源主要有( )。

P28A.用于归还借款的利润B.公益金、盈余公积金的提取C.固定资产折旧D.无形资产及其他资产摊销费E.其他还款资金29、分期建成投产的技术方案,应按各期投产时间分别停止借款费用的资本化,此后发生的借款利息应计入( )。

P29A.总成本费用B.管理费用C.期间费用D.财务费用30、投资项目借款偿还期是指用可作为还款的收益偿还( )所需要的时间。

P29A.项目投资借款本金和利息B.项目投资借款本金和建设期利息C.项目投资借款和流动资金借款本金D.项目流动资金借款本金和利息31、偿债备付率是指项目在借款偿还期内各年( )的比值。

P30A.可用于还本付息的资金与当期应还本付息金额B.可用于还款的利润与当期应还本付息金额C.可用于还本付息的资金与全部应还本付息金额D.可用于还款的利润与全部应还本付息金额32、利息备付率和偿债备付率是评价投资项目偿债能力的重要指标,对于正常经营的项目,利息备付率和偿债备付率应( )。

P30A.均大于1B.分别大于1和2C.均大于2D.分别大于2和133、产生不确定性的主要原因有( )。

P32A.预测方法的局限,预测的假设不准确B.技术进步C.所依据的基本数据的不足或者统计偏差D.无法以定量来表示的定性因素的影响E.可变因素对经济评价指标影响34、投资项目财务评价中的不确定性分析有( )。

P33A.盈亏平衡分析B.增长率分析C.敏感性分析D.发展速度分析E.均值分析35、下列项目中,在盈亏平衡分析中属于变动成本的是( )。

P33A.折旧费B.长期借款利息C.短期借款利息D.动力费E.生产工人工资36、盈亏平衡分析分线性盈亏平衡分析和非线性盈亏平衡分析。

其中,线性盈亏平衡分析的前提条件之一是( )。

P34A.只生产单一产品,且生产量等于销售量B.单位可变成本随生产量的增加成比例降低C.生产量与销售量之间成线性比例关系D.销售收入是销售量的线性函数37、在项目盈亏平衡点的多种表达形式中,应用最为广泛的是以( )表示的盈亏平衡点。

P35 A.产量和单价B.产量和生产能力利用率C.可变成本和固定成本D.单价和生产能力利用率38、以生产能力利用率表示的项目盈亏平衡点越低,表明项目建成投产后的( )越小。

P37A.盈利可能性B.适应市场能力C.抗风险能力D.盈亏平衡总成本39、下列关于单因素敏感性分析的步骤排序正确的是( )。

P38A.确定分析指标、选择需要分析的不确定性因素、分析每个不确定性指标的波动程度及其对分析指标可能带来的增减变化情况、确定敏感性因素、方案选择B.确定分析指标、分析每个不确定性印度的波动程度及其对分析指标可能带来的增减变化情况、方案选择、、选择需要分析的不确定性因素、确定敏感性因素、C.确定分析指标、方案选择、选择需要分析的不确定性因素、分析每个不确定性印度的波动程度及其对分析指标可能带来的增减变化情况、确定敏感性因素、D.确定分析指标、选择需要分析的不确定性因素、分析每个不确定性印度的波动程度及其对分析指标可能带来的增减变化情况、方案选择、确定敏感性因素40、在投资项目经济评价中进行敏感性分析时,首先应确定分析指标。

如果要分析产品价格波动对投资方案超额净收益的影响,可选用的分析指标是( )。

P38A.投资回收期B.净现值C.内部收益率D.借款偿还期41、在投资项目经济评价中进行敏感性分析时,如果要分析投资大小对方案资金回收能力的影响,可选用的分析指标是( )。

P38A.净现值B.投资收益率C.内部收益率D.借款偿还期42、敏感性分析的目的在于寻求敏感因素,这可以通过计算( )来判断。

P39A.超额净收益和财务净现值B.临界点和不确定性因素C.财务净现值和敏感性系数D.敏感度系数和临界点43、根据对项目不同方案的敏感性分析,投资者应选择( )的方案实施。