基于FPGA的数字相敏检波算法实现

FPGA实现数字相敏检波(DPSD)

FPGA实现数字相敏检波(DPSD)

原理是从⽹上论⽂找到的,⼤家⾃⼰找⼀下。

相敏检波利⽤互相关原理,能够⼗分有效地从噪声中提取出与参考信号具有相关性的待测信号的幅度和相位信息,同时忽略不相关的背景噪声的⼲扰。

⼀、数字相敏检波原理

待测信号:x(t)为待测信号s(t)与系统噪声n(t)的叠加,表达式为: x(t) = s(t) + n(t) = A cos(wt +θ)+n(t)

r(t)为与待测信号s(t)同频率的参考信号,在r(t)与s(t)的相位关系不明确的情况下,欲测得s(t)的幅度A与相位差Θ,需要采⽤两组正交的参考信号r1(t)和r2(t)同时完成相敏检波流程。

假设参考信号幅值为1,相位为0,既:

r1(t)=cos(wt), r2(t)=sin(wt),

经过运算:

若认为噪声为随机噪声,与参考信号⽆关,则要积分时间⾜够长,n(t)的影响可以被消除得

显然,结合R1和R2即可求得待测信号的幅度A与相位θ。

⼆、DPSD算法实现

DPSD是上述模拟相敏检波的数字实现⽅式,⽤数学⽅式⾯熟互相关算法的表达式为:

从公式中,可以看出,DPSD算法需要对待测信号进⾏AD转换后再完成两者的乘法和累加操作,在这个过程中,诸多因素都可能对DPSD算法的精度照成影响。

算法输出信噪⽐与测量时间成正⽐,且在满⾜奈奎斯特采样率的前提下,采⽤频率对信噪⽐⽆直接影响。

但若考虑到电路中带通滤波器性能和采样率不⾜可能带来频率混叠,对⾼采样率对抑制ADC量化误差的积极作⽤,适当提⾼采样率对DPSD算法精度多少有些好处。

FPGA逻辑功能框图如下:。

基于FPGA的高灵敏度数字磁通门设计

1 T 2L B DfV S 3 1( s ) 1 S

BI 4R F O A S ] T E C M( V s

图5 A DC 电 路

臣

E H

图 3 功率放大电路

2 2 滤波 放大 电路 . 由于磁通 门激励信号频率为 1. 2 Hz因此 为了提取感 5 6 5k , 应线 圈端 的二次谐 波 分量 , 采用 滤波 器设 计 软件 ft oui ie slt n lr o

23 转 换 电路 .

考虑到磁通门感应信号频率较 高 , 而且 F G P A输入输 出 口

充足 , 为了便于 电路驱 动 , 选取 1 并行输 出高精 度 A 2位 D芯片

A 92 D 24搭建 A D转换 电路 j 电路 图如图 5所示 , , 检测 信号频

励信号 。

4 实 验及 结 果 分 析

Ul

CL K

BI l Tl BI O Tl BI T9 BI c 8 I BI T7 BI T6 BI T5 BI T3 BI T2 Br 1 r OTR AD 2 4 9 2

DR VDD

A VDD AV S S Ⅵ NB Ⅵ NA CM L C AP T C PB A V REF S ENS E A VS S AVDD

图 4 带通 滤 波 电路

正弦波 幅度 的数字量信号 , 以驱动 I A转换 电路 。在实际应用 ) /

当 中经 过 对 比实 验 , 现 方 波 驱 动 效 果 最 佳 , 此 将 D S模 块 发 因 D 进 行 了相 关 简 化 , 接 采 用 系 统 时 钟 分 频 得 到 1.2 H 的 激 直 5 6 5k z

压信号 , 该直流信号与外界磁场 大小线性 对应 。由于图 1所示 电路 当中, 相敏检波 电路 中凋相 电路很难 保证进 入乘 法器 的 2 路信号严格 同相 , 中设计使用 F G 文 P A代替 图 1中虚线框 部分 ,

测井仪器中数字相敏检波算法的设计与实现

1 π ( fs + fr ) t +θ es er co s 2 2 1 π ( fn - fr ) t +φ en er co s 2 2 1 π ( fn + fr ) t +φ en er co s 2 2

2 数字相敏检波算法

在模拟相敏检波中 , 乘法和检波都是通过电路 来实现的 , 不仅降低了仪器的精度和分辨率 , 而且 电路本身也会引入一定的噪声 。本设计中数字相敏 检波利用 DSP 采用软件的方式实现对待测信号的 幅值计算 , 既简化了电路设计 , 又减少了噪声引 入 。数字相敏检波的基本原理是对待测信号进行若 干周期采样 , 并将采样值与存储于数组中相应参考 值进行乘累加并取平均 , 求出其同相分量与正交分 量 , 然后计算出其幅值与相位 。其数学描述如下 : 2 nfsπ 2 nfnπ x ( n ) = es co s +θ + en co s +φ

[2] 廖谟圣 1 海洋油气工业的发展与新一代的移动式钻

采平台 [ J ] 1中国海洋平台 , 2002, 17 ( 1 ) : 1 - 31

[3] 朱 江 1 海洋钻井设备综述 [ J ] 1 中国海上油气 (工程 ) , 2000, 12 (6) : 44 - 461

此套海洋 3 000 m 多功能钻修机用于我国第 1 艘海洋油气多功能作业船 , 能为多个海洋钻井作业 平台提供优质高效服务 。 随着海洋油气资源开发力度的进一步加大 , 对 海洋修井及其他作业的需求会越来越多 , 对具有快 [3] 速拆卸 、安装的钻修井设备需求会更加旺 盛 。 L IFTBOAT钻修机在我国石油钻采装备研发史上是 一项具有里程碑意义的新产品 , 它的成功研发为我 国海洋石油开发提供了有力支持 。

基于FPGA的数字相敏检波算法实现

基于FPGA的数字相敏检波算法实现

梁世盛;乔凤斌;张燕

【期刊名称】《自动化仪表》

【年(卷),期】2013(034)011

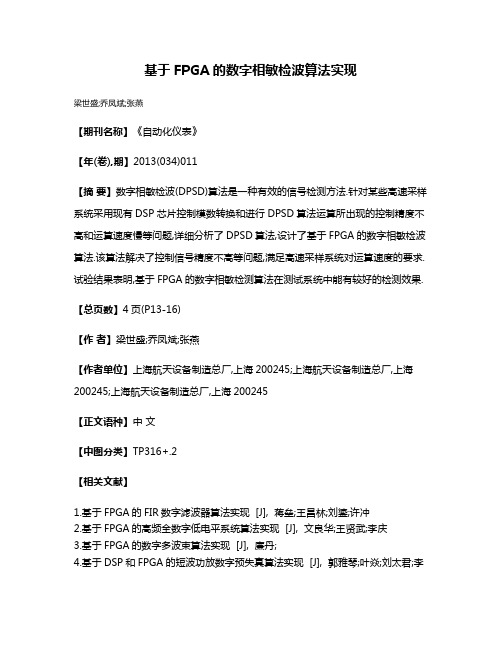

【摘要】数字相敏检波(DPSD)算法是一种有效的信号检测方法.针对某些高速采样系统采用现有DSP芯片控制模数转换和进行DPSD算法运算所出现的控制精度不高和运算速度慢等问题,详细分析了DPSD算法,设计了基于FPGA的数字相敏检波算法.该算法解决了控制信号精度不高等问题,满足高速采样系统对运算速度的要求.试验结果表明,基于FPGA的数字相敏检测算法在测试系统中能有较好的检测效果.【总页数】4页(P13-16)

【作者】梁世盛;乔凤斌;张燕

【作者单位】上海航天设备制造总厂,上海200245;上海航天设备制造总厂,上海200245;上海航天设备制造总厂,上海200245

【正文语种】中文

【中图分类】TP316+.2

【相关文献】

1.基于FPGA的FIR数字滤波器算法实现 [J], 蒋垒;王昌林;刘鎏;许冲

2.基于FPGA的高频全数字低电平系统算法实现 [J], 文良华;王贤武;李庆

3.基于FPGA的数字多波束算法实现 [J], 廉丹;

4.基于DSP和FPGA的短波功放数字预失真算法实现 [J], 郭雅琴;叶焱;刘太君;李

先印;程琪榕

5.基于SoC FPGA的数字荧光算法实现 [J], 张晋;严建桥;黄光明

因版权原因,仅展示原文概要,查看原文内容请购买。

基于FPGA的多通道同步数字锁相放大器

基于FPGA的多通道同步数字锁相放大器王晓娜;陈珂;陶鹏程;张莹莹【摘要】针对多通道弱信号检测的需求,提出了基于FPGA的多通道数字锁相同步检测技术方案.锁相放大器的相敏检波和低通滤波功能采用数字互相关算法实现.通过理论分析,优化了系统设计参数,减少了离散化效应和量化误差对锁相高次谐波抑制能力和动态储备的影响,并用仿真程序对互相关算法和选定的参数进行了验证.所研制的基于FPGA的四通道同步数字锁相放大器具有体积小和成本低等特点,其动态储备达100 dB,极限检测灵敏度达到10 nV,输入噪声密度为7.4 nV/Hz,通道隔离度大于80 dB.【期刊名称】《大学物理实验》【年(卷),期】2019(032)003【总页数】5页(P5-9)【关键词】数字锁相放大器;多通道检测;同步检测;互相关;FPGA【作者】王晓娜;陈珂;陶鹏程;张莹莹【作者单位】大连理工大学物理学院,辽宁大连 116024;大连理工大学光电工程与仪器科学学院,辽宁大连 116024;大连理工大学光电工程与仪器科学学院,辽宁大连 116024;大连理工大学物理学院,辽宁大连 116024【正文语种】中文【中图分类】TP216+.1锁相放大器技术从诞生至今,经历了不间断的发展,特别是DSP(digital signal processor)和FPGA(field programmable gate array)的出现,数字化逐渐成为锁相放大器的主要发展方向 [1-2]。

此外,数字化硬件平台成本较低,易于被模块化并方便地移植到其他系统中,且在不改变硬件平台的情况下,也可以利用升级软件算法的方法来提升系统整体的性能,因此,近年来数字锁相放大器获得了大规模的应用[3]。

FPGA技术近年来发展迅速,在对信号进行并行处理等方面与DSP和单片机等处理器相比,具有无可比拟的优势,因此,FPGA技术在多通道信号处理领域应用广泛[4-6]。

在相敏检波方面,FPGA技术对信号处理速度较快并且可以对兆赫兹频率段的信号进行检测。

基于FPGA的低频数字相位测量仪的设计

1引言关于低频数字相位测量系统的设计与实现方法,提出了以单片机最小系统和复杂可编程逻辑芯片为核心的电路设计模型。

相位的数字测量方法基本分为硬件电路测量与A/D采样后利用软件计算两种。

硬件法测量由于电路结构比较复杂,易受外界干扰影响以及准确度较差的缺点,限制了其作用进一步发挥。

近年来,随着计算机硬件及其外围设备的日益发展,以数字信号处理为核心的软件法测量技术在相位差的测量中得到了越来越多关注,并且得到了较快发展。

同频率正弦信号间的相位差测量在电工技术、工业自动化、智能控制及通讯、电子等许多领域都有广泛的应用,如电工领域中的电机功角测试,介质材料的损耗角的确定等。

因此相位差测量有着广泛的实用价值。

本系统由数据采集电路、数据运算控制电路和数据显示电路三大部份构成,其系统功能主要是进行相位差测量及频率测量。

该系统采用单片机和FPGA作为低频数字相位测量仪的核心部分。

采用单片机和FPGA作为低频数字相位测量仪的核心部分,由数据采集电路、数据运算控制电路基于FPGA的低频数字相位测量仪的设计康占义 张家口教育学院宣化分校职业教育部图1 系统原理框图图3 采用施密特触发器的整形电路和数据显示电路三大部分构成,其系统功能主要是进行相位差测量及频率测量。

采用VHDL语言实现FPGA的功能。

2系统设计方案本系统分为三大基本组成部分:数据采集电路、数据运算控制电路和数据显示电路。

考虑到FPGA具有集成度高,I/O资源丰富,稳定可靠,可现场在线编程等优点,而单片机具有很好的人机接口和运算控制功能,本系统拟用FPGA和单片机相结合,构成整个系统的测控主体。

系统原理框图如图1。

2.1 信号整形电路的设计最简单的信号整形电路就是一个单门限电压比较器(如图2所示),当输入信号每通过一次零时触发器的输出就要产生一次突然的变化。

当输入正弦波时,每过一次零,比较器的输出端将产生一次电压跳变,它的正负向幅度均受到供电电源的限制,因此输出电压波形是具有正负极性的方波,这样就完成了电压波形的整形工作。

基于CORDIC算法的数字鉴相器的FPGA实现

时 ,不 易在 硬件 上实现 ,所 以鉴 别器算 法实 现也 是研究 的热 点 。C O R D I C 算法 功 能较 多 ,可 以同时 实现 多种 函数 ,它 在

AC ADE MI C RE S E AR C H 学 术研究

基 ̄ ' C O R D I C算法 的数 字鉴 相器 的F P G A实现

◆ 王珂南 杜 建 平

摘 要 :本 文 提 出 了 一 种 实现 GP s 载 波 跟 踪 环 鉴 相 器 的 方 法 ,该 方 法采 用 改 进 后 的 CORDI C算 法来 实现 用 于鉴相 的a r c t a n 函数 。 同时 ,给 出了 ̄ &  ̄ CORDI C算 法的迭代 算 法 流 图和部 分 实现 代码 。这种 算法 结构 简单 ,只需要采 用加 法和移位 操作 即可 , 因此 非常 易于

硬 件 电路 的 实现 上 只用 到 了移位 和 累加 ,大 大 节约 了F F GA 的资源 ,使 得这 些算法 在硬 件上 可 以得 到较 好地 实现 ,从 而 可 以满 足设 计 者 的要求 。但 是现 有 的C OR DI C 算 法计算 反 正 切 时输 入输 出范 围较小 ,因此本 文将 原有 C OR DI C 算 法做 部 分改进 ,扩大 了鉴相 器输入输 出 的范 围 。

坐标 旋转计 算机) 是一种 用于计算 一些 常用 的基本运算 函数 和 算术 操作 的循 环迭 代算 法 。其基 本思想 是 用一 系列与 运算 基

基于FPGA的高频数字鉴相技术

电子技术• Electronic Technology86 •电子技术与软件工程 Electronic Technology & Software Engineering【关键词】带通采样 高频数字鉴相 多相低通滤波1 引言宽带探测系统可以很好的利用大带宽信号提供的更加丰富的目标信息和高分辨率,一般用与SAR/ISAR 成像等应用,是实现成像雷达的关键技术。

但是由于大带宽的影响,整个接收通道的设计十分困难,采用射频直采可有效简化接收通道的设计难度,灵活性更大,是实现数字接收机的关键技术。

同时鉴相质量直接决定了后续算法的结果质量,对系统指标十分关键。

基于FPGA 的高频数字鉴相技术文/张绘 王艳涛本文提出了一种基于FPGA 的通用高频数字鉴相技术,采用数字信号处理的方法进行鉴相,提高处理精度。

该技术将射频信号直接经过AD 采样后得到高频的数字信号,然后通过FPGA 进行高频数字鉴相得到用于后端信号处理的I/Q 信号,相对于传统的鉴相方法,减轻了前端模拟处理对性能的影响,并且更符合软件无线电技术的发展趋势。

2 高频数字鉴相如图1所示,高频数字鉴相的处理流程如下:将AD 采样得到的数字信号传送到FPGA 中,在此过程中,对数据进行了扩位降速处理;通过Matlab 设计生成用于在FPGA 中实现滤波器的系数进行滤波,由于数据量过大,进行带通滤波时采用了多路并行处理的方法;将Matlab 中设计的正余弦信号存入到FPGA 的块RAM 中,运用读取出的本振信号与带通滤波后的信号相乘实现变频;在多相低通滤波的过程中选择对固定的相位进行滤波处理来达到数据降速的目的,滤波之后的结果就是I/Q 路数字信号。

2.1 高频AD采样根据带通采样得知采样频率应满足以下两个关系式F s ≥2B (1) (2F c +B)/(m+1) ≤Fs ≤(2F c -B)/m (2)其中B 为被采样带通信号的带宽,本文中为130MHz ;F c 为被采样带通信号的中心频率,本文中为1.29GHz ;m 为满足(公式1)和(公式2)的任意正整数;F s 为采样频率,根据(公式1)和(公式2),本文中采用960MHz 。

基于FPGA的数字式相位测量仪的设计与制作

基于FPGA的数字式相位测量仪的设计与制作基于FPGA的数字式相位测量仪的设计与制作摘要:本设计给出了基于FPGA核心的数字式相位测量的基本原理与实现方案,实现的是对两列信号的相位差的精确测量并数字显示测量结果。

该系统利用可编程逻辑器件为主系统芯片,用VHDL对其进行设计开发,系统由相位测量仪、数字式移相信号发生器和移相网络三个模块构成,整个装置具有原理简单,测量精度高,测量结果显示直观的特点。

本次设计在EDA软件开发平台MAX+PLUSⅡ上利用硬件描述语言VHDL进行设计编程。

关键词:FPGA/CPLD、VHDL、测相仪FPGA-based digital phase-measuring instrument design and production Abstract: The design is based on the FPGA core of the digital phase measurement and realization of the basic principles of the programme, the realization of the two signals in the phase of precision measurement and statistics show that the measurement results. The system of programmable logic devices based system chips, with their VHDL design and development, the system by the phase-measuring instrument, the digital shift believe that the phase-shifting, generator and a network of three modules, the device has a simple theory, measurement High-precision measurement results show that the visual characteristics. The design of the EDA software development platform MAX + PLUS Ⅱon the use of hardware description language VHDL design programming.Key words: FPGA / CPLD;VHDL;measurement of the instrument第1章绪论1.1 EDA技术概述1.1.1 引言20世纪末,电子技术获得飞速发展,在其推动下,现代电子产品几乎渗透了社会的各个领域,有力推动社会生产力的发展和社会信息化程度的提高,同时也使现代电子产品性能进一步提高,产品更新换代的节奏也越来越快。

基于fpga的数字相敏检波算法实现

基于fpga的数字相敏检波算法实现fpga(Field Programmable Gate Array)是一种非易失可配置逻辑器件,成为当今技术发展的关键产品之一。

近年来,由于其高速处理能力、低功耗、低成本等特点,fpga在数字信号处理领域得到了越来越多的应用。

一种常见的应用就是基于fpga的数字相敏检波算法实现。

在基于fpga的数字相敏检波算法中,首先要实现的是数字滤波器的设计。

这里的滤波器必须能够满足信号处理的时序要求,保证信号有较低的噪声水平。

基于此,一般采用离散傅立叶变换(DFT)进行信号滤波,使用折线拟合技术对滤波系数进行优化,从而获得高质量的滤波结果。

接下来,应该实现的是数字相敏检波的算法。

首先,通过数字滤波器进行数据采样,并将数据转换为频域数据。

然后,为了解决检波问题,把信号进行振幅处理,使噪声的振幅大小小于某一特定阈值,以判断其检波结果。

最后,以系统仿真结果为准,基于fpga实现数字相敏检波算法。

数字相敏检波算法是fpga应用中常用的一种有效方法,它可以将信号进行调制和解调,从而控制信号的振幅。

此外,基于fpga的数字相敏检波算法具有较强的容错性和可靠性,可以提供调制解调以及精确测量等功能,在许多领域得到了广泛的应用。

综上所述,基于fpga的数字相敏检波算法是一种有效的信号处理技术,由于其低功耗、低成本特点,被广泛应用于许多领域。

它可以利用数字滤波器进行数据采样和频域数据转换;利用折线拟合技术优化系统性能;利用振幅处理和判断阈值实现信号检波;利用fpga实现算法,最终达到调制解调以及精确测量等功能。

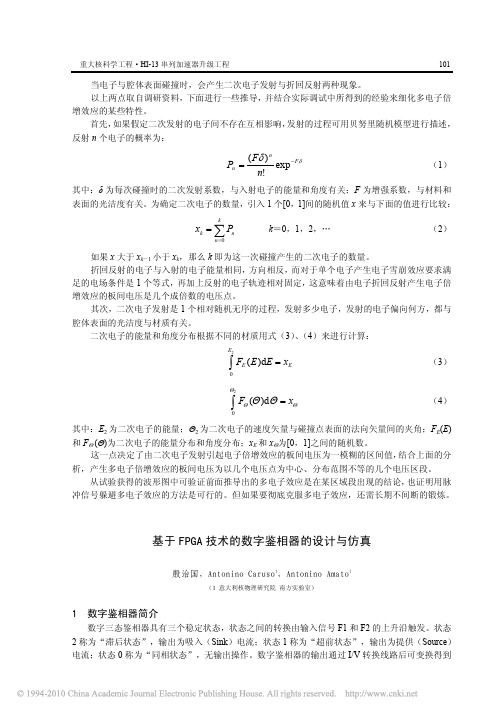

基于FPGA技术的数字鉴相器的设计与仿真

F2 "R9" "R9" "R9" "R9൪ "R7" "R7" "M7" "M7"

表 1 不同布局能达到的最优情况

Up "P9" "P9" "P9" "P7" "N7"

SLICE

S1(N_35) X18Y1 X18Y1 X18Y0 X14Y1 X14Y1

S2(N_36) X18Y0 X18Y0 X18Y1 X14Y0 X14Y0

重大核科学工程·HI-13 串列加速器升级工程

101

当电子与腔体表面碰撞时,会产生二次电子发射与折回反射两种现象。 以上两点取自调研资料,下面进行一些推导,并结合实际调试中所得到的经验来细化多电子倍 增效应的某些特性。 首先,如果假定二次发射的电子间不存在互相影响,发射的过程可用贝努里随机模型进行描述, 反射 n 个电子的概率为:

经逻辑映射后,图 1 描述的数字鉴相器的响应可通过 POST-MAP 仿真得到,仿真采用的计算 公式为:

Vout

= VOD

⋅

PWUp − PWDown PW45 MHz

(1)

其中: VOD 为输出驱动电平,设计采用 LV CMOS33 标准,故取值为 3.3 V;设计针对 45 MHz,故 PW45 MHz 取值 22.222 ns;PWUp、PWDown 分别为仿真得到的输出脉宽。

E2

∫ FE (E)dE = xE

0

(3)

Θ2

∫ FΘ (Θ )dΘ = xΘ

0

(4)

其中:E2 为二次电子的能量;Θ2 为二次电子的速度矢量与碰撞点表面的法向矢量间的夹角;FE(E) 和 FΘ (Θ)为二次电子的能量分布和角度分布;xE 和 xΘ为[0,1]之间的随机数。

基于FPGA的数字正交检波的实现

基于FPGA的数字正交检波的实现

靳鹏

【期刊名称】《电子世界》

【年(卷),期】2014(000)006

【摘要】阐述了数字正交检波的基本原理,设计完成了数字正交检波在FPGA中的实现,最后给出了测试结果,验证了设计的正确性。

%The basic principle of digital orthogonal demodulation is ter,it expounds the implementation of digital orthogonal demodulation in FPGA.Final y,the measurement is performed to verify the correctness of the design.

【总页数】2页(P78-78,79)

【作者】靳鹏

【作者单位】中国电子科技集团公司第二十研究所

【正文语种】中文

【相关文献】

1.基于FPGA的数字相敏检波算法实现 [J], 梁世盛;乔凤斌;张燕

2.基于多相滤波的正交采样零中频数字化接收及QPSK高速解调的FPGA实现 [J], 赵国栋;徐建良

3.基于FPGA的数字B超检波器设计与实现 [J], 彭勇;陈菲;高小明

4.一种超声回波信号的数字正交检波方法及FPGA实现 [J], 曹文;刘春梅;胡莉

5.基于FPGA的数字正交混频变换算法的实现 [J], 胡跃;张正鸿

因版权原因,仅展示原文概要,查看原文内容请购买。

DPSD算法的FPGA高效实现

DPSD算法的FPGA高效实现陈洋;聂在平【摘要】Introduced are the practical applications of digital phase sensitive detector (DPSD).In order to effectively reduce the excessive demands of the practical application of the multi-channel low-frequency sine and cosine signal and high-frequency sine and cosine signal DPSD detection algorithms on the DSP processing capability,proposed is a DPSD algorithm based on the Field Programmable Gate Array (FPGA) to achieve two effective frameworks respectively by analyzing the general architecture of digital signal processing hardware.For multi-channel detection,the architecture is able to reduce hardware resource consumption significantly.For the high-frequency detection,the maximum sampling rate of the system clock can be achieved.The structure mapped in FPGAA3P400 may reach 70 Mbit/s sampling rate,so the structure will greatly reduce the computational burden of the DSP in the high sampling rate DPSD.Detailed design ideas and methods as well as new designs in the FPGA implementation are discussed,the hardware structure,FSM state machine diagram and FPGA hardware resource consumption and simulation test results are shown.These two methods based on the FPGA DPSD architecture are flexible and configurable to meet the different number of channels and sampling rate requirements while ensuring the calculation accuracy.%为有效降低实际应用中多通道低频正余弦信号以及高频正余弦信号的DPSD检测算法对DSP处理能力的过高要求,分析了数字信号处理硬件一般架构,提出基于现场可编程门阵列(FPGA)的DPSD算法实现的2种有效架构.针对多通道检测,该架构能够显著降低硬件资源消耗;针对高频检测,架构最大可实现采样率为系统时钟.该结构在FPGA A3P400实现最大70 Mbit/s的采样率,能够极大地降低DSP在高采样率时DPSD的计算负担.讨论了设计思路与方法以及新设计在FPGA中的实现,给出详细的硬件结构、有限状态机(FSM)图、FPGA硬件资源消耗以及仿真测试结果.这2种基于FPGA的DPSD架构具有灵活的可配置性,在保证计算精度的同时,可满足不同的通道数量以及速率检测需求.【期刊名称】《测井技术》【年(卷),期】2013(037)004【总页数】5页(P421-425)【关键词】测井仪器;数字相敏检波;多通道DPSD FPGA架构;高速DPSD FPGA架构;采样率【作者】陈洋;聂在平【作者单位】电子科技大学电子工程学院,四川成都611731;电子科技大学电子工程学院,四川成都611731【正文语种】中文【中图分类】P631.840 引言电阻率测井仪器一般是通过发射单频的正弦波或多种频率的正弦波叠加信号激励地层,通过线圈或电极接收感兴趣的电压或电流信号,根据该信号的变化反映出地层电阻率的变化[1]。

基于FPGA的高精度相位差测量算法实现

基于FPGA的高精度相位差测量算法实现作者:郎杰邹建彬张尔扬来源:《现代电子技术》2011年第21期摘要:首先介绍了两种高精度相位差测量算法,一种是基于直接数字频率合成(DDS)的相关测量法,另一种是基于快速傅里叶变换(FFT)的FFT测量法。

其次,通过理论仿真分析两种算法在不同信噪比和数据长度下的性能,并在此基础上给出了硬件平台的设计方案。

最后,基于高性能的FPGA芯片XC5SX95T,搭建了硬件实验平台,完成了两种相位差测量算法的硬件实现。

经过实测,该硬件平台能够达到良好的相位差测量精度。

关键词:相位差;相关; FFT; FPGA 中图分类号:TN874-34 文献标识码:A文章编号:1004-373X(2011)21-0028-03Implementation of High Precision Phase Difference Measurement Algorithm Based on FPGA LANG Jie, ZOU Jian-bin, ZHANG Er-yang(College of Electronic Science and Engineering, National University of Defense Technology, Changsha 410073,China)Abstract:Two kinds of high precision phase difference measurement algorithms are presented: correlation measurement based on direct digital synthesize (DDS) and FFT measurement based on fast Fourier transform (FFT). The performance of these two algorithms under different SNR and data length are analyzed by theoretical simulation, and a design scheme of hardware platform is proposed. The two kinds of phase difference algorithms are realized on the hardware platform where the core of the platform that is high performance FPGA chip XC5SX95T is implemented. The hardware platform can achieve a well precision through the real-time measurement results of phase difference.Keywords: phase difference; correlation; FFT; FPGA0 引言两个同频信号的相位差测量在工程上有着广泛的应用。

基于FPGA的数字正交检波的实现

基于FPGA的数字正交检波的实现作者:靳鹏来源:《电子世界》2014年第06期【摘要】阐述了数字正交检波的基本原理,设计完成了数字正交检波在FPGA中的实现,最后给出了测试结果,验证了设计的正确性。

【关键词】正交检波;FPGAImplementation of Digital Orthogonal Demodulation based on FPGAJin PengAbstract:The basic principle of digital orthogonal demodulation is ter,it expounds the implementation of digital orthogonal demodulation in FPGA.Finally,the measurement is performed to verify the correctness of the design.Keywords:Orthogonal Demodulation;FPGA随着软件无线电技术的发展,传统的模拟接收机已经被数字接收机所取代。

相对于模拟接收机中所使用的模拟正交检波,现在的数字接收机中普遍使用数字正交检波,直接对中频信号进行采样,将模拟中频信号转换为数字信号,之后在数字域对信号进行处理,得到两路正交的基带信号[1]。

这种方法相较于传统的模拟正交检波方法,具有非常高的精度和稳定性,并且可以提高系统的灵活性。

目前,数字正交检波主要是通过使用专用可编程芯片、DSP和FPGA 这三种方式来实现。

FPGA具有出色的并行处理能力,适用于相关运算和滤波等各种复杂的数字信号处理运算。

此外,FPGA的可编程性使其具有极大的灵活性,非常便于系统的功能扩充和升级,是目前被普遍采用的一种数字正交检波实现方法。

本文基于Altera公司的StratixⅢ系列中的EP3SE110F1152来实现对一中频窄带信号的数字正交检波及后续处理。

一种基于FPGA的高精度数字鉴相器

一种基于FPGA的高精度数字鉴相器贺为婷;裴广利【摘要】本文提出一种基于CIC滤波器和CORDIC算法的高精度数字鉴相器.本鉴相器通过两路正交本振信号分别与两路待测相信号相乘,使用CIC滤波器的滤除乘积中的高频信号,最后通过CORDIC算法计算出相位差.上述方法适于FPGA实现,Alteral公司的FGPA有丰富的乘法器资源,并且可以通过增加数据位宽度和使用流水线来实现鉴相器的高精度性和高速度性.通过modelsim和matlab的联合功能仿真,在加入一路35dB的高斯白噪声的信号中进行30次测量最大误差小于0.0032 rad.%A method based on CIC filter and the CORDIC algorithm for high accuracy digital phase discriminator is presented. First of all, the two orthogonal local oscillator signals generated by FPGA are respectively multiplied by two measured signals. Then, the phase demodulator use CIC filter to filter high frequency signal of the product. Last, the CORDIC algorithm calculates the phase difference. FPGA is fit to complete the design. The al-teral company' s FPGA has rich multiplier resources and can increase the data bit width and use the pipeline to achieve phase for the high precision and high speed. The maximum error is less than 0. 003 2 rad of 30 measures adding 35 dB Gauss white noise to one signal, through the Modelsim and Matlab joint function simulation.【期刊名称】《科学技术与工程》【年(卷),期】2012(012)030【总页数】6页(P8047-8051,8057)【关键词】FPGA;CIC滤波器;CORDIC算法【作者】贺为婷;裴广利【作者单位】西安工业大学电子信息工程学院,西安710032;西安工业大学电子信息工程学院,西安710032【正文语种】中文【中图分类】TN7633;TN79.1激光测距是随着激光技术的发展而发展起来的一种高精度测距技术。

基于FPGA的高精度鉴相器实现

Microelectr o n ic Tech no l ogy基于FPGA的高精度鉴相器实现董淑豪丨,吴东岷2(1.中国科学技术大学微电子学院,安徽合肥230026;2.中国科学院苏州纳米技术与纳米仿生研究所,江苏苏州215000)摘要:基于模拟电路的鉴相器虽然响应速度快,但是很难达到较高的精度,并且开发周期长不易优化。

为了可以实时检测MEMS器件谐振时微小的相位变化,提出一种基于FPGA的高精度鉴相器遥该鉴相器主要是由数字混频器、FIR数字滤波器、DDS信号发生器以及模数转换电路组成。

鉴相方法是通过将被测信号与一同频、相位可调、且初始相位为90毅的参考信号混频,并通过高阶FIR滤波器提取与相位有关的差频信号,调节参考信号相位使得此差频信号趋近于0,则此参考信号的相位调节量即为被测信号的相位。

鉴相器的时钟频率为100MHz,鉴相精度可以达到0.0001毅遥工作频率灵活可调,并且应用于锁相环中时,可以很方便地与MEMS器件的驱动电路兼容。

关键词:FPGA;FIR;鉴相器;DDS;MEMS中图分类号:TN763.3文献标识码:A DOI:10.16157/j.issn.0258-7998.200377中文引用格式:董淑豪,吴东岷.基于FPGA的高精度鉴相器实现[J].电子技术应用,2020,46(10):57-60,78.英文弓I用格式:Dong Shuhao,Wu Dongmin.Realization of high precision phase detector based on FPGA[J].Application of Electronic Technique,2020,46(10):57-60,78.Realization of high precision phase detector based on FPGADong Shuhao1,Wu Dongmin2(1.School of Microelectronics,University of Science and Technology of China,Hefei230026,China;2.Suzhou Institue of Nano-Tech and Nano-Bionics,Suzhou215000,China)Abstract:Although the response speed of the phase detector based on analog circuit is fast,it is difficult to achieve high precision, and the development cycle is long and difficult to optimize.In order to detect the tiny phase change of micro-electro-mechanical system(MEMS)devices in real time,a high-precision phase detector based on field programmable gate array(FPGA)is proposed. The phase detector is mainly composed of digital mixer,finite impulse response(FIR)digital filter,direct digital synthesis(DDS)signal generator and analog digital converter conversion circuit.The phase detection method is to mix the measured signal with the reference signal with the same frequency,adjustable phase and initial phase of90毅,and extract the phase related difference frequency signal through high-order FIR filter,adjust the reference signal phase to make the difference frequency signal close to0, then the phase adjustment amount of the reference signal is the phase of the measured signal.The clock frequency of the phase detector is100MHz,and the phase accuracy can reach0.0001毅.The working frequency is flexible and adjustable.When it is used in PLL,it can be easily compatible with the driving circuit of MEMS devices.Key words:FPGA;FIR;phase detector;DDS;MEMS0引言微机电系统(Micro-Electro-Mechanical System,MEMS),体积小、功耗低、谐振频率高、光学特性好[1],在医疗、军事、科研等领域得到广泛应用。

基于FPGA的一种新型数字鉴频鉴相器的设计

多相滤波的数字相干检波原理及FPGA实现

来源:电子科技作者:何光明黄云介绍一种利用带通采样定理及多相滤波的方式实现数字相干检波的方法,由于采用数字信号处理的方式获取I、Q基带信号,因此具有镜频抑制能力强、线性动态范围大、系统设备简单、一致性好等优点。

文章主要从理论及工程实现两个方面展开论述。

1 基本原理设某一数字滤波器的脉冲响应为h(n),则其Z变换H(z)定义为对式(1)展开变换后,可得令则式(2)即为数字滤波器H(z)多相滤波结构,显然H(z)由D个EK(z),K=0,1,2,…,D-1分支滤波器构成,并且每个滤波器的阶数为H(z)阶数的1/D,这种多相滤波的结构不仅能够提高系统实时处理能力,而且可以降低传统滤波器滤波运算后的累计误差。

下面对多相滤波技术在数字相干检波中的应用进行理论分析。

通常,对于载频为fo的带限(带宽B)中频信号,若以采样率为fs=4fo/(2m+1),m=O,1,2,…,且fs≥2B对其采样,通过符号修正及多相滤波的方式可准确获得正交的两路基带信号,如图1所示。

设信号x(t)=a(t)cos[2πfot+φ(t)],若以采样率为fs=4fo/(2m+1),m=0,1,2,…,且fs≥2B 对x(t)采样后得到的采样序列为式中,分别为信号的同向分量和正交分量,对x(n)进行奇偶分路和符号变换,可以得到显然,和分别为同向分量和正交分量的2倍抽取序列,容易证明和的数字谱为式(7)和式(8)描述了正交解调后同向I及正交Q支路的频谱,但二者的数字谱相差一个延迟因子,这相当于在时域上相差O.5个采样点,需要两个延迟滤波器校正,这两个滤波器需要满足,两路延迟滤波器需要具有相似的幅度或相位特性,保证、支路严格匹配。

理论分析知,可以采用多相滤波的方式从一原型低通滤波器中取出数字谱相差的两个支路分别对I、Q两路延迟滤波,由于两个滤波器是从同一个原型滤波器中抽取出来的两个分支,因此具有相似的幅度及相位特性。

设原型滤波器的冲击响应为h(n),由(1)式知,其多相结构第K条支路的冲击响应为则EK(z)频率响应为令D=4,则式中除i=0项不为零外,其余均为零,所以求得提取K=3及K=1作为式(7)及式(8)I、Q两路延迟滤波,得由此可见,经过滤波,两个正交得基带信号在时间上完全对齐,满足数字正交相干检波的要求。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Байду номын сангаас

1 数 字相敏检 波

1 . 1 数 字相 敏 检 波 的优 点

模 拟 相 敏 检 波 主要 是 利 用 三 极 管 的开 关 特 性 实 现

d e t e c t i o n , D P S D)算法 能很好 地对 淹 没 于噪声 中的信

号进行 提 取 。因此 , 该 方 法 被 广 泛应 用 于 现 有 检 测

基于 F P G A的数字相敏检 波算法实现

梁世盛 。 等

基于 F P G A的数 字 相敏 检 波算 法 实现

mp l e m en t a t i on o f F PGA— b a s e d Di g i t a l Ph a s e S e n s i t i v e De t e c t i o n Al g o r i t h m

s i g n l a p r o c e s s o r ( D S P) T e s t s y s t e m Hi g h - s p e e d s a m p l i n g s y s t e m

0 引言

在实 际工程测量 中 , 被测信 号 常常会被 强噪 声所 干扰或 淹 没 , 而 数 字相 敏 检 波 ( d i g i t a l p h a s e 。 s e n s i t i v e

D P S D算 法运 算所 出现 的控制 精度不 高 和运算 速度慢 等 问题 , 详细 分 析 了 D P S D算 法 , 设计 了基于 F P G A 的数字 相敏 检 波算 法 。该算

法解 决 了控 制信 号精 度不 高等 问题 , 满 足高 速采 样系统 对运 算速 度的要 求 。试 验结 果表 明 , 基于 F P G A 的数字相 敏检测 算法在 测试 系

磐世 盛 寿 凤云 荻 旅 蒸

( 上海航 天设 备制 造总厂 , 上海 2 0 0 2 4 5)

摘

要 :数 字相 敏检 波 ( D P S D ) 算 法是 一种 有效 的信 号检 测 方 法。针 对 某 些高 速 采样 系 统 采用 现 有 D S P芯 片控 制模 数 转换 和 进行

Ke y wo r d s :D i g i t a l p h a s e s e n s i t i v e d e t e c t i o n( D P S D) F i e l d p r o g r a m ma b l e g a t e a r r a y( F P G A) An l a o g t o d i g i t a l c o n v e r t e r ( A D C) D i g i t l a

统 中能有较 好 的检测 效果 。 关键 词 :数字 相敏检 波 ( D P S D) F P G A A D C D S P 测试 系统

中图分类 号 :T P 3 1 6 + . 2 文献 标志 码 :A

高速 采样 系统

Ab s t r a c t :F o r t e s t s y s t e ms ,d i g i t a l p h a s e s e n s i t i v e d e t e c t i o n( DP S D)a l g o r i t h m i s a n i mp o r t a n t me t h o d t o d e t e c t s i g n a l s .I n s o m e o f t h e h i g h