CortexM3中断服务程序设计

第9章-Cortex-M3异常和中断

第九章Cortex-M3异常和中断9.1Cortex-M3异常91C t M39.2NVIC与中断控制929.1.1 异常类型异常。

CM3支持为所有能打断正常执行流的事件都称为CM3支持为数众多的系统异常和外部中断。

异常是另一种形式的中断,它是由内部fault引起的,或者内核的SysTick、SVCall等。

而中断是由随机的外部事件引发的。

件引发的编号为1~15的对应系统异常;编号为16~255的对应外部中断。

除了个别异常的优先级被定死外,其它异常的优先级都是可编程的。

可编程的当前运行的异常编号,是由特殊寄存器IPSR或NVIC的中断控制状态寄存器来给出的。

断控制状态寄存器来给出的异常表异常号异常类型优先级描述0N/A N/A没有异常在运行1复位-3 (最高)复位2NMI-2 不可屏蔽中断(外部NMI 输入)3硬件fault-1各种fault情况4内存管理fault可编程内存管理fault;MPU 访问非法地址5总线fault可编程总线fault,比如预取终止6用法fault可编程由于程序fault或尝试访问协处理器导致的异常7-10保留N/A—11SVCall可编程系统服务调用12调试监视器可编程调试监视器(续)13保留N/A—14PendSV可编程可挂起系统设备申请15SysTick可编程系统时钟定时器16外部中断#0可编程外部中断17外部中断#1可编程外部中断…………255外部中断#239可编程外部中断当一个被使能的异常发生时,如果它不能够被立即执行,它将被挂起(pending)。

9.1.2 优先级定义在CM3中优先级对于异常来说很关键的它决定一个 在CM3中,优先级对于异常来说很关键的,它决定个异常是否能被屏蔽,以及在未被屏蔽的情况下何时可以响应。

应优先级的数值越小,则优先级越高。

CM3支持中断嵌套,使得高优先级异常会抢占(preempt)低优先级异常。

3个系统异常:复位、NMI以及硬fault有固定的优先级,并且它们的优先级号是负数,从而高于所有其它异常。

Cortex系列M1、M2、M3、M4对比只是分享

Cortex-M 系列针对成本和功耗敏感的MCU 和 终端应用(如智能测量、人机接口设备、汽车和 工业控制系统、大型家用电器、消费性产品和医 疗器械)的混合信号设备进行过优化。

.比较Cortex-M 处理器Cortex-M 系列是适用于具有不同的成本、功耗和性能的一系列易于使用的兼容嵌入式设备 (如微控制器(MCU ))的理想解决方案。

每个处理器都针对十分广泛的嵌入式应用范围提供 最佳权衡取舍。

关于Cortex-M4与Cortex-M3的区别,:M4不是用来取代M3的,它只是多了浮点运算功能。

如果 你不需要浮点DSP, M3就足够了"8/16位”应用“8/16位”应用"16/32位”应用“32位/DSC ”应用低成本和简单性低成本,最佳能效高性能,通用有效的数字信号控制20-50M 工作频率20-50M 工作频率32-100M 工作频率80-204M 工作频率冯诺依曼结冯诺依曼结哈佛结哈佛结构构构构Cortex-M 系列处理器都是二进制向上兼容的,这使得软件重用以及从一个Cortex-M 处理器 无缝发展到另一个成为可能。

FPGA Low Cost MCU High Performance MCUMCortex-M 技术RISC 处理器内核Thumb-2® 技术•高性能32位CPU •具有确定性的运尊•低延退3阶段管道• 16/32位指令的最佳混合•小于8位设费3倍的代码大小•对性能没有负面影响低功耗模式嵌套矢堂中断控制器(NVIC)•集成的睡眠状态支持•多电源域•基于架构的软件控制•低延返、低抖动中断响应•不需要汇编编程•以纯C 语言编写的中断服务例程工具和RTOS 支持99[竺!9里袒试犯建朦.厂泛的第三方工具支持• Cortex 微控制器软件接口标准(CMSIS)•最大限度地增加软件成果重用• JTAG 或2针串行线调试(SWD)连接•支持多处理器•支持实时跟踪CMSISARM Cortex 微控制器软件接口标准(CMSIS) 是Cortex-M 处理器系列的与供应商无关的硬 件抽象层。

Cortex-M3咬尾中断与晚到中断

Cortex-M3咬尾中断与晚到中断【咬尾中断】在处理器在响应某些异常时,如果⼜发⽣其他异常,但它们优先级不够⾼,则它们会被阻塞。

那么,在当前的异常执⾏返回后,系统处理悬起的异常时,倘若还是先POP,然后⼜把POP处理的内容PUSH回去,那么就⽩⽩浪费CPU 时间了。

因此,Cortex-M3不会再POP这些寄存器,⽽是继续使⽤上⼀个异常已经PUSH好的结果,消除POP和PUSH操作的耗时。

这么⼀来,看上去好像后⼀个异常把前⼀个的尾巴要掉了,前前后后只执⾏了⼀次PUSH/POP操作。

于是,这两个异常之间的“时间沟”就变窄了很多,如图所⽰:和常规中断处理(ARM7)的⽐较:【晚到中断】Cortex-M3的中断处理还有另⼀个机制,它强调了优先级的作⽤,这就是“晚到的异常处理”。

当Cortex-M3对某异常的响应序列还处在早期:⼊栈的阶段,尚未执⾏其他服务程序时。

如果此时收到了更⾼优先级异常的请求,则本次⼊栈就成了⾼优先级中断做的了。

⼊栈后,将执⾏⾼优先级的异常服务程序。

可见,⾼优先级的异常虽然来晚了,却因为优先级⾼使得服务程序可以被先处理,低优先级异常的⼊栈操作则变成了为⾼优先级异常的⼊栈。

⽐如,若在响应某低优先级异常#1的早起,检测到了⾼优先级异常#2,则只要#2没有太晚,就能以“晚到中断”的⽅式处理,在⼊栈完毕后执⾏ISR#2。

如图所⽰:如果异常#2来得太晚,以⾄于已经执⾏了ISR#1的指令,则按普通的抢占处理,这会需要更多的处理器时间和额外32字节的堆栈空间。

在ISR#2执⾏完毕后,则以“咬尾中断”的⽅式来启动ISR#1的执⾏。

参考摘录:《Cortex-M内核系列和STM32-讲座2教程.pdf》《ARM Cortex-M3权威指南.pdf》。

stm32f103c8t6单片机核心电路设计

stm32f103c8t6单片机核心电路设计STM32F103C8T6是一款低功耗、高性能的8位微控制器,是STM32系列中的一款主要单片机。

本文将介绍该单片机的核心电路设计,包括处理器、存储器、输入输出端口、中断控制器、时钟等组成部分。

一、处理器STM32F103C8T6采用了ARM Cortex-M3内核,具有低功耗、高性能的特点。

处理器内部包括一个主处理器和一个辅助处理器,主处理器负责控制整个系统的运行,辅助处理器则负责辅助主处理器完成一些基本的任务。

主处理器采用了ARM Cortex-M3的内核,具有以下几个特点:1. 时钟频率高:该处理器的时钟频率高达32MHz,使得系统运行更加稳定。

2. 功耗低:该处理器的功耗只有5瓦,相对于传统的8位单片机来说,具有更高的功耗优势。

3. 处理能力强:该处理器具有4个处理核心,可以同时处理多个任务,使得系统运行更加高效。

二、存储器STM32F103C8T6内置了2个16位的MGB存储器,可以同时存储256个位的数据。

存储器内部包括一个EEPROM和一个 Flash存储器,EEPROM用于存储系统配置信息、程序存储器等,而 Flash存储器则用于存储程序和数据。

三、输入输出端口STM32F103C8T6具有多个输入输出端口,包括串口、USB、I2C、SPI、CAN等多种接口。

这些接口可以通过外部电路实现数据传输,使得系统更加灵活。

四、中断控制器STM32F103C8T6具有一个中断控制器,可以控制系统的各个部分之间的通信和交互。

中断控制器可以实现中断服务程序的设计,使得系统具有更好的响应能力和灵活性。

五、时钟STM32F103C8T6内置了一颗32MHz的时钟,可以确保系统运行的稳定性和精度。

同时,该时钟还具有高速采样功能,可以方便地进行数据采集和处理。

综上所述,STM32F103C8T6单片机的核心电路设计包括了处理器、存储器、输入输出端口、中断控制器和时钟等多个部分,具有低功耗、高性能的特点,可以方便地实现各种复杂的控制和数据处理。

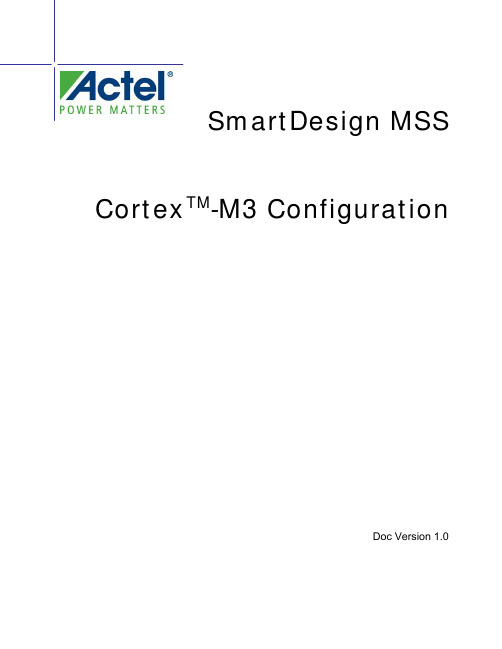

智能设计MSS Cortex-M3配置文档说明书

SmartDesign MSS Cortex TM-M3 ConfigurationDoc Version 1.02 CortexTM-M3 ConfigurationTable of ContentsIntroduction...................................................................................................................3 Configuration Options..................................................................................................3 Port Description (3)CortexTM-M3 Configuration3IntroductionThe SmartFusion Microcontroller Subsystem (MSS) contains an ARM Cortex-M3 microcontroller, a low-power processor that features low gate count, low and predictable interrupt latency, and low-cost debug. It is intended for deeply embedded applications that require fast interrupt response features. This document describes the ports that are available on the Cortex-M3 core in the SmartDesign MSS Configurator.For more information about the specific implementation of the Cortex-M3 in the Actel SmartFusion device, please refer to the Actel SmartFusion Microcontroller Subsystem User’s Guide .Configuration OptionsThere are no configuration options for the Cortex-M3 core in the SmartDesign MSS Configurator.Figure 1: Cortex-M3 in SmartFusionPort DescriptionPort NameDirectionPAD?DescriptionRXEV In No Causes the Cortex-M3 to wake up from a WFE ( wait for event ) instruction. The eventinput, RXEV, is registered even when not waiting for an event, and so affects the next WFE. TXEV Out No Event transmitted as a result of a Cortex-M3 SEV ( send event ) instruction. This is asingle-cycle pulse equal to 1 FCLK period. SLEEP Out No This signal is asserted when the Cortex-M3 is in sleep now or sleep-on-exit mode, andindicates that the clock to the processor can be stopped. DEEPSLEEP OutNo This signal is asserted when the Cortex-M3 is in sleep now or sleep-on-exit mode whenthe SLEEPDEEP bit of the System Control Register is set.Note:Non-PAD ports must be promoted manually to the top level from the MSS configurator canvas to be available as the next level of hierarchy.Actel Corporation2061 Stierlin Court Mountain View, CA 94043-4655 USA Phone 650.318.4200 Fax 650.318.4600Actel Europe Ltd.River Court, Meadows Business Park Station Approach, Blackwater Camberley Surrey GU17 9AB United KingdomPhone +44 (0) 1276 609 300 Fax +44 (0) 1276 607 540Actel JapanEXOS Ebisu Building 4F 1-24-14 Ebisu Shibuya-ku Tokyo 150, JapanPhone +81.03.3445.7671 Fax +81.03.3445.7668 Actel is the leader in low-power and mixed-signal FPGAs and offers the most comprehensive portfolio of system and power management solutions. Power Matters. Learn more at .© 2009 Actel Corporation. All rights reserved. Actel and the Actel logo are trademarks of Actel Corporation. All other brand or product names are the property of their respective owners.Actel Hong KongRoom 2107, China Resources Building 26 Harbour Road Wanchai, Hong Kong Phone +852 2185 6460 Fax +852 2185 6488 5-02-00242-0。

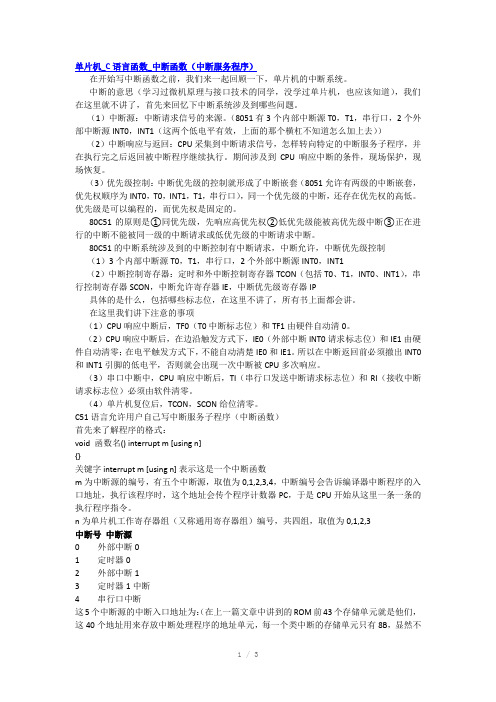

单片机C语言函数中断函数(中断服务程序)

单片机_C语言函数_中断函数(中断服务程序)在开始写中断函数之前,我们来一起回顾一下,单片机的中断系统。

中断的意思(学习过微机原理与接口技术的同学,没学过单片机,也应该知道),我们在这里就不讲了,首先来回忆下中断系统涉及到哪些问题。

(1)中断源:中断请求信号的来源。

(8051有3个内部中断源T0,T1,串行口,2个外部中断源INT0,INT1(这两个低电平有效,上面的那个横杠不知道怎么加上去))(2)中断响应与返回:CPU采集到中断请求信号,怎样转向特定的中断服务子程序,并在执行完之后返回被中断程序继续执行。

期间涉及到CPU响应中断的条件,现场保护,现场恢复。

(3)优先级控制:中断优先级的控制就形成了中断嵌套(8051允许有两级的中断嵌套,优先权顺序为INT0,T0,INT1,T1,串行口),同一个优先级的中断,还存在优先权的高低。

优先级是可以编程的,而优先权是固定的。

80C51的原则是①同优先级,先响应高优先权②低优先级能被高优先级中断③正在进行的中断不能被同一级的中断请求或低优先级的中断请求中断。

80C51的中断系统涉及到的中断控制有中断请求,中断允许,中断优先级控制(1)3个内部中断源T0,T1,串行口,2个外部中断源INT0,INT1(2)中断控制寄存器:定时和外中断控制寄存器TCON(包括T0、T1,INT0、INT1),串行控制寄存器SCON,中断允许寄存器IE,中断优先级寄存器IP具体的是什么,包括哪些标志位,在这里不讲了,所有书上面都会讲。

在这里我们讲下注意的事项(1)CPU响应中断后,TF0(T0中断标志位)和TF1由硬件自动清0。

(2)CPU响应中断后,在边沿触发方式下,IE0(外部中断INT0请求标志位)和IE1由硬件自动清零;在电平触发方式下,不能自动清楚IE0和IE1。

所以在中断返回前必须撤出INT0和INT1引脚的低电平,否则就会出现一次中断被CPU多次响应。

(3)串口中断中,CPU响应中断后,TI(串行口发送中断请求标志位)和RI(接收中断请求标志位)必须由软件清零。

ARMCortex-M3系统设计与实现——STM32基础篇 共211页

郭书军 cortex_m3126

前页 返回

ARM Cortex-M3系统设计与实现——STM32基础篇

第1章 STM32 MCU简介

1.4 Cortex-M3简介 • Keil的SysTick对话框

郭书军 cortex_m3126

前页 返回

ARM Cortex-M3系统设计与实现——STM32基础篇

郭书军 cortex_m3126

前页 返回

ARM Cortex-M3系统设计与实现——STM32基础篇

第1章 STM32 MCU简介

1.3 STM32 MCU系统时钟树

• 系统时钟树中的时钟选择、预分频值和外设时钟使能等 都可以通过对复位和时钟控制(RCC)寄存器编程实现

偏移 地址

名称

类型 复位值

9 ADC1EN 读/写 0 ADC1时钟使能:0-关闭时钟,1-开启时钟

11 TIM1EN 读/写 0 TIM1时钟使能:0-关闭时钟,1-开启时钟

12 SPI1EN 读/写 0 SPI1时钟使能:0-关闭时钟,1-开启时钟

14 USART1EN 读/写 0 USART1时钟使能:0-关闭时钟,1-开启时钟

郭书军 cortex_m3126

前页 返回

ARM Cortex-M3系统设计与实现——STM32基础篇

第2章 通用并行接口GPIO

2.1 GPIO结构及寄存器说明

• 每个端口的4个配置位是CNF[1:0]和MODE[1:0]

CNF MODE [1:0] [1:0]

输入配置

CNF MODE [1:0] [1:0] (2)

郭书军 cortex_m3126

前页 返回

ARM Cortex-M3系统设计与实现——STM32基础篇

Cortex M3异常与NVIC

异常处理注意事项

确保异常处理程序能够正确处理 所有可能的异常情况

异常处理程序应该能够正确恢复 系统状态,避免系统崩溃

添加标题

添加标题

添加标题

添加标题

异常处理程序应该尽可能简洁, 避免不必要的代码执行

异常处理程序应该能够正确记录 异常信息,便于调试和维护

NVIC(Nested Vecred Interrupt Controller)介绍

案例三:智能家居系统中Cortex M3异常与NVIC的应用

智能家居系统概述:介绍智能家居系统的功能、组成和特点。

Cortex M3异常与NVIC在智能家居系统中的应用:介绍Cortex M3异常与NVIC在智能 家居系统中的具体应用,如控制家电、安全监控等。

案例分析:分析一个具体的智能家居系统案例,如智能照明系统,介绍Cortex M3异常 与NVIC在其中的应用。

Cortex M3异常:当CPU检测到 异常时,会跳转到异常处理程序

异常处理程序:由用户编写,用 于处理异常情况

添加标题

添加标题

添加标题

添加标题

NVIC:用于管理中断和异常,包 括优先级、使能、清除等操作

配合使用:NVIC用于管理异常, 异常处理程序用于处理异常情况, 两者配合使用可以提高系统的稳 定性和可靠性。

6

Cortex M3异常与NVIC的常见问题及解决 方案

单击此处添加章节标题

Cortex M3异常处理

异常种类及功能

异常种类:Cortex M3支持多种异常类型, 包括中断、复位、未定义指令、数据访问错误 等

功能:每种异常类型都有其特定的处理方式, 例如中断用于处理外部事件,复位用于恢复系 统状态等

Cortex M3异常与NVIC的常见问 题及解决方案

微处理器9CortexM3异常(中断)处理

Cortex-M3的异常(中断)处理

优先级分组

为了对具有大量中断的系统加强优先级控制,NVIC

支持优先级分组机制。您可以使用应用中断和复位控制寄 存器中的PRIGROUP区来将每个PRI_N中的值分为占先优

先级区和次优先级区。我们将占先优先级称为组优先级。 如果有多个挂起异常共用相同的组优先级,则需使用次优 先级区来决定同组中的异常的优先级,这就是同组内的次 优先级。组优先级和次优先级的结合就是通常所说的优先 级。如果两个挂起异常具有相同的组优先级,则挂起异常 的编号越低优先级越高。这与优先级机制是一致的。

Cortex-M3的异常(中断)处理

优先级分组

中断优先级区(PRI_N[7:0])

占先区

次优先区

PRI_N 7 6 5 4 3 2 1 0

注意: 修改PRIGROUP区的值可改变占先区和 次优先区的位数。

1. 占先优先级又称 为组优先级

2. 如果两个挂起异 常具有相同的组 优先级,则挂起 异常的编号越低 优先级越高。

Cortex-M3的异常(中断)处理

优先级分组

PRIGROU P[2:0]

二进制点 的位置

中断优先级区,PRI_N[7:0]

占先区 次优先 占先优先级

级区

的数目

次优先级 的数目

b000

bxxxxxxx.y [7:1] [0]

128

2

b001

bxxxxxx.yy [7:2] [1:0] 64

4

b010

Cortex-M3的异常(中断)处理

返回

异常基于优先级的动作

在没有挂起异常或没有比被压栈的ISR优先级更高 的挂起异常时,处理器执行出栈操作,并返回到被压 栈的ISR或线程模式。

arm cortex-m3全可编程soc原理

arm cortex-m3全可编程soc原理如下:

1.架构:Cortex-M3 核心是基于ARMv7-M 架构,这是一个针对

嵌入式应用程序优化的架构。

它包含一个ARM 指令集、一个

ARM 连接至程序的接口以及一些特定于嵌入式应用的扩展。

2.核心功能:Cortex-M3 核心具有高性能、低功耗和低成本的特

点。

它包含一个32 位RISC 处理器,具有一个三级流水线。

核心还包含一个嵌套向量中断控制器,允许高效的异常和中断

处理。

3.可编程性:Cortex-M3 是完全可编程的。

这意味着硬件和软件

都可以通过编程来定制。

ARM 的微控制器工具链(如Keil 或

IAR)可用于编译和调试代码,以适应特定的应用需求。

4.系统集成:SoC 是一种将多个硬件组件集成到一个单一芯片上

的技术。

在Cortex-M3 中,这些组件可能包括内存、通信接口、

ADC、DAC 等。

通过将所有这些组件集成到单个芯片上,可以

降低系统成本、减小体积并提高可靠性。

5.低功耗:Cortex-M3 被设计为低功耗微控制器,适用于电池供

电的应用。

它具有多种低功耗模式,可以在不使用时降低功耗。

6.安全性:Cortex-M3 提供了多种安全特性,如内存保护单元

(MPU)和安全区域(Secure Zone),以保护敏感数据和代码。

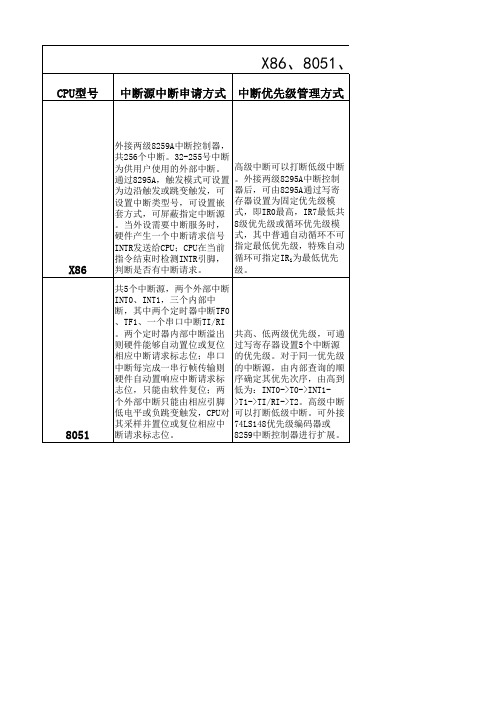

X86、8051、cortex-M3三种CPU中断部分的比较

中断向量

外接两级8295A中断控制器情况下,实 模式下存放于存储器的低端00000H003FFH,共1K字节,每一个中断号占 据4字节的空间,低2字节存放对应中 断入口子程序的偏移地址,高2字节存 放对应中断入口子程序的段基址。

5个中断源对应5个固定的中断向量, 具体情况如下: INT0:0003H T0: 000BH INT1:0013H T1: 001BH TI/RI:0023H T2: 002BH

X86、8051、Cortex-M3中断部分

CPU型号 中断源中断申请方式 中断优先级管理方式

X86

外接两级8259A中断控制器, 共256个中断。32-255号中断 为供用户使用的外部中断。 通过8295A,触发模式可设置 为边沿触发或跳变触发,可 设置中断类型号,可设置嵌 套方式,可屏蔽指定中断源 。当外设需要中断服务时, 硬件产生一个中断请求信号 INTR发送给CPU;CPU在当前 指令结束时检测INTR引脚, 判断是否有中断请求。 共5个中断源,两个外部中断 INT0、INT1,三个内部中 断,其中两个定时器中断TF0 、TF1、一个串口中断TI/RI 。两个定时器内部中断溢出 则硬件能够自动置位或复位 相应中断请求标志位;串口 中断每完成一串行帧传输则 硬件自动置响应中断请求标 志位,只能由软件复位;两 个外部中断只能由相应引脚 低电平或负跳变触发,CPU对 其采样并置位或复位相应中 断请求标志位。

高级中断可以打断低级中断 。外接两级8295A中断控制 器后,可由8295A通过写寄 存器设置为固定优先级模 式,即IR0最高,IR7最低共 8级优先级或循环优先级模 式,其中普通自动循环不可 指定最低优先级,特殊自动 循环可指定IRi为最低优先 级。

8051

Cortex-M3

Cortex-M3 异常和中断

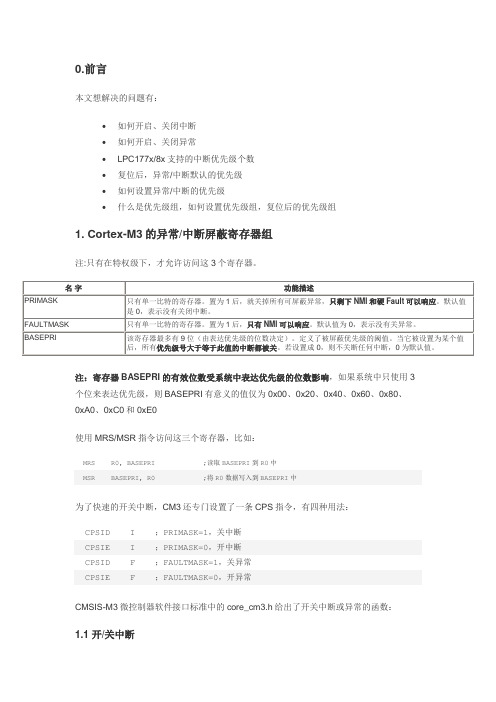

0.前言本文想解决的问题有:∙如何开启、关闭中断∙如何开启、关闭异常∙LPC177x/8x支持的中断优先级个数∙复位后,异常/中断默认的优先级∙如何设置异常/中断的优先级∙什么是优先级组,如何设置优先级组,复位后的优先级组1. Cortex-M3的异常/中断屏蔽寄存器组注:只有在特权级下,才允许访问这3个寄存器。

注:寄存器BASEPRI的有效位数受系统中表达优先级的位数影响,如果系统中只使用3个位来表达优先级,则BASEPRI有意义的值仅为0x00、0x20、0x40、0x60、0x80、0xA0、0xC0和0xE0使用MRS/MSR指令访问这三个寄存器,比如:MRS R0, BASEPRI ;读取BASEPRI到R0中MSR BASEPRI, R0 ;将R0数据写入到BASEPRI中为了快速的开关中断,CM3还专门设置了一条CPS指令,有四种用法:CPSID I ;PRIMASK=1,关中断CPSIE I ;PRIMASK=0,开中断CPSID F ;FAULTMASK=1,关异常CPSIE F ;FAULTMASK=0,开异常CMSIS-M3微控制器软件接口标准中的core_cm3.h给出了开关中断或异常的函数:1.1 开/关中断1:/**2: * @brief Set the Priority Mask value3: *4: * @param priMask PriMask5: *6: * Set the priority mask bit in the priority mask register7: */8:static __INLINE void __set_PRIMASK(uint32_t priMask)9: {10:register uint32_t __regPriMask __ASM("primask");11: __regPriMask = (priMask);12: }使用__set_PRIMASK(1)关闭中断;__setPRIMASK(0)开启中断。

CortexM3嵌入式系统开发STM32单片机体系结构、编程与项目实

内容摘要

在软件编程方面,本书不仅介绍了基于Cortex-M3的汇编语言编程和C语言编程方法,还深入讲 解了STM32的固件库开发、中断服务程序编写、多任务处理等关键技术。书中还通过丰富的实例 和案例,展示了如何在STM32上实现各种典型应用,如串口通信、定时器应用、ADC和DAC转换、 PWM波形生成等。

接下来,目录转向了编程方面的内容。它详细阐述了使用C语言和汇编语言进 行STM32单片机编程的方法,包括常用的编程接口、库函数以及编程技巧。这 些内容对于提升开发者的编程能力,特别是针对嵌入式系统的编程能力,具有 重要的指导意义。

目录还涉及了多个实际项目的开发实例。这些项目实例涵盖了从简单的LED闪 烁到复杂的通信协议实现等多个方面,不仅展示了STM32单片机的强大功能, 也为读者提供了宝贵的实践经验。通过学习和实践这些项目,读者可以更加深 入地理解Cortex-M3和STM32单片机的应用技巧,提升自己的项目开发能力。

CortexM3嵌入式系统开发STM32单片 机体系结构、编程与项目实

读书笔记

01 思维导图

03 精彩摘录 05 目录分析

目录

02 内容摘要 04 阅读感受 06 作者简介

思维导图

本书关键字分析思维导图

系统

项目

stm32

体系

开发

stm32

m3 cortex

实践

读者

嵌入

结构

单片机

单片机

体系

编程

应用

该书的目录结构清晰、逻辑严密,从基础知识到高级应用,层层递进,让读者 能够循序渐进地掌握Cortex-M3和STM32单片机的开发技巧。

目录的开头部分,详细介绍了Cortex-M3的体系结构和STM32单片机的硬件特 性。这部分内容对于初学者来说非常重要,它帮助读者建立起对Cortex-M3和 STM32单片机的基本认识,为后续的学习打下坚实的基础。

Cortex-M3中断响应和中断返回过程分析

一、中断/异常响应当CM3开始响应一个中断时,它的内部会依次自动地进行以下三个操作:●入栈:把8个寄存器的值压入栈。

●取向量:从向量表中找出对应的服务程序入口地址。

●选择堆栈指针MSP/PSP,更新堆栈指针SP,更新连接寄存器LR,更新程序计数器PC。

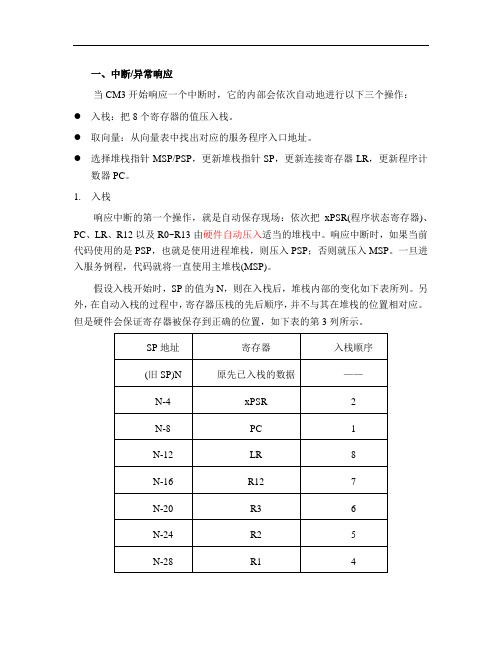

1.入栈响应中断的第一个操作,就是自动保存现场:依次把xPSR(程序状态寄存器)、PC、LR、R12以及R0~R13由硬件自动压入适当的堆栈中。

响应中断时,如果当前代码使用的是PSP,也就是使用进程堆栈,则压入PSP;否则就压入MSP。

一旦进入服务例程,代码就将一直使用主堆栈(MSP)。

假设入栈开始时,SP的值为N,则在入栈后,堆栈内部的变化如下表所列。

另外,在自动入栈的过程中,寄存器压栈的先后顺序,并不与其在堆栈的位置相对应。

但是硬件会保证寄存器被保存到正确的位置,如下表的第3列所示。

表1 入栈顺序以及入栈后堆栈内容先保存PC与xPSR的值,就可以更早地启动服务例程指令的预取;同时,也可以做到在早期更新xPSR中IPSR位段的值。

至于为何保存R0~R3和R12的值,则是根据ARM的C函数调用标准约定(AAPCS,Ref5):它使得中断服务例程能用C语言编写,编译器优先使用入栈的寄存器来保存中间结果。

2.取向量当数据总线正在为入栈操作而忙得风风火火时,指令总线则正在为响应中断紧张有序地执行另一项重要的任务:从向量表中找出正确的中断向量,然后在服务程序的入口处预取指。

由此可以看到各自都有专用总线的好处:入栈和取指可以同时进行。

3.更新寄存器入栈和取向量操作完成后,在执行服务例程之前,还要更新一系列寄存器。

SP:入栈后堆栈指针(PSP或MSP)更新到新的位置。

执行服务例程时,将由MSP负责对堆栈的访问。

PSR:更新IPSR位段(PSR的最低部分)的值更新为新响应的中断编号。

PC:取向量完成后,PC指向服务例程的入口地址。

LR:在出入ISR的时候,LR的值将被重新诠释,这种特殊的值称为“EXC_RETURN”,该值在中断进入时由系统计算并赋给LR,并在中断返回时使用它。

ARMCortex-M3权威指南-中断和异常(2)

ARMCortex-M3权威指南-中断和异常(2)中断和异常它⽀持16-4-1=11 种系统异常(同步)(保留了 4+1 个档位),外加 240 个外部中断输⼊(异步)。

在 CM3 中取消了 FIQ 的概念(v7 前的ARM 都有这个 FIQ,快中断请求),这是因为有了更新更好的机制——中断优先级管理以及嵌套中断⽀持,它们被纳⼊ CM3 的中断管理逻辑中。

因此,⽀持嵌套中断的系统就更容易实现 FIQ。

虽然 CM3 是⽀持 240 个外中断的,但具体使⽤了多少个是由芯⽚⽣产商决定。

CM3还有⼀个NMI(不可屏蔽中断)输⼊脚。

当它被置为有效(assert)时, NMI 服务例程会⽆条件地执⾏。

NMI 究竟被拿去做什么,还要视处理器的设计⽽定。

在多数情况下, NMI 会被连接到⼀个看门狗定时器,有时也会是电压监视功能块,以便在电压掉⾄危险级别后警告处理器。

向量表当 CM3 内核响应了⼀个发⽣的异常后,对应的异常服务例程(ESR)就会执⾏。

为了决定 ESR 的⼊⼝地址, CM3 使⽤了“向量表查表机制”。

这⾥使⽤⼀张向量表。

向量表其实是⼀个 WORD(32 位整数)数组,每个下标对应⼀种异常,该下标元素的值则是该 ESR 的⼊⼝地址。

向量表在地址空间中的位置是可以设置的,通过 NVIC 中的⼀个重定位寄存器来指出向量表的地址。

在复位后,该寄存器的值为 0。

因此,在地址 0 处必须包含⼀张向量表,⽤于初始时的异常分配。

举个例⼦,如果发⽣了异常 11(SVC),则 NVIC 会计算出偏移移量是11x4=0x2C,然后从那⾥取出服务例程的⼊⼝地址并跳⼊。

要注意的是这⾥有个另类: 0 号类型并不是什么⼊⼝地址,⽽是给出了复位后MSP 的初值。

CM3允许向量表重定位即从其它地址处开始执⾏各异常向量。

这些地址对应的区域可以是代码区,但也可以是 RAM 区。

在 RAM区就可以修改向量的⼊⼝地址了。

为了实现这个功能, NVIC中有⼀个寄存器,称为“向量表偏移量寄存器”(在地址 0xE000_ED08 处),通过修改它的值就能定位向量表。

cortexM3

姓名:黄常建班级:硕5106 学号:3115322009ARM微处理器cortex-M3简介前言:之所以会选这款微处理器是因为最近开发蓝牙应用时用到了Soc芯片TI的CC2650,里面包含了cortex-M3和cortex-M0两个微处理器,并且主要是对M3进行开发,所以针对自己之前所了解的信息以及网上的资料对cortex-M3进行一个简单的介绍。

概述:ARM公司于2006年推出了Cortex-M3内核,就在当年ARM公司与其他投资商合伙成立了luminary公司,由该公司率先设计、生产与销售基于Cortex-M3内核的ARM芯片-Stellaris系列ARM。

Cortex_M3内核是整个Cortex内核系列中的微控制器系列(M)内核,还有其他两个系列中的微控制系列(A)与实时控制处理系列(R),这三个系列又分别简称为A、R、M系列,当然这三个系列的内核分别有各自不同的应用场合。

A 部分面向复杂的尖端应用程序,用于运行开放式的复杂操作系统;R部分针对实时系统;M部分为成本控制和微控制器应用提供优化。

Cortex-M3是首款基于ARMv7-M架构的处理器,是专门为了在微控制器,汽车车身系统,工业控制系统和无线网络等对功耗和成本敏感的嵌入式应用领域实现高系统性能而设计的,它大大简化了可编程的复杂性,使ARM架构成为各种应用方案的上佳选择。

内核构架:基于ARMv7架构的Cortex-M3处理器带有一个分级结构。

它集成了名为CM3Core的中心处理器内核和先进的系统外设,实现了内置的中断控制、存储器保护以及系统的调试和跟踪功能。

这些外设可进行高度配置,允许Cortex-M3处理器处理大范围的应用并更贴近系统的需求。

目前Cortex-M3内核和集成部件已进行了专门的设计,用于实现最小存储容量、减少管脚数目和降低功耗。

Cortex-M3中央内核基于哈佛架构,指令和数据各使用一条总线。

与Cortex-M3不同,ARM7系列处理器使用冯·诺依曼架构,指令和数据共用信号总线以及存储器。

ARM CORTEX-M3 内核架构理解归纳

在我看来,Cotex-M3内核的主要包括:嵌套向量中断控制器(NVIC),取值单元,指令译码器,算数逻辑单元(ALU),寄存器组,存储器映射(4GB统一编址各区域功能的划分与界定),对于开发者而言,其实主要关注的主要分为三大块:1、寄存器组2、地址功能划分映射3、中断机制(NVIC)。

1)寄存器组Cortex-M3内核共有19组32位寄存器:R0——R12(通用寄存器);低寄存器组R0——R732位Thumb-2指令与16位Thumb指令均可访问高寄存器组R8——R1232位Thumb-2指令与极少数16位Thumb指令可访问R13(堆栈指针寄存器);主堆栈寄存器MSP(main-SP)/进程堆栈寄存器PSP(Process-SP)同一时间只能使用其中一个。

MSP供操作系统内核及中断(异常)处理子程序使用,PSP只供用户的应用程序代码使用(详细使用详见3、嵌套向量中断控制器(NVIC)的总结)。

堆栈指针是4字节对齐的,故最低两位永远是00;R14(连接寄存器)用于存储程序返回的地址及PC的返回地址;R15(程序寄存器)指向当前程序执行的地址;2)特殊功能寄存器组xPSR(程序状态字寄存器组),32位,可分为三个寄存器分别进行访问,也可以PSR或xPSR 的名字直接组合访问。

应用程序PSR(APSR)中断号PSR(IPSR)执行PSR(EPSR)中断屏蔽寄存器PRIMASK 单一比特位,置位后,除NMI与硬fault外,其他中断都不响应;FAULTMASK 单一比特位,置位后,除NMI外,其他中断都不响应;BASEPRI 共有9位,中断号小于等于该寄存器设置值的中断都不响应;控制寄存器controlControl[0] 0决定特权级线程模式;1用户级线程模式;Control[1] 0主堆栈;1进程堆栈;控制寄存器只能在特权级模式下改写,handler模式永远是特权级,且只允许使用主堆栈MSP 复位后,处理器进入特权级+线程模式下;2、地址功能划分映射Cortex-m3是一个32位处理器,其地址总线、数据总线都是32位的,故可在4G的地址范围上资源寻址。

cortex-m3中断系统结构

cortex-m3中断系统结构Cortex-M3中断系统结构是一个重要的主题,它涉及到处理器的核心功能之一。

Cortex-M3处理器的中断系统结构包括中断向量表、中断优先级和中断控制器三个主要方面。

首先,让我们来谈谈中断向量表。

Cortex-M3处理器使用中断向量表来存储中断服务程序的入口地址。

当发生中断时,处理器会根据中断号从中断向量表中找到对应的中断服务程序的入口地址,并跳转到该地址开始执行中断服务程序。

中断向量表通常位于处理器的起始地址处,每个中断都有一个固定的位置,以便处理器能够快速找到对应的中断服务程序。

其次,中断优先级是Cortex-M3中断系统结构中的另一个重要方面。

Cortex-M3处理器支持多级中断优先级,允许开发人员为不同的中断设置不同的优先级。

这样可以确保在多个中断同时发生时,处理器能够按照优先级顺序来响应中断,以保证关键的中断能够及时得到处理。

最后,中断控制器是Cortex-M3中断系统结构的第三个方面。

中断控制器负责管理中断的使能、屏蔽和清除操作。

它还负责处理中断的优先级和中断请求的响应顺序。

Cortex-M3处理器的中断控制器通常具有灵活的配置选项,可以根据应用需求进行调整。

总的来说,Cortex-M3处理器的中断系统结构包括中断向量表、中断优先级和中断控制器三个主要方面,这些方面共同构成了处理器对中断的管理和响应机制。

对于嵌入式系统开发者来说,深入理解Cortex-M3中断系统结构是非常重要的,可以帮助他们更好地设计和实现中断服务程序,提高系统的稳定性和可靠性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Cortex-M3中断服务程序设计

ISR是嵌入式应用系统获取各种事件的基本手段。

而事件是实时性问题的讨论基础和事件计算的起点。

中断优先级

不同中断服务程序应有不同优先级,在允许中断嵌套时,最高优先级的中断总是能够得到响应。

只要没关中断,ISR可以中断任何任务的运行,比最高优先级的任务还要高。

Cortex-M3中断资源

抢占优先级:实现中断嵌套

子优先级:当抢占优先级相同的两个中断同时发生时,子优先级高的中断可以首先获得运行权。

中断优先级安排原则

紧迫性:触发中断的事件允许耽误的时间越短,优先级越高。

关键性:触发中断的事件越关键,越高

频繁性:触发中断的事件发生越频繁,越高

快捷性:前三项相近,ISR处理越快,越高。

ISR功能应尽量简单,只要将获取的异步事件用通信手段发给关联任务就行,后续处理由关联任务完成。

1. 中断服务程序设计

ISR结构

4部分

A:使os掌握当前中断的嵌套深度。

B:ISR功能代码。

必须调用系统通信服务函数,与其他任务进行通信。

正是这种通信功能是关联任务得到同步信号或数据,从而进入就绪状态。

不允许调用延时函数和可能被挂起的系统服务函数。

C:清除该中断的相应标志。

以便下次再次相应。

不用ISR函数,中断源的中断相应标志不同,清除中断标志的代码也不同。

D:调用退出中断函数。

实现任务调度功能。

判断是返回中断(中断嵌套)还是返回任务(原任务还是更高级任务)

选择与关联任务的通信手段

两种类型:

A:信号型。

ISR只完成发送信号量的工作。

表示事件发生,通过信号量的同步功能出发关联任务,所有具体工作由任务完成。

B:数据型。

ISR需要完成信息采集工作,然后使用消息邮箱(消息队列)将数据发送给关联任务,由关联任务完成后续数据处理工作。

细分如下:

A:触发ISR事件不包含数据。

用信号量与关联任务通信。

B:触发ISR事件包含数据低频事件。

用信号量与关联任务通信。

采集任务放在关联任务中。

C:触发ISR事件包含数据中高频事件。

ISR采集数据。

ISR中使用消息邮箱与关联任务通信。

关联任务完成后续工作。

D:触发ISR事件包含数据非周期高频事件。

ISR采集数据,ISR中使用具有数据缓冲功能的消息队列与关联任务通信。

例子。