一种基于FPGA的高速误码测试仪的设计

最新-一种基于FPGA的误码性能测试方案 精品

一种基于FPGA的误码性能测试方案摘要提出了一种基于的误码测试方案,并简要介绍了该方案的设计思想。

关键词误码仪数字微波传输1系列在数字通信系统的性能测试中,通常使用误码分析仪对其误码性能进行测量。

它虽然具有简单易用、测试内容丰富、误码测试结果直观、准确等优点,但是,价格昂贵、不易与某些系统接口适配,通常需要另加外部辅助长线驱动电路;此外,误码分析仪对于突发通信系统的误码性能测试存在先天不足。

例如,在对系统上行链路误码性能测试时,只有通过外加接口,对连续数据进行数据压扩,才能为被测设备模拟出突发形式的数据,从而完成测试。

这给测试工作带来极大的不便。

另一方面,现今的通信系统大量采用作为系统的核心控制器件。

将物理层上的各协议层的功能集中在内部实现,不仅提高了通信系统的集成,同时也减少了硬件和软件设计的复杂度。

基于上述两方面的考虑,笔者在内部实现了一个简易的多功能误码分析仪。

该误码仪主要有三方面优点一是可以根据用户需要,以连续或突发的方式产生若干种不同的随机序列或固定序列,并据此测试数字通信系统的误码性能;二是测试结果可以误码率或者误码数两种形式,通过外围器件直观地显示出来;三是作为被测系统的一个嵌入式模块,便于功能扩展及系统调试。

1伪随机序列序列许多数字通信理论的结论都基于这样一个假设原始的信源信号为0、1等概并相互独立的随机数字序列。

同样,实际数字通信系统的设计,也是基于相同假设。

因此,为使测试结果尽可能真实地反映系统的性能,采用伪随机序列序列作为测试中传输的信号。

序列是一种线反馈移位寄存器序列,其原理方框图如图1所示。

每级移位寄存器的输出被反馈系数加权可以取1或0,经模2和运算再反馈到第一级。

令第一级的输入为,就有根据反馈系数的取值不同,电路可以产生出各种具有不同特性的数字序列。

对于一定的移位寄存器级数,存在一些特殊的取值,使得输出序列的周期达到最长,即为2-1。

这样的序列被称为最长线性反馈移位寄存器序列,即序列。

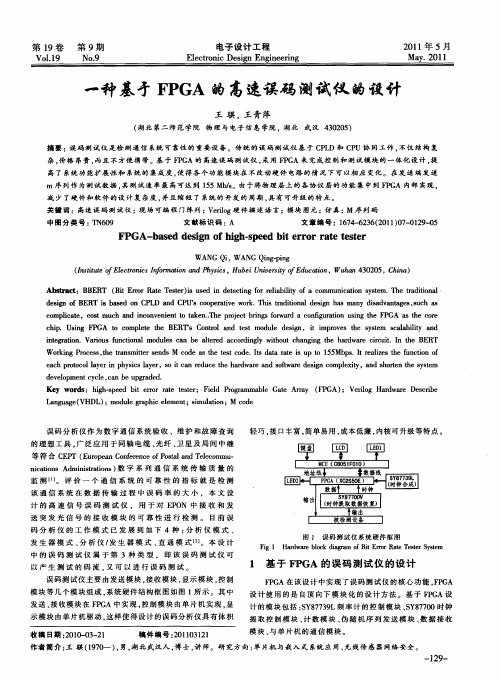

一种基于FPGA的高速误码测试仪的设计

据设置 的参数合 成相 应的频 率。具体 合成 哪一个 , F G 由 PA

来 实 现 对 S 7 3 L的 控 制 。 Y87 9

该 模 块 还 要 实 现 F G 读 取 S 8 7 0 的 功 能 . 以 确 定 PA Y 7 0 ̄

S 70V是否 完成 时钟提 取及 数据恢 复 。根据 S 870 Y87 o Y 70 V 的 工 作 原 理 ,可 以用 硬 件 语 言 V ro 编 写 程 序 在 F G 实 e lg i PA

发送 、 收模块在 F G 中实现 , 制模块 由单片机实 现 , 接 PA 控 显 示 模 块 由 单 片 机 驱 动 . 样 使 得 设 计 的 误 码 分 析 仪 具 有 体 积 这

收稿 日期 :0 0 0 — 1 2 1 - 3 2 稿 件 编 号 :0 1 3 2 2 10 1 1

输 输出

码 分 析 仪 的 工 作 模 式 已 发 展 到 如 下 4种 : 析 仪 模 式 、 分 发 生 器 模 式 、 析 仪 , 生 器 模 式 、 通 模 式 [。 本 设 计 分 发 直 2 1

中 的 误 码 测 试 仪 属 于 第 3 种 类 型 。 即 该 误 码 测 试 仪 可 以产 生 测 试 的 码 流 . 可 以进 行 误 码 测 试 。 又

m 序 列 作 为 测 试数 据 , 测 试 速 率 最 高 可达 到 15Mbs 其 5 /。由 于将 物 理 层 上 的各 协 议 层 的 功 能 集 中 到 F G 内部 实现 . PA 减 少 了硬 件 和 软 件 的 设 计 复 杂 度 , 并且 缩短 了 系统 的 开发 的 周 期 , 有 可 升 级 的特 点 。 具 关键 词 :高速 误 码 测 试 仪 ; 场 可 编 程 门阵 列 ; e l 现 V ro i g硬 件 描 述 语 言 ; 块 图元 ; 真 ; 序 列码 模 仿 M 中 图分 类 号 : N O T 69 文献标识码 : A 文 章 编 号 :17 — 2 6 2 1 )7 19 0 6 4 6 3 (0 10 - 2 — 5 0

基于FPGA的RS485接口误码测试仪的设计

基于FPGA的RS485接口误码测试仪的设计

摘要:介绍了一种基于FPGA 的误码测试仪的设计原理、实现过程及调试经验。

该误码测试系统使用RS485 接口,具有原理简单、接口独特、功能丰富等特点,系统具有较好的可扩展性。

在数字通信中,误码率BER(Bit Error Rate)是衡量通信系统质量的一项重要指标。

无论是设备故障、传播衰落、码间干扰、临近信道干扰等因素都可能造成系统性能恶化甚至造成通信中断,其结果都可通过误码的形式表现出来[1]。

因此,误码测试仪是现代通信系统的主要测试仪器之一。

目前,通常使用的传统误码测试仪虽然具有测试内容丰富、测试结果直观等优点,但是由于通信系统复杂程度的不断增加,接口形式变化多样以及一些非标准码率的应用,使得传统误码测试仪的使用受到了一定的限制。

另一方面,近年来FPGA 技术得到了迅速发展,使用FPGA 设计电路具有很大的灵活性,可以大大提高集成度和设计速度,还可以简化接口和控制,有利于提高系统的整体性能和工作可靠性。

本文即介绍了一种基于FPGA 的RS485 接口误码测试仪的设计和实现。

该设计具有系统简单、功能可靠、接口独特等特点,并且增加了传统误码测试仪所没有的测量系统传输延时的功能。

1 设计背景

本文所设计的误码测试仪主要用于测试某通信系统的误码性能。

该通信系统是一个庞大复杂的系统,本文主要介绍信道部分,包括基带的信道编解码和无线信道的收发,其基本框图如图1 所示。

为了在线路传输上保证良好的抗干扰能力,系统采用了RS485 接口,选用了4.096 Mb/s 的码率。

因此,为了测试图1 所示系统的误码性能,误码测试。

基于FPGA的高速误码测试系统设计.doc

1.系统组成原理数字通信系统的误码测试一般有近端测试和远端测试2种方式,如图1 (a)、(b)所7J\o(a)近端测试(单向)方式图(b)远端测试(环路)方式图图1数字通信系统的误码测试图1中误码测试发送部分与误码测试接收部分为误码测试系统的基本组成。

木文设计的误码测试发送和接收系统图分别如图2和图3所示。

时钟信号发生器—►码型产生与选择Tp吴码插入控制f输出接口电路图2误码测试发送系统图(3)误码测试接收系统误码测试发送部分主要由时钟信号发生器、伪随机码和人工•码发生器、误码插入发生器以及接曰电路组成它可以输出各种不同序列长度的伪随机码(从(2”7-1广(2'23-1)bit)和16bit的人工码,以满足ITU-T对不同速率的PCM系统所规定的不同测试用的序列长度。

它具有“0”码插入功能,并能发出带有10^3^10^-6误码率的数据,可用于检测被测设备和系统的承受能力和检测告警功能等。

接口电路用来实现输出CM 1码、HDB3 码、NRZ码和RZ码等码型,以适应符合ITU-T要求的被测电路的各种不同接口码型。

输出码型经被测信道或被测设备后,由误码测试接收部分接收,接收部分可产生一个与发送部分码发生器产生的图像完全相同的且严格同步的码型,并以此为标准,在比特比较器中与输入的图案进行逐比特比较。

被测设备产生的任何一个错误比特,都会被检出误码,并送误码计数器显示。

2.伪随机序列发生与自校验误码插入误码测试系统的工作码流是伪随机序列。

印序列具有B好的伪随机噪声性质,是在通信工程中被广泛应用的伪随机序列之一,本系统采用m序列发生器产生伪随机序列。

图4为『7的伪随机序列发生器结构。

伪随机序列发生器在2. 048MHz时钟信号的作用下产生序列长度为2^7-1=127的伪随机序列。

伪随机序列发生器部分VHDL源程序如下:library ieee;use ieee. std logic 1164. al;1 entitympsn7isport (elk: in std logic;load: in stdlogic;Q: out std logic);endmpsn7;architecture one ofmpsn7issignal cO, cl, c2, c3, c4, c5, c6, c7: std logic; beginprocess (elk, load)beginif (elk' eventand elk二'1! ) thenif (load='1! ) thenc7<=z (T ;c63 O';c5<=, 0z ;c4<=, O';c3<=z O';c2<=z O';cl<=, 0z ;coe r ;Q<=c7;elsecl<=cO;c2<=cl;c3<=c2;c4<=c3;c5<=c4;c6<=c5;c7<=c6;c0<=c7xor c4xor c3xor c2;Q<=c7;end if;end if;end process;end one;图(5)给出了在EP1K30TC144-3FPGA上实现VHDL伪随机序列发生器模块时序仿真结果。

基于FPGA的高速突发模式误码测试系统的设计与实现的开题报告

基于FPGA的高速突发模式误码测试系统的设计与实现的开题报告一、选题背景与意义随着各种信息技术的迅猛发展,高速通信系统已经成为了人们生活和工作中不可或缺的一部分。

而在这些高速通信系统中,比如数据通信、传感器网络等等,突发模式误码测试是一个重要的课题。

因为在实际的应用场景中,会出现瞬间的电磁噪声、信号干扰等情况,从而使得高速通信系统的信号质量出现异常,比如出现误码等。

因此,突发模式误码测试对于保证高速通信系统的可靠性至关重要。

现有的突发模式误码测试系统多采用软件实现,在测试速度和实时性上存在优化空间,并且软件实现需要CPU的干预,更容易受到CPU性能的限制。

因此,本课题尝试基于FPGA(Field Programmable Gate Array)器件,设计一种高速突发模式误码测试系统,能够提高测试速度和实时性。

二、研究内容与目标本课题的研究目标是设计并实现一种基于FPGA的高速突发模式误码测试系统。

具体的研究内容包括以下几个方面:(1)调研突发模式误码测试系统的基本原理和现有的测试方法;(2)研究FPGA技术的应用和原理,以及如何在FPGA上实现高速突发模式误码测试;(3)设计突发模式误码测试系统的硬件电路,包括信号输入输出、FPGA芯片放置、时序控制、误码检测等电路设计;(4)编写突发模式误码测试系统的软件程序,实现误码测试的参数设置、误码检测与数据存储等功能。

三、研究方法与技术路线本课题的研究方法主要是理论分析和实验研究相结合。

具体的技术路线如下:(1)首先,调研突发模式误码测试系统的基本原理和现有的测试方法,为后续的研究提供理论依据;(2)然后,研究FPGA技术的应用和原理,掌握如何在FPGA上实现高速突发模式误码测试;(3)接着,设计突发模式误码测试系统的硬件电路,包括信号输入输出、FPGA芯片放置、时序控制、误码检测等电路设计;(4)编写突发模式误码测试系统的软件程序,实现误码测试的参数设置、误码检测与数据存储等功能;(5)最后,根据实验数据进行误码测试结果的分析和实验优化,完善突发模式误码测试系统。

基于某FPGA误码检测器的设计与实现

基于FPGA误码检测器的设计与实现欧亚学院本科毕业论文(设计)开题报告题目基于FPGA误码检测器的设计与实现学生:*****学生学号:12610602150807指导教师:导师职称:所在分院:信息工程学院专业:通信工程班级:统本通信1201班提交日期:2015年12月21日备注:“指导教师意见”和“教研室意见”请在“□”打“√”表示。

摘要随着通信测试技术的发展,对测试仪器也提出了更高的要求。

要求测试仪器软件化、智能化。

而且由于通信技术的迅速发展,通信测试仪器的价格比较昂贵,所以要求仪器开发商要考虑到测试仪器的功能问题及仪器的成本问题。

另外,小型化和便携化的思想是通信测试仪器的两个重要发展趋势和方向。

鉴于网络通信监测具有移动性,要对同一通信网络不同测试点进行监测,对于测试点的物理距离比较远的通信网络,要求通信网络测试设备向小型化,便携化的两个方向发展。

手持式网络测试设备主要以现场施工以及运行维护使用为目的,不要求其测试功能的完善,但侧重于实用性和方便性。

误码测试仪主要基于FPGA技术,并且以方便,实用,经济三个方面为主要特点进行设计开发的。

它的核心器件是现场可编程逻辑阵列(FPGA),便于移植或者升级。

FPGA是目前应用比较广泛的可编程门阵列,如今很多数字通信系统都是用FPGA作为系统的核心控制器件,不仅使系统的集成度大大提高而且降低了硬件设计的复杂程度。

所以,采用FPGA作为智能误码仪的核心控制器件是比较合适的选择。

本论文在分析了误码仪工作原理的基础上,釆用FPGA等构建硬件平台,完成误码仪的功能。

用FPGA实现伪随机序列的收发和误码统计,然后通过数码管显示检测结果。

关键词:误码检测仪FPGA 伪随机码同步AbstractWith the rapid development of communication technology test, also put forward higher requirements for the test instrument. Requirement of intelligent instrument software. And because of the rapid development of communication technology, communication test instruments are expensive, the cost function and instrument so instrument developers to consider to test instruments. In addition, miniaturization and portability of the thought is the two important development trend and direction of communication testing instrument. In view of the network traffic monitoring with mobility, to monitor the same communication networks of different test points, for the physical distance between the test point is far from the communication network, communication network testing equipment to the miniaturization,portable two direction. The portable network test equipment to the main maintenance on-site construction and operation for the purpose, does not require the test function perfect, but focuses on the practicality and convenience. Intelligent error tester is mainly based on FPGA technology, and with convenient, practical, the three aspects of economy as the main characteristics of the design and development of the. It is the core component of field programmable logic array (FPGA), easy to transplant or upgrade. FPGA is widely used programmable gate array, now a lot of digital communication system is using FPGA as the core of the system control device,not only the system integration degree greatly improve and reduce the complexity of the hardware design. So, using FPGA as the core control device of intelligent error tester is a suitable choice.In this paper, based on the analysis of the principle of the error code, using FPGA,processor and other hardware platform to complete the function of the error tester. FPGA implementation of the pseudo random sequence of transceiver and error statistics,and then through the digital tube display detection results.Key Words : Error detecting instrument FPGA Pseudo random code Synchronization目录摘要 (I)Abstract .......................................................................................................................... I I 1.绪论 ........................................................................................................................- 1 -1.1研究目的及意义 .........................................................................................- 1 -1.2国外研究现状 .............................................................................................- 1 -1.3本课题主要要求容 .....................................................................................- 2 -2.系统的总体方案设计 ............................................................................................- 4 -2.1 EDA与VHDL介绍 .......................................................................................- 4 -2.1.1 FPGA发展历程.................................................................................- 4 -2.1.2 VHDL语言介绍.................................................................................- 6 -2.2总体方案设计, .........................................................................................- 7 -2.2误码率测试基本原理 .................................................................................- 7 -2.3伪随机序列的原理及特点 .........................................................................- 8 -2.4硬件电路设计方案选择 .......................................................................... - 10 -3.功能设计 ............................................................................................................. - 11 -3.1基本功能设计 .......................................................................................... - 11 -3.1.1伪随机码型发生单元设计 ........................................................... - 12 -3.1.2误码插入单元 ............................................................................... - 12 -3.1.3误码检测单元设计 ....................................................................... - 13 -3.1.4同步模块 ....................................................................................... - 14 -3.1.5显示模块 ....................................................................................... - 15 -3.1.6模拟信道模块 ............................................................................... - 18 -3.2 顶层电路的设计 ..................................................................................... - 19 -4.功能的仿真和验证 ..............................................................................................- 20 -4.1仿真验证 ...................................................................................................- 20 -4.1.1伪随机码型发生单元设计 ....................................................................- 20 -4.1.2误码插入单元和模拟信道模块 ............................................................- 20 -4.1.3误码检测单元设计 ................................................................................- 20 -4.1.4同步模块 ............................................................................................... - 21 -4.1.5显示模块 ............................................................................................... - 21 -4.2整体仿真图 .............................................................................................. - 21 -4.3FPGA验证.................................................................................................. - 21 -5.结论 ..................................................................................................................... - 23 -参考文献................................................................................................................. - 24 -致谢..........................................................................................................................- 25 -1.绪论1.1研究目的及意义在当今的信息时代,通信在我们生活中必不可少。

国产FPGA高速串行接口误码率测试软件设计

国产FPGA高速串行接口误码率测试软件设计

李卿;段辉鹏;惠锋

【期刊名称】《电子与封装》

【年(卷),期】2024(24)5

【摘要】随着内嵌高速串行接口FPGA的广泛应用,其信号质量的监测变得极为重要。

设计了1种基于国产FPGA芯片的高速串行接口误码率测试软件,采用软核实现高速串行接口误码率统计、属性动态重配置,利用上位机软件进行实时监测,有效地提高了测试效率。

通过实际用例详述了软件进行误码率测试的方法与步骤,进而验证了该软件测试的有效性。

研究结果表明,该软件具有较好的用户体验度、较高的测试效率,对FPGA国产化进程起到了积极的推动作用。

【总页数】6页(P59-64)

【作者】李卿;段辉鹏;惠锋

【作者单位】无锡中微亿芯有限公司

【正文语种】中文

【中图分类】TN402

【相关文献】

1.基于FPGA的高速并行光通信误码率测试系统

2.基于FPGA和高速串行接口AD 转换器AD7476的接口应用

3.串行通信接口卡驱动及测试软件设计和实现

4.基于FPGA的高速误码率测试仪的硬件设计

5.FPGA在高速位误码率测试仪中的应用

因版权原因,仅展示原文概要,查看原文内容请购买。

一种基于FPGA的新型误码测试仪的设计与实现

一种基于FPGA的新型误码测试仪的设计与实现摘要:本文设计实现了一种用于测量基带传输信道的误码仪,阐述了主要模块的工作原理,提出了一种新的积分鉴相同步时钟提取的实现方法,此方法能够提高同步时钟的准确度,从而提高误码测量精度。

关键词:误码测试仪;FPGA ;鉴相器;数字锁相环引言误码仪是评估信道性能的基本测量仪器。

本文介绍的误码仪结合FPGA 的特点,采用全新的积分式鉴相结构,提出了一种新的误码测试方法,经多次测试验证,方案可行,设计的系统稳定。

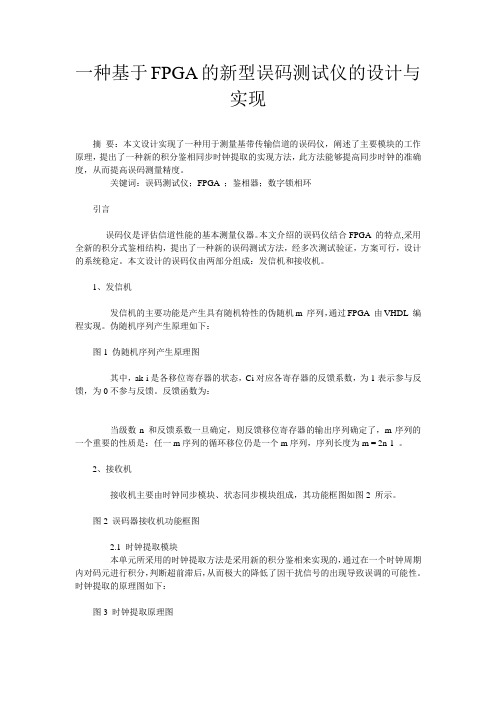

本文设计的误码仪由两部分组成:发信机和接收机。

1、发信机发信机的主要功能是产生具有随机特性的伪随机m 序列,通过FPGA 由VHDL 编程实现。

伪随机序列产生原理如下:图1 伪随机序列产生原理图其中,ak-i是各移位寄存器的状态,Ci对应各寄存器的反馈系数,为1表示参与反馈,为0不参与反馈。

反馈函数为:当级数n 和反馈系数一旦确定,则反馈移位寄存器的输出序列确定了,m序列的一个重要的性质是:任一m序列的循环移位仍是一个m序列,序列长度为m = 2n-1 。

2、接收机接收机主要由时钟同步模块、状态同步模块组成,其功能框图如图2 所示。

图2 误码器接收机功能框图2.1 时钟提取模块本单元所采用的时钟提取方法是采用新的积分鉴相来实现的,通过在一个时钟周期内对码元进行积分,判断超前滞后,从而极大的降低了因干扰信号的出现导致误调的可能性。

时钟提取的原理图如下:图3 时钟提取原理图(1 )鉴相器导前- 滞后型数字鉴相器的特点是,它输出一个表示本地估算信号超前或滞后于输入信号的量.如果本地估算信号超前于输入信号,则输出“超前脉冲”, 以便利用该“超前脉冲”控制本地估算信号的相位推后。

反之,则输出“滞后脉冲”,并使本地估算信号的相位前移. 导前- 滞后型数字鉴相器可分为微分型和积分型两种.由于积分型导前- 滞后数字鉴相器,具有优良的抗干扰性能. 因此本设计采用了积分型导前-滞后型数字鉴相器.积分型导前-滞后型数字鉴相器中,本地时钟的上升沿为同相积分的清洗时刻,上升沿到来时,在本地高频时钟下,同相计数器开始计数,当输入码元是“1”时,每来一高频脉冲计数器加1计数,当输入码元是“0”时,每来一高频脉冲计数器减1计数。

基于FPGA的误码测试仪的设计

基于FPGA的误码测试仪的设计

张蕴玉;田俊

【期刊名称】《自动化与仪表》

【年(卷),期】2005(020)006

【摘要】误码测试仪是评估系统传输性能的基本仪器.提出了一种基于FPGA的误码测试仪的设计方案,在Altera公司的FLEX10K10芯片上实现了其功能.先介绍了误码测试仪的基本工作原理,再从逻辑结构入手,介绍各模块的功能,并简要介绍了其实现方法.

【总页数】4页(P23-26)

【作者】张蕴玉;田俊

【作者单位】华中科技大学,电子与信息工程系,湖北,武汉,430074;华中科技大学,电子与信息工程系,湖北,武汉,430074

【正文语种】中文

【中图分类】TP216;TN914

【相关文献】

1.基于FPGA的RS485接口误码测试仪的设计和实现 [J], 杨洪军;刘永亮

2.基于DSP和FPGA的开环多码型误码测试仪的设计 [J], 王辉;周志权;赵占锋

3.基于FPGA的FSO通信误码测试仪的设计 [J], 闫思家;彭仁军;高建双;冯波

4.一种基于FPGA的高速误码测试仪的设计 [J], 王骐;王青萍

5.基于FPGA的串行自适应误码测试仪设计 [J], 钟鸣;江洁;华伊;魏祎;陆卫强

因版权原因,仅展示原文概要,查看原文内容请购买。

基于FPGA的FSO通信误码测试仪的设计

21 0 1年 1 0月

电 子 器 件

C i ee Ju lo lcrn De ie hn s o ma f e t vc s E o

Vo . 4 No 5 13 .

0c .2 1 t 01

De in o sg fBER se s d o Te t r Ba e n FPGA o O m m un c t n f r FS Co ia i o

Y N ia, E ejn G O Ja su n F NG B A S i P NG R nu , A inh a g, E o j

(colfO t l t n nom t n U i rt lt nc c nea dTcnlg hn , h “6 0 5 , hn ) Sh o o po e r i I r ai , nv syo Ee r iSi c n eh ooyo C ia C e eco c f o ei f co e f 10 4 C ia

ቤተ መጻሕፍቲ ባይዱ

基于 FG P A的 F O通 信 误 码 测试 仪 的设计 S

闫思家 , 彭仁军 , 高建双 , 冯 波

( 电子科技大学光 电信息 学院 , 成都 60 5 ) 10 4

摘 要 : 提出了一种基于 F G P A的 FO通信误码测试方案。该方案中。 S 误码测试主要是由伪随机序列发生模块、 同步模块、

误码 统计模块 以及 L D显示模块来实现 , C 对这些模 块进行了详细 的论述 。误码测试 的关键技术之一是 比特 同步 , 该方案利 用 FF IO实 现误 码仪 内部数据与接收数据之 间的同步 。利用该方案研制 了一 套 1 bts的误码测试仪 。大量实验 表明 , 0M i / 所研 制 的误 码仪性能稳定可靠 , 证实 了设计 方案的可行性 。目前该误码测试仪 已成功应用于 F O通信系统并交付用户使用 。 S

基于FPGA的误码分析仪设计

基于FPGA的误码分析仪设计摘要:为了设计出基于FPGA的误码分析仪,选用以STC10F08XE单片机为主控制器、以EP1C3T144C8N芯片为误码检测、USART GPU串口屏为显示和控制以及EPCS和MAX232为下载程序,完成了整个硬件系统的设计。

并在整个硬件系统实现的基础上,进行了M序列的产生、数据同步实现、误码监测统计以及液晶显示控制等相关实验。

结合硬件电路以及实现的功能设计了各个功能模块的软件流程图,并结合流程图编写了各个模块的实现程序,然后结合硬件完成了联合调试,最终实现了系统的预期功能。

关键词:误码分析仪;FPGA;M序列;STC10F08XE中图分类号:TN911 文献标识码:A 文章编号:2095-1302(2016)07-00-040 引言在通信系统中,由于信号在传输过程中衰变引起信号电压的变化,导致信号在传输过程中遭到破坏,产生误码。

误码分析仪便是测试误码率的测试仪器,本文旨在通过误码分析仪模块的设计来深入了解其原理及使用方法[1]。

1 总体方案设计1.1 系统需求分析系统使用FPGA和单片机共同控制的方式,使系统具有很高的集成度,并且方便扩展和升级。

经过调研和讨论分析,整个设计的基本功能包括如下几部分[2]:(1)八种测试速率可调:1 K/10 K/100 K/500 K/1 M/2 M/5 M/10 M速率;(2)三种测试码型可选:9位、15位、23位伪随机序列码;(3)误码率的统计和计算;(4)误码的发送、接收、同步以及手动插入误码的设计;(5)TFT-LCD彩屏显示和触摸按键的控制;(6)单片机与TFT-LCD的通信设计;(7)误码测试仪的菜单显示设计;(8)外部指示系统的设计;(9)时钟锁相环设计。

1.2 系统设计方案误码分析仪系统分为硬件设计和软件设计两部分。

选用FPGA芯片实现误码的测试,采用Verilog硬件描述语言通过EDA软件设计外围电路和必要的功能。

基于FPGA的两种误码仪实现方法设计

基于FPGA的两种误码仪实现方法设计刘浩;刘睿强;卢静【期刊名称】《微型机与应用》【年(卷),期】2014(33)15【摘要】设计了一种基于 EPF10KRC208-4的误码仪,该设计充分利用了 FPGA 强大的可编程能力和丰富的资源,以及软件开发平台Quartus Ⅱ的完备功能,具有体积小巧、携带方便、测量精确等优点。

其核心部分分别采用了逐位比较法和移位寄存器法,并在仿真过程中设置了多种误码情况进行对比。

最后,根据仿真结果分析了方案的可行性和两种方法的优缺点。

%A kind of BERT basedEPF10KRC208-4 is provided in the paper with full use of programmability and rich resources of FPGA, and the complete functions of Quartus Ⅱ software development platform. It′s compact, easy to carry and has excellent accurate. The core part is developed by using a bit-by-bit comparison method and the shift register, and various bit error cases are compared in the simulation process. Finally, the analysis of the feasibility and the advantages and disadvantages of the two methods are provided according to the simulation results.【总页数】4页(P50-53)【作者】刘浩;刘睿强;卢静【作者单位】重庆电子工程职业技术学院应用电子学院,重庆 401331;重庆电子工程职业技术学院应用电子学院,重庆 401331;重庆电子工程职业技术学院应用电子学院,重庆 401331【正文语种】中文【中图分类】TP216【相关文献】1.基于FPGA的基带信号误码测试仪的设计与实现 [J], 孙增友;李亚军;刘瑞;侯亮;王瑶宝2.基于FPGA的误码仪设计与实现 [J], 陈小敏;朱秋明;虞湘宾;孟田珍3.基于FPGA的误码仪IP核的设计与实现 [J], 潘勇;袁慧梅;侯长宏4.基于FPGA的RS485接口误码测试仪的设计和实现 [J], 杨洪军;刘永亮5.基于FPGA的误码检测仪设计与实现 [J], 吴晓晶;成卫忠因版权原因,仅展示原文概要,查看原文内容请购买。

基于FPGA的误码仪设计与实现

e ro r t e s t e r , a s a t o o l t o t e s t t h e r e l i a b i l i t y o f a c o mmu n i c a t i o n s y s t e m, i s wi d e l y u s e d i n t h e p r o d u c t i o n , t e s t i n g , i n s p e c t i n g a n d ma i n t e n a n c e

摘 要 :误码率是评价数据传 输设备及其信道工作质量 的一个重要指标 ,而误码 仪作为通信系统的可靠性测量工 具,广泛 用于传输设备 的生产调试 、检验 以及 日常维护维修 ,旨在完成一个 高斯 衰落信道 下数字基带系统的实现及其误码率性 能的 测试 。借助F P GA实验平 台,通过v r i l o g 语言在F P GA, …片上编程 以实现数字 基带信号 的产 生、星座映射 、基带成 型、信 o 道 、匹配滤波、判决、解映射、误码 计算等模块 ,并通过F P G A的数码管显示误码率。 关键词:通信系统 误码仪 F P GA Ma t l a b

of t r a ns mi s s i o n e qu i pm e nt .I n t hi s pa p e r , a bi t e ro r t e s t e r or f di gi t a l b a s e b a n d c o mmu n i c a t i on s y s t e ms o v e r Ga u s s i a n f a di n g c h a nn e l i s

d e s i g n e d , a n d t h e c o re s p o n d i n g t e s t o f b i t e r r o r r a t e( B ER) p e r f o r ma n c e c a n b e r e a l i z e d . By me a n s o f F P GA e x p e r i me n t p l a t f o r m, t h e

高速突发模式误码测试仪的FPGA实现方案

t c in i o uc e e to sc nd t d;m or o er urn rorbisde e ton,t e r c ie u tfle he p e b ea e i ie nd ge se r t t ts e v ,d ig e r t t ci h e ev rm s it rt r am l nd d lm t ra t rorbis sa i—

pr c i a l . a tc lva ue

Ke o d y w r s: b s — o om m u c ton BER e t r; l c xta t Ro ke l GTP r ns eve ur tm de c nia i s; t s e co k e r c ; c t O ta c i r

一

种 基 于 F GA 实现 的 高速 突发 模 式 误 码 测 试 仪 设 计 方 案 , 介 绍 该 方 案 的 总 体 设 计 过 程 , 及 F GA 中主 要 功 能 逻 P 并 以 P

辑模 块 的 工 作 原理 和控 制 系统 的 设 计 。 该 测 试 仪 应 用 于 1 2 . 5 GHzGP ON 系统 突发 式 光 接 收 模 块 的误 码 测 试 中 , 有 具

S n Le u u  ̄ n,Hu C h i i u ,Ma C a ho

( ho lofI f m a i Sc o n or ton Eng n e i g,W u n U ni r iy ofTe hnoog i e rn ha ve st c l y,W u n 63 70,Chi ) ha 00 na Ab tac :Beng dif r ntfom e r lc ntnu ld t te m sr t i fe e r g ne a o i a — a a s r a BER e t r t e e ev r o r tm o t s e , h r c ie f bu s — de BER e t r i e uie o e t a t t s e s r q r d t x r c

基于FPGA的误码仪设计与实现

基于FPGA的误码仪设计与实现作者:陈小敏朱秋明虞湘宾孟田珍来源:《中国现代教育装备·高教》2013年第02期摘要:误码率是评价数据传输设备及其信道工作质量的一个重要指标,而误码仪作为通信系统的可靠性测量工具,广泛用于传输设备的生产调试、检验以及日常维护维修,旨在完成一个高斯衰落信道下数字基带系统的实现及其误码率性能的测试。

借助FPGA实验平台,通过Verilog语言在FPGA芯片上编程以实现数字基带信号的产生、星座映射、基带成型、信道、匹配滤波、判决、解映射、误码计算等模块,并通过FPGA的数码管显示误码率。

关键词:通信系统误码仪 FPGA Matlab在数字通信系统中,通常使用误码分析仪对系统的误码性能进行测量,并以此来判断该系统的性能优劣。

因为误码分析仪有丰富的测试接口和测试内容,能将结果直观、准确地显示出来而得到广泛应用,并为工程实际应用带来极大便利。

但是由于通用误码仪价格昂贵,并且通常需要另加外部辅助长线驱动电路才能与某些系统接口适配而严重制约了它在实际中的应用。

基于工程的需要,并考虑到实际应用中的困难,提出一个基于FPGA的多功能误码测试方案,借助FPGA实验平台、Verilog语言在FPGA芯片上通过编程实现数字基带信号的产生、星座映射、基带成型、信道、匹配滤波、判决、解映射、误码计算等模块,并通过FPGA的数码管显示误码率[1,2]。

1 数字基带系统无线信道的广泛应用,使得无线衰落信道下数字基带系统的误码性能研究具有更重要的意义[3,4],数字基带系统模型如图1所示。

在图1中,通过星座映射将比特信息映射为符号信息,脉冲成型使信号转换成适于信道传输的信号波形。

对于低通基带信道,适合于信道传输的时间响应波形通常为近似矩形波。

这里假设图1中的信道为狭义信道,即传输媒介,包括电缆、光纤、无线信道等,并必然存在噪声干扰。

其中,脉冲成型、信道和匹配滤波统称为广义信道。

通常利用匹配滤波器(均衡器)对广义信道的传递函数进行均衡,使其达到理想低通或者余弦滚降低通特性以及限制带外噪声的作用。

一种基于FPGA的误码性能测试方案

摘要:提出了一种基于fpga的误码测试方案,并简要介绍了该方案的设计思想。

关键词:误码仪数字微波传输 acex1k系列fpga在数字通信系统的性能测试中,通常使用误码分析仪对其误码性能进行测量。

它虽然具有简单易用、测试内容丰富、误码测试结果直观、准确等优点,但是,价格昂贵、不易与某些系统接口适配,通常需要另加外部辅助长线驱动电路;此外,误码分析仪对于突发通信系统的误码性能测试存在先天不足。

例如,在对tdma 系统上行链路误码性能测试时,只有通过外加接口,对连续数据进行数据压扩,才能为被测设备模拟出突发形式的数据,从而完成测试。

这给测试工作带来极大的不便。

另一方面,现今的通信系统大量采用fpga作为系统的核心控制器件。

将物理层上的各协议层的功能集中在fpga内部实现,不仅提高了通信系统的集成,同时也减少了硬件和软件设计的复杂度。

基于上述两方面的考虑,笔者在fpga内部实现了一个简易的多功能误码分析仪。

该误码仪主要有三方面优点:一是可以根据用户需要,以连续或突发的方式产生若干种不同的随机序列或固定序列,并据此测试数字通信系统的误码性能;二是测试结果可以误码率或者误码数两种形式,通过外围器件直观地显示出来;三是作为被测系统的一个嵌入式模块,便于功能扩展及系统调试。

1 伪随机序列(m序列)许多数字通信理论的结论都基于这样一个假设:原始的信源信号为0、1等概并相互独立的随机数字序列。

同样,实际数字通信系统的设计,也是基于相同假设。

因此,为使测试结果尽可能真实地反映系统的性能,采用伪随机序列(m序列)作为测试中传输的信号。

m序列是一种线反馈移位寄存器序列,其原理方框图如图1所示。

每级移位寄存器的输出被反馈系数ci加权(ci可以取1或0),经模2和运算再反馈到第一级。

令第一级的输入为ak,就有:根据反馈系数的取值不同,电路可以产生出各种具有不同特性的数字序列。

对于一定的移位寄存器级数r,存在一些特殊的ci取值,使得输出序列的周期达到最长,即为2r-1。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

F1E 8

CⅡPh…k…off耕ud沪…Iom‘q…㈣Ⅲ¨moduk

功能仿真结果(合成23级伪随机序列)如阿9所不。

误码分析仪作为数字通信系统验收、维护和故障查询 的理想工具.广泛应用于同轴电缆、光纤、卫星及局间中继 等符合CEPT(Eumpe觚Conference

of

轻巧,接口丰富,简单易用,成本低廉,内核可升级等特点。

Postal舳d

Telec咖mu.

陌习而司同

rIic“o啮AdmiIIistra血on¥)数字系列通信系统传输质量的 监测…。评价一个通信系统的可靠性的指标就是检测 该通信系统在数据传输过程中误码率的大小.本文设 计的高速信号误码浏试仪。用于对EPON中接收和发 送突发光信号的接收模块的可靠性进行检测。目前误 码分析仪的工作模式已发展到如下4种:分析仪模式、 发生器模式、分析仪,发生器模式、直通模式I 21。本设计 中的误码测试仪属于第3种类型.即该误码测试仪可 以产生测试的码流.又可以进行误码测试。 误码测试仪主要由发送模块,接收模块,显示模块。控制 模块等几个模块组成,系统硬件结构框图如图1所示。其中 发送、接收模块在n,GA中实现,控制模块由单片机实现.显 示模块由单片机驱动.这样使得设计的误码分析仪具有体积 收稿日期:加10—03—2l

sY87739L

世!旦!!竺:.:}

Gm讪lc

el…Id con州Ⅱ州uIe

该模块控制sY87739I.台成32 M频率功能仿真结果

由M0deblm sE6l仿真)如图3所爪。

F‘g

3

SI叫I帅k

目3

的.该计散器是一个同步复位计数器。由一l醒HDL代码

综合出的圈元如图6所示。

口H13x8B∞

SY37739L&d《块*#结%

所币。

啦4

cm曲lcd…ld枷t“m甜uk

目4

廛

SY877叫v控d模块月元

sY87700v

时在PROGsK端输^时钟信号:4)设置PROGcs为低电平: 5)等待L.oCKED跳为高电平。 根据sY87739L的工作原理.可u用硬件语占编写出

sY87739L的控制代码,罔2是由venkg代码用synp狮

的同步时钟.因为该误码测试仪Hf以测试的频率有

32

M№、64 Mb,s.122

Mb,s

155

M乩4种。所H该芯片要根

钟是否进行分频,也要根据设置的参数由FPG^控制。此外 泼模块还要宴现FPcA读取sY87700v的功能.“确定

SY87700V是否完成时钟提取厦数据恢复。舣据sY87700v

据设置的参数台成相应的颇率。具体合成哪一个,由FPcA

时钟提取芯片sY盯7帅v的控制模块 sY877∞v对FPGA接收的数据进行时钟提取和数据恢

复“I。将恢复的技据与接收端产生的本地伪随机序列进行对 一130一

万方数据

王骐.等一种基于FPGA的高速误码测试仪的设计

F‘g l

7Ⅸ叫mnm帅v椭d…”r rr州m。

月7计翦模块自*仿^*口

4伪随机序列发进模块 伪随机序列发送模块的任务是“SY盯739L合成的频

d咖n10I脚duk

SY877拍L

测试文件中培DATA—l赋值为0000000I.町“观察出

prog_dl串行输出的编程数据为0000-01100一0110l_0lOo_眦

100叭_l

0l-10l;P”g_c^在P“啦di有效编程数据输出为高

F‘g 6

电平.待缩程数据输出结束后叫落到低电平:PR0csK输出

m序列作为测试数据,其测试速率最高可达到155 Mb,8。由于将物理层上的各协议层的功能集中到Ⅱ,GA内部实现.

减少了硬件和软件的设计复杂度。并且缩短了系统的开发的周期,具有可升级的特点。 关键词:高速误码测试仪;现场可编程门阵列;Veril唱硬件描述语言;模块图元;仿真;M序列码 中圈分类号:TN609 文献标识码:A 文章编号:1674_6236(2011)07-0129-05 bit

developmem Key

can

code.Its data

rate

is up

to

hardw肿circu“.IIl tlle BERT 155Mbps.It mali瑚tlIe mncti∞of

c哪plexit)r,舳d

s}Iorten tlle system

reduce tlle

llardware觚d sofhare

SY87739L的编程时钟。经分析nf以看出sY87739L控制模 块可“实现预想的功能。

10

craPh…k…of删H呻duI。

目6”#模*日i

该计数模块照大的计数值达22.用M0delslm仿真软件 对计数模块进行功能仿真的结果如罔7所示: 在测试文件中,c-・赋值为一个脉冲流,在cnLo辅出的 计数结果是正确的。可“判断出该模块的功能的正确性。

的传输协议合成相应的参考频率。sY87739I。台戚的频率是 由一个32位的串行输^的编程数据陕定。PR()Gcs为高电 平时.绾程数据才会被sY87739L接收。若用户需要改变编

程数据获得一十新的频帛时府先将PROCCS设置为高电

平.延时一殷时问(待32 bn编程数据被sY8了739L接收)后 在回落到低电平。既在PRoccs的下降沿时,sY87739L会

nle

system∞alabiliIy舳d

integratioll.V撕ous如nctio砌modules

c卸be altered∞cordingly witIl伽t charIgiIlg

test

Working Process,tlle tmnsmitter sends M code酗tlle e舶h protocol layer in physics layer,的it

来实现对SY87739L的控树。

sY87739L(规程式透明3 3

v 10—729

MHz分散N合成

的T作原理,可“用硬件语言venJoE绾写程序在FPcA实

现控{6I sY87700v的模块.图4是由代码综合出的圈元。

器)是一个频率合成芯片“。依照一参考频宰耀.它可“合成

lO一729

MHz范围内的差分频率。此外£可以精确地为标准

design

cycle,c粕be

up删ed.

bit

eⅡUr

words:higII一叩eed

mte tester;Field Pmgra舶mable

G砒e

Amy(FPGA);Verilog Hard砌糟Describe

L助glIage(VHDL);modIlle

g陋phic

ekr舱nt;simIllation;M code

the Ff,cA鼬tlle com

c岫plicate,cost

chip.UsiIlg

much and

to

inc彻veniem

tlle

to

taken¨The

pmject kn伊fbrwaId

test

co—igIl瑚脏on using

FPGA

c锄pkte

BEf盯s Control锄d

moduk

desi驴,it impmves

一129—

万方数据

《电子设计工程》2011年第9期

1-l频辜台成芯片SYS丌鲫L的控制模块

在设计中sY87739L台成的频串j甘于伪随机序列台成 比.实现误码检测,两数据流对比时H提取的时钟为同步时

钟。sY87700v在提取数据前要预知提取的频率的范甩.此

频率范围由FPcA发送给sY87700v。sY877。0v的参考时

综合m的用元如闭8所示。

厂丽酮几丽旧几丽司 拦”进拱sc箍}#”衅

L上&U

L±ML—L旦堕-J

目8伪%m月w&Ⅸ模*目E

上的控制散据。FPcA与单片机的通信控制模块将FPGA接

收到的控制信息产生控制其他模块的信号,这些控制情号 包括SY87739L频率合成的使能信号.SY87700v控制模块 的使能信号.计数器复位信号,伪随机码的缀数、建牢、发

l三

目Il

心lI

slⅡmlmm…‰mdhb眦c呲胁duk

#《接№横&∞自№∞^

在仿真文件中对该模块输^靖口*r_l赋值一个码流, 当赋值码流与车地伪随机序列同步的(同颧同耜).数据接

率为时钟产生伪随机序列并串行输出伪随机序列。诙模块

可H产生二种级数的伪随机序列.生成的伪随机序列串行

收模块每比对一bit码,就在s岫_0端日输出一高电平,若

设计使用的是自顶向下模块化的设计方法。基于H,GA设 计的模块包括:SY87739L频率计的控制模块、SY87700时钟 提取控制模块、计数模块、伪随机序列发送模块、数据接收 模块、与单片机的通信模块。

作者简介:王骐(197旺),男,湖北武汉人,博士,讲师。研究方向:单片机与嵌入式系统应用、无线传感器网络安全。

on

R且te

Tester)is used in detecting for

ml汕ility

of

a

co姗unic鲥∞system.1he

traditioIlal

CPLD and CPU’8

co叩emtive

work.r11lis lraditional

a

desi印h鹊mny

tIle

disadv锄tages,鲫ch船

稿件编号:20110312l

LED2H

输叫避

FPGA(Xc2s50E)

MCU(c8051F010)

硒瓦丁———1丽磊

SY87739L

(时钟合成)

●

t输出

检测设

图l误码测试仪系统硬件框图

隐l

1

Hardw眦block di咿锄0f