TL1100BF260Q;中文规格书,Datasheet资料

BF861C,215;中文规格书,Datasheet资料

Min Typ Max Unit

25 -

-

V

0.2 -

0.5 -

0.8 -

-

-

1 V

1.5 V

2 V

1

V

2

-

6

-

12 -

-

-

6.5 mA 15 mA 25 mA 1 nA

© NXP B.V. 2011. All rights reserved.

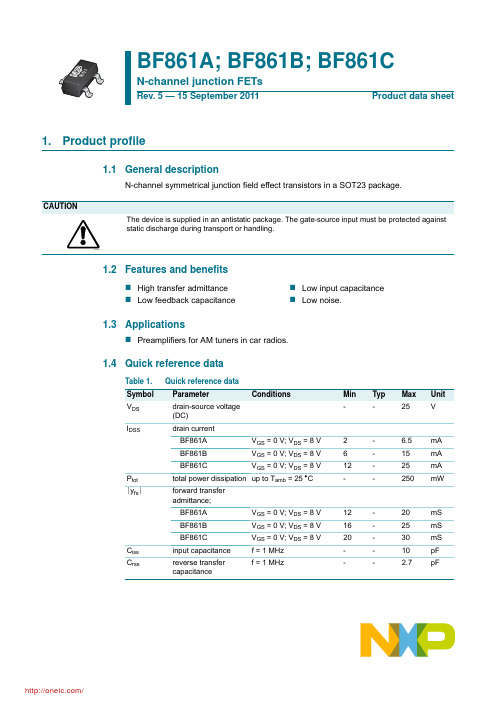

Table 1. Symbol VDS IDSS

Ptot yfs

Ciss Crss

Quick reference data

Parameter

Conditions

drain-source voltage (DC)

drain current

BF861A

VGS = 0 V; VDS = 8 V

BF861B

Symbol Parameter

Conditions

Min

VDS VGSO VDGO IG Ptot Tstg Tj

drain-source voltage (DC) gate-source voltage drain-gate voltage (DC) forward gate current (DC) total power dissipation storage temperature operating junction temperature

VDS = 8 V. (1) VGS = 0 V. (2) VGS = 100 mV. (3) VGS = 200 mV. (4) VGS = 300 mV.

Fig 7. Typical output characteristics: BF861A.

BR1100资料

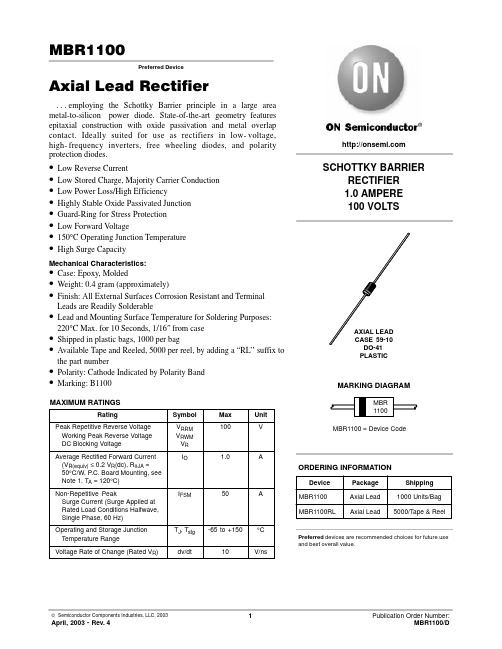

MBR1100Preferred DeviceAxial Lead Rectifier...employing the Schottky Barrier principle in a large area metal-to-silicon power diode. State-of-the-art geometry features epitaxial construction with oxide passivation and metal overlap contact. Ideally suited for use as rectifiers in low-voltage, high-frequency inverters, free wheeling diodes, and polarityprotection diodes.•Low Reverse Current•Low Stored Charge, Majority Carrier Conduction•Low Power Loss/High Efficiency•Highly Stable Oxide Passivated Junction•Guard-Ring for Stress Protection•Low Forward V oltage•150°C Operating Junction Temperature•High Surge CapacityMechanical Characteristics:•Case: Epoxy, Molded•Weight: 0.4 gram (approximately)•Finish: All External Surfaces Corrosion Resistant and Terminal Leads are Readily Solderable•Lead and Mounting Surface Temperature for Soldering Purposes: 220°C Max. for 10 Seconds, 1/16″ from case•Shipped in plastic bags, 1000 per bag•Available Tape and Reeled, 5000 per reel, by adding a “RL’’ suffix to the part number•Polarity: Cathode Indicated by Polarity Band•Marking: B1100MAXIMUM RATINGSPreferred devices are recommended choices for future use and best overall value.THERMAL CHARACTERISTICS (See Note 2)ELECTRICAL CHARACTERISTICS (T= 25°C unless otherwise noted)Figure 2. Typical Reverse Current {Figure 3. Current Derating (Mounting Method 3 per Note 1)Figure 4. Power Dissipation20102.05.01.0V R , REVERSE VOLTAGE (VOLTS)609000.20.040.020.011201600T A , AMBIENT TEMPERATURE (°C)4.03.02.01.00I F(AV), AVERAGE FORWARD CURRENT (AMPS)1.004.03.02.01.02.0140i F , I N S T A N T A N E O U S F O R W A R D C U R R E N T (A M P S )I I P F (A V ), A V E R A G E P O W E R D I S S I P A T I O N (W A T T S )0.50.20.1708010203040500.10.41.020********* 3.0 4.0 5.00.050.02100, R E V E R S E C U R R E N T ( A )R m 4.02.01020100402001 K400200180, A V E R A G E F O R W A R D C U R R E N T (A M P S )F (A V ){ The curves shown are typical for the highest voltagedevice in the voltage grouping. Typical reverse current for lower voltage selections can be estimated from these same curves if V R is sufficiently below rated V R .Figure 5. Typical Capacitance2040V R , REVERSE VOLTAGE (VOLTS)150504*********C , C A P A C I T A N C E (p F )50100601001070809070609080NOTE 1 — MOUNTING DATA:Data shown for thermal resistance junction-to-ambient (R q JA) for the mounting shown is to be used as a typical guideline values for preliminary engineering or in case the tie point temperature cannot be measured.Typical Values for Rin Still AirMounting Method 1P .C. Board with 1-1/2″ x 1-1/2″copper surface.Mounting Method 3P .C. Board with 1-1/2″ x 1-1/2″copper surface.VECTOR PIN MOUNTINGMounting Method 2NOTE 2 — THERMAL CIRCUIT MODEL:(For heat conduction through the leads)Use of the above model permits junction to lead thermal resistance for any mounting configuration to be found. For a given total lead length, lowest values occur when one side of the rectifier is brought as close as possible to the heat sink.Terms in the model signify:T A = Ambient Temperature T C = Case Temperature T L = Lead Temperature T J = Junction Temperature R q S = Thermal Resistance, Heat Sink to Ambient R q L = Thermal Resistance, Lead to Heat Sink R q J = Thermal Resistance, Junction to Case P D = Power Dissipation(Subscripts A and K refer to anode and cathode sides,respectively.) V alues for thermal resistance components are:R q L = 100°C/W/in typically and 120°C/W/in maximum.R θJ = 36°C/W typically and 46°C/W maximum.NOTE 3 — HIGH FREQUENCY OPERATION:Since current flow in a Schottky rectifier is the result of majority carrier conduction, it is not subject to junction diode forward and reverse recovery transients due to minority carrier injection and stored charge. Satisfactory circuit analysis work may be performed by using a model consisting of an ideal diode in parallel with a variable capacitance. (See Figure 5)Rectification efficiency measurements show that operation will be satisfactory up to several megahertz. For example, relative waveform rectification efficiency is approximately 70 percent at 2 MHz, e.g., the ratio of dc power to RMS power in the load is 0.28 at this frequency,whereas perfect rectification would yield 0.406 for sine wave inputs. However, in contrast to ordinary junction diodes, the loss in waveform efficiency is not indicative of power loss: it is simply a result of reverse current flow through the diode capacitance, which lowers the dc output voltage.PACKAGE DIMENSIONSCASE 59-10ISSUE SAXIAL LEAD, DO-41DIM MIN MAX MIN MAX MILLIMETERSINCHES A 4.10 5.200.1610.205B 2.00 2.700.0790.106D 0.710.860.0280.034F −−− 1.27−−−0.050K25.40−−−1.000−−−NOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: INCH.3.59−04 OBSOLETE, NEW STANDARD 59−09.4.59−03 OBSOLETE, NEW STANDARD 59−10.5.ALL RULES AND NOTES ASSOCIATED WITH JEDEC DO−41 OUTLINE SHALL APPLY6.POLARITY DENOTED BY CATHODE BAND.7.LEAD DIAMETER NOT CONTROLLED WITHIN F DIMENSION.ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to makechanges without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. “Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others.SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer.PUBLICATION ORDERING INFORMATIONJAPAN : ON Semiconductor, Japan Customer Focus Center 2-9-1 Kamimeguro, Meguro-ku, Tokyo, Japan 153-0051Phone : 81-3-5773-3850。

.LCZ260;.LCZ460;中文规格书,Datasheet资料

DESCRIPTIONThe LCZ Series Hall-effect Zero Speed Sensors provide a durable, cost-effective solution in most harsh environments.The sensor is available in 9,5 mm [3/8 in/0.375 in] and 15,9 mm [5/8 in/0.625 in] diameters, in both 50,8 mm [2.00 in] and 76,2 mm [3.00 in] lengths.The stainless steel package is simple to install and adjust. It does not require rotational orientation.FEATURESLow costOmni-directional sensor to target orientationDigital outputSmall sizeLow power consumptionPOTENTIAL APPLICATIONSIndustrial process controlFactory automationRotary applications, such as: – Pumps – Rollers – Mixers– Fan speed measurement – Transmission – Spindles– Gear reducer RPM – Process speed – Synchronization – Generator set – Compressor speed – Dyno testing2/sensingHoneywell Sensing and Control3Sensing and Control Honeywell1985 Douglas Drive NorthGolden Valley, MN 55422 /sensing 005886-3-ENSeptember 2011Copyright © 2011 Honeywell International Inc. All rights reserved.PERSONAL INJURYWARRANTY/REMEDYHoneywell warrants goods of its manufacture as being free of defective mat erials and faulty workmanship. Honeywell’s standard product warranty applies unless agreed to otherwise by Honeywell in writing; please refer to your order acknowledgement or consult your local sales office for specific warranty details. If warranted goods are returned to Honeywell during the period of coverage, Honeywell will repair or replace, at its option, without charge those items it finds defective. The foregoing is b uyer’s sole remedy and is in lieu of all other warranties, expressed or implied, including those of merchantability and fitness for a particular purpose. In no event shall Honeywell be liable for consequential, special, or indirect damages.While we provide application assistance personally, through our literature and the Honeywell web site, it is up to the customer to determine the suitability of the product in the application.Specifications may change without notice. The information we supply is believed to be accurate and reliable as of this printing. However, we assume no responsibility for its use.WARNINGMISUSE OF DOCUMENTATIONThe information presented in this product sheet is forComplete installation, operation, and maintenanceSALES AND SERVICEHoneywell serves its customers through a worldwide network of sales offices, representatives and distributors. For application assistance, current specifications, pricing or name of the nearest Authorized Distributor, contact your local sales office or:E-mail: info.sc@Internet: /sensingPhone and Fax:Asia Pacific +65 6355-2828+65 6445-3033 FaxEurope +44 (0) 1698 481481+44 (0) 1698 481676 FaxLatin America +1-305-805-8188+1-305-883-8257 FaxUSA/Canada +1-800-537-6945+1-815-235-6847+1-815-235-6545 Fax分销商库存信息: HONEYWELL.LCZ260.LCZ460。

TL082ACDR,TL082ACDR,TL082ACDR,TL082IDR,TL082IDR,TL082IDR,TL081CDR,TL081CDR, 规格书,Datasheet 资料

Addendum-Page 1PACKAGING INFORMATIONOrderable Device Status(1)Package Type PackageDrawingPins Package QtyEco Plan(2)Lead/Ball Finish MSL Peak Temp (3)Samples (Requires Login)5962-9851501Q2A ACTIVE LCCC FK 201TBD Call TI Call TI5962-9851501QPA ACTIVE CDIP JG 81TBD A42N / A for Pkg Type 5962-9851503Q2A ACTIVE LCCC FK 201TBD Call TI Call TI 5962-9851503QCAACTIVE CDIP J 141TBDCall TICall TITL081ACD ACTIVE SOIC D 875Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL081ACDE4ACTIVE SOIC D 875Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL081ACDG4ACTIVE SOIC D 875Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL081ACDR ACTIVE SOIC D 82500Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL081ACDRE4ACTIVE SOIC D 82500Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL081ACDRG4ACTIVE SOIC D 82500Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL081ACJG OBSOLETE CDIP JG 8TBD Call TICall TITL081ACP ACTIVE PDIP P 850Pb-Free (RoHS)CU NIPDAU N / A for Pkg Type TL081ACPE4ACTIVE PDIP P 850Pb-Free (RoHS)CU NIPDAU N / A for Pkg Type TL081BCD ACTIVE SOIC D 875Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL081BCDE4ACTIVE SOIC D 875Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL081BCDG4ACTIVE SOIC D 875Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL081BCDR ACTIVE SOIC D 82500Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL081BCDRE4ACTIVE SOIC D 82500Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL081BCDRG4ACTIVE SOIC D 82500Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL081BCP ACTIVE PDIP P 850Pb-Free (RoHS)CU NIPDAU N / A for Pkg Type TL081BCPE4ACTIVEPDIPP850Pb-Free (RoHS)CU NIPDAU N / A for Pkg Type芯天下--/Addendum-Page 2Orderable DeviceStatus(1)Package Type PackageDrawingPins Package QtyEco Plan(2)Lead/Ball FinishMSL Peak Temp(3)Samples (Requires Login)TL081CD ACTIVE SOIC D 875Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL081CDE4ACTIVE SOIC D 875Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL081CDG4ACTIVE SOIC D 875Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL081CDR ACTIVE SOIC D 82500Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL081CDRE4ACTIVE SOIC D 82500Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL081CDRG4ACTIVE SOIC D 82500Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL081CP ACTIVE PDIP P 850Pb-Free (RoHS)CU NIPDAU N / A for Pkg Type TL081CPE4ACTIVE PDIP P 850Pb-Free (RoHS)CU NIPDAU N / A for Pkg Type TL081CPSR ACTIVE SO PS 82000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL081CPSRE4ACTIVE SO PS 82000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL081CPSRG4ACTIVE SO PS 82000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL081CPWLE OBSOLETE TSSOP PW 8TBD Call TICall TITL081ID ACTIVE SOIC D 875Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL081IDE4ACTIVE SOIC D 875Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL081IDG4ACTIVE SOIC D 875Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL081IDR ACTIVE SOIC D 82500Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL081IDRE4ACTIVE SOIC D 82500Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL081IDRG4ACTIVE SOIC D 82500Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL081IP ACTIVE PDIP P 850Pb-Free (RoHS)CU NIPDAU N / A for Pkg Type TL081IPE4ACTIVEPDIPP850Pb-Free (RoHS)CU NIPDAU N / A for Pkg Type芯天下--/Addendum-Page 3Orderable Device Status(1)Package Type PackageDrawingPins Package QtyEco Plan(2)Lead/Ball Finish MSL Peak Temp (3)Samples (Requires Login)TL081MFKB OBSOLETE LCCC FK 20TBD Call TI Call TI TL081MJG OBSOLETE CDIP JG 8TBD Call TI Call TI TL081MJGB OBSOLETE CDIP JG 8TBDCall TICall TITL082ACD ACTIVE SOIC D 875Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL082ACDE4ACTIVE SOIC D 875Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL082ACDG4ACTIVE SOIC D 875Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL082ACDR ACTIVE SOIC D 82500Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL082ACDRE4ACTIVE SOIC D 82500Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL082ACDRG4ACTIVE SOIC D 82500Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL082ACP ACTIVE PDIP P 850Pb-Free (RoHS)CU NIPDAU N / A for Pkg Type TL082ACPE4ACTIVE PDIP P 850Pb-Free (RoHS)CU NIPDAU N / A for Pkg Type TL082ACPSR ACTIVE SO PS 82000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL082ACPSRE4ACTIVE SO PS 82000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL082ACPSRG4ACTIVE SO PS 82000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL082BCD ACTIVE SOIC D 875Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL082BCDE4ACTIVE SOIC D 875Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL082BCDG4ACTIVE SOIC D 875Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL082BCDR ACTIVE SOIC D 82500Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL082BCDRE4ACTIVE SOIC D 82500Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL082BCDRG4ACTIVESOICD82500Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM芯天下--/Addendum-Page 4Orderable DeviceStatus(1)Package Type PackageDrawingPins Package QtyEco Plan(2)Lead/Ball FinishMSL Peak Temp(3)Samples (Requires Login)TL082BCP ACTIVE PDIP P 850Pb-Free (RoHS)CU NIPDAU N / A for Pkg Type TL082BCPE4ACTIVE PDIP P 850Pb-Free (RoHS)CU NIPDAU N / A for Pkg Type TL082CD ACTIVE SOIC D 875Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL082CDE4ACTIVE SOIC D 875Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL082CDG4ACTIVE SOIC D 875Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL082CDR ACTIVE SOIC D 82500Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL082CDRE4ACTIVE SOIC D 82500Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL082CDRG4ACTIVE SOIC D 82500Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL082CJG OBSOLETE CDIP JG 8TBD Call TICall TITL082CP ACTIVE PDIP P 850Pb-Free (RoHS)CU NIPDAU N / A for Pkg Type TL082CPE4ACTIVE PDIP P 850Pb-Free (RoHS)CU NIPDAU N / A for Pkg Type TL082CPSR ACTIVE SO PS 82000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL082CPSRG4ACTIVE SO PS 82000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL082CPW ACTIVE TSSOP PW 8150Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL082CPWE4ACTIVE TSSOP PW 8150Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL082CPWG4ACTIVE TSSOP PW 8150Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL082CPWLE OBSOLETE TSSOP PW 8TBD Call TICall TITL082CPWR ACTIVE TSSOP PW 82000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL082CPWRE4ACTIVE TSSOP PW 82000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL082CPWRG4ACTIVETSSOPPW82000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM芯天下--/27-Apr-2012Orderable Device Status (1)Package Type PackageDrawing Pins Package Qty Eco Plan (2)Lead/Ball FinishMSL Peak Temp (3)Samples(Requires Login)TL082ID ACTIVE SOIC D875Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTL082IDE4ACTIVE SOIC D875Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTL082IDG4ACTIVE SOIC D875Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTL082IDR ACTIVE SOIC D82500Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTL082IDRE4ACTIVE SOIC D82500Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTL082IDRG4ACTIVE SOIC D82500Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL082IJG OBSOLETE CDIP JG8TBD Call TI Call TITL082IP ACTIVE PDIP P850Pb-Free (RoHS)CU NIPDAU N / A for Pkg Type TL082IPE4ACTIVE PDIP P850Pb-Free (RoHS)CU NIPDAU N / A for Pkg Type TL082IPWR ACTIVE TSSOP PW82000Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTL082IPWRE4ACTIVE TSSOP PW82000Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTL082IPWRG4ACTIVE TSSOP PW82000Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL082MFK OBSOLETE LCCC FK20TBD Call TI Call TITL082MFKB ACTIVE LCCC FK201TBD POST-PLATE N / A for Pkg Type TL082MJG ACTIVE CDIP JG81TBD A42N / A for Pkg Type TL082MJGB ACTIVE CDIP JG81TBD A42N / A for Pkg Type TL084ACD ACTIVE SOIC D1450Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTL084ACDE4ACTIVE SOIC D1450Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTL084ACDG4ACTIVE SOIC D1450Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTL084ACDR ACTIVE SOIC D142500Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTL084ACDRE4ACTIVE SOIC D142500Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIM27-Apr-2012Orderable Device Status (1)Package Type PackageDrawing Pins Package Qty Eco Plan (2)Lead/Ball FinishMSL Peak Temp (3)Samples(Requires Login)TL084ACDRG4ACTIVE SOIC D142500Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTL084ACN ACTIVE PDIP N1425Pb-Free (RoHS)CU NIPDAU N / A for Pkg Type TL084ACNE4ACTIVE PDIP N1425Pb-Free (RoHS)CU NIPDAU N / A for Pkg Type TL084ACNSR ACTIVE SO NS142000Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTL084ACNSRE4ACTIVE SO NS142000Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTL084ACNSRG4ACTIVE SO NS142000Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTL084BCD ACTIVE SOIC D1450Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTL084BCDE4ACTIVE SOIC D1450Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTL084BCDG4ACTIVE SOIC D1450Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTL084BCDR ACTIVE SOIC D142500Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTL084BCDRE4ACTIVE SOIC D142500Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTL084BCDRG4ACTIVE SOIC D142500Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL084BCN ACTIVE PDIP N1425Pb-Free (RoHS)CU NIPDAU N / A for Pkg Type TL084BCNE4ACTIVE PDIP N1425Pb-Free (RoHS)CU NIPDAU N / A for Pkg Type TL084CD ACTIVE SOIC D1450Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTL084CDE4ACTIVE SOIC D1450Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTL084CDG4ACTIVE SOIC D1450Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTL084CDR ACTIVE SOIC D142500Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTL084CDRE4ACTIVE SOIC D142500Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIM27-Apr-2012Orderable Device Status (1)Package Type PackageDrawing Pins Package Qty Eco Plan (2)Lead/Ball FinishMSL Peak Temp (3)Samples(Requires Login)TL084CDRG4ACTIVE SOIC D142500Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTL084CJ OBSOLETE CDIP J14TBD Call TI Call TITL084CN ACTIVE PDIP N1425Pb-Free (RoHS)CU NIPDAU N / A for Pkg Type TL084CNE4ACTIVE PDIP N1425Pb-Free (RoHS)CU NIPDAU N / A for Pkg Type TL084CNSLE OBSOLETE SO NS14TBD Call TI Call TITL084CNSR ACTIVE SO NS142000Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTL084CNSRG4ACTIVE SO NS142000Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTL084CPW ACTIVE TSSOP PW1490Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTL084CPWE4ACTIVE TSSOP PW1490Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTL084CPWG4ACTIVE TSSOP PW1490Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL084CPWLE OBSOLETE TSSOP PW14TBD Call TI Call TITL084CPWR ACTIVE TSSOP PW142000Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTL084CPWRE4ACTIVE TSSOP PW142000Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTL084CPWRG4ACTIVE TSSOP PW142000Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTL084ID ACTIVE SOIC D1450Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTL084IDE4ACTIVE SOIC D1450Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTL084IDG4ACTIVE SOIC D1450Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTL084IDR ACTIVE SOIC D142500Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTL084IDRE4ACTIVE SOIC D142500Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTL084IDRG4ACTIVE SOIC D142500Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIM27-Apr-2012Orderable Device Status (1)Package Type PackageDrawing Pins Package Qty Eco Plan (2)Lead/Ball FinishMSL Peak Temp (3)Samples(Requires Login)TL084IJ OBSOLETE CDIP J14TBD Call TI Call TITL084IN ACTIVE PDIP N1425Pb-Free (RoHS)CU NIPDAU N / A for Pkg TypeTL084INE4ACTIVE PDIP N1425Pb-Free (RoHS)CU NIPDAU N / A for Pkg TypeTL084MFK ACTIVE LCCC FK201TBD POST-PLATE N / A for Pkg TypeTL084MFKB ACTIVE LCCC FK201TBD POST-PLATE N / A for Pkg TypeTL084MJ ACTIVE CDIP J141TBD A42N / A for Pkg TypeTL084MJB ACTIVE CDIP J141TBD A42N / A for Pkg TypeTL084QD ACTIVE SOIC D1450Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTL084QDG4ACTIVE SOIC D1450Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTL084QDR ACTIVE SOIC D142500Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTL084QDRG4ACTIVE SOIC D142500Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIM(1) The marketing status values are defined as follows:ACTIVE: Product device recommended for new designs.LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.PREVIEW: Device has been announced but is not in production. Samples may or may not be available.OBSOLETE: TI has discontinued the production of the device.(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check /productcontent for the latest availability information and additional product content details.TBD: The Pb-Free/Green conversion plan has not been defined.Pb-Free (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and27-Apr-2012 continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.OTHER QUALIFIED VERSIONS OF TL082, TL082M, TL084, TL084M :•Catalog: TL082, TL084•Automotive: TL082-Q1, TL082-Q1•Military: TL082M, TL084MNOTE: Qualified Version Definitions:•Catalog - TI's standard catalog product•Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects•Military - QML certified for Military and Defense ApplicationsTAPE AND REELINFORMATION*Alldimensions are nominalDevicePackage Type Package Drawing Pins SPQReel Diameter (mm)Reel Width W1(mm)A0(mm)B0(mm)K0(mm)P1(mm)W (mm)Pin1Quadrant TL081ACDR SOIC D 82500330.012.4 6.4 5.2 2.18.012.0Q1TL081BCDR SOIC D 82500330.012.4 6.4 5.2 2.18.012.0Q1TL081CDR SOIC D 82500330.012.4 6.4 5.2 2.18.012.0Q1TL081CPSR SO PS 82000330.016.48.2 6.6 2.512.016.0Q1TL081IDR SOIC D 82500330.012.4 6.4 5.2 2.18.012.0Q1TL082ACDR SOIC D 82500330.012.4 6.4 5.2 2.18.012.0Q1TL082ACDR SOIC D 82500330.012.4 6.4 5.2 2.18.012.0Q1TL082ACPSR SO PS 82000330.016.48.2 6.6 2.512.016.0Q1TL082BCDR SOIC D 82500330.012.4 6.4 5.2 2.18.012.0Q1TL082CDR SOIC D 82500330.012.4 6.4 5.2 2.18.012.0Q1TL082CDR SOIC D 82500330.012.4 6.4 5.2 2.18.012.0Q1TL082CPSR SO PS 82000330.016.48.2 6.6 2.512.016.0Q1TL082CPWR TSSOP PW 82000330.012.47.0 3.6 1.68.012.0Q1TL082IDR SOIC D 82500330.012.4 6.4 5.2 2.18.012.0Q1TL082IDR SOIC D 82500330.012.4 6.4 5.2 2.18.012.0Q1TL082IPWR TSSOP PW 82000330.012.47.0 3.6 1.68.012.0Q1TL084ACDR SOIC D 142500330.016.4 6.59.0 2.18.016.0Q1TL084ACDRSOICD142500330.016.46.59.02.18.016.0Q114-Jul-2012DevicePackage Type Package Drawing Pins SPQReel Diameter (mm)Reel Width W1(mm)A0(mm)B0(mm)K0(mm)P1(mm)W (mm)Pin1Quadrant TL084ACNSR SO NS 142000330.016.48.210.5 2.512.016.0Q1TL084BCDR SOIC D 142500330.016.4 6.59.0 2.18.016.0Q1TL084CDR SOIC D 142500330.016.4 6.59.0 2.18.016.0Q1TL084CNSR SO NS 142000330.016.48.210.5 2.512.016.0Q1TL084CPWR TSSOP PW 142000330.012.4 6.9 5.6 1.68.012.0Q1TL084IDR SOIC D 142500330.016.4 6.59.0 2.18.016.0Q1TL084QDRSOICD142500330.016.46.59.02.18.016.0Q1*All dimensions are nominalDevice Package TypePackage DrawingPins SPQ Length (mm)Width (mm)Height (mm)TL081ACDR SOIC D 82500340.5338.120.6TL081BCDR SOIC D 82500340.5338.120.6TL081CDR SOIC D 82500340.5338.120.6TL081CPSR SO PS 82000367.0367.038.0TL081IDR SOIC D 82500340.5338.120.6TL082ACDR SOIC D 82500340.5338.120.6TL082ACDR SOIC D 82500367.0367.035.0TL082ACPSR SO PS 82000367.0367.038.0TL082BCDR SOIC D 82500340.5338.120.6TL082CDRSOICD82500340.5338.120.614-Jul-2012Device PackageTypePackage DrawingPins SPQ Length (mm)Width (mm)Height (mm)TL082CDR SOIC D 82500367.0367.035.0TL082CPSR SO PS 82000367.0367.038.0TL082CPWR TSSOP PW 82000367.0367.035.0TL082IDR SOIC D 82500367.0367.035.0TL082IDR SOIC D 82500340.5338.120.6TL082IPWR TSSOP PW 82000367.0367.035.0TL084ACDR SOIC D 142500333.2345.928.6TL084ACDR SOIC D 142500367.0367.038.0TL084ACNSR SO NS 142000367.0367.038.0TL084BCDR SOIC D 142500333.2345.928.6TL084CDR SOIC D 142500333.2345.928.6TL084CNSR SO NS 142000367.0367.038.0TL084CPWR TSSOP PW 142000367.0367.035.0TL084IDR SOIC D 142500333.2345.928.6TL084QDRSOICD142500367.0367.038.014-Jul-2012IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,enhancements,improvements and other changes to its semiconductor products and services per JESD46C and to discontinue any product or service per JESD48B.Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All semiconductor products(also referred to herein as“components”)are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its components to the specifications applicable at the time of sale,in accordance with the warranty in TI’s terms and conditions of sale of semiconductor products.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by applicable law,testing of all parameters of each component is not necessarily performed.TI assumes no liability for applications assistance or the design of Buyers’products.Buyers are responsible for their products and applications using TI components.To minimize the risks associated with Buyers’products and applications,Buyers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any patent right,copyright,mask work right,or other intellectual property right relating to any combination,machine,or process in which TI components or services are rmation published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.Buyer acknowledges and agrees that it is solely responsible for compliance with all legal,regulatory and safety-related requirements concerning its products,and any use of TI components in its applications,notwithstanding any applications-related information or support that may be provided by TI.Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures,monitor failures and their consequences,lessen the likelihood of failures that might cause harm and take appropriate remedial actions.Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.In some cases,TI components may be promoted specifically to facilitate safety-related applications.With such components,TI’s goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements.Nonetheless,such components are subject to these terms.No TI components are authorized for use in FDA Class III(or similar life-critical medical equipment)unless authorized officers of the parties have executed a special agreement specifically governing such use.Only those TI components which TI has specifically designated as military grade or“enhanced plastic”are designed and intended for use in military/aerospace applications or environments.Buyer acknowledges and agrees that any military or aerospace use of TI components which have not been so designated is solely at the Buyer's risk,and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.TI has specifically designated certain components which meet ISO/TS16949requirements,mainly for automotive ponents which have not been so designated are neither designed nor intended for automotive use;and TI will not be responsible for any failure of such components to meet such requirements.Products ApplicationsAudio /audio Automotive and Transportation /automotiveAmplifiers Communications and Telecom /communicationsData Converters Computers and Peripherals /computersDLP®Products Consumer Electronics /consumer-appsDSP Energy and Lighting /energyClocks and Timers /clocks Industrial /industrialInterface Medical /medicalLogic Security /securityPower Mgmt Space,Avionics and Defense /space-avionics-defense Microcontrollers Video and Imaging /videoRFID OMAP Mobile Processors /omap TI E2E Community Wireless Connectivity /wirelessconnectivityMailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2012,Texas Instruments Incorporated。

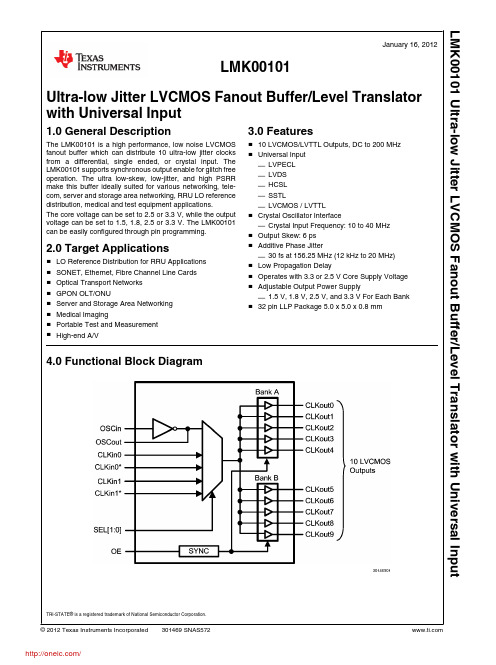

LMK00101SQXNOPB;LMK00101SQNOPB;LMK00101SQENOPB;LMK00101BEVALNOPB;中文规格书,Datasheet资料

LMK00101January 16, 2012Ultra-low Jitter LVCMOS Fanout Buffer/Level Translator with Universal Input1.0 General DescriptionThe LMK00101 is a high performance, low noise LVCMOS fanout buffer which can distribute 10 ultra-low jitter clocks from a differential, single ended, or crystal input. The LMK00101 supports synchronous output enable for glitch free operation. The ultra low-skew, low-jitter, and high PSRR make this buffer ideally suited for various networking, tele-com, server and storage area networking, RRU LO reference distribution, medical and test equipment applications.The core voltage can be set to 2.5 or 3.3 V, while the output voltage can be set to 1.5, 1.8, 2.5 or 3.3 V. The LMK00101 can be easily configured through pin programming.2.0 Target Applications■LO Reference Distribution for RRU Applications■SONET, Ethernet, Fibre Channel Line Cards■Optical Transport Networks■GPON OLT/ONU■Server and Storage Area Networking■Medical Imaging■Portable Test and Measurement■High-end A/V 3.0 Features■10 LVCMOS/LVTTL Outputs, DC to 200 MHz ■Universal Input—LVPECL—LVDS—HCSL—SSTL—LVCMOS / LVTTL■Crystal Oscillator Interface—Crystal Input Frequency: 10 to 40 MHz■Output Skew: 6 ps■Additive Phase Jitter—30 fs at 156.25 MHz (12 kHz to 20 MHz)■Low Propagation Delay■Operates with 3.3 or 2.5 V Core Supply Voltage ■Adjustable Output Power Supply—1.5 V, 1.8 V, 2.5 V, and 3.3 V For Each Bank ■32 pin LLP Package 5.0 x 5.0 x 0.8 mm4.0 Functional Block Diagram30146901TRI-STATE® is a registered trademark of National Semiconductor Corporation.© 2012 Texas Instruments Incorporated301469 LMK00101 Ultra-low Jitter LVCMOS Fanout Buffer/Level Translator with Universal Input5.0 Connection Diagram32-Pin LLP Package301469026.0 Pin DescriptionsPin #Pin Name Type DescriptionDAP DAP -The DAP should be grounded1CLKout0Output LVCMOS Output2, 6Vddo Power Power Supply for Bank A (CLKout0 to CLKout4) CLKout pins.19,23Vddo Power Power Supply for Bank B (CLKout5 to CLKout9) CLKout pins.3CLKout1Output LVCMOS Output 4,9,15,16,21,25,26,32GND GND Ground5CLKout2Output LVCMOS Output 7CLKout3Output LVCMOS Output 8CLKout4Output LVCMOS Output10Vdd Power Supply for operating core and input buffer 11OSCin Input Input for Crystal 12OSCout Output Output for Crystal 13CLKin0Input Input Pin14CLKin0*Input Optional complimentary input pin 17CLKout5Output LVCMOS Output 18CLKout6Output LVCMOS Output 20CLKout7Output LVCMOS Output 22CLKout8Output LVCMOS Output 24CLKout9Output LVCMOS Output27CLKin1*Input Optional Complimentary Input Pin 28CLKin1Input Input Pin29SEL1Input MSB for Input Clock Selection. This pin has an internal pull-down resistor.30SEL0Input LSB for Input Clock Selection. This pin has an internal pull-down resistor.31OEInputOutput Enable. This pin has an internal pull-down resistor. 2L M K 00101 U l t r a -l o w J i t t e r L V C M O S F a n o u t B u f f e r /L e v e l T r a n s l a t o r w i t h U n i v e r s a l I n p u t7.0 Absolute Maximum Ratings (Note 1, Note 2)If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.Parameter Symbol Ratings Units Core Supply Voltage Vdd-0.3 to 3.6VOutput Supply Voltage Vddo-0.3 to 3.6V Input Voltage V IN-0.3 to Vdd + 0.3V Storage Temperature Range T STG-65 to 150°CLead Temperature (solder 4 s)T L+260°C Junction Temperature T J+125°C8.0 Recommended Operating ConditionsParameter Symbol Min Typ Max Units Ambient Temperature T A-402585°CCore Supply Voltage Vdd 2.375 3.3 3.45V Output Supply Voltage (Note 3)Vddo 1.425 3.3Vdd VNote 1:"Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditions indicate conditions at which the device is functional and the device should not be operated beyond such conditions.Note 2:This device is a high performance integrated circuit with ESD handling precautions. Handling of this device should only be done at ESD protected work stations. The device is rated to a HBM-ESD of > 2.5 kV, a MM-ESD of > 250 V, and a CDM-ESD of > 1 kV.Note 3:Vddo should be less than or equal to Vdd(Vddo≤ Vdd)9.0 Package Thermal Resistance32-Lead LLPPackage Symbols Ratings UnitsThermal resistance from junction to ambienton 4-layer Jedec board (Note 4)θJA50° C/WThermal resistance from junction to case(Note 5)θJC (DAP)20° C/WNote 4:Specification assumes 5 thermal vias connect to die attach pad to the embedded copper plane on the 4-layer Jedec board. These vias play a key role in improving the thermal performance of the LLP. For best thermal dissipation it is recommended that the maximum number of vias be used on the board layout.Note 5:Case is defined as the DAP (die attach pad).LMK00101 Ultra-low Jitter LVCMOS Fanout Buffer/Level Translator with Universal Input10.0 Electrical Characteristics(2.375 V ≤ Vdd ≤ 3.45 V, 1.425 ≤ Vddo ≤ Vdd, -40 °C ≤ T A ≤ 85 °C, Differential inputs. Typical values represent most likely parametric norms at Vdd = Vddo = 3.3 V, T A = 25 °C, at the Recommended Operation Conditions at the time of product charac-terization and are not guaranteed). Test conditions are: F test = 100 MHz, Load = 5 pF in parallel with 50 Ω unless otherwise stated.SymbolParameterTest ConditionsMinTypMaxUnitsTotal Device CharacteristicsVddCore Supply Voltage2.3752.5 or3.33.45VVddo Output Supply Voltage 1.425 1.5,1.8,2.5, or3.3Vdd VI VddCore CurrentNo CLKin1625mAV ddo = 3.3 V, F test = 100 MHz 24 V ddo = 2.5 V, F test = 100 MHz 20 I Vddo[n]Current for Each OutputV ddo = 2.5 V,OE = High, F test = 100 MHz5 mAV ddo = 3.3 V,OE = High, F test = 100 MHz7 OE = Low 0.1 I Vdd + I VddoTotal Device Current with Loads onall outputsOE = High @ 100 MHz95 mAOE = Low16Power Supply Ripple Rejection (PSRR)PSRRRipple Induced Phase Spur Level100 kHz, 100 mVpp Ripple Injected on V dd , V ddo = 2.5 V-44dBcOutputs (Note 6)Skew Output Skew Measured between outputs,referenced to CLKout06 ps f CLKoutOutput Frequency(Note 7)DC 200MHzt Rise Rise/Fall Time V dd = 3.3 V, V ddo = 1.8 V, C L = 10 pF500 psV dd = 2.5 V, V ddo = 2.5 V, C L = 10 pF 300 V dd = 3.3 V, V ddo = 3.3 V, C L = 10 pF200 V CLKout Low Output Low Voltage 0.1V V CLKout High Output High Voltage Vddo-0.1 R CLKoutOutput Resistance50 ohm t jRMS Additive Jitterf CLKout = 156.25 MHz,CMOS input slew rate ≥ 2 V/ns C L = 5 pF, BW = 12 kHz to 20 MHz30fs 4L M K 00101 U l t r a -l o w J i t t e r L V C M O S F a n o u t B u f f e r /L e v e l T r a n s l a t o r w i t h U n i v e r s a l I n p u tSymbol Parameter Test ConditionsMin Typ Max UnitsDigital Inputs (OE, SEL0, SEL1)V Low Input Low Voltage Vdd = 2.5 V 0.4VV High Input High Voltage Vdd = 2.5 V 1.3 Vdd = 3.3 V1.6 I IH High Level Input Current 50uAI IL Low Level Input Current -5 5CLKin0/0* and CLKin1/1* Input Clock Specifications, (Note 9, Note 10)I IH High Level Input Current V CLKin = Vdd 20uA I IL Low Level Input Current(Note 8)V CLKin = 0 V-20 uA V IH Input High Voltage Vdd VV ILInput Low VoltageGND V CMDifferential InputCommon Mode Input Voltage(Note 12)V ID = 150 mV0.5 Vdd-1.2VV ID = 350 mV 0.5 Vdd-1.1V ID = 800 mV0.5 Vdd-0.9V ID Differential Input Voltage Swing CLKin driven differentially 0.15 1.5V OSCin/OSCout Pinsf OSCinInput Frequency (Note 7)Single-Ended Input, OSCout floatingDC200MHzf XTALCrystal Frequency Input Range Fundamental Mode Crystal ESR < 200 Ω ( f Xtal ≤ 30 MHz )ESR < 120 Ω ( f Xtal > 30 MHz )(Note 11, Note 7)10 40MHzC OSCinShunt Capacitance1 pFNote 6:AC Parameters for CMOS are dependent upon output capacitive loading Note 7:Guaranteed by characterization.Note 8:V IL should not go below -0.3 volts.Note 9:See Section 12.1 Differential Voltage Measurement Terminology for definition of V ID and V OD .Note 10:Refer to application note AN-912 Common Data Transmission Parameters and their Definitions for more information.Note 11:The ESR requirements stated are what is necessary in order to ensure that the Oscillator circuitry has no start up issues. However, lower ESR values for the crystal might be necessary in order to stay below the maximum power dissipation requirements for that crystal.Note 12:When using differential signals with V CM outside of the acceptable range for the specified V ID , the clock must be AC coupled.LMK00101 Ultra-low Jitter LVCMOS Fanout Buffer/Level Translator with Universal Input30146942Iddo per Output vs Frequency50100150200250051015C U R R E N T (m A )FREQUENCY (MHz)Cload = 10 pFVddo = 1.5 V Vddo = 1.8 V Vddo = 2.5 V Vddo = 3.3 V 30146976Note 13:Test conditions: LVCMOS Input, slew rate ≥ 2 V/ns, C L = 5 pF in parallel with 50 6L M K 00101 U l t r a -l o w J i t t e r L V C M O S F a n o u t B u f f e r /L e v e l T r a n s l a t o r w i t h U n i v e r s a l I n p u t12.0 Measurement Definitions12.1 Differential Voltage Measurement TerminologyThe differential voltage of a differential signal can be de-scribed by two different definitions causing confusion when reading datasheets or communicating with other engineers. This section will address the measurement and description of a differential signal so that the reader will be able to under-stand and discern between the two different definitions when used.The first definition used to describe a differential signal is the absolute value of the voltage potential between the inverting and non-inverting signal. The symbol for this first measure-ment is typically VID or VODdepending on if an input or outputvoltage is being described.The second definition used to describe a differential signal is to measure the potential of the non-inverting signal with re-spect to the inverting signal. The symbol for this second measurement is VSSand is a calculated parameter. Nowherein the IC does this signal exist with respect to ground, it onlyexists in reference to its differential pair. VSScan be measured directly by oscilloscopes with floating references, otherwisethis value can be calculated as twice the value of VODas de-scribed in the first sectionFigure 1 illustrates the two different definitions side-by-side for inputs and Figure 2 illustrates the two different definitionsside-by-side for outputs. The VIDand VODdefinitions showVAand VBDC levels that the non-inverting and inverting sig-nals toggle between with respect to ground. VSSinput and output definitions show that if the inverting signal is consid-ered the voltage potential reference, the non-inverting signal voltage potential is now increasing and decreasing above and below the non-inverting reference. Thus the peak-to-peak voltage of the differential signal can be measured.VIDand VODare often defined in volts (V) and VSSis oftendefined as volts peak-to-peak (VPP).30146912FIGURE 1. Two Different Definitions for Differential Input Signals30146913FIGURE 2. Two Different Definitions for Differential Output Signals LMK00101 Ultra-low Jitter LVCMOS Fanout Buffer/Level Translator with Universal Input13.0 Functional DescriptionThe LMK00101 is a 10 output LVCMOS clock fanout buffer with low additive jitter that can operate up to 200 MHz. It fea-tures a 3:1 input multiplexer with a crystal oscillator input,single supply or dual supply (lower power) operation, and pin-programmable device configuration. The device is offered in a 32-pin LLP package.13.1 V dd and V ddo Power Supplies (Note 14, Note 15)Separate core and output supplies allow the output buffers to operate at the same supply as the Vdd core supply (3.3 V or 2.5 V) or from a lower supply voltage (3.3 V, 2.5 V, 1.8 V, or 1.5 V). Compared to single-supply operation, dual supply op-eration enables lower power consumption and output-level compatibility.Bank A (CLKout0 to CLKout4) and Bank B (CLKout5 to CLK-out9) may also be operated at different V ddo voltages, provid-ed neither V ddo voltage exceeds V dd .Note 14:Care should be taken to ensure the V ddo voltage does not exceed the Vdd voltage to prevent turning-on the internal ESD protection circuitry.Note 15:DO NOT DISCONNECT OR GROUND ANY OF THE V ddo PINS as the V ddo pins are internally connected within an output bank.13.2 CLOCK INPUTSThe LMK00101 has three different inputs, CLKin0/CLKin0*,CLKin1/CLKin1*, and OSCin that can be driven in different manners that are described in the following sections.13.2.1 SELECTION OF CLOCK INPUTClock input selection is controlled using the SEL0 and SEL1pins as shown in Table 1. Refer to Section 14.1 Driving the Clock Inputs for clock input requirements. When CLKin0 or CLKin1 is selected, the crystal circuit is powered down. When OSCin is selected, the crystal oscillator will start-up and its clock will be distributed to all outputs. Refer to Section 14.2Crystal Interface for more information. Alternatively, OSCin may be driven by a single ended clock, up to 200 MHz, instead of a crystal.TABLE 1. Input SelectionSEL1SEL0Input 00CLKin0, CLKin0*01CLKin1, CLKin1*1XOSCin (Crystal Mode)13.2.1.1 CLKin/CLKin* PinsThe LMK00101 has two differential inputs (CLKin0/CLKin0*and CLKin1/CLKin1*) that can be driven single-ended or dif-ferentially. They can accept AC or DC coupled 3.3V/2.5V LVPECL, LVDS, or other differential and singled ended sig-nals that meet the input requirements under the “CLKin0/0*and CLKin1/1* Input Clock Specifications” portion of the Sec-tion 10.0 El ectrical Characteristics and (Note 12). Refer to Section 14.1 Driving the Clock Inputs for more details on driv-ing the LMK00101 inputs.In the event that a Crystal mode is not selected and the CLKin pins do not have an AC signal applied to them, Table 2 fol-lowing will be the state of the outputs.TABLE 2. CLKinX Input vs. Output States CLKinX CLKinX*Output State Open Open Logic Low Logic Low Logic Low Logic Low Logic High Logic Low Logic High Logic LowLogic HighLogic Low13.3 CLOCK OUTPUTSThe LMK00101 has 10 LVCMOS outputs.13.3.1 Output Enable PinWhen the output enable pin is held High, the outputs are en-abled. When it is held Low, the outputs are held in a Low state as shown in Table 3.TABLE 3. Output Enable Pin StatesOE Outputs Low Disabled (Hi-Z)HighEnabledThe OE pin is synchronized to the input clock to ensure that there are no runt pulses. When OE is changed from Low to High, the outputs will initially have an impedance of about 400 Ω to ground until the second falling edge of the input clock. Starting with the second falling edge of the input clock,the outputs will buffer the input. If the OE pin is taken from Low to High when there is no input clock present, the outputs will either go High or Low and stay a that state; they will not oscillate. When the OE pin is taken from High to Low the out-puts will become Low after the second falling edge of the clock input and then will go to a Disabled (Hi-Z) state starting after the next rising edge.13.3.2 Using Less than Ten OutputsAlthough the LMK00101 has 10 outputs, not all applications will require all of these. In this case, the unused outputs should be left floating with a minimum copper length (Note 16) to minimize capacitance. In this way, this output will con-sume minimal output current because it has no load.Note 16:For best soldering practices, the minimum trace length should extend to include the pin solder mask. This way during reflow, the solder has the same copper area as connected pins. This allows for good, uniform fillet solder joints helping to keep the IC level during reflow. 8L M K 00101 U l t r a -l o w J i t t e r L V C M O S F a n o u t B u f f e r /L e v e l T r a n s l a t o r w i t h U n i v e r s a l I n p u t14.0 Application Information14.1 Driving the Clock InputsThe LMK00101 has two differential inputs (CLKin0/CLKin0*and CLKin1/CLKin1*) that can accept AC or DC coupled 3.3V/2.5V LVPECL, LVDS, and other differential and single ended signals that meet the input requirements specified in Sec-tion 10.0 Electrical Characteristics . The device can accept a wide range of signals due to its wide input common mode voltage range (V CM ) and input voltage swing (V ID )/dynamic range. AC coupling may also be employed to shift the input signal to within the V CM range.To achieve the best possible phase noise and jitter perfor-mance, it is mandatory for the input to have a high slew rate of 2 V/ns (differential) or higher. Driving the input with a lower slew rate will degrade the noise floor and jitter. For this rea-son, a differential input signal is recommended over single-ended because it typically provides higher slew rate and common-mode noise rejection.While it is recommended to drive CLKin0 and CLKin1 with a differential signal input, it is possible to drive them with a sin-gle ended clock. The single-ended input slew rate should be as high as possible to minimize performance degradation.The CLKinX input has an internal bias voltage of about 1.4 V,so the input can be AC coupled as shown in Figure 3, Figure 4, or Figure 5 depending upon the application.30146938FIGURE 3. Single-Ended LVCMOS Input, AC Coupling,Near and Far End Termination30146943FIGURE 4. Single-Ended LVCMOS Input, AC Coupling,Near End Termination30146944FIGURE 5. Single-Ended LVCMOS Input, AC Coupling,Far End Termination A single ended clock may also be DC coupled to CLKinX as shown in Figure 6. If the DC coupled input swing has a com-mon mode level near the devices internal bias of 1.4 V, then only a 0.1 µF bypass cap is required on CLKinX*. Otherwise,if the input swing is not optimally centered near the internal bias voltage, then CLKinX* should be externally biased to the midpoint voltage of the input swing. This can be achieved us-ing external biasing resistors, R B1 and R B2, or another low-noise voltage reference. The external bias voltage should be within the specified input common voltage (VCM) range. This will ensure the input swing crosses the threshold voltage at a point where the input slew rate is the highest.30146939FIGURE 6. Single-Ended LVCMOS Input, DC Couplingwith Common Mode Biasing If the crystal oscillator circuit is not used, it is possible to drive the OSCin input with an single-ended external clock as shown in Figure 7. Configurations similar to Figure 4 or Figure 5 could also be used as long as the OSCout pin is left floating. The input clock should be AC coupled to the OSCin pin, which has an internally generated input bias voltage, and the OSCout pin should be left floating. While OSCin provides an alterna-tive input to multiplex an external clock, it is recommended to use either differential input (CLKinX) since it offers higher op-erating frequency, better common mode, improved power supply noise rejection, and greater performance over supply voltage and temperature variations.LMK00101 Ultra-low Jitter LVCMOS Fanout Buffer/Level Translator with Universal Input30146903FIGURE 7. Driving OSCin with a Single-Ended ExternalClock 14.2 Crystal InterfaceThe LMK00101 has an integrated crystal oscillator circuit that supports a fundamental mode, AT-cut crystal. The crystal in-terface is shown in Figure 8.30146904FIGURE 8. Crystal InterfaceThe load capacitance (C L ) is specific to the crystal, but usually on the order of 18 to 20 pF. While C L is specified for the crys-tal, the OSCin input capacitance (C IN = 1 pF typical) of the device and PCB stray capacitance (C STRAY ~ 1 to 3 pF) can affect the discrete load capacitor values, C 1 and C 2. For the parallel resonant circuit, the discrete capacitor values can be calculated as follows:C L = (C 1 * C 2) / (C 1 + C 2) + C IN + C STRAY(1)Typically, C 1 = C 2 for optimum symmetry, so Equation 1 can be rewritten in terms of C 1only:C L = C 12 / (2 * C 1 ) + C IN + C STRAY(2)Finally, solve for C 1:C 1 = (C L - C IN - C STRAY ) * 2(3)Section 10.0 Electrical Characteristics provides crystal inter-face specifications with conditions that ensure start-up of the crystal, but it does not specify crystal power dissipation. The designer will need to ensure the crystal power dissipation does not exceed the maximum drive level specified by the crystal manufacturer. Overdriving the crystal can cause pre-mature aging, frequency shift, and eventual failure. Drive level should be held at a sufficient level necessary to start-up and maintain steady-state operation.The power dissipated in the crystal, P XTAL , can be computed by:P XTAL = I RMS 2 * R ESR * (1 + C 0 / C L )2(4)Where:•I RMS is the RMS current through the crystal.•R ESR is the maximum equivalent series resistance specified for the crystal.•C L is the load capacitance specified for the crystal.•C 0 is the minimum shunt capacitance specified for the crystal.I RMS can be measured using a current probe (e.g. Tektronix CT-6 or equivalent) placed on the leg of the crystal connected to OSCout with the oscillation circuit active.As shown in Figure 8, an external resistor, R LIM , can be used to limit the crystal drive level if necessary. If the power dissi-pated in the selected crystal is higher than the drive level specified for the crystal with R LIM shorted, then a larger resis-tor value is mandatory to avoid overdriving the crystal. How-ever, if the power dissipated in the crystal is less than the drive level with R LIM shorted, then a zero value for R LIM can be used.As a starting point, a suggested value for R LIM is 1.5 k Ω14.3 Power Supply Ripple RejectionIn practical system applications, power supply noise (ripple)can be generated from switching power supplies, digital ASICs or FPGAs, etc. While power supply bypassing will help filter out some of this noise, it is important to understand the effect of power supply ripple on the device performance.When a single-tone sinusoidal signal is applied to the power supply of a clock distribution device, such as LMK00101, it can produce narrow-band phase modulation as well as am-plitude modulation on the clock output (carrier). In the single-side band phase noise spectrum, the ripple-induced phase modulation appears as a phase spur level relative to the car-rier (measured in dBc).For the LMK00101, power supply ripple rejection (PSRR),was measured as the single-sideband phase spur level (in dBc) modulated onto the clock output when a ripple signal was injected onto the V ddo supply. The PSRR test setup is shown in Figure 9.30146940FIGURE 9. PSRR Test SetupA signal generator was used to inject a sinusoidal signal onto the V ddo supply of the DUT board, and the peak-to-peak ripple amplitude was measured at the V ddo pins of the device. A lim-iting amplifier was used to remove amplitude modulation on the differential output clock and convert it to a single-ended signal for the phase noise analyzer. The phase spur level measurements were taken for clock frequencies of 100 MHz under the following power supply ripple conditions:•Ripple amplitude: 100 mVpp on V ddo = 2.5 V •Ripple frequency: 100 kHzAssuming no amplitude modulation effects and small index modulation, the peak-to-peak deterministic jitter (DJ) can be calculated using the measured single-sideband phase spur level (PSRR) as follows:10L M K 00101 U l t r a -l o w J i t t e r L V C M O S F a n o u t B u f f e r /L e v e l T r a n s l a t o r w i t h U n i v e r s a l I n p u t分销商库存信息:NATIONAL-SEMICONDUCTORLMK00101SQX/NOPB LMK00101SQ/NOPB LMK00101SQE/NOPB LMK00101BEVAL/NOPB。

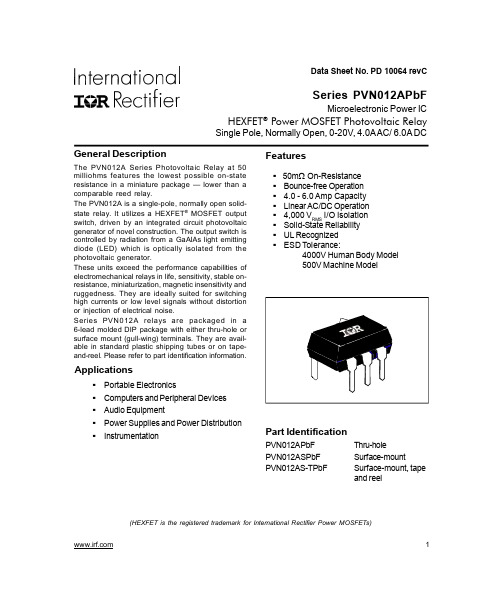

PVN012AS-TPBF;PVN012APBF;PVN012ASPBF;中文规格书,Datasheet资料

Data Sheet No. PD 10064 revCSeries PVN012APbFMicroelectronic Power ICHEXFET ® Power MOSFET Photovoltaic RelaySingle Pole, Normally Open, 0-20V, 4.0A AC/ 6.0A DCGeneral DescriptionThe PVN012A Series Photovoltaic Relay at 50milliohms features the lowest possible on-state resistance in a miniature package — lower than a comparable reed relay.The PVN012A is a single-pole, normally open solid-state relay. It utilizes a HEXFET ® MOSFET output switch, driven by an integrated circuit photovoltaic generator of novel construction. The output switch is controlled by radiation from a GaAlAs light emitting diode (LED) which is optically isolated from the photovoltaic generator.These units exceed the performance capabilities of electromechanical relays in life, sensitivity, stable on-resistance, miniaturization, magnetic insensitivity and ruggedness. They are ideally suited for switching high currents or low level signals without distortion or injection of electrical noise.Series PVN012A relays are packaged in a 6-lead molded DIP package with either thru-hole or surface mount (gull-wing) terminals. They are avail-able in standard plastic shipping tubes or on tape-and-reel. Please refer to part identification information.Applications§Portable Electronics§Computers and Peripheral Devices §Audio Equipment§Power Supplies and Power Distribution §InstrumentationPart IdentificationPVN012APbF Thru-holePVN012ASPbF Surface-mountPVN012AS-TPbFSurface-mount, tape and reel(HEXFET is the registered trademark for International Rectifier Power MOSFETs)Features§ 50m W On-Resistance §Bounce-free Operation § 4.0 - 6.0 Amp Capacity §Linear AC/DC Operation §4,000 V RMS I/O Isolation §Solid-State Reliability §UL Recognized §ESD Tolerance:4000V Human Body Model 500V Machine Model1Series PVN012APbF 2Electrical Specifications (-40°C £ T A £ +85°C unless otherwise specified )International Rectifier does not recommend the use of this product in aerospace, avionics, military or life support ers of this International Rectifier product in such applications assume all risks of such use and indemnify International Rectifier against all damages resulting from such use.Series PVN012APbF 3* Derating of ‘B’ and ‘C’ connections at +85 C will be 70% of that specified at +40 C and is linear from +40 C to +85 C.Series PVN012APbF 4(Current Controlled)Leakage Figure 7. Typical Delay Times Figure 8. Delay Time DefinitionsCase Outlines233 Kansas St., El Segundo, California 90245 Tel: (310) 252-7105qualified for the Industrial marketchange without notice. 2/2008分销商库存信息:IRPVN012AS-TPBF PVN012APBF PVN012ASPBF。

3590S-2-502L;3590S-2-102L;3590S-2-103L;3590S-2-203L;3590S-1-502L;中文规格书,Datasheet资料

Specifi cations are subject to change without notice.Customers should verify actual device performance in their specifi c applications.*RoHS Directive 2002/95/EC Jan. 27, 2003 including annex and RoHS Recast 2011/65/EU June 8, 2011.Stop Strength..............................................................................................................................................................................45 N-cm (64 oz.-in.) minimum Mechanical Angle ...........................................................................................................................................................................................3600 ° +10 °, -0 °Torque (Starting & Running) ................................................................................................................................0.35 N-cm (0.5 oz.-in.) maximum (unsealed) 1.1 N-cm (1.5 oz.-in.) maximum (sealed) Mounting ..............................................................................................................................................................................55-80 N-cm (5-7 lb.-in.) (plastic) 90-113 N-cm (8-10 in.-lb.) (metal)Shaft Runout......................................................................................................................................................................................0.13 mm (0.005 in.) teral Runout ...................................................................................................................................................................................0.20 mm (0.008 in.) T.I.R.Shaft End Play ...................................................................................................................................................................................0.25 mm (0.010 in.) T.I.R.Shaft Radial Play ...............................................................................................................................................................................0.13 mm (0.005 in.) T.I.R.Pilot Diameter Runout .......................................................................................................................................................................0.08 mm (0.003 in.) T.I.R.Backlash ............................................................................................................................................................................................................1.0 ° maximum Weight ........................................................................................................................................................................................................Approximately 19 G Terminals ................................................................................................................................................................................................Solder lugs or PC pins Soldering ConditionManual Soldering...........................................................96.5Sn/3.0Ag/0.5Cu solid wire or no-clean rosin cored wire; 370 °C (700 °F) max. for 3 seconds Wave Soldering ...................................................................................96.5Sn/3.0Ag/0.5Cu solder with no-clean fl ux; 260 °C (500 °F) max. for 5 seconds Wash processes .......................................................................................................................................................................................Not recommended Marking .....................................Manufacturer’s name and part number, resistance value and tolerance, linearity tolerance, wiring diagram, and date code.Ganging (Multiple Section Potentiometers) ......................................................................................................................................................1 cup maximum Hardware ............................................................................................................One lockwasher and one mounting nut is shipped with each potentiometer.NOTE: For Anti-rotation pin add 91 after confi guration dash number. Example: -2 becomes -291 to add AR pin.1At room ambient: +25 °C nominal and 50 % relative humidity nominal, except as noted. 2Consult manufacturer for complete specifi cation details for resistances below 1k ohms.BOLDFACE LISTINGS ARE IN STOCK AND READILY AVAILABLETHROUGH DISTRIBUTION. FOR OTHER OPTIONS CONSULT FACTORY.ROHS IDENTIFIER: L = COMPLIANTRecommended Part Numbers(Printed Circuit)(Solder Lug)(Solder Lug)Resistance (Ω)Resolution (%)3590P-2-102L 3590S-2-102L 3590S-1-102L 1,000.0293590P-2-202L 3590S-2-202L 3590S-1-202L 2,000.0233590P-2-502L 3590S-2-502L 3590S-1-502L 5,000.0253590P-2-103L 3590S-2-103L 3590S-1-103L 10,000.0203590P-2-203L 3590S-2-203L 3590S-1-203L 20,000.0193590P-2-503L 3590S-2-503L 3590S-1-503L 50,000.0133590P-2-104L3590S-2-104L3590S-1-104L100,000.009*Ro H S C O MP L I A N T/Panel Thickness Dimensions(For Bushing Mount Only)1.60 +.08/-.03(.063 +.003/-.001)DIA.ANTI-ROTATION PINAnti-rotation pin hole is shown at six o'clockposition for reference only. The actual location isdetermined by the customer's application. Referto the front view of the potentiometer to see thelocation of the optional A/R pin.Panel thickness and hole diameters arerecommended for best fit. However, customersmay adjust the dimensions to suit their specificapplication.Product DimensionsSpecifi cations are subject to change without notice.Customers should verify actual device performance in their specifi c applications.REV. 06/12 MOUNTING SURFACE-2, -4, -6, -8 Confi gurations-1, -3, -5, -7 Confi gurationsRecommended PCB LayoutHOLE DIAMETER5.08(.200)5.08(.200)6.99(.275)SchematicTOLERANCES: EXCEPT WHERE NOTED.508 .127DECIMALS: .XX ±(.02),.XXX ±(.005)FRACTIONS: ±1/64MMDIMENSIONS:(IN.)Shaft & Bushing Confi gurations(Bushing - DxL, Shaft - D):(-1) Plastic Bushing (3/8 ” x 5/16 ”)and Shaft (.2480 + .001, - .002)(-2) Metal Bushing (3/8 ” x 5/16 ”)and Shaft (.2497 + .0000, - .0009)(-3) Sealed, Plastic Bushing (3/8 ” x 5/16 ”)and Shaft (.2480 + .001, - .002)(-4) Sealed, Metal Bushing (3/8 ” x 5/16 ”)and Shaft (.2497 + .0000, - .0009)(-5) Metric, Plastic Bushing (9 mm x 7.94 mm)and Shaft (6 mm + 0, - .076 mm)(-6) Metric, Metal Bushing (9 mm x 7.94 mm)and Shaft (6 mm + 0, - .023 mm)(-7) Metric, Sealed, Plastic Bushing (9 mm x7.94 mm) and Shaft (6 mm + 0, - .076 mm)(-8) Metric, Sealed, Metal Bushing (9 mm x7.94 mm) and Shaft (6 mm + 0, - .023 mm)Terminal Styles“P” Terminal Style“S” Terminal Style/分销商库存信息:BOURNS3590S-2-502L3590S-2-102L3590S-2-103L 3590S-2-203L3590S-1-502L3590S-2-104L 3590S-1-203L3590S-2-501L3590S-2-202L 3590S-1-503L3590S-2-503L3590S-1-104L 3590S-291-102L3590S-291-203L3590S-291-502L 3590S-1-201L3590S-1-501L3590S-2-101L 3590S-2-201L3590P-1-102L3590P-1-103L 3590P-1-201L3590P-1-502L3590S-1-102L 3590S-1-103L3590S-2-252L3590P-291-501L 3590P-2-102L3590P-2-201L3590P-2-203L 3590P-2-502L3590S-1-202L3590S-6-102L 3590S-6-201L3590S-6-202L3590S-6-203L 3590S-6-501L3590P-1-104L3590S-6-502L 3590S-4-102L3590S-4-103L3590S-4-202L 3590S-4-203L3590S-4-502L3590S-8-102L 3590S-8-103L3590S-8-202L3590P-2-104L 3590P-4-103L3590P-4-202L3590S-6-503L 3590S-6-104L3590S-4-104L3590P-4-503L 3590P-4-104L3590S-2-5023590S-1-102 3590S-1-1033590S-1-1043590S-1-203 3590S-1-5023590S-1-5033590S-2-102 3590S-2-1033590S-2-1043590S-2-203 3590S-2-5033590S-1-2023590S-2-202 3590S-2-501。

T1620-600W;T1620-700W;T1630-600W;中文规格书,Datasheet资料

October 2011Doc ID 3759 Rev 11/8T1620W, T1630WSnubberless™ 16A TriacsFeatures■I T(RMS) = 16 A■V DRM / V RRM = 600, 700 and 800 V ■I GT = 20 to 30 mADescriptionBased on ST’s Snubberless technology providing high commutation performances, theT1620-600W/700W/800W and T1630-600W are especially recommended for use with inductive loads such as rice cookers. They comply with UL standards (ref. E81734).TM : Snubberless is a trademark of STMicroelectronicsCharacteristics T1620W, T1630W2/8Doc ID 3759 Rev 11 CharacteristicsTable 1.Absolute maximum ratingsSymbol ParameterValue Unit I T(RMS)On-state rms current (full sine wave)T c = 80 °C 16A I TSM Non repetitive surge peak on-state current (full cycle, T j initial = 25 °C) F = 50 Hz t = 20 ms 200A F = 60 Hz t = 16.7 ms218I ²t I ²t Value for fusingt p = 10 ms220A ²s dI/dtCritical rate of rise of on-state current I G = 2 x I GT , t r≤ 100 nsF = 120 HzT j = 125 °C 50A/µs V DSM /V RSM Non repetitive surge peak off-statevoltage t p = 10 ms T j = 25 °C V DRM /V RRM+ 100V I GM Peak gate currentt p = 20 µsT j = 125 °C 4A P G(AV)Average gate power dissipation T j = 125 °C 1W T stgT jStorage junction temperature range Operating junction temperature range- 40 to + 150- 40 to + 125°CTable 2.Electrical characteristics (T j = 25 °C, unless otherwise specified)Symbol Test conditionsQuadrantValueUnitT1620T1630I GT (1)V D = 12 V R L = 30 ΩI - II - III MAX.2030mA V GT I - II - III MAX. 1.3V V GD V D = V DRM , R L = 3.3 k Ω, T j = 125 °C I - II - IIIMIN.0.2V I H (2)I T = 250 mA MAX.3550mA I LI G = 1.2 I GTI - III MAX.7080mA II 80100dV/dt (2)V D = 67% V DRM, gate open, T j = 125 °C MIN.300500V/µs (dI/dt)c(2)Without snubber, T j = 125 °CMIN.8.511A/ms 1.minimum I GT is guaranted at 5% of I GT max.2.for both polarities of A2 referenced to A1.T1620W, T1630W CharacteristicsDoc ID 3759 Rev 13/8Table 3.Static characteristicsSymbol Test conditionsValue Unit V T (1)I TM = 22.5 A, t p = 380 µs T j = 25 °C MAX. 1.4V V TO (1)Threshold voltage T j = 125 °C MAX.0.85V R D (1)Dynamic resistance T j = 125 °C MAX.250m ΩI DRM I RRMV DRM = V RRMT j = 25 °C MAX.5µA T j = 125 °C1mA1.for both polarities of A2 referenced to A1.Table 4.Thermal resistanceSymbol ParameterValue Unit R th(j-c)Junction to case (AC) (360° conduction angle) 3.1 °C/W R th(j-a)Junction to ambient60°C/WFigure 1.Maximum power dissipation versusFigure 2.On-state rms current versus caseFigure 3.Relative variation of thermalFigure 4.On-state characteristicsCharacteristicsT1620W, T1630W4/8Doc ID 3759 Rev 1Figure 9.Relative variation of critical rate of decrease of main current versus junctionFigure 5.Surge peak on-state current versus Figure 6.Non-repetitive surge peak on-state Figure 7.Relative variation of I GT ,I H , I L vs junction temperature Figure 8.Relative variation of critical rate of decrease of main current versusT1620W, T1630W Ordering information schemeDoc ID 3759 Rev 15/82 Ordering information schemeTable 5.Product SelectorPart Numbers Voltage (xxx)SensitivityTypePackage600 V700 V800 VT1620-600W X20 mASnubberless ISOWA TT220ABT1620-700W XT1620-800W XT1630-600WX30 mAPackage mechanical data T1620W, T1630W3 Package mechanical data●Epoxy meets UL94, V0●Recommended torque 0.4 to 0.6 N·mIn order to meet environmental requirements, ST offers these devices in different grades ofECOPACK® packages, depending on their level of environmental compliance. ECOPACK®specifications, grade definitions and product status are available at: .ECOPACK® is an ST trademark.6/8Doc ID 3759 Rev 1T1620W, T1630W Ordering InformationDoc ID 3759 Rev 17/84 Ordering Information5 Revision historyTable 7.Ordering informationOrder code Marking PackageWeightBase qtyDelivery modeT1620-600W T1620600W ISOWA TT220AB2.3 g50TubeT1620-700W T1620700W T1620-800W T1620800W T1630-600WT1630600WTable 8.Document revision historyDate RevisionChangesMar-20042Last update.18-Oct-20113Insert T1620-700W, Insert 700 V in fig.10,deleted T1630-800W.T1620W, T1630WPlease Read Carefully:Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.All ST products are sold pursuant to ST’s terms and conditions of sale.Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.UNLESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. UNLESS EXPRESSLY APPROVED IN WRITING BY TWO AUTHORIZED ST REPRESENTATIVES, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER’S OWN RISK.Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.ST and the ST logo are trademarks or registered trademarks of ST in various countries.Information in this document supersedes and replaces all information previously supplied.The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.© 2011 STMicroelectronics - All rights reservedSTMicroelectronics group of companiesAustralia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America8/8Doc ID 3759 Rev 1分销商库存信息:STMT1620-600W T1620-700W T1630-600W。

744272251;中文规格书,Datasheet资料