74LS192引脚图管脚及功能表

LS引脚图管脚及功能表最新文档

LS引脚图管脚及功能表最新文档(可以直接使用,可编辑最新文档,欢迎下载)十进制可逆计数器74LS192引脚图管脚及功能表74LS192是同步十进制可逆计数器,它具有双时钟输入,并具有清除和置数等功能,其引脚排列及逻辑符号如下所示:图5-4 74LS192的引脚排列及逻辑符号(a)引脚排列 (b) 逻辑符号图中:为置数端,为加计数端,为减计数端,为非同步进位输出端,为非同步借位输出端,P0、P1、P2、P3为计数器输入端,为清除端,Q0、Q1、Q2、Q3为数据输出端。

其功能表如下:输入输出MR P3 P2 P1 P0 Q3 Q2 Q1 Q01 ×××××××0 0 0 00 0 ×× d c b a d c b a0 1 1 ××××加计数0 1 1 ××××减计数1. 前台功能方案41.1主页面41.2 商品搜索41.3 商品列表41.4 虚拟分类51.5 商品展示516 会员中心51.7 购物车61.8 促销专题71.9 帮助中心72 后端管理72.1 商品72.2 订单102.3 会员112.4 营销推广122.5 模版设计132.6 系统工具132.7 商店配置132.8 网站内容管理142.9 统计报表142.10 系统工具151. 前台功能方案1.1主页面主分类导航商品搜索广告公告商品分类推荐商品虚拟分类(快速检索链接)最新发货信息最新留言自定义版块1.2 商品搜索分词搜索货号糊模搜索商品关键词搜索(配合商品关键词)1.3 商品列表无限商品分类按商品规格筛选列表按销量、人气、价格筛选排序热卖排行顾客游览过的商品快速订货1.4 虚拟分类虚拟分类(快速检索链接)1.5 商品展示商品规格选择相册图片展示立刻购买与加入购物车功能16 会员中心交易记录我的订单我的积分积分兑换优惠券我的优惠券收藏夹商品留言评论与咨询个人设置个人信息修改密码收货地址预存款管理站内消息管理1.7 购物车所购商品名称列表商品积分销售价格优惠价格数量小计商品总额商品享受订单优惠说明功能按钮按货号订购购物车商品EXCEL 下载继续购物清空购物车使用优惠券去结算1.8 促销专题1.9 帮助中心购物流程图购物指南新手上路支付与配送1.11 会员注册登陆弹会员注册或登陆1.12 评论/咨询/留言更简化的评论咨询页面1.13 友情链接支持图文链接2 后端管理2.1 商品商品管理批量操作商品上架商品下架统一调价分别调价统一调库存分别调库存商品名称商品简介商品品牌商品排序商品重量分类转换类型转换添加商品一键调用相册图片添加相关商品商品搜索货号模糊搜索商品筛选按名称按货号按商品标签按商品分类按商品品牌按商品销售价商品CSV 导入商品CSV 导出商品定时上下架货品上下架商品页SEO 功能商品分类无级分类管理自定义分类模板分类页SEO 功能虚拟分类商品类型商品类型管理商品类型下载商品类型导入扩展属性管理商品规格商品规格管理商品规格导入品牌管理品牌名称、网址,LOGO 添加管理品牌页SEO 功能自定义品牌页模板品牌关联商品类型商品批量上传CSV 文件下载上传CSV 文件第三方平台CSV 上传配置CSV 上传2.2 订单订单管理添加订单订单状态操作管理订单支付订单发货订单退款订单退货订单作废订单标签订单筛选订单导出订单打印配货单打印购物清单打印订单打印样式管理购物清单样式配货单样式单据管理收款单管理退款单管理发货单管理退货单管理售后服务管理快递单管理快递单模板添加快递单模板编辑快递单模板下载快递单模板导出发货信息管理2.3 会员会员管理会员等级管理群发邮件群发消息群发短信批量编辑批量修改会员等级批量修改积分会员筛选会员导出会员注册项管理统计报表预存款充值/冻结冻结列表预存款交易报表购买咨询管理商品评论管理商店留言管理站内消息管理2.4 营销推广批发方案混批方案管理批发方案管理SEO 设置管理SiteMaps 管理站外推广链接2.5 模版设计网站内容管理站点栏目管理文章管理友情链接网页底部信息管理模板管理模板编辑模板下载图片管理样式管理模板在线预览2.6 系统工具2.7 商店配置全站设置基本设置购物显示设置商品图片设置支付管理支付方式添加编辑管理配送管理配送方式添加编辑管理配送费用管理配送地区管理权限分配管理角色权限分配管理货币管理第三方整合地区管理2.8 网站内容管理2.9 统计报表访问统计预付款统计销售统计销售额总览销售量排名会员购物量排名商品访问购买次数销售指标分析2.10 系统工具数据管理数据备份数据恢复数据库校验体验数据清除网店暂停营业页面显示管理2.11 第三方应用扩展插件1 采购单中心1、1 供应商管理供应商列表更新列表同步更新采购价同步最后同步时间代销商品列表我的采购单商品数据下载1、2 采购单列表刷新导出筛选1、3 同步更新配置添加配置添加规则选择供应商针对产品线1、4 配置列表添加配置刷新删除回收站增加:供应商内部进销存项目招投标项目及产品的智能匹配支付可以整体支付给平台,也可以通过参数设置支付到每个供应商;项目招投标暂时不需要网上支付增加中介管理:中介可以发布招标信息和求购信息原则上:游客浏览网站,先注册会员,会员可以购买产品和投标项目,可以发布求购信息,但是不能上架产品及发布招标信息,通过平台认证后,方可;通过开店认证,该会员具有发布新产品、发布招标信息;会员也可以通过认证成为中介;B2B(Business To Business),是指一个市场的领域的一种,是企业对企业之间的营销关系。

集成计数器74LS192的使用

图 六进制计数

集成计数器74LS192的使用

计数器的级联使用 利用进பைடு நூலகம்输出控制高一位的CPU端构成的加数级联图

用两个 74LS192集成构计数成器714L0S1092的进使用制计数器

▲ 利用74LS192实现100进制计数器 (想一想)

将多个74LS192级联可以构成高位计数器。

画出逻辑电路图。

集成计数器74LS192的使用

0 0 × × d0 d1 d2 d3 d0 d1 d2 d3 1 0 ↑ 1 ×××× 加计数

1 0 1 ↑ ×××× 减计数

1 0 1 1 ×××× 保 持

× 1 × × ×××× 0 0 0 0

各引脚功能符号的意义:

D0~D3:并行数据输入端 Q0~Q3:数据输出端 CU:加法计数脉冲输入端 CD:减法计数脉冲输入端 RD :异步置 0 端(高电平有效) LD :置数控制端(低电平有效)

集成计数器 74LS192的使用

集成计数器74LS192的使用

74LS192是同步可拟计数器,具有双时钟输入, 并具有清除和置数等功能

集成计数器74LS192的使用

集成计数器74LS192的使用

同步十进制计数器——74LS192集成计数器

▲ 逻辑符号

▲ 74LS192功能表

输入

输出

LD RD CU CD D0 D1 D2 D3 Q0 Q1 Q2 Q3

的

时

序

0

10

0

00

01

图 分

00

析

0

00

00

0

10

01

集成计数器74LS192的使用

三、实验内容及步骤

芯片74LS192中文资料

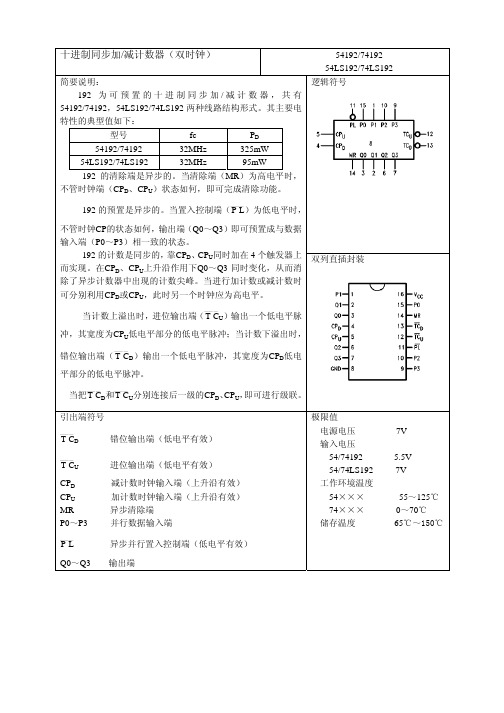

十进制同步加/减计数器(双时钟)54192/7419254LS192/74LS192 逻辑符号简要说明:192为可预置的十进制同步加/减计数器,共有54192/74192,54LS192/74LS192两种线路结构形式。

其主要电特性的典型值如下:型号 fc P D54192/74192 32MHz 325mW 54LS192/74LS192 32MHz 95mW 192的清除端是异步的。

当清除端(MR )为高电平时,不管时钟端(CP D 、CP U )状态如何,即可完成清除功能。

192的预置是异步的。

当置入控制端(P __L _)为低电平时,不管时钟CP 的状态如何,输出端(Q0~Q3)即可预置成与数据输入端(P0~P3)相一致的状态。

192的计数是同步的,靠CP D 、CP U 同时加在4个触发器上而实现。

在CP D 、CP U 上升沿作用下Q0~Q3同时变化,从而消除了异步计数器中出现的计数尖峰。

当进行加计数或减计数时可分别利用CP D 或CP U ,此时另一个时钟应为高电平。

当计数上溢出时,进位输出端(T __C _U )输出一个低电平脉冲,其宽度为CP U 低电平部分的低电平脉冲;当计数下溢出时,错位输出端(T __C _D )输出一个低电平脉冲,其宽度为CP D 低电平部分的低电平脉冲。

当把T __C _D 和T __C _U 分别连接后一级的CP D 、CP U ,即可进行级联。

双列直插封装引出端符号T __C _D 错位输出端(低电平有效)T __C _U 进位输出端(低电平有效)CP D 减计数时钟输入端(上升沿有效) CP U 加计数时钟输入端(上升沿有效) MR 异步清除端P0~P3 并行数据输入端P __L _异步并行置入控制端(低电平有效)Q0~Q3 输出端 极限值电源电压 7V 输入电压54/74192 5.5V 54/74LS192 7V 工作环境温度54××× -55~125℃ 74××× 0~70℃储存温度 -65℃~150℃功能表状态图推荐工作条件:54/74192 54/74LS192单位最小额定最大最小额定最大54 4.5 5 5.5 4.5 5 5.5V 电源电压V CC5.2555.2574 4.7554.75输入高电平电压V iH 2 2 V54 0.8 0.7V 输入低电平电压V iL74 0.8 0.8uA 输出高电平电流I OH-400 -400mA54 16 4输出低电平电流I OL74 16 8MHz 时钟频率fcp 0 25 0 20脉冲宽度T W CP 20 20 nsnsP 20 20 建立时间 tsetMR无效40 保持时间t H0 5 ns逻辑图静态特性(T A 为工作环境温度范围)‘192 LS192 单位参 数测 试 条 件【1】最小最大最小最大I ik =-12mA -1.5 V IK 输入嵌位电压 Vcc=最小,I ik =-18mA-1.5V 54 2.4 2.5 V OH 输出高电平电压 Vcc =最小V IH =2V V IL =最大, I OH =-400µA 74 2.4 2.7 V540.4 0.4V OL 输出低电平电压 Vcc=最小,V IH =2V , V IL =最大,I OL =最大 74 0.4 0.5V I I 最大输入电压时输入电流Vcc =最大V I =5.5V (LS192为7V )1 0.1 mA I IH 输入高电平电流Vcc =最大V IH =2.4V (LS192为2.7V )40 20 µA I IL 输入低电平电流 Vcc =最大,V IL =0.4V -1.6 -0.4 mA54 -20 -65 -20 -100 I OS 输出短路电流 Vcc =最大74 -18 -65 -20 -100mA 54 89 34 I CC 电源电流Vcc =最大,MR 和P __L _接地,其余接4.5V74 102 34mA [1]: 测试条件中的“最小”和“最大”用推荐工作条件中的相应值。

74LS192是双时钟方式的十进制可逆计数器

74LS192是双时钟方式的十进制可逆计数器。

(bcd,二进制)。

◆ CPU为加计数时钟输入端,CPD为减计数时钟输入端。

◆ LD为预置输入控制端,异步预置。

◆ CR为复位输入端,高电平有效,异步清除。

◆ CO为进位输出:1001状态后负脉冲输出,◆ BO为借位输出:0000状态后负脉冲输出。

74ls192引脚图:74ls192功能表:74LS192是属8421BCD码的十进制计数器,其功能真值表如表4所示。

其中MR是异步清零端,高电平有效。

PL(———)是并行置数端,低电平有效,且在MR=0有效。

CPU和CPu是两个时钟脉冲,当CPd=1,时钟脉冲由CPU端接入。

并且MR=0,PL(———)=1时,74LS192处于加法计数状态;当CPu脉冲从CPd端输入,且MR=0,PL(———)=1时,74LS192处于减法计数状态;CPd=CPu=1时,计数器处于保持状态。

TCu是进位端,TCd是借位端。

表4 74LS192功能真值表MR PL(———)CPu CPd P3 P2 P1 P0 Q3x+1 Q2x+1 Q1x+1 1 ×××××××00 00 1 ×↑d3 d2 d1 d0 d3d2 d10 1 ↑ 1 ××××加法计数0 1 1 ↑××××减法计数0 1 1 1 ××××保持74192的工作原理是:当LD(———)=1,MR=0时,若时钟脉冲加到CPu端,且CPd =1则计数器在预置数的基础上完成加计数功能,当加计数到9时,TCu端发出进位下跳变脉冲;若时钟脉冲加到CPd端,且CPu =1,则计数器在预置数的基础上完成减计数功能,当减计数到0时,TCd 端发出借位下跳变脉冲。

74LS192具有下述功能:①异步清零:MR=1,Q3Q2Q1Q0=0000②异步置数:MR=0,PL(———)=0,Q3Q2Q1Q0=P3P2P1P0③保持:MR=0,PL(———)=1,CPu=CPd=1,Q3Q2Q1Q0保持原态④加计数:MR=0, PL(———)=1,CPu=CP,CPd=1,Q3Q2Q1Q0按加法规律计数⑤减计数:MR=0, PL(———)=1,CPu=1,CPd= CP,Q3Q2Q1Q0按减法规律计数。

74LS192芯片总结[大全五篇]

![74LS192芯片总结[大全五篇]](https://img.taocdn.com/s3/m/50bc931d657d27284b73f242336c1eb91a37333a.png)

74LS192芯片总结[大全五篇]第一篇:74LS192芯片总结74LS192引脚图管脚及功能表74LS192是同步十进制可逆计数器,它具有双时钟输入,并具有清除和置数等功能,其引脚排列及逻辑符号如下所示:(a)引脚排列(b)逻辑符号图中:为置数端,为加计数端,为减计数端,为非同步进位输出端,计数器输入端,为非同步借位输出端,P0、P1、P2、P3为为清除端,Q0、Q1、Q2、Q3为数据输出端。

其功能表如下:例如:用74LS192芯片设计出三十进制计数器用 192 采用级联法做成 3*10 的一个芯片满十进一另一个芯片到3 即0011的时候提供清零脉冲恢复到0000详见图第二篇:常用芯片总结常用芯片总结1.音频pcm编码DA转换芯片cirrus logic的cs4344,cs43344334是老封装,据说已经停产,4344封装比较小,非常好用。

还有菲利谱的8211等。

2.音频放大芯片4558,LM833,5532,此二芯片都是双运放。

3.244和245,由于244是单向a=b的所以只是单向驱动。

而245是用于数据总线等双向驱动选择。

同时245的封装走线非常适合数据总线,它按照顺序d7-d0。

4.373和374,地址锁存器,5.max232和max202,max3232 TTL电平转换6.网络接口变压器。

需要注意差分信号的等长和尽量短的规则。

7.amd29系列的flash,有bottom型和top型,主要区别是loader区域设置在哪里?bottom型的在开始地址空间,top型号的在末尾地址空间,我感觉有点反,但实际就是这么命名的。

8.74XX164,它是一个串并转换芯片,可以把串行信号变为并行信号,控制数码管显示可以用到。

9.网卡控制芯片CS8900,ax88796,rtl8019as,dm9000ae当然这些都是用在isa总线上的。

24位AD:CS5532,LPC2413,ADS1240,ADS1241效果还可以仪表运放:ITL114,不过据说功耗有点大音频功放:一般用LM368音量控制IC:PT2257,Pt2259.PCM双向解/编码:/ CW6691.cirruslogic公司比较多2.4G双工通讯IC CC25001.cat809,max809,这些是电源监控芯片,当低于某一电压以后比如3.07v等出现一个100ms的低电平,实现复位功能。

中规模十进制计数器74LS192(或CC40192)

中规模十进制计数器74LS192(或CC40192)3、中规模十进制计数器74LS192(或CC40192)74LS192是同步十进制可逆计数器,它具有双时钟输入,并具有清除和置数等功能,其引脚排列及逻辑符号如下所示:图14-4 74LS192的引脚排列及逻辑符号(a)引脚排列 (b) 逻辑符号图中:(LD)为置数端,为加计数端,为减计数端,(CO)为非同步进PLCPCPTCUDU 位输出端 (BO)为非同步借位输出端,P0(D)、P1、P2、P3为计数器输入端,(CR)MRTC0D为清除端,Q0、Q1、Q2、Q3为数据输出端。

计数器及其应用(设计性)一、实验目的1(学习集成触发器构成计数器的方法。

2(掌握中规模集成计数器的使用方法及功能侧试方法。

3(用集成电路计数器构成1,N分频器。

二、实验预习要求1(复习计数器电路工作原理。

2(预习中规模集成电路计数器74LS192的逻辑功能及使用方法。

3(复习实现任意进制计数的方法。

三、实验原理计数器是典型的时序逻辑电路,它是用来累计和记忆输入脉冲的个数(计数是数字系统中很重要的基本操作,集成计数器是最广泛应用的逻辑部件之一。

计数器种类较多,按构成计数器中的多触发、器是否使用一个时钟脉冲源来分,有同步计数器和异步计数器;根据计数制的不同,可分为二进制计数器、十进制计数器和任意进制计数器:根据计数的增减趋势,又分为加法、减法和可逆计数器。

还有可预置数和可编程序功能计数器等。

本实验主要研究中规模十进制计数器74LS192的功能及应用。

1. 74LS192的主要原理(1)74LS192是同步十进制可逆计数器,具有双时钟输入,并具有清除和置数等功能,其逻辑符号及引脚排列如图4-1所示。

图4—1 74LS192逻辑符号及引脚排列图中:CPU—加计数端 CP一减计数端 /LD一置数端 CR一清零端 /CO一非同D 步进位输出端/BO一非同步借位输出端 D0、 D1、D2、 D3一数据输入端 Q0、Q1、Q2、Q3一数据输出端74LS192功能如下表4—1:(1)清零(CR)令CR=1,其它输入端状态为任意态,,记录Q3Q2Q1Q0的状态和译码显示的数值。

74ls192芯片

74ls192芯片74LS192是一种技术较老的逻辑门集成电路(IC),它是一种同步可编程计数器。

该芯片可以实现四位二进制计数,并且可以通过外部的控制信号来实现不同的计数模式和功能。

74LS192具有带锁存功能的四位二进制计数器。

它包含四个独立的计数器,每个计数器都可以通过控制端进行控制。

此外,它还有一个可编程的控制端,可以用来选择计数方向(向上计数或向下计数)以及计数模式(十进制模式、二进制模式等)。

该芯片的引脚图和引脚功能如下:1. CP0 - 输入引脚,用于时钟脉冲的输入。

2. CP1 - 输入引脚,用于时钟脉冲的输入。

3. MR - 输入引脚,用于复位计数器。

4. PC0 - 输入引脚,用于选择计数模式。

5. PC1 - 输入引脚,用于选择计数模式。

6. U/D - 输入引脚,用于选择计数方向。

7. A - 输出引脚,用于输出二进制位的最低位。

8. B - 输出引脚,用于输出二进制位的次低位。

9. C - 输出引脚,用于输出二进制位的次高位。

10. D - 输出引脚,用于输出二进制位的最高位。

11. QA - 输出引脚,用于输出BCD码的最低位。

12. QB - 输出引脚,用于输出BCD码的次低位。

13. QC - 输出引脚,用于输出BCD码的次高位。

14. QD - 输出引脚,用于输出BCD码的最高位。

15. Vcc - 正电源引脚。

16. GND - 接地引脚。

74LS192的工作原理如下:首先,需要将MR引脚置低,从而使计数器复位。

然后,通过CP0和CP1引脚输入时钟信号,控制计数器的计数速度。

U/D引脚用于选择计数方向,当U/D引脚为低电平时,计数器向上计数,当U/D引脚为高电平时,计数器向下计数。

PC0和PC1引脚用于选择计数模式。

当PC1引脚为低电平,PC0引脚为高电平时,计数器工作在二进制模式下。

当PC1引脚为高电平,PC0引脚为低电平时,计数器工作在十进制模式下。

其它的PC1和PC0的组合可以实现更多的计数模式。

集成计数器74LS192的使用

CU为高电平,计数脉冲从CD端输入。 CU为高电平 计数脉冲从CD端输入 为高电平, 端输入。

的 时 序 图

0 0 0 0

1 0 0 1

0 0 0 0

0 0 0 0

1 0 0 1

三、实验内容及步骤

1、利用一块74LS192作十进制0~9加法计数。 2、用两块74LS192组成二位计数脉冲上升沿触发的 计数电路,作十进制数0~99计数。 3、用计数器的预置BCD码的输入端和预置数装入端 设计一个22进制和特殊15进制(1-15)的计数器, 并验证该电路的正确性。

集成计数器 74LS192的使用 74LS192的使用

华东理工大学信息学院电信系

74LS192是同步可拟计数器,具有双时钟输入, 并具有清除和置2集成计数器 74LS192集成计数器 同步十进制计数器

▲ 74LS192功能表 74LS192功能表 ▲ 逻辑符号

此上升沿使十位的74LS192(2)从0000开始计数 直到第100 此上升沿使十位的74LS192(2)从0000开始计数,直到第100 开始计数, CP脉冲作用后 计数器由1001 1001恢复为 脉冲作用后, 恢复为0000 0000, 个CP脉冲作用后,计数器由1001 1001恢复为0000 0000,完成 一次计数循环。 一次计数循环。

74LS192引脚图管脚及功能表

(a)引脚排列 (b) 逻辑符号

图中:为置数端,为加计数端,为减计数端,为非同步进位输出端, 为非同步借位输出端,P0、P1、P2、P3为计数器输入端,为清除端,Q0、Q1、Q2、Q3为数据输出端。

其功能表如下:

输入

输出

MR

P3

P2

P1

P0

Q3

Q2

Q1

Q0

精品文档可修改十进制可逆计数器74ls192引脚图管脚及功能表74ls192是同步十进制可逆计数器它具有双时钟输入并具有清除和置数等功能其引脚排列及逻辑符号如下所示

十进制可逆计数器74LS192引脚图管脚及功能表

74LS192是同步十进制可逆计数器,它具有双时钟输入,并具有清除和置数等功能,其引脚排列及逻辑符号如下所示:

1

×

×

×

×

×

×

×

0

0

0

0

0

0

×

×

d

c

b

a

d

c

b

×

×

加计数

0

1

1

×

×

×

×

减计数

74ls192n的计数原理

74ls192n的计数原理74LS192N的计数原理1. 引言•介绍74LS192N是一种计数器芯片,可用于在数字电路中进行计数操作。

•本文将深入解释74LS192N计数器的基本原理。

2. 74LS192N的功能概述•74LS192N是一种可重置的4位二进制上升计数器。

•它能够根据输入时钟信号逐次递增计数,并具有可重置功能。

3. 74LS192N的引脚定义•74LS192N具有双向计数功能,其引脚定义如下:–引脚1和15:输出端Q1和∅R1–引脚2和5:输出端Q2和∅R2–引脚3和6:输出端Q3和∅R3–引脚4和7:输出端Q4和∅R4–引脚8和16:电源VCC和接地GND–引脚9:时钟输入端CP–引脚10:复位输入端MR–引脚11:时钟使能输入端CPE–引脚12和13:数据输入端A和B–引脚14:时钟输出端TC4. 计数原理•当74LS192N接收到上升沿时钟信号时,计数器会根据当前状态以及输入信号进行计数操作。

初始化•在开始计数之前,需先将使能输入端CPE置高,以确保计数器能够进行计数。

上升计数•当时钟输入端CP接收到上升沿信号时,计数器会根据当前状态进行计数操作:1.如果复位输入端MR为高电平,则计数器会被复位为0000,并将输出端Q1-Q4置为低电平。

2.如果复位输入端MR为低电平,则计数器会进行正常的上升计数操作。

•输出端Q1-Q4为计数器的二进制输出结果。

•输出端∅R1-∅R4为输出端Q1-Q4的反相输出结果。

时钟输出•时钟输出端TC为计数器的时钟输出,可用于级联多个计数器进行高位计数操作。

5. 总结•74LS192N是一个常用的可重置的4位二进制上升计数器芯片。

•它具有逐次递增计数、可重置以及多种输出功能。

•本文对74LS192N的引脚定义和计数原理进行了详细解释。

以上是关于74LS192N的计数原理的详细解释。

通过了解这些基本原理,您可以更好地理解和应用该芯片在数字电路中的计数功能。

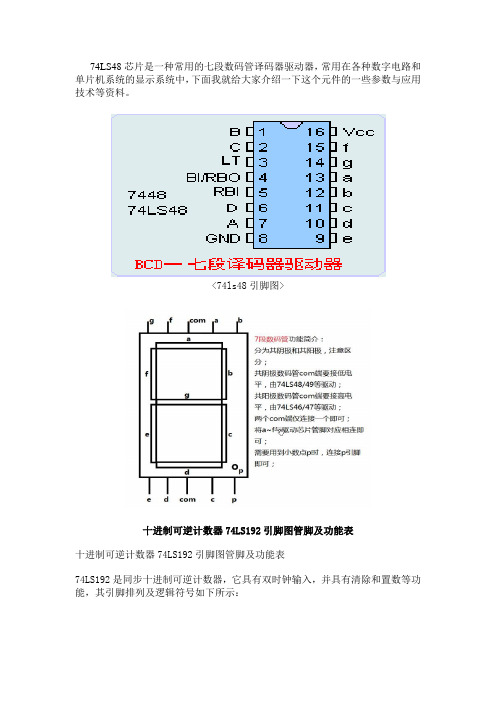

引脚图及功能表

74LS48芯片是一种常用的七段数码管译码器驱动器,常用在各种数字电路和单片机系统的显示系统中,下面我就给大家介绍一下这个元件的一些参数与应用技术等资料。

<74ls48引脚图>

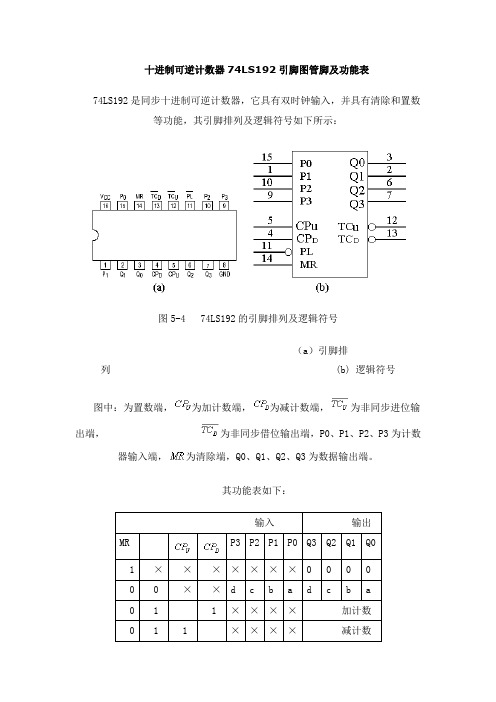

十进制可逆计数器74LS192引脚图管脚及功能表

十进制可逆计数器74LS192引脚图管脚及功能表

74LS192是同步十进制可逆计数器,它具有双时钟输入,并具有清除和置数等功能,其引脚排列及逻辑符号如下所示:

图 74LS192的引脚排列及逻辑符号

(a)引脚排列 (b) 逻辑符号

图中:为置数端,为加计数端,为减计数端,为非同步进位输出

端,为非同步借位输出端,P0、P1、P2、P3为计数器输入端,为清除端,Q0、Q1、Q2、Q3为数据输出端。

其功能表如下:。

LS引脚图管脚及功能表

十进制可逆计数器74LS192引脚图管脚及功能表74LS192是同步十进制可逆计数器,它具有双时钟输入,并具有清除和置数等功能,其引脚排列及逻辑符号如下所示:图5-4 74LS192的引脚排列及逻辑符号(a)引脚排列 (b) 逻辑符号图中:为置数端,为加计数端,为减计数端,为非同步进位输出端,为非同步借位输出端,P0、P1、P2、P3为计数器输入端,为清除端,Q0、Q1、Q2、Q3为数据输出端。

其功能表如下:输入输出MR P3 P2 P1 P0 Q3 Q2 Q1 Q01 ×××××××0 0 0 00 0 ×× d c b a d c b a0 1 1 ××××加计数0 1 1 ××××减计数74ls161引脚图与管脚功能表资料74LS161是常用的四位二进制可预置的同步加法计数器,他可以灵活的运用在各种数字电路,以及单片机系统种实现分频器等很多重要的功能,:<74ls161引脚图>管脚图介绍:时钟CP和四个数据输入端P0~P3清零/MR使能CEP,CET置数PE数据输出端Q0~Q3以及进位输出TC. (TC=Q0·Q1·Q2·Q3·CET)输入输出C R CP LD EP ET D3D2D1D0Q3 Q2Q1Q00 Ф Ф Ф Ф Ф Ф Ф Ф 0 0 0 01 ↑ 0 Ф Ф d c b a d c b a1 ↑ 1 0 Ф Ф Ф Ф Ф Q3 Q2Q1Q01 ↑ 1 Ф 0 Ф Ф Ф Ф Q3 Q2Q1Q01 ↑ 1 1 1 Ф Ф Ф Ф 状态码加1<74LS161功能表>从74LS161功能表功能表中可以知道,当清零端CR=“0”,计数器输出Q3、Q2、Q1、Q0立即为全“0”,这个时候为异步复位功能。

74LS192参数

同步十进制可逆计数器注:74LS192参数74192引脚图真值表:H=高电平 L=低电平 X=不定(高或低电平)↑=由“低”→“高”电平的跃变引脚功能表:NOTES:a. 1 TTL UNIT 单位 Load (U.L.) = 40 mA HIGH/1.6 mA LOW.b. The Output LOW drive factor is 2.5 U.L.for Military(54)and 5 U.L.for Commercial(74)Temperature Ra EQUATIONSOperating Conditions 建议操作条件:DC SPECIFICATIONS直流电气规格:AC CHARACTERISTICS (TA = 25℃) 交流特性(TA = 25℃):交流安装要求(TA =25℃)原理:本电路复杂程度为55 个等效门。

本电路通过同时触发所有触发器而提供同步操作,以便在使用控制逻辑结构时,输出端的变化可相互重合。

本工作方式避免了一般用异步(行波时钟)计数器所带来的计数输出的尖峰脉冲。

四个主从触发器的输出端,由两计数(时钟)输入之一的“低”到“高”电平的过渡而被触发。

计数方向在其它计数输入端为“高”时,由脉冲的计数输入端所定。

本电路为全可编程的,当置数输入为“低”时,把所希望的数据送入数据输入端上,来把每个输出端预置到两电平之一。

输出将符合独立于计数脉冲的数据输入的改变。

该特点可使电路以预置输入而简单地更改计数长度,用作N 模数分频器(除法器)。

清零输入在加高电平时,迫使所有输出端为低电平。

清零功能独立于计数输入和置数输入。

清零、计数和置数等输入端都是缓冲过的,它降低了驱动的要求,这就可减少为长字所要求的时钟驱动器数等等。

本电路都设计成可被直接级联而勿需外接电路。

借位和进位两输出端可级联递增计数和递减计数两功能。

借位输出在计数器下谥时,产生宽度等于递减计数输入的脉冲;同样,进位输出在计数器上谥时, 产生宽度等于递加计数输入的脉冲。