74LS192引脚图管脚及功能表Word版

集成计数器74LS192的使用

图 六进制计数

集成计数器74LS192的使用

计数器的级联使用 利用进பைடு நூலகம்输出控制高一位的CPU端构成的加数级联图

用两个 74LS192集成构计数成器714L0S1092的进使用制计数器

▲ 利用74LS192实现100进制计数器 (想一想)

将多个74LS192级联可以构成高位计数器。

画出逻辑电路图。

集成计数器74LS192的使用

0 0 × × d0 d1 d2 d3 d0 d1 d2 d3 1 0 ↑ 1 ×××× 加计数

1 0 1 ↑ ×××× 减计数

1 0 1 1 ×××× 保 持

× 1 × × ×××× 0 0 0 0

各引脚功能符号的意义:

D0~D3:并行数据输入端 Q0~Q3:数据输出端 CU:加法计数脉冲输入端 CD:减法计数脉冲输入端 RD :异步置 0 端(高电平有效) LD :置数控制端(低电平有效)

集成计数器 74LS192的使用

集成计数器74LS192的使用

74LS192是同步可拟计数器,具有双时钟输入, 并具有清除和置数等功能

集成计数器74LS192的使用

集成计数器74LS192的使用

同步十进制计数器——74LS192集成计数器

▲ 逻辑符号

▲ 74LS192功能表

输入

输出

LD RD CU CD D0 D1 D2 D3 Q0 Q1 Q2 Q3

的

时

序

0

10

0

00

01

图 分

00

析

0

00

00

0

10

01

集成计数器74LS192的使用

三、实验内容及步骤

74LS192是双时钟方式的十进制可逆计数器

74LS192是双时钟方式的十进制可逆计数器。

(bcd,二进制)。

◆ CPU为加计数时钟输入端,CPD为减计数时钟输入端。

◆ LD为预置输入控制端,异步预置。

◆ CR为复位输入端,高电平有效,异步清除。

◆ CO为进位输出:1001状态后负脉冲输出,◆ BO为借位输出:0000状态后负脉冲输出。

74ls192引脚图:74ls192功能表:74LS192是属8421BCD码的十进制计数器,其功能真值表如表4所示。

其中MR是异步清零端,高电平有效。

PL(———)是并行置数端,低电平有效,且在MR=0有效。

CPU和CPu是两个时钟脉冲,当CPd=1,时钟脉冲由CPU端接入。

并且MR=0,PL(———)=1时,74LS192处于加法计数状态;当CPu脉冲从CPd端输入,且MR=0,PL(———)=1时,74LS192处于减法计数状态;CPd=CPu=1时,计数器处于保持状态。

TCu是进位端,TCd是借位端。

表4 74LS192功能真值表MR PL(———)CPu CPd P3 P2 P1 P0 Q3x+1 Q2x+1 Q1x+1 1 ×××××××00 00 1 ×↑d3 d2 d1 d0 d3d2 d10 1 ↑ 1 ××××加法计数0 1 1 ↑××××减法计数0 1 1 1 ××××保持74192的工作原理是:当LD(———)=1,MR=0时,若时钟脉冲加到CPu端,且CPd =1则计数器在预置数的基础上完成加计数功能,当加计数到9时,TCu端发出进位下跳变脉冲;若时钟脉冲加到CPd端,且CPu =1,则计数器在预置数的基础上完成减计数功能,当减计数到0时,TCd 端发出借位下跳变脉冲。

74LS192具有下述功能:①异步清零:MR=1,Q3Q2Q1Q0=0000②异步置数:MR=0,PL(———)=0,Q3Q2Q1Q0=P3P2P1P0③保持:MR=0,PL(———)=1,CPu=CPd=1,Q3Q2Q1Q0保持原态④加计数:MR=0, PL(———)=1,CPu=CP,CPd=1,Q3Q2Q1Q0按加法规律计数⑤减计数:MR=0, PL(———)=1,CPu=1,CPd= CP,Q3Q2Q1Q0按减法规律计数。

中规模十进制计数器74LS192(或CC40192)

中规模十进制计数器74LS192(或CC40192)3、中规模十进制计数器74LS192(或CC40192)74LS192是同步十进制可逆计数器,它具有双时钟输入,并具有清除和置数等功能,其引脚排列及逻辑符号如下所示:图14-4 74LS192的引脚排列及逻辑符号(a)引脚排列 (b) 逻辑符号图中:(LD)为置数端,为加计数端,为减计数端,(CO)为非同步进PLCPCPTCUDU 位输出端 (BO)为非同步借位输出端,P0(D)、P1、P2、P3为计数器输入端,(CR)MRTC0D为清除端,Q0、Q1、Q2、Q3为数据输出端。

计数器及其应用(设计性)一、实验目的1(学习集成触发器构成计数器的方法。

2(掌握中规模集成计数器的使用方法及功能侧试方法。

3(用集成电路计数器构成1,N分频器。

二、实验预习要求1(复习计数器电路工作原理。

2(预习中规模集成电路计数器74LS192的逻辑功能及使用方法。

3(复习实现任意进制计数的方法。

三、实验原理计数器是典型的时序逻辑电路,它是用来累计和记忆输入脉冲的个数(计数是数字系统中很重要的基本操作,集成计数器是最广泛应用的逻辑部件之一。

计数器种类较多,按构成计数器中的多触发、器是否使用一个时钟脉冲源来分,有同步计数器和异步计数器;根据计数制的不同,可分为二进制计数器、十进制计数器和任意进制计数器:根据计数的增减趋势,又分为加法、减法和可逆计数器。

还有可预置数和可编程序功能计数器等。

本实验主要研究中规模十进制计数器74LS192的功能及应用。

1. 74LS192的主要原理(1)74LS192是同步十进制可逆计数器,具有双时钟输入,并具有清除和置数等功能,其逻辑符号及引脚排列如图4-1所示。

图4—1 74LS192逻辑符号及引脚排列图中:CPU—加计数端 CP一减计数端 /LD一置数端 CR一清零端 /CO一非同D 步进位输出端/BO一非同步借位输出端 D0、 D1、D2、 D3一数据输入端 Q0、Q1、Q2、Q3一数据输出端74LS192功能如下表4—1:(1)清零(CR)令CR=1,其它输入端状态为任意态,,记录Q3Q2Q1Q0的状态和译码显示的数值。

74ls192芯片

74ls192芯片74LS192是一种技术较老的逻辑门集成电路(IC),它是一种同步可编程计数器。

该芯片可以实现四位二进制计数,并且可以通过外部的控制信号来实现不同的计数模式和功能。

74LS192具有带锁存功能的四位二进制计数器。

它包含四个独立的计数器,每个计数器都可以通过控制端进行控制。

此外,它还有一个可编程的控制端,可以用来选择计数方向(向上计数或向下计数)以及计数模式(十进制模式、二进制模式等)。

该芯片的引脚图和引脚功能如下:1. CP0 - 输入引脚,用于时钟脉冲的输入。

2. CP1 - 输入引脚,用于时钟脉冲的输入。

3. MR - 输入引脚,用于复位计数器。

4. PC0 - 输入引脚,用于选择计数模式。

5. PC1 - 输入引脚,用于选择计数模式。

6. U/D - 输入引脚,用于选择计数方向。

7. A - 输出引脚,用于输出二进制位的最低位。

8. B - 输出引脚,用于输出二进制位的次低位。

9. C - 输出引脚,用于输出二进制位的次高位。

10. D - 输出引脚,用于输出二进制位的最高位。

11. QA - 输出引脚,用于输出BCD码的最低位。

12. QB - 输出引脚,用于输出BCD码的次低位。

13. QC - 输出引脚,用于输出BCD码的次高位。

14. QD - 输出引脚,用于输出BCD码的最高位。

15. Vcc - 正电源引脚。

16. GND - 接地引脚。

74LS192的工作原理如下:首先,需要将MR引脚置低,从而使计数器复位。

然后,通过CP0和CP1引脚输入时钟信号,控制计数器的计数速度。

U/D引脚用于选择计数方向,当U/D引脚为低电平时,计数器向上计数,当U/D引脚为高电平时,计数器向下计数。

PC0和PC1引脚用于选择计数模式。

当PC1引脚为低电平,PC0引脚为高电平时,计数器工作在二进制模式下。

当PC1引脚为高电平,PC0引脚为低电平时,计数器工作在十进制模式下。

其它的PC1和PC0的组合可以实现更多的计数模式。

74LS192参数

同步十进制可逆计数器注:74LS192参数74192引脚图真值表:H=高电平 L=低电平 X=不定(高或低电平)↑=由“低”→“高”电平的跃变引脚功能表:NOTES:a. 1 TTL UNIT 单位 Load (U.L.) = 40 mA HIGH/1.6 mA LOW.b. The Output LOW drive factor is 2.5 U.L.for Military(54)and 5 U.L.for Commercial(74)Temperature Ra EQUATIONSOperating Conditions 建议操作条件:DC SPECIFICATIONS直流电气规格:AC CHARACTERISTICS (TA = 25℃) 交流特性(TA = 25℃):交流安装要求(TA =25℃)原理:本电路复杂程度为55 个等效门。

本电路通过同时触发所有触发器而提供同步操作,以便在使用控制逻辑结构时,输出端的变化可相互重合。

本工作方式避免了一般用异步(行波时钟)计数器所带来的计数输出的尖峰脉冲。

四个主从触发器的输出端,由两计数(时钟)输入之一的“低”到“高”电平的过渡而被触发。

计数方向在其它计数输入端为“高”时,由脉冲的计数输入端所定。

本电路为全可编程的,当置数输入为“低”时,把所希望的数据送入数据输入端上,来把每个输出端预置到两电平之一。

输出将符合独立于计数脉冲的数据输入的改变。

该特点可使电路以预置输入而简单地更改计数长度,用作N 模数分频器(除法器)。

清零输入在加高电平时,迫使所有输出端为低电平。

清零功能独立于计数输入和置数输入。

清零、计数和置数等输入端都是缓冲过的,它降低了驱动的要求,这就可减少为长字所要求的时钟驱动器数等等。

本电路都设计成可被直接级联而勿需外接电路。

借位和进位两输出端可级联递增计数和递减计数两功能。

借位输出在计数器下谥时,产生宽度等于递减计数输入的脉冲;同样,进位输出在计数器上谥时, 产生宽度等于递加计数输入的脉冲。

引脚图及功能表

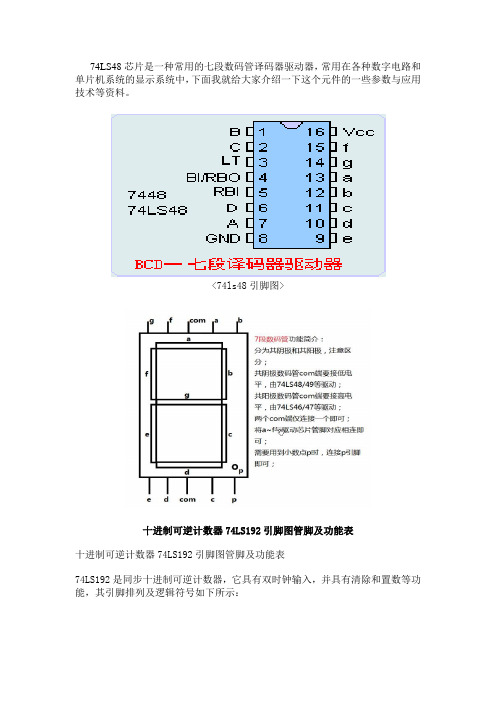

74LS48芯片是一种常用的七段数码管译码器驱动器,常用在各种数字电路和单片机系统的显示系统中,下面我就给大家介绍一下这个元件的一些参数与应用技术等资料。

<74ls48引脚图>

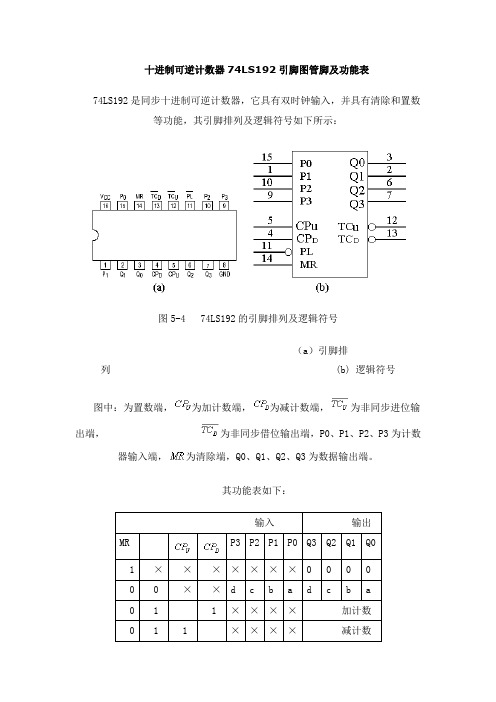

十进制可逆计数器74LS192引脚图管脚及功能表

十进制可逆计数器74LS192引脚图管脚及功能表

74LS192是同步十进制可逆计数器,它具有双时钟输入,并具有清除和置数等功能,其引脚排列及逻辑符号如下所示:

图 74LS192的引脚排列及逻辑符号

(a)引脚排列 (b) 逻辑符号

图中:为置数端,为加计数端,为减计数端,为非同步进位输出

端,为非同步借位输出端,P0、P1、P2、P3为计数器输入端,为清除端,Q0、Q1、Q2、Q3为数据输出端。

其功能表如下:。

LS引脚图管脚及功能表

十进制可逆计数器74LS192引脚图管脚及功能表74LS192是同步十进制可逆计数器,它具有双时钟输入,并具有清除和置数等功能,其引脚排列及逻辑符号如下所示:图5-4 74LS192的引脚排列及逻辑符号(a)引脚排列 (b) 逻辑符号图中:为置数端,为加计数端,为减计数端,为非同步进位输出端,为非同步借位输出端,P0、P1、P2、P3为计数器输入端,为清除端,Q0、Q1、Q2、Q3为数据输出端。

其功能表如下:输入输出MR P3 P2 P1 P0 Q3 Q2 Q1 Q01 ×××××××0 0 0 00 0 ×× d c b a d c b a0 1 1 ××××加计数0 1 1 ××××减计数74ls161引脚图与管脚功能表资料74LS161是常用的四位二进制可预置的同步加法计数器,他可以灵活的运用在各种数字电路,以及单片机系统种实现分频器等很多重要的功能,:<74ls161引脚图>管脚图介绍:时钟CP和四个数据输入端P0~P3清零/MR使能CEP,CET置数PE数据输出端Q0~Q3以及进位输出TC. (TC=Q0·Q1·Q2·Q3·CET)输入输出C R CP LD EP ET D3D2D1D0Q3 Q2Q1Q00 Ф Ф Ф Ф Ф Ф Ф Ф 0 0 0 01 ↑ 0 Ф Ф d c b a d c b a1 ↑ 1 0 Ф Ф Ф Ф Ф Q3 Q2Q1Q01 ↑ 1 Ф 0 Ф Ф Ф Ф Q3 Q2Q1Q01 ↑ 1 1 1 Ф Ф Ф Ф 状态码加1<74LS161功能表>从74LS161功能表功能表中可以知道,当清零端CR=“0”,计数器输出Q3、Q2、Q1、Q0立即为全“0”,这个时候为异步复位功能。

74LS192参数

同步十进制可逆计数器注:74LS192参数74192引脚图真值表:H=高电平 L=低电平 X=不定(高或低电平)↑=由“低”→“高”电平的跃变引脚功能表:NOTES:a. 1 TTL UNIT 单位 Load (U.L.) = 40 mA HIGH/1.6 mA LOW.b. The Output LOW drive factor is 2.5 U.L.for Military(54)and 5 U.L.for Commercial(74)Temperature Ra EQUATIONSOperating Conditions 建议操作条件:DC SPECIFICATIONS直流电气规格:AC CHARACTERISTICS (TA = 25℃) 交流特性(TA = 25℃):交流安装要求(TA =25℃)原理:本电路复杂程度为55 个等效门。

本电路通过同时触发所有触发器而提供同步操作,以便在使用控制逻辑结构时,输出端的变化可相互重合。

本工作方式避免了一般用异步(行波时钟)计数器所带来的计数输出的尖峰脉冲。

四个主从触发器的输出端,由两计数(时钟)输入之一的“低”到“高”电平的过渡而被触发。

计数方向在其它计数输入端为“高”时,由脉冲的计数输入端所定。

本电路为全可编程的,当置数输入为“低”时,把所希望的数据送入数据输入端上,来把每个输出端预置到两电平之一。

输出将符合独立于计数脉冲的数据输入的改变。

该特点可使电路以预置输入而简单地更改计数长度,用作N 模数分频器(除法器)。

清零输入在加高电平时,迫使所有输出端为低电平。

清零功能独立于计数输入和置数输入。

清零、计数和置数等输入端都是缓冲过的,它降低了驱动的要求,这就可减少为长字所要求的时钟驱动器数等等。

本电路都设计成可被直接级联而勿需外接电路。

借位和进位两输出端可级联递增计数和递减计数两功能。

借位输出在计数器下谥时,产生宽度等于递减计数输入的脉冲;同样,进位输出在计数器上谥时, 产生宽度等于递加计数输入的脉冲。

集成计数器74LS192的使用

此上升沿使十位的74LS192(2)从0000开始计数,直到第100 个CP脉冲作用后,计数器由1001 1001恢复为0000 0000,完成 一次计数循环。

C :加法计数时,进位输出端(低电平有效) B :减法计数时,借位输出端(低电平有效)

置 零

RD :异步置 0 端。计数器复位。

LD :置数控制端(低电平有效) 。

1 CD为高电平,计数脉冲从CU端输入。

C :进位输出;

▲ 74LS192

1

1 0

B :借位输出。

CU为高电平,计数脉冲从CD端输入。

0 0 0

1 0 0

0 0 0

0 0 0

1 0 0

的 时 序 图 分 析

0

1

0

0

பைடு நூலகம்

1

三、实验内容及步骤

1、利用一块74LS192作十进制0~9加法计数。 2、用两块74LS192组成二位计数脉冲上升沿触发的 计数电路,作十进制数0~99计数。 3、用计数器的预置BCD码的输入端和预置数装入端 设计一个22进制和特殊15进制(1-15)的计数器, 并验证该电路的正确性。

集成计数器 74LS192的使用

华东理工大学信息学院电信系

74LS192是同步可拟计数器,具有双时钟输入, 并具有清除和置数等功能

同步十进制计数器——74LS192集成计数器

▲ 74LS192功能表 ▲ 逻辑符号

输 入 输 出

LD RD CU CD D0 D1 D2 D3 Q0 Q1 Q2 Q3