常见计数器引脚图

芯片引脚说明

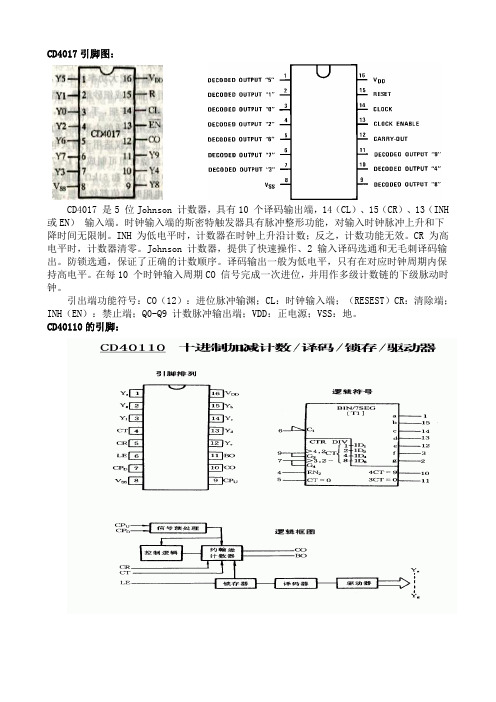

CD4017引脚图:CD4017 是5 位Johnson 计数器,具有10 个译码输出端,14(CL)、15(CR)、13(INH 或EN)输入端。

时钟输入端的斯密特触发器具有脉冲整形功能,对输入时钟脉冲上升和下降时间无限制。

INH 为低电平时,计数器在时钟上升沿计数;反之,计数功能无效。

CR 为高电平时,计数器清零。

Johnson 计数器,提供了快速操作、2 输入译码选通和无毛刺译码输出。

防锁选通,保证了正确的计数顺序。

译码输出一般为低电平,只有在对应时钟周期内保持高电平。

在每10 个时钟输入周期CO 信号完成一次进位,并用作多级计数链的下级脉动时钟。

引出端功能符号:CO(12):进位脉冲输渊;CL:时钟输入端;(RESEST)CR:清除端;INH(EN):禁止端;Q0-Q9 计数脉冲输出端;VDD:正电源;VSS:地。

CD40110的引脚:Ya~Yg:七段码,高电平有效;CPD(CP-):第七脚,减一、脉冲上升沿有效;CPU(CP+):第九脚,加一、脉冲上升沿有效;LE:第六脚,高电平有效,锁存数据;CT(TE):第四脚,高电平有效,禁止计数;CR(R):第五脚,高电平有效,清除计数显示。

数字式频率计LM317:输出电压连续可调的集成稳压电源,输出电压在1.25-37V之间连续可调,输出最大电流可达1.5A。

工作原理:电路原理图见图1。

LM317输出电流为1.5A,输出电压可在1.25-37V之间连续调节,其输出电压由两只外接电阻R1、RP1决定,输出端和调整端之间的电压差为1.25V,这个电压将产生几毫安的电流,经R1、RP1到地,在RP1上分得的电压加到调整端,通过改变RP1就能改变输出电压。

注意,为了得到稳定的输出电压,流经R1的电流小于3.5mA。

LM317在不加散热器时最大功耗为2W,加上200×200×4mm3散热板时其最大功耗可达15W。

VD1为保护二极管,防止稳压器输出端短路而损坏IC,VD2用于防止输入短路而损坏集成电路。

74ls163引脚图与管脚功能表资料

74ls163引脚图与管脚功能表资料

74LS163是常用的四位二进制可预置的同步加法计数器,他可以灵活的运用在各种数字电路,以及单片机系统种实现分频器等很多重要的功能,:

<74ls163引脚图>

管脚图介绍:

时钟CP和四个数据输入端P0~P3

清零/MR

使能CEP,CET

置数PE

数据输出端Q0~Q3

以及进位输出TC. (TC=Q0·Q1·Q2·Q3·CET)

输入输出

C R CP L

D EP ET D3D2D1D0Q3 Q2Q1Q0

0 ↑ x x x x x x x 0 0 0 0

1 ↑ 0 x x D C B A D C B A

1 ↑ 1 0 x x x x x Q3 Q2Q1Q0

1 ↑ 1 x 0 x x x x Q3 Q2Q1Q0

1 ↑ 1 1 1 x x x x 状态码加1

<74LS163功能表>

从74LS163功能表功能表中可以知道,当清零端CR=“0”,计数器输出Q3、Q2、Q1、Q0

立即为全“0”,这个时候为异步复位功能。

当CR=“1”且LD=“0”时,在CP信号上升沿作用后,74LS163输出端Q3、Q2、Q1、Q0的状态分别与并行数据输入端D3,D2,D1,D0的状态一样,为同步置数功能。

而只有当CR=LD=EP=ET=“1”、CP脉冲上升沿作用后,计数器加1。

74LS163还有一个进位输出端CO,其逻辑关系是CO= Q0·Q1·Q2·Q3·CET。

合理应用计数器的清零功能和置数功能,一片74LS163可以组成16进制以下的任意进制分频器。

十进制可逆计数器74LS192引脚图管脚及功能表

十进制可逆计数器74LS192引脚图管脚及功

能表

2011年05月19日11:22 本站整理作者:本站用户评论(0)

关键字:

十进制可逆计数器74LS192引脚图管脚及功能表

74LS192是同步十进制可逆计数器,它具有双时钟输入,并具有清除和置数等功能,其引脚排列及逻辑符号如下所示:

图5-4 74LS192的引脚排列及逻辑符号

(a)引脚排列(b) 逻辑符号

图中:为置数端,为加计数端,为减计数端,为非同步进位输出端,为非同步借位输出端,P0、P1、P2、P3为计数器输入端,为清除端,Q0、Q1、Q2、Q3为数据输出端。

其功能表如下:

74ls00 是常用的2输入四与非门集成电路,他的作用很简单顾名思义就是实现一个与非门。

Vcc 4B 4A 4Y 3B 3A 3Y

┌┴—┴—┴—┴—┴—┴—┴┐

__ │14 13 12 11 10 9 8│

Y = AB )│ 2输入四正与非门 74LS00

│ 1 2 3 4 5 6 7│

└┬—┬—┬—┬—┬—┬—┬┘

1A 1B 1Y 2A 2B 2Y GND

<74LS00引脚图>

74LS00真值表:

A=1 B=1 Y=0

A=0 B=1 Y=1

A=1 B=0 Y=1

A=0 B=0 Y=1

表5-2 74LS192的功能表

[图]74LS20管脚图74LS27管脚图

74LS20管脚图74LS27管脚图

(5) 74LS20四输入双与非门,管脚图如附图1-31所示。

(6) 74LS27三输入三或非门,管脚图如附图1-32所示。

74ls192引脚图

74LS192引脚图引言在数字电子技术中,集成电路(IC)扮演着至关重要的角色。

它们通过集成了许多电子元件来实现各种电子功能。

其中,74LS192是一款常用的集成电路,广泛应用于数码逻辑设计中。

本文档将介绍74LS192集成电路的引脚图及其功能。

74LS192简介74LS192是一款四位可编程二进制同步计数器,它可以在特定时钟脉冲的控制下进行计数。

具体来说,它可以以二进制(BCD)或二进制(Binary)模式计数。

该芯片还具有清零、预设、加载和递增/递减计数的能力。

通过正确配置其引脚连接,我们可以实现各种计数需求。

74LS192引脚图下面是74LS192集成电路的引脚图:Vcc ─┐│┌────────┐ ┌────────┐ ┌────────┐ ┌─┴─┐│ CP │ │ MR │ │ PL │ │ PE ││ (6) │ │ (7) │ │ (8) │ │ (10)│└──┬─────┘ └──┬─────┘ └──┬─────┘ └──┬──┘│ │ │ ││ │ │ │┌─┴─┐ ┌─┴─┐ ┌─┴─┐ ▼ ▲│ D │ │ C │ │ B │ ▼ ▲│ (5) │ │ (4) │ │ (3) │ │ │└───┬┘ └───┬┘ └───┬─┘ ┌───┘ └───┐│ BI/RBO │ BCD1 │ │ BCD0 ││ (9) │ (14) │ │ (13) ││ │ │ │ │┌───┴─┐ ┌─┴─┐ ┌─┴─┐ ┌─┴─┐ ┌─┴─┐│ G │ │ F │ │ E │ │ D │ │ C ││ (16) │ │ (15) │ │ (1) │ │ (2) │ │ (12)│└─┬───┘ └─┬───┘ └─┬─┘ └───┬─┘ └───┬─┘│ Vdd │ CARRY/BORROW │ LATCH CLOCK└───────────────┴──────────────┴───────────┘ CLOCK上述引脚图基于74LS192的DIP(双行直插式)封装。

74ls161引脚图与管脚功能表资料

74ls161引脚图与管脚功能表资料

74LS161是常用的四位二进制可预置的同步加法计数器,他可以灵活的运用在各种数字电路,以及单片机系统种实现分频器等很多重要的功能,:

<74ls161引脚图>

管脚图介绍:

时钟CP和四个数据输入端P0~P3

清零/MR

使能CEP,CET

置数PE

数据输出端Q0~Q3

以及进位输出TC. (TC=Q0·Q1·Q2·Q3·CET)

输入输出

C R CP L

D EP ET D3D2D1D0Q3 Q2Q1Q0

0 Ф Ф Ф Ф Ф Ф Ф Ф 0 0 0 0

1 ↑ 0 Ф Ф d c b a d c b a

1 ↑ 1 0 Ф Ф Ф Ф Ф Q3 Q2Q1Q0

1 ↑ 1 Ф 0 Ф Ф Ф Ф Q3 Q2Q1Q0

1 ↑ 1 1 1 Ф Ф Ф Ф 状态码加1

<74LS161功能表>

从74LS161功能表功能表中可以知道,当清零端CR=“0”,计数器输出Q3、Q2、Q1、Q0立即为全“0”,这个时候为异步复位功能。

当CR=“1”且LD=“0”时,在CP信号上升沿作用后,74LS161输出端Q3、Q2、Q1、Q0的状态分别与并行数据输入端D3,D2,D1,D0的状态一样,为同步置数功能。

而只有当CR=LD=EP=ET=“1”、CP脉冲上升沿作用后,计数器加1。

74LS161还有一个进位输出端CO,其逻辑关系是CO= Q0·Q1·Q2·Q3·CET。

合理应用计数器的清零功能和置数功能,一片74LS161可以组成16进制以下的任意进制分频器。

74ls161引脚图与管脚功能表资料

74LS161是常用的四位二进制可预置的同步加法计数器,他可以灵活的运用在各种数字电路,以及单片机系统种实现分频器等很多重要的功能,:<74ls161引脚图>管脚图介绍:时钟CP和四个数据输入端P0~P3清零/MR使能CEP,CET置数PE数据输出端Q0~Q3以及进位输出TC. (TC=Q0·Q1·Q2·Q3·CET)输入输出C R CP LDEP ET D3D2D1DQ3Q2Q1Q0 Ф Ф Ф Ф Ф Ф Ф Ф 0 0 0 01 ↑ 0 Ф Ф d c b a d c b a1 ↑ 1 0 Ф Ф Ф Ф Ф Q3 Q2Q1Q01 ↑ 1 Ф 0 Ф Ф Ф Ф Q3 Q2Q1Q01 ↑ 1 1 1 Ф Ф Ф Ф 状态码加1<74LS161功能表>从74LS161功能表功能表中可以知道,当清零端CR=“0”,计数器输出Q3、Q2、Q1、Q0立即为全“0”,这个时候为异步复位功能。

当CR=“1”且LD=“0”时,在CP信号上升沿作用后,74LS161输出端Q3、Q2、Q1、Q0的状态分别与并行数据输入端D3,D2,D1,D0的状态一样,为同步置数功能。

而只有当CR=LD=EP=ET=“1”、CP脉冲上升沿作用后,计数器加1。

74LS161还有一个进位输出端CO,其逻辑关系是CO= Q0·Q1·Q2·Q3·CET。

合理应用计数器的清零功能和置数功能,一片74LS161可以组成16进制以下的任意进制分频器。

161 的清除端是异步的。

当清除端C LEAR 为低电平时,不管时钟端C LOCK 状态如何,即可完成清除功能。

161 的预置是同步的。

当置入控制器L OAD 为低电平时,在C LOCK 上升沿作用下,输出端QA-QD 与数据输入端A-D 相一致。

对于54/74161,当C LOCK 由低至高跳变或跳变前,如果计数控制端E NP、ENT 为高电平,则L OAD 应避免由低至高电平的跳变,而54/74LS161 无此种限制。

CD4017引脚图,引脚功能及工作时序图

பைடு நூலகம்

CD4017 的引脚图 CD4017 引脚功能: CD4017 内部是除 10 的计数器及二进制对 10 进制译码电路。CD4017 有 16 支脚,除电源脚 VDD 及 VSS 为电源接脚,输入电压范围为 3–15V 之外,其余接脚为: A、频率输入脚:CLOCK(Pin14),为频率信号的输入脚。 B、数据输出脚: a、 Q1-Q9(Pin3,2,4,7,10,1,5,6,9,11),为*后的时进制 输出接脚,被计数到的值,其输出为 Hi,其余为 Lo 电位。

CD4017 引脚图,引脚功能及工作时序图

CD4017 功能简述:

CD4017 是 5 位 Johnson 计算器,具有 10 个译码输出端,CP,CR, INH 输入端。时钟输入端的斯密特触发器具有脉冲整形功能,对输入 时钟脉冲上升和下降时间无限制。INH 为低电平时,计算器在时钟上 升沿计数;反之,计数功能无效。CR 为高电平时,计数器清零。Johnson 计数器,提供了快速操作,2 输入译码选通和无毛刺译码输出。防锁 选通,保证了正确的计数顺序。译码输出一般为低电平,只有在对应 时钟周期内保持高电平。在每 10 个时钟输入周期 CO 信号完成一次 进位,并用作多级计数链的下级脉动时钟。

b、CARRY OUT(Pin12),进位脚,当 4017 计数 10 个脉冲之后,CARRY OUT 将输出一个脉波,代表产生进位,共串级计数器使用。 D、 控制脚: a、 CLEAR(Pin15):清除脚或称复位(Reset)脚,当此脚为 Hi 时,会 使 CD4017 的 Q0 为”1”,其余 Q1-Q9 为”0”。 b、CLOCK ENABLE(Pin13),时序允许脚,当此脚为低电位,CLOCK 输入脉波在正缘时,会使 CD4017 计数,并改变 Q1-Q9 的输出状态。

14位二进制异步计数器74HC4060引脚图及功能简介

14位二进制异步计数器74HC4060引脚图及功能简介高速CMOS集成电路(74HC/74HCT/54HC/54HCT系列)引脚图,功能及主要参数大全--14位二进制异步计数器74HC4060引脚图及功能简介(中文资料)国产TTL集成电路的标准系列为CT54/74系列或CT0000系列,其功能和外引线排列与国际54/74系列相同。

国产CMOS集成电路主要为CC(CH)4000系列,其功能和外引线排列与国际CD4000系列相对应。

高速CMOS系列中,74HC和74HCT 系列与TTL74系列相对应,74HC4000系列与CC4000系列相对应。

CC系列为国产型号,其命名方法请参考:国产高速CMOS芯片型号命名方法74LS系列与74HC,74HCT,CD系列的区别:1.LS、HC 二者高电平低电平定义不同:HC高电平规定为0.7倍电源电压,低电平规定为0.3倍电源电压。

LS规定高电平为2.0V,低电平为0.8V。

带负载特性不同。

2.HC上拉下拉能力相同,LS上拉弱而下拉强。

3.输入特性不同:HC输入电阻很高,输入开路时电平不定。

LS输入内部有上拉,输入开路时为高电平。

4.74LS系列是“低功耗肖特基TTL”,统称74LS系列。

其改进型为“先进低功耗肖特基TTL”,既74ALS系列,它的性能比74LS更好。

5.74HC系列,它具有CMOS的低功耗和相当于74LS高速度的性能,属于一种高速低功耗产品。

6.74HC系列与74LS的工作频率都在30mHz以下,74ALS略高,可达50mHz。

7.工作电压却大不相同:74LS系列为5V,74HC系列为2~6V。

8.扇出能力:74LS系列为20,而74HC系列在直流时则高达1000以上,但在交流时很低,由工作频率决定。

9.74HC与74HCT都是高速CMOS器件,是同一系列,其中74hct的输入信号为TTL 电平.10.74hc与74hct都是高速CMOS器件,是同一系列,其中74hct的输入信号为TTL 电平.提示:如有需要,请用鼠标轮控制图片的缩放.。

74ls161引脚图与管脚功能表资料

74ls161引脚图与管脚功能表资料

74LS161是常用的四位二进制可预置的同步加法计数器,他可以灵活的运用在各种数字电路,以及单片机系统种实现分频器等很多重要的功能,:

<74ls161引脚图>

管脚图介绍:

时钟CP和四个数据输入端P0~P3

清零/MR

使能CEP,CET

置数PE

数据输出端Q0~Q3

以及进位输出TC. (TC=Q0·Q1·Q2·Q3·CET)

输入输出

C R CP L

D EP ET D3D2D1D0

Q

3

Q

2

Q

1

Q0

<74LS161功能表>

从74LS161功能表功能表中可以知道,当清零端CR=“0”,计数器输出Q3、Q2、Q1、Q 0立即为全“0”,这个时候为异步复位功能。

当CR=“1”且LD=“0”时,在CP信号上升沿作用后,74LS161输出端Q3、Q2、Q1、Q0的状态分别与并行数据输入端D3,D2,D1,D0的状态一样,为同步置数功能。

而只有当CR=LD=EP=ET=“1”、CP脉冲上升沿作用后,计数器加1。

74 LS161还有一个进位输出端CO,其逻辑关系是CO= Q0·Q1·Q2·Q3·CET。

合理应用计数器的清零功能和置数功能,一片74LS161可以组成16进制以下的任意进制分频器。

74ls161引脚图与管脚功能表资料

74ls161引脚图与管脚功能表资料

74LS161是常用的四位二进制可预置的同步加法计数器,他可以灵活的运用在各种数字电路,以及单片机系统种实现分频器等很多重要的功能,:

<74ls161引脚图>

管脚图介绍:

时钟CP和四个数据输入端P0~P3

清零/MR

使能CEP,CET

置数PE

数据输出端Q0~Q3

以及进位输出TC. (TC=Q0·Q1·Q2·Q3·CET)

输入输出

C R CP L

D EP ET D3D2D1D0Q3 Q2Q1Q0

0 Ф Ф Ф Ф Ф Ф Ф Ф 0 0 0 0

1 ↑ 0 Ф Ф d c b a d c b a

1 ↑ 1 0 Ф Ф Ф Ф Ф Q3 Q2Q1Q0

1 ↑ 1 Ф 0 Ф Ф Ф Ф Q3 Q2Q1Q0

1 ↑ 1 1 1 Ф Ф Ф Ф 状态码加1

<74LS161功能表>

从74LS161功能表功能表中可以知道,当清零端CR=“0”,计数器输出Q3、Q2、Q1、Q0立即为全“0”,这个时候为异步复位功能。

当CR=“1”且LD=“0”时,在CP信号上升沿作用后,74LS161输出端Q3、Q2、Q1、Q0的状态分别与并行数据输入端D3,D2,D1,D0的状态一样,为同步置数功能。

而只有当CR=LD=EP=ET=“1”、CP脉冲上升沿作用后,计数器加1。

74LS161还有一个进位输出端CO,其逻辑关系是CO= Q0·Q1·Q2·Q3·CET。

合理应用计数器的清零功能和置数功能,一片74LS161可以组成16进制以下的任意进制分频器。

stc89c52引脚图及引脚功用

stc89c52引脚图及引脚功用VCC(40引脚):电源电压VSS(20引脚):接地P0端口(P0.0~P0.7,39~32引脚):P0口是一个漏极开路的8位双向I/O口。

作为输出端口,每个引脚能驱动8个TTL负载,对端口P0写入1时,能够作为高阻抗输入。

在拜访外部程序和数据存储器时,P0口也能够供给低8位地址和8位数据的复用总线。

此刻,P0口内部上拉电阻有用。

在FlashROM编程时,P0端口接纳指令字节;而在校验程序时,则输出指令字节。

验证时,恳求外接上拉电阻。

P1端口(P1.0~P1.7,1~8引脚):P1口是一个带内部上拉电阻的8位双向I/O口。

P1的输出缓冲器可驱动(吸收或许输出电流办法)4个TTL输入。

对端口写入1时,经过内部的上拉电阻把端口拉到高电位,这是可用作输进口。

P1口作输进口运用时,因为有内部上拉电阻,那些被外部拉低的引脚会输出一个电流。

此外,P1.0和P1.1还能够作为守时器/计数器2的外部技能输入(P1.0/T2)和守时器/计数器2的触发输入(P1.1/T2EX),详细拜见下表:在对FlashROM编程和程序校验时,P1接纳低8位地址。

表XXP1.0和P1.1引脚复用功用引脚号功用特性P1.0T2(守时器/计数器2外部计数输入),时钟输出P1.1T2EX(守时器/计数器2捕获/重装触发和方向操控)P2端口(P2.0~P2.7,21~28引脚):P2口是一个带内部上拉电阻的8位双向I/O端口。

P2的输出缓冲器能够驱动(吸收或输出电流办法)4个TTL输入。

对端口写入1时,经过内部的上拉电阻把端口拉到高电平,这时可用作输进口。

P2作为输进口运用时,因为有内部的上拉电阻,那些被外部信号拉低的引脚会输出一个电流。

在拜访外部程序存储器和16位地址的外部数据存储器(如实施MOVX@DPTR指令)时,P2送出高8位地址。

在拜访8位地址的外部数据存储器(如实施MOVX@R1指令)时,P2口引脚上的内容(即是专用寄存器(SFR)区中的P2寄存器的内容),在悉数拜访时期不会改动。

14位二进制异步计数器74HC4060引脚图及功能简介

14位⼆进制异步计数器74HC4060引脚图及功能简介14位⼆进制异步计数器74HC4060引脚图及功能简介⾼速CMOS集成电路(74HC/74HCT/54HC/54HCT系列)引脚图,功能及主要参数⼤全--14位⼆进制异步计数器74HC4060引脚图及功能简介(中⽂资料)国产TTL集成电路的标准系列为CT54/74系列或CT0000系列,其功能和外引线排列与国际54/74系列相同。

国产CMOS集成电路主要为CC(CH)4000系列,其功能和外引线排列与国际CD4000系列相对应。

⾼速CMOS系列中,74HC和74HCT 系列与TTL74系列相对应,74HC4000系列与CC4000系列相对应。

CC系列为国产型号,其命名⽅法请参考:国产⾼速CMOS芯⽚型号命名⽅法74LS系列与74HC,74HCT,CD系列的区别:1.LS、HC ⼆者⾼电平低电平定义不同:HC⾼电平规定为0.7倍电源电压,低电平规定为0.3倍电源电压。

LS规定⾼电平为2.0V,低电平为0.8V。

带负载特性不同。

2.HC上拉下拉能⼒相同,LS上拉弱⽽下拉强。

3.输⼊特性不同:HC输⼊电阻很⾼,输⼊开路时电平不定。

LS输⼊内部有上拉,输⼊开路时为⾼电平。

4.74LS系列是“低功耗肖特基TTL”,统称74LS系列。

其改进型为“先进低功耗肖特基TTL”,既74ALS系列,它的性能⽐74LS更好。

5.74HC系列,它具有CMOS的低功耗和相当于74LS⾼速度的性能,属于⼀种⾼速低功耗产品。

6.74HC系列与74LS的⼯作频率都在30mHz以下,74ALS略⾼,可达50mHz。

7.⼯作电压却⼤不相同:74LS系列为5V,74HC系列为2~6V。

8.扇出能⼒:74LS系列为20,⽽74HC系列在直流时则⾼达1000以上,但在交流时很低,由⼯作频率决定。

9.74HC与74HCT都是⾼速CMOS器件,是同⼀系列,其中74hct的输⼊信号为TTL 电平.10.74hc与74hct都是⾼速CMOS器件,是同⼀系列,其中74hct的输⼊信号为TTL 电平.提⽰:如有需要,请⽤⿏标轮控制图⽚的缩放.。

74ls161引脚图与管脚功能表资料

74ls161引脚图与管脚功能表资料

74LS161是常用的四位二进制可预置的同步加法计数器,他可以灵活的运用在各种数字电路,以及单片机系统种实现分频器等很多重要的功能,:

<74ls161引脚图>

管脚图介绍:

时钟CP和四个数据输入端P0~P3

清零/MR

使能CEP,CET

置数PE

数据输出端Q0~Q3

以及进位输出TC. (TC=Q0·Q1·Q2·Q3·CET)

输入输出

C R CP L

D EP ET D3D2D1D0Q3 Q2Q1Q0

0 Ф Ф Ф Ф Ф Ф Ф Ф 0 0 0 0

1 ↑ 0 Ф Ф d c b a d c b a

1 ↑ 1 0 Ф Ф Ф Ф Ф Q3 Q2Q1Q0

1 ↑ 1 Ф 0 Ф Ф Ф Ф Q3 Q2Q1Q0

1 ↑ 1 1 1 Ф Ф Ф Ф 状态码加1

<74LS161功能表>

从74LS161功能表功能表中可以知道,当清零端CR=“0”,计数器输出Q3、Q2、Q1、Q0立即为全“0”,这个时候为异步复位功能。

当CR=“1”且LD=“0”时,在CP信号上升沿作用后,74LS161输出端Q3、Q2、Q1、Q0的状态分别与并行数据输入端D3,D2,D1,D0的状态一样,为同步置数功能。

而只有当CR=LD=EP=ET=“1”、CP脉冲上升沿作用后,计数器加1。

74LS161还有一个进位输出端CO,其逻辑关系是CO= Q0·Q1·Q2·Q3·CET。

合理应用计数器的清零功能和置数功能,一片74LS161可以组成16进制以下的任意进制分频器。

74161引脚功能表

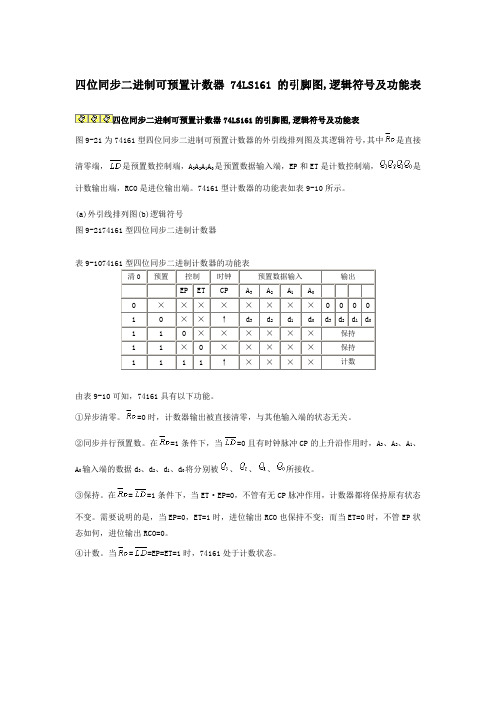

四位同步二进制可预置计数器74LS161的引脚图,逻辑符号及功能表

四位同步二进制可预置计数器74LS161的引脚图,逻辑符号及功能表

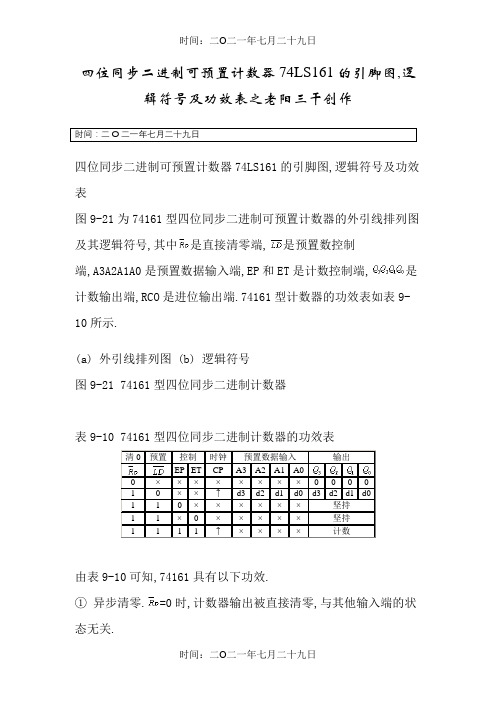

图9-21为74161型四位同步二进制可预置计数器的外引线排列图及其逻辑符号,其中是直接清零端,是预置数控制端,A3A2A1A0是预置数据输入端,EP和ET是计数控制端,是计数输出端,RCO是进位输出端。

74161型计数器的功能表如表9-10所示。

(a)外引线排列图(b)逻辑符号

图9-2174161型四位同步二进制计数器

表

由表9-10可知,74161具有以下功能。

①异步清零。

=0时,计数器输出被直接清零,与其他输入端的状态无关。

②同步并行预置数。

在=1条件下,当=0且有时钟脉冲CP的上升沿作用时,A3、A2、A1、

A0输入端的数据d3、d2、d1、d0将分别被、、、所接收。

③保持。

在==1条件下,当ET·EP=0,不管有无CP脉冲作用,计数器都将保持原有状态不变。

需要说明的是,当EP=0,ET=1时,进位输出RCO也保持不变;而当ET=0时,不管EP状态如何,进位输出RCO=0。

④计数。

当==EP=ET=1时,74161处于计数状态。

74161引脚功能表

四位同步二进制可预置计数器74LS161的引脚图,逻辑符号及功效表之老阳三干创作时间:二O二一年七月二十九日四位同步二进制可预置计数器74LS161的引脚图,逻辑符号及功效表图9-21为74161型四位同步二进制可预置计数器的外引线排列图及其逻辑符号,其中是直接清零端,是预置数控制端,A3A2A1A0是预置数据输入端,EP和ET是计数控制端,是计数输出端,RCO是进位输出端.74161型计数器的功效表如表9-10所示.(a) 外引线排列图 (b) 逻辑符号图9-21 74161型四位同步二进制计数器表9-10 74161型四位同步二进制计数器的功效表清0预置控制时钟预置数据输入输出EP ET CP A3A2A1A00××××××××000010××↑d3d2d1d0d3d2d1d0110××××××坚持11×0×××××坚持1111↑××××计数由表9-10可知,74161具有以下功效.① 异步清零.=0时,计数器输出被直接清零,与其他输入端的状态无关.② 同步并行预置数.在=1条件下,当=0且有时钟脉冲CP的上升沿作用时,A3、A2、A1、A0输入端的数据 d3、d2 、d1、d0将辨别被、、、所接收.③ 坚持.在==1条件下,当ET·EP=0,不管有无CP脉冲作用,计数器都将坚持原有状态不变.需要说明的是,当EP=0,ET=1时,进位输出RCO也坚持不变;而当ET=0时,不管EP状态如何,进位输出RCO=0.④ 计数.当==EP=ET=1时,74161处于计数状态.时间:二O二一年七月二十九日。