GE300控制器说明书

CG300多功能控制器操作说明

重新设定量程或者清除多余的物料,保证最大计量的物料不超过设定的量程

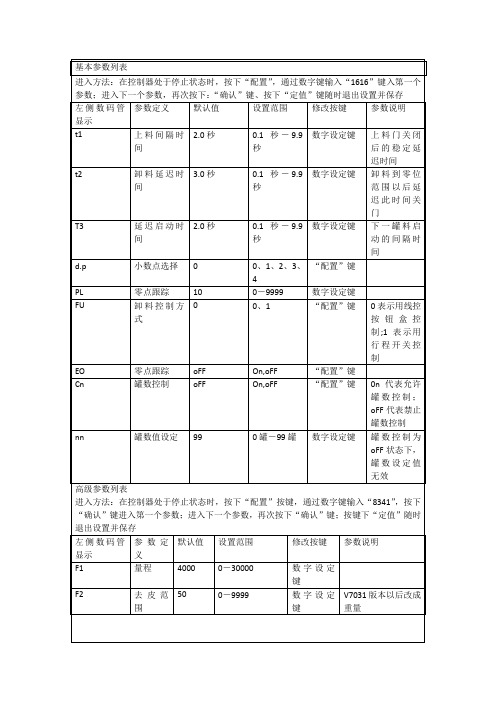

t2

卸料延迟时间

3.0秒

0.1秒-9.9秒

数字设定键

卸料到零位范围以后延迟此时间关门

T3

延迟启动时间

2.0秒

0.1秒-9.9秒

数字设定键

下一罐料启动的间隔时间

d.p

小数点选择

0

0、1、2、3、4

“配置”键

PL

零点跟踪

U

卸料控制方式

0

0、1

“配置”键

0表示用线控按钮盒控制;1表示用行程开关控制

常见故障处理

左侧数码管显示

故障定义

故障原因

排除措施

E1

校秤错误

1.传感器接线不正确

检查传感器接线,重新校秤后仍显示E1,更换传感器

2.校秤操作不正确

重新进行校秤操作

3.控制器故障

返厂维修

E2

设定值不正确

设定值总和超量程或者定值大于落差

重新输入设定值或修改落差

OL

超量程

1.还未进行校零、校秤操作

按步骤进行校零和校秤

基本参数列表

进入方法:在控制器处于停止状态时,按下“配置”,通过数字键输入“1616”键入第一个参数;进入下一个参数,再次按下:“确认”键、按下“定值”键随时退出设置并保存

左侧数码管显示

参数定义

默认值

设置范围

修改按键

参数说明

t1

上料间隔时间

2.0秒

0.1秒-9.9秒

数字设定键

上料门关闭后的稳定延迟时间

设定值及落差

进入方法:在控制器处于停止状态时,按下“定值”按键,进入定值设定操作:再次按下“定值”键随时退出设置并保存。

GE说明书

保护构造

IP65(产品前面部)

保存温度

-20~65℃(不结冰状态)

使用周围温湿度

-10~55℃,35~85% R.H.(不准有结露/结冰现象)

重

量 133g 以下

138g 以下

203g 以下

203g 以下

获得认证

CE 认证

※其它输·出入式样的追加变更事项请咨询营业部。

2/8

各部位名称

▢ 计数输入 1(CP1)/禁止输入(INHIBIT)端子 ∙ 选择计数功能时,被使用为计数输入或计数禁止。 ∙ 选择计时功能时,进行时间会停止(HOLD)。

振

动 耐 久 10-55Hz(周期 1 分钟)复振幅 0.5mm X·Y·Z 各方向 2 小时

误动作 10-55Hz(周期 1 分钟)复振幅 0.5mm X·Y·Z 各方向 10 分钟

冲

击 耐久

误动作

300m/s2 (约 30G) 100m/s2 (约 10G)

继 电 器 电气的 寿 命 机械的

10 万次以上(250V a.c 2A 阻抗负荷) 1000 万次以上

中国工厂

上海韩荣电子有限公司 中国上海市嘉定区复华路 33 号 A 座 2 楼 TEL:(021)-5990-3155 FAX:(021)-5990-3676

安全注意事项

为正确使用本产品,请务必在使用前认真阅读安全注意事项。 注意事项里列明的有关安全方面的重要内容,请务必遵守。 安全注意事项区分为危险、警告、注意。

▢ BAT.RESET ∙ 使用计数/计时器时,被使用为 BATCH RESET。

▢ RESET ∙ 使用计数/计时器时,使计数值及当前时间初始化。

▢ OUT,OUT2:被使用为计数/计时的比较输出 ▢ BAT.O:批次输出。(1 段设定型) ▢ (BAT.O):可选择 1 段设定输出或批次输出(2 段设定型)

主发电机盘EG300操作教案

D 无载起机 功能关闭 E 启动模式 改为自动 自动 F 自动模式操作 功能关闭 G 手动模式操作 功能关闭 H 停止模式操作 功能关闭

三,EG300参数设置 参数设置

4.配置应急操作 功能关闭 5 配置输入/输出,进入后画面如下:(参看原理图中每个输入输出点的功能)

三,EG300参数设置 参数设置

一, EG300概述 概述

EG300 正面

二,EG300与外部设备连接 与外部设备连接

开始——所有程序——woodward—— ——所有程序——woodward——toolkit 一.单击 开始——所有程序——woodward——toolkit

二, EG300与外部设备连接 与外部设备连接

打开软件如下 图所示: 图所示:

二, EG300与外部设备连接 与外部设备连接

四,连接成功后弹出以 下对话框, 下对话框,然后再 tool device 下拉选 项中选择toolkit 项中选择toolkit configure 。此时软 件上的画面有灰色变 亮,可以显示一些参 数了。 数了。并且在左下角 有状态显示 connected。 connected。说明已 经连接上。 经连接上。后面参数 的设置就和直接手动 EG3000上操作一 在EG3000上操作一 致了。 致了。

最后进入下图中的系统参 数,在弹出的对话框中 将器件编号 器件编号改成不一致 器件编号 最好与上图中的NODEI CAN-BUS 1的地址一 致(如一号车的地址为1. 二号车的为2.等等) 以上的设置步骤完成后,负荷分配线就算是基本建立起来了。

三,EG300参数设置 参数设置

二.配置画面如下 1.首先配置发动机

谢谢大家!

1.发电机监视(这里主要的是发电机的一些保护性设置)

GE300控制器说明书

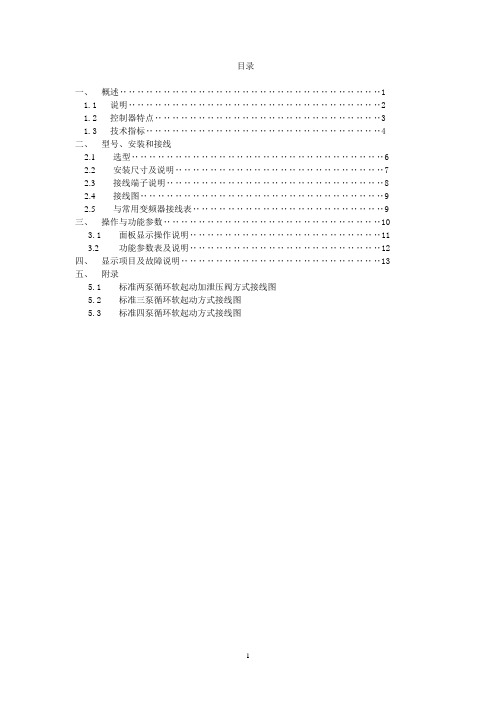

目录一、概述‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥11.1说明‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥2 1.2控制器特点‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥31.3技术指标‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥4二、型号、安装和接线2.1选型‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥6 2.2安装尺寸及说明‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥7 2.3接线端子说明‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥8 2.4接线图‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥92.5与常用变频器接线表‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥9三、操作与功能参数‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥103.1面板显示操作说明‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥113.2功能参数表及说明‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥12四、显示项目及故障说明‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥13五、附录5.1标准两泵循环软起动加泄压阀方式接线图5.2标准三泵循环软起动方式接线图5.3标准四泵循环软起动方式接线图一、概述1.1说明本手册包含GE300系列微机控制器的安装、操作和配置信息。

在使用GE300系列微机给水控制器之前,请您仔细阅读本使用说明书,并请妥善保存。

由于我们始终致力于产品的不断升级和完善,因此,本公司提供的资料如有变动,恕不另行通知。

1.2控制器特点本产品是应广大用户的要求最新推出的高性能微机给水控制器。

采用高品质元件、材料及融合最新的控制技术而成;和变频器组合在一起,即可构成民用、工业、消防等行业适用的微机变频调速恒压供水系统。

●采用模糊控制原理,自动优化时无需调整控制器参数,响应快、精度高、泵切换时管网冲击小。

●具备自动定时换泵,定时开关机设置,提高水泵平均使用寿命。

GE系列运动控制器用户手册

第二章

快速使用 ..............................................................5

2.1 开箱检查 ....................................................................................................................................... 5 2.2 GE运动控制器的外形结构 ....................................................................................................... 5 2.2.1 GE-X00-SX运动控制器................................................................................................................ 5 2.3 安装步骤 ......................................................................................................................................... 8

第三章 系统调试 .............................................................22

附录A 技术参数 ...............................................................23

GE300控制器说明书

增量 F24 作为当前的设定压力,当实际压力到达此压力时即 0-0.50

进入休眠状态,如实际压力到达不了此设定值则延时 3 分钟

自动进入休眠状态。

F25 减泵频率

有工频泵工作时,当实际频率低于减泵频率,经过减泵延时 0-50.0

F26 则减掉一工频泵

F26 减泵延时

功能见 F25 项

0-250

泄压阀压力控制浮动上 当实际压力高 F01+F27 值时,并延时 F29 时间则泄压阀打开,

DL

低水位指示,即 CT2 与 COM2 短接时,灯亮并停机

Hz

灯亮,实际压力显示数值为变频器输出频率

注:文中 X 通T3

24 CT4

三、 操作与功能参数

3.1 操作各按键名称和功能

部件

名称

ESC

编程键

▲

增加键

▼

减小键

SET

切换/存储键

功能 进入参数查看、修改状态 退出参数查看、修改状态 功能代码或设定参数值递增 欠压报警时,按压此键可消除报警

功能代码或设定参数值递减

实际压力与输出频率间切换 功能代码与参数递增 存储当前修改的功能代码参数值

N 12

L 11 GE300

10 R8 9 R7 8 R6 7 R5 6 R4 5 R3 4 R2 3 R1 2

1

13 GND

14 IN 15 +V

远传压力表

16 COM2

0-5v/0-10v

17 D/A

18 COM1 19 FWD 20 FRS

光耦输出,变 频器运行信号

光耦输出,变 频器急停信号

21 CT1

时间,实际压力仍小于设定压力,变频泵倒为工频运行,下 0-250

GE-PLC-使用手册

F1

I1

ADD INT

I2

Q

?????

?????

?????

减法运算

F2

I1

SUB INT

I2

Q

?????

?????

?????

乘法运算

F3

I1

MUL INT

I2

Q

?????

?????

?????

除法运算

F4

I1

DIV INT

I2

Q

?????

?????

?????

MATH mul

F3

Shift

>

| 10

| 4

0

1

0

0

0

0

Q1

(

)

Q2

(

)

I1

I1

I

2

Q2

CPU

输出地址%Q

输入地址%I

用户程序

数据储存 (%M,%R,...)

I

1

I

2

I

3

I

4

I

5

I

6

I

7

I

8

C

O

M

输入模块

输出模块

Q1

Q2

Q3

Q4

Q5

Q6

Q7

Q8

C

O

M

1

2

3

输入扫描

执行 程序

输出刷新

通讯服务

1

2

3

GE PLC 地址表示形式

外部地址

I2

OK

%I,%Q,%M,%T,%G 不能用于 REAL

Q

%I,%Q,%M,%T,%G, %R,%AI,%AQ,CONST

GS8662Q18GE-300I中文资料

GS8662Q08/09/18/36E-300/250/200/16772Mb SigmaQuad-II Burst of 2 SRAM300 MHz–167 MHz1.8 V V DD1.8 V and 1.5 V I/O165-Bump BGA Commercial Temp Industrial Temp Features• Simultaneous Read and Write SigmaQuad™ Interface • JEDEC-standard pinout and package • Dual Double Data Rate interface• Byte Write controls sampled at data-in time • Burst of 2 Read and Write• 1.8 V +100/–100 mV core power supply • 1.5 V or 1.8 V HSTL Interface • Pipelined read operation• Fully coherent read and write pipelines• ZQ pin for programmable output drive strength • IEEE 1149.1 JTAG-compliant Boundary Scan• Pin-compatible with present 9Mb, 18Mb, and 36Mb and future 144Mb devices• 165-bump, 15 mm x 17 mm, 1 mm bump pitch BGA package • RoHS-compliant 165-bump BGA package availableSigmaQuad ™ Family OverviewThe GSQ8662Q08/09/18/36E are built in compliance with the SigmaQuad-II SRAM pinout standard for Separate I/O synchronous SRAMs. They are 75,497,472-bit (72Mb)SRAMs. The GSQ8662Q08/09/18/36E SigmaQuad SRAMs are just one element in a family of low power, low voltage HSTL I/O SRAMs designed to operate at the speeds needed to implement economical high performance networking systems.Clocking and Addressing SchemesThe GSQ8662Q08/09/18/36E SigmaQuad-II SRAMs are synchronous devices. They employ two input register clock inputs, K and K. K and K are independent single-ended clock inputs, not differential inputs to a single differential clock input buffer. The device also allows the user to manipulate theoutput register clock inputs quasi independently with the C andC clock inputs. C and C are also independent single-ended clock inputs, not differential inputs. If the C clocks are tied high, the K clocks are routed internally to fire the output registers instead.Because Separate I/O SigmaQuad-II B2 RAMs always transfer data in two packets, A0 is internally set to 0 for the first read or write transfer, and automatically incremented by 1 for the next transfer. Because the LSB is tied off internally, the address field of a SigmaQuad-II B2 RAM is always one address pin less than the advertised index depth (e.g., the 4M x 18 has a 2048K addressable index).Parameter Synopsis-300-250-200-167tKHKH 3.3 ns 4.0 ns 5.0 ns 6.0 ns tKHQV0.45 ns0.45 ns0.45 ns0.5 ns165-Bump, 15 mm x 17 mm BGA 1 mm Bump Pitch, 11 x 15 Bump ArrayBottom View2M x 36 SigmaQuad-II SRAM—Top View1234567891011ACQ MCL/SA (288Mb)SA W BW2K BW1R SA MCL/SA (144Mb)CQ B Q27Q18D18SA BW3K BW0SA D17Q17Q8C D27Q28D19V SS SA SA SA V SS D16Q7D8D D28D20Q19V SS V SS V SS V SS V SS Q16D15D7E Q29D29Q20 V DDQ V SS V SS V SS V DDQ Q15D6Q6F Q30Q21D21 V DDQ V DD V SS V DD V DDQ D14Q14Q5G D30D22Q22 V DDQ V DD V SS V DD V DDQ Q13D13D5H Doff V REF V DDQ V DDQ V DD V SS V DD V DDQ V DDQ V REF ZQ J D31Q31D23 V DDQ V DD V SS V DD V DDQ D12Q4D4K Q32D32Q23V DDQ V DD V SS V DD V DDQ Q12D3Q3L Q33Q24D24 V DDQ V SS V SS V SS V DDQ D11Q11Q2M D33Q34D25 V SS V SS V SS V SS V SS D10Q1D2N D34D26Q25 V SS SA SA SA V SS Q10D9D1P Q35D35Q26SA SA C SA SA Q9D0Q0RTDOTCKSASASACSASASATMSTDI11 x 15 Bump BGA—15 x 17 mm 2 Body—1 mm Bump PitchNotes:1.BW0 controls writes to D0:D8; BW1 controls writes to D9:D17; BW2 controls writes to D18:D26; BW3 controls writes to D27:D352.MCL = Must Connect LowGS8662Q08/09/18/36E-300/250/200/1674M x 18 SigmaQuad-II SRAM—Top View1234567891011ACQ MCL/SA (144Mb)SA W BW1K NC R SA SA CQ B NC Q9D9SA NC K BW0SA NC NC Q8C NC NC D10V SS SA SA SA V SS NC Q7D8D NC D11Q10V SS V SS V SS V SS V SS NC NC D7E NC NC Q11 V DDQ V SS V SS V SS V DDQ NC D6Q6F NC Q12D12 V DDQ V DD V SS V DD V DDQ NC NC Q5G NC D13Q13 V DDQ V DD V SS V DD V DDQ NC NC D5H Doff V REF V DDQ V DDQ V DD V SS V DD V DDQ V DDQ V REF ZQ J NC NC D14 V DDQ V DD V SS V DD V DDQ NC Q4D4K NC NC Q14V DDQ V DD V SS V DD V DDQ NC D3Q3L NC Q15D15 V DDQ V SS V SS V SS V DDQ NC NC Q2M NC NC D16 V SS V SS V SS V SS V SS NC Q1D2N NC D17Q16 V SS SA SA SA V SS NC NC D1P NC NC Q17SA SA C SA SA NC D0Q0RTDOTCKSASASACSASASATMSTDI11 x 15 Bump BGA—15 x 17 mm 2 Body—1 mm Bump PitchNotes:1.BW0 controls writes to D0:D8. BW1 controls writes to D9:D17.2.MCL = Must Connect LowGS8662Q08/09/18/36E-300/250/200/1678M x 8 SigmaQuad-II SRAM—Top View1234567891011ACQ SA SA W NW1K NC R SA SA CQ B NC NC NC SA NC K NW0SA NC NC Q3C NC NC NC V SS SA SA SA V SS NC NC D3D NC D4NC V SS V SS V SS V SS V SS NC NC NC E NC NC Q4 V DDQ V SS V SS V SS V DDQ NC D2Q2F NC NC NC V DDQ V DD V SS V DD V DDQ NC NC NC G NC D5Q5 V DDQ V DD V SS V DD V DDQ NC NC NC H Doff V REF V DDQ V DDQ V DD V SS V DD V DDQ V DDQ V REF ZQ J NC NC NC V DDQ V DD V SS V DD V DDQ NC Q1D1K NC NC NC V DDQ V DD V SS V DD V DDQ NC NC NC L NC Q6D6 V DDQ V SS V SS V SS V DDQ NC NC Q0M NC NC NC V SS V SS V SS V SS V SS NC NC D0N NC D7NC V SS SA SA SA V SS NC NC NC P NC NC Q7SA SA C SA SA NC NC NC RTDOTCKSASASACSASASATMSTDI11 x 15 Bump BGA—15 x 17 mm 2 Body—1 mm Bump PitchNotes:1.NW0 controls writes to D0:D3. NW1 controls writes to D4:D7.2.MCL = Must Connect LowGS8662Q08/09/18/36E-300/250/200/1678M x 9 SigmaQuad-II SRAM — Top View1234567891011ACQ SA SA W NC K NC R SA SA CQ B NC NC NC SA NC K BW SA NC NC Q4C NC NC NC V SS SA SA SA V SS NC NC D4D NC D5NC V SS V SS V SS V SS V SS NC NC NC E NC NC Q5 V DDQ V SS V SS V SS V DDQ NC D3Q3F NC NC NC V DDQ V DD V SS V DD V DDQ NC NC NC G NC D6Q6 V DDQ V DD V SS V DD V DDQ NC NC NC H Doff V REF V DDQ V DDQ V DD V SS V DD V DDQ V DDQ V REF ZQ J NC NC NC V DDQ V DD V SS V DD V DDQ NC Q2D2K NC NC NC V DDQ V DD V SS V DD V DDQ NC NC NC L NC Q7D7 V DDQ V SS V SS V SS V DDQ NC NC Q1M NC NC NC V SS V SS V SS V SS V SS NC NC D1N NC D8NC V SS SA SA SA V SS NC NC NC P NC NC Q8SA SA C SA SA NC D0Q0RTDOTCKSASASACSASASATMSTDI11 x 15 Bump BGA—15 x 17 mm 2 Body—1 mm Bump PitchNote: MCL = Must Connect LowGS8662Q08/09/18/36E-300/250/200/167Pin Description TableSymbolDescriptionTypeCommentsSA Synchronous Address InputsInput —NC No Connect ——R Synchronous Read Input Active Low W Synchronous Write Input Active Low BW Synchronous Byte Write Input Active Low x9 only BW0–BW3Synchronous Byte Writes Input Active Low x18/x36 only NW0–NW1Nybble Write Control PinInput Active Low x8 only K Input Clock Input Active High K Input Clock Input Active Low C Output Clock Input Active High C Output Clock Input Active LowTMS Test Mode Select Input —TDI Test Data Input Input —TCK Test Clock Input Input —TDO Test Data Output Output —V REF HSTL Input Reference Voltage Input —ZQ Output Impedance Matching Input Input —Qn Synchronous Data Outputs Output Dn Synchronous Data Inputs Input D off Disable DLL when low Input Active LowCQ Output Echo Clock Output —CQ Output Echo Clock Output —V DD Power Supply Supply 1.8 V Nominal V DDQ Isolated Output Buffer Supply Supply 1.5 or 1.8 V NominalV SSPower Supply: GroundSupply—GS8662Q08/09/18/36E-300/250/200/167Note:NC = Not Connected to die or any other pinGS8662Q08/09/18/36E-300/250/200/167BackgroundSeparate I/O SRAMs, from a system architecture point of view, are attractive in applications where alternating reads and writes are needed. Therefore, the SigmaQuad-II SRAM interface and truth table are optimized for alternating reads and writes. Separate I/O SRAMs are unpopular in applications where multiple reads or multiple writes are needed because burst read or write transfers from Separate I/O SRAMs can cut the RAM’s bandwidth in half.Alternating Read-Write OperationsSigmaQuad-II SRAMs follow a few simple rules of operation.- Read or Write commands issued on one port are never allowed to interrupt an operation in progress on the other port.- Read or Write data transfers in progress may not be interrupted and re-started. - R and W high always deselects the RAM.- All address, data, and control inputs are sampled on clock edges.In order to enforce these rules, each RAM combines present state information with command inputs. See the Truth Table for details.SigmaQuad-II B2 SRAM DDR ReadThe read port samples the status of the Address Input and R pins at each rising edge of K. A low on the Read Enable-bar pin, R, begins a read cycle. Data can be clocked out after the next rising edge of K with a rising edge of C (or by K if C and C are tied high), and after the following rising edge of K with a rising edge of C (or by K if C and C are tied high). Clocking in a high on the Read Enable-bar pin, R, begins a read port deselect cycle.SigmaQuad-II B2 Double Data Rate SRAM Read FirstRead ANOPWrite BRead C Write DRead E Write FRead G Write HA B C D E F G HB B+1D D+1F F+1H H+1B B+1D D+1F F+1H H+1A A+1C C+1EKKAddress RWBWx D CCQ CQCQGS8662Q08/09/18/36E-300/250/200/167SigmaQuad-II B2 SRAM DDR WriteThe write port samples the status of the W pin at each rising edge of K and the Address Input pins on the following rising edge of K. A low on the Write Enable-bar pin, W, begins a write cycle. The first of the data-in pairs associated with the write command is clocked in with the same rising edge of K used to capture the write command. The second of the two data in transfers is captured on the rising edge of K along with the write address. Clocking in a high on W causes a write port deselect cycle.SigmaQuad-II B2 Double Data Rate SRAM Write FirstWrite ARead BRead C Write DNOPRead E Write FRead G Write HNOPA B C D E F G HA A+1D D+1F F+1H H+1A A+1D D+1F F+1H H+1B B+1C C+1E E+1KKAddress RWBWx D CCQ CQCQGS8662Q08/09/18/36E-300/250/200/167Power-Up Sequence for SigmaQuad-II SRAMsSigmaQuad-II SRAMs must be powered-up in a specific sequence in order to avoid undefined operations.Power-Up Sequence1. Power-up and maintain Doff at low state.1a.Apply V DD .1b. Apply V DDQ .1c. Apply V REF (may also be applied at the same time as V DDQ ).2. After power is achieved and clocks (K, K, C, C) are stablized, change Doff to high.3. An additional 1024 clock cycles are required to lock the DLL after it has been enabled.Note:If you want to tie Doff high with an unstable clock, you must stop the clock for a minimum of 30 seconds to reset the DLL after the clocks become stablized.DLL Constraints•The DLL synchronizes to either K or C clock. These clocks should have low phase jitter (t KCVar on page 21).•The DLL cannot operate at a frequency lower than 119 MHz.•If the incoming clock is not stablized when DLL is enabled, the DLL may lock on the wrong frequency and cause undefined errors or failures during the initial stage.Power-Up Sequence (Doff controlled)Power UP IntervalUnstable Clocking IntervalDLL Locking Interval (1024 Cycles)Normal OperationKKV DDV DDQV REFDoffPower-Up Sequence (Doff tied High)Power UP IntervalUnstable Clocking IntervalStop Clock IntervalDLL Locking Interval (1024 Cycles)Normal OperationKKV DDV DDQV REFDoff30ns MinNote:If the frequency is changed, DLL reset is required. After reset, a minimum of 1024 cycles is required for DLL lock.GS8662Q08/09/18/36E-300/250/200/167Special FunctionsByte Write and Nybble Write ControlByte Write Enable pins are sampled at the same time that Data In is sampled. A high on the Byte Write Enable pin associated with a particular byte (e.g., BW0 controls D0–D8 inputs) will inhibit the storage of that particular byte, leaving whatever data may be stored at the current address at that byte location undisturbed. Any or all of the Byte Write Enable pins may be driven high or low during the data in sample times in a write sequence.Each write enable command and write address loaded into the RAM provides the base address for a 2 beat data transfer. The x18 version of the RAM, for example, may write 36 bits in association with each address loaded. Any 9-bit byte may be masked in any write sequence.Nybble Write (4-bit) control is implemented on the 8-bit-wide version of the device. For the x8 version of the device, “Nybble Write Enable” and “NBx” may be substituted in all the discussion above.Example x18 RAM Write Sequence using Byte Write EnablesData In SampleTimeBW0BW1D0–D8D9–D17Beat 101Data In Don’t CareBeat 210Don’t Care Data InResulting Write OperationByte 1 D0–D8Byte 2D9–D17Byte 3D0–D8Byte 4D9–D17Written Unchanged Unchanged WrittenBeat 1Beat 2Output Register ControlSigmaQuad-II SRAMs offer two mechanisms for controlling the output data registers. Typically, control is handled by the Output Register Clock inputs, C and C. The Output Register Clock inputs can be used to make small phase adjustments in the firing of the output registers by allowing the user to delay driving data out as much as a few nanoseconds beyond the next rising edges of the K and K clocks. If the C and C clock inputs are tied high, the RAM reverts to K and K control of the outputs, allowing the RAM to function as a conventional pipelined read SRAM.A K RW A 0–AnK W 0D 1–D nBank 0Bank 1Bank 2Bank 3R 0D A K W D A K W D A K W D R R R QQQQCCCCQ 1–Q nC W 1R 1W 2R 2W 3R 3Note:For simplicity BWn, NWn, K, and C are not shown.CQ CQ CQ CQ CQ 0CQ 1CQ 2CQ 3GS8662Q08/09/18/36E-300/250/200/167Example Four Bank Depth Expansion SchematicΣ2x 2B 2 S i g m a Q u a d -I IS R A MD e p t hE x p a n s i o nR e a d A W r i t e BR e a d C W r i t e D R e a d E W r i t e F R e a d G W r i t e H R e a d I W r i t e J R e a d K W r i t e L N O PAB C D E F G H I J K LF F +1H H +1J J +1F F +1H H +1J J +1BB +1D D +1L L +1BB +1D D +1L L +1A A +1G G +1I I +1C C +1E E +1KKA d d r e s s R (B a n k 1)R (B a n k 2)W (B a n k 1)W (B a n k 2)B W x (B a n k 1)D (B a n k 1)B W x (B a n k 2)D (B a n k 2)C (B a n k 1)C (B a n k 1)Q (B a n k 1)C Q (B a n k 1)C Q (B a n k 1)C (B a n k 2)C (B a n k 2)Q (B a n k 2)C Q (B a n k 2)C Q (B a n k 2)GS8662Q08/09/18/36E-300/250/200/167GS8662Q08/09/18/36E-300/250/200/167FLXDrive-II Output Driver Impedance ControlHSTL I/O SigmaQuad-II SRAMs are supplied with programmable impedance output drivers. The ZQ pin must be connected to V SS via an external resistor, RQ, to allow the SRAM to monitor and adjust its output driver impedance. The value of RQ must be 5X the value of the desired RAM output impedance. The allowable range of RQ to guarantee impedance matching continuously is between 150Ω and 300Ω. Periodic readjustment of the output driver impedance is necessary as the impedance is affected by drifts in supply voltage and temperature. The SRAM’s output impedance circuitry compensates for drifts in supply voltage and temperature. A clock cycle counter periodically triggers an impedance evaluation, resets and counts again. Each impedance evaluation may move the output driver impedance level one step at a time towards the optimum level. The output driver isimplemented with discrete binary weighted impedance steps. Updates of pull-down drive impedance occur whenever a driver is producing a “1” or is High-Z. Pull-up drive impedance is updated when a driver is producing a “0” or is High-Z.SigmaQuad-II B2 Coherency and Pass Through FunctionsBecause the SigmaQuad-II B2 read and write commands are loaded at the same time, there may be some confusion over what constitutes “coherent” operation. Normally, one would expect a RAM to produce the just-written data when it is read immediately after a write. This is true of the SigmaQuad-II B2 except in one case, as is illustrated in the following diagram. If the user holds the same address value in a given K clock cycle, loading the same address as a read address and then as a matching write address, the SigmaQuad-II B2 will read or “Pass-thru” the latest data input, rather than the data from the previously completed write operation.SigmaQuad-II B2 Coherency and Pass Through FunctionsSeparate I/O SigmaQuad-II B2 SigmaQuad-II SRAM Read Truth TableA R Output Next StateQ Q K ↑(t n )K ↑(t n )K ↑(t n )K ↑(t n+1)K ↑(t n+1½)X 1Deselect Hi-Z Hi-Z VReadQ0Q1Notes:1.X = Don’t Care, 1 = High, 0 = Low, V = Valid.2.R is evaluated on the rising edge of K.3.Q0 and Q1 are the first and second data output transfers in a read.Separate I/O SigmaQuad-II B2 SigmaQuad-II SRAM Write Truth TableA W BWn BWn Input Next State D D K ↑(t n + ½)K ↑(t n )K ↑(t n )K ↑(t n + ½)K ↑, K ↑(t n ), (t n + ½)K ↑(t n )K ↑(t n + ½)V 000Write Byte Dx0, Write Byte Dx1D0D1V 001Write Byte Dx0, Write Abort Byte Dx1D0X V 010Write Abort Byte Dx0, Write Byte Dx1X D1X 011Write Abort Byte Dx0, Write Abort Byte Dx1X X X1XXDeselectXXNotes:1.X = Don’t Care, H = High, L = Low, V = Valid.2.W is evaluated on the rising edge of K.3.D0 and D1 are the first and second data input transfers in a write.4.BWn represents any of the Byte Write Enable inputs (BW0, BW1, etc.).GS8662Q08/09/18/36E-300/250/200/167x36 Byte Write Enable (BWn) Truth TableBW0BW1BW2BW3D0–D8D9–D17D18–D26D27–D351111Don’t Care Don’t Care Don’t Care Don’t Care 0111Data In Don’t Care Don’t Care Don’t Care 1011Don’t Care Data In Don’t Care Don’t Care 0011Data In Data In Don’t Care Don’t Care 1101Don’t Care Don’t Care Data In Don’t Care 0101Data In Don’t Care Data In Don’t Care 1001Don’t Care Data In Data In Don’t Care 0001Data In Data In Data In Don’t Care 1110Don’t Care Don’t Care Don’t Care Data In 0110Data In Don’t Care Don’t Care Data In 1010Don’t Care Data In Don’t Care Data In 0010Data In Data In Don’t Care Data In 1100Don’t Care Don’t Care Data In Data In 0100Data In Don’t Care Data In Data In 1000Don’t Care Data In Data In Data In 0Data InData InData InData Inx18 Byte Write Enable (BWn) Truth Table BW0BW1D0–D8D9–D1711Don’t Care Don’t Care 01Data In Don’t Care 10Don’t Care Data In 0Data InData Inx8 Nybble Write Enable (NWn) Truth Table NW0NW1D0–D3D4–D711Don’t Care Don’t Care 01Data In Don’t Care 10Don’t Care Data In 0Data InData InGS8662Q08/09/18/36E-300/250/200/167GS8662Q08/09/18/36E-300/250/200/167State DiagramPower-UpRead NOPLoad New Read Address DDR Read Write NOPLoad New Write AddressDDR WriteWRITEREAD READ WRITEREAD WRITEAlways (Fixed)Always (Fixed)READWRITENotes:1.Internal burst counter is fixed as 1-bit linear (i.e., when first address is A0+), next internal burst address is A0+1.2.“READ” refers to read active status with R = Low, “READ” refers to read inactive status with R = High. The same istrue for “WRITE” and “WRITE”.3.Read and write state machine can be active simultaneously.4.State machine control timing sequence is controlled by K.Absolute Maximum Ratings(All voltages reference to V SS )SymbolDescriptionValueUnitV DD Voltage on V DD Pins –0.5 to 2.9V V DDQ Voltage in V DDQ Pins –0.5 to V DD V V REF Voltage in V REF Pins –0.5 to V DDQV V I/O Voltage on I/O Pins –0.5 to V DDQ +0.5 (≤ 2.9 V max.)V V IN Voltage on Other Input Pins –0.5 to V DDQ +0.5 (≤ 2.9 V max.)V I IN Input Current on Any Pin +/–100mA dc I OUT Output Current on Any I/O Pin +/–100mA dcT J Maximum Junction Temperature125o C T STGStorage Temperature–55 to 125oCNote:Permanent damage to the device may occur if the Absolute Maximum Ratings are exceeded. Operation should be restricted to Recommended Operating Conditions. Exposure to conditions exceeding the Recommended Operating Conditions, for an extended period of time, may affect reliability of this component.GS8662Q08/09/18/36E-300/250/200/167Recommended Operating ConditionsPower SuppliesParameterSymbolMin.Typ.Max.UnitSupply Voltage V DD 1.7 1.8 1.9V I/O Supply Voltage V DDQ 1.4 1.5V DD V Reference VoltageV REF0.68—0.95VNotes:1.The power supplies need to be powered up simultaneously or in the following sequence: V DD , V DDQ , V REF , followed by signalinputs. The power down sequence must be the reverse. V DDQ must not exceed V DD .2.Most speed grades and configurations of this device are offered in both Commercial and Industrial Temperature ranges. Thepart number of Industrial Temperature Range versions end the character “I”. Unless otherwise noted, all performance specifications quoted are evaluated for worst case in the temperature range marked on the device.Operating TemperatureParameterSymbolMin.Typ.Max.UnitAmbient Temperature (Commercial Range Versions)T A 02570°C Ambient Temperature (Industrial Range Versions)T A–402585°CGS8662Q08/09/18/36E-300/250/200/167HSTL I/O DC Input CharacteristicsParameterSymbolMinMaxUnitsNotesDC Input Logic High V IH (dc)V REF + 0.1V DD + 0.3 V 1DC Input Logic LowV IL (dc)–0.3V REF – 0.1V1Notes:patible with both 1.8 V and 1.5 V I/O drivers2.These are DC test criteria. DC design criteria is V REF ± 50 mV. The AC V IH /V IL levels are defined separately for measuring timing param-eters.3.V IL (Min)DC = –0.3 V, V IL (Min)AC = –1.5 V (pulse width ≤ 3 ns).4.V IH (Max)DC = V DDQ + 0.3 V, V IH (Max)AC = V DDQ + 0.85 V (pulse width ≤ 3 ns).HSTL I/O AC Input CharacteristicsParameterSymbolMinMaxUnitsNotesAC Input Logic High V IH (ac)V REF + 200—mV 3,4AC Input Logic LowV IL (ac)—V REF – 200mV 3,4V REF Peak to Peak AC VoltageV REF (ac)—5% V REF (DC)mV1Notes:1.The peak to peak AC component superimposed on V REF may not exceed 5% of the DC component of V REF .2.To guarantee AC characteristics, V IH ,V IL , Trise, and Tfall of inputs and clocks must be within 10% of each other.3.For devices supplied with HSTL I/O input buffers. Compatible with both 1.8 V and 1.5 V I/O drivers.20% tKHKHV SS – 1.0 V50%V SS V IHUndershoot Measurement and TimingOvershoot Measurement and Timing20% tKHKHV DD + 1.0 V50%V DDV ILCapacitanceo C, f = 1 MH Z , V DDParameterSymbolTest conditionsTyp.Max.UnitInput Capacitance C IN V IN = 0 V 45pF Output Capacitance C OUT V OUT = 0 V 67pF Clock CapacitanceC CLKV IN = 0 V56pFNote:This parameter is sample tested.GS8662Q08/09/18/36E-300/250/200/167AC Test ConditionsParameterConditionsInput high level 1.25 V Input low level 0.25 V Max. input slew rate 2 V/ns Input reference level 0.75 V Output reference levelV DDQ /2Note:Test conditions as specified with output loading as shown unless otherwise noted.DQVT = V DDQ /250ΩRQ = 250 Ω (HSTL I/O)V REF = 0.75 VAC Test Load DiagramInput and Output Leakage CharacteristicsParameterSymbolTest ConditionsMin.MaxNotesInput Leakage Current (except mode pins)I IL V IN = 0 to V DD –2 uA 2 uA DoffI INDOFF V DD ≥ V IN ≥ V IL 0 V ≤ V IN ≤ V IL –2 uA –2 uA 2 uA 2 uA Output Leakage CurrentI OLOutput Disable,V OUT = 0 to V DDQ–2 uA2 uA(T A = 25= 1.8 V)GS8662Q08/09/18/36E-300/250/200/167Programmable Impedance HSTL Output Driver DC Electrical CharacteristicsParameterSymbolMin.Max.UnitsNotesOutput High Voltage V OH1 V DDQ /2 – 0.12V DDQ /2 + 0.12V 1, 3Output Low Voltage V OL1 V DDQ /2 – 0.12V DDQ /2 + 0.12V 2, 3Output High Voltage V OH2 V DDQ – 0.2V DDQ V 4, 5Output Low VoltageV OL2Vss0.2V4, 6Notes:1. I OH = (V DDQ /2) / (RQ/5) +/– 15% @ V OH = V DDQ /2 (for: 175Ω ≤ RQ ≤ 350Ω).2. I OL = (V DDQ /2) / (RQ/5) +/– 15% @ V OL = V DDQ /2 (for: 175Ω ≤ RQ ≤ 350Ω).3.Parameter tested with RQ = 250Ω and V DDQ = 1.5 V or 1.8 V4.Minimum Impedance mode, ZQ = V SS5.I OH = –1.0 mA6.I OL = 1.0 mAOperating CurrentsParameterSymbolTest Conditions-300-250-200-167Notes0to 70°C –40 to 85°C0to 70°C –40 to 85°C0to 70°C –40 to 85°C0to 70°C –40 to 85°C Operating Current (x36): DDR I DD V DD = Max, I OUT = 0 mA Cycle Time ≥ t KHKH Min 900 mA920 mA 800 mA820 mA 670 mA690 mA 590 mA610 mA2, 3Operating Current (x18): DDR I DD V DD = Max, I OUT = 0 mA Cycle Time ≥ t KHKH Min 840 mA 860 mA 740 mA 760 mA 620 mA 640 mA 550 mA 570 mA 2, 3Operating Current (x9): DDR I DD V DD = Max, I OUT = 0 mA Cycle Time ≥ t KHKH Min 840 mA 860 mA 740 mA 760 mA 620 mA 640 mA 550 mA 570 mA 2, 3Operating Current (x8): DDR I DDV DD = Max, I OUT = 0 mA Cycle Time ≥ t KHKH Min 840 mA 860 mA 740 mA 760 mA 620 mA 640 mA 550 mA 570 mA 2, 3Standby Current (NOP): DDR I SB1Device deselected,I OUT = 0 mA, f = Max,All Inputs ≤ 0.2 V or ≥ V DD – 0.2 V330 mA 340 mA 300 mA 310 mA 280 mA 290 mA 260 mA 270 mA 2, 4Notes:1.Power measured with output pins floating.2.Minimum cycle, I OUT = 0 mA3.Operating current is calculated with 50% read cycles and 50% write cycles.4.Standby Current is only after all pending read and write burst operations are completed.GS8662Q08/09/18/36E-300/250/200/167AC Electrical CharacteristicsParameter Symbol-300-250-200-167Units Notes Min Max Min Max Min Max Min MaxClockK, K Clock Cycle Time C, C Clock Cycle Time t KHKHt CHCH3.34.2 4.0 6.35.07.886.08.4nstKC Variable t KCVar—0.2—0.2—0.2—0.2ns5K, K Clock High Pulse Width C, C Clock High Pulse Width t KHKLt CHCL1.32— 1.6—2.0— 2.4—nsK, K Clock Low Pulse Width C, C Clock Low Pulse Width t KLKHt CLCH1.32— 1.6—2.0— 2.4—nsK to K HighC to C Hight KHKH 1.49— 1.8— 2.2— 2.7—nsK, K Clock High to C, C Clock High t KHCH0 1.450 1.80 2.30 2.8nsDLL Lock Time t KCLock1024—1024—1024—1024—cycle6 K Static to DLL reset t KCReset30—30—30—30—ns Output TimesK, K Clock High to Data Output Valid C, C Clock High to Data Output Valid t KHQVt CHQV—0.45—0.45—0.45—0.5ns3K, K Clock High to Data Output Hold C, C Clock High to Data Output Hold t KHQXt CHQX–0.45—–0.45—–0.45—–0.5—ns3K, K Clock High to Echo Clock Valid C, C Clock High to Echo Clock Valid t KHCQVt CHCQV—0.45—0.45—0.45—0.5nsK, K Clock High to Echo Clock Hold C, C Clock High to Echo Clock Hold t KHCQXt CHCQX–0.45—–0.45—–0.45—–0.5—nsCQ, CQ High Output Valid t CQHQV—0.27—0.30—0.35—0.40ns7 CQ, CQ High Output Hold t CQHQX–0.27—–0.30—–0.35—–0.40—ns7K Clock High to Data Output High-Z C Clock High to Data Output High-Z t KHQZt CHQZ—0.45—0.45—0.45—0.5ns3K Clock High to Data Output Low-Z C Clock High to Data Output Low-Z t KHQX1t CHQX1–0.45—–0.45—–0.45—–0.5—ns3Setup TimesAddress Input Setup Time t AVKH0.3—0.35—0.4—0.5—nsControl Input Setup Time t IVKH0.3—0.35—0.4—0.5—ns2 Data Input Setup Time t DVKH0.3—0.35—0.4—0.5—nsGS8662Q08/09/18/36E-300/250/200/167Hold TimesAddress Input Hold Time t KHAX 0.3—0.35—0.4—0.5—ns Control Input Hold Time t KHIX 0.3—0.35—0.4—0.5—ns Data Input Hold Timet KHDX0.3—0.35—0.4—0.5—nsNotes:1.All Address inputs must meet the specified setup and hold times for all latching clock edges.2.Control singles are R, W, BW0, BW1, and (NW0, NW1 for x8) and (BW2, BW3 for x36).3.If C, C are tied high, K, K become the references for C, C timing parameters4.To avoid bus contention, at a given voltage and temperature tCHQX1 is bigger than tCHQZ. The specs as shown do not imply bus contention because tCHQX1 is a MIN parameter that is worst case at totally different test conditions (0°C, 1.9 V) than tCHQZ, which is a MAX parameter (worst case at 70°C, 1.7 V). It is not possible for two SRAMs on the same board to be at such different voltages and temperatures.5.Clock phase jitter is the variance from clock rising edge to the next expected clock rising edge.6.V DD slew rate must be less than 0.1 V DC per 50 ns for DLL lock retention. DLL lock time begins once V DD and input clock are stable.7.Echo clock is very tightly controlled to data valid/data hold. By design, there is a ±0.1 ns variation from echo clock to data. The datasheet parameters reflect tester guard bands and test setup variations.AC Electrical Characteristics (Continued)ParameterSymbol-300-250-200-167Units NotesMinMaxMinMaxMinMaxMinMax。

EncorePro 300 Series 头沿式耳机使用说明书

EncorePro 300 Series Schnurgebundenes HeadsetBedienungsanleitungInhaltÜberblick3Einrichtung4Download der Software4Passung5Kopfbügel anpassen5Positionieren des Mikrofonarms5Anpassen des Mikrofonarms5Grundlagen6Anrufe tätigen/annehmen/beenden6Lautstärke6Stumm6Support7Gesprächstaste Blinkt dreimal grün Eingehender AnrufLangsames, grünes Blinken Anruf halten Leuchtet grün auf Laufendes GesprächT aste zum Erhöhen der LautstärkeHörlautstärke erhöhen T aste zum Verringern der LautstärkeHörlautstärke verringern Stummschaltung Leuchtet durchgehend rotHeadset ist stummgeschaltet HINWEIS Inline-Steuerungen können je nach mit den DA70/DA80-Audioprozessoren verbundenen Headsets variieren.ÜberblickSchalten Sie Ihr Headset ein, indem Sie es mit dem Computer verbinden.Ihr Headset lässt sich auf zwei Arten verbinden:•über den USB-Anschluss •per DA70/DA80-Audioprozessor mit Quick Disconnect (QD)Laden Sie Poly Lens-App herunter, um Ihre Gerät optimal zu nutzen. Manche Softphoneserfordern die Installation von Poly Software, um Steuerungsfunktionen (Anruf annehmen/beenden und Stummschaltung) des Geräts zu unterstützen. Download: /software .•Funktionen aktivieren•Einstellungen ändern•Anrufsteuerung für Softphones konfigurieren•Geräte-Firmware aktualisieren•Benachrichtigungen und Warnungen verwalten•Gesundheits- und Wellness-Erinnerungen einrichtenHINWEIS Die Geräteeinstellungen und -Updates sind auch in der Plantronics Hub Appverfügbar.EinrichtungDownload der SoftwareVerlängern oder verkürzen Sie den Kopfbügel so, dass das Headset angenehm sitzt. DieOhrkissen sollten bequem am Ohr anliegen.Dieses Headset kann sowohl links als auch rechts getragen werden.Drehen Sie den Mikrofonarm so, dass sich das Mikrofon direkt vor Ihrem Mund befindet.VORSICHT Stellen Sie den Mikrofonarm auf bis zu 180°, damit dieser nicht beschädigt wird.Positionieren Sie den Mikrofonarm vorsichtig so, dass er in einem Abstand von 3 cm zur Ecke Ihres Mundes zeigt.PassungKopfbügel anpassenPositionieren desMikrofonarmsAnpassen desMikrofonarms/software ) nicht Gesprächstaste am Headset und tätigen/beenden Sie dann den Anruf über die Softphone-Anwendung.Annehmen und Beenden von Anrufen Tippen Sie auf die Gesprächstaste oder nehmen Sie den Anruf über Ihr Softphone an.Anruf tätigen Wählen Sie mithilfe der Softphone-Anwendung.Halten Halten Sie die Gesprächstaste 2 Sekunden lang gedrückt, um einen Anruf zu halten.Hörlautstärke Drücken Sie die Taste zum Erhöhen (+) oder Verringern (-) der Lautstärke.Anpassen der Lautstärke des Headset-Mikrofons (Softphone)Führen Sie einen Testanruf mit dem Softphone durch und passen Sie die Softphone-Lautstärke und den PC-Sound an.Drücken Sie die Stummschalttaste , um Ihr Headset während eines aktiven Anrufsstummzuschalten oder die Stummschaltung aufzuheben.GrundlagenAnrufe tätigen/annehmen/beendenLautstärkeStummSupportBENÖTIGEN SIE WEITERE HILFE?/supportHersteller:Plantronics, Inc.Plantronics B.V.Plantronics Ltd.345 Encinal Street Santa Cruz, CA 95060 United States Scorpius 1712132 LR HoofddorpNetherlandsBuilding 4, Foundation ParkCannon Lane, Part 1st FloorMaidenhead, SL6 3UDUnited Kingdom© 2022 Poly. Alle Markennamen sind Eigentum ihrer jeweiligen Besitzer. Hergestellt von Plantronics, Inc.216045-04 01.22。

固高用户手册(GE系列)

技术支持和售后服务

您可以通过以下途径获得我们的技术支持和售后服务: ♦ 电子邮件: support@; ♦ 电话: (0755) 26970835 ♦ 发函至:深圳市高新技术产业园南区园深港产学研基地西座二楼 W211 室 固高科技(深圳)有限公司 邮编:518057

固高科技(香港)有限公司

地 址:香港九龙清水湾香港科技大学新翼楼 3639 室 电 话:(852) 2358-1033 传 真:(852) 2358-4931 电子邮件:info@ 网 址:/

GE 系列运动控制器 用户手册

运动中的机器有危险!使用者有责任在机器中设计有效的出错处理和 安全保护机制,固高科技没有义务或责任对由此造成的附带的或相应 产生的损失负责。

前言

前言

感谢选用固高运动控制器

为回报客户,我们将以品质一流的运动控制器、完善的售后服务、高效的技术支持,帮 助您建立自己的控制系统。

固高产品的更多信息

固高科技的网址是 。在我们的网页上可以得到更多关 于公司和产品的信息,包括:公司简介、产品介绍、技术支持、产品最新发布等等。

固高科技(深圳)有限公司

地 址:深圳市高新技术产业园南区深港产学研基地西座 二层 W211 室

电 话:0755-26970823 26970817 26970824 传 真:0755-26970846 电子邮件:support@ 网 址:

2.3.1 步骤 1:在运动控制器上设置跳线(仅对 ISA 卡).................................................... 8 2.3.2 步骤 2:将运动控制器插入计算机 .............................................................................. 10 2.3.3 步骤 3:安装控制器通讯驱动(Windows 操作系统) ............................................ 11 2.3.4 步骤 4:建立主机与运动控制器的通讯(Windows 操作系统) ............................ 11 2.3.5 步骤 5:连接电机和驱动器........................................................................................ 11 2.3.6 步骤 6:连接运动控制器和端子板 ............................................................................ 11 2.3.7 步骤 7:连接驱动器、系统输入/输出和端子板 ....................................................... 12

汇泽源GE300软启动柜说明书

汇泽源GE300软启动柜说明书

1、自动操作:接通电源,电源指示灯亮,将转换开关转至“自动”位置,检查控制柜(箱)所控制的电机是否按液位控制仪的指令动作。

当液位达到控制液位时,对应液位指示灯发光,相应的限位控制继电器常开触点自动闭合,二次控制回路自动接通,电机起动,同时运行指示灯亮。

当水位达到停止水位时,对应的指示灯发光,液位测控仪的对应限位控制继电器常闭触点断开,二次控制回路开路,电机停止工作,运行指示灯熄灭。

2、手动操作:接通电源,电源指示灯亮,将转换开关转至“手动”位置,按下起动按钮,电机开始运转,运行指示灯亮,按下”停止”按钮,电机停止运转,其运行指示灯熄灭。

3、不论采用何种控制方式,当达到极限水位时,其超限水位信号触点接通,二次控制回路失电,使电机停止运转,并发出声光报苦信号。

在电机运行过程中如有事故出现,事故指示灯亮,电铃自动报苦,这时,按下停止按钮,迫使电机停止工作。

FM11-GE-300_消回音

FM11-GE-300Low-Power Voice Processor Data Sheet v1.0September 2008PRELIMINARY INFORMATIONTHIS DOCUMENT CONTAINS INFORMATION ON A PREPRODUCTION PRODUCT. SPECIFICATIONS AND PREPRODUCTION INFORMATION HEREIN ARE SUBJECT TO CHANGE WITHOUT NOTICE.FORTEMEDIA, INC. PRODUCTS ARE NOT INTENDED FOR LIFE SAVING NOR LIFE SUSTAINING APPLICATIONS AND FORTEMEDIA, INC. THUS, ASSUMES NO LIABILITY IN SUCH USAGES. FORTEMEDIA, INC. PRODUCTS MAY ONLY BE USED IN LIFE-SUPPORT DEVICES OR SYSTEMS WITH THE EXPRESS WRITTEN APPROVAL OF FORTEMEDIA, INC., IF A FAILURE OF SUCH COMPONENTS CAN REASONABLY BE EXPECTED TO CAUSE THE FAILURE OF THAT LIFE-SUPPORT DEVICE OR SYSTEM, OR TO AFFECT THE SAFETY OR EFFECTIVENESS OF THAT DEVICE OR SYSTEM. LIFE SUPPORT DEVICES OR SYSTEMS ARE INTENDED TO BE IMPLANTED IN THE HUMAN BODY, OR TO SUPPORT AND/OR MAINTAIN AND SUSTAIN AND/OR PROTECT HUMAN LIFE. IF THEY FAIL, IT IS REASONABLE TO ASSUME THAT THE HEALTH OF THE USER OR OTHER PERSONS MAY BE ENDANGERED.WE HEREIN DISCLAIM ANY AND ALL WARRANTIES, INCLUDING BUT NOT LIMITED TO WARRANTIES OF NON-INFRINGEMENT, REGARDING CIRCUITS, DESCRIPTIONS AND CHARTS STATED HEREIN.Fortémedia, SAM, fortémedia and SAM logos are trademarks of Fortémedia, Inc.All other trademarks belong to their respective companies.Copyright © 2007-2008 Fortémedia. All rights reserved.TABLE OF CONTENT1. INTRODUCTION (7)1.1O VERVIEW (7)1.2K EY F EATURES (7)1.3I NTERNAL H ARDWARE B LOCK D IAGRAM (8)2. FUNCTIONAL BLOCKS DESCRIPTION (9)2.1S ERIAL EEPROM I NTERFACE (P INS 15,16) (9)2.2UART I NTERFACE (P INS 12,13) (9)2.3SHI(S ERIAL H OST I NTERFACE)(P INS 23,24) (10)2.4S ERIAL P ORT (P INS 8,9,10,11) (11)2.5ADC(P INS 39,40,41,42,43,44) (12)2.6DAC(P INS 3,47,48) (12)3. SYSTEM OPERATIONAL DESCRIPTION (13)3.1M ODES OF O PERATION (13)3.2P OWER-U P O PTION P INS (S TRAP O PTIONS) (16)3.3P OWER O N/O FF T IMING (17)3.4S YSTEM C LOCK (18)3.5A CCESSING FM11-GE-300T HROUGH EEPROM,UART,SHI (18)3.5.1 Accessing Through EEPROM (18)3.5.2 Examples of Accessing Through EEPROM (18)3.5.3 Accessing Through UART (19)3.5.4 Examples of Accessing Through UART (19)3.6M ISCELLANEOUS F UNCTIONS (20)4. ELECTRICAL & TIMING SPECIFICATION (21)4.1A BSOLUTE M AXIMUM R ATINGS (21)4.2R ECOMMENDED O PERATING C ONDITIONS (21)4.3DC C HARACTERISTICS (21)4.4AC C HARACTERISTICS (22)4.5DSP P ERFORMANCE D ETAILS (23)4.6T IMING C HARACTERISTICS (23)5. PIN DEFINITION (26)6. PACKAGING (30)7. ORDERING INFORMATION (31)APPENDIX I: REQUIRED EXTERNAL COMPONENTS FOR OPERATION (32)APPENDIX II: AUDIO MEASUREMENT SYSTEM (33)APPENDIX III: SUGGESTED EXTERNAL POWER CIRCUITRY (34)REFERENCES (35)I.T ERMINOLOGY (35)II.R ELATED D OCUMENTS (35)FIGURESFigure 1: Internal Hardware Block Diagram (8)Figure 2: UART Interface: 8-bit/character, 1 stop-bit protocol (9)Figure 3: UART Transfers(TX & RX) (9)Figure 4: SHI Start, Restart, & Stop (10)Figure 5: SHI Burst write (on SDA) (10)Figure 6: SHI Read (on SDA) (10)Figure 7: Serial Port - One Clock Delay (11)Figure 8: Serial Port - Zero Clock Delay (11)Figure 9: FM11-GE-300 ADC Details (12)Figure 10: FM11-GE-300 DAC Details (12)Figure 11: State Transition Diagram (14)Figure 12: Timing Chart of State Transitions (15)Figure 13: Timing Chart of Power Down Transition (15)Figure 14: Timing Chart of External Reset (16)Figure 15: Timing Chart of Power On/Off Sequence (17)Figure 16: Power-down to Speaker-out Timing (24)Figure 17: Digital Input Timing (No Clock Delay) (24)Figure 18: Digital Input Timing (One Clock Delay) (24)Figure 19: Digital Output Timing (No Clock Delay) (25)Figure 20: Digital Output Timing (One Clock Delay) (25)Figure 21: FM-GE-300 Pin Configuration (28)Figure 22: PAD_IN Symbol for Digital Input Pins (28)Figure 23: PAD_BI Symbol for Digital Input/Output Pins (29)Figure 24: LQFP Packaging Drawings (30)Figure 25: External XTAL_IN Clock Source (32)Figure 26: Echo Cancellation Test Setup (33)Figure 27: Noise Suppression Test Setup (33)Figure 28: Suggested External Power Circuitry (34)TABLESTable 1: Status of Serial Port Output Pins (11)Table 2: Strap Option Pins to Select Desired Operation (16)Table 3: Strap Option Pins for EEPROM (16)Table 4: Strap Pin settings for default internal mode (17)Table 5: Command Entry Data Pattern (18)Table 6: Command Entries (18)Table 7: Examples of Accessing Through EEPROM (18)Table 8: Examples of Accessing Through UART (19)Table 9: Absolute Maximum Ratings (21)Table 10: Recommended Operating Conditions (21)Table 11: DC Characteristics (21)Table 12: AC Characteristics (22)Table 13: ADC(Mic0/Mic1/Line_in) PGA Gain (22)Table 14: DAC(Line_out, Speaker Out) PGA Gain (23)Table 15: DSP Performance Details (23)Table 16: Timing Characteristics (23)Table 17: Pin Number sorted Description (26)Table 18: Ordering Information (31)Table 19: External Components Recommendation (32)Table 20: Echo Cancellation Measurement (33)Table 21: Noise Suppression Measurement (33)Table 22: Terminology (35)Table 23: Related Reference Documents (35)Revision HistoryRevision Description Date0.1 Initial Draft Aug 20081.0 Initial Release Sept 20081. IntroductionFortemedia’s FM11-GE-300 voice processor is a high-performance, low-power single chip solution for echo cancellation and noise suppression. Providing SAM (small array microphone) technology supporting beam forming capability while consuming only 30mW power, FM11-GE-300 is ideal for any portable application with stringent requirements for battery life and power consumption. Offered in a 7x7mm² LQFP package, the FM11-GE-300 is ideally suited for applications such as hands free car kit, cordless desktop speaker phone, notebook computers and VoIP phones.For more information, please refer to the Fortemedia Technology White Paper.1.1 OverviewTo achieve the lowest power consumption, FM11-GE-300 features an integrated hardware accelerator to speed up voice related applications. This new device is designed to achieve the lowest power while providing the highest performance. With an enhanced CODEC, FM11-GE-300 provides high SNR for the best voice quality. FM11-GE-300 provides excellent noise suppression and full duplex capabilities, including non-linear echo cancellation and side tone cancellation.1.2 Key FeaturesHighly integrated single chip solution▪16-bit DSP w/ Hardware Accelerator▪ 3 ADC (Analog to Digital Converter)▪ 2 DAC (Digital to Analog Converter)▪RAM, ROM▪On-chip microphone amplifier▪SHI, UART interface to external controller▪Serial port interface supports 16-bit & 13-bit PCM formatLow power consumption (30mW)High performance▪Powerful AEC (acoustic echo cancellation) (60dB)▪Superior full-duplex▪Supports 1 & 2 microphone modes▪Run-time microphone select mode♦Select Mic0 or Mic1 as the main microphone (when using small array microphone with beam-forming) ▪Differential I/O to reduce RF interference and increase noise immunity▪Dynamic range control (DRC) to increase voice intelligibility▪Side tone cancellation of 25 to 35dB▪Acoustic echo tail length coverage: 64 to 100ms▪Mic_in, Line_in, Line_out, & Spk_out PGA (programmable gain amplification)Supports 2 clock inputs: 4.096MHz or 13MHz48-pin LQFP package option1.3 Internal Hardware Block DiagramM I C 0I /FFigure 1: Internal Hardware Block Diagram2. Functional Blocks DescriptionWith many built-in functions and modes of operation, designers can easily implement their low power voice processing systems with the FM11-GE-300. The IC can be analyzed in different interface blocks which include EEPROM serial interface, UART, Serial Host Interface (SHI), serial port, ADC and DAC. UART and SHI communication are just some examples of FM11-GM-300’s digital interfaces.Please refer to Figure 1 for an overview of the internal block functions.2.1 Serial EEPROM Interface (Pins 15, 16)FM11-GE-300 supports a serial interface to an optional external EEPROM. It supports 256 bytes (small sized) and 1Kbytes (large sized) EEPROM. Most of the internal variables can be accessed through this EEPROM interface. See section 3 for more details.2.2 UART Interface (Pins 12, 13)FM11-GE-300 has one UART port which is used to transmit and receive control commands. Each transfer will have one command byte, one or two address bytes, and up to two data bytes. UART needs a sync word “FCF3” to sync up each transfer. See section 3 for more details.NOTE: The UART port is recommended as the standard interface to access FM11-GE-300.8-bit/character 1 stop-bit protocolFigure 3: UART Transfers(TX & RX)2.3 SHI (Serial Host Interface) (Pins 23, 24)The SHI block is the interface to an external micro-controller which can initialize FM11-GE-300 through thisinterface. SHI supports slave mode with 8 bit address mode. The maximum clock speed that the SHI interface can support is 100 KHz. Each transfer will have one command byte, one or two address bytes, and up to two data bytes. SHI needs a sync word “FCF3” to sync up each transfer. Please note that SHI is used for transferring parameters during power-up, and is off after the DSP is in normal operation mode. Please refer to section 3 and FM11-GE-300 SHI Implementation Application Note for more details.S: start, Sr: restart, P: stop, Ack: acknowledgeStart, Restart and StopFigure 4: SHI Start, Restart, & StopFigure 5: SHI Burst write (on SDA)Figure 6: SHI Read (on SDA)Burst WriteRead2.4 Serial Port (Pins 8, 9, 10, 11)The serial port provides an interface to an existing host (micro-controller) for digital voice data transfer. Both themaster and the slave modes support either an internal or external clock source for the BCLK signal. While operating with the internal clock, “FSYNC” runs at 8KHz.The serial port data format can be 16-bit or 13-bit linear pulse code modulation (linear PCM). The default setting is to run 16-bit linear PCM mode. The format can be selected by EEPROM or an external controller.In slave mode, FM11-GE-300 supports both short (one clock delay) and long (zero clock delay) “FSYNC”. In master mode, FM11-GE-300 drives short “FSYNC”. Table 1 below shows the status of the serial port output pins during different modes.Table 1: Status of Serial Port Output Pins Master Mode Slave ModePower-down Serial Port Enabled (1) Analog Mode (2) Power-down Serial Port Enabled (1)Analog Mode (2) BCLK Tri-state Normal “0” n/a n/a “0” FSYNC Tri-state Normal “0” n/a n/a “0” PCM_OUT Tri-stateTri-stateTri-stateTri-stateTri-stateTri-stateNotes:(1) CHI_EN (bit2 of 0x3fe1) set to “0” (Refer to FM11-GE-300 Parameter Tuning Guide)(2) ANA_COM asserted during reset; otherwise, asserting ANA_COM will turn off all digital clocks and leavestates unknownFigure 7: Serial Port - One Clock DelayFigure 8: Serial Port - Zero Clock DelayBCLKMSBMSB1MSB MSB1 PCM_OUTPCM_INFSYNC2.5 ADC (Pins 39, 40, 41, 42, 43, 44)FM11-GE-300 includes 3 analog-to-digital converters (ADC). The converters are at 16-bit precision and 8ksampling rate with sigma-delta architecture. All 3 converters are differential; they are used for 2 microphone inputs with built-in microphone pre-amplifier and 1 line level input. The full scale of the input is 2.4Vpp. See figure 10 fordetails.For more information on how to program the attenuation/gains for the ADC and DAC blocks, please refer to theFM11GE-300 Parameter Tuning Guide.Figure 9: FM11-GE-300 ADC Details2.6 DAC (Pins 3, 47, 48)FM11-GE-300 includes two digital-to-analog converters (DAC). The converters are at 16-bit precision and 8k sampling rate with sigma-delta architecture. One of the converters (differential) is used to feed into an external power amplifier to drive the speaker (Spk_out). The other converter (single-ended) provides programmable attenuations/gains that can be connected to a PC’s analog input (Line_out). See figure 11 for more details.For more information on how to program the attenuation/gains for the ADC and DAC blocks, please refer to the FM11-GE-300 Parameter Tuning Guide.Figure 10: FM11-GE-300 DAC Details+-Max 1.5VppMax 1.5VppMax 1.5Vpp3. System Operational Description3.1 Modes of OperationDepending on the condition, the FM11-GE-300 chip may enter into in one of the following four modes.Hardware Reset ModeWhenever power is applied, the chip will enter this mode and remain until 10ms after the RST_ pin is pulled high. In this mode, the chip samples the strap-options (section 3.2), adjusts the clock source, and waits for the external clock (XTAL_IN or BCLK) and internal PLL to become stable. After the 10ms, the chip enters the Software Reset Mode. The chip re-enters the Hardware Reset Mode whenever the RST_ pin is pulled low externally.Software Reset ModeIn this mode, the embedded DSP software reads the strap-options (section 3.2), determines where the parameters will be coming from, and then either waits passively for the download from an external host (UART, SHI) or actively reads the parameters from an external EEPROM. The chip exits this mode when parameter at 1E3A becomes 0 (handled by embedded DSP when parameter configuration is done). Except when RST_ is pulled low, the chip moves to the Operational Mode after the Software Reset Mode.Operational ModeIn this mode, software will set up hardware MMREGs according to the parameter configuration, followed by a nominal 70ms for initialization. This is the mode where the chip samples its input and delivers its outputs through the analog/digital interfaces. After that, the chip may enter the Power Down Mode if the PWD_ pin is pulled low.Power Down ModeThe chip enters the Power Down Mode 10ms after the PWD_ pin is pulled low. During the Power Down Mode, the PLL source clock can also be turned off because the on-chip PLL is turned off. After the Power Down Mode, the chip may move to either the Software Reset Mode or the Operational Mode (depending on the setting of the pwrdwn_set parameter, 1E51). In order for the chip to exit the Power Down Mode correctly, the external PLL source clock must resume 10ms before PWD_ is pulled high. After that, the chip will need another 13ms for house-cleaning work before it can take the new round of parameter download, or resume to the Operational Mode.The following figures show the state transition diagram and the timing chart when the FM11-GE-300 chip moves between these 4 states.Figure 11: State Transition DiagramFigure 12: Timing Chart of State TransitionsFigure 14: Timing Chart of External Reset3.2 Power-Up Option Pins (Strap Options)Strap options are used by the chip to determine the desired operation of the chip. All the strap options mentioned below must be pulled high or low using a weak 100k resistor. If left floating, the status will be unknown.In the software reset mode, the chip samples 5 different strap options to determine desired operation, such as where the chip will load its parameters from (through an external EEPROM or from an external µP through the UART or SHI interface).Table 2: Strap Option Pins to Select Desired OperationModePin 17(GPIO7)Pin 20(STRAP0)Pin 21(MUTE_OUT)Internal(1)0 0 XReserved 0 1 XSmall EEPROM (256 Byte) 1 0 0Large EEPROM (1 KByte) 1 1 0SHI 1 0 1UART 1 1 1Notes:(1) Uses pre-defined parameters; please refer to Appendix section for more detailsIf one of the EEPROM modes is selected, use the strap option pins shown in the table below to select which section of the EEPROM to load parameters from.Table 3: Strap Option Pins for EEPROMStarting AddressSegment Small (256 Byte) Large (1 KByte)Pin 10(PCM_OUT)Pin 13(UART_TX)The below table shows the pre-defined settings of internal mode operation. The strap pin settings are for default internal mode profiles.Table 4: Strap Pin settings for default internal modeProfile Pin 13 Pin 211-mic (uni), analog 0 01-mic (omni), analog 0 1Uni-omni (default), analog 1 0Omni-omni, analog 1 13.3 Power On/Off TimingThe following timing chart shows the power on sequence of 3 power pins, namely VDD_D, VDD_S and V10. The power off sequence is just the reverse order of power on.Figure 15: Timing Chart of Power On/Off Sequence3.4 System ClockA user can apply a clock source (crystal or oscillator) of either 4.096MHz or 13MHz to pin 27 (XTAL_IN). Acrystal applied to pins 27(XTAL_IN) and 28(XTAL_OUT) will also work. For more information on crystal specifications, please refer to the Appendix section.3.5 Accessing FM11-GE-300 Through EEPROM, UART, SHIUsers can read or write to registers in FM11-GE-300 (ex: to update parameters) through one of 3 interfaces: EEPROM, UART, or SHI. To access the registers in FM11-GE-300, designers must use a pre-defined command entry pattern. The UART or SHI interfaces are used if applications require control through an external host (SHI is off after DSP is in normal operation mode).Table 5: Command Entry Data Pattern Command ByteAddress Byte(s)Data Byte(s)The table below shows the available command entries and the associated number of bytes required for each entry. Table 6: Command Entries Command Entry Available for Interface Command ByteNo. of Address Bytes No. of Data Bytes Total No. of Bytes Mem_write UART, SHI, EEPROM 3B 2 2 5 Mem_readUART, SHI 37 2 0 3 Short_reg_write UART 68 1 1 3 Long_reg_write UART6A 1 2 4 reg_readUART, SHI60123.5.1 Accessing Through EEPROMUsers can have a maximum of 4 different sets of parameters in the same EEPROM. Every time a reset is initiated, the user can select which set of parameters to access. For a large size EEPROM (1 KByte), the absolute maximum number of bytes is 256 in each section.When the EEPROM mode is selected to be the source to initialize the parameters after reset, the EEPROM access is set to burst mode up to 256 bytes. FM11-GE-300 will retrieve data continuously in burst mode until the end of transfer byte, “F0,” is detected. Then FM11-GE-300 will enter the normal operation mode.3.5.2 Examples of Accessing Through EEPROMThe table below provides a few examples of how to update parameters in FM11-GE-300 through the EEPROM interface. For more details, please refer to the FM11GE-300 Parameter Tuning Guide .Table 7: Examples of Accessing Through EEPROM3.5.3 Accessing Through UARTUART serves as an interface between the FM11-GE-300 and a host PC or controller which can send commands to program the chip’s parameters. UART is an asynchronous bi-directional serial interface; the protocol is determined by a start bit, number of character bits, a parity bit and a stop bit. The transfer speed is determined by the baud rate which can be programmed internally. There is no clock signal between the transmitter and receiver.There are 5 different types of command entries for the FM11-GE-300 UART interface. A sync word, “FCF3,” is required before each command entry. Since the speed of the UART interface is much slower than the internal clock of FM11-GE-300, it is safe to continue a write transfer without checking the status of the data transfer.There are two access modes: mem_read and reg_read. Mem_read is used to read the memory contents and save them in registers 25 and 26 of FM11-GE-300. Reg_read then transfers the register contents to the UART interface output pin TXD. The micro-controller host will then receive the register contents by monitoring the TXD pin.No partial command entry is allowed. A partial command entry may cause system mal-function.3.5.4 Examples of Accessing Through UARTThe table below provides a few examples of how to update parameters in FM11-GE-300 through the UART interface. For more details, please refer to the FM11GE-300 Parameter Tuning Guide.Table 8: Examples of Accessing Through UARTa. mem_write transferFC F3 3B 1E 34 00 55 -- write memory 1E34 with 0055b. mem_readFC F3 37 1E 34 -- read memory contents of 1E34c. long_reg_writeFC F3 6A 2A 00 30 -- software reset of DSPd. reg_readFC F3 60 25 -- read register 25e. read out contents of memory location 1E34FC F3 37 1E 34FC F3 60 26 -- MSB of 1E34 will transmit through TXDFC F3 60 25 -- LSB of 1E34 will transmit through TXD3.6 Miscellaneous FunctionsSpeaker Volume Control (Pins 25, 26)The speaker volume of FM11-GE-300 can be controlled by the Vol- (pin 25) and Vol+ (pin 26) pins. These input signals are level triggered and active high. The DSP will increase/decrease the volume by one step once it senses a high signal on either pin (minimum length of active state is 80ms). If either pin is held high continuously, the DSP will increase/decrease the volume by 4 steps in 1 second. The step-size and maximum volume is programmable (see FM11GE-300 Parameter Tuning Guide).If these pins are not used, they must be pulled low using a weak 100K resistor.Microphone Mute (Pins 21, 24)A user can mute the microphone input of FM11-GE-300 by using mute_in (pin 24). This signal is level triggered and active high. The default setting after reset is the “no mute” mode, and will toggle between “no mute” and “mute” every time the signal is active (minimum length of the active state is 80ms). Please note that the mute function is not available in SHI mode, as pin 24 serves as the SDA pin of the SHI bus. The mute_out (pin 21) signal is active high and is a status indication of the “mute” mode. It will output a “high” if in “mute” mode.If this pin is not used, it must be pulled low using a weak 100 kΩ resistor.Earpiece and Speaker Mode (Pin 23)This input signal is edge triggered. On the falling edge, FM11-GE-300 will switch to the “earpiece” mode, which has a lower internal power amplifier gain. On the rising edge, FM11-GE-300 will switch to the “speaker” mode, which has the standard internal power amplifier gain. If the built-in power amplifier is not used, the speaker PGA will be changed accordingly. Please note that this feature is not available in SHI mode, as pin 23 serves as the SCL pin of the SHI bus.If this pin is not used, it must be pulled high with a weak 100 kΩ resistor to be in speakerphone mode.4. Electrical & Timing Specification4.1 Absolute Maximum RatingsTable 9: Absolute Maximum RatingsParameter Symbol Condition Rating Unit Power Supply Voltage VDD_S - 2.0 V Digital Input Voltage VIN - 3.6 V Digital Output Voltage VOUT - 3.6 V Storage Temperature T stg- -40 to 150 0C 4.2 Recommended Operating ConditionsTable 10: Recommended Operating ConditionsParameter Symbol Condition Min Typ Max Unit ESD Protection HBM 2 kV Power SupplyVoltage(1)VDD_S - 1.62 1.8 2.0 VI/O Supply Voltage VDD_D 1.62 1.8 or3.33.6 VOperatingTemperatureT amb- -5 25 50 °CInput High Voltage V IH VDD_D-0.3VDD_D VInput LowVoltageV IL0 0.3 VMaster Clock Frequency f mck XTAL_IN 4.096,13MHzMaster ClockDuty RatioD mck XTAL_IN 40 50 60 %Bit Clock Frequency f bck BCLK (MasterMode)128 256 1,024 kHzBit Clock Frequency f bck BCLK (SlaveMode)128 256 4,096 kHzBit Clock DutyCycleD bck BCLK 45 50 55 %Sync SignalFrequencyf sync FSYNC 8 kHz Notes: The power ripple (AC element) has to be limited within 100mV4.3 DC CharacteristicsTable 11: DC CharacteristicsParameter Symbol Condition Min Typ Max Unit Digital Supplyfor CoreV10 1.62 1.8 2.0 VPower Supply Current I SU Operating, Analog +Digital- 17 19 mAPower Down I PD PWD_ is low - 40* - µAºI PD is only for V10. VDD_D and VDD_S leakage current may be up to additional 20µA.4.4 AC CharacteristicsTable 12: AC CharacteristicsAC Characteristics (room temperature, gain set to 0dB)Parameter Condition Min Typ Max UnitMic0 & Mic1 Input Range (differential) Reference as 0dB fullscale2.4 VppLine_in Input Range (differential) Reference as 0dB fullscale2.4 VppSpk_out Full Scale Output (differential) Reference as 0dB fullscale2.2 2.4 2.6 VppLine_out Full Scale Output @ 0dB PGA gain; 1.1 1.2 1.3 Vpp (single-ended) @ 2dB PGA gain 1.5 Vpp SNR for Line_in (digital oranalog) to Spk_out Path77 dBSNR for Mic0 & Mic1 to DigitalLine_out Path80 dBSNR for Mic0 & Mic1 toAnalog Line_out Path72 dB CODEC Sampling Frequency 8 KHzInput Impedance for Mic/Line_in Reference as 0dB fullscale27.5 kΩLoad impedance for Line_out /Spk_out600 ΩTable 13: ADC(Mic0/Mic1/Line_in) PGA GainParameter Condition Min Typ Max Unit Gain Range -2 - 26 dB Step Size Range: -2dB to 0dB - 1 - dB Step Size Range: 0dB to 26dB - 2 - dB Step Size Error Range: -2dB to 0dB -0.5 0.5 dB Step Size Error Range: 0dB to 26dB -1 - 1 dBTable 14: DAC(Line_out, Speaker Out) PGA GainParameter Condition Min Typ Max Unit Gain Range -29 - 2 dB Step Size Range: -29dB to 2dB - 1 - dB Step Size Error Range: -29dB to 2dB -0.5 - 0.5 dB 4.5 DSP Performance DetailsTable 15: DSP Performance DetailsParameter Condition Min Typ Max Unit Acoustic Echo Cancellation 2-mic mode - - 60 dB Stationary Noise Suppression For Mic0, Mic1 12 dBNon-stationary Noise Suppression For Mic0 & Mic1 Beam-forming20 dBBeam-forming angle U+O SAM mode* 120 º Side Tone Cancellation 25 - 35 dB Acoustic Echo Tail Length 64 - 100 ms Echo Convergence 2-mic mode 30 msNon-stationary Noise Convergence 2-mic beam formingoperating mode200 msStationary Noise Convergence 1-mic mode 1.5 s4.6 Timing CharacteristicsTable 16: Timing CharacteristicsParameter Symbol Condition Min. Typ. Max. Unit Power-down to power-up time t pdu100 - - us Set parameter timing afterresett param 4 - - msData delay after parametersettingt data- 70 - msSpeaker out delay afterparameter settingt spk- 75 - ms Mic to Line_out delay t mlo 2 mic mode - 54 - ms Bit clock frequency f bclk Output Mode 128 256 1,024 kHz FSYNC Setup Time t fs10 - - ns FSYNC Hold Time t fh10 - - ns Input Setup Time t ds10 - - ns Input Hold Time t dh10 - - ns Digital Output Delay Time t dd Output Mode - - 30 ns FSYNC Output Delay Time t fd Output Mode - - 30 nsFigure 16: Power-down to Speaker-out TimingFigure 17: Digital Input Timing (No Clock Delay)Figure 18: Digital Input Timing (One Clock Delay)Figure 19: Digital Output Timing (No Clock Delay)Figure 20: Digital Output Timing (One Clock Delay)5. Pin DefinitionTable 17: Pin Number sorted Description Pin # Pin Name I/OType Pin Description PowerDownStatus1 NC NC No connect NC2 NC NC No connect NC3 SPK_OUT_N O Speaker output (-) Tri-State4 NC NC No connect NC5 NC NC No connect NC6 NC NC No connect NC7 VSS_D GND Digital ground GND8 BCLK I/O BCLK signal for Serial Port I9 FSYNC I/O Frame sync signal for Serial Port I10 PCM_OUT I/O During power up, used as strapoption (section 7.2); after powerup, transmits voice data to SerialPortI11 PCM_IN I Receive voice data from SerialPortI12 UART_RX I Serial commands from UART port I13 UART_TX I/O During power up, used as strapoption (section 7.2); after powerup, transmits serial commands toUART portI14 ANA_COM I For analog communications mode,which will bypass DSP (1)I15 SDA_EE I/O Serial data access for EEPROM I16 SCL _EE I/O Serial clock for EEPROM17 GPIO7 I/O Mode select strap option (section7.2)In18 VSS_D GND Digital ground GND19 VDD_D VDD Digital power (2)VDD20 STRAP0 I/O During power up, used as strapoption (section 7.2); not usedduring normal operationI21 MUTE_OUT I/O During power up, used as strapoption (section 7.2); after powerup, serves as output LED toindicate microphone “mute” statusI22 VAD_LED I/O Must pull low using weak 100Kresistor to select XTAL_IN as PLLclock source; after power up,serves as LED output to indicateinternal status for VAD (VoiceActivity Detection) tuningI23 SCL I/O Serial clock for SHI interface, ifselected; if SHI is not selected,serves as input pin to select“earpiece” mode where the speakeroutput gain will be reduced tosupport earpiece function (3) ; if notused, pull high using weak 100 kΩresistor to be in speaker-phoneI。

GE300控制器说明书

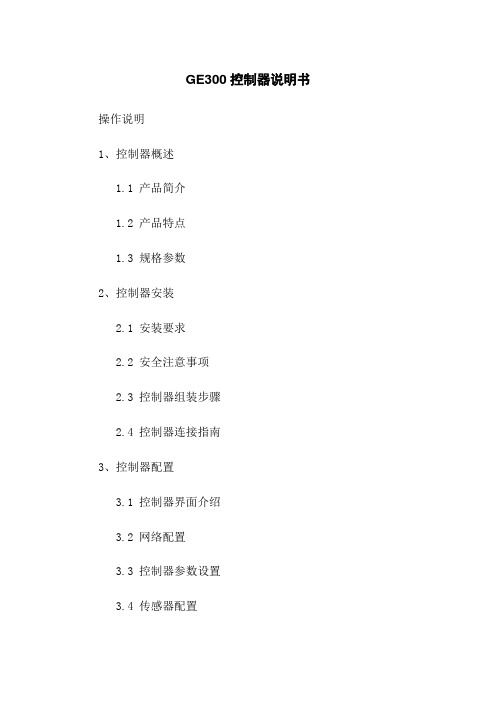

GE300控制器说明书操作说明1、控制器概述1.1 产品简介1.2 产品特点1.3 规格参数2、控制器安装2.1 安装要求2.2 安全注意事项2.3 控制器组装步骤2.4 控制器连接指南3、控制器配置3.1 控制器界面介绍3.2 网络配置3.3 控制器参数设置3.4 传感器配置3.5 输出设备配置3.6 控制策略设置3.7 告警设置4、控制器操作4.1 控制器启动4.2 控制器关闭4.3 控制器状态监控4.4 控制器运行日志4.5 控制器数据导出与导入5、故障诊断与维修5.1 常见故障排除方法5.2 维修流程5.3 定期维护6、控制器升级6.1 控制器固件升级步骤6.2 控制器软件升级步骤7、使用控制器的注意事项7.1 法律法规遵守7.2 安全警示7.3 使用环境要求8、附件8.1 附件1、连接线路示意图8.2 附件2、控制器参数表格8.3 :::法律名词及注释:1、控制器:指GE300控制器,本文档所述控制器的特定型号。

2、参数设置:用户根据实际需求对控制器进行的个性化配置。

3、传感器:测量、监测系统所使用的设备,用于采集数据。

4、输出设备:控制器通过输出接口对外部设备进行控制的设备。

5、控制策略:控制器根据预先设定的策略控制输出设备的方式。

6、告警设置:用户设定的控制器异常情况下的警示方式。

7、固件升级:通过更新控制器固件使其具备新功能或解决已知问题的操作。

本文档涉及附件:附件1、连接线路示意图附件2、控制器参数表格:::。

GE300控制器说明书-推荐下载

目录一、概述‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥11.1说明‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥21.2控制器特点‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥31.3技术指标‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥4二、型号、安装和接线2.1选型‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥6 2.2安装尺寸及说明‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥7 2.3接线端子说明‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥8 2.4接线图‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥92.5与常用变频器接线表‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥9三、操作与功能参数‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥103.1面板显示操作说明‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥113.2功能参数表及说明‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥12四、显示项目及故障说明‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥13五、附录5.1标准两泵循环软起动加泄压阀方式接线图5.2标准三泵循环软起动方式接线图5.3标准四泵循环软起动方式接线图一、概述1.1说明本手册包含GE300系列微机控制器的安装、操作和配置信息。

在使用GE300系列微机给水控制器之前,请您仔细阅读本使用说明书,并请妥善保存。

由于我们始终致力于产品的不断升级和完善,因此,本公司提供的资料如有变动,恕不另行通知。

1.2控制器特点本产品是应广大用户的要求最新推出的高性能微机给水控制器。

采用高品质元件、材料及融合最新的控制技术而成;和变频器组合在一起,即可构成民用、工业、消防等行业适用的微机变频调速恒压供水系统。

●采用模糊控制原理,自动优化时无需调整控制器参数,响应快、精度高、泵切换时管网冲击小。

●具备自动定时换泵,定时开关机设置,提高水泵平均使用寿命。

美国GE保护说明书

频率变化率保护

G60发电机保护系统包括4个频率变化率(df/dt) 元件,这些元件针对系统的扰动情况通过甩负 荷对系统提供保护,而且,这些元件还可以提 供解列保护。这些元件通过对电压、电流和频率 的检测来监视频率在各个方向上的变化率。

RTD热保护

G60发电机保护系统具有过温度保护功能,这 是普通发电机保护继电器不具备的特性。G60 发电机保护系统能够接收来自任何类型的外部 电阻温度探测器(RTD)的信号并将其转换为 所需要的数字格式。基于RTD过热的动作,如 跳闸或告警,是与FlexElementTM特性配合完成 的。FlexElementTM操作数与FlexElementTM配合 使用可进一步实现联锁或直接操作接点输出。

发电机保护系统交流发电机综合保护测量电流电压功率电能频率录波每个周波64次采样最多64次记录事件记录1024个带时间标签的事件05ms数字输入扫描数据记录用户可选择采样速率最多16个通道用户可编程故障报告由汽轮机燃气轮机或水轮机驱动的任何容量的交流发电机独立应用或作为自动化变电站控制系统中的元件主要优点用途特性保护和控制通讯监视与测量就地访问通过前面板显示屏和小键盘就地pc访问通过rs232接口用户可编程就地显示屏用户可编程led和按钮使用flexlogictmflexcurvestm和flexelementstm软件实现用户化保护和控制功能继电器配备enervistalaunchpad软件简化继电器的配置过程和编程过程多种语言选择法文中文俄文选择用户接口与编程发电机全功能保护满足任何应用先进的自动化功能提供双电源选择提高保护和控制可靠性完全支持多断路器配置方案如环形母线和1个半断路器所具有的特性能够对外部故障提供可靠的保护动作高效的信息访问多种通讯选择及多种规约选择设计紧凑减少安装空间多功能设备集成保护和控制功能可编程按钮状态指示led和通讯接口定子差动100定子接地差动后备距离系统振荡闭锁及跳闸同期检查限制性接地故障裂相保护失磁过激磁逆功率和低正向功率发电机不平衡组网选择以太网光纤冗余选择rs485rs422g703c3794多种规约iec61850dnp30modbusrtumodbustcpipiec608705104以太网全球数据egd直接iour继电器之间的二进制数据交换应用高速通讯减少配线和安装成本继电器间输入和输出交换实现继电器间交互应用灵活性多io选择可编程逻辑flexlogictm模块化设计可满足用户特殊的具有个性化的应用要求缩短系统事件分析时间并实现成本降低事件顺序报告录波数据记录irigb时间同步内置iec61850规约无需外部规约转换器17830710a9cdr50g87g51g64tn51p51n4667p67n67268782459p27p592测量3250274059n81u81o27tn59aux27auxg60发电机保护系统87s50n81r50p21p2521p242527p27tn27x32404650g50n50p50sp502751gansi设备号及功能保护与控制g60发电机保护系统是一种发电机综合保护系统它可以满足发电机保护应用的任何要求

GE 数据中心关键电源静态转换开关说明书

MTBFtotal = 126,582 hours

MTBFA = 250K + 250K - 1 / (1/250K + 1/250K) MTBFA = 375,000 hours

MTBFAB = 1/(1/375,000 + 1/300,000)

Redundant Fail-Safe Operator Panel • Password Log-In • One-Line color change based on source select • USB Port for downloading stored event data • 16MB Memory - Flash SD card for additional memory

with Static Transfer Switches

….thus providing end-to-end customer solutions

2

Increasing Redundant UPS Reliability using STS devices

Block Diagrams

2-Module Parallel-Redundant UPS with Centralized Static Bypass

continues for 10sec to capture alarms and waveforms

11

Zenith STS-3 / MDU Combo Unit

Three Phase Static Transfer Switch with Output PDU

CORE RATINGS

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

标准接线图

2.2

FWD CM1

与常用变频器接线表

FUJI 变频器端子 FRD CM 三肯变频器端子 FR DCM12 西门子变频器端子 5 9

微机控制器端子

CM2 D/A

GND VS

ACM VRF

4 3

一、 操作与功能参数 3.1 操作各按键名称和功能

3.1

面板操作说明

功能参数

功能码

代码 名称 参数值

说明书

一、概述 1.1 说明

本手册包含 GE300系列微机控制器的安装、操作和配置信息。

在使用 GE300系列微机给水控制器之前,请您仔细阅读本使用说明书,并请妥 善保存。 由于我们始终致力于产品的不断升级和完善,因此,本公司提供的资料如有变 动,恕不另行通知。

1.2 控制器特点 本产品是应广大用户的要求最新推出的高性能微机给水控制器。采用高品 质元件、材料及融合最新的控制技术而成;和变频器组合在一起,即可构成民用、 工业、消防等行业适用的微机变频调速恒压供水系统。 l l l l l l l l l l l l l 采用模糊控制原理,自动优化时无需调整控制器参数,响应快、精度高、泵切 换时管网冲击小。 具备自动定时换泵,定时开关机设置,提高水泵平均使用寿命。 系统提供休眠功能节能工作方式。 在压力不足需要加泵时,变频泵将自动降速,减少切换冲击。 增加锅炉补水,泄压阀压力区间控制选择。 变频器故障时,可选择自动转入工频运行。 一用一备、一用一补、两泵、三泵、四泵循环软起等功能,能满足不同用户的 需求。 简化键盘菜单式设定和调整工作状态。 参数在线编程,大大方便使用。 采用开关电源供电设计,具有宽电压适用范围,抗干扰能力强。 器件采用先进的 SMT(表面贴装)工艺,可靠性高。 保护及报警功能齐全,具有变频器故障,远传压力表断线、短路 故障、欠压超时、低水位报警指示。 完善的密码功能。

四、显示项目及故障说明

五、 附录

2 3 4 5 6 7 8 9

R1 R2 R3 R4 R5 R6 R7

备注:GE300BX 型控制器为泄压控制端子

R8

M4号工频泵控制端子。直接驱动接触器线圈

11 12 13 14 15 16 17 18 19 20 21 22 23 24 2.2

L N GND IN

控制器 AC220V 电源,接火线 控制器 AC220V 电源,接零线 模拟输入信号公共端 模拟输入信号输入端,接远传压力表中心滑动端; 外接4-20mA 电流信号时,需在 GND 与 IN 端子间跨接150Ω电阻

用一备使用, F00参数值作为自动定时换 泵时间 GE300C(D) 单泵工作 1:1,2泵 2:1,3泵 3:1,4泵 4:2,3 泵 5:2,4泵 6:3,4泵 7:1,2,3泵 8:1,2,4 F04 第一工作泵 F05 换泵定时器 F06 传感器校零 F07 F08 F09 F10 传感器类型 泵 9:1,3,4泵, 10:2,3,4泵 11:1,2,3,4泵 上电第一工作泵 定时换泵定时器已工作时间(查询) 填入压力表零压力时控制器实际压力显示值 0-2.5V 1:4-20mA 0 0 1

输入电压范围(AC) 额定频率 额定功耗 CT1-CT4与 CM2 FWD BX 与 CM1 R1-R8继电器输出

模拟端 子

环境条 件

D/A 与 CM2 IN 与 GND +2.5V 环境温度 环境湿度

二、型号、安装和接线 2.1 型号 l l l l 两台泵循环软起型: GE300B 三台泵循环软起型: GE300C 四台泵循环软起型: GE300D 两台泵循环软起型(带泄压功能) GE300BX : 备注:型号中含 T,表示带时控功能。 安装尺寸及说明 外形尺寸: 长×宽×深=152×75×85 最大开孔尺寸: 长×宽=152×75

+V COM1 D/A COM2 FWD FRS CT1 CT2 CT3 CT4

模拟供电电源端子,2.5V/20mA 模拟输出信号公共端及开关量控制信号公共端 模拟输出0-5V 或0-10V,用于输出变频器频率给定信号 光耦输出控制信号公共端 变频器运行信号控制端子 变频器自由停车信号控制端子 变频故障报警端子,当 CT1与 COM2短接时,显示 E0,系统运行停止 低水位控制端子,当 CT2与 COM2短接时, LD 指示灯亮 双压控制端子,当 CT3与 COM2短接时,设定压力显示 F02的值 消防压力控制端子,当 CT4与 COM2短接时,设定压力显示 F02的值

0-999 0-9.99 0-250

120 0.15

F24

休眠前压力增 量

用户设定压力加增量 F24作为当前的设定压 力,当实际压力到达此压力时即进入休眠状 态,如实际压力到达不了此设定值则延时 3 分钟自动进入休眠状态。 0-0.50 0.03

F25

减泵频率

有工频泵工作时,当实际频率低于减泵频

0-50.0

概述

设定恒压给水压力值

取值范围 出厂值

0-252 0-9.99 48 0.30 0.20

F00 自动定时换泵时间值为0时此功能无效 设 F01 设定压力1 F02 设定压力2

双压运行(CT3与 CM2短接),消防压力(CT4于 0-9.99 CM2短接) GE300B(X)

F03 泵工作方式

:单泵工作 1:一用一补。如将 F12设为100,可作一

2.2 l l

本控制器采用直插式安装方法,控制器带有回钩,可直接卡在箱体开孔处。

2.3

端子 标号

接线端子

端子名 称 端子功能说明 M1号变频泵控制端子。直接驱动接触器线圈 M1号工频泵控制端子。直接驱动接触器线圈 M2号变频泵控制端子。直接驱动接触器线圈 M2号工频泵控制端子。直接驱动接触器线圈 M3号变频泵控制端子。直接驱动接触器线圈 M3号工频泵控制端子。直接驱动接触器线圈 M4号变频泵控制端子。直接驱动接触器线圈

传感器量程可以任意设定 例: 0.6Mpa 设0.6;1Mpa 设1.00 0-9.99 泵倒换死区时 由变频泵停车倒换至工频泵启动的时间 间 输出控制电压 0-5V 1:0-10V 3 1

多台泵工作时,当变频泵运行频率升至50Hz 时, 经过 F11时间,实际压力仍小于设定压力, F11 欠压加泵时间 变频泵倒为工频运行,下一台变频泵投入 0-250 运行。欠压加泵时间根据系统实际情况设 定 在设定压力的正负偏差范围内,不进行加减泵, F12 欠压加泵偏差 防止水泵频繁起停。 当值设为100时欠压不 0-100 加泵,则按定 F00设定的时间换泵 F13 调节速度 大则调节快,小则调节慢 防止压力表和传感器失效,压力在此项值以下2 F14 欠压报警阀值 分钟后产生 E1报警停机。设为0则此项功 能无效 F15 输入信号滤波 F16 变频泵启动频率 系统震动大时,加大此值 填入一数值,可以快速启动水泵,降速时到达此 值变频器输出频率为零 3 20 0 3 0 3

26.0

率,经过减泵延时 F26则减掉一工频泵 F26 减泵延时 功能见 F25项 当实际压力高 F01+F27值时,并延时 F29时 间则泄压阀打开,当压力小于 F01+0.02值 时,则泄压阀关闭, 0-250 5

泄 压阀 压力

F27

控 制浮 动上 限

工厂设置

0-9.99

0.35

F28

F29

泄 压阀 动作 延时 0-60 5

F17

超压设定值

实际压力≥F01+F17时,频率迅速下降,如有 工频泵运行,则延时3秒后减一工频泵 0:不可以通过操作加﹑减键直接设定压力;

0-0.5

0.05

F18

设定压力方式 1:可以通过操作加﹑减键直接设定压力 只有在上电正计时时,进入参数设置状态

0-1

0

F19

数据初始化

后,此项设为1则数据初始化,在运行时此 项不能修改 实际压力大于“ 设定压力”-0.02时,频率小于

1.3

技术指标

项目

内容 85V~265V 50/60Hz 5W 光耦高阻输入,严禁接入电源信号 光耦输出,有正负极 3A/250V(AC)或5A/30V(DC) 输出0-5V 0-10V 输入0-2.5V 4-20mA 30mA -10℃~40℃ 90%以下(无水珠凝结)

电源

(L N) 数字端 子

0-1

0

F20

休眠频率

F20时, 这种状态保持 F21时间, 则运转信号 断开,当 F20为0时此功能无效

0-50.0

0

F21 F22 F23

休眠延时时间 唤醒压力 唤醒延时

功能见 F20项 当压力小于此值时,经过 F23延时后运转信 号闭合,重新启动 功能见 F22项 当休眠条件满足时,为了延长停机时间,将