TSOP31336中文资料

ZSPM4013AA1W33中文资料(ZMDI)中文数据手册「EasyDatasheet - 矽搜」

该ZSPM4013采用电流模式反馈 正常调节PWM模式.当稳压 被禁用(EN为低电平)时,设备将小于 10uA静态电流.

该ZSPM4013集成多种防护护电路,包括: 输入欠压锁定,输出电压软启动,限流和热关断.

该ZSPM4013包括通过PG(电源良好)开漏输出 监管报告接口等组成系统.

特征

· 固定输出电压:1.5V,1.8V,2.5V,3.3V, 并用5V +/- 2%输出容差

· ZSPM1000:5A单相,单轨,真 数字PWM控制器(24引脚4×4 QFN)

提供支持

· 评估套件 · 数据表

物理特性

· 结工作温度-40°C至125°C · 包装在一个16针QFN(3×3)

ZSPM4013应用电路

可调输出

ZSPM4013

固定输出 VCC

VOUT

ZSPM4013

EN

PG

芯片中文手册,看全文,戳

2 典型性能特性................................................................................................................... 9 3 电路说明......................................................................................................................................... 12

5 引脚配置和包装......................................................................................................................... 15 5.1.标记图& Pin-out......................................................................................................................... 16 5.2.引脚说明为16引脚3x3 QFN封装....................................................................................................... 17 5.3.详细引脚说明............................................................................................................................. 17 5.3.1.未经稳压输入,VCC(引脚#2,3)....................................... .................................................. ........... 17 5.3.2.引导控制,BST(引脚#10) ......................................................................................................... 17 5.3.3.检测反馈,FB(引脚#5) ............................................................................................................... 17 5.3.4.开关量输出,VSW(引脚#12,13)....................................... .................................................. ......... 18 5.3.5.接地,GND(引脚#4) .......................................................................................................................... 18 5.3.6.电源接地,防护护接地(引脚#14,15)....................................... .................................................. .......... 18 5.3.7.启用,高电压,EN(管脚#9) ........................................................................................................ 18 5.3.8. PG输出,PG(引脚#8) ....................................................................................................................... 18

ADSP-21363资料

a Preliminary Technical DataSHARC and the SHARC logo are registered trademarks of Analog Devices, Inc.SHARC® ProcessorADSP-21363Rev. PrAInformation furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for anyinfringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective companies.One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106 U.S.A. Tel: Fax:781.326.8703© 2004 Analog Devices, Inc. All rights reserved.SUMMARYHigh performance 32-bit/40-bit floating point processor optimized for professional audio processingAt 333 MHz/2 GFLOPs, with unique audio centric peripherals such as the Digital Audio Interface the ADSP-21363 SHARC processor is ideal for applications that require industry leading equalization, reverberation and other effects processingSingle-Instruction Multiple-Data (SIMD) computational architectureTwo 32-bit IEEE floating-point/32-bit fixed-point/40-bit extended precision floating-point computational units, each with a multiplier, ALU, shifter, and register file On-chip memory—3M bit of on-chip SRAM and a dedicated 4M bit of on-chip mask-programmable ROMCode compatible with all other members of the SHARC family The ADSP-21363 is available with a 333 MHz core instruction rate. For complete ordering information, see Ordering Guide on Page44Figure 1.Functional Block Diagram – Processor CoreADSP-21363Preliminary Technical DataKEY FEATURES – PROCESSOR COREAt 333 MHz (3.0 ns) core instruction rate, the ADSP-21363 performs 2 GFLOPS/666 MMACS3M bit on-chip single-ported SRAM (1M Bit in blocks 0 and 1, and 0.50M Bit in blocks 2 and 3) for simultaneous access by the core processor and DMA4M bit on-chip mask-programmable ROM (2M bit in block 0 and 2M bit in block 1)Dual Data Address Generators (DAGs) with modulo and bit-reverse addressingZero-overhead looping with single-cycle loop setup, provid-ing efficient program sequencingSingle Instruction Multiple Data (SIMD) architecture provides:Two computational processing elementsConcurrent executionCode compatibility with other SHARC family members atthe assembly levelParallelism in busses and computational units allows sin-gle cycle executions (with or without SIMD) of a multiply operation, an ALU operation, a dual memory read orwrite, and an instruction fetchTransfers between memory and core at a sustained 5.4G bytes/s bandwidth at 333 MHz core instruction rate INPUT/OUTPUT FEATURESDMA Controller supports:25 DMA channels for transfers between ADSP-21363 internal memory and a variety of peripherals32-bit DMA transfers at core clock speed, in parallel with full-speed processor executionAsynchronous parallel port provides access to asynchronous external memory16 multiplexed address/data lines support 24-bit address external address range with 8-bit data or 16-bit address external address range with 16-bit data55M byte per sec transfer rateExternal memory access in a dedicated DMA channel8- to 32- bit and 16- to 32-bit packing options Programmable data cycle duration options: 2 to 31 CCLK Digital audio interface (DAI) includes six serial ports, two Pre-cision Clock Generators, an Input Data Port, three timers, and a Signal routing unitSix dual data line serial ports that operate at up to 50M bit/s on each data line—each has a clock, frame sync and two data lines that can be configured as either a receiver or transmitter pairLeft-justified Sample Pair and I2S Support, programmable direction for up to 24 simultaneous receive or transmit channels using two I2S compatible stereo devices per serial portTDM support for telecommunications interfaces including 128 TDM channel support for newer telephony interfaces such as H.100/H.110Up to 12 TDM stream support, each with 128 channels per frameCompanding selection on a per channel basis in TDM mode Input data port provides an additional input path to the SHARC core, configurable as eight channels of serial data or seven channels of serial data and a single channel of up to 20-bit wide parallel dataSignal routing unit provides configurable and flexible con-nections between all DAI components–six serial ports, two precision clock generators, an input data port with a data acquisition port, one SPI port, three timers, 10 interrupts, six flag inputs, six flag outputs, and 20 SRU I/O pins(DAI_P20-1)Two Serial Peripheral Interfaces (SPI): primary on dedicated pins, secondary on DAI pins provide:Master or slave serial boot through primary SPIFull-duplex operationMaster-Slave mode multi-master supportOpen drain outputsProgrammable baud rates, clock polarities and phases3 Muxed Flag/IRQ lines1 Muxed Flag/Timer expired linePulse Width Modulation provides:16 PWM outputs configured as four groups of four outputs Supports center-aligned or edge-aligned PWM waveforms Can generate complementary signals on two outputs in paired mode or independent signals in non paired mode PLL has a wide variety of software and hardware multi-plier/divider ratiosDual voltage: 3.3 V I/O, 1.2 V coreAvailable in 136-ball Mini-BGA and 144-lead INT–HS LQFP Packages (see Ordering Guide on Page44)Rev. PrA|Page 2 of 44|September 2004ADSP-21363Preliminary Technical DataRev. PrA |Page 3 of 44|September 2004GENERAL DESCRIPTIONThe ADSP-21363 SHARC processor is a member of the SIMD SHARC family of DSPs that feature Analog Devices' Super Har-vard Architecture. The ADSP-21363 is source code compatible with the ADSP-2126x, and ADSP-2116x DSPs as well as with first generation ADSP-2106x SHARC processors in SISD (Sin-gle-Instruction, Single-Data) mode. The ADSP-21363 is a 32-bit/40-bit floating point processor optimized for professional audio applications with a large on-chip SRAM, multiple internal buses to eliminate I/O bottlenecks, and an innovative Digital Audio Interface (DAI).As shown in the functional block diagram on Page 1, theADSP-21363 uses two computational units to deliver a signifi-cant performance increase over previous SHARC processors on a range of signal processing algorithms. Fabricated in a state-of-the-art, high speed, CMOS process, the ADSP-21363 processor achieves an instruction cycle time of 3.0 ns at 333 MHz. With its SIMD computational hardware, the ADSP-21363 can perform 2 GFLOPS running at 333 MHz.Table 1 shows performance benchmarks for the ADSP-21363.The ADSP-21363 continues SHARC’s industry leading stan-dards of integration for DSPs, combining a high performance 32-bit DSP core with integrated, on-chip system features. The block diagram of the ADSP-21363 on Page 1, illustrates the following architectural features:•Two processing elements, each of which comprises an ALU, Multiplier, Shifter and Data Register File •Data Address Generators (DAG1, DAG2)•Program sequencer with instruction cache•PM and DM buses capable of supporting four 32-bit data transfers between memory and the core at every core pro-cessor cycle•Three Programmable Interval Timers with PWM Genera-tion, PWM Capture/Pulse width Measurement, and External Event Counter Capabilities •On-ChipSRAM(3Mbit)•On-Chip mask-programmable ROM (4M bit)•8- or 16-bit Parallel port that supports interfaces to off-chipmemory peripherals •JTAG test access portThe block diagram of the ADSP-21363 on Page 6, illustrates the following architectural features:•DMA controller •Six full duplex serial ports•Two SPI-compatible interface ports—primary on dedi-cated pins, secondary on DAI pins•Digital Audio Interface that includes two precision clock generators (PCG), an input data port (IDP), six serial ports, eight serial interfaces, a 20-bit parallel input port, 10 inter-rupts, six flag outputs, six flag inputs, three timers, and a flexible signal routing unit (SRU) and an SPI port Figure 2 on Page 4 shows one sample configuration of a SPORT using the precision clock generators to interface with an I 2S ADC and an I 2S DAC with a much lower jitter clock than the serial port would generate itself. Many other SRU configura-tions are possible.ADSP-21363 FAMILY CORE ARCHITECTUREThe ADSP-21363 is code compatible at the assembly level with the ADSP-2126x, ADSP-21160 and ADSP-21161, and with the first generation ADSP-2106x SHARC processors. The ADSP-21363 shares architectural features with the ADSP-2126x and ADSP-2116x SIMD SHARC processors, as detailed in the fol-lowing sections.SIMD Computational EngineThe ADSP-21363 contains two computational processing ele-ments that operate as a Single-Instruction Multiple-Data(SIMD) engine. The processing elements are referred to as PEX and PEY and each contains an ALU, multiplier, shifter and reg-ister file. PEX is always active, and PEY may be enabled bysetting the PEYEN mode bit in the MODE1 register. When this mode is enabled, the same instruction is executed in both pro-cessing elements, but each processing element operates on different data. This architecture is efficient at executing math intensive signal processing algorithms.Entering SIMD mode also has an effect on the way data is trans-ferred between memory and the processing elements. When in SIMD mode, twice the data bandwidth is required to sustain computational operation in the processing elements. Because of this requirement, entering SIMD mode also doubles the band-width between memory and the processing elements. When using the DAGs to transfer data in SIMD mode, two data values are transferred with each access of memory or the register file.Independent, Parallel Computation UnitsWithin each processing element is a set of computational units. The computational units consist of an arithmetic/logic unit (ALU), multiplier, and shifter. These units perform all opera-tions in a single cycle. The three units within each processingTable 1.ADSP-21363 Benchmarks (at 333 MHz)Benchmark AlgorithmSpeed(at 333 MHz)1024 Point Complex FFT (Radix 4, with reversal)27.9 µs FIR Filter (per tap)11Assumes two files in multichannel SIMD mode1.5 ns IIR Filter (per biquad)1 6.0 ns Matrix Multiply (pipelined)[3x3] × [3x1][4x4] × [4x1]13.5 ns 23.9 ns Divide (y/×)10.5 ns Inverse Square Root 16.3 nsADSP-21363Preliminary Technical Dataelement are arranged in parallel, maximizing computational throughput. Single multifunction instructions execute parallel ALU and multiplier operations. In SIMD mode, the parallel ALU and multiplier operations occur in both processing ele-ments. These computation units support IEEE 32-bit single-precision floating-point, 40-bit extended precision floating-point, and 32-bit fixed-point data formats.Data Register FileA general-purpose data register file is contained in each processing element. The register files transfer data between the computation units and the data buses, and store intermediate results. These 10-port, 32-register (16 primary, 16 secondary) register files, combined with the ADSP-2136x enhanced Har-vard architecture, allow unconstrained data flow between computation units and internal memory. The registers in PEX are referred to as R0-R15 and in PEY as S0-S15.Single-Cycle Fetch of Instruction and Four Operands The ADSP-21363 features an enhanced Harvard architecture in which the data memory (DM) bus transfers data and the pro-gram memory (PM) bus transfers both instructions and data (see Figure1 on Page1). With the ADSP-21363’s separate pro-gram and data memory buses and on-chip instruction cache, the processor can simultaneously fetch four operands (two over each data bus) and one instruction (from the cache), all in a sin-gle cycle.Instruction CacheThe ADSP-21363 includes an on-chip instruction cache that enables three-bus operation for fetching an instruction and four data values. The cache is selective—only the instructions whose fetches conflict with PM bus data accesses are cached. This cache allows full-speed execution of core, looped operations such as digital filter multiply-accumulates, and FFT butterfly processing.Data Address Generators With Zero-Overhead Hardware Circular Buffer SupportThe ADSP-21363’s two data address generators (DAGs) are used for indirect addressing and implementing circular data buffers in hardware. Circular buffers allow efficient program-ming of delay lines and other data structures required in digital signal processing, and are commonly used in digital filters and Fourier transforms. The two DAGs of the ADSP-21363 contain sufficient registers to allow the creation of up to 32 circular buff-ers (16 primary register sets, 16 secondary). The DAGs automatically handle address pointer wraparound, reduce over-head, increase performance, and simplify implementation. Circular buffers can start and end at any memory location.Figure 2.ADSP-21363 System Sample ConfigurationRev. PrA|Page 4 of 44|September 2004ADSP-21363Preliminary Technical DataRev. PrA |Page 5 of 44|September 2004Flexible Instruction SetThe 48-bit instruction word accommodates a variety of parallel operations, for concise programming. For example, theADSP-21363 can conditionally execute a multiply, an add, and a subtract in both processing elements while branching and fetch-ing up to four 32-bit values from memory—all in a single instruction.ADSP-21363 MEMORY AND I/O INTERFACE FEATURESThe ADSP-21363 adds the following architectural features to the SIMD SHARC family core.On-Chip MemoryThe ADSP-21363 contains three megabits of internal SRAM and four megabits of internal mask-programmable ROM. Each block can be configured for different combinations of code and data storage (see Table 2). Each memory block supports single-cycle, independent accesses by the core processor and I/O pro-cessor. The ADSP-21363 memory architecture, in combination with its separate on-chip buses, allow two data transfers from the core and one from the I/O processor, in a single cycle.The ADSP-21363’s, SRAM can be configured as a maximum of 96K words of 32-bit data, 192K words of 16-bit data, 64K words of 48-bit instructions (or 40-bit data), or combinations of differ-ent word sizes up to three megabits. All of the memory can be accessed as 16-bit, 32-bit, 48-bit, or 64-bit words. A 16-bit float-ing-point storage format is supported that effectively doubles the amount of data that may be stored on-chip. Conversion between the 32-bit floating-point and 16-bit floating-point for-mats is performed in a single instruction. While each memory block can store combinations of code and data, accesses are most efficient when one block stores data using the DM bus for transfers, and the other block stores instructions and data using the PM bus for transfers.Table 2.ADSP-21363 Internal Memory SpaceIOP Registers 0x0000 0000 - 0003 FFFF Long Word (64 bits)Extended Precision Normal or Instruction Word (48 bits)Normal Word (32 bits)Short Word (16 bits)BLOCK 0 ROM0x0004 0000–0x0004 7FFF BLOCK 0 ROM0x0008 0000–0x0008 AAAABLOCK 0 ROM0x0008 0000–0x0008 FFFF BLOCK 0 ROM0x0010 0000–0x0011 FFFF Reserved0x0004 8000–0x0004 BFFF Reserved0x0009 0000–0x0009 7FFF Reserved0x0012 0000–0x0012 FFFF BLOCK 0 RAM0x0004 C000–0x0004 FFFF BLOCK 0 RAM0x0009 0000–0x0009 5555BLOCK 0 RAM0x0009 8000–0x0009 FFFF BLOCK 0 RAM0x0013 0000–0x0013 FFFF BLOCK 1 ROM0x0005 0000–0x0005 7FFF BLOCK 1 ROM0x000A 0000–0x000A AAAABLOCK 1 ROM0x000A 0000– 0x000A FFFF BLOCK 1 ROM0x0014 0000–0x0015 FFFF Reserved0x0005 8000–0x0005 BFFF Reserved0x000B 0000– 0x000B 7FFF Reserved0x0016 0000–0x0016 FFFF BLOCK 1 RAM0x0005 C000–0x0005 FFFF BLOCK 1 RAM0x000B 0000–0x000B 5555BLOCK 1 RAM0x000B 8000–0x000B FFFF BLOCK 1 RAM0x0017 0000–0x0017 FFFF BLOCK 2 RAM0x0006 0000–0x0006 1FFF BLOCK 2 RAM0x000C 0000–0x000C 2AAA BLOCK 2 RAM0x000C 0000–0x000C 3FFF BLOCK 2 RAM0x0018 0000–0x0018 7FFF Reserved0x0006 2000– 0x0006 FFFF Reserved0x000C 4000– 0x000D FFFF Reserved0x0018 8000–0x001B FFFF BLOCK 3 RAM0x0007 0000–0x0007 1FFF BLOCK 3 RAM0x000E 0000–0x000E 2AAA BLOCK 3 RAM0x000E 0000–0x000E 3FFF BLOCK 3 RAM0x001C 0000–0x001C 7FFF Reserved0x0007 2000– 0x0007 FFFFReserved0x000E 4000–0x000F FFFFReserved0x001C 8000–0x001F FFFF Reserved0x0020 0000–0xFFFF FFFFADSP-21363Preliminary Technical DataUsing the DM bus and PM buses, with one bus dedicated to each memory block, assures single-cycle execution with two data transfers. In this case, the instruction must be available in the cache.DMA ControllerThe ADSP-21363’s on-chip DMA controller allows data trans-fers without processor intervention. The DMA controller operates independently and invisibly to the processor core, allowing DMA operations to occur while the core is simulta-neously executing its program instructions. DMA transfers can occur between the ADSP-21363’s internal memory and its serial ports, the SPI-compatible (Serial Peripheral Interface) ports, the IDP (Input Data Port), the Parallel Data Acquisition Port (PDAP), or the parallel port. Twenty-five channels of DMA are available on the ADSP-21363—two for the SPI interface, two for memory-to-memory transfers, twelve via the serial ports, eight via the Input Data Port, and one via the processor’s parallel port. Programs can be downloaded to the ADSP-21363 using DMA transfers. Other DMA features include interrupt genera-tion upon completion of DMA transfers, and DMA chaining for automatic linked DMA transfers. Digital Audio Interface (DAI)The Digital Audio Interface (DAI) provides the ability to con-nect various peripherals to any of the SHARCs DAI pins (DAI_P20–1).Programs make these connections using the Signal Routing Unit (SRU, shown in Figure3).The SRU is a matrix routing unit (or group of multiplexers) that enables the peripherals provided by the DAI to be intercon-nected under software control. This allows easy use of the DAI associated peripherals for a much wider variety of applications by using a larger set of algorithms than is possible with noncon-figurable signal paths.The DAI also includes six serial ports, two precision clock gen-erators (PCGs), an input data port (IDP), an SPI port, six flag outputs and six flag inputs, and three timers. The IDP provides an additional input path to the ADSP-21363 core, configurable as either eight channels of I2S serial data or as seven channels plus a single 20-bit wide synchronous parallel data acquisition port. Each data channel has its own DMA channel that is inde-pendent from the ADSP-21363's serial ports.For complete information on using the DAI, see the ADSP-2136x SHARC Processor Hardware Reference.Serial PortsThe ADSP-21363 features six synchronous serial ports that pro-vide an inexpensive interface to a wide variety of digital and mixed-signal peripheral devices such as Analog Devices’AD183x family of audio codecs, ADCs, and DACs. The serial ports are made up of two data lines, a clock and frame sync. The data lines can be programmed to either transmit or receive and each data line has a dedicated DMA channel.Serial ports are enabled via 12 programmable and simultaneous receive or transmit pins that support up to 24 transmit or 24 receive channels of audio data when all six SPORTS are enabled, or six full duplex TDM streams of 128 channels per frame.The serial ports operate at a maximum data rate of 50M bits/s. Serial port data can be automatically transferred to and from on-chip memory via dedicated DMA channels. Each of the serial ports can work in conjunction with another serial port to provide TDM support. One SPORT provides two transmit sig-nals while the other SPORT provides the two receive signals. The frame sync and clock are shared.Serial ports operate in four modes:•Standard DSP serial mode•Multichannel(TDM)mode•I2S mode•Left-justified sample pair modeLeft-justified sample pair mode is a mode where in each frame sync cycle two samples of data are transmitted/received—one sample on the high segment of the frame sync, the other on the low segment of the frame sync. Programs have control over var-ious attributes of this mode.Figure 3.ADSP-21363 I/O Processor and Peripherals Block DiagramRev. PrA|Page 6 of 44|September 2004ADSP-21363Preliminary Technical DataRev. PrA |Page 7 of 44|September 2004Each of the serial ports supports the left-justified sample pair and I 2S protocols (I 2S is an industry standard interface com-monly used by audio codecs, ADCs and DACs such as the Analog Devices AD183x family), with two data pins, allowing four left-justified sample pair or I 2S channels (using two stereo devices) per serial port, with a maximum of up to 24 I 2S chan-nels. The serial ports permit little-endian or big-endiantransmission formats and word lengths selectable from 3 bits to 32 bits. For the left-justified sample pair and I 2S modes, data-word lengths are selectable between 8 bits and 32 bits. Serial ports offer selectable synchronization and transmit modes as well as optional µ-law or A-law companding selection on a per channel basis. Serial port clocks and frame syncs can be inter-nally or externally generated.Parallel PortThe Parallel Port provides interfaces to SRAM and peripheral devices. The multiplexed address and data pins (AD15–0) can access 8-bit devices with up to 24 bits of address, or 16-bit devices with up to 16 bits of address. In either mode, 8- or 16-bit, the maximum data transfer rate is 55M bytes/sec.DMA transfers are used to move data to and from internal memory. Access to the core is also facilitated through the paral-lel port register read/write functions. The RD, WR, and ALE (Address Latch Enable) pins are the control pins for the parallel port.Serial Peripheral (Compatible) InterfaceThe ADSP-21363 SHARC processor contains two Serial Periph-eral Interface ports (SPIs). The SPI is an industry standardsynchronous serial link, enabling the ADSP-21363 SPI compati-ble port to communicate with other SPI compatible devices. The SPI consists of two data pins, one device select pin, and one clock pin. It is a full-duplex synchronous serial interface, sup-porting both master and slave modes. The SPI port can operate in a multimaster environment by interfacing with up to four other SPI compatible devices, either acting as a master or slave device. The ADSP-21363 SPI compatible peripheral implemen-tation also features programmable baud rate and clock phase and polarities. The ADSP-21363 SPI compatible port uses open drain drivers to support a multimaster configuration and to avoid data contention.Pulse Width ModulationThe PWM module is a flexible, programmable, PWM waveform generator that can be programmed to generate the required switching patterns for various applications related to motor and engine control or audio power control. The PWM generator can generate either center-aligned or edge-aligned PWM wave-forms. In addition, it can generate complementary signals on two outputs in paired mode or independent signals in non paired mode (applicable to a single group of four PWM waveforms).The entire PWM module has four groups of four PWM outputs each. Therefore this module generates 16 PWM outputs in total. Each PWM group produces two pairs of PWM signals on the four PWM outputs.The PWM generator is capable of operating in two distinct modes while generating center-aligned PWM waveforms: single update mode, or double update mode. In single update mode the duty cycle values are programmable only once per PWM period. This results in PWM patterns that are symmetrical around the mid-point of the PWM period. In double update mode, a second updating of the PWM registers is implemented at the mid-point of the PWM period. In this mode, it is possible to produce asymmetrical PWM patterns that produce lower harmonic distortion in three-phase PWM inverters.TimersThe ADSP-21363 has a total of four timers: a core timer able to generate periodic software interrupts and three general purpose timers that can generate periodic interrupts and be indepen-dently set to operate in one of three modes:•Pulse Waveform Generation mode •Pulse Width Count /Capture mode •External Event Watchdog modeThe core timer can be configured to use FLAG3 as a Timer Expired signal, and each general-purpose timer has one bidirec-tional pin and four registers that implement its mode ofoperation: a 6-bit configuration register, a 32-bit count register, a 32-bit period register, and a 32-bit pulse width register. A sin-gle control and status register enables or disables all three general purpose timers independently.Program BootingThe internal memory of the ADSP-21363 boots at system power-up from an 8-bit EPROM via the parallel port, an SPI master, an SPI slave or an internal boot. Booting is determined by the Boot Configuration (BOOTCFG1–0) pins. Selection of the boot source is controlled via the SPI as either a master or slave device.Phase-Locked LoopThe ADSP-21363 uses an on-chip Phase-Locked Loop (PLL) to generate the internal clock for the core. On power up, theCLKCFG1–0 pins are used to select ratios of 32:1, 16:1, and 6:1. After booting, numerous other ratios can be selected via soft-ware control. The ratios are made up of software configurable numerator values from 1 to 32 and software configurable divi-sor values of 1, 2, 4, 8, and 16.Power SuppliesThe ADSP-21363 has separate power supply connections for the internal (V DDINT ), external (V DDEXT ), and analog (A VDD /A VSS ) power supplies. The internal and analog supplies must meet the 1.2 V requirement. The external supply must meet the 3.3 V requirement. All external supply pins must be connected to the same power supply.Note that the analog supply (A VDD ) powers the ADSP-21363’s clock generator PLL. To produce a stable clock, programs should provide an external circuit to filter the power input to the A VDD pin. Place the filter as close as possible to the pin. For an example circuit, see Figure 4. To prevent noise coupling, useRev. PrA |Page 8 of 44|September 2004ADSP-21363Preliminary Technical Dataa wide trace for the analog ground (A VSS ) signal and install a decoupling capacitor as close as possible to the pin. Note that the A VSS and A VDD pins specified in Figure 4 are inputs to the processor and not the analog ground plane on the board.Target Board JTAG Emulator ConnectorAnalog Devices DSP Tools product line of JTAG emulators uses the IEEE 1149.1 JTAG test access port of the ADSP-21363 pro-cessor to monitor and control the target board processor during emulation. Analog Devices DSP Tools product line of JTAG emulators provides emulation at full processor speed, allowing inspection and modification of memory, registers, and proces-sor stacks. The processor's JTAG interface ensures that the emulator will not affect target system loading or timing.For complete information on Analog Devices’ SHARC DSP Tools product line of JTAG emulator operation, see the appro-priate “Emulator Hardware User's Guide”.DEVELOPMENT TOOLSThe ADSP-21363 is supported with a complete set ofCROSSCORE ® software and hardware development tools, including Analog Devices emulators and VisualDSP++® devel-opment environment. The same emulator hardware that supports other SHARC processors also fully emulates the ADSP-21363.The VisualDSP++ project management environment lets pro-grammers develop and debug an application. This environment includes an easy to use assembler (which is based on an alge-braic syntax), an archiver (librarian/library builder), a linker, a loader, a cycle-accurate instruction-level simulator, a C/C++ compiler, and a C/C++ runtime library that includes DSP and mathematical functions. A key point for these tools is C/C++ code efficiency. The compiler has been developed for efficient translation of C/C++ code to DSP assembly. The SHARC has architectural features that improve the efficiency of compiled C/C++ code.The VisualDSP++ debugger has a number of important fea-tures. Data visualization is enhanced by a plotting package that offers a significant level of flexibility. This graphical representa-tion of user data enables the programmer to quickly determine the performance of an algorithm. As algorithms grow in com-plexity, this capability can have increasing significance on the designer’s development schedule, increasing productivity. Sta-tistical profiling enables the programmer to non intrusively poll the processor as it is running the program. This feature, unique to VisualDSP++, enables the software developer to passively gather important code execution metrics without interruptingthe real-time characteristics of the program. Essentially, the developer can identify bottlenecks in software quickly and effi-ciently. By using the profiler, the programmer can focus on those areas in the program that impact performance and take corrective action.Debugging both C/C++ and assembly programs with the VisualDSP++ debugger, programmers can:•View mixed C/C++ and assembly code (interleaved source and object information)•Insert breakpoints•Set conditional breakpoints on registers, memory, and stacks•Trace instruction execution•Perform linear or statistical profiling of program execution •Fill, dump, and graphically plot the contents of memory •Perform source level debugging •Create custom debugger windowsThe VisualDSP++ IDDE lets programmers define and manage DSP software development. Its dialog boxes and property pages let programmers configure and manage all of the SHARC devel-opment tools, including the color syntax highlighting in the VisualDSP++ editor. This capability permits programmers to:•Control how the development tools process inputs and generate outputs•Maintain a one-to-one correspondence with the tool’s command line switchesThe VisualDSP++ Kernel (VDK) incorporates scheduling and resource management tailored specifically to address the mem-ory and timing constraints of DSP programming. Thesecapabilities enable engineers to develop code more effectively, eliminating the need to start from the very beginning, when developing new application code. The VDK features include Threads, Critical and Unscheduled regions, Semaphores,Events, and Device flags. The VDK also supports Priority-based, Preemptive, Cooperative, and Time-Sliced schedulingapproaches. In addition, the VDK was designed to be scalable. If the application does not use a specific feature, the support code for that feature is excluded from the target system.Because the VDK is a library, a developer can decide whether to use it or not. The VDK is integrated into the VisualDSP++ development environment, but can also be used via standard command line tools. When the VDK is used, the development environment assists the developer with many error-prone tasks and assists in managing system resources, automating the gen-eration of various VDK based objects, and visualizing thesystem state, when debugging an application that uses the VDK.VisualDSP++ Component Software Engineering (VCSE) is Analog Devices’ technology for creating, using, and reusing software components (independent modules of substantial functionality) to quickly and reliably assemble software applica-tions. Download components from the Web and drop them intoFigure 4.Analog Power (A VDD ) Filter CircuitV DDINTA VDDA VSS0.01F0.1F10⍀。

电力线载波扩频通信芯片-应用开发指南.

EASTSOFT® PLCi36G-Ⅲ-E DATA SHEETPLCi36G-Ⅲ-E电力线载波扩频通信芯片–应用开发指南R&D GUIDE FOR PLCi36G-Ⅲ-E DATA SHEET青岛东软电脑技术有限公司2009年9月17日版权所有 2009 青岛东软电脑技术有限公司地址:青岛市上清路16号甲EASTSOFT® PLCi36G-Ⅲ-E DATA SHEET目录1. PLCi36G-Ⅲ-E扩频通信芯片概述 (2)1.1 PLCi36G-Ⅲ-E芯片特点 (2)1.2 PLCi36G-Ⅲ-E主要应用范围 (3)1.3 PLCi36G-Ⅲ-E引脚图 (3)1.4 引脚定义 (4)1.5 主要电气特性 (5)1.6 封装信息 (5)2. 引脚描述......................................................................................................................................... . (6)2.1 晶体振荡器 (6)2.2 编程使能控制 (6)2.3 网络地址管理 (7)2.4 185kHz方波信号输出 (8)2.5 ZCP_DET本地交流电过零检测 (11)2.5.1 推荐电路 (11)2.5.2 电气参数 (11)2.6 终端设备数据输入RX 和终端设备数据输出TX (13)2.6.1 电气特性 (13)2.6.2 数据通信标准 (13)2.7 扩频调制信号输入/输出(SSCIN/SSCOUT) (14)3. 信号耦合电路(Signal Coupling Circuit) (15)3.1 设计目标 (15)3.2 电路组成 (15)3.2.1 电路元器件说明 (15)3.2.2 抑制瞬时电压冲击 (15)3.2.3 信号耦合电路对发送电路和接收电路的影响 (16)4.信号发送部分(Transmitting Section) (17)4.1 发送电路组成 (17)4.2 电路元器件说明 (17)5.信号接收部分(Receiving Section) (19)5.1 接收电路组成 (19)5.2 带通滤波器BPF特性 (19)5.3 低功耗窄带模拟前端AFE3361 (20)5.3.1 AFE3361描述 (20)5.3.2 AFE3361主要特点 (20)5.3.3 最大额定值 (21)5.3.4 电气特性 (21)5.3.5 AFE3361的典型应用电路 (22)6.电源系统......................................................................................................................................... . (23)版权所有 2009 青岛东软电脑技术有限公司地址:青岛市上清路16号甲- 1 -EASTSOFT® PLCi36G-Ⅲ-E DATA SHEET1. PLCi36G-Ⅲ-E扩频通信芯片概述EASTSOFT® PLCi36G-Ⅲ-E是专门为电力线介质作为通信信道而设计的扩频通信芯片。

XP313使用手册

2

XP313 使用手册

4.2 指示灯

图 4-1 XP313 结构简图

表 4-1 卡件状态指示灯

LED 指示灯 意义

状态 常灭

常亮 闪

FAIL(红) RUN(绿) WORK(绿) COM(绿)

故障指示 运行指示 工作/备用

通信指示

正常 自检故障Байду номын сангаасCPU 复位

不运行

-正常

备用 工作 切换中

无通信 组态错误

第四通道 (CH4) 第五通道 (CH5) 第六通道 (CH6)

4.5 安全栅底板选型

XP313 卡件可通过转接端子板 XP528/XP528R 与安全栅底板相连。

4

XP313 使用手册

表 4-5 安全栅底板选型

卡件工作方式

转接模块

单卡

XP528

冗余

XP528R

安全栅底板使用说明请查看《XP513-E8R 使用手册》。

4.4 端子定义及接线

配电

端子图

表 4-4 接线端子说明

不配电

端

端子定义

子

号 配电

不配电

1

+

-

2

-

+

3

+

-

4

-

+

5

+

-

6

-

+

7 不接线 不接线 8 不接线 不接线

9

+

-

10

-

+

11

+

-

12

-

+

13

+

-

14

-

+

2SK3133L中文资料

2SK3133(L),2SK3133(S)Silicon N Channel MOS FETHigh Speed Power SwitchingADE-208-720 (Z)Target Specification1st. EditionFebruary 1999 Features• Low on-resistance= 7 mΩ typ.RDS(on)• Low drive current• 4 V gate drive device can be driven from 5 V sourceOutline2SK3133(L),2SK3133(S)2Absolute Maximum Ratings (Ta = 25°C)ItemSymbol Ratings Unit Drain to source voltage V DSS 30V Gate to source voltage V GSS ±20V Drain current I D50A Drain peak currentI D(pulse) Note 1200A Body-drain diode reverse drain current I DR50A Channel dissipation Pch Note 250W Channel temperature Tch 150°C Storage temperature Tstg–55 to +150°CNote:1.PW ≤ 10 µs, duty cycle ≤ 1%2.Value at Tc = 25°CElectrical Characteristics (Ta = 25°C)ItemSymbol MinTyp Max Unit Test Conditions Drain to source breakdown voltage V (BR)DSS30——V I D = 10 mA, V GS = 0Gate to source leak current I GSS ——±0.1µA V GS = ±20 V, V DS = 0Zero gate voltege drain current I DSS ——10µA V DS = 30 V, V GS = 0Gate to source cutoff voltage V GS(off) 1.0— 2.5V I D = 1 mA, V DS = 10 V Note 1Static drain to source on state R DS(on)—710m ΩI D = 25 A, V GS = 10 V Note 1resistance—1218m ΩI D = 25 A, V GS = 4 V Note 1Forward transfer admittance |y fs |TBD TBD —S I D = 25 A, V DS = 10 V Note 1Input capacitance Ciss —TBD —pF V DS = 10V Output capacitanceCoss —TBD —pF V GS = 0Reverse transfer capacitance Crss —TBD —pF f = 1 MHz Total gate charge Qg —TBD —nc V DD = 10 V Gate to source charge Qgs —TBD —nc V GS = 10 V Gate to drain charge Qgd —TBD —nc I D = 50 ATurn-on delay time t d(on)—TBD —ns V GS = 10 V, I D = 25 A Rise timet r —TBD —ns R L = 0.4 ΩTurn-off delay time t d(off)—TBD —ns Fall timet f —TBD —ns Body–drain diode forward voltage V DF —TBD —V I F = 50 A, V GS = 0Body–drain diode reverse recovery time t rr—TBD—nsI F = 50 A, V GS = 0diF/ dt = 50 A/ µs Note:1.Pulse test2SK3133(L),2SK3133(S) Main Characteristics32SK3133(L),2SK3133(S)Package DimensionsUnit: mm4Cautions1.Hitachi neither warrants nor grants licenses of any rights of Hitachi’s or any third party’s patent,copyright, trademark, or other intellectual property rights for information contained in this document.Hitachi bears no responsibility for problems that may arise with third party’s rights, includingintellectual property rights, in connection with use of the information contained in this document.2.Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.3.Hitachi makes every attempt to ensure that its products are of high quality and reliability. However,contact Hitachi’s sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation,traffic, safety equipment or medical equipment for life support.4.Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installationconditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.5.This product is not designed to be radiation resistant.6.No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.7.Contact Hitachi’s sales office for any questions regarding this document or Hitachi semiconductor products.Hitachi, Ltd.Semiconductor & Integrated Circuits.Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Tel: Tokyo (03) 3270-2111 Fax: (03) 3270-5109Copyright ' Hitachi, Ltd., 1999. All rights reserved. Printed in Japan.Hitachi Asia Pte. Ltd.16 Collyer Quay #20-00Hitachi TowerSingapore 049318Tel: 535-2100Fax: 535-1533URLNorthAmerica : http:/Europe : /hel/ecg Asia (Singapore): .sg/grp3/sicd/index.htm Asia (Taiwan): /E/Product/SICD_Frame.htm Asia (HongKong): /eng/bo/grp3/index.htm Japan : http://www.hitachi.co.jp/Sicd/indx.htmHitachi Asia Ltd.Taipei Branch Office3F, Hung Kuo Building. No.167, Tun-Hwa North Road, Taipei (105)Tel: <886> (2) 2718-3666Fax: <886> (2) 2718-8180Hitachi Asia (Hong Kong) Ltd.Group III (Electronic Components)7/F., North Tower, World Finance Centre,Harbour City, Canton Road, Tsim Sha Tsui,Kowloon, Hong Kong Tel: <852> (2) 735 9218Fax: <852> (2) 730 0281 Telex: 40815 HITEC HXHitachi Europe Ltd.Electronic Components Group.Whitebrook ParkLower Cookham Road MaidenheadBerkshire SL6 8YA, United Kingdom Tel: <44> (1628) 585000Fax: <44> (1628) 778322Hitachi Europe GmbHElectronic components Group Dornacher Stra§e 3D-85622 Feldkirchen, Munich GermanyTel: <49> (89) 9 9180-0Fax: <49> (89) 9 29 30 00Hitachi Semiconductor (America) Inc.179 East Tasman Drive,San Jose,CA 95134 Tel: <1> (408) 433-1990Fax: <1>(408) 433-0223For further information write to:。

S331C中文说明书

Site MasterS113C,S114C,S331C,S332C,天线、电缆和频谱分析仪用户指南专门用于传输线和其它射频器件的手持式测试仪目录第一章—概述简介………………………………………………………………..1-1说明………………………………………………………………..1-1标准附件……………………………………………………………1-1选件…………………………………………………………………1-2可选附件……………………………………………………………1-2性能指标…………………………………………………………..1-3维护事项……………………………………………………………1-6校准…………………………………………………………………1-6自动校准InstaCal 模块…………… ………………………………1-7年检………………………………………………………………….1-7第二章—功能和操作简介…………………………………………………………….…….2-1测试连接器面板…………………………………………………….2-1前面板概述………………………………………………………….2-2功能区硬键……………………………………………………………2-3 键盘区硬键…………………………………………………………2-4软键…. ………………………………………………………………2-6功率监测菜单……………………………………………………….2-15符号………………………………………………………………….2-19自检………………………………………………………………….2-19错误代码…………………………………………………………….2-19 自检错误…………..…………………………………………….2-19范围错误……..………………………………………………….2-21自动校准InstaCal错误消息………….…………………………2-22 电池信息…………………………………………….………………2-24新电池充电…………………………………………………………2-24 在Site Master上给电池充电…………………………………….2-24用充电器给电池充电………………………………………………2-24电池充电指示……………………………………………………2-25电池寿命…………………………………………………………..2-25关于电池的重要信息……………………………………………..2-26第三章—操作入门简介…………………………………………………………3-1开机过程……………………………………………………3-1选择频率/距离………………………………………………3-2校准…………………………………………………………..3-2校准确认……………………………………………….3-3手动校准过程………………………………………….3-4自动校准InstaCal 模块确认…………………………3-5自动校准InstaCal模块校准过程……………………. 3-6有测试端口延长电缆的校准………………………3-6 设臵刻度…………………………………………………3-7 自动刻度……………………………………………….3-7幅度刻度………………………………………………3-7 保存和调用设臵………………………………………….3-7 保存设臵……………………………………………...3-7调用设臵……………………………………………..3-8 保存和调用显示…………………………………………3-8 保存显示…………………………………………….3-8调用显示……………………………………………3-8设臵距离和电缆类型……………………………..3-9 改变单位…………………………………………………..3-9改变显示语言……………………………………………..3-9打印………………………………………………………..3-10 打印屏幕……………………………………………..3-10打印机开关设臵……………………………………..3-11 使用软背包……………………………………………….3-12第四章—电缆测量和天线测量简介……………………………………………………….4-1传输线扫描的基本原理………………………………….4-1进行传输线扫描所需的信息…………………………….4-2典型传输线扫描的测试过程…………………………….4-3 系统回波损耗测量………………………………….4-3插入损耗测量………………………………………4-4故障点定位(DTF)传输线测试…………………4-8天线子系统回波损耗测试………………………..4-10第五章—频谱分析仪测量简介……………………………………………………….5-1占用带宽………………………………………………….5-1通道功率测量…………………………………………….5-2 Site Master的通道功率测量…………………………5-2 邻道功率测量…………………………………………….5-4带外杂波散射测量……………………………………….5-6带内/通道外测量…………………………………………5-7场强测量…………………………………………………5-8天线校准………………………………………………….5-9 第六章—功率测量简介………………………………………………………..6-1功率测量…………………………………………………..6-1 第七章—Site Master软件工具简介………………………………………………………… 7-1特点…………………………………………………………7-1系统需求……………………………………………………7-1安装…………………………………………………………7-2 通讯口设臵……………………………………………7-2接口电缆安装………………………………………….7-3 使用软件工具……………………………………………….7-3从Site Master下载图形曲线………………………………..7-3图形获取……………………………………………………..7-3图形属性…………………………………………………….7-4 曲线叠加或图形叠加…………………………………..7-4保存曲线………………………………………………7-5常规电缆列表…………………………………………7-6输入天线因子…………………………………………7-7上载天线因子………………………………………...7-8创建数据库…………………………………………..7-8打印格式……………………………………………..7-8附录 A—参考数据同轴电缆技术数据…………………………………………………A-1附录B—视窗简介…………………………………………………………………B-1 样例…………………………………………………………………B-1第一章概述简介本章对Site Master S113C、S114C、S331C和S332C型号及其性能指标、选用附件、日常维护和校准要求进行了说明。

mc33063中文资料【范本模板】

低成本开关电源芯片MC34063A (MC33063)中文资料该器件本身包含了DC/DC变换器所需要的主要功能的单片控制电路且价格便宜.它由具有温度自动补偿功能的基准电压发生器、比较器、占空比可控的振荡器,R—S触发器和大电流输出开关电路等组成。

该器件可用于升压变换器、降压变换器、反向器的控制核心,由它构成的DC/DC变换器仅用少量的外部元器件。

在各类电子产品中均非常广泛的应用。

MC34063主要特性:输入电压范围:2、5~40V输出电压可调范围:1.25~40V最大输出电流:1.5A最大开关频率:100kHz低静态电流短路电流限制可实现升压或降压电源变换器MC34063的内部结构,引脚图及引脚功能:图1 MC34063内部结构及引脚图1脚:开关管T1集电极引出端;2脚:开关管T1发射极引出端;3脚:定时电容ct接线端;调节ct可使工作频率在100—100kHz范围内变化;4脚:电源地;5脚:电压比较器反相输入端,同时也是输出电压取样端;使用时应外接两个精度不低于1%的精密电阻;6脚:电源端;7脚:负载峰值电流(Ipk)取样端;6,7脚之间电压超过300mV时,芯片将启动内部过流保护功能;8脚:驱动管T2集电极引出端.MC34063A在线电源计算器-Online Power calculationMC34063主要参数:项目条件参数单位Power Supply V oltage 电源电压VCC40VdcComparator Input V oltage Range 比较器输入电压范围VIR0。

3-+40VdcSwitch Collector V oltage 集电极电压开关VC(switch)40VdcSwitch Emitter V oltage (VPin 1 = 40 V)发射极电压开关VE(switch)40VdcSwitch Collector to Emitter V oltage 开关电压集电极到发射极VCE(switch)40VdcDriver Collector V oltage 驱动集电极电压VC(driver)40VdcDriver Collector Current (Note 1) 驱动集电极电流IC(driver)100mASwitch Current 开关电流ISW1。

CPV363资料

C-149IGBT SIP MODULEFeaturesParameterTyp.Max.UnitsR θJC (IGBT)Junction-to-Case, each IGBT, one IGBT in conduction — 3.5R θJC (DIODE)Junction-to-Case, each diode, one diode in conduction — 5.5°C/W R θCS (MODULE)Case-to-Sink, flat, greased surface 0.1—WtWeight of module20 (0.7)—g (oz)• Fully isolated printed circuit board mount package • Switching-loss rating includes all "tail" losses• HEXFRED TMsoft ultrafast diodes• Optimized for medium operating frequency (1 to 10kHz) See Fig. 1 for Current vs. Frequency curveOutput Current in a Typical 5.0 kHz Motor DriveProduct SummaryPD - 5.023BFast IGBTCPV363MF7.65 A RMS per phase (2.4 kW total) with T C = 90°C, T J = 125°C, Supply Voltage 360Vdc,Power Factor 0.8, Modulation Depth 80% (See Figure 1)Thermal ResistanceParameterMax.UnitsV CESCollector-to-Emitter Voltage600VI C @ T C = 25°C Continuous Collector Current, each IGBT 16I C @ T C = 100°C Continuous Collector Current, each IGBT 8.7I CM Pulsed Collector Current50AI LMClamped Inductive Load Current 50I F @ T C = 100°C Diode Continuous Forward Current 6.1I FM Diode Maximum Forward Current 50V GE Gate-to-Emitter Voltage±20V V ISOLIsolation Voltage, any terminal to case, 1 min.2500V RMS P D @ T C = 25°C Maximum Power Dissipation, each IGBT 36WP D @ T C = 100°C Maximum Power Dissipation, each IGBT 14T J Operating Junction and-40 to +150T STGStorage Temperature Range°CSoldering Temperature, for 10 sec.300 (0.063 in. (1.6mm) from case)Mounting torque, 6-32 or M3 screw.5-7 lbf•in (0.55-0.8 N•m)DescriptionThe IGBT technology is the key to International Rectifier's advanced line of IMS (Insulated Metal Substrate) Power Modules. These modules are more efficient than comparable bipolar transistor modules, while at the same time having the simpler gate-drive requirements of the familiar power MOSFET.This superior technology has now been coupled to a state of the art materials system that maximizes power throughput with low thermal resistance. This package is highly suited to motor drive applications and where space is at a premium.Absolute Maximum Ratings3671319181510164912D1D3D5D2D4D6Q1Q2Q3Q4Q5Q61IMS-2Revision 1CPV363MFC-150C-151Fig. 1 - RMS Current and Output Power, Synthesized Sine WaveFig. 2 - Typical Output Characteristics Fig. 3- Typical Transfer CharacteristicsC-152Fig. 5 - Collector-to-Emitter Voltage vs.Case TemperatureFig. 4 - Maximum Collector Current vs.Case TemperatureCPV363MFCPV363MFC-153Fig. 11 - Typical Switching Losses vs.Collector-to-Emitter CurrentFig. 12 - Turn-Off SOA Fig. 13- Maximum Forward Voltage Drop vs. Instantaneous Forward CurrentC-154C-155Fig. 18a - Test Circuit for Measurement of I LM, E on, E off(diode), t rr, Q rr, I rr, t d(on), t r, t d(off), t f CPV363MFC-156。

TSOP31338中文资料

New TSOP311../TSOP313..Document Number 81763Rev. 1.0, 09-Aug-07Vishay Semiconductors1IR Receiver Modules for Remote Control SystemsDescriptionThe TSOP31#.. series are miniaturized receivers for infrared remote control systems. A PIN diode and a preamplifier are assembled on a lead frame, the epoxy package acts as an IR filter.The demodulated output signal can be directly decoded by a microprocessor. The TSOP311.. is compatible with all common IR ... remote control data formats. The TSOP313.. is optimized to better suppress spurious pulses from energy saving fluorescent lamps but will also suppress some data signals.This component has not been qualified according to automotive specifications.Features•Very low supply current •Photo detector and preamplifier in one package•Internal filter for PCM frequency•Improved shielding against EMI •Supply voltage: 2.5 V to 5.5 V•Improved immunity against ambient light•Component in accordance to RoHS 2002/95/EC and WEEE 2002/96/EC•Insensitive to supply voltage ripple and noiseMechanical DataPinning:1 = GND,2 = V S ,3 = OUTProduct MatrixParts TableBlock DiagramApplication CircuitStandard applications Very noisy enviroments TSOP311..TSOP313..PartCarrier Frequency TSOP31#3030 kHz TSOP31#3333 kHz TSOP31#3636 kHz TSOP31#3838 kHz TSOP31#4040 kHz TSOP31#5656 kHz94 8691123 2Document Number 81763Rev. 1.0, 09-Aug-07New TSOP311../TSOP313..Vishay Semiconductors Absolute Maximum RatingsT amb = 25°C, unless otherwise specifiedElectrical and Optical CharacteristicsT amb = 25°C, unless otherwise specifiedTypical CharacteristicsT amb = 25°C, unless otherwise specifiedParameterTest conditionSymbol Value Unit Supply voltage (Pin 2)V S - 0.3 to + 6.0V Supply current (Pin 2)I S 3mA Output voltage (Pin 3)V O - 0.3 to (V S + 0.3)V Output current (Pin 3)I O 5mA Junction temperature T j 100°C Storage temperature range T stg - 25 to + 85°C Operating temperature range T amb - 25 to + 85°C Power consumption (T amb ≤ 85°C)P tot 10mW Soldering temperaturet ≤ 10 s, 1 mm from caseT sd260°CParameterTest conditionSymbol Min Typ.Max Unit Supply current (Pin 2)E v = 0, V S = 3.3 V I SD 0.270.350.45mA E v = 40 klx, sunlightI SH 0.45mA Supply voltage V S 2.55.5V Transmission distanceE v = 0, test signal see fig. 1,IR diode TSAL6200, IF = 250 mAd45mOutput voltage low (Pin 3)I OSL = 0.5 mA, E e = 0.7 mW/m 2,test signal see fig. 1V OSL 100mVMinimum irradiancePulse width tolerance:t pi - 5/f o < t po < t pi + 6/f o ,test signal see fig. 1E e min 0.150.35mW/m 2Maximum irradiance t pi- 5/f o < t po < t pi + 6/f o ,test signal see fig. 1E e max 30W/m 2DirectivityAngle of half transmission distanceϕ1/2± 45degFigure 1. Output Active Low Figure 2. Pulse Length and Sensitivity in Dark AmbientNew TSOP311../TSOP313..Document Number 81763Rev. 1.0, 09-Aug-07Vishay Semiconductors3Figure 3. Output Function Figure 4. Output Pulse Diagram Figure 5. Frequency Dependence of Responsivity EV O V V0.00.20.40.60.81.01.20.70.9 1.1 1.3f/f 0 - Relati v e Fre qu ency16925E /E - R e l. R e s p o n s i v i t y e m i ne Figure 6. Sensitivity in Bright AmbientFigure 7. Sensitivity vs. Supply Voltage DisturbancesFigure 8. Sensitivity vs. Electric Field Disturbances 4Document Number 81763Rev. 1.0, 09-Aug-07New TSOP311../TSOP313..Vishay SemiconductorsFigure 9. Max. Envelope Duty Cycle vs. Burst Length Figure 10. Sensitivity vs. Ambient Temperature Figure 11. Relative Spectral Sensitivity vs. Wavelength0.00.20.40.60.81.01.275085095010501150λ-W a v elength (nm)16919S ()- R e l a t i v e S p e c tr a l S e n s i t i v i t yλr e l Figure 12. Horizontal DirectivityFigure 13. Vertical DirectivityFigure 14. Sensitivity vs. Supply VoltageNew TSOP311../TSOP313..Document Number 81763Rev. 1.0, 09-Aug-07Vishay Semiconductors5Suitable Data FormatThe TSOP31#.. series is designed to suppress spurious output pulses due to noise or disturbance signals. Data and disturbance signals can be distinguished by the devices according to carrier frequency, burst length and envelope duty cycle. The data signal should be close to the band-pass center frequency (e.g. 38 kHz) and fulfill the conditions in the table below.When a data signal is applied to the TSOP31#.. in the presence of a disturbance signal, the sensitivity of the receiver is reduced to insure that no spurious pulses are present at the output. Some examples of disturbance signals which are suppressed are: •DC light (e.g. from tungsten bulb or sunlight) •Continuous signals at any frequency •Modulated noise from fluorescent lamps with electronic ballastsFor data formats with long bursts (more than 10 carrier cycles) please see the data sheet for TSOP312../TSOP314..Figure 15. IR Signal from Fluorescent Lampwith low ModulationFigure 16. IR Signal from Fluorescent Lampwith high Modulation101520Time (ms)16920I R S i g n a l50101520Time (ms)16921I R S i g n a l10TSOP311..TSOP313..Minimum burst length 6 cycles/burst 6 cycles/burst After each burst of length A gap time is required of6 to 70 cycles 10 cycles 6 to 35 cycles 10 cycles For bursts greater thanA gap time in the data stream is needed of 70 cycles> 1.2 x burst length35 cycles > 6 x burst lengthMaximum continuous short bursts/second 20002000Compatible to NEC code yes yes Compatible to RC5/RC6 code yes yes Compatible to Sony code yes no Compatible to RCMM code yes yes Compatible to r-step code yes yes Compatible to XMP codeyesyesSuppression of interference from fluorescent lampsCommon disturbance signals aresupressed (Example: Signal pattern of fig. 15)Even critical disturbance signals are suppressed (Examples: Signal patternof fig. 15 and fig. 16) 6Document Number 81763Rev. 1.0, 09-Aug-07New TSOP311../TSOP313.. Vishay SemiconductorsPackage Dimensionsin millimetersNew TSOP311../TSOP313..Document Number 81763Rev. 1.0, 09-Aug-07Vishay Semiconductors7Ozone Depleting Substances Policy StatementIt is the policy of Vishay Semiconductor GmbH to1.Meet all present and future national and international statutory requirements.2.Regularly and continuously improve the performance of our products, processes, distribution and operating systems with respect to their impact on the health and safety of our employees and the public, as well as their impact on the environment.It is particular concern to control or eliminate releases of those substances into the atmosphere which are known as ozone depleting substances (ODSs).The Montreal Protocol (1987) and its London Amendments (1990) intend to severely restrict the use of ODSs and forbid their use within the next ten years. Various national and international initiatives are pressing for an earlier ban on these substances.Vishay Semiconductor GmbH has been able to use its policy of continuous improvements to eliminate the use of ODSs listed in the following documents.1.Annex A, B and list of transitional substances of the Montreal Protocol and the London Amendments respectively2.Class I and II ozone depleting substances in the Clean Air Act Amendments of 1990 by the Environmental Protection Agency (EPA) in the USA3.Council Decision 88/540/EEC and 91/690/EEC Annex A, B and C (transitional substances) respectively.Vishay Semiconductor GmbH can certify that our semiconductors are not manufactured with ozone depleting substances and do not contain such substances.We reserve the right to make changes to improve technical designand may do so without further notice.Parameters can vary in different applications. All operating parameters must be validated for each customer application by the customer. Should the buyer use Vishay Semiconductors products for any unintended or unauthorized application, the buyer shall indemnify Vishay Semiconductors against all claims, costs, damages, and expenses, arising out of, directly or indirectly, any claim of personal damage, injury or death associatedwith such unintended or unauthorized use.Vishay Semiconductor GmbH, P.O.B. 3535, D-74025 Heilbronn, GermanyLegal Disclaimer NoticeVishay Document Number: Revision: 08-Apr-051NoticeSpecifications of the products displayed herein are subject to change without notice. Vishay Intertechnology, Inc., or anyone on its behalf, assumes no responsibility or liability for any errors or inaccuracies.Information contained herein is intended to provide a product description only. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Vishay's terms and conditions of sale for such products, Vishay assumes no liability whatsoever, and disclaims any express or implied warranty, relating to sale and/or use of Vishay products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright, or other intellectual property right. The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications. Customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Vishay for any damages resulting from such improper use or sale.。

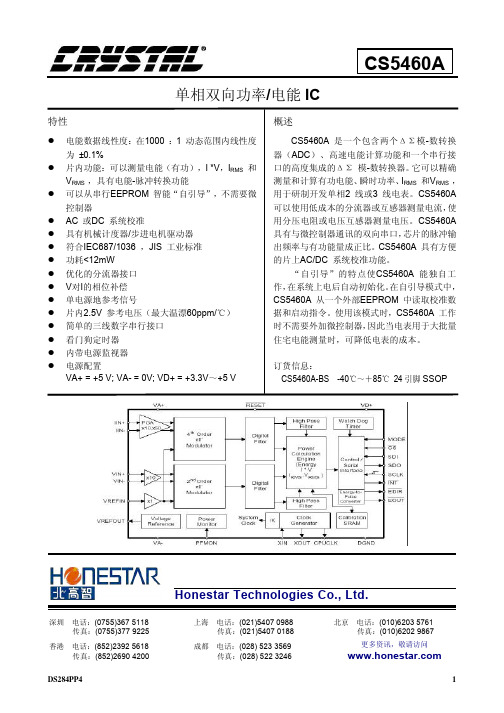

CS5463A中文资料手册pdf

NCP603SN280T1G,NCP603SN300T1G,NCP603SN330T1G,NCP603SN350T1G,NCP603SN500T1G, 规格书,Datasheet 资料

1. True no connect. Printed circuit board traces are allowable.

ABSOLUTE MAXIMUM RATINGS

Rating

Symbol

Value

Unit

Input Voltage (Note 2) Output, Enable, Adjustable Voltage

Dropout Voltage 1.25 V

Regload Iout = 1.0 mA to 300 mA

−

2.0

45

mV

Vn

f = 10 Hz to 100 kHz

−

50

−

mVrms

Isc

350

650

900

mA

VDO

Measured at: Vout – 2.0%,

Iout = 150 mA, Figure 2

VIN GND

Fixed Voltage Only

Driver w/ Current Limit

Thermal Shutdown

+ -

+ −1.25 V

Adjustable Version Only

ENABLE Figure 1. Simplified Block Diagram

VOUT ADJ

PIN CONNECTIONS

Vin 1 GND 2 ENABLE 3

5 Vout 4 ADJ/NC*

(Top View)

* ADJ − Adjustable Version * NC − Fixed Voltage Version

ORDERING INFORMATION

TMP320C6211GJL120资料

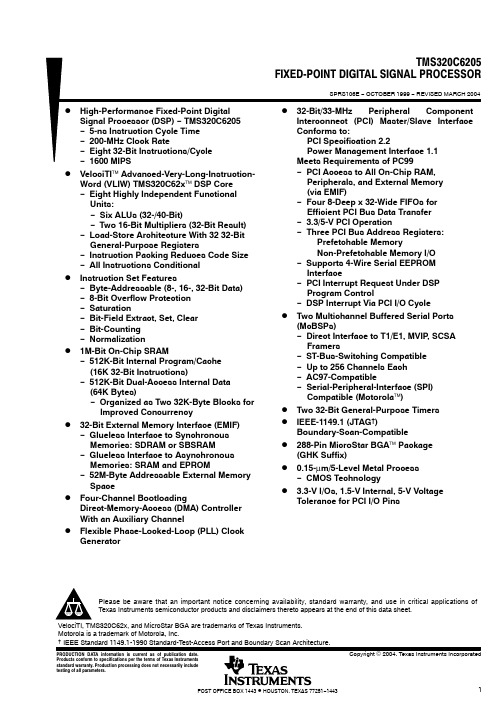

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. VelociTI, TMS320C62x, and MicroStar BGA are trademarks of Texas Instruments. Motorola is a trademark of Motorola, Inc. † IEEE Standard 1149.1-1990 Standard-Test-Access Port and Boundary Scan Architecture.

Copyright 2004, Texas Instruments Incorporated

POST OFFICE BOX 1443

• HOUSTON, TEXAS 77251−1443

1

元器件交易网

TMS320C6205 FIXED-POINT DIGITAL SIGNAL PROCESSOR

元器件交易网

TMS320C6205 FIXED-POINT DIGITAL SIGNAL PROCESSOR

SPRS106E − OCTOBER 1999 − REVISED MARCH 2004

D High-Performance Fixed-Point Digital

D 32-Bit/33-MHz

DLeabharlann D D D D DPeripheral Component Interconnect (PCI) Master/Slave Interface Conforms to: PCI Specification 2.2 Power Management Interface 1.1 Meets Requirements of PC99 − PCI Access to All On-Chip RAM, Peripherals, and External Memory (via EMIF) − Four 8-Deep x 32-Wide FIFOs for Efficient PCI Bus Data Transfer − 3.3/5-V PCI Operation − Three PCI Bus Address Registers: Prefetchable Memory Non-Prefetchable Memory I/O − Supports 4-Wire Serial EEPROM Interface − PCI Interrupt Request Under DSP Program Control − DSP Interrupt Via PCI I/O Cycle Two Multichannel Buffered Serial Ports (McBSPs) − Direct Interface to T1/E1, MVIP, SCSA Framers − ST-Bus-Switching Compatible − Up to 256 Channels Each − AC97-Compatible − Serial-Peripheral-Interface (SPI) Compatible (Motorola) Two 32-Bit General-Purpose Timers IEEE-1149.1 (JTAG†) Boundary-Scan-Compatible 288-Pin MicroStar BGA Package (GHK Suffix) 0.15-µm/5-Level Metal Process − CMOS Technology 3.3-V I/Os, 1.5-V Internal, 5-V Voltage Tolerance for PCI I/O Pins

TPS60313中文资料

EFFICIENCY vs OUTPUT CURRENT (OUT2) 90 80 70 Efficiency – % 60 50 40 30 20 VI = 1.3 V 0 10 100 0.001 0.01 0.1 1 IO – Output Current (OUT2) – mA Snooze mode improves efficiency at an output current in the range of 1 µA to 100 µA. 10 Normal Mode Snooze Mode

SLVS362A – MAY 2001 – REVISED AUGUST 2001

TPS60310 and TPS60311 functional block diagram

C1F C1– C1+

VIN

CP1 2x (Doubler) Charge Pump

OUT1

_ SNOOZE Control Oscillator + _ Reg + Vref CP2 1.5x/2x Charge Pump + _

AVAILABLE OPTIONS PART NUMBER† TPS60310DGS TPS60311DGS TPS60312DGS TPS60313DGS MARKING DGS PACKAGE ATG ATI ATK ATL OUTPUT CURRENT 1 [mA]‡ 40 40 40 40 OUTPUT CURRENT 2 [mA]§ 20 20 20 20 OUTPUT VOLTAGE 1 [V] 2 x VIN 2 x VIN 2 x VIN 2 x VIN OUTPUT VOLTAGE 2 [V] 3.3 3 3.3 3 FEATURE Open-drain power-good output Open-drain power-good output Push-pull power-good output

NTGD3133P资料

NTGD3133P Power MOSFET−20 V, −2.5 A, P−Channel, TSOP−6 DualFeatures•Reduced Gate Charge for Fast Switching •−2.5 V Gate Rating•Leading Edge Trench Technology for Low On Resistance •Independent Devices to Provide Design Flexibility •This is a Pb−Free DeviceApplications•Li−Ion Battery Charging•Load Switch / Power Switching •DC to DC Conversion•Portable Devices like PDA’s, Cellular Phones, and Hard DrivesMAXIMUM RATINGS (T J = 25°C unless otherwise noted)ParameterSymbol Value Unit Drain−to−Source Voltage V DSS −20V Gate−to−Source Voltage VGS ±12V Continuous Drain Current (Note 1)Steady State T A = 25°C I D−2.3AT A = 85°C −1.6t ≤5 sT A = 25°C−2.5Power Dissipation (Note 1)Steady State T A = 25°CPD1.1Wt ≤5 s 1.3Continuous DrainCurrent (Note 2)Steady StateT A = 25°C I D−1.6AT A = 85°C −1.2Power Dissipation(Note 2)T A = 25°C P D 0.56W Pulsed Drain Currentt p = 10 m sI DM ±7.0A Operating Junction and Storage Temperature T J , T STG−55 to 150°C Source Current (Body Diode)I S −0.8A Lead Temperature for Soldering Purposes (1/8″ from case for 10 s)T L 260°CStresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.1.Surface Mounted on FR4 Board using 1 in sq pad size (Cu area = 1.127 in sq [2 oz] including traces).2.Surface Mounted on FR4 Board using the minimum recommended pad size.G1S2G2D1S1D2P−CHANNEL MOSFET(Top View)PIN CONNECTION−20 V200 m W @ −2.5 V145 m W @ −4.5 V R DS(on) MAX −2.5 AI D MAX V (BR)DSS Device Package Shipping †ORDERING INFORMATIONNTGD3133PT1GTSOP6(Pb−Free)3000/Tape & Reel†For information on tape and reel specifications,including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.P−CHANNEL MOSFETTHERMAL RESISTANCE RATINGSParameter Symbol Max Unit Junction−to−Ambient – Steady State (Note 3)R q JA115°C/W Junction−to−Ambient – t ≤ 5 s (Note 3)R q JA95Junction−to−Ambient – Steady State Min Pad (Note 4)R q JA2253.Surface Mounted on FR4 Board using 1 in sq pad size (Cu area = 1.127 in sq [2 oz] including traces).4.Surface Mounted on FR4 Board using the minimum recommended pad size.MOSFET ELECTRICAL CHARACTERISTICS(T J = 25°C unless otherwise noted)Parameter Symbol Test Conditions Min Typ Max Unit OFF CHARACTERISTICSDrain−to−Source Breakdown Voltage V(BR)DSS V GS = 0 V I D = −250 m A−20−−V Drain−to−Source Breakdown VoltageTemperature CoefficientV(BR)DSS/T J−14.4−mV/°CZero Gate Voltage Drain Current I DSSV GS = 0 V, V DS = −16 V T J = 25°C−−−1.0m A T J = 85°C−−−10Gate−to−Source Leakage Current I GSS V DS = 0 V, V GS = ±12 V−−100nA ON CHARACTERISTICS (Note 5)Gate Threshold Voltage V GS(TH)V GS = V DS I D = −250 m A−0.6−0.9−1.4V Drain−to−Source On Resistance R DS(on)V GS = −4.5 V, I D = −1.9 A−95145m WV GS = −2.5 V, I D = −1.6 A−150200 Forward Transconductance g FS V DS = −5.0 V, I D = −2.5 A− 4.0−S CHARGES, CAPACITANCES & GATE RESISTANCEInput Capacitance C ISSV GS = 0 V, V DS = −10 V, f = 1.0 MHz −390−pFOutput Capacitance C OSS−75−Reverse Transfer Capacitance C RSS−37−Total Gate Charge Q G(TOT)V GS = −4.5 V, V DS = −10 V, I D = −2.2 A − 3.7 5.5nCThreshold Gate Charge Q G(TH)−0.7−Gate−to−Source Charge Q GS− 1.1−Gate−to−Drain Charge Q GD− 1.2−SWITCHING CHARACTERISTICS (Note 6)Turn−On Delay Time t d(ON)V GS = −4.5 V, V DD = −10 V,I D = −1.0 A, R G = 6.0 W − 6.7−nsRise Time t r−12.7−Turn−Off Delay Time t d(OFF)−13.2−Fall Time t f−11−DRAIN−SOURCE DIODE CHARACTERISTICSForward Diode Voltage V SD V GS = 0 V, T J = 25°C I S = −0.8 A−−0.8−1.2VReverse Recovery Time t RRV GS = 0 V,dI SD / dt = 100 A/m s, I S = −1.0 A −7.4−nsCharge Time t a− 4.8−Discharge Time t b− 2.6−Reverse Recovery Charge Q RR− 2.4−nC5.Pulse Test: pulse width v 300 m s, duty cycle v 2%.6.Switching characteristics are independent of operating junction temperatures.0246810I D , D R A I N C U R R E N T (A )V DS , DRAIN−TO−SOURCE VOLTAGE (V)Figure 1. On−Region CharacteristicsI D , D R A I N C U R R E N T (A )V GS , GATE−TO−SOURCE VOLTAGE (V)Figure 2. Transfer Characteristics00.20.40.60.82345R D S (o n ), D R A I N −T O −S O U R C E R E S I S T A N C E (W )V GS , GATE−TO−SOURCE VOLTAGE (V)Figure 3. On−Resistance versusGate−to−Source Voltage246810I D , DRAIN CURRENT (A)Figure 4. On−Resistance versus Drain Currentand Gate VoltageR D S (o n ), D R A I N −T O −S O U R C E R E S I S T A N C E (W )0.60.811.21.41.6R D S (o n ), D R A I N −T O −S O U R C E R E S I S T A N C E (N O R M A L I ZE D )T J , JUNCTION TEMPERATURE (°C)Figure 5. On−Resistance Variation withTemperatureGATE−TO−SOURCE OR DRAIN−TO−SOURCE VOLTAGE (V)Figure 6. Capacitance VariationC , C A P A C I T A N C E (p F )12345V G S , G A T E −T O −S O U R C E V O L T A G E (V )Q G , TOTAL GATE CHARGE (nC)Figure 7. Gate−to−Source andDrain−to−Source Voltage versus Total Charge110100Figure 8. Resistive Switching Time Variation versus Gate ResistanceR G , GATE RESISTANCE (W )t , T I M E (n s )0.010.11100.20.40.60.811.2Figure 9. Diode Forward Voltage versusCurrent V SD , SOURCE−TO−DRAIN VOLTAGE (V)I S , S O U R C E C U R R E N T (A )0.010.1110Figure 10. Maximum Rated Forward BiasedSafe Operating AreaV DS , DRAIN−TO−SOURCE VOLTAGE (V)I D , D R A I N C U R R E N T (A )0.010.11Figure 11. Thermal Responset, TIME (s)r (t ), N O R M A L I Z E D E F F E C T I V E T R A N S I E N T T H E R M A L R E S I S T A N C EPACKAGE DIMENSIONSTSOP−6CASE 318G−02NOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.MAXIMUM LEAD THICKNESS INCLUDES LEAD FINISH THICKNESS. MINIMUM LEADTHICKNESS IS THE MINIMUM THICKNESS OF BASE MATERIAL.4.DIMENSIONS A AND B DO NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR GATE BURRS.*For additional information on our Pb−Free strategy and solderingdetails, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.SOLDERING FOOTPRINT*DIM A MIN NOM MAX MIN MILLIMETERS0.90 1.00 1.100.035INCHESA10.010.060.100.001b 0.250.380.500.010c 0.100.180.260.004D 2.90 3.00 3.100.114E 1.30 1.50 1.700.051e 0.850.95 1.050.034L 0.200.400.600.0080.0390.0430.0020.0040.0140.0200.0070.0100.1180.1220.0590.0670.0370.0410.0160.024NOM MAX 2.50 2.75 3.000.0990.1080.118H E −−0°10°0°10°qON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

TPS61032中文资料

MAX UNIT

1.8

5.5 V

-40

85 °C

-40

125 °C

2

元器件交易网

TPS61030 TPS61031, TPS61032

SLUS534D – SEPTEMBER 2002 – REVISED APRIL 2004

ELECTRICAL CHARACTERISTICS

in a TSSOP-16 Package

APPLICATIONS

• All Single Cell Li or Dual Cell Battery Operated Products as MP-3 Player, PDAs, and Other Portable Equipment

DESCRIPTION

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

The device is packaged in a 16-pin QFN package measuring 4 mm x 4 mm (RSA) or in a 16-pin TSSOP PowerPAD™ package (PWP).

1.8 V to 5 V

C1

Input 10 µF

L1 6.8 µH

96% EFFICIENT SYNCHRONOUS BOOST CONVERTER WITH 4A SWITCH

ICP DAS PM-3133-100-MTCP 三相智能电能表快速启动指南说明书

PM-3133-100-MTCP3-Phase Smart Power MeterQuick Start GuideProduct Website:https:///pm_3133_100_mtcp.html1. IntroductionICP DAS offers PM-3133 family in a full range of Single-phase and Three-phase smart power meters for power monitoring. The products offer a rich feature set combined with easy-to-integrate communications. With its high accuracy (<0.5%, PF=1) the PM-3133 series products can be applied both on low voltage primary side and/or medium/high voltage secondary side and enable the users to obtain in real time the reliable and accurate energy consumption readings from the monitored equipment while in operation. These compact size and cost effective Power Meters are equipped with revolutionary wired clip-on CT (various types support input current up to 200A) and standard Modbus communication RS-485 protocol for easy deployment. It works with input voltages ranging 10V ~ 500V, supporting a wide range of applications.2.1. Caution & WarningThe meter contains hazardous voltages, and should never be disassembled. Failing to follow this practice will result in serious injury or death. Any work on or near energized meters, meter sockets, or other metering equipment could induce a danger of electrical shock. It is strongly recommended that all work should be performed only by qualified industrial electricians and metering specialist. ICP DAS assumes no responsibility if your electrical installer does not follow the appropriate national and local electrical codes.ICP DAS assumes no liability for any damage resulting from the use of this product. ICP DAS reserves the right to change this manual at any time without notice. The information furnished by ICP DAS is believed to be accurate and reliable. However, no responsibility is assumed by ICP DAS for its use, not for any infringements of patents or other rights of third parties resulting from its use.2.2. Product Warranty & Customer SupportICP DAS warrants all products free from defects in material and workmanship for a period of one year from the date of shipping. During the warranty period, we will, at our position, either repair or replace any product that proves to be defective.To report any defect, please contact :+310-517-9888 or *******************2.2.1. Limitation of WarrantyThis warranty does not apply to defects resulting from unauthorized modification, misuse, or use for reason other than electrical power monitoring. The supplied meter is not a user-serviceable product.3. InstallationPlease use the soft dry clothes to clean the instrument.Please do not use any chemical or detergent or volatile solvents to clean the instrument, in order to avoid any possibility of the cover damage.3.1.•Dimension: 127mm(length)× 33mm(wide)× 105mm(high)•Products come with external split type clip-on CT’s. Disconnect the CT’s or use other CT’s is highly prohibited.•Please read this operation manual carefully before using.•Please re-confirm the measure position.•Reconfirm the RST (ABC) phase sequence of the power system.•PM-3133 series can be installed as rail mounting mode or embedded, no need to drill a hole or screw to fix it (rail mounting width can up to the length of 35 mm).•Meter auxiliary power for PM-3133 series is DC +12V ~+48V.3.2. Voltage Input1. PM-3133 series: Input Voltage up to 500V. For any higher Input Voltage large than 500V,please add the PT (power transformer), and Change PT RATIO setup.2. Confirm the RST (ABC) phase sequence.3.3. Current Input1. The external CT’s are fragile, please handle with care.2. The current input of PM-3133 series is in mA range. Only the ex-factory attached CT’scan be used. The other CT’s, for example, from panel will damage the instrument due to its large current (around 5A).3. The current input of PM-3133-xxxP series is in mV range. Only the ex-factory attachedCT’s can be used. The other CT’s, for example, from panel will damage the instrumentdue to its large current (around 5A or mA).4. When more than one smart meter (PM-3133 series) are installed, please do notdisconnect the CT with its original meter and mix use with each other. Since each set of smart meter (PM-3133 series) and its attached split type clip-on CT are calibrated set by set. The mix use may cause wrong measurements.5. To install CT’s correctly, please ensure the CT lines sequences is right before clip theCT’s onto the power cable of the monitoring equipment. (Detail will be found in nextsection)6. When measuring the current, the secondary circuit of a CT should never be openedwhen a load is passing through its primary. Make sure you always open the CT clip todetach the CT before removing the terminal lines. Otherwise, it will cause severe injury.7. Please handle with extra care, especially when the operation space of CT’s is limited.8. The current direction must follow K-L marked on CT’s.9. Please select the right size CT’s for different size of monitoring equipment cables: powercable diameter <Φ10 use 60A CT,Φ10~Φ16 use 100A CT,Φ16~Φ24 use 200ACT ,Φ24~Φ36 use 300A or 400A CT。

313LBPOCZFHGA资料

•

MODEL 313L 4-20mA SERIES B ±0.5% FSO (RSS) C ±0.2% FSO (RSS) D ±0.1% FSO (RSS)

•

•

•/•/•

OPTIONS AA None (standard connector) CZ Alternate cable length (specify) ALTERNATE PRESSURE PORT FH 1/8” NPT (F) FL 1/8” NPT (M) LD Tapered inlet LJ Tapered inlet with standoff plate

with Option LJ tapered inlet with stand off plate

ORDERIห้องสมุดไป่ตู้G GUIDE

Ordering: Specify model, and pressure range and indicate modifications or accessories required. Use the following codes to identify desired item. Example 313L-B-PZ-LJ MODEL SERIES RANGE OPTIONS

TOPE Co., Ltd. Tel. (02) 8228-0658 • Fax. (02) 8228-0659 • E-mail: tope@ • Website:

SL5B-313L.02C

元器件交易网

SPECIFICATIONS

Standard

PRESSURE RANGES:

• From 0-3 through 0-100 psig (See ordering guide.)

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。