微机原理及其应用_第7章

《微机原理与应用教学资料》第七章 中断(课件)

中断源 硬件屏蔽 CPU的IF

CPU

ppt课件

7

二、中断分类

1、内部中断(软件中断)

⑴中断指令 INT n

n—中断类型码 n=0~255

⑵由CPU的运算错误引起的:

a.除法错中断: INT 0 (除数为零或商超过范围,自动产生中断)

b.溢出中断: INT 4 (当OF=1,且在程序中有INTO指令,产生中断)

b.中断请求

显然,中断请求的方法较合理

中断定义:当有外部数据输入或内部异常时,发送请求给 CPU,CPU暂时停止正在运行的程序,处理中断结束后, 返回继续运行先前的程序。

两个最重要的特点:可返回性,现场保护

ppt课件断点保护

2

一、中断概念

1、中断源:引起程序中断的事件,内部中断、外部中断

2、中断响应:对外部中断而言,INTA对INTR的响应

ppt课件

00103H 13H 5

★各个外设的中断服务子程序的入口地址集中在一个表

(中断向量表)中,CPU响应中断时,根据中断源提供 的中断类型号 i, →i×4→在中断向量表查找对应的中断 服务子程序 i 的入口地址,内容装入CS、IP,转而执行 中断服务子程序 i

ppt课件

6

4、中断优先级: ①当同时有多个中断请求,先响应优先级高的 ②当一个中断服务程序正在执行时,又一个中断源申请中断:

ppt课件

9

2、外部中断(硬件中断) ⑴不可屏蔽中断NMI

a. 上升沿触发 b. CPU必须予以响应,不能用IF屏蔽 c. INT 2,中断类型码为2,

中断向量固定存放于00008H~ 0000BH中 d. 用于发生重大故障时申请中断

微型计算机原理及应用第三版课后答案

微型计算机原理及应用第三版课后答案【篇一:《微型计算机原理及应用》课后习题答案】=txt>第一章1.1 解释题(1) 微处理器【解答】由大规模集成电路芯片构成的中央处理器(cpu),叫做微处理器。

(2) 微型计算机【解答】以微处理器为基础,配以内存储器、输入输出接口电路、总线以及相应的辅助电路而构成的计算机裸机,叫做微型计算机。

(3) 微型计算机系统【解答】微型计算机系统由硬件系统和软件系统组成。

即由微型计算机、配以相应的外部设备(如打印机、显示器、键盘、磁盘机等),再配以足够的软件而构成的系统。

(4) 单板机【解答】将微处理器、ram、rom以及i/o接口电路,再配上相应的外设(如小键盘、led显示器等)和固化在rom中的监控程序等,安装在一块印刷电路板上构成的微型计算机系统称为单板机。

(5) 运算器【解答】运算器是直接完成各种算术运算、逻辑运算的部件,主要由alu(arithmetic and logic unit,算术逻辑部件)、通用寄存器、标志寄存器等组成。

(6) 地址总线【解答】地址总线是cpu对内存或外设进行寻址时,传送内存及外设端口地址的一组信号线。

地址总线的条数多少决定了cpu的寻址能力。

(7) 数据总线【解答】数据总线是cpu与内存或外设进行信息交换时,所用的一组数据信号线。

它决定了cpu一次并行传送二进制信息的位数,反映出cpu的“字长”这个重要性能指标。

(8) 控制总线【解答】控制总线是在cpu与外部部件之间传送控制信息(如读/写命令、中断请求命令等)的一组信号线。

1-2 单片机应包括哪些基本部件?其主要应用于哪些领域?【解答】一般单片机芯片中包括微处理器、ram、rom、i/o接口电路、定时器/计数器,有的还包括a/d、d/a转换器等。

其主要应用于智能化仪器仪表及工业控制领域。

1-3 按图1-11和图1-12,写出取第二条指令操作码和执行第二条指令的过程。

【解答】1) ip的值(002h)送入地址寄存器ar;2) ip的内容自动加1,变为003h;3) ar将地址码通过地址总线送到存储器的地址译码器,经译码后选中002h单元;4) 微处理器给出读命令;5) 所选中的002h单元内容04h送上数据总线db;6) 数据总线db上的数据04h送到数据寄存器dr;7) 因是取指操作,取出的是指令操作码04h,即由dr送入指令寄存器ir;8) ir中的操作码经指令译码器id译码后,通过pla发出执行该指令的有关控制命令。

微机原理及应用(双语)知到章节答案智慧树2023年山东科技大学

微机原理及应用(双语)知到章节测试答案智慧树2023年最新山东科技大学第一章测试1.What kind of device does the MCS-51 microcontroller belong to? ( )参考答案:8-bit device2.The operation of taking a number from memory into the CPU is called ( ).参考答案:READ3.The 8951 microcontroller contains ()参考答案:EEPROM4.What is the highest address in a memory system with 16 data lines? ()参考答案:655355.What are the basic actions that a microprocessor can carry out?参考答案:Taking a number from memory (READ);Arithmeticoperations; Putting a number into memory (WRITE);Making decisions about the program route (jumps and subroutine calls);Logicaloperations (bit manipulation)第二章测试1.In internal RAM, only one of the four register banks is in used at any timewhen the program is running. ()参考答案:对2.When using an external crystal for the 8051 clock, what values of capacitorsshould be connected to it? ()参考答案:30 pF3.On the 8051 what is the storage size (in bits) of accumulator A? ( )参考答案:8 bit4.Which port has alternate function pins? ( )参考答案:Port 35.Which type of memory organization is used by the MCS-51 microcontrollers?参考答案:Harvard第三章测试1.What is the jump range of instruction LJMP? ()参考答案:64KB2.What is the addressing mode of the second operand in the instruction MOVXA, @DPTR ? ()参考答案:Indirect3.If MOV (direct) is used for address 87h which type of memory is accessed?()参考答案:SFRs4.The Stack Pointer will be decremented when a PUSH operation is made? ( )参考答案:错5.Which instruction will clear the low nibble of A if A = C5h?参考答案:ANL A, #0F0h第四章测试1.What is the jump range of instruction CJNE or DJNZ ? ()参考答案:256B2.What is the address of the second operand in the instruction:MOVC A,@A+DPTR ?Assume DPTR=1000h, A=80h. ()参考答案:1080h3.Which programming types does the assembly language belong to? ()参考答案:Linear4.What are the basci program sturcture in assembly language? ( )参考答案:Subroutine structure;Branching structure;Sequential structure;Loop structure5.Which Pseudo-instruction can put bytes in ROM memory? ( )参考答案:DB---------------------------------------------------------------------------------------------------------------------------------第五章测试1.How many interrupt sources are there in 8051 ? ()参考答案:52.The EA bit in IE register does not actually enable all interrupts, but allowsthem to be enabled separately. ()参考答案:对3.For 8051, each interrupt causes the program to jump directly to an addressat which an ISR is located. ()参考答案:对4.In an ISR (Interrupt Service Routine), which of the following instructionsmust be included? ()参考答案:Return from interrupt instruction5.How many interrupts are enabled after running this instruction “MOV IE,#05h”?参考答案:第六章测试1.For timers, which mode produces an 8-bit auto-reload timer? ()参考答案:Mode 22.Which register can we use to set up the mode of operation of Timer 0? ()参考答案:TCON3.For the serial port, which mode is an 8-bit UART? ()参考答案:Mode 14.Where is the parity bit in an RS232 packet? ()参考答案:After data bits5.How many modes can we use in a timer/counter ?参考答案:4第七章测试 the three types of bus which are used when external memory isconnected to the 8051.( )参考答案:Address bus;Control bus;Data bus2.When using external RAM, which port is used for the low address byte? ()参考答案:Port 03.If we need to expand an 8031 by adding 32Kbytes of code memory EPROM,how many address lines should be connected between the 8031 and theEPROM? ()参考答案:154.If an 8031 chip is connected to an external EPROM, Which line can generate asignal to enable reading of data from the EPROM? ()参考答案:/PSEN5.If the program is stored entirely in an external EPROM, what voltage must beapplied to the /EA PIN on the 8051? ()参考答案:0 volts第八章测试1.There are 8 analog input channels that be connected to the ADC0809. ()参考答案:对2.How many bits are required to select which analog channel is active on theADC0809? ()参考答案:33.In order to use the DAC0832, an external operational amplifier must beconnected. ()参考答案:对4.How many port pins would be used to connect a 6*4 matrix keypad to an8051 (excluding the interrupt input)? ()参考答案:105.What are the common forms that the internal wiring of the 7-segmentdisplay can take?( )参考答案:Common anode;Common cathode---------------------------------------------------------------------------------------------------------------------------------第九章测试1.In almost all cases, except completely trivial instances, the design of amicrocontroller-based system must be a top-down activity. This means that one must look first at the broad picture and then refine it down to systemsand sub-systems in both hardware and software. ()参考答案:对2.The lowest level of errors comprises those that result from incorrect use ofthe assembly language, and these are known as syntax errors. ()参考答案:对3.Which errors belong to syntax error of assembly language? ( )参考答案:Symbol not define;Wrong representation of numbers;Misspelling of instructions;Incorrect addressing modes4.The basic steps of microcontroller system design are: Requirement analysis,functional specification, design, implementation, system testing,documentation, and installation. ()参考答案:对5.The function of WDT(Watchdog Timer) is to do the syntax error detection.()参考答案:错。

《微机原理及其应用》

3.单片机-Single Chip Microcomputer 。 CPU+RAM+ROM+T/C+I/O接口+UART一块芯片

2,3 间的差别在于:

CPU不同 复杂和简单:外 存设 贮不 器同 量不同

操作平台不同

软件:编译器 和仿真系统 监控程序 汇编语言,

C51

但应用领域广泛,价格也不同。

1964-1971 第三代集成电路计算机。使用半导体存储 器,出现多终端计算机和计算机网络。

1971- 第四代大规模集成电路计算机。出现微型计算 机、单片微型计算机,外部设备多样化。

1981- 第五代人工智能计算机。模拟人的智能和 交流方式。

0.2 单片机简介与发展

0.2.1 单片机简介 单片机即单片微型计算机,是将计算机主机(CPU、 内

存和I/O接口等)集成在一小块硅片上的微型机。

单片机为工业测控而设计,又称微控制器。具有三高

优势(集成度高、可靠性高、性价比高)。

主要应用于工业检测与控制、计算机外设、智能仪器 仪表、通讯设备、家用电器等。 特别适合于嵌入式微 型机应用系统。

0.2.2 单片机发展概况

1976-1978 初级8位单片机 Intel MCS-48 系列 1978- 高档8位单片机 Intel MCS-51系列:

高级语言:用C语言来编写程序,然后通过“编译”程序

生成代码,是一种面向问题的语言,容易学习和理解。

1.4.6 单片机在控制领域中应用的优点

(1) 体积小,成本低,易于嵌入系统内部。 (2) 面向控制,能解决各类简单到复杂的控制任务。 (3) 抗干扰能力强,适应温度范围宽,可在恶劣环境下可靠工作。 (4) 易实现多机和分布式控制

单片机与嵌入式技术

微机原理及应用参考答案

参考答案第一章计算机中的数制和码制第二章计算机概述一、填空题1.82. 23.10244.25.5、11001.1、.0101B5.B、42H、66H6.41.625、29.AH7. B8.、9.-128 ~ +12710.系统软件、应用软件11.电子管、超大规模集成电路二、单选题1. A 2. C 3. D4. C 5. A 6. C三、分析简答题1.8086 CPU的总线根据其中信息传送的类型可分为几种?哪几种?答:8086 CPU的总线根据其中信息传送的类型可分为三种种,分别是:数据总线、地址总线和控制总线2.写出-25的原码、反码、补码,并将补码转换成十六进制数(设机器字长为8位)。

答:X=-25=-11001BX原码:BX反码:BX补码:B = E7H3.举例说明什么是机器数,什么是真值?答:将符号数值化了的数称为机器数。

如:-18=-10010B(真值);机器数为:B第三章半导体存贮器一、填空题1.ROM、RAM2.6个3.8、4二、单选题1. A 2. B 3. D 4. B5. C 6. C 7. B三、分析简答题1.在对存储器芯片进行片选时,全译码方式、部分译码方式和线选方式各有何特点?答:①全译码方式:存储器芯片中的每一个存储单元对应一个唯一的地址。

译码需要的器件多;②部分译码方式:存储器芯片中的一个存储单元有多个地址。

译码简单;③线选:存储器芯片中的一个存储单元有多个地址。

地址有可能不连续。

不需要译码。

四、硬件接口设计题1.答:(1)(2) 存储器类型为RAM 总容量为4K×8地址范围: 0#2000H-27FFH1# 2800H-2FFFH2.答:(9分)(1)存储器类型:RAM该系统的存储器容量为:6K×8位(或:6K字节)(2)1#芯片的地址范围:1000H ~ 17FFH2#芯片的地址范围:0800H ~ 0FFFH3#芯片的地址范围:0000H ~ 07FFH3.1)1K×42)2K×8或2KB3)地址分配范围第一组:A19~ A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0最小地址0 ~ 0 0 0 0 0 0 0 0 0 0 0 00000H~ 最大地址0 ~ 0 1 1 1 1 1 1 1 1 1 1 003FFH 第二组:0 ~ 1 0 0 0 0 0 0 0 0 0 0 00400H~0 ~ 1 1 1 1 1 1 1 1 1 1 1 007FFH《微机原理及应用》第 3 页共24 页第四章微型计算机及微处理器的结构和组成一、填空题1.BIU、EU、指令的译码和指令执行2.4、16、16、6、203.8、164.1、2二、单选题1. B 2. B三、分析简答题1.8086/8088微处理器内部有那些寄存器,它们的主要作用是什么?答:执行部件有8个16位寄存器,AX、BX、CX、DX、SP、BP、DI、SI。

微机原理ch7

第七章 可编程外围接口芯片8255A 及其应用应用本章的本章的重点重点重点::(1)掌握8255A 的工作原理及使用方法;(2)结合实验,加深理解,为今后的应用打下基础。

8255A 是一种通用的可编程并行I/O 接口芯片,通过对它的编程,芯片可工作在不同的工作方式。

在微机计算机系统中,用8255A 作接口时,通常不需附加外部逻辑电路就可直接为CPU 与外设之间提供数据通道,因此它得到广泛的应用。

本章介绍8255A 的基本工作原理和应用实例。

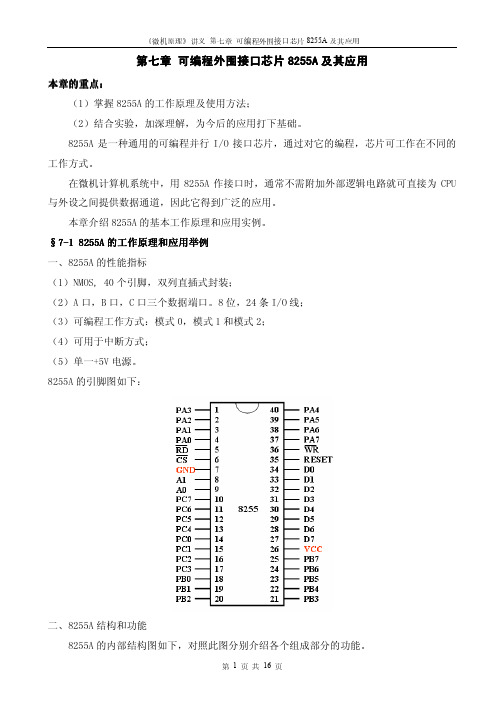

§7-1 1 8255A 8255A 的工作原理的工作原理和应用举例和应用举例和应用举例 一、8255A 的性能指标(1)NMOS, 40个引脚,双列直插式封装;(2)A 口,B 口,C 口三个数据端口。

8位,24条I/O 线; (3)可编程工作方式:模式0,模式1和模式2; (4)可用于中断方式; (5)单一+5V 电源。

8255A 的引脚图如下:二、8255A 结构和功能8255A 的内部结构图如下,对照此图分别介绍各个组成部分的功能。

1、数据端口A、B和C8255A内部包含3个8位的输入输出端口A、B和C,通过外部的24根线与外设交换数据或通信联络(其中C口被分成C口上半部分和C口下半部分),C口又可分为两个4位端口。

下面介绍每个数据端口在不同的工作方式下的具体功能。

工作方式工作方式 A口 B B 口口C口0 基本输入输出输出锁存输入三态基本输入输出输出锁存输入三态基本输入输出输出锁存输入三态1 应答式输入输出输入输出均锁存应答式输入输出输入输出均锁存作为A口、B口的控制位及状态位2 应答双向输入输出输入输出均锁存作为A口的控制位及状态位2、A组和B组控制逻辑两组根据CPU的编程命令控制8255A工作电路。

它们内部有控制寄存器,用来接收CPU的命令字,然后决定两组的工作方式或对C口每一位执行置位/复位的操作。

3、数据总线缓冲器一个双向三态8位缓冲器,用做8255A和系统数据总线之间的接口。

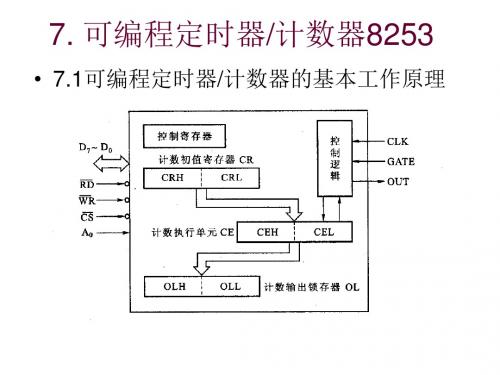

微机原理与接口技术_第7章8253

§7-1 8253的工作原理 ——8253的内部结构和引脚信号

然后,开始递减计数。即每输入一个时钟脉冲,计数

器的值减1,当计数器的值减为0时,便从OUT引脚输出 一个信号。输出信号的波形主要由工作方式决定,同 时还受到从外部加到GATE引脚上的门控信号控制,它 决定是否允许计数。 当用8253作外部事件计数器时,在CLK脚上所加的计 数脉冲是由外部事件产生的,这些脉冲的间隔可以是 不相等的。 如果要用它作定时器,则CLK引脚上应输入精确的时 钟脉冲。这时,8253所能实现的定时时间,决定于计 数脉冲的频率和计数器的初值,即 定时时间=时钟脉冲周期tc×预臵的计数初值n

16

§7-1 8253的工作原理 ——8253的内部结构和引脚信号 ③引脚 8253的3个计数器都各有3个引脚,它们是:

CLK0~CLK2:计数器0~2的输入时钟脉冲从这里输

入。频率不能大于2MHz。

OUT0~OUT2:计数器0~2的输出端。

GATE0~GATE2:计数器0~2的门控脉冲输入端。

4

第七章 可编程计数器/定时器8253及其应用 ——概述 2. 不可编程的硬件定时 555芯片是一种常用的不可编程器件,加上外接电阻和电 容就能构成定时电路。这种定时电路结构简单,价格 便宜,通过改变电阻或电容值,可以在一定的定时范 围内改变定时时间。但这种电路在硬件已连接好的情 况下,定时时间和范围就不能由程序来控制和改变, 而且定时精度也不高。 3. 可编程的硬件定时 ①可编程定时器/计数器电路利用硬件电路和中断 方法控制定时,定时时间和范围完全由软件来确 定和改变,并由微处理器的时钟信号提供时间基 准,这种时钟信号由晶体振荡器产生,故计时精

12

§7-1 8253的工作原理 ——8253的内部结构和引脚信号 8253输入信号组合的功能表

微机原理习题集第七章存贮器

第七章内存储器一、填空题1、内存储器是计算机系统中的装置,用来存放和。

2、CPU对RAM存贮器进行读/写操作时,应送出的方向控制命令有和命令。

3、Intel 2114 RAM存贮芯片引脚中用于片选的控制引脚为,用于读/写控制引脚为。

4、Intel 4116 RAM芯片容量为2K 8,访问该芯片须用根地址线。

5、存贮芯片存贮的信息会,必须定时刷新,刷新的时间间隔为。

6、存贮器分为、、、。

7、逻辑地址为2000H:1234H的存储单元的物理地址是。

8、8086CPU写入一个规则字,数据线的高8位写入存储体,低8位写入存储体。

9 、将存储器与系统相连的译码片选方式有法和法。

10、对6116进行读操作,6116引脚= ,= ,= 。

二、单项选择题1、随机存贮器即RAM是指()A.存贮单元中所存信息是随机的。

B.存贮单元中的地址是随机的。

C.用户的程序和数据可随机的放在内存的任何地方。

D.存贮器中存取操作与时间存贮单元物理位置顺序无关。

2、CPU对主存进行操作,下面哪种说法是不能实现的()A.按地址并能读/写一个字节代码B.按地址串行1位1位进行读/写操作C.按地址并行读/写一个字长代码D.按地址进行并行读出而不能实现并行写入3、动态存贮器刷新,下面哪种说法正确()A.刷新可在CPU执行程序过程中进行B.刷新在外电路控制下,定时刷新,但刷新时,信息不读出C.在正常存贮器读操作时也会发生刷新,可防止刷新影响读出信息,故读操作时,应关闭电路工作。

D.刷新过程一定伴随着信息输出,无法控制,故刷新时不要进行读出操作。

4、用4K×8的存贮芯片,构成64K×8的存贮器,需使用多少4K×8的存贮芯片,正确答案为()A.128片B.16片C.8片D.32片5、在存贮器读周期时,根据程序计数器PC提供的有效地址,使用从内存中取出()6、动态存贮器的主要缺点是()A.存贮容量少B.存取速度低C.功耗大D.外围电路复杂7、动态RAM芯片容量为16K×1位,要构成32K字节的RAM存贮器,需要该芯()A.4片B.8片C.16片D.32片8、堆栈操作时,段地址由()寄存器指出,段内偏移量由()寄存器指出。

微型计算机原理及应用第三版课后答案

微型计算机原理及应用第三版课后答案【篇一:《微型计算机原理及应用》课后习题答案】=txt>第一章1.1 解释题(1) 微处理器【解答】由大规模集成电路芯片构成的中央处理器(cpu),叫做微处理器。

(2) 微型计算机【解答】以微处理器为基础,配以内存储器、输入输出接口电路、总线以及相应的辅助电路而构成的计算机裸机,叫做微型计算机。

(3) 微型计算机系统【解答】微型计算机系统由硬件系统和软件系统组成。

即由微型计算机、配以相应的外部设备(如打印机、显示器、键盘、磁盘机等),再配以足够的软件而构成的系统。

(4) 单板机【解答】将微处理器、ram、rom以及i/o接口电路,再配上相应的外设(如小键盘、led显示器等)和固化在rom中的监控程序等,安装在一块印刷电路板上构成的微型计算机系统称为单板机。

(5) 运算器【解答】运算器是直接完成各种算术运算、逻辑运算的部件,主要由alu(arithmetic and logic unit,算术逻辑部件)、通用寄存器、标志寄存器等组成。

(6) 地址总线【解答】地址总线是cpu对内存或外设进行寻址时,传送内存及外设端口地址的一组信号线。

地址总线的条数多少决定了cpu的寻址能力。

(7) 数据总线【解答】数据总线是cpu与内存或外设进行信息交换时,所用的一组数据信号线。

它决定了cpu一次并行传送二进制信息的位数,反映出cpu的“字长”这个重要性能指标。

(8) 控制总线【解答】控制总线是在cpu与外部部件之间传送控制信息(如读/写命令、中断请求命令等)的一组信号线。

1-2 单片机应包括哪些基本部件?其主要应用于哪些领域?【解答】一般单片机芯片中包括微处理器、ram、rom、i/o接口电路、定时器/计数器,有的还包括a/d、d/a转换器等。

其主要应用于智能化仪器仪表及工业控制领域。

1-3 按图1-11和图1-12,写出取第二条指令操作码和执行第二条指令的过程。

【解答】1) ip的值(002h)送入地址寄存器ar;2) ip的内容自动加1,变为003h;3) ar将地址码通过地址总线送到存储器的地址译码器,经译码后选中002h单元;4) 微处理器给出读命令;5) 所选中的002h单元内容04h送上数据总线db;6) 数据总线db上的数据04h送到数据寄存器dr;7) 因是取指操作,取出的是指令操作码04h,即由dr送入指令寄存器ir;8) ir中的操作码经指令译码器id译码后,通过pla发出执行该指令的有关控制命令。

微机原理与应用第七章

表达式:由操作数和运算符组成的式子

⑴算术运算符: +、-、*、/、MOD(除法取余)、SHL(左移)、 SHR(右移)

例: MOV AX,100*4+5

⑵ 逻辑运算符:AND、OR、NOT、XOR

;AX=405

按位运算

关系运算结果总是 一个数值。若关系不 成立,则结果为0,若 关系成立,则结果 为0FFFFH

⑴ 定位方式(定位类型)

书(P162)

定位类型指出了对当前段起始地址的要求,有4个选项

PAGE ——指定起始地址的低8位是0,即其值能被256整除(称页边界) PARA ——指定起始地址的低4为是0,即其值能被16整除(称段边界)

例1:

DSEG1 SEGMENT DATA_B DB 10,5,10H DATA_W DW 100H,-4 DATA_D DD 0FFFBH DSEG1 ENDS

DSEG1: DATA_B

0AH 05H 10H

10 5

10H 100H -4

DATA_W

00H 01H FCH

汇编后的内存分配情况 如右图所示。

先定义

后引用

⑴ 字节定义语句DB

格式:[名字] DB <表达式或数据项表> 功能:表达式值或项表中的每一项是一个字节数, 符号地址 它们从符号名地址开始按字节连续存放。

例:COUNT DB 100 COUNT→ DB 0DH,0AH,’$ ’ VARW DB ?,6,?,?

可以使用重复操作符DUP如: BUFFER DB 8 DUP(0)

⑺ 汇编运算符的优先级

括号 LENGTH、SIZE PTR、OFFSET、…. HIGH、LOW *、/、MOD、SHL、SHR +、例:设SSY=2050H EQ、NE、LT、LE、GT、GE MOV AL,LOW 3080H ;AL=80H NOT MOV AH,HIGH SSY ;AH=20 AND MOV CL, LOW 3A4BH ;CL=4BH OR、XOR

《微机原理及应用》复习精华

EPROM:可紫外线擦除的可编程 ROM

EEPROM:可电擦除的可编程 ROM

2.典型存储器芯片及容量

SRAM

EPROM

E 2 PROM

6264: 8K×8bit

2764: 8K×8bit

28C64: 8K×8bit

62128:16K×8bit

27128:16K×8bit

28C128:16K×8bit

2.8086 与 8088 主要区别: ①外部数据总线位数的差别:8086 是 16 位,8088 是 8 位; ②指令队列容量的差别:8086 指令队列可容纳 6 个字节,8088 只能容纳 4 个字节;

《微机原理及应用》复习精华 第 3 页

淮阴工学院

科学男孩 /kexuenanhai

______

______

连),WE是★★★(一般与 CPU 的WR直接相连),还有地址线 A..和数据线 D..(这

两者一般与 CPU 对应连接即可)。

③当还有 74LS373、Intel8282 等芯片时,一般将 CPU 的地址锁存允许信号

ALE 接至芯片的使能端,将 CPU 的 AD7~AD0 接至芯片的 I7~I0,将芯片的 O7~O0 接至存储器的 A7~A0 .

62256:32K×8bit

27256:32K×8bit

《微机原理及应用》课后答案(黄冰 覃伟年 著)习题参考答案

《微机原理》习题参考答案第一章绪论1.2①[+65]10=01000001B [+65]补=[+65]原=01000001B②[+115]10=01110011B [+115]补=[+115]原=01110011B③[-65]10=11000001B [-65]补=10111111B[-115]10=11110011B [-115]补=10001101B方法:正数的原码、反码、补码相同负数的补码在原码的基础上除过符号外,先取反,再加1。

1.3①[+120]10=0000000001111000B [+120]补=[+120]原=000000001111000B②[-120]10=1000000001111000B [-120]补=1111111110001000B③[+230]10=0000000011100110B [+230]补=[+230]原=0000000011100110B④[-230]10=1000000011100110B [-230]补=1111111100011010B方法:与上题相同,只是扩展了位数,用16位表示1.4①55 (00110111)②89 (01011001)③-115 (11110011)④-7总结:知道补码,求原码(或数值)的方法:如果是正数,直接转换。

如果是负数用以下三种方法:①根据[[X]补]补=X 求得例如10001101 各位取反11110010 加一11110011转换-115②求补的逆运算例如:11111001 先减一11111000 各位取反10000111 转换-7③-(模+补码转换结果)例如:10001101转换-13模+补码转换结果128-13=115 加负号–1151.9本题问题不太明确例如:如果手边有手册或是知道产品的型号,就可从手册中查到微处理器的处理位数。

也可以根据系统总线得知。

因为系统总线是公共的数据通道,表现为数据传输位数和总线工作时钟频率。

微机原理及应用第7章

7.2 中断处理过程及中断源识别

中断处理过程

四个步骤:

中断请求 中断响应 中断服务 中断返回

以下以外部中断为主介绍这四个步骤。

1)中断请求

外设接口(中断源)发出中断请求信号,送到 CPU的INTR或NMI引脚;

中断请求及响应 中断处理 中断返回

中断的用途

CPU的中断功能的实现带来了以下好处: 1、同步处理 2、实现了实时处理 3、多道程序或多重任务的运行 4、突发事件处理

中断的定义

CPU执行程序时,由于发生了某种随机的事件 (外部或内部),引起CPU暂时中断正在运行的程 序,转去执行一段特殊的服务程序(称为中断服 务程序或中断处理程序),以处理该事件,该事 件处理完后又返回被中断的程序继续执行,这一 过程称为中断。

中断请求信号:边沿请求,电平请求 例如,NMI为边沿请求,INTR为电平请求

中断请求信号应保持到中断被处理为止; CPU响应中断后,中断请求信号应及时撤销。 在8086/8088系统中,外设的中断要经过8259A

可编程中断控制器(PIC)的排队判优后向CPU发出: (I/O接口)n1 → PIC → CPU

中断矢量法。由中断源提供中断类型号,CPU根 据类型确定中断源。(8086/8088即采用此种方 法)

1.查询中断(软件识别中断优先权)

INTR

≥1 ...

AB

A15~A0

译码

器 IOR

D7~D0

DB

G 缓冲

器

中断源1 ...

中断源8

软件查询法判优流程

读中断请求寄存器

微机原理-第7章 汇编语言与汇编程序5 常用DOS系统功能调用及BIOS功能调用-文档资料

常用DOS系统功能调用

① ② ③ ④ ⑤ ⑥

单字符输入 ( 01H、07H、08H功能 ) 显示单字符 ( 02H、05H功能 ) 单字符输入或显示( 06H功能 ) 字符串输入 ( 0AH功能 ) 显示字符串 ( 09H功能 ) 检测键盘状态 ( 0BH功能 )

① 单字符输入 (01H、07H、08H功能)

max DB 11 DB ? DB 11 DUP(?)

SEGMENT ASSUME CS:code, DS:data MOV AX , data ;置缓冲区地址于DS:DX

ROM BASIC ROM BIOS ( a)

FFFFH

ROM BASIC ROM BIOS (b)

FFFFH

图 7.5-1 PC-DOS (a) DOS启动后 (b) 执行程序装入后

软件中断分类

DOS中断

中断类型号

20H~3FH 为用户程序和系统程序提供磁盘读写、程 序退出、系统功能调用等功能。

③ 单字符输入或显示 (06H功能)

入口参数:DL = 0FFH,表示从键盘输入字符

或 DL ≠ 0FFH,表示DL中是要显示字符的ASCII 码

功能号:

类型号:

AH = 06H

21H

出口参数:若ZF=0时,表示有键按下,将字符的ASCII码

送入寄存器AL, AL=输入字符。 若标志ZF=1时,表示无键按下,寄存器AL中不 是键入字符ASCII码, AL=0 。

② 显示单字符 (02H、05H功能)

(a)2号系统功能调用

入口参数:DL = 要显示字符的ASCII 码 功能号: AH = 02H 类型号: 21H 出口参数:无 实现功能:显示指定字符,光标右移。

(完整word版)《微机原理及应用》习题答案

(完整word版)《微机原理及应用》习题答案《微机原理及应用》习题答案教材:《80X86/Pentium微型计算机原理及应用》答案第一章计算机基础1-3(1)01101110 真值=110(2)10001101 真值=-131-4(1)+010111[+010111]原=[+010111]反=[+010111]补=00010111 (2) +101011[+101011]原=[+101011]反=[+101011]补=00101011 (3) –101000[-101000]原=10101000 [-101000]反=11010111 [-101000]补=11011000(4) -111111[-111111]原=10111111 [-111111]反=11000000 [-111111]补=110000011-6(1) [x1+y1]补=[x1]补+ [y1]补=00010100+00100001=00110101(2)[x2-y2]补=[x2]补+ [-y2]补=11101100+00100001=000011011-7 (1)85+60解:[-85]补=10101011 [60]补=00111100[-85]补+[60]补=10101011+00111100=11100111 (11100111)补=10011001 真值=-25CS=0,CP=0, CS⊕CP=0 无溢出(4)-85-60[-85]补=10101011 [-60]补=11000100[-85]补+[-60]补=10101011+11000100=101101111 CS=1, CP=0 CS⊕CP=1 有溢出1-8(1) [x]补+ [y]补=01001010+01100001=10101011 CS=0, CP=1 CS⊕CP=1 有溢出(2) [x]补- [y]补=[x]补+ [-y]补=01001010- 01100001=01001010+10101010=100010110CS=1, CP=1 CS⊕CP=0 无溢出1-9(1) (127)10=(000100100111)BCD(2) (74)H=(116)10=(000100010110)BCD1-10(1) 41H 代表A(2) 72H 代表r(3) 65H 代表e(4) 20H 代表SP1-14(1) 69.57(69.57)10=(1000101.100)B=0.1000101100 X 27=0.1000101100 X 2+111浮点规格数为011101000101(2)-38.405(-38.405)10=(-100110.011)B-100110.011= -0.100110011 x 26 = - 0.100110011 x 2110浮点规格数为011011001100(3) - 0.3125(-0.3125)10=(-0.0101)2=(-0.101)2 x 2-001浮点规格数为1111110100001.+0.008342.(+0.00834)10=(0.000000100010001)2=(0.100010001)2 x 2-1103.浮点规格数为1010010001004.1-155.(1) (69.57)10=(1000101.10010001111010111)26. =(1.00010110010001111010111)2 x 21107. p=6+127=133=(10000101)28.单精度浮点数为010000101000101100100011110101119.(2)(-38.405)10=(-100110.011001111010111000)210. = - (1.00110011001111010111000)2 x 210111. p=5+127=132=(10000100)212.单精度浮点数为1100001000011001100111101011100013.(3) (-0.3125)10=(-0.0101)2=(-1.01)2 x 2-1014. p=-2+127=125=(1111101)215.单精度浮点数为10111110101000000000000000000000第二章 80X86/Pentium 微处理器2-3IO/M DT/R DEN RD WR读存储器 0 0 0 0 1写存储器 0 1 0 1 02-17PA=CS x 16+IP IP的范围为0000H~FFFFH 而CS为A000H因此PA的范围即现行代码段可寻址的存储空间范围为A0000H~AFFFFH2-201234ABCDH=00010010001101001010101111001101 BPA=SS x 16+SP=A0000H+0100H=A0100H栈顶SP=0100H-4=00FCH11001101 A00FCH101010110011010000010010 A0100F2-21(1) 1278H+3469H=0001 0010 0111 1000+0011 0100 0110 1001=0100 0110 1110 0001SF=0 ZF=0 AF=1 PF=1 CF=0 OF=0(2) 54E3H-27A0H=0101 0100 1110 0011+1101 1000 0110 0000=1 0010 1101 0100 0011SF=0 ZF=0 AF=1 PF=0 CF=0 OF=0当进行16位或8位加或减运算时,若最高位产生进位或借位时,将CF置1,否则为0,当进行带符号数补码运算时,运算结果超出了机器所能表示的数值范围,就产生溢出,将OF置1,否则OF置0,即OF用来表示有符号数运算的溢出,而CF则用来表示无符号数运算的溢出。

微机原理及应用教学大纲

微机原理及应用教学大纲《微机原理及应用》是计算机类、电气信息类等专业的核心课程,其从微型计算机的芯片级构成着眼,讲解微处理器、存储器和典型接口芯片及其编程使用方法。

通过本课程的学习,使学生能够更加深刻的理解计算机系统软硬件协同工作原理,建立计算机的系统观,具备微型计算机系统的软/硬件设计开发能力。

课程概述本课程是计算机类、电气信息类等专业的一门重要专业课,是一门面向应用、具有很强的实践性与综合性的课程。

本课程以Intel 8086/8088为起点,逐步介绍80286、80386、80486以及Pentium CPU,使学生能够层层深入,逐步掌握各种微处理器的结构、原理以及它们之间的区别和联系。

在接口技术部分,主要讲述微型计算机中常用的中断控制器、并行/串行接口、计数器/定时器和A/D、D/A 转换器等典型接口电路及其编程使用方法。

本课程内容深入浅出、注重系统性、先进性和实用性,是学生学习和掌握微型计算机系统的基本组成、工作原理、接口及其应用技术的重要课程。

授课目标本课程是计算机类、电气信息类等专业的一门重要专业课,通过对本课程的学习,学生将系统地从理论和实践上掌握微型计算机的基本组成、工作原理及常用接口技术,建立微机系统整体概念,使学生具备微机应用系统软、硬件开发的初步能力。

课程大纲第一章微型计算机基础1. 微型计算机系统的组成与性能指标2. 微型计算机中常用数制和编码第一章微型计算机基础作业第一章微型计算机基础单元测试第二章16位和32位微处理器1. 8086/8088CPU的内部结构2. 8086/8088CPU的引脚信号和功能3. 8086/8088 系统的工作模式和典型时序4. 8086/8088CPU的存储器组织5. 32位微处理器第二章16位和32位微处理器单元测验第二章16位和32位微处理器作业第三章16位/32位微处理器指令系统1. 指令的基本格式和寻址方式2. 数据传送类指令3. 算术运算类指令4. 逻辑运算与移位类指令5. 串操作类指令6. 控制转移类指令与处理器控制类指令第三章16位/32位微处理器指令系统单元测验第三章16位/32位微处理器指令系统作业第四章汇编语言程序设计1. 汇编语言概述及源程序格式2. 伪指令3. 顺序和分支4. 循环结构5. 子程序结构及系统功能调用第四章汇编语言程序设计单元测验第四章汇编语言程序设计作业第五章存储器1. 存储器概述2. 半导体存储器芯片结构及使用3. 存储器容量的扩展第五章存储器单元测验第五章存储器作业第六章输入输出与中断1. 输入/输出接口概述2. CPU与外设之间的数据传送方式3. 中断及其处理过程4. 8086/8088的中断与服务程序设计5. 8259A的内部结构及工作方式6. 8259A的编程及应用第六章输入输出与中断单元测试第六章输入输出与中断作业第七章并行接口1. 简单并行接口2. 8255A的内部结构及控制字3. 8255A的工作方式4. 8255A的编程及应用5. 键盘接口6. LED显示器接口第七章并行接口单元测试第七章并行接口作业第八章串行接口1. 串行通信基础2. 可编程串行通信接口芯片8251A 第八章串行接口单元测验第八章串行接口作业第九章计数器/定时器1. 8253的内部结构及控制字2. 8253的初始化编程及工作方式3. 8253的应用第九章计数器/定时器单元测验第九章计数器/定时器作业第十章数/模和模/数转换1. 数/模(D/A)转换器基础2. DAC0832及接口电路3. 模/数(A/D)转换器基础4. ADC0809及接口电路第十章数/模和模/数转换单元测试第十章数/模和模/数转换作业第十一章总线技术1. 总线技术第十一章总线技术单元测验第十一章总线技术作业预备知识数字电子技术基础、计算机组成原理参考资料教材:李云、曹永忠、于海东等,微型计算机原理及应用(第二版),北京:清华大学出版社,2015必读书目:[1] 葛桂萍等,微机原理学习与实践指导(第二版)[M].北京:清华大学出版社,2015[2] 戴梅萼,史嘉权,微型计算机技术及应用(第4版)[M].北京:清华大学出版社,2008选读书目:[1] 李继灿,新编16、32位微型计算机原理及应用(第4版)[M].北京:清华大学出版社,2010[2] 余春暄等,80X86/Pentium微机原理及接口技术(第2版)[M].北京:机械工业出版社.2014[3] 钱晓捷等,80X86/Pentium微机原理及接口技术-基于IA-32处理器和32位汇编语言(第4版)[M].北京:机械工业出版社.2011。

第7章8253微机原理及应用

MOV AL,37H;写入方式控制字 OUT 83H,AL MOV AL,50H;写入计数初始值低8位 OUT 80,AL MOV AL,12H ;写入计数初始值高8位 OUT 80H,AL

(3)读计数值 ①以普通对计数器端口读的方法取得当前计数值 ②锁存计数器的当前值(RL1RL0=00)

7.2.4 8253-5的应用举例 一、用8253-5监视一个生产流水线 1.硬件设计

INT 1 +5V

2.5MHz 8255PA0

OUT0 CLK0

GATE0

8253

CLK1 GATE1

OUT1

• 方式2:可变频率脉冲发生器

(MODE 2) CLOCK

WRn#

OUTPUT

n=4

n=3

4 3 2 1 0(4) 3 2 1 0(3) 2 1 0

0(3) OUTPUT

3 2 1 0(3) 2 1 0(3) 2 1 0

GATE (RESET)

方式3—方波速率发生器 方式3的输出都是周期性的,方式3在计数过程中输出

(2)计数器1用来产生动态存储器刷新操作的定 时控制,它工作于方式2,计数初值为18, OUT1端输出一个负脉冲序列,其脉冲周期约 为18 ÷1.1931816MHz=15.08(μs)。该输出将 作为动态刷新控制器8237A中通道0的DMA请 求信号DREQ0,控制DMA控制器完成每隔 15.08(μs)对系统中的动态存储芯片进行一次 刷新操作

– 选通输入(门控输入)GATE——用于启动或禁止计数器的 操作,以使计数器 和计测对象同步。

微机原理与应用第7章2-3节2010SGQ

③ CPU响应中断 4、CPU执行完当前指令

CPU在执行当前指令最后一个时钟周期时采样INTR,然后 响应中断。

IF=1

INTR=1

二、CPU对中断的响应

执行一条指令 取下一条指令 N 指令结束 INTR=1 关中断 断点保护 转中断服务 1、CPU发INTA同 时,自动关中断 2、CPU自动将 断点CS,IP,PSW 入栈 3、CPU将中断 源提供的中断类型 码形成中断服务入 口地址,送CS,IP 执行PUSH指令

三、 中断传送

(无条件、查询传送都需要CPU的等待或不断查询,

使CPU的效率降低。)

中断传送:外设需要传送数据时,申请中断;当CPU允许 中断,在中断服务程序中执行IN /OUT指令;然后返回主 程序。 主程序 中断服务程序

启动外设

外设准备好 输入设备Ready=1 输出设备Busy=0 中断请求 中断响应

流程

五、传送方式的比较

无条件传送:慢速外设需与CPU保持同 步 查询传送: 简单实用,效率较低 中断传送:外设主动,可与CPU并行工 作,但每次传送需要大量额外时间开销 DMA传送:DMAC控制,外设直接和存 储器进行数据传送,适合大量、快速数 据传送

第三节 中断

中断处理的过程: 外设中断源 申请中断

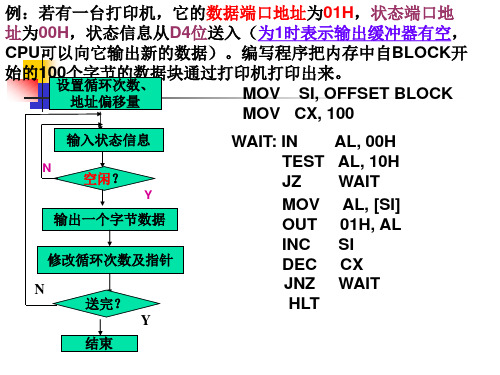

输入状态信息

N

空闲?

Y

输出一个字节数据 修改循环次数及指针 N 送完? Y 结束

WAIT: IN TEST JZ MOV OUT INC DEC JNZ HLT

AL, 00H AL, 10H WAIT AL, [SI] 01H, AL SI CX WAIT

习题:若有一个CRT(阴极射线管显示器)终端,它的输入输出数 据的端口地址为01H,状态端口的地址为00H,其中D7位为1时表 示输出缓冲器有空,CPU可以向它输出新的数据;D6位为1时,表 示输入数据有效,CPU可以把它输入。 实现:(1)从终端上输入100个字节的字符,送入到以BUFFER 开始的内存单元。 (2)把内存中自BLOCK开始的100个字节的数据块通过终端显示 出来。

微机原理及其应用_第7章

2. A组和B组控制部件 A组和 组和B

A组 组

A口:PA0~PA7 C口的高4位:PC4~PC7 B口:PB0~PB7 C口的低4位:PC0~PC3

B组 组

A组,B组的控制寄存器, 组的控制寄存器, 接收来自数据总线的控制字, 接收来自数据总线的控制字, 并根据控制字确定各端口的工 作状态和工作方式。 作状态和工作方式。

8255A 8255A 可 编 程 外 围 设 备 接 口 (Programmable Peripheral Interface, 简写 为PPI) ,其内部结构如图所示。 其内部结构如图所示。

A组控制 部件 双向 D7~D0

A1 A0

RD WR

A组 端口A 8位 A组 端口C (高4位) B组 端口C (低4位) B组 端口B 8位

图7.4 8255A 置位/复位控制字格式

关于控制字要说明几点: 关于控制字要说明几点:

(1) 设置方式控制字时 , A 口 、 B 口作为 设置方式控制字时, 整体设置, 整体设置 , 而 C 口要分成上 、 下两部分 分别 口要分成上、 下两部分分别 设置。三个端口的工作方式由一个控制字规 设置。三个端口的工作方式由 一个控制字规 定。 (2) C口按位置位/复位控制字不是送到C 口按位置位/复位控制字不是送到C 口地址,而是送到控制寄存器地址; 口地址,而是送到控制寄存器地址;且一个 控制寄存器地址 控制字只能使C 一位置位或复位。 控制字只能使C口一位置位或复位。

方式0控制字具体格式如图7.5所示

图7.5 8255A工作方式0控制字格式

由控制字中D 由控制字中D4D3D1D0 等4位的不同取值, 位的不同取值, 可定义方式0 16种工作方式的组合。 可定义方式0的16种工作方式的组合。 方式0 方式0中,端口C被分成两个4位 端口C被分成两个4 端口,它们可被定义为输入或输出端口, 端口,它们可被定义为输入或输出端口, CPU与 个端口之间交换数据, CPU与3个端口之间交换数据, 可直接由CPU执行 和OUT指令来完成 执行IN 可直接由CPU执行IN和OUT指令来完成

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

INTR:中断请求信号。当输出设备从 8255A端口中提取数据,从而发出ACK 信号 后,8255A向CPU发出中断请求信号,以便 CPU再次输出数据。 INTE:中断允许信号。通过软件设 置可控制A、B口的中断允许与否: PC6置1,允许A口中断 PC2置1,允许B口中断

图7.8 方式1输出控制字格式

(3) 方式控制字和按位置位/复位控制字均 方式控制字和按位置位/ 控制寄存器地址 写入同一个控制寄存器地址, 写入同一个 控制寄存器 地址 , 二者通过最高 位D7来区别。D7=1为方式控制字,D7=0为按 来区别。 方式控制字 控制字, 位置位/复位控制字。 置位/复位控制字 控制字。

2. 工作方式

37 18

PA0

. . .

A

D7 控 制 线 A0 A1

CS RD WR

27 9 8 6 5 36 35 8255A PPI

PA7 PB0

. . .

B

RESET

电 源 线 VCC GND CPU

25 14 15 16 17 13 12 11 10

PB7 PC0

. . .

C

PC7

图7.2 8255A引脚

(1) 方式 —— 基本输入 输出方式 基本输入/输出方式 ) 方式0 方式0 是一种基本输入输出工作方式, 方式 0 是一种 基本 输入输出工作方式 , 它 基本输入输出工作方式 的 24条 I/O 线可以全部都用作传送数据 , 不设 24 条 I/O线可以全部都用作传送数据 线可以全部都用作传送数据, 置应答信号线,常用于无条件传送 置应答信号线,常用于无条件传送,输出有锁 无条件传送, 存,输入只有缓冲能力而无锁存功能。 输入只有缓冲能力而无锁存功能。

图7.6工作方式1输入控制字格式

方式1选通输出 ② 方式 选通输出 当端口A或端口B为方式1输出时,各 指定PC的3条线作为8255A与外设及CPU之 间应答(握手)信号。下图为方式1选通输出 操作的内部结构图。

方式1输出端口A

PA7~0

方式1输出端口B

PB7~0

OBFA

ACK A

PC7 INTEA PC6 PC3 PC4,5 WR

(3) 工作方式 工作方式2—双向选通输入 输出方式 双向选通输入/输出方 双向选通输入 方式2只允许A组采用,此时端口A 变为双向,允许数据在同一组8条线上 发送和接收。

端口B 端口B和C: 都包含一个8位数据输入缓冲器和 都包含一个8 一个8 位的数据输出锁存器/ 缓冲器, 一个 8 位的数据输出锁存器 / 缓冲器 , 输出数据能 锁存, 锁存,输入数据不锁存。 端口C 可分成两个4 位端口, 端口 C: 可分成两个 4 位端口 , 分别定义为输 入或输出端口, 还可定义为控制、 状态端口, 入或输出端口 , 还可定义为控制 、 状态端口 , 配 合端口A和端口B工作。 合端口A和端口B工作。

8255A包括四大部分: 8255A包括四大部分:数据总线缓冲器、 读写控制部件、A组和B组控制部件、端口 A、B、C。

1.并行输入/输出端口PA、PB、PC 1.并行输入 输出端口PA、PB、 并行输入/

端口A 包含一个8 位数据输出 端口 A : 包含一个 8 位数据输 出 锁存 器/缓冲器和一个8位数据输入锁存器,输 缓冲器和一个8位数据输入锁存器, 入输出数据均受到锁存。 入输出数据均受到锁存。

方式0控制字具体格式如图7.5所示

图7.5 8255A工作方式0控制字格式

由控制字中D 由控制字中D4D3D1D0 等4位的不同取值, 位的不同取值, 可定义方式0 16种工作方式的组合。 可定义方式0的16种工作方式的组合。 方式0 方式0中,端口C被分成两个4位 端口C被分成两个4 端口,它们可被定义为输入或输出端口, 端口,它们可被定义为输入或输出端口, CPU与 个端口之间交换数据, CPU与3个端口之间交换数据, 可直接由CPU执行 和OUT指令来完成 执行IN 可直接由CPU执行IN和OUT指令来完成

A1 A0: 端口选择信号

当A1A0=00时 选择端口A =00时 选择端口A 当A1A0=01时 选择端口B =01时 选择端口B 当A1A0=10时 选择端口C =10时 选择端口C 当A1A0=11时 选择控制端口 =11时

表7.1 8255A的读写操作控制

7.2 8255A的控制字及其工作方式

(a)端口A方式1输入

(b)端口B方式1输入

图7.7方式1输入端口状态

STB:选通信号。由外设输入,有效时,将 外设输入的数据锁存到所选端口的输 入锁存器中。 IBF:输入缓冲器满信号,向外设输出,有效时, 表示由输入设备输入的数据已占用该端口 的输入锁存器,它实际上是对STB的回答信 号。

INTR:中断请求信号,INTR在、IBF均 为高时被置为高电平,即:当选通信号结束、 已将一个数据送进输入缓冲存储器中,并且输 入缓冲区满信号已为高电平时,8255A向CPU 发出中断请求信号 INTE:中断允许信号,它是通过端口 PC4(端口A)或PC2(端口B)的位来编程的内部 位。

图7.4 8255A 置位/复位控制字格式

关于控制字要说明几点: 关于控制字要说明几点:

(1) 设置方式控制字时 , A 口 、 B 口作为 设置方式控制字时, 整体设置, 整体设置 , 而 C 口要分成上 、 下两部分 分别 口要分成上、 下两部分分别 设置。三个端口的工作方式由一个控制字规 设置。三个端口的工作方式由 一个控制字规 定。 (2) C口按位置位/复位控制字不是送到C 口按位置位/复位控制字不是送到C 口地址,而是送到控制寄存器地址; 口地址,而是送到控制寄存器地址;且一个 控制寄存器地址 控制字只能使C 一位置位或复位。 控制字只能使C口一位置位或复位。

第7章 并行I/O接口 并行I/O接口 I/O

本章内容 I/O接口概述 接口概述 并行接口 —— 8255A

学习目的

掌握可编程并行接口芯片 8255A的连接与编程 的连接与编程

概述

微机系统的信息交换有并行通信 微机系统的信息交换有并行通信 串行通信两种方式 两种方式。 和串行通信两种方式。 并行通信是以微机的字长为传输单位;适合 于外部设备与微机之间进行近距离、大量和快速 的信息交换。

3. 数据总线缓冲器

三态双向8 位缓冲器, 8255A 三态双向 8 位缓冲器 , 是 8255A 与 CPU 之间的数据接口。传送输入数据、 之间的数据接口 传送输入数据、 数据接口。 输出数据、控制命令字。 输出数据、控制命令字。

4. 读/写控制部件

接收来自CPU地址总线信号和控制信号 接收来自CPU地址总线信号和控制信号,并发 地址总线信号和控制信号, 出命令到两个控制组 (A组和B组)。 (A组和 组和B CS:片选信号,接CPU高位地址的译码输出 片选信号, 片选信号 高位地址的译码输出 RD:读信号,RD有效,CPU读8255A的数据或状态; 读信号, 有效 有效, 的数据或状态; 读信号 读 的数据或状态 WR: 写信号, WR有效 , CPU向 8255A写入控制 : 写信号 , 有效, 向 写入控制 有效 或数据信息。 或数据信息。 RESET:复位信号。有效时,清8255A 所有控制寄 :复位信号。有效时, 存器内容。并将各端口置成输入方式。 存器内容。并将各端口置成输入方式。

8255A 8255A 可 编 程 外 围 设 备 接 口 (Programmable Peripheral Interface, 简写 为PPI) ,其内部结构如图所示。 其内部结构如图所示。

A组控制 部件 双向 D7~D0

A1 A0

RD WR

A组 端口A 8位 A组 端口C (高4位) B组 端口C (低4位) B组 端口B 8位

PA7~PA0

数据总线 缓冲器 读/写

PC7~PC4

PC3~PC0

CS RESET

控制部件

B组控制 部件

图7.1 8255A内部结构 8255A内部结构

PB7~PB0

2. 8255A的引脚 的引脚

8255A 采 用 40 线 双 列直插封装, 引脚图如图

数 据 总 线

D0

. . .

34

. . .

4 3 2 1 40

8255A共有两个控制字: 8255A共有 两个 控制字 : 即 工作方式控 两个控制字 制字和对C口置位/复位控制字。 制字和对C口置位/复位控制字。 1. 控制字

(1)工作方式控制字: 工作方式控制字: 控制字和各位的含义如图所示。

D7

D6 D5

D4 D3

D2 D1 D0

B组 端口C(PC3~PC0) 1=输入, 0=输出 端口B 1=输入,0=输出 方式选择 0=方式0, 1=方式1 A组 端口C(PC7~PC4) 1=输入, 0=输出 端口A 1=输入,0=输出 方式选择 00=端口A方式0, 01=端口 A方式1,1×=端口A方式2 方式设置标志 1=有效

方式0 方式0的工作状态组合

A组 序号 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 控制字 D7,…,D0 10000000 10000001 10000010 10000011 10001000 10001001 10001010 10001011 10010000 10010001 10010010 10010011 10011000 10011001 10011010 10011011 端口A 端口A 输出 输出 输出 输出 输出 输出 输出 输出 输入 输入 输入 输入 输入 输入 输入 输入 端口C 端口C 高 4位 (PC7~PC4) 输出 输出 输出 输出 输入 输入 输入 输入 输出 输出 输出 输出 输入 输入 输入 输入 端口B 端口B 输出 输出 输入 输入 输出 输出 输入 输入 输出 输出 输入 输入 输出 输出 输入 输入 B组 端口C 端口C 低 4位 (PC3~PC0) 输出 输入 输出 输入 输出 输入 输出 输入 输出 输入 输出 输入 输出 输入 输出 输入