一种基于CPLD的DMA控制器IP核设计

cpld原理

cpld原理

CPLD是复杂可编程逻辑器件(Complex Programmable Logic Device)的缩写,它是一种集成电路芯片,通过对其内部的逻

辑门、触发器和可编程互连资源进行编程,实现不同的逻辑功能。

CPLD的原理主要基于可编程逻辑阵列(PAL)和可编程压缩

阵列(GAL)。

它由一个或多个可编程逻辑单元(PLU)或宏单元组成,每个单元包含逻辑门和触发器等基本逻辑元件。

CPLD的内部结构主要由两部分组成:可编程逻辑单元(PLU)和全局输入/输出(IO)资源。

PLU是CPLD的核心部分,它由多个可编程逻辑单元组成,

每个单元接收输入信号并输出相应的逻辑运算结果。

其中每个单元可以实现任意的逻辑功能,并通过互连通道与其他单元进行连接。

全局IO资源用于连接CPLD与外部器件,包括输入输出引脚、时钟信号等。

它提供了与外界通信的接口。

CPLD的编程通常采用硬件描述语言(HDL)或可编程逻辑阶

梯(PLD)语言,如VHDL、Verilog等。

通过编写逻辑描述

代码,并使用专门的软件工具进行综合、布局和布线,可以将逻辑功能转化为CPLD内部资源的配置和连接。

在编程完成后,CPLD可以实现各种逻辑功能,如组合逻辑、

时序逻辑、状态机等。

它还可以实现多个逻辑块之间的通信和控制,具有较高的灵活性和可扩展性。

总而言之,CPLD原理是通过对其内部逻辑资源进行编程,实

现不同的逻辑功能。

它由可编程逻辑单元和全局IO资源组成,通过编写逻辑描述代码并使用专门的软件工具进行编程,可以实现各种逻辑功能,并与外部器件进行通信和控制。

Linux 系统下基于PCI 控制器(PLX9054)的DMA 编程

建立 DMA 操作环境的工作包括:PCI 设 备检测和初始化、DMA 缓冲区分配和中断处

关 键 词 : Linux; PCI; DMA; 驱 动 程 序 ;

PLX9054;

Abstract: DMA is a way to quickly

transport large amount of data. DMA communication highly depends on operating system and certain hardware. This paper discusses the major problem and solution of DMA programming in Linux operating system. At the same time, an example is given to show how to design DMA communication with PLX9054-PCI controller.

PLX9054 是 PLX 公司生产的 PCI 总线接 口控制器芯片。PLX9054 符合 PCIV2.2 规范, 32 位,工作频率为 33MHz,拥有两个独立的 DMA 通道,传输速度达 132MB/s。PLX9054 提供了 PCI 总线、EEPROM、LOCAL 总线三个 接口,其中 LOCAL 总线有三种工作模式:M 模式、C 模式和 J 模式。在实际的数据采集 时, LOCAL 总线接口一般设置为 C 模式。 PLX9054 芯片在 PCI 总线和 LOCAL 总线之间 有三种直接的数据传输模式:PCI Initiator 模式--LOCAL 总线主设备通过 PLX9054 访问 PCI 总线存储空间和 I/O 空间;PCI Target 模式--PCI 总线主设备通过 PLX9054 访问 LOCAL 总线存储空间和 I/O 空间;DMA 方式 --PLX9054 作为两总线的主设备,实现 PCI 总线存储空间与 LOCAL 总线存储空间之间的 数据传输。

基于CPLD的I2C总线主控制器IP核的设计

基于CPLD的I2C总线主控制器IP核的设计摘要:根据单片机I2C串行扩展的特点,在EDA软件MaxplusII的环境下,利用硬件描述语言,建立IP核。

此设计利用状态机实现,在给出设计的同时详细说明IP核的建立过程,并下载到芯片通过硬件试验验证。

关键词:I2C总线;IP核;CPLD系统引言I2C总线是PHILIPS公司推出的新一代串行总线,其应用日渐广泛。

目前许多单片机都带有I2C总线接口,能方便地实现I2C总线设计;对没有I2C总线的微控制器(MCU),可以采用两条I/O口线进行模拟。

在以单片机为MCU的系统中/很容易实现I2C总线的模拟扩展,有现成的通用软件包可以使用。

1 基于CPLD系统中开发自己的I2C总线IP核的重要性对有些基于CPLD的系统,要与带有I2C总线接口的外围器件连接,实现起来相对复杂一些。

为实现系统中的I2C总线接口,可以另外引入单片机,也可以采用PCF8584或者PCA9564器件(PHILIPS公司推出的专用I2C总线扩展器)进行扩展,但这样会增加系统成本,使系统冗余复杂。

像ALTERA、XILINX等一些大公司有专用的基于CPLD器件的I2C总线IP核,但这些IP核的通用性不强,需要的外围控制信号较多,占用系统很大的资源,因此直接采用这种IP核不可取。

鉴于此,依照I2C总线协议的时序要求,在基于CPLD的系统中开发了自己的I2C总线IP核。

对于一些带有I2C总线接口的外围器件较少、对I2C总线功能要求较简单的CPLD系统,自主开发IP核显得既经济又方便。

图1 i2c的传输原理2 I2C总线的协议I2C总线仅仅依靠两根连线就实现了完善的全双工同步数据传送:一根为串行数据线SDA,一根为串行时钟线SCL。

该总线协议有严格的时序要求。

总线工作时,由时钟控制线SCL传送时钟脉冲,由串行数据线SDA传送数据。

总线传送的每帧数据均为一个字节8bit,但启动I2C总线后,传送的字节个数没有限制,只要求每传送一个字节后,对方回应一个应答位(Acknowledge Bit)。

CPLD实验报告

实验一 Xilinx软件及状态机设计一实验目的:学习FPGA设计软件, 掌握软件流程, 掌握状态机编程。

二实验内容:设计一个状态机三实验说明:状态机设计是数字电路中使用非常广泛和方便的时序设计工具。

由于硬件是并行的触发, 相对软件是串行执行, 那么让硬件电路按照节拍执行串行操作指令就成为一个问题, 这就是状态机的主要功能。

相应的, 软件指令中的几十条简单顺序执行代码可能需要硬件的几十上百个触发器去实现其功能。

所以, 软件与硬件的设计思路有相当大的区别。

当然, 随着FPGA规模的不断扩大, 这些问题也越来越容易解决了。

我们可以用软件的思路去描述自己的设计, 可能最终实现的电路是几十万门级的器件, 但是你只要花费几美元就能买到。

状态机是数字电路的基础, 因此, VHDL的学习也从这个实验开始。

四实验过程:1.在进行实验之前, 我先自学了VHDL语言。

2.熟悉Xilinx软件环境。

3.通过仿真, 读懂了states这段代码所实现的功能及其出现的问题。

五思考题:1.通过仿真, 这段代码实现相应功能时出了什么问题?请修正代码。

答:这段程序完成的是对红绿灯的控制功能。

通过仿真发现所有的灯都比预期的多亮了2秒, 比如东西方向绿灯亮62秒(应该是60秒), 黄灯是5秒(应该是3秒)。

出现此问题的原因是没有考虑到硬件的延时问题。

所以只要把程序中的59改为57, 39改为37, 3改为1, 再进行仿真, 结果就正确了。

2.状态机输出分成同步输出和异步输出, 状态机异步输出直接用状态机的某个状态进行组合逻辑运算来得到一个输出, 同步输出是在该状态的时钟上跳沿控制输出变化。

请问同步输出和异步输出利弊各在哪里?答: 同步输出的优点是: 时钟脉冲的间距解决了组合逻辑电路中的延时和竞争问题。

只要时钟脉冲的宽度合适, 输出就不会存在竞争与现象。

缺点是: 外部输入信号的变化应满足触发器正常工作所需的建立和保持时间。

因为上述特点使得同步时序输出的工作速度的提高受到限制, 且对时钟脉冲到达个触发器的时间及外部信号的变化有较严格的要求。

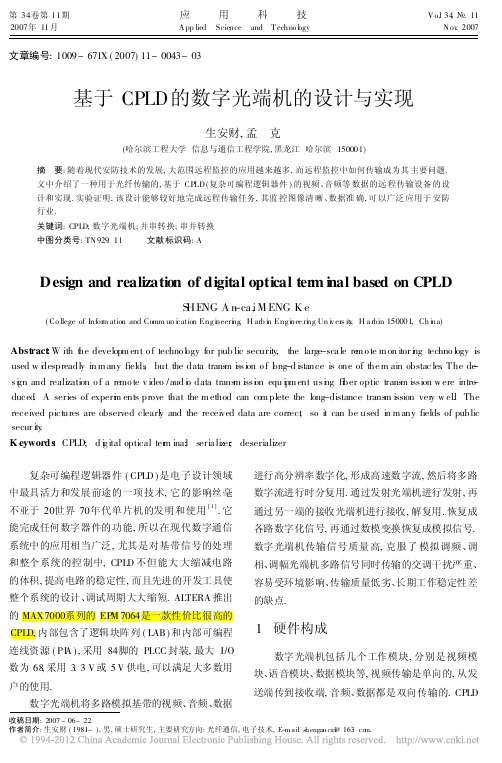

基于CPLD的数字光端机的设计与实现

第34卷第11期应用科技V o.l 34,l .112007年11月A pp lied Science and T echno l ogyN ov .2007文章编号:1009-671X (2007)11-0043-03基于CPLD 的数字光端机的设计与实现生安财,孟 克(哈尔滨工程大学信息与通信工程学院,黑龙江哈尔滨150001)摘 要:随着现代安防技术的发展,大范围远程监控的应用越来越多,而远程监控中如何传输成为其主要问题.文中介绍了一种用于光纤传输的,基于CPLD (复杂可编程逻辑器件)的视频、音频等数据的远程传输设备的设计和实现.实验证明,该设计能够较好地完成远程传输任务,其监控图像清晰、数据准确,可以广泛应用于安防行业.关键词:CPLD;数字光端机;并串转换;串并转换中图分类号:TN 929.11 文献标识码:ADesign and realization of digital optical ter m i nal based on CPLDS HENG A n -ca,i M ENG K e(Co llege of Infor m ation and Comm un i cation Eng i neeri ng ,H arb i n Eng i nee ri ng Un i v ers it y ,H a rbin 150001,Ch i na)Abst ract :W ith t h e developm ent o f techno l o gy for pub lic security ,the large -sca le re m o te m on itor i n g techno logy isused w i d espreadly in m any fields ,but the data trans m ission o f l o ng -d istance is one of the m ain obstac les .The de -si g n and realization o f a re mo te v ideo /aud i o data trans m issi o n equ i p m ent usi n g fi b er optic trans m ission w ere intro -duced .A series of experi m ents prove that the m ethod can co m plete the long -distance trans m ission ver y w el.l The received pictures are observed clearl y and the received data are correc,t so it can be used in m any fields of public secur ity .K eywords :CPLD;d i g ital optical ter m ina;l seria lizer ;deserializer 收稿日期:2007-06-22.作者简介:生安财(1981-),男,硕士研究生,主要研究方向:光纤通信,电子技术,E-m ai:l s h engan ca@i 163.co m.复杂可编程逻辑器件(CPLD )是电子设计领域中最具活力和发展前途的一项技术,它的影响丝毫不亚于20世界70年代单片机的发明和使用[1].它能完成任何数字器件的功能,所以在现代数字通信系统中的应用相当广泛,尤其是对基带信号的处理和整个系统的控制中,CPLD 不但能大大缩减电路的体积,提高电路的稳定性,而且先进的开发工具使整个系统的设计、调试周期大大缩短.ALTERA 推出的MAX7000系列的EP M 7064是一款性价比很高的CPLD,内部包含了逻辑块阵列(LAB )和内部可编程连线资源(PI A ),采用84脚的PLCC 封装,最大I/O 数为68,采用3.3V 或5V 供电,可以满足大多数用户的使用.数字光端机将多路模拟基带的视频、音频、数据进行高分辨率数字化,形成高速数字流,然后将多路数字流进行时分复用.通过发射光端机进行发射,再通过另一端的接收光端机进行接收,解复用.恢复成各路数字化信号,再通过数模变换恢复成模拟信号.数字光端机传输信号质量高,克服了模拟调频、调相、调幅光端机多路信号同时传输的交调干扰严重、容易受环境影响、传输质量低劣、长期工作稳定性差的缺点.1 硬件构成数字光端机包括几个工作模块,分别是视频模块、语音模块、数据模块等,视频传输是单向的,从发送端传到接收端,音频、数据都是双向传输的.CPLD是系统的核心,接收各个模块送来的数据,然后时分复用到信道上,通过光纤传到对端,对端再将接收到的数据发送给各个相对应的模块.收发芯片TI65LV1023A /1224B 的主要作用是实现并串/串并转换、数据帧的同步.系统的逻辑框图如图1所示.图1 系统模块图视频模块采用了德州仪器(TI)的A /D 转换芯片TLC5510和D /A 转换芯片TL5632,这2款芯片都是T I 公司针对视频数字化推出的高性价比产品.TLC5510为8位A /D 转换器,最高采样率为20MH z ,在使用时只需将8位数字输出与CPLD 的I/O 相连即可.在PAL 制的电视信号中,模拟视频信号的频率为4.43MH z ,根据奈奎斯特采样定理,采样速率最低为8.86MH z ,但在实际中所采用的A /D 采样速率为最优的17.7MH z ,系统传输的是实时数字视频流,在发送端将A /D 采集来的数字流发送出去,没有压缩与编码,在接收端将收到的数字信号经过D /A 芯片TL5632转换为模拟视频信号送到监视器.TL5632是一种低功耗的3路输出的D /A 转换器,最高转换速率为60MH z ,在实际使用中只需要将从CPLD 解调出来的8位数字视频信号与TL5632的一个输出通道相连,同时把相应通道的时钟输入接到CPLD 的视频时钟输出端即可.最后在监视器上显示出来的信号完全可以满足视频监控的要求.语音模块采用的是德州仪器(TI)的音频A /D 芯片PC M 1402将模拟音频信号转换为数字信号,采样率为48kH z .在接收端采用TI 的D /A 转换芯片PC M 1502将数字信号转换为模拟音频信号,转换后的信号通过R J11头与交换机相连,让接收端电话机接入语音网络.在实际中,应充分考虑电话振铃带来的干扰,并且使系统不稳定的影响.数据模块采用国家半导体(NS)的L M 331芯片,采用5V 电压供电,最高转换速率为1M bps ,完全可以满足要求.LM 331结构简单,外围电路少,使用非常方便,并且可以实现F /V 和V /F 的双向转换.并串转换模块串并转换模块采用德州仪器的T I 65LV1023A 和T I 65LV1224B ,它是一款1B 10的高性价比串行器,采用3.3V 电源供电,最大时钟为66MH z .在工作中它采用的是10B 12的转换,10位有效数据为加2位时钟位为一帧,所以最高的串行传输速率为60@12=720M bps [2].串行数据采用的是低电压差分信号(LVDS )传输.低电压差分信号的电压摆幅小,所以转换速度更快,可以实现更高的速度,且不会增加串扰、E M I 和功耗,可以大大地提高信噪比[3].在接收端,并行器1224B 具有自动恢复时钟的能力,当接收端接收到传过来的串行数据后,首先锁定、恢复出系统时钟,然后将串行数据转换为10位并行数据输出.激光发射/接收模块采用武汉电信器件公司的RTXM 123B -3-35-SC 和RTXM 123B -3-53-SC.这是一款收发一体的激光发射模块,分别采用1310n m 发射、1550nm 接收和1550发射、1310nm 接收,电路接口采用LVPECL 电平,电源采用3.3V 电源供电,最高传输速率为622M bps .2 软件设计CPLD 功能是通过V eril o g HDL 编程来实现的.Verilog 是一种功能强大的硬件描述语言,被广泛应用在电子设计中[4].在本系统的实现中,采用了模块化设计.对不同的接口构建不同的module ,在主程序中再调用这些m odu le .主程序主要完成对光纤接口处收发芯片的控制.在本系统中,光纤接口处的高速收发芯片选用T I 公司的T I 65LV1023A /1224B ,它是用于高速串行收发芯片与CPLD 相连的控制信号和数据信号,如图2所示,其他一些对T I 65LV1023A /1224B 进行初始化设置的信号线并未标出.主程序中发送模块设置了一个主计数器对t_#44#应 用 科 技 第34卷clk 发射时钟进行计数,根据计数值控制t_en 发送使能信号,使TI65LV1023A /1224B 输出一定格式的串行数据(可参见TI65LV1023A /1224Bdatasheet).在接收端,TI65LV1023A /1224B 收到串行数据后,实现帧定位,串/并转换,产生r_cl k 接收时钟信号和r_dv 数据有效指示信号送入CPLD,主程序中的接收模块根据c l k 、r_dv 信号将接收到的数据解复用后,传给各个对应的模块.图2 CPLD 与串行器/解串器T I65LV 1023A /1224B 的接口3 实际应用中的设计要点在实际的设计中,有几点需要特别注意,因为它们影响到整个系统的稳定性,甚至关系到整个系统设计的成败.3.1 视频信号的同步为了使视频信号在传输过程中始终保持同步,需要在发送端对模拟的视频信号提取同步信号,用于控制视频信号的同步,这里采用LM 1881加74H C123来实现.提取出的同步信号加到CPLD 的I/O 口,作为一个缓冲器的清零端,如果A /D 后的信号不同步,则进行清零,丢掉这一帧数据.在实际的工作中,这一方法很有效,可以较好地解决视频信号的同步问题.3.2 串行信号的电平转换由于并串/串并转换芯片TI65LV1023A /1224B的串行数据采用的是低电压差分信号(LVDS ),而激光发射/接收模块的接口为LVPECL 信号电平,所以需要进行LVDS 到LVPECL 和LVPECL 到LVDS 的转换,但在实际试验中,只需要做前者,LVPECL 到LVDS 不需要转换,直接对接就可以.采用电阻分配网络的方法进行转换,如图3所示,可以简单有效地完成转换[5].图3 LV PECL 到LVD S 的电平转换3.3 电源设计整个系统用到正5V 和正3.3V 电源,这里采用78M 05芯片来稳压,将外界电源转换为正5V 电源,采用L M 1117芯片将正5V 电压转换为正3.3V 电压.对于芯片的数字电源引脚,应接一个磁珠与电源相连,可以有效地对电源进行滤波.激光发射/接受模块的电源输入需要接一个C-L-C 滤波电路,因为任何的电源波动都会影响到该模块的发送与接受.4 结束语此套远程监控系统实现了各个监控点和总监控室的信号远程传输.经过试验,各监控点的摄像头传回视频信号,总监控室通过数据接口线对各个摄像头进行远程控制,远程两端之间还可以进行话音通信,能够较好地满足安防的要求.参考文献:[1]亿特科技.CPLD /FPGA 应用系统设计与产品开发[M ].北京:人民邮电出版社,2005.[2]T I Inc .10-MH z To 66-M H z ,10:1LV DS SER I A L IZERA nd DESER I AL IZER [Z ].A ustin :T I l nc ,2006.[3]NS Inc .D ata T rans m ission Comm un i cations Inte rfece D iv-ision[Z ].A tl anta :N S Inc ,2003.[4]夏宇闻.V eril ong 数字系统设计教程[M ].北京:北京航空航天大学出版社,2003.[5]NS Inc .C M L 、PECL 及LV DS 间的相互连接[Z ].A tlan -ta :NS Inc ,2001.[责任编辑:张晓京]#45#第11期生安财,等:基于CPLD 的数字光端机的设计与实现。

基于CPLD的PWM控制电路设计说明

2008 年 08 月 04 日

社区交流

介绍了利用硬件描述语言 VHDL 设计的一种基于 CPLD 的 PWM 控制电路,该PWM控制电路具有 PWM 开关频率可调,同侧2路信号互锁、延时时间可调、接口简单等特点,可应用于现代直流伺服 系统。

在直流伺服控制系统中,通过专用集成芯片或中小规模的数字集成电路构成的传 统 PWM 控制电路往往存在电路设计复杂,体积大,抗干扰能力差以及设计困难、设计周 期长等缺点 因此 PWM 控制电路的模块化、集成化已成为发展趋势.它不仅可以使系统 体积减小、重量减轻且功耗降低,同时可使系统的可靠性大大提高.随着电子技术的发 展,特别是专用集成电路(ASIC)设计技术的日趋完善,数字化的电子自动化设计(EDA) 工具给电子设计带来了巨大变革,尤其是硬件描述语言的出现,解决了传统电路原理图 设计系统工程的诸多不便.针对以上情况,本文给出一种基于复杂可编程逻辑器件(CPL D)的 PWM 控制电路设计和它的仿真波形. 1 PWM 控制电路基本原理

‘0'; Q<=Qs; cao<=reset or caolock; end a_counter;

在原理图中,延迟模块必不可少,其功能是对 PWM 波形的上升沿进行延时,而不影响 下降沿,从而确保桥路同侧不会发生短路.其模块的 VHDL 程序如下:

entity delay is port(clk: in std_logic; input: in std_logic_vector(1 downto 0); output:out std_logic_vector(1 downto 0) end delay; architecture a_delay of delay is

基于CPLD/FPGA平台I2C总线IP核的设计

基于CPLD/FPGA平台I2C总线IP核的设计摘要:本文通过对一个I2C总线IP核的设计,介绍了用VHDL语言设计和实现该IP核的过程。

首先简要介绍了I2C总线协议的标准及应用,分析了影响8位MPU的传输速率低的因素,然后提出了基于CPLD/FPGA平台设计“虚拟器件”I2C总线IP核的设想。

其次给出系统自顶向下的设计方案。

接着对系统的功能进行了详细的总体规划与层次设计,讲解了系统体系结构和系统各个功能模块的电路设计。

最后进行了调试,并给出在MAX+Plus II 10.0环境下的仿真波形。

关键词:I2C总线VHDL IP核CPLD/FPGA一、系统设计的背景与意义在现代通讯类产品、仪器仪表、工业测控系统中,逐渐形成了以一个或多个微处理器组成的智能系统,并且对外围电路之间主要是实现控制功能,因而I2C 总线对应用系统的开发带来很多好处:一方面,二线制的I2C串行总线使得各电路单元之间只需最简单的连接,而且可实现电路系统的模块化、标准化设计;另一方面,标准的I2C总线模块的组合方式大大地缩短了新产品的开发周期,并且I2C总线系统构成具有最大的灵活性和极好的可维护性。

目前,在绝大多数单片机应用系统中仍保持着单主结构(其中包括一些双主系统中,主节点之间不能进行直接通信的情况)。

在单主系统中,I2C总线只存在着主方式,I2C总线的数据传输状态比较简单,主要是实现单片机(或MCU)对I2C总线简单的读/写操作。

因此,利用VHDL硬件语言实现I2C总线接口功能,并通过下载到CPLD/FPGA实现与其他节点的数据传输,使这些器件不受系统单片机必须带有I2C总线接口的限制。

这也大大地扩展了I2C总线器件的适用范围,使I2C总线在应用系统设计中有着更为广泛的应用。

二、系统设计方案目前,许多IC器件广泛采用I2C接口来读/写数据,但是多数的8位微处理器都没有专用的I2C接口,因此一般只有通过GPIO口利用软件编程来实现I2C 总线的数据传送。

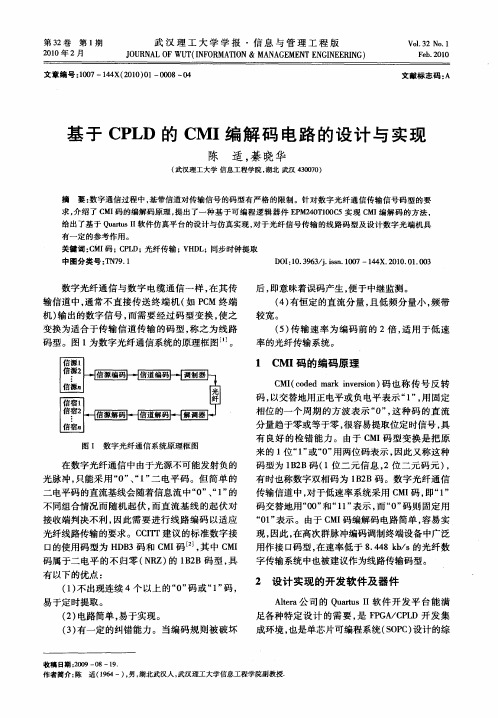

基于CPLD的CMI编解码电路的设计与实现

信 源解码 H 信 道解码 H 解调器

分 量趋 于零或 等于 零 , 容易提 取位 定时信 号 , 很 具

有 良好 的检错 能 力 。 由于 C 码 型 变 换 是 把 原 MI 来的 1 “ ” “” 位 1 或 0 用两 位码 表 示 , 因此 又称 这种

图 I 数字光纤通信系统原理框 图

在 数字 光纤通 信 中 由于 光源 不可 能发射 负 的

光脉冲, 只能 采 用 “ ” “ ” 电平 码 。但 简 单 的 0 、1 二

码 型 为 12 B B码 ( 位 二 元 信 息 , 二 元 码 元 ) 1 2位 ,

有 时也称 数字 双相 码 为 1 2 B B码 。数 字光 纤 通信

第3 卷 第 1 2 期

21 00年2月

武 汉 理 工 大 学 学 报 ・ 息 与 管 理 工 程 版 信

J U N LO L ( F R A IN&M N G M N N IE RN 1 O R A FW r I O M TO FN A A E E TE GN E IG

Vo . 2 N . 13 o 1

有 以下的优 点 : ( ) 出现连续 4个 以上 的 “ ” 或 “ ” , 1不 0码 1码 易于定 时提 取 。

传 输信 道 中 , 对于低 速率 系统 采用 C 码 , 1 MI 即“ ”

码 交替 地用 “ 0 和“ 1 表 示 , “ ” 则 固定 用 0 ” 1” 而 0码 “ 1 表示 。 由于 C 码编 解码 电路 简单 , 易 实 0” MI 容

Fe . Ol b2 O

文章编号 :0 7—14 2 1 ) 1— 0 8— 4 10 4 X(00 0 00 0

文献标志码 : A

一种基于CPLD的高速同步采样系统的设计

l A 92 4 D 4 A DD V

— . . .. —.

C== _ l 卜 6 D] C= l 5 D】 1 4 D】 C=: _ 1 卜 3 D】

2

3

A D vD

不 1 F ==c == 0 u 2

上

T +

T

32

L+ K

LB D S —0

8

7

- - 一 1 " x 0

T

AD VD

D D VD

r 0 F

:

1 .i 1

:

= i0F A } F. V = l D 0 I 3 D 0 14

A D GN

AD G N

0 E B

V R

1 .

:

:

:l D Y 5 R肋

化 加 的性 能

个 信 号 告 诉 计 算 机 已经 采 样 完 毕 ,可 以进 入 读 R M 状 A

态 。读 取 的 时 候 由计 算 机 并 口来 控 制 C L 产 生 片选 和 地 PD 址 信 号 。 其具 体 的程 序 流 程 图如 图 4所 示

==

一

T

T A D 4 VD

1

MB S

—

O TR D1 3

2 8 2 7

3 4

2 6

5 C =

7 C =

—

1D 2E

1 0 D

l…

一

0 u l0 1 J.1 l2 AN . . F 0u GD F 0 0 F

的情 况 下 会 造 成 数 据 堵 塞 现 象 。在 系 统 设 计 的过 程 中 采 用

高 速 双 口 R M 构 成 的 高 速 数 据 交 换 接 口成 功 地 解 决 了此 A 问题 。 系 统 每 采 集 满 一 组 数 据 再 一 次性 向 计 算 机 传 送 .减 轻 整 个 系 统 的负 担 。

基于PCIE总线的DMA控制器设计与实现

/ndustrialApplication •行业良用基于P L E总线的D M A控制器设计与实现何广亮(中国空空导弹研究院,河南洛阳471000)摘要:基于XilinxVirtex-6系列FPGA设计实现了PCIE总线的DMA控制器,用来解决PC与FPGA的高速数据传输问题。

利用DMA控制器传输数据在提高数据传输速率的同时还可大大提高CPU利用率。

对设计的DMA控制器进行了功能和性能验证,结果表明该控制器能够正确地进行DMA数据传输,速率高达6Gb/s。

关键词:PCIE*DMA*FPGA中图分类号:TP274文献标识码:A DOI:10.19358/j.issn. 2096-5133.2018.04. 030引用格式:何广亮.基于PCIE总线的DMA控制器设计与实现[J].信息技术与网络安全,2018,37(4):131-135.Design and implementation of DMA controller based on PCIE busHe Guangliang(Ch i n a A ir b or n e M issil e A c ad e my,Luo y an g 471000, C h i na)Abstract:In th is paper,th e PC IE bus D M A con troller based o n X ilinx V irte x-(3series FPG A is d esigned an d im pl resolve th e problem of h igh speed data transm ission betw een P C an d FPG A. B y using D M A be greatly im proved w h ile im provin g data transm ission rate. T h e fu n ction an d perform ance of tlie designed D M A con troller are verified,an d th e results sh o w th at th e D M A con troller can transm it data correctly,an d th e speed is as h igh as 6 Key words:PC I E;DM A;FPG A〇引言在信号与信息处理领域,数据采集技术发挥着至关重要的作用,而高传输技术采集系统中的关键部分。

一种基于CPLD的数据采集控制板的设计

摘要:针对多种采集信号类型,设计了一种采用CPLD实现信号采集控制、信号处理、通讯及输出控制等功能的复合数据采集控制板,并分析了其相关应用性能。

关键词:CLPD EPP接口编码器数据采集在需要采集多路模拟信号、开关信号、频率(计数)信号以及编码器信号等的数据采集应用中,利用通用板卡构成计算机测控系统是可行的,但对于产品的批量应用,其成本与综合性能不能令人满意。

技术成熟的CPLD芯片的应用,可以很好地将逻辑控制、数据信号处理等功能集于一身,使以往需要利用多块信号板卡才能完成的任务整合于同一采集控制器中,从而有效地提高控制系统的可靠性,降低测控系统的实现成本。

本文设计一种基于CPLD的数据采集控制板。

它能实现信号采集与控制、信号处理、通讯及输出控制等功能。

1 总体设计方案本专用数据采集控制板利用CPLD作为主控制器,统一协调通道切换与数字信号处理、实现数据采集与接口传输逻辑控制。

该数据采集控制板共有四种类型的信号输入和一种开关信号量输出。

图1给出其基本硬件模块组成。

利用CPLD的资源和结构特点是本设计的核心。

为提高编码器输入信号的分辨细长,配套设计一个四倍频电路,并在通道后端设计一个脉冲静态计数电路,使输入信号转换为8bit信号挂接到采集板总线上。

八路模拟输入信号主要依靠CPLD实现通道切换和A/D采集,采样数据也以8bit信号并行进入总线。

考虑到提高计数精度的要求,对两路频率输入信号设计了一个动态计数电路,使计数值通过总线读出。

I/O切换控制、EPP接口电路等都按一定的逻辑要求采用同一 CPLD元件来实现。

如此可使硬件电路十分简单,并有利于上位机编程实现。

2 数据接口根据IEEE1284标准,在标准并行口(SPP)、增强并行口(EPP)和扩展并行口(ECP)三种模式中,EPP模式既具有双向数据传输功能,又具有较高的数据传输能力,且编程操作相对容易,最适合在数据采集系统中使用。

从硬件设计角度考虑,EPP接口的主要功能之一是将采集到的数据上传给微型计算机或将开关控制命令下载到采集控制板(数据流对应8bit数据端口);之二是实现硬件接口之间的信号通讯握手(控制状态对应其它I/O端口)。

DMA_IP设计_详解

DMA模块介绍

地址寄存器:(两寄存器共用一个端口地址) 1、基地址寄存器:初始化编程时由CPU写入,整个DMA传送期 间不再改变,只能写入不能读出,保存内存数据块首地址; 2、现行地址寄存器:初始值与上相同,DMA传送期间,不断通 过加1或减1来修改访问存储器的地址指针,指出当前正在访问的存储 器地址,可写入也可读出;

DMA模块介绍

通道请求模块: 1、DMA请求寄存器:外设有DMA请求时,DMA请求寄存器中相应位置 “1“,并由控制模块向CPU发起总线请求; 2、屏蔽寄存器:软件编程规定某通道请求被屏蔽; 3、优先级判别:当有多个通道请求时,优先级判别电路根据优先级判 别法来决定响应哪个通道请求; DMA通道的优先级由编程来决定: (1)固定优先级:规定每个通道的优先级是固定的,即通道0的优先级 最高,依次最低。 (2)循环优先级:规定刚被服务的通道优先级最低,依次循环。这样就 可以保证每个通道都有机会被服务。

单元

电路

模块DMA功能测试源自模拟验证方法图示问题综合:

1、DMA请求总线时,在嵌入式系统中是向 CPU发起请求还是向某个仲裁器发起请求。

DMA的初始化编程

(5)写入屏蔽寄存器; (6)写入命令寄存器,以控制DMA的工作; (7)写入请求寄存器,若有软件请求,则写入指定通道,若无软件请求 ,则完成前六步后由DREQ启动DAM传输。 由于不同芯片的寄存器端口地址不同,这里不再举例。

关于复位

复位是ASIC设计中最容易出问题的一环。DMA控制器主要有两种复 位方式,一种是上电复位,即异步复位,另一种是软件复位,即同步 复位。

(3)DMA的数据传送是以数据块为基本单位进行的,因此,无论是输入还是输 出操作,都是通过循环来实现的。 (4)DMA读数据和写数据是分开的: DMA会率先进行读数据操作,从源地址读取数据至FIFO中,每次读一个字或一 个字节,当FIFO中数据量够一次Burst操作后,写数据开始行动,将数据从FIFO 中写到目地地址所指向的模块中。若FIFO满,则自动停止读数据,若FIFO空则 自动停止写数据。当读数据部分完成了此次DMA传输要求的长度,则状态机 进入下一个子状态,等待写数据完成,归还总线。至此DMA控制器回到空闲 状态,等待下一次DMA传输。

基于CPLD的步进电机控制器设计

基于CPLD的步进电机控制器设计王海华,宋蕾辽宁科技大学电信学院 114051摘要:本文设计了一种基于CPLD的步进电机控制系统。

它以CPLD作为核心器件,极大地减少了外围元件的使用。

具有系统扩展性能好、可靠性高、抗干扰能力强、结构简单、成本低廉,不占用CPU时间、易于高速控制等优点。

关键词:步进电机,控制器,CPLD中图分类号:TP393 文献标识码:AThe designing of the stepper motor controlled by the CPLDWang Haihua ,Song LeiUniversity of Science and Technlogy Liaoning 114044Abstract:This paper devices a kind of control system of the stepper motor based upon CPLD. As the core of the device, CPLD implements the most logic functions and minimizes the peripheral components. The distinctive advantages of the system are expandable, stable, simple, lowly-cost and changing functions on system without occupying CPU time etc.Keywords:Stepping motor,Controller,CPLD1、前言步进电机可在宽广的频率范围内通过改变脉冲频率实现调速、快速起停、正反转控制等,由其组成的开环系统简单、可靠,因此它被广泛的运用于数控机床、自动记录仪、工业机器人、无损检测等系统中,步进电机的性能很大程度上取决于其控制系统[1]。

基于CPLD数字频率计的设计

山东理工大学毕业设计(论文)题目:基于CPLD的频率计设计学院:电气与电子工程学院专业:电子信息工程学生姓名:***指导教师:**毕业设计(论文)时间:二О一О年 3月 1 日~ 6 月17 日共16 周摘要本文主要论述了利用CPLD进行测频计数,单片机实施控制实现多功能频率计的设计过程。

该频率计利用等精度的设计方法,克服了基于传统测频原理的频率计的测量精度随被测信号频率的下降而降低的缺点。

等精度的测量方法不但具有较高的测量精度,而且在整个频率区域保持恒定的测试精度。

该频率计利用CPLD来实现频率、周期、脉宽和占空比的测量计数。

利用单片机完成整个测量电路的测试控制、数据处理和显示输出。

并详细论述了硬件电路的组成和单片机的软件控制流程。

其中硬件电路包括键控制模块、显示模块、输入信号整形模块以及单片机和CPLD主控模块。

本文详细论述了系统自上而下的设计方法及各部分硬件电路组成及单片机、CPLD的软件编程设计。

使用以GW48-CK EDA实验开发系统为主的实验环境下进行了仿真和验证,达到了较高的测量精度。

关键词: 频率计,EDA技术,CPLD,单片机IAbstractThis article discusses the use of frequency counts for CPLD, microcontroller control to achieve the implementation of the design process of multi-frequency meter. The use of such precision frequency meter design ways to overcome the traditional frequency measurement based on the principle of the measurement precision frequency meter with a decline in the measured signal frequency decreases the shortcomings. And other precision measurement method not only has high accuracy, but in the entire frequency region to maintain a constant precision. The frequency meter using CPLD to implement the frequency, period, pulse width and duty cycle measurement count .I used SUM complete the measurement circuit control, data processing and display output. Then I discussed about the composition of hardware and microcontroller software control flow. The hardware circuit includes key control module, display module, the input signal shaping module and MCU and CPLD control module.This paper has particularly described the top-to-bottom design method of the system, the circuit composite of the hardware and the software program device of CPLD and single chip computer. Under the test environment of the system developed by GW48-CK EDA experiment, the precision and velocity of the measurement have been obtained after the simulation and the test of the hardware.KEYWORDS: Frequency meter, EDA technique, CPLD, Single chip computerII目录摘要 (I)Abstract (II)目录 (III)第一章引言 (1)第二章测量原理及其性能指标 (2)2.1测量原理 (2)2.2 系统设计指标 (3)第三章硬件电路设计 (4)3.1 系统顶层电路设计 (4)3.2 测频模块的工作原理及设计 (5)3.2.1 CPLD的结构与功能介绍 (5)3.2.2 CPLD测频专用模块逻辑设计 (6)3.3 单片机主控模块 (10)3.3.1 AT89C51单片机性能 (10)3.3.2 单片机控制电路 (12)3.4 外围电路设计 (14)3.4.1 键盘接口电路 (14)3.4.2 显示电路 (15)3.4.3 电源模块 (15)3.4.4 其他电路 (16)第四章软件设计 (17)4.1 VHDL语言 (17)4.1.1 VHDL简介 (17)4.1.2 VHDL程序设计 (18)4.1.3 VHDL的设计方法 (18)4.2 本系统CPLD模块的设计 (20)4.2.1程序设计步骤: (20)4.2.2 本系统CPLD模块的顶层设计 (21)III4.3 单片机的汇编语言编程 (25)第五章实验测试及误差分析 (30)5.1实验测试的方法 (30)5.2 系统的硬件验证 (30)5.3 系统误差分析 (31)结论 (33)参考文献 (34)致谢 (35)IV第一章引言第一章引言测频一直以来都是电子和通讯系统工作的重要手段之一。

换体DMA高速数据采集电路的CPLD实现

换体DMA高速数据采集电路的CPLD实现摘要:介绍了块体DMA高速数据采集电路原理及其CPLD实现。

用CPLD设计双端口RAM缓存、控制译码、时序逻辑电路,很好地解决了电路元件所占体积大、电路复杂、不能实现在线升级等问题,大大提高了系统的整体性能。

关键词:换体DMA CPLD 双端口RAM 在线升级在许多仪器和控制系统中,高速数据采集电路是必不可少的,也是经常需要解决的问题。

数据采集电路设计方法很多,但往往离不开A/D转换电路、数据缓存电路、控制逻辑电路、地址发生器、址译码电路等。

而数据缓存、控制逻辑、地址译码等电路通常是由RAM芯片、与非门、触发器、缓冲/驱动器等构成,导致数据采集电路复杂、芯片繁多,特别是硬件的固定使得采集系统在线升级几乎不可能。

很多情况下只有重新设计电路和印刷板,重新焊接和调试,造成开发周期长、成本大大增高。

复杂可编程逻辑器件CPLD的应用,为这些问题的解决提供了一种好的办法。

利用CPLD芯片本身集成的上万个逻辑门和EAB,把数据采集电路中的数据缓存、地址发生器、控制译码等电路全部集成进一片CPLD芯片中,大大减小了系统的体积,降低了成本,提高了可靠性。

同时,CPLD可由软件实现逻辑重构,而且可实现在系统中编程(ISP)以及有众多功能强大的EDA软件的支持,使得系统具有升级容易、开发周期短等优点。

在数据采集有电路中,采用换体DMA技术不但大大地提高了数据采集的速度,而且弥补了数据采集中可能丢失数据的缺陷。

1 换体DMA数据采集电路原理系统原理框图如图1所示。

在时序电路的控制下,模拟输入开关将多达16路(单端输入)或8路(差分输入)的模拟输入信号经多路开关送至放大器的输入端,放大后由内含采样/保持电路的模数转换器AD774B转换成数字量,转换完的数字量经时序电路的控制写入两个存储体的一个(例如存储体0)中。

每个存储体有4KB的容量,但实际使用中存储容量可设定为小于4KB。

当计数到设定的存储空量后,控制电路产生换体信号,后续的A/D转换数据自动地存入另一个存储体(存储体1)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

图 1 83 与外部 数据存储器之间数据传送波形图 01

维普资讯

2 期

王笑 怡等 : 一种基 于 C L P D的 D MA控制器 I 核设计 I '

在图 1 a 的外部数据存储器读周期 中 ,2口 () P 输出外部 R M单元 的高八 位地址 ,0口分时传送 A P 低八位地址及数据。当地址锁存信号 A E为高 电 L 平时,0口输出的地址信息有效 , L P A E的下降沿将 Байду номын сангаас此地址打人外部地址锁存器 , 接着 P 0口变为输入方 式, 读信号 R D有效 , 选通外部 R M, A 相应存储单元

Ke wo d CPL ; y r s: D VHDL a g a e; l u g DMA o tol r n c nr le

盯 兰 l 阳 I嗣

1 前

言

场、 恢复现场之类 的工作 。内存地址修改、 传送字个 数的计数等等, 也不是 由软件实现 , 而是用硬件线路 直接实现的。所 以 D A方式能满足高速 IO设备 M / 的要求 , 也有利于 C U效率的发挥。 P

D A数据传输技术。 M

I 篙I 篙I 篙 rrnnr几nnr ]I I I nnr 1] ] 簧 ] 几nrr 篙I I r ] ] ]篙I ]

.

I

厂面 ]

IR 输出 I

r ̄ r c 2

S FR

l

输出 厂

S R F

l I

中图分 类 号 :P0 . T 3 22 文献标 识码 : A 文 章编 号 :02— 29 20 )2— 10— 3 10 27 (07 0 0 1 0

DMA nr l rI sg s d O Co t l P De in Ba e n CPL oe D

W ANG a Xio—y , i ZHONG e, Zh HAO n Bi g

3 标 准 8 3 数据传 输与 M 数据传输对 比 0 1 D A

M S 5 单 片机读 写外部数据存储器 的时序 C 一1 如图 1 示。 所

需要高速率大批量数据传送时 , 数据吞 吐速率往往 不能满足设计要求。即使采用提升振荡器频率的办 法, 结果仍不尽如人意, 以寻找一种新的数据传输 所 方法显得很有必要 , 这不仅使人想 到通用计算机 的

Ab t a t T i p p ri t d c st e D s r c : hs a e n r u e MA r a r n mis n me o n h l n d . ti r a i d b o h e d t s s i t d i a t gmo e I s e l e y a o h i z u ig C L T e s h ma i da r m d V s P D. h c e t ig a a HDL p o r m o e c r o o e tae is e . n ti a , n c n rg a f rt o e c mp n n l s u d I s w y h h h aa t n mi o ae i i rv d v r e r a l . t e d t a s s i n r t mp o e e y r ma k b y r s s

单片机以其高可靠性 , 高性能价格比, 在工业控 制系统 、 数据采集系统、 智能化仪器仪表 、 办公 自动 化等诸多领域得到极为广泛的应用。在单片机家族

的众多成员中, S 5 系列单片机 占领了广 阔的 M C一 1 市场 , 成为国内单片机应用领域的主流。 但是由于 83 硬件结构和指令系统的限制 , 01 当

D 2 嗡出 P 蜮PF s  ̄F2 cR S  ̄F

()外 部 数据 存储器 写周 期 b

舞陀I

参与数据传送操作 , 因此就省去 了 C U取指令 、 P 取 数、 送数等操作。在数 据传送过程 中, 没有保存 现

作者简介 : 王笑怡( 94一) 男 , 人 , 17 , 北京 工程师 , 主研方 向; 计算机应用。 收稿 1 : 0 —1 一 5 3 2 6 1 o 期 0

摘

要: 介绍了一种基于 C L P D实现的 C U停机方式 D A读传送 的方法, P M 并给 出了相应的原

理 图及核心部件的 V D H L程序。采用此方案可以显著提高单片机 的数据传输速度。 关键词 : 可编 程逻 辑器 件 C L V L语 言 ; M 控制器 P D;HD D A

维普资讯

No 2 . Ap . 2 0 r,07

微

处

理

机

第2 期

20 0 7年 4月

MI CR0P R0CES 0RS S

一

.

种基 于 C L P D的 D MA控 制器 I 设 计 P核

王笑怡 , 钟 哲, 郝 兵

( 中国电子科技集 团公司第四十七研 究所, 沈阳 10 3 ) 10 2

( h 7hR s r ntueo hn l t n s e nl yGop C r rt nS eyn 10 2 C i ) T e t e ac Is t 4 e h i t fC i Ee r i c oo ru o oai ,hnag 10 3 ,hn a co c T h g p o a

D 旭 2s R 出 P P F 输

控制信号, 修改地址 , 对传送字的个数计数 , 并且以 中断方式向 C U报告传送操作的结束 。 P

D A方式的主要优点是速度快 。由于 C U不 M P

—

—

—

f f ’ 一R 出J D P I L 输 数输 据出 F_ 输} C L 出

浮空 I 数据输入 I 浮空 IFL . C I

r  ̄ r c 2

2 D MA简介

D A数据传送是 由 D A控制器完成的。进行 M M 数据传输时, M D A控制器从 C U完 全接管对总线 P 的控制, 数据交换不经过 C U 而直接在 内存 和 IO P, / 设备之间进行 。D A控制器将 向内存发 出地址和 M