基于FPGA的NANDFLASH控制器

基于FPGA的异构计算单元数据动态分配控制器及方法

• 34•基于FPGA的异构计算单元数据动态分配控制器及方法扬州万方电子技术有限责任公司 陶 娅异构计算多单元的网络数据分配多在系统及软件层面解决,这就导致计算单元种类或数量较多的情况下适配困难、花费大等问题。

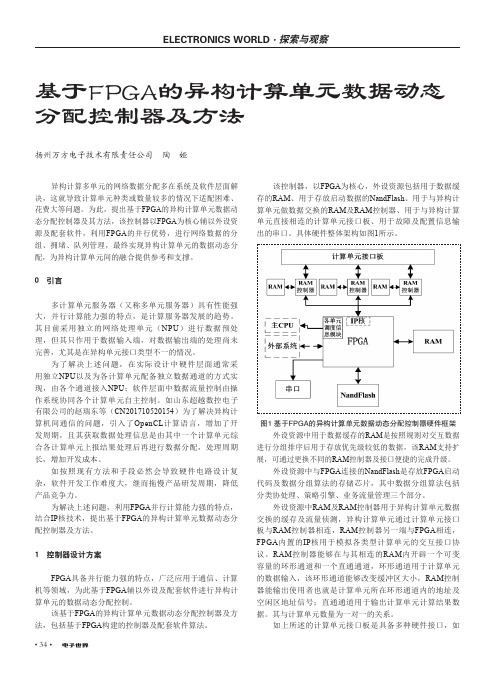

为此,提出基于FPGA 的异构计算单元数据动态分配控制器及其方法,该控制器以FPGA 为核心辅以外设资源及配套软件,利用FPGA 的并行优势,进行网络数据的分组、拥堵、队列管理,最终实现异构计算单元的数据动态分配,为异构计算单元间的融合提供参考和支撑。

0 引言多计算单元服务器(又称多单元服务器)具有性能强大,并行计算能力强的特点,是计算服务器发展的趋势。

其目前采用独立的网络处理单元(NPU )进行数据预处理,但其只作用于数据输入端,对数据输出端的处理尚未完善,尤其是在异构单元接口类型不一的情况。

为了解决上述问题,在实际设计中硬件层面通常采用独立NPU 以及为各计算单元配备独立数据通道的方式实现,由各个通道接入NPU ;软件层面中数据流量控制由操作系统协同各个计算单元自主控制。

如山东超越数控电子有限公司的赵瑞东等(CN201710520154)为了解决异构计算机间通信的问题,引入了OpenCL 计算语言,增加了开发周期,且其获取数据处理信息是由其中一个计算单元综合各计算单元上报结果处理后再进行数据分配,处理周期长,增加开发成本。

如按照现有方法和手段必然会导致硬件电路设计复杂,软件开发工作难度大,继而拖慢产品研发周期,降低产品竞争力。

为解决上述问题,利用FPGA 并行计算能力强的特点,结合IP 核技术,提出基于FPGA 的异构计算单元数据动态分配控制器及方法。

1 控制器设计方案FPGA 具备并行能力强的特点,广泛应用于通信、计算机等领域,为此基于FPGA 辅以外设及配套软件进行异构计算单元的数据动态分配控制。

该基于FPGA 的异构计算单元数据动态分配控制器及方法,包括基于FPGA 构建的控制器及配套软件算法。

基于FPGA的星载NANDFLASH控制器的设计

Abstract: In order to achieve efficient data storage in orbit satellite,this paper designs a NAND FLASH controller based on FPGA. The controller is compatible with commonly used asynchronous NAND FLASH,support for multiple NAND FLASH array ;support NAND FLASH operation timeout anomaly detection;support FLASH reset,read data,program,block erase,read ID and other commonly used functions. Select AHB bus,an efficient on- chip bus proposed by ARM Company. Design the AHB interface module and mount the FPGA module to the AHB bus. Through the Cortex-M3,transfer related commands and data to the underlying FPGA and achieve CPU + FPGA architecture. By simulation and board debugging,the design performance is stable,reducing power consumption,reaching the data storage rate of millisecond requirements. Key words: NAND FLASH;controller;AHB BUS;FPGA

在SOC中实现NandFlash控制器的一种方法

在S OC中实现Nand Fla sh控制器的一种方法肖 建(南京邮电学院 电子工程系,江苏南京210003)摘 要:N and F lash以其优越的特性和更高的性价比,在现代数码产品中得到了广泛的应用。

本文提出了在一款基于A RM7TDM I CPU COR E的片上系统(SOC)芯片中的N and F lash控制器的实现方案及其在U clinux下的驱动移植。

该设计方法已通过了R TL级验证、FGPA验证,并在实际芯片的演示样机上得到了具体实现。

关键词:SOC;N and F lash;驱动中图分类号:TN492;T P332 文献标识码:B文章编号:1008-0686(2004)04-0040-04A M ethod to Rea l ize Nand Fla sh Con troller i n S OC Ch ipX I AO J i an(N anj ing U niversity of P ost&T eleco mm unication,N anj ing210003,Ch ina)Abstract:B ecau se of its ou tstanding m erits and cheap er p rice,N and F lash has been w idely u sed in m any k inds of digital equ i pm en ts.T h is p ap er p resen ts a design m ethod of N and F lash con tro ller included in one k ind of SO C w h ich is based on A RM7TDM I,and related driverπs tran sp lan ting to U clinux is also in troduced.T h is con tro ller has p assed R TL verificati on and FPGA verificati on,and it is also u sed as a p art of dem o p ro to typ e now.Keywords:SO C;nand flash;driving 在当今数字技术飞速发展的时代,F lash因其非易失性及可擦除性而在数码相机、手机、个人数字助理(PDA)、掌上电脑、M P3播放器等手持设备中得到广泛的使用。

基于Xilinx FPGA的SPI Flash控制器设计与验证

备 , FG 使 P A一方面 与电脑 串 口通信获得数据 , 另一方面对 S IFah进行控制 , P ls 这样就完成了 F G P A配置数据 的控制 和存储 。

关 键词 : 可编程逻辑门阵列; 串行接口F s;el D ;i lhV ro H LIm仿真 a ig s

中图分 类号 : P 3 . T 3 21

( oi E e et , L gc lm n) 3 2个 1 bt BokR M模 块 , 8k ye的 lc A l 6个 1  ̄ 8b 嵌入式乘 法器 , 8 1 i t 2个锁 相环 ( L ) 4 PL和 个时钟管 理模 块 ( C 。在这 款 14针 tg封 装 的 D M) 4 q F G 中. PA 用户可用 I0为 12个 _ , / 0 3 可以满足本 系统 ] 的需求 。 Fah芯 片采 用 的 配置 芯 片 是 Wi o d公 司 的 l s n n b

关珊 珊 . 洁 敏 周

( 南京航空航天大学 民航学院 , 南京 2 0 1 ) 10 6

摘 要 : 基于 Xlx P A的SI lh i G i F n P a 控制器实现了一种在线配置Fa 的方法。由于 F s 芯片本身功能指令较多, Fs lh s lh a 使得对

它进行直接操作变得非常 困难 , 而利用 F G P A丰富的逻辑资源以及 产生精确 时序 的能力 , F G 以 P A为主设备 ,P l h为从设 SI a Fs

( il v t nClg ,a n n esyo eoats& At n ui ,aj g20 1 ) Cv i i o eeN g U irt iA a o l v i fA rn ui c s oatsN ni 10 6 r c n

Ab t a t S ls o tol rb s d o ln s r c : PIF a h c n r l a e n Xi x FPGA u sfr r id o n—i e c n iu a in meh d o l s e i p t o wa d a kn fo ln o fg r to to fF a h. Th l s h p i ef h s to mo e f cin i sr c in h tma e is ee t o e ain b c me v r d岱 c t b t e F a h c i t l a o r un to n tu t s t a k t d r c p r to e o e y i ul. u s o F PGA c u is rc o i e o r e n r d c sa c r t i n b lt . GA a e u e s ma t re u p n o c p e ih l gc r s u c s a d p o u e c u ae tmi g a iiy FP c n b s d a se q i me t a d S l s s sa e. PGA o n c si e iswih c mp trf rc mmun c to a a a q iiin a d c n r l h n PIF a h a l v F c n e t n s re t o u e o o iain d t c u sto n o to st e S l s n oh rh n h ti GA o fg r t n frc n r la d so a e h s b e mp e n e . PIF a h i t e a d t a t FP s c n u ai o o to n tr g a e n i lme t d i o Ke r s: GA; PIF a h; rlg HDL;i l t n y wo d FP S l s Ve io smu a i o

基于FPGA控制的NAND Flash存储设计

该存储 电路 主要完成对数据 的实时存储及操

作, 电源模块对其他模块供 电, 使其 进入正常工作

状态 ; 高速数据接收发送模块实现数据的高速 长距

离传输 , 其 一般采 用 L V D S , H o t l i n k芯片实 现此功 能; F P G A作为整个存储 电路的控制核心 , 接收上级

以扩展 到所有类似 F l a s h存储 系统 中, 对其他 的电路具 有一定 的借鉴意义。 关键词 F la s h F P G A 三线控制 无效块地址列表

中图法分类号

T P 3 3 3 ;

文献标志码

A

现代信息存 储技术 中对存储器 的容量和速度 及存储可靠性提出越来越高 的要求 , 而传统的存储 器件如 D R A M, S R A M, E P R O M, E E P R O M 等 由于 容 量小 、 速度低等缺点无法满足高速大容量存储 的技 术要求 , F l a s h因其具有体积小 、 成本低 、 功耗小 、 寿 命长 、 存储密度 高等特点 , 逐 渐成为高速 大容量存 储系统设计 的主流方案 。F l a s h存储是一种非易

图2 F P G A控 制模 块 设 计 框 图

表 1 状态线组合指令定义

制模块 , 另一个功能是将接收或发送 的数据进行 串

图 1 系 统 硬 件 结 构 框 图

易实现大容 量存储 , 而且其读写 和擦除速度很 快 , 其缺点是逻辑控制 比较复杂, 需要 相应 的逻辑控制

器件如单片机 , C P L D , F P G A等对 其进行逻辑控 制 , 其中 F P G A由于时钟频率高、 内部延时小 、 全部控制 逻辑 由硬件完成 、 速度快 、 效率高 以及丰富 的逻

基于FPGA的K9F2G08U0M Nand FLASH控制器设计

收稿 日期 :0 7 0 — 4 20 - 9 1

(k 6 ) 2 ~ 2 2 + 4。A 8 A1 被称 为行地 址 ,即页地址 。

. d. e an c c

4

电 子元 器 件 主 用 20 . 0 83

Ⅳ03 IO IO5 IO6 IO7 /4 / / /

Ⅲ

1 期 周 2 期 周

M o

o

\_ _,

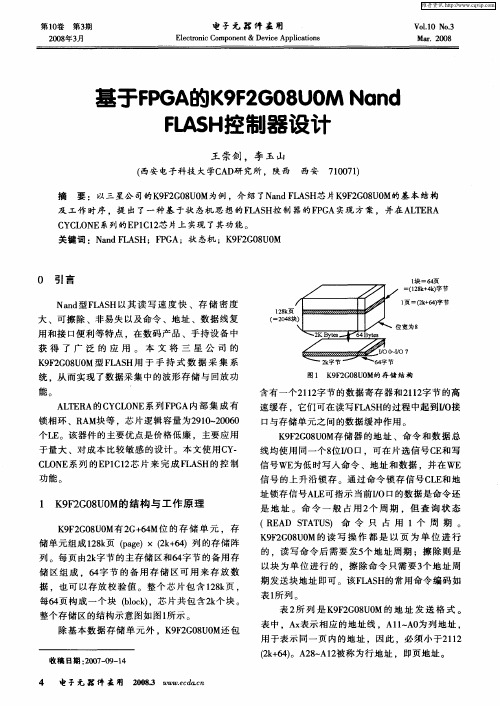

表1 所列 。 表2 列 是K FG 8 O 所 9 2 0 U M的 地 址 发 送 格 式 。 表 中 。A 表示相 应 的地 址线 ,A1- 0 x l A 为列 地址 。 用于表 示 同一页 内的地 址 ,因此 。必 须小 于2 1 12

据 ,也 可 以存 放 校验 值 。 整个 芯 片包 含 1 8 页 , 2k 每 6 页构成 一 个块 (l k 。芯 片共 包 含2 个块 。 4 bo ) c k 整个 存储 区的结构 示意 图如 图 l 所示 。

加

舭

脚

。

除命 令要 将 所有2 4 个 块擦 除一遍 。擦除 一个 块 08 的时序 如 图3 示 。 所

CE L 八 几 门

枷

衰 2 F A H地 址发 送 格 式 LS

IO0 / Ⅳ01 Ⅳ02

。

。

。

西 _\ _

W E ALE RE

维普资讯

第 1卷 O

第3 期

电 子元 嚣 件 主 用

E e t n cCo o e t De ieAp l ain lcr i mp n n & o vc p i t s c o

基于FPGA的NAND Flash坏块处理方法

2 Grd ae i. f ieeA ae f ce csB in 0 0 9 3 Hu o gTanOprt nDeo, a u al yB ra , ao g0 7 0 ) a ut v o ns c dmyo ine, e ig1 0 3 ; . d n ri Un Ch S j eai p tT i a R i ueu D tn 3 0 3 o yn wa

[ src] miga erq et f tblyo aas rg b u AND Fah ti pp r n lzsh i d atg s frdt nl a desh me Ab ta t Ai n th u so a it f t t aeao t t e s i d o N ls,hs ae aye eds vnae a io a n l c e a t a ot i h

F GA o s i l h a l c . i t o h r u h y e i i a e n u n e o t ro e a i n c u e y b d b o k By usn h sme h d d t P t h e d t e b d b o k Th s me h d t o o g l l n t s t i f e c n o he p r t a s d b a l c . i g t i t o , a a m he l o

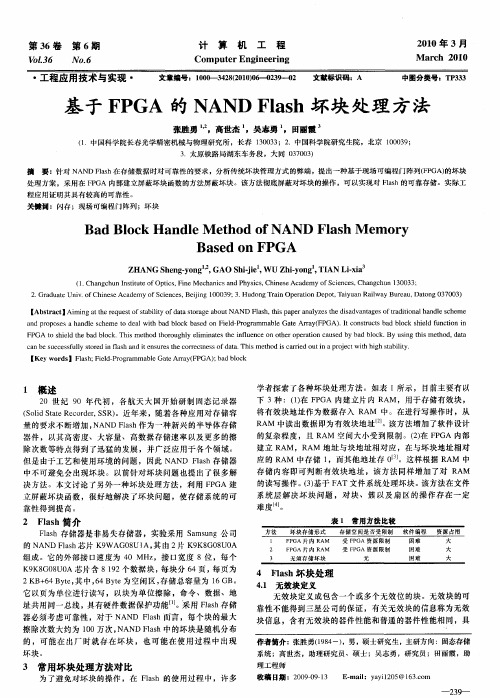

l 概 述

2 0世纪 9 0年代 初 ,各航 天大 国开 始研制 固态记 录器 (oi tt R c re S R 。近年来 ,随着各种应用对存储容 S l Sa eodr S ) d e , 量 的要求不断增加 , A ls N NDFah作为一种新兴 的半导体存储 器件 ,以其高密度、大容量、高数据存储速率以及更多的擦 除次数 等特点得到 了迅猛 的发展 ,并广泛应 用于各个领域 。 但是 由于工艺和使用环境的问题,因此 N ND Fah存储器 A ls 中不可避免会 出现坏块 。以前针对坏块 问题也提 出了很多解

xilinx的fpga读取flash的原理

xilinx的fpga读取flash的原理一、概述Xilinx的FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,广泛应用于工业和消费电子领域。

Flash存储器是FPGA 的一种重要外部存储设备,用于存储FPGA的配置信息和其他需要长期保存的数据。

本文将介绍Xilinx的FPGA读取Flash的原理,包括Flash存储器的基本原理、FPGA与Flash的接口设计、数据传输方式以及读取Flash的控制逻辑。

二、Flash存储器原理Flash存储器是一种非易失性存储器,可以像硬盘一样进行写入和擦除操作。

它主要由存储单元和外围电路组成,存储单元通常采用浮栅晶体管结构。

写入操作时,Flash通过把掺杂剂注入到浮栅中来改变浮栅电导率,从而实现电荷的存储。

擦除操作时,通过改变浮栅的电场强度来移除注入到浮栅中的电荷,从而恢复到原始状态。

读取操作时,通过测量电荷的变化来确定存储单元的值。

三、FPGA与Flash接口设计FPGA与Flash之间的接口设计是实现数据传输和控制的关键。

Xilinx的FPGA通常采用AXI-Stream接口与外部设备进行数据传输。

AXI-Stream接口是一种通用的、基于流的接口,适用于高性能数据传输。

FPGA与Flash之间的接口通常包括以下部分:1. 物理层:包括总线协议和物理连接方式,如PCIe、USB、SPI 等。

2. 数据层:用于传输数据和控制信号,包括地址、读写控制信号和数据信号。

3. 控制层:用于实现数据的读取、写入和擦除操作,包括命令、状态机和中断信号。

四、数据传输方式FPGA读取Flash的数据传输方式通常采用AXI-Stream流接口进行数据传输。

FPGA通过发送AXI-Stream控制指令来控制Flash的数据传输,包括数据的起始地址、传输速率和传输周期等。

Flash则根据FPGA的控制指令进行数据的读取和传输。

在数据传输过程中,FPGA和Flash之间需要进行时钟同步和数据校验,以确保数据传输的准确性和完整性。

NAND FLASH 控制器的FPGA实现

为了控制方便,本设计中包含一个写数据 RAM[4]和一个读数据 RAM[4],同时包含两个 RAM 控制器。写数据 RAM 控制器实现了一端从外部连续写入数据,一端读出数据给调用 的程序写入到芯片内部。考虑到芯片写入数据是以页为单位,每页数据是 512+16 字节,该 控制器内设计了一个计数器,当计数器的值少于 600 时不进行数据读出,当计数器的值多于 1200 时可以进行数据读出。读数据 RAM 控制器实现了一端把从芯片里读出的数据写入到该 RAM 中,一端把数据输出给用户。读数据 RAM 控制器内也设计了一个计数器,当计数器 的值少于 600 时不进行数据输出,当计数器的值多于 1200 时可以进行数据输出。

地址映射过程:执行块扫描功能时将每一个好块的地址(12 位)依次写入 RAM 中(作 为地址映射 RAM),然后再写入第一块中。由于数据是 8 位,所以每个好块地址要占用一 个半字节,控制器为每个好块地址提供两个字节存放空间,前 12 位为有效地址。用户通过 NAND FLASH 控制器使用 FLASH 时,只要给定 12 位地址,控制器内部通过访问好块地址 映射 RAM,就可以把用户的 12 位地址对应到有效的好块地址。

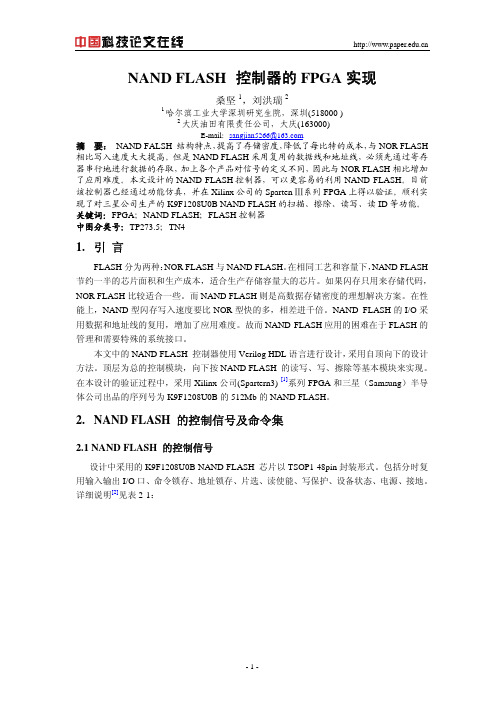

3.4 顶层控制模块

顶层控制模块主要完成各个子功能模块之间的切换,根据低层模块功能,状态机[5]分为 如下状态:空闲状态、读地址状态、读数据状态、写地址状态、擦除状态、写数据状态、扫 描状态、等待状态。其状态转换图如图 3-3

-4-

http://www.papeLeabharlann

图 3-3 顶层控制状态转换图 Fig.3-3 Chart of Top Control State

-1-

符号 I/O0I/O7 CLE ALE CE

fpga中flash存储数据和程序的方法

fpga中flash存储数据和程序的方法

在FPGA中,通常使用flash存储器来存储数据和程序。

FPGA开发板上一

般都有一个或多个flash存储器芯片,如NOR flash或NAND flash。

以下是fpga中flash存储数据和程序的方法:

1. 编程flash存储器:使用FPGA开发工具(如Xilinx Vivado、Altera Quartus等)将数据和程序编译成二进制文件,然后将这些文件下载到FPGA的flash存储器中。

在FPGA上电后,这些数据和程序会自动从flash 存储器中加载到FPGA的内部RAM中,供FPGA使用。

2. 擦除和重新编程:如果需要更新FPGA中的数据或程序,可以使用FPGA 开发工具重新编译和下载新的二进制文件到flash存储器中。

在更新之前,

需要先擦除旧的二进制文件。

可以使用FPGA开发工具提供的擦除功能来擦除整个flash存储器,或者只擦除特定的区域。

3. 保护和加密:为了保护flash存储器中的数据和程序不被非法访问或修改,可以使用FPGA开发工具提供的保护和加密功能。

这些功能可以限制对flash存储器的访问权限,或者对flash存储器中的数据进行加密和解密。

4. 硬件锁:一些FPGA开发板还提供了硬件锁功能,用于锁定整个flash存储器或其中的特定区域。

通过使用硬件锁,可以防止未经授权的访问和修改flash存储器中的数据和程序。

需要注意的是,不同的FPGA开发工具和flash存储器芯片可能有不同的操作方法和特性。

因此,在使用之前,建议先仔细阅读相关的技术文档和用户手册。

基于FPGA的SDRAM控制器的设计与实现

基于FPGA的SDRAM控制器的设计与实现1.设计SDRAM控制器的功能:SDRAM控制器的主要功能是控制SDRAM的读写操作,包括地址、数据和控制信号的生成以及时序管理。

其次,还需要实现初始化、写入数据、读取数据等相关功能。

2.确定SDRAM的总线类型:SDRAM控制器需要根据不同的SDRAM接口类型进行设计,例如,DDR、SDR、LPDDR等。

不同的接口类型有不同的时序和数据传输方式,因此根据使用的SDRAM类型确定总线宽度、传输速率和时序约束等。

3.确定FPGA型号和资源:根据SDRAM控制器的设计规模和FPGA的资源情况选择合适的FPGA型号。

资源包括逻辑门、存储器单元、DSP片等,选择合适的型号可以满足设计要求并提高系统性能。

4.设计时序控制电路:根据SDRAM的时序要求,设计时序控制电路来实现SDRAM读写操作的同步和序列控制。

时序控制电路通常包括时钟分频模块、时钟同步模块、读写状态机和地址计数器等功能模块。

5.实现控制信号与FPGA引脚的映射:将SDRAM控制器内部产生的控制信号映射到FPGA引脚上,以便与SDRAM进行数据的传输和时钟同步。

通过FPGA引脚的选择和约束来满足SDRAM接口要求。

6.进行功能仿真和时序分析:在FPGA设计工具中进行功能仿真和时序分析,验证SDRAM控制器的设计是否满足功能要求,并检查时序约束是否满足。

7.进行硬件布局和布线:根据FPGA设计工具生成的后端文件,进行硬件布局和布线,将逻辑电路映射到FPGA芯片上,并考虑时序约束和引脚约束等因素,以满足设计要求。

8.进行SDRAM控制器的验证和调试:通过连接SDRAM和FPGA开发板,验证SDRAM控制器的读写操作是否正常,检查数据的正确性和时序的准确性。

9.进行性能优化和资源利用:根据实际需求,考虑对SDRAM控制器进行性能优化,例如增加缓存、提高数据通路宽度等。

同时,优化资源利用,减小逻辑门延迟和功耗等。

基于FPGA和NAND Flash的存储器ECC设计与实现

点。该设计 已应 用于某 星载存储 系统 中,为存储 系统的可靠性提供 了 保证 。

关键词 FG P A;N N ls ;E C算 法 A D Fah C

T 7 N9 文献标识码 A 文章 编号 10 7 2 (0 2 1 0 0— 4 0 7— 80 2 1 )0— 7 0 中图分类号

h s ar a y b e p le n as tli y tm oe s r her l ii ft e so a e s se . a e d e n a p id i ael e s se t n u e t ei l y o h tr g y tm l t b a t Ke wo ds F GA ; NAND fa h; ECC ag rt m y r P s l oi l h

近年 来 , 益 于 大 规 模 集 成 电路 技 术 的 发 展 , 得 以 N N ls 代 表 的 半 导 体 固态 存 储 器 发 展 迅 速 。 A D Fah为 与 传统 的磁 带记 录设 备 相 比, A D Fah具有 存 储 密 N N ls 度高、 靠性强、 可 体积 小 、 量 轻 、 作 速 度 快 、 量价 重 操 容

c n rlc i ft esoa es se o to hp o trg y tm. T ru h c mp rn h woECC c d sc lu ae rm h trd d t u n e d h h o g o a ig te t o e ac ltd fo tesoe aa d r g ra i a d wrt p r t n, b te o a elc td a d c re td, a d t e c re tn a a i t s 1 b t4 k n i o eai e o i r rc n b o ae n o rce n h o cig c p bl y i i/ B. Th i e ECC ag rt m a h d a tg s o o d c re tn a a ii lo h h ste a v na e fg o o ci g c p bl y, ls e o r e e ur me ta d h g p e . T e d sg i t es r su c sr q ie n n ih s e d h e in

fpga与外部并行flash读写的工作原理

文章标题:深度解析FPGA与外部并行Flash读写的工作原理在当今数字化时代,数据处理和存储的需求呈指数级增长。

作为一种可编程逻辑设备,FPGA(Field-Programmable Gate Array)以其灵活性和高性能成为了处理大规模数据的首选之一。

而外部并行Flash则作为一种常见的非易失性存储器,被广泛应用于嵌入式系统和通信设备中。

本文将从FPGA与外部并行Flash的基本工作原理、数据读写流程、优缺点及应用场景等方面进行深入探讨,并将结合个人观点和理解,为读者全面解析这一主题。

一、FPGA与外部并行Flash的基本工作原理1. FPGA的基本工作原理FPGA是一种可编程逻辑设备,其基本工作原理是通过配置可编程逻辑单元和可编程互连资源,从而实现不同的逻辑功能。

其内部包含大量的可编程逻辑单元和存储单元,用户可以根据实际需求对FPGA进行编程,从而实现各种复杂的逻辑功能与算法。

FPGA的高度灵活性和并行处理能力,使其成为处理各种实时数据处理和控制任务的理想选择。

2. 外部并行Flash的基本工作原理外部并行Flash是一种非易失性存储器,其基本工作原理是通过使用并行接口来进行高速数据读写。

它通常由多个存储单元组成,并且可以同时进行多个存储单元的读写操作,从而大大提高了数据的传输速度。

外部并行Flash具有容量大、数据读写速度快等优点,被广泛应用于嵌入式系统和通信设备中。

二、数据读写流程1. FPGA与外部并行Flash的连接FPGA与外部并行Flash通常通过并行接口进行连接,这要求它们之间的数据传输速度要相匹配。

在实际连接中,需要考虑时序同步、数据稳定性等因素,以确保数据的可靠传输。

2. 数据读写流程在进行数据读写时,首先FPGA通过控制信号将所需的数据位置区域发送给外部并行Flash,然后外部并行Flash根据位置区域识别并读取相应的数据。

在写操作时,FPGA同样通过控制信号将待写入的数据发送给外部并行Flash,外部并行Flash将数据写入相应的存储单元中。

flash芯片fpga读写原理

flash芯片fpga读写原理

flash芯片FPGA的读写原理主要基于SPI协议。

SPI协议是一种同步全双工通信协议,通常有一个主设备和一个或多个从设备。

在Flash芯片FPGA的读写过程中,主设备通

过SPI协议向Flash芯片发送指令和数据,实现对Flash芯片的读写操作。

具体来说,Flash芯片FPGA的读写操作可以分为以下步骤:

1.上位机主动发起配置,FPGA被动接收数据进行重配置,此时的配置模式是基于JTAG的被动配置。

此操作的结果是

将FPGA配置为一个Flash的读写器。

2.配置完成后,上位机开始发送/接收Flash的数据,

数据通道为JTAG。

FPGA通过JTAG接收到数据之后,根据需求发起对Flash的读写操作,将需要更新的数据写入Flash,完成更新。

此过程是更新Flash的过程,烧录过程中Flash

只收到FPGA的控制。

3.Flash更新完毕后,在合适的时候让FPGA进行重新配置(例如重新上下电),FPGA会开始主动配置过程,从Flash

中读取配置数据完成加载。

配置过程是将原厂提供的

JTAG-Flash读写控制器加载到FPGA中,在通过JTAG和这个内部的FPGA控制器烧录Flash。

以上信息仅供参考,如需获取更多详细信息,建议咨询专业技术人员。

fpga毕业设计任务书

[5]夏宇闻.《Verilog数字系统设计》,北京:北京航空航天大学出版社,2004:120-126.

[6]王等,吴继华,范丽珍,等.AlteraFPGA/CPLD设计[M].北京:人民邮电出版社,2005

毕业设计(论文)题目:

基于FPGA的NAND Flash控制器设计

一、毕业设计(论文)内容及要求(包括原始数据、技术要求、达到的指标和应做的实验等)

1提供条件:

PC机,FPGA开发板,USB等数据线,数码管,flash存储器

2设计内容与要求:

(1)查阅有关资料,了解FLASH Memory的分类和NAND FLASH的一些基本知识

[7]王崇剑,李玉山.基于FPGA的K9F2G08UOM NAND Flash控制器设计[J].电子元器件应用,2008,10(3):4- 7.

系(教研室)主任:(签章)年月日

学院主管领导:(签章)年月日

6.5.15~6.3,撰写论文

四、主要参考资料(包括书刊名称、出版年月等):

[1]孙航,《Xilinx可编程逻辑器件的高级应用与设计技巧》[M],北京:电子工业出版社,2004:35-60.

[2] SAMSUNG..K9F1028U0B. Data Sheet. 2004:6-21.

[3]王冠.《Verilog HDL与数字电路设计》[J],北京:机械工业出版社,2006:4-7.

2.3.19~3.31,熟练使用Quartus II 9.0、NIOS II,了解基本Verilog语言

3.4.1~4.22,编写程序,能把数据输入Flash中并在数码管上显示出来

21-22、NandFlash控制器

//写入地址 列地址(页内地址) NF_ADDRESS(nColAddr & 0xFF); NF_ADDRESS(((nColAddr >> 8)& 0xF)); NF_ADDRESS((nRowAddr >> 0) & 0xFF);

行地址(即页地址)

NF_ADDRESS((nRowAddr >> 8) & 0xFF); NF_ADDRESS((nRowAddr >> 16) & 0x1);

NandFlash控制指令

NandFlash控制指令

NandFlash控制指令

NandFlash控制指令

NandFlash控制指令

NandFlash控制指令

NandFlash控制指令

NandFlash控制指令

NandFlash控制指令

NandFlash控制指令

NandFlash控制指令

• Block:是组成Nand Flash的最大单元,它由若干个 Page组成,Block的个数由Nand Flash的具体容量决定。 Block是Flash擦除的最小单位. • Page: 是Nand Flash的基本读写单位,Page内部划分 为主数据区(Main Area)和备用区(Spare Area)两块区域, 主数据区用于存储写入Flash的数据.备用区一般用于保存该 Page存储属性和数据ECC校验值等信息. • 目前Nand Flash的Page主要有 (512+16)Bytes和 (2048+64)Bytes两种规格,我们通常也忽略掉备用区的 字节数称之为Page大小为512Bytes和2Kbyte的Flash.

NandFlash组成结构

fpga中flash的作用

fpga中flash的作用FPGA中的Flash:存储和配置的关键在现代电子设备中,FPGA(现场可编程门阵列)是一种重要的集成电路,它具有灵活性和可重配置性。

而FPGA中的Flash存储器起着至关重要的作用,它不仅用于存储配置文件,还承担着其他关键任务。

本文将深入探讨FPGA中Flash的作用,以及它在电子设备中的重要性。

一、存储配置文件FPGA的核心是其可编程逻辑单元(PL)和可编程间连单元(IOB),它们可以按照特定的需求进行重新配置。

而FPGA中的Flash存储器用于存储配置文件,这些文件包含了FPGA的逻辑功能、连接和I/O设置等信息。

每当设备上电或重新启动时,FPGA都会从Flash 中加载这些配置文件,从而确保FPGA能够按照预定的逻辑和连接方式工作。

二、提供非易失性存储与传统的SRAM(静态随机存储器)相比,FPGA中的Flash存储器具有非常重要的优势,即它是一种非易失性存储器。

这意味着即使在设备断电或重新启动后,Flash存储器中的数据仍然能够保持不变。

这为FPGA的配置提供了可靠的保护,确保设备在断电后能够恢复到上一次的配置状态。

三、支持在线更新FPGA中的Flash存储器还支持在线更新,这意味着可以通过软件更新FPGA的配置文件,而不需要重新烧录Flash存储器。

这种灵活性使得FPGA能够随时适应新的需求和功能,而无需停机或更换硬件。

在线更新还可以提高设备的可维护性和可扩展性,减少了对硬件更改的依赖。

四、存储其他重要数据除了配置文件外,FPGA中的Flash存储器还可以用于存储其他重要数据,例如校准参数、设备序列号、加密密钥等。

这些数据对于设备的正常运行和安全性至关重要。

通过将这些数据存储在Flash中,可以确保它们在设备断电或重新启动后仍然可用。

五、实现快速启动FPGA中的Flash存储器还可以用于实现快速启动功能。

在设备上电或重新启动时,FPGA可以直接从Flash中加载配置文件,而无需等待外部存储器的加载。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

刘思平等 :基于 FP GA 的 NAND FL A S H 控制器

基于 FPGA 的 NAND FLASH控制器

刘思平 ,陈利学

(西南石油大学 研究生院 四川 成都 616000)

摘 要 :主要介绍现场可编程阵列 FP GA 在 NAND FL ASH 芯片测试仪系统中的应用 ,由于芯片本身内部结构非常复 杂 ,还可以允许坏块的存在 ,而且坏块的数目在使用过程中还可以增加 ,这使得对芯片进行操作变得非常难 ,而利用 FP GA 对 NAND FL AS H 进行控制 ,可以非常方便地对他进行读写 、擦除以及坏块判断等几种重要的操作 ,从而能快捷 、准确 、稳定 地测试出芯片的好坏 ,为 NAND FL ASH 厂商和用户提供更为准确的判断依据 。

3 擦除操作

一 般 芯 片 进 行 PRO GRAM/ ERASE 的 次 数 是 100 000 cycles ,第一个 BLOC K 次数更多 , 一般可用于存 放 boot code 或 者 重 要 的 信 息 。由 于 擦 除 操 作 是 以 BLOC K 为基准 ,也就是每执行一次擦除操作将会擦除指 定的 BLOC K ,所以在执行擦除时必须注意共享区域里的 重要信息如坏块标识 、ECC 校验等 。以免被擦除掉 ,擦除 掉了及时恢复 ,擦除操作仿真如图 5 所示 。

参 考 文 献

[ 1 ] 王等 ,吴继华 ,范丽珍 ,等. Altera FP GA/ CPLD 设计[ M ] . 北 京 :人民邮电出版社 ,2005.

[ 2 ] 2 4 8gb nand m49a 1. f m - Rev. B 4/ 06 EN. Mi2 cron Technology ,Inc.

关键词 :NAND FL ASH ; FP GA ;V HDL ;BLOC K; PA GE ;Modelsim 中图分类号 : TP273 文献标识码 :B 文章编号 :1004 - 373X(2007) 09 - 134 - 02

NAND FLASH Controller Based on FPGA

以及容量大小 ,这些重要的信息是判断 NAND FLASH 的 重要凭证 ,因此将这些信息读出来加以判断就显得特别重 要 。在 CL E 为高 , WE # 上升沿 ,在 I/ O 输入 90 H 命令让 NAND FLASH 进入读 ID 状态 ,接着在 AL E 为高 ,WE # 上 升沿 ,在 I/ O 输入 00 H 地址 ,在等待 t WHR 将 RE # 置为 读 ,在 RE # 连续 4 个上升沿将 ID 读 出。仿真 图 如图 2 所示。 2. 2 判断坏块

Keywords :NAND FL ASH ; FP GA ;V HDL ;BLOC K; PA GE ;Modelsim

1 引 言

在便携式电子产品如 U 盘 、MP3 播放器 、数码相机 中 ,常常需要大容量 、高密度的存储器 , 而在各种存储器 中 ,NAND FL AS H 以价格低 、密度高 、效率高等优势成为 最理想的器件 。但 NAND FL AS H 的控制逻辑比较复杂 , 对时序要求也十分严格 ,而且最重要的是 NAND FL AS H 中允许存在一定的坏块 (坏块在使用过程中还可能增加) , 这就给判断坏块 、给坏块做标记和擦除等操作带来很大的 难度 ,于是就要求有一个控制器 ,使系统用户能够方便地 使用 NAND FL AS H , 为 此 提 出 了 一 种 基 于 FP GA 的 NAND FL AS H 控制器的设计方法 ,并用 V HDL 给予实 现 , Modelsim 得 出 仿 真 结 果 , 并 在 AL TERA 公 司 的 EP2C35 F672 器件中得到验证 。FP GA 与 NAND FL AS H 接口图如图 1 所示 。

《现代电子技术》(半月刊) 欢迎刊登广告 029 - 85393376

135

NAND FL AS H 作为一种特殊的储存器件 ,内部集成 电路使得 BLOC K 与 BLOC K 是相互独立的 ,因此一定数

《现代电子技术》2007 年第 9 期总第 248 期

测试 ·测ቤተ መጻሕፍቲ ባይዱ ·自动化

目坏块的存在不会影响其他 BLOCK。但坏块总数是有一 定的限制的 ,超过一定的数目后器件将认为不能再使用 。 在出厂前厂家会在器件的每个 BLOC K 的第一页和第二 页的列地址为 2048 标注上坏的信息 , FFh 代表此 BLOC K 是好 ,非 FFh 代表此 BLOCK 是坏 。但是这些重要信息在 执行 Erase 和 Programming 命令的时候会被擦除掉 , 因 此 ,我们在做这些操作之前应该将坏块识别出来如图 3 所 示 ,并加以标注或者用好的块来代替 ,以方便以后的访问 。 随着使用时间的推移 ,坏块的数目还会增加 ,因此我们必 须随时更新坏块链表 。坏块识别时序仿真图如图 4 所示 。

5 结 语

在实际应用中 ,使用 AL TERA 公司的 Cyclone2 FP2 GA 器件进行设计 ,设计输入采用 V HDL 来完成 ,实现了 上述的 NAND FL AS H 控制器接口电路 。此外 ,由于采用 了通用性设计思想 ,可以对不同厂家不同的芯片进行控制 和操作 ,具有一定的通用性 。

图 2 NAND FL ASH READ ID 仿真图 图 3 坏块识别流程

图 4 坏块识别时序仿真图

图 5 擦除操作仿真

4 编程操作及其他操作

编程操作和擦除操作相似 ,只不过编程操作是以页为 单位 ,在执行编程操作时同样也要注意共享区域里的重要 信息以免被覆盖掉 ,重要信息被覆盖后要及时恢复 。其他 操作如复位还有有些芯片厂家各自新的操作等 ,但总体来 说主流芯片都支持以上几种操作 。

L IU Siping ,C H EN Lixue

( Graduate School ,Sout hwest Pet relum University ,Chengdu ,616000 ,China)

Abstract : The paper mainly int roduces FP GA in t he chip tester system application. As t he chip it self is very complicated st ruct ure ,it allows t he existence of bad blocks ,t he number of bad blocks in t he use of t he p rocess can still increase ,it operat s t he chip has become very difficult . And t he use of NAND FL ASH FP GA cont rol ,it is very co nvenient for reading ,writing ,e2 rasing and bad block judgment of several pieces of important operatio nal. So it can quickly and accurately test t he stability of t he chip is good o r bad for NAND FL ASH manufact urers and users wit h a more accurate basis for t he judgment .

PA GE ,每个 NAND FL AS H 器件把 BLOC K , PA GE 按照 行列地址进行寻址 ,基于这种特殊的结构 ,NAND FL AS H 有如下工作特性 :

图 1 FP GA 与 NAND FL ASH 接口

2. 1 R EAD ID NAND FLASH 器件 ID 包括 :Manufacture ID ,device ID

[ 3 ] 256 M ×8 bit / 128 M ×16 bit NAND Flash Memory. SA2 MSUN G Elect ronics Co . ,L td.

[ 4 ] NAND Flash Spare Area Assignment Standard. Samsung Elect ro nics Co . ,L td. 27. Ap ril. 2005.

2 NAND FLASH 操作

NAND FL AS H 器件的管脚分为控制信号 、I/ O 二类 , 地址和数据是复用 I/ O 管脚 。通常 NAND FL AS H 器件 包括 一 定 数 目 BLOC K , 每 个 BLOC K 包 括 一 定 数 目 的

收稿日期 :2006 - 09 - 13 134