PDTA144WE中文资料

W144资料

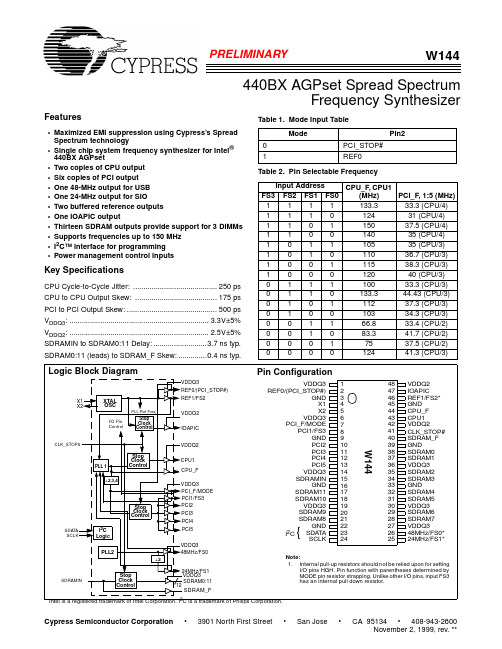

PRELIMINARY440BX AGPset Spread SpectrumFrequency SynthesizerW144Features•Maximized EMI suppression using Cypress’s Spread Spectrum technology•Single chip system frequency synthesizer for Intel ® 440BX AGPset•Two copies of CPU output •Six copies of PCI output •One 48-MHz output for USB •One 24-MHz output for SIO•Two buffered reference outputs •One IOAPIC output•Thirteen SDRAM outputs provide support for 3 DIMMs •Supports frequencies up to 150 MHz •I 2C™ interface for programming •Power management control inputsKey SpecificationsCPU Cycle-to-Cycle Jitter: .........................................250 ps CPU to CPU Output Skew: ........................................175 ps PCI to PCI Output Skew:............................................500 ps V DDQ3:....................................................................3.3V±5%V DDQ2:....................................................................2.5V±5%SDRAMIN to SDRAM0:11 Delay:..........................3.7 ns typ.SDRAM0:11 (leads) to SDRAM_F Skew:..............0.4 ns typ.Table 1.Mode Input TableModePin20PCI_STOP#1REF0Table 2.Pin Selectable FrequencyInput Address CPU_F, CPU1 (MHz)PCI_F, 1:5 (MHz)FS3FS2FS1FS01111133.333.3 (CPU/4)111012431 (CPU/4)110115037.5 (CPU/4)110014035 (CPU/4)101110535(CPU/3)101011036.7 (CPU/3)100111538.3 (CPU/3)100012040 (CPU/3)011110033.3 (CPU/3)0110133.344.43 (CPU/3)010111237.3 (CPU/3)010010334.3 (CPU/3)001166.833.4 (CPU/2)001083.341.7 (CPU/2)00017537.5 (CPU/2)000012441.3 (CPU/3)Intel is a registered trademark of Intel Corporation. I 2C is a trademark of Philips Corporation.Logic Block DiagramVDDQ3REF0/(PCI_STOP#)VDDQ2CPU1PCI_F/MODE XTAL PLL Ref FreqPLL 1X2X1REF1/FS2VDDQ3Stop Clock ControlStop Clock ControlPCI2PCI3PCI448MHz/FS024MHz/FS1PLL2÷2,3,4OSCVDDQ2CLK_STOP#VDDQ3IOAPIC PCI5I 2C SDA TA Logic SCLKI/O Pin ControlSDRAM0:11SDRAMIN12VDDQ3PCI1/FS3Stop Clock ControlStop Clock ControlCPU_F ÷2SDRAM_FPin ConfigurationVDDQ3REF0/(PCI_STOP#)GND X1X2VDDQ3PCI_F/MODEPCI1/FS3GND PCI2PCI3PCI4PCI5VDDQ3SDRAMINGND SDRAM11SDRAM10VDDQ3SDRAM9SDRAM8GNDSDA TA SCLKW144VDDQ2IOAPIC REF1/FS2*GND CPU_F CPU1VDDQ2CLK_STOP#SDRAM_F GND SDRAM0SDRAM1VDDQ3SDRAM2SDRAM3GND SDRAM4SDRAM5VDDQ3SDRAM6SDRAM7VDDQ348MHz/FS0*24MHz/FS1*484746454443424140393837363534333231302928272625123456789101112131415161718192021222324I 2C{Note:1.Internal pull-up resistors should not be relied upon for settingI/O pins HGH. Pin function with parentheses determined by MODE pin resistor strapping. Unlike other I/O pins, input FS3 has an internal pull down resistor.元器件交易网Pin DefinitionsPin Name Pin No.PinType Pin DescriptionCPU_F44O Free-running CPU Clock: Output voltage swing is controlled by the voltage applied toVDDQ2. See T ables 2 and 6 f or detailed frequency information.CPU143O CPU Clock Output 1: This CPU clock output is controlled by the CLK_STOP# controlpin. Output voltage swing is controlled by voltage applied to VDDQ2.PCI2:510, 11, 12,13O PCI Clock Outputs 2 through 5: These four PCI clock outputs are controlled by the PCI_STOP# control pin. Output voltage swing is controlled by voltage applied to VDDQ3.PCI1/FS38I/O Fixed PCI Clock Output: As an output. frequency is set by the FS0:3 inputs or throughserial input interface, see Tables 2 and 6. This output is affected by the PCI_STOP# input.When an input, latches data selecting the frequency of the CPU and PCI outputs.PCI_F/MODE7I/O Fixed PCI Clock Output: As an output, frequency is set by the FS0:3 inputs or throughserial input interface, see T ables 2 and 6. This output is not affected by the PCI_STOP#input. When an input, sets function of pin 2.CLK_STOP#41I CLK_STOP# input: When brought LOW, affected clock outputs are stopped LOW aftercompleting a full clock cycle (2–3 CPU clock latency). When brought HIGH, affected clockoutputs start, beginning with a full clock cycle (2–3 CPU clock latency).IOAPIC47O IOAPIC Clock Output: Provides 14.318-MHz fixed frequency. The output voltage swingis controlled by VDDQ2. This output is disabled when CLK_STOP# is set LOW.48MHz/FS026I/O48-MHz Output: 48 MHz is provided in normal operation. In standard systems, this outputcan be used as the reference for the Universal Serial Bus. Upon power-up FS0 input willbe latched, which will set clock frequencies as described in T able 2.24MHz/FS125I/O24-MHz Output:24 MHz is provided in normal operation. In standard systems, this outputcan be used as the clock input for a Super I/O chip. Upon power-up FS1 input will belatched, which will set clock frequencies as described in T able 2.REF1/FS246I/O I/O Dual-Function REF0 and FS2 pin: Upon power-up, FS2 input will be latched, whichwill set clock frequencies as described in Table 2. When an output, this pin provides afixed clock signal equal in frequency to the reference signal provided at the X1/X2 pins.REF0/(PCI_STOP#)2I/O Fixed 14.318-MHz Output 0 or PCI_STOP# Pin: Function determined by MODE pin.The PCI_STOP# input enables the PCI 1:5 outputs when HIGH and causes them toremain at logic 0 when LOW. The PCI_STOP signal is latched on the rising edge of PCI_F.Its effects take place on the next PCI_F clock cycle. When an output, this pin provides afixed clock signal equal in frequency to the reference signal provided at the X1/X2 pins.SDRAMIN15I Buffered Input Pin: The signal provided to this input pin is buffered to 13 outputs(SDRAM0:11, SDRAM_F).SDRAM0:1138, 37, 35,34, 32, 31,29, 28, 21,20, 18, 17O Buffered Outputs: These twelve dedicated outputs provide copies of the signal provided at the SDRAMIN input. The swing is set by VDDQ3, and they are deactivated whenCLK_STOP# input is set LOW.SDRAM_F40O Free-running Buffered Output: This dedicated output provides a copy of the SDRAMINinput which is not affected by the CLK_STOP# inputSCLK24I Clock pin for I2C CircuitrySDA TA23I/O Data pin for I2C CircuitryX14I Crystal Connection or External Reference Frequency Input: This pin has dual func-tions. It can be used as an external 14.318-MHz crystal connection or as an externalreference frequency input.X25I Crystal Connection:An input connection for an external 14.318-MHz crystal. If using anexternal reference, this pin must be left unconnected.VDDQ31, 6, 14,19, 27, 30,36P Power Connection: Power supply for core logic, PLL circuitry, SDRAM outputs, PCI outputs, reference outputs, 48-MHz output, and 24-MHz output. Connect to 3.3V supply.VDDQ242, 48P Power Connection: Power supply for IOAPIC, CPU_F, and CPU1 output buffers. Connectto 2.5V or 3.3V.GND3, 9, 16,22, 33, 39,45G Ground Connections: Connect all ground pins to the common system ground plane.OverviewThe W144 was developed as a single-chip device to meet the clocking needs of the Intel 440BX AGPset. In addition to the typical outputs provided by standard 100-MHz 440BX FTGs,the W144 adds a thirteen output buffer, supporting SDRAM DIMM modules in conjunction with the chipset.Cypress ’s proprietary spread spectrum frequency synthesis technique is a feature of the CPU and PCI outputs. When en-abled, this feature reduces the peak EMI measurements of not only the output signals and their harmonics, but also of any other clock signals that are properly synchronized to them.Functional DescriptionI/O Pin OperationPins 7, 8, 25, 26, and 46 are dual-purpose l/O pins. Upon pow-er-up these pins act as logic inputs, allowing the determination of assigned device functions. A short time after power-up, the logic state of each pin is latched and the pins become clock outputs. This feature reduces device pin count by combining clock outputs with input select pins.An external 10-k Ω “strapping ” resistor is connected between the l/O pin and ground or V DD . Connection to ground sets a latch to “0,” connection to V DD sets a latch to “1.” Figure 1 and Figure 2 show two suggested methods for strapping resistor connections.Upon W144 power up, the first 2 ms of operation is used for input logic selection. During this period, the five I/O pins (7, 8,25, 26, 46) are three-stated, allowing the output strapping re-sistor on the l/O pins to pull the pin and their associated ca-pacitive clock load to either a logic HIGH or LOW state. At the end of the 2ms period, the established logic “0” or “1” condition of the l/O pin is latched. Next the output buffer is enabled con-verting the l/O pins into operating clock outputs. The 2-ms tim-er starts when VDD reaches 2.0V . The input bits can only be reset by turning VDD off and then back on again.It should be noted that the strapping resistors have no signifi-cant effect on clock output signal integrity. The drive imped-ance of clock outputs are <40Ω (nominal) which is minimally affected by the 10-k Ω strap to ground or V DD . As with the se-ries termination resistor, the output strapping resistor should be placed as close to the l/O pin as possible in order to keep the interconnecting trace short. The trace from the resistor to ground or V DD should be kept less than two inches in length to prevent system noise coupling during input logic sampling.When the clock outputs are enabled following the 2-ms input period, the specified output frequency is delivered on the pin,assuming that V DD has stabilized. If V DD has not yet reached full value, output frequency initially may be below target but will increase to target once V DD voltage has stabilized. In either case, a short output clock cycle may be produced from the CPU clock outputs when the outputs are enabled.Power-on Reset TimerOutput Three-stateData LatchHold QDW144V DDClock Load10 k ΩOutput Buffer(Load Option 1)10 k Ω(Load Option 0)Output LowOutput Strapping R esistor Series Term ination ResistorFigure 1.Input Logic Selection Through Resistor Load OptionPower-on Reset TimerOutput Three-stateData LatchHold QDW144V DDClock LoadR10 k ΩOutput BufferOutput LowOutput Strapping Resistor Series Termination Resistor Jumper OptionsResistor Value RFigure 2.Input Logic Selection Through Jumper OptionSpread Spectrum FeatureThe device generates a clock that is frequency modulated in order to increase the bandwidth that it occupies. By increasing the bandwidth of the fundamental and its harmonics, the am-plitudes of the radiated electromagnetic emissions are re-duced. This effect is depicted in Figure 3.As shown in Figure 3, a harmonic of a modulated clock has a much lower amplitude than that of an unmodulated signal. The reduction in amplitude is dependent on the harmonic number and the frequency deviation or spread. The equation for the reduction isdB = 6.5 + 9*log10(P) + 9*log10(F)Where P is the percentage of deviation and F is the frequency in MHz where the reduction is measured.The output clock is modulated with a waveform depicted in Figure 4. This waveform, as discussed in “Spread Spectrum Clock Generation for the Reduction of Radiated Emissions ” by Bush, Fessler, and Hardin produces the maximum reduction in the amplitude of radiated electromagnetic emissions. The deviation selected for this chip is specified in Table 7. Figure 4details the Cypress spreading pattern. Cypress does offer op-tions with more spread and greater EMI reduction. Contact your local Sales representative for details on these devices.Spread Spectrum clocking is activated or deactivated by se-lecting the appropriate values for bits 1–0 in data byte 0 of the I 2C data stream. Refer to Table 7 for more details.Figure 3.Clock Harmonic with and without SSCGModulation Frequency Domain RepresentationSSFTGTypical ClockFrequency Span (M Hz)--SS%+SS%A m p l i t u d e (dB )5dB/divMAX (+0.5%)MIN (–0.5%)10%20%30%40%50%60%70%80%90%100%10%20%30%40%50%60%70%80%90%100%F R E Q U E N C YFigure 4.Typical Modulation ProfileSerial Data InterfaceThe W144 features a two-pin, serial data interface that can be used to configure internal register settings that control partic-ular device functions. Upon power-up, the W144 initializes with default register settings, therefore the use of this serial data interface is optional. The serial interface is write-only (to the clock chip) and is the dedicated function of device pins SDAT A and SCLOCK. In motherboard applications, SDA TA and SCLOCK are typically driven by two logic outputs of the chipset. Clock device register changes are normally made upon system initialization, if any are required. The interface can also be used during system operation for power manage-ment functions. T able 3 summarizes the control functions of the serial data interface. OperationData is written to the W144 in eleven bytes of eight bits each.Bytes are written in the order shown in T able 4.Table 3.Serial Data Interface Control Functions SummaryControl Function DescriptionCommon ApplicationClock Output DisableAny individual clock output(s) can be disabled. Disabled outputs are actively held LOW.Unused outputs are disabled to reduce EMI and system power. Examples are clock outputs to unused PCI slots.CPU Clock Frequency SelectionProvides CPU/PCI frequency selections through software. Frequency is changed in a smooth and controlled fashion.For alternate microprocessors and power management options. Smooth frequency transition allows CPU frequency change under normal system operation.Spread Spectrum EnablingEnables or disables spread spectrum clocking.For EMI reduction.Output Three-state Puts clock output into a high-impedance state.Production PCB testing.(Reserved)Reserved function for future device revision or production device testing.No user application. Register bit must be written as 0.Table 4.Byte Writing Sequence Byte SequenceByte Name Bit Sequence Byte Description1Slave Address11010010Commands the W144 to accept the bits in Data Bytes 0–6 for internal register configuration. Since other devices may exist on the same com-mon serial data bus, it is necessary to have a specific slave address for each potential receiver. The slave receiver address for the W144 is 11010010. Register setting will not be made if the Slave Address is not correct (or is for an alternate slave receiver).2Command Code Don ’t CareUnused by the W144, therefore bit values are ignored (“don ’t care ”). This byte must be included in the data write sequence to maintain proper byte allocation. The Command Code Byte is part of the standard serial communication protocol and may be used when writing to anoth-er addressed slave receiver on the serial data bus.3Byte Count Don ’t CareUnused by the W144, therefore bit values are ignored (“don ’t care ”). This byte must be included in the data write sequence to maintain proper byte allocation. The Byte Count Byte is part of the standard serial communication protocol and may be used when writing to anoth-er addressed slave receiver on the serial data bus.4Data Byte 0Refer to Table 5The data bits in Data Bytes 0–7 set internal W144 registers that control device operation. The data bits are only accepted when the Address Byte bit sequence is 11010010, as noted above. For description of bit control functions, refer to T able 5, Data Byte Serial Configuration Map.5Data Byte 16Data Byte 27Data Byte 38Data Byte 49Data Byte 510Data Byte 611Data Byte 7Writing Data BytesEach bit in Data Bytes 0–7 controls a particular device function except for the “reserved” bits, which must be written as a logic 0. Bits are written MSB (most significant bit) first, which is bit7. T able 5 gives the bit formats for registers located in Data Bytes 0–7. Table 6 details additional frequency selections that are avail-able through the serial data interface.Table 7 details the select functions for Byte 0, bits 1 and 0.Table 5.Data Bytes 0-7 Serial Configuration MapBit(s)Affected PinControl FunctionBit ControlDefault Pin No.Pin Name01Data Byte 07----(Reserved)----0 6----SEL_2See T able 60 5----SEL_1See T able 60 4----SEL_0See T able 60 3----Hardware/Software Frequency Select Hardware Software0 2----SEL_3See T able 60 1–0----Bit1Bit 0Function (See T able 7 for function details)00Normal Operation01(Reserved)10Spread Spectrum On11All Outputs Three-stated00Data Byte 17----(Reserved)----0 6----(Reserved)----0 5----(Reserved)----0 4----(Reserved)----0 340SDRAM_F Clock Output Disable Low Active1 2----(Reserved)----0 143CPU1Clock Output Disable Low Active1 044CPU_F Clock Output Disable Low Active1 Data Byte 27----(Reserved)----0 67PCI_F Clock Output Disable Low Active1 5----(Reserved)----0 413PCI5Clock Output Disable Low Active1 312PCI4Clock Output Disable Low Active1 211PCI3Clock Output Disable Low Active1 110PCI2Clock Output Disable Low Active1 08PCI1Clock Output Disable Low Active1 Data Byte 37----(Reserved)----0 6----(Reserved)----0 52648MHz Clock Output Disable Low Active1 42524MHz Clock Output Disable Low Active1 3----(Reserved)----0 221, 20,18, 17SDRAM8:11Clock Output Disable Low Active1132, 31, 29, 28SDRAM4:7Clock Output Disable Low Active 1038, 37, 35, 34SDRAM0:3Clock Output DisableLowActive1Data Byte 47----(Reserved)----06----(Reserved)----05----(Reserved)----04----(Reserved)----03----(Reserved)----02----(Reserved)----01----(Reserved)----00----(Reserved)----0Data Byte 57----(Reserved)----06----(Reserved)----05----(Reserved)----0447IOAPIC Clock Output Disable Low Active 13----(Reserved)----02----(Reserved)----0146REF1Clock Output Disable Low Active 102REF0Clock Output DisableLowActive1Data Byte 67----(Reserved)----06----(Reserved)----05----(Reserved)----04----(Reserved)----03----(Reserved)----02----(Reserved)----01----(Reserved)----00----(Reserved)----0Data Byte 77----(Reserved)----06----(Reserved)----05----(Reserved)----04----(Reserved)----03----(Reserved)----02----(Reserved)----01----(Reserved)----00----(Reserved)----0Table 5.Data Bytes 0-7 Serial Configuration Map (continued)Bit(s)Affected PinControl FunctionBit ControlDefault Pin No.Pin Name 01Table 6.Additional Frequency Selections through Serial Data Interface Data BytesInput Conditions Output FrequencyData Byte 0, Bit 3 = 1CPU, SDRAM Clocks(MHz)PCI Clocks (MHz)Bit 2 SEL_3Bit 6SEL_2Bit 5SEL_1Bit 4SEL_01111133.333.3 (CPU/4) 111012431 (CPU/4) 110115037.5 (CPU/4) 110014035 (CPU/4) 101110535 (CPU/3) 101011036.7 (CPU/3) 100111539.3 (CPU/3) 100012040 (CPU/3) 011110033.3 (CPU/3) 011013344.3 (CPU/3) 010111237.3 (CPU/3) 010010334.3 (CPU/3) 001166.833.4 (CPU/2) 001083.341.7 (CPU/2) 00017537.5 (CPU/2) 000012441.3 (CPU/3)Table 7.Select Function for Data Byte 0, Bits 0:1Function Input Conditions Output ConditionsData Byte 0CPU_F,CPU1PCI_F,PCI1:5REF0:1,IOAPIC48MHZ24MHZ Bit 1Bit 0Normal Operation00Note 1Note 114.318 MHz48 MHz24 MHz Spread Spectrum10±0.5%±0.5%14.318 MHz48 MHz24 MHz Three-state11Hi-Z Hi-Z Hi-Z Hi-Z Hi-Z Note:2.CPU and PCI frequency selections are listed in T able 2 and T able 6.Absolute Maximum RatingsStresses greater than those listed in this table may cause per-manent damage to the device. These represent a stress rating only. Operation of the device at these or any other conditions above those specified in the operating sections of this specifi-cation is not implied. Maximum conditions for extended peri-ods may affect reliabilityParameter Description Rating UnitV DD, V IN Voltage on any pin with respect to GND–0.5 to +7.0VT STG Storage T emperature–65 to +150°CT B Ambient T emperature under Bias–55 to +125°CT A Operating Temperature0 to +70°CESD PROT Input ESD Protection 2 (min)kVDC Electrical Characteristics:T A = 0°C to +70°C; V DDQ3 = 3.3V±5%; V DDQ2 = 2.5V±5%Parameter Description Test Condition Min.Typ.Max.Unit Supply CurrentI DD 3.3V Supply Current CPU_F, CPU1 = 100 MHzOutputs Loaded[3]260mAI DD 2.5V Supply Current CPU_F, CPU1 = 100 MHzOutputs Loaded[3]25mA Logic InputsV IL Input Low Voltage GND –0.30.8VV IH Input High Voltage 2.0V DDQ3 +0.3V I IL Input Low Current[4]–25µA I IH Input High Current[4]10µA I IL Input Low Current (SEL100/66#) –5µA I IH Input High Current (SEL100/66#)+5µA Clock OutputsV OL Output Low Voltage I OL = 1 mA50mV V OH Output High Voltage I OH = 1 mA 3.1V V OH Output High Voltage CPU_F,1,IOAPICI OH = –1 mA 2.2V I OL Output Low Current CPU_F, CPU1V OL = 1.25V275797mAPCI_F, PCI1:5V OL = 1.5V20.553139mAIOAPIC V OL = 1.25V4085140mAREF0:1V OL = 1.5V253776mA48MHz V OL = 1.5V253776mA24MHz V OL = 1.5V253776mA I OH Output High Current CPU_F, CPU1V OH = 1.25V255597mAPCI_F, PCI1:5V OH = 1.5V3155139mAIOAPIC V OH = 1.25V4087155mAREF0:1V OH = 1.5V274494mA48MHz V OH = 1.5V274494mA24MHz V OH = 1.5V253776mAAC Electrical CharacteristicsT A = 0°C to +70°C; V DDQ3 = 3.3V±5%; V DDQ2 = 2.5V±5%; f XTL = 14.31818 MHzAC clock parameters are tested and guaranteed over stated operating conditions using the stated lump capacitive load at the clock output; Spread Spectrum clocking is disabled.Crystal Oscillator V TH X1 Input threshold Voltage [5]V DDQ3 = 3.3V1.65V C LOAD Load Capacitance, Imposed on External Crystal [6]14pF C IN,X1X1 Input Capacitance [7]Pin X2 unconnected 28pF Pin Capacitance/InductanceC IN Input Pin Capacitance Except X1 and X25pF C OUT Output Pin Capacitance 6pF L INInput Pin Inductance7nHNotes:3.All clock outputs loaded with 6" 60Ω traces with 22-pF capacitors.4.W144 logic inputs (except FS3) have internal pull-up devices (pull-ups not full CMOS level). Logic input FS3 has an internal pull-down device.5.X1 input threshold voltage (typical) is V DDQ3/2.6.The W144 contains an internal crystal load capacitor between pin X1 and ground and another between pin X2 and ground. Total load placed on crystal is14pF; this includes typical stray capacitance of short PCB traces to crystal.7.X1 input capacitance is applicable when driving X1 with an external clock source (X2 is left unconnected).DC Electrical Characteristics: (continued)T A = 0°C to +70°C; V DDQ3 = 3.3V±5%; V DDQ2 = 2.5V±5%Parameter DescriptionTest ConditionMin.Typ.Max.Unit CPU Clock Outputs, CPU_F, CPU1 (Lump Capacitance Test Load = 20 pF)Parameter Description Test Condition/Comments CPU = 66.6 MHzCPU = 100 MHz UnitMin.Typ.Max.Min.Typ.Max.t P Period Measured on rising edge at 1.251515.51010.5ns t H High Time Duration of clock cycle above 2.0V 5.6 3.3ns t L Low TimeDuration of clock cycle below 0.4V 5.3 3.1ns t R Output Rise Edge Rate Measured from 0.4V to 2.0V1.54 1.54V/ns t F Output Fall Edge Rate Measured from2.0V to 0.4V1.54 1.54V/ns t D Duty CycleMeasured on rising and falling edge at 1.25V45554555%t JCJitter, Cycle-to-CycleMeasured on rising edge at 1.25V. Max-imum difference of cycle time between two adjacent cycles.200200pst SK Output Skew Measured on rising edge at 1.25V 250250ps f STFrequency Stabiliza-tion from Power-up (cold start)Assumes full supply voltage reached within 1 ms from power-up. Short cycles exist prior to frequency stabilization.33msZ oAC Output ImpedanceAverage value during switching transi-tion. Used for determining series termi-nation value.2020ΩSDRAM Clock Outputs, SDRAM, SDRAM0:11 (Lump Capacitance Test Load = 30 pF)Parameter Description Test Condition/CommentsCPU = 66.6 MHz CPU = 100 MHzUnit Min.Typ.Max.Min.Typ.Max.t P Period Measured on rising edge at 1.5V3030ns t H High Time Duration of clock cycle above 2.4V,at min. edge rate (1.5V/ns)5.6 3.3nst L Low Time Duration of clock cycle below 0.4V,at min. edge rate (1.5V/ns)5.3 3.1nst R Output Rise EdgeRateMeasured from 0.4V to 2.4V 1.54 1.54V/nst F Output Fall EdgeRateMeasured from 2.4V to 0.4V 1.54 1.54V/ns t PLH Prop Delay LH Input edge rate faster than 1V/ns1515ns t PHL Prop Delay HL Input edge rate faster than 1V/ns1515ns t D Duty Cycle Measured on rising and fallingedge at 1.5V,at min. sdge rate(1.5V/ns)45554555%t JC Jitter, Cycle-to-Cycle Measured on rising edge at 1.5V.Maximum difference of cycle timebetween two adjacent cycles.250250ps t SK Output Skew Measured on rising edge at 1.5V250250pst O CPU to PCI ClockSkew Covers all CPU/PCI outputs. Mea-sured on rising edge at 1.5V. CPUleads PCI output.1.54 1.54nsf ST FrequencyStabilization fromPower-up (cold start)Assumes full supply voltagereached within 1 ms from power-up. Short cycles exist prior to fre-quency stabilization.33msZ o AC OutputImpedance Average value during switchingtransition. Used for determiningseries termination value.3030ΩPCI Clock Outputs, PCI_F and PCI1:5 (Lump Capacitance Test Load = 30 pF)Parameter Description Test Condition/CommentsCPU = 66.6/100 MHzUnit Min.Typ.Max.t P Period Measured on rising edge at 1.5V30ns t H High Time Duration of clock cycle above 2.4V 12.0ns t L Low Time Duration of clock cycle below 0.4V12.0ns t R Output Rise Edge Rate Measured from 0.4V to 2.4V14V/ns t F Output Fall Edge Rate Measured from 2.4V to 0.4V 14V/ns t D Duty Cycle Measured on rising and falling edge at 1.5V4555% t JC Jitter, Cycle-to-Cycle Measured on rising edge at 1.5V. Maximumdifference of cycle time between two adja-cent cycles.250pst SK Output Skew Measured on rising edge at 1.5V500ps t O CPU to PCI Clock Skew Covers all CPU/PCI outputs. Measured onrising edge at 1.5V. CPU leads PCI output.1.5 4.0nsf ST Frequency Stabilizationfrom Power-up (cold start)Assumes full supply voltage reached within1ms from power-up. Short cycles exist pri-or to frequency stabilization.3.0msZ o AC Output Impedance Average value during switching transition.Used for determining series terminationvalue.30ΩIOAPIC Clock Output (Lump Capacitance Test Load = 20 pF)Parameter Description Test Condition/CommentsCPU = 66.6/100 MHzUnit Min.Typ.Max.f Frequency, Actual Frequency generated by crystal oscillator14.31818MHz t R Output Rise Edge Rate Measured from 0.4V to 2.0V14V/ns t F Output Fall Edge Rate Measured from 2.0V to 0.4V14V/ns t D Duty Cycle Measured on rising and falling edge at 1.25V4555%f ST Frequency Stabilizationfrom Power-up (cold start)Assumes full supply voltage reached within1ms from power-up. Short cycles exist priorto frequency stabilization.1.5msZ o AC Output Impedance Average value during switching transition.Used for determining series termination value.15ΩREF0:1 Clock Output (Lump Capacitance Test Load = 20 pF)Parameter Description Test Condition/Comments CPU = 66.6/100 MHzUnit Min.Typ.Max.f Frequency, Actual Frequency generated by crystal oscillator14.318MHz t R Output Rise Edge Rate Measured from 0.4V to 2.4V0.52V/ns t F Output Fall Edge Rate Measured from 2.4V to 0.4V0.52V/ns t D Duty Cycle Measured on rising and falling edge at 1.5V4555%f ST Frequency Stabilizationfrom Power-up (coldstart)Assumes full supply voltage reached within 1 ms frompower-up. Short cycles exist prior to frequency stabili-zation.3msZ o AC Output Impedance Average value during switching transition. Used for de-termining series termination value.40Ω。

丰田EXP-1444电池测试仪软件更新说明书

Select Update menu Select UPDATE from the UTILITY MENU.

Load original configuration Select option 3 LOAD CONFIG and press NEXT / OK.

167-000793B EN 7/17 ©2017 Midtronics B.V. All rights reserved

Username: Password:

TMEupdate exp1444

Fill out the form, all five fields are required.

Note that you need to provide the software serial number, NOT the product serial number displayed on the tool’s back label.

Otherwise, please proceed downloading the new software version and follow the instructions of the software update instruction sheet to install the software.

Save tester configuration Select option 2 SAVE CONFIG and press NEXT / OK.

Step 5. Update tester firmware

Stanford EAZ0144G33A_A 产品说明书

ASSY COVER FOR M CABINET

19 EAS2246G63A

FOOT EXTENSION FOR M2 CABINET

Désignation

Designaciòn

N. Note Nota

BOUCHON NOIR POUR VIS M5

TAPÓN CASQUETE NEGRO TORNILLOS M5 2

B = on request - sur demande - a petición

C = suggested - suggeré - sugerido

7

Pos Code

Designation

Désignation

Designaciòn

N. Note Nota

ABC

1 1-16609A

SCREW TCEI

A = available - disponible - disponible

B = on request - sur demande - a petición

Designaciòn

Pedal "p", 2 conmutador GRUPO PEDAL FRENO J PEDAL FRENO ALUMINIO 2 MICRO PEDAL FRENO CAJA M TAPON-GRUPO MEDIDAS PROTECCIÓN BRIDAS PERNO PORTA BRIDAS TAPÓN NEGRO DE COB. PARA CHAPAS CABLE TIERRA CONECTOR PLATO M/TIERRA COBERTURA INF. GRUPO MIS. RAL9005 COBERT. INF. GRUPO MIS. TORNILLO AUTORR. Transformador 100/230V Transformador Transformador 230/230V Transformador 100/230V

PDTC144WEF中文资料

2004 Aug 17

4

Philips Semiconductors

Product specification

NPN resistor-equipped transistors; R1 = 47 kΩ, R2 = 22 kΩ

THERMAL CHARACTERISTICS SYMBOL Rth(j-a) SOT54 SOT23 SOT346 SOT323 SOT490 SOT883 SOT416 Notes 1. Refer to standard mounting conditions. 2. Reflow soldering is the only recommended soldering method. 3. Refer to SOT883 standard mounting conditions; FR4 with 60 µm copper strip line. CHARACTERISTICS Tamb = 25 °C unless otherwise specified. SYMBOL ICBO ICEO IEBO hFE VCEsat Vi(off) Vi(on) R1 R2 -----R1 Cc PARAMETER collector-base cut-off current collector-emitter cut-off current emitter-base cut-off current DC current gain collector-emitter saturation voltage input-off voltage input-on voltage input resistor resistor ratio collector capacitance IE = ie = 0 A; VCB = 10 V; f = 1 MHz CONDITIONS VCB = 50 V; IE = 0 A VCE = 30 V; IB = 0 A VCE = 30 V; IB = 0 A; Tj = 150 °C VEB = 5 V; IC = 0 A VCE = 5 V; IC = 5 mA IC = 10 mA; IB = 0.5 mA IC = 100 µA; VCE = 5 V IC = 2 mA; VCE = 0.3 V PARAMETER thermal resistance from junction to ambient CONDITIONS in free air note 1 note 1 note 1 note 1 notes 1 and 2 notes 2 and 3 note 1

144W太阳能柔性组件

产品特性·极佳的高温性能和低光照性能·功率输出保证20年内不低于80%·多触点连接器或接线盒·耐阴影设计,每片电池加装二极管旁路保护·最大系统电压600VDC·符合IEC61646标准性能参数额定功率: 144W误差: ±5%结构参数·外型尺寸: 5486mm×394mm×4mm (包括接线盒厚度为16mm)·重量: 7.7Kg·输出导线: 截面2.5mm2,长560mm,带防风雨直流额定多触点连接器·旁路二极管: 每一片电池都加装旁路二极管·封装材料: 耐用、高透光率的ETFE (Tefzel@)聚醋膜·胶粘剂: 乙烯丙烯共聚物密封胶,含有微生物抑制剂·电池类型: 22片三结非晶硅薄膜太阳电池(356×239mm)串联质量和安全在最大系统电压应用时,产品电气、防火安全性能,符合UL相关标准要求输出配置标准配置: 层压组件组装终端盒,连接导线和多触点连接器可选配置: 光伏组件接线盒应用准则·合格的屋顶设施·钢板平整宽度最小407mm·钢板有PVDF(电镀或锌铝)涂层·钢板表面平整(无碎屑、无装饰痕迹、无污染)·有资质的安装人员安装·安装温度 10℃-40℃·屋顶最高温度 85℃·安装倾角:最小50°,最大60°·参考制造商安装规范电性能参数标准测试条件 非标准测试条件 温度系数(1000W/m2,AM1.5,电池温度:25℃)(800W/m2,AM1.5,风速1米/秒)(1000W/m2,AM1.5)最大功率(Pmax) :144W 最大功率(Pmax):111W I sc : 0.10%/℃工作电压(Vmp) :33.0V 工作电压(Vmp) :30.8V V oc :-0.38%/℃工作电流(Imp) :4.36A 工作电流(Imp) :3.6A P max:-0.21%/℃短路电流(Isc) :5.3A 短路电流(Isc):4.3A I mp : 0.10%/℃开路电压(Voc) :46.2V 开路电压(Voc) :42.2V V mp :-0.31%/℃最大串联保险丝电流 :8A 非标准温度 :46℃y=yreference•[1+TC•(T-Treference)]注意事项·在最初运行8-10周内,电性能输出会高出额定值,功率输出可能高出15%,电压可能高出11%, 电流可能高出4%。

Philips Semiconductors BTA140 series Data Sheet

现货库存、技术资料、百科信息、热点资讯,精彩尽在鼎好!Philips Semiconductors Product specificationTriacs BTA140 seriesGENERAL DESCRIPTIONQUICK REFERENCE DATAGlass passivated triacs in a plastic SYMBOL PARAMETERMAX.MAX.MAX.UNIT envelope,intended for use in applications requiring high BTA140-500600800bidirectional transient and blocking V DRM Repetitive peak off-state 500600800V voltage capability and high thermal voltagescycling performance.Typical I T(RMS)RMS on-state current252525A applications include motor control,I TSMNon-repetitive peak on-state 190190190Aindustrial and domestic lighting,currentheating and static switching.PINNING - TO220ABPIN CONFIGURATIONSYMBOLLIMITING VALUESLimiting values in accordance with the Absolute Maximum System (IEC 134).SYMBOL PARAMETERCONDITIONSMIN.MAX.UNIT -500-600-800V DRM Repetitive peak off-state -50016001800V voltagesI T(RMS)RMS on-state current full sine wave; T mb ≤ 91 ˚C-25A I TSMNon-repetitive peak full sine wave; T j = 25 ˚C prior to on-state current surge t = 20 ms -190A t = 16.7 ms -209A I 2t I 2t for fusingt = 10 ms-180A 2s dI T /dtRepetitive rate of rise of I TM = 30 A; I G = 0.2 A;on-state current after dI G /dt = 0.2 A/µstriggeringT2+ G+-50A/µs T2+ G--50A/µs T2- G--50A/µs T2- G+-10A/µs I GM Peak gate current -2A V GM Peak gate voltage -5V P GM Peak gate power -5W P G(AV)Average gate power over any 20 ms period-0.5W T stg Storage temperature -40150˚C T jOperating junction -125˚Ctemperature1 Although not recommended, off-state voltages up to 800V may be applied without damage, but the triac may switch to the on-state. The rate of rise of current should not exceed 15 A/µs.THERMAL RESISTANCESSYMBOL PARAMETER CONDITIONS MIN.TYP.MAX.UNITRth j-mb Thermal resistance full cycle-- 1.0K/W junction to mounting base half cycle-- 1.4K/WRth j-a Thermal resistance in free air-60-K/W junction to ambientSTATIC CHARACTERISTICSTj= 25 ˚C unless otherwise statedSYMBOL PARAMETER CONDITIONS MIN.TYP.MAX.UNITI GT Gate trigger current VD= 12 V; IT= 0.1 AT2+ G+-635mAT2+ G--1035mAT2- G--1135mAT2- G+-2370mAI L Latching current VD= 12 V; IGT= 0.1 AT2+ G+-840mAT2+ G--3060mAT2- G--1840mAT2- G+-1560mAI H Holding current VD= 12 V; IGT= 0.1 AT2+-730mAT2--1230mAVT On-state voltage IT= 30 A- 1.3 1.55VVGT Gate trigger voltage VD= 12 V; IT= 0.1 A-0.7 1.5VVD= 400 V; IT= 0.1 A; Tj= 125 ˚C0.250.4-VI D Off-state leakage current VD= VDRM(max); Tj= 125 ˚C-0.10.5mADYNAMIC CHARACTERISTICSTj= 25 ˚C unless otherwise statedSYMBOL PARAMETER CONDITIONS MIN.TYP.MAX.UNITdVD /dt Critical rate of rise of VDM= 67% VDRM(max); Tj= 125 ˚C;100300-V/µs off-state voltage exponential waveform; gate open circuitdVcom /dt Critical rate of change of VDM= 400 V; Tj= 95 ˚C; IT(RMS)= 25 A;-10-V/µs commutating voltage dIcom/dt = 9 A/ms; gate open circuitt gt Gate controlled turn-on ITM= 30 A; VD= VDRM(max); IG= 0.1 A;-2-µs time dIG/dt = 5 A/µsMECHANICAL DATANotes1. Refer to mounting instructions for TO220 envelopes.2. Epoxy meets UL94 V0 at 1/8".DEFINITIONSData sheet statusObjective specification This data sheet contains target or goal specifications for product development. Preliminary specification This data sheet contains preliminary data; supplementary data may be published later. Product specification This data sheet contains final product specifications.Limiting valuesLimiting values are given in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of this specification is not implied. Exposure to limiting values for extended periods may affect device reliability. Application informationWhere application information is given, it is advisory and does not form part of the specification.© Philips Electronics N.V. 1997All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner.The information presented in this document does not form part of any quotation or contract, it is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent or other industrial or intellectual property rights.LIFE SUPPORT APPLICATIONSThese products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.。

GridVis-Basic 电力分析仪产品说明书

1Network visualisation software• GridVis ®-Basic (in the scope of supply)3 digital inputs/outputs•Usable as either inputs or outputs•Switch output•Threshold value output •Logic output•Remote via Modbus / ProfibusT emperature measurement •PT100, PT1000, KTY83, KTY84Interfaces •RS485•Ethernet•SNTP •TFTP•BACnet (optional)Networks• T N, T T , IT networks•3 and 4-phase networks•Up to 4 single-phase networksMeasured data memory •256 MB Flash• H armonics up to 40th harmonic •Rotary field components•Distortion factor T HD-U / T HD-I2 analogue inputs • A nalogue, temperature or residual current input (RCM)Residual current measurement BACnet (optional)HomepageAlarm managementMemory 256 MB Ethernet-Modbus gateway2• M easurement, monitoring and checking of electrical characteristics in energy distribution systems • R ecording of load profiles in energy management systems (e.g. ISO 50001)• Acquisition of the energy consumption for cost centre analysis • M easured value transducer for building management systems or PLC (Modbus)• M onitoring of power quality characteristics, e.g. harmonics up to 40th harmonic • R esidual current monitoring (RCM)Areas of applicationMain featuresUniversal meter• O perating current monitoring for general electrical parameters • H igh transparency through a multi-stage and scalable measurement system in the field of energy measurement • A cquisition of events through continuous measurement with 200 ms high resolutionRCM device• C ontinuous monitoring of residual currents (Residual Current Monitor, RCM)• A larming in case a preset threshold fault current reached • N ear-realtime reactions for triggering countermeasures • P ermanent RCM measurement for systems in permanent operation without the opportunity to switch offEnergy measurement device•Continuous acquisition of the energy data and load profiles • E ssential both in relation to energy efficiency and for the safe design of power distribution systemsHarmonics analyser / event recorder• Analysis of individual harmonics for current and voltage •Prevention of production downtimes•Significantly longer service life for equipment • R apid identification and analysis of power quality fluctuations by means of user-friendly tools (GridVis ®)Fig.: UMG 96RM-E with residual current monitoring via measuring inputs I5 / I6Fig.: Event logger: Voltage dip in the low voltage distribution system3Extensive selection of tariffs• 7 tariffs each for effective energy (consumption, delivery and without backstop)• 7 tariffs each for reactive energy (inductive, capacitive and without backstop)•7 tariffs for apparent energy •L1, L2 and L3, for each phaseHighest possible degree of reliability•Continuous leakage current measurement • H istorical data: Long-term monitoring of the residual current allows changes to be identified in good time, e.g. insulation faults•Time characteristics: Recognition of time relationships •Prevention of neutral conductor carryover • R CM threshold values can be optimized for each individual case: Fixed, dynamic and stepped RCM threshold value • M onitoring of the CGP (central ground point) and the sub-distribution panelsAnalysis of fault current events• E vent list with time stamp and values•Presentation of fault currents with characteristic and duration • R eproduction of phase currents during the fault current surge • P resentation of the phase voltages during the fault current surgeAnalysis of the harmonic fault current components•Frequencies of the fault currents (fault type)•Current peaks of the individual frequency components in A and %•Harmonics analysis up to 40th harmonic •Maximum values with real-time bar displayDigital IOs• E xtensive configuration of IOs for intelligent integration, alarmand control tasksFig.: Continuous leakage current measurementFig.: Analysis of fault current eventsFig.: Analysis of the harmonic fault current components4Dimension diagramsAll dimensions in mmSide viewRear viewEthernet (TCP/IP)- / Homepage- / Ethernet-Modbus gateway functionality•Simple integration into the network •More rapid and reliable data transfer •Modern homepage • W orld-wide access to measured values by means of standard web browsers via the device's inbuilt homepage • Access to measurement data via various channels • R eliable saving of measurement data possible over a very long periods of time in the 256 MByte measurement data memory • C onnection of Modbus slave devices via Ethernet-ModbusgatewayFig.: Ethernet-Modbus gateway functionalityMeasuring device homepage• W ebserver on the measuring device, i.e. device's own homepage •Remote operation of the device display via the homepage •Comprehensive measurement data incl. PQ • O nline data directly available via the homepage, historic data optional via the APP measured value monitor, 51.00.246Fig.: Illustration of the online data via the device's inbuilt homepageCut out: 92+0,8 x 92+0,8 mm5Typical connectionDevice overview and technical dataFig.: Connection example residual currentmeasurement and PE monitoringFig.: Connection example with temperature and residual current measurementS2S1S2S2S1S1Digital-Eingänge/Ausgänge UMG 96RM-E (RCM)L1L2L3Spannungsmessung 3456StrommessungVersorgungs-spannung12RS4851617BAB AV e r b r a u c h e r230V/400V 50HzI 41918N282930313233343536Analog-Eingänge13141524V DC K1K2=E t h e r n e t10/100B a s e -TPCK3K4K5==37R J 450-30 mAS2S1I DIFFI 5I 6PT100S1S2S3Gruppe 1Gruppe 2V 1V 2V 3V N N/-L/+2)1)2)2)3)3)3)3)Digital inputs/outputs Power supply voltage Current measurement Measuring voltage Analog inputs L o d s Group 1Group 2Comment:For detailed technical information please refer to the operation manual and the Modbus address list.•= included - = not included *1 Inclusive UL certification.6Fig.: GridVis ®software, configuration menuComment:For detailed technical information please refer to the operation manual and the Modbus address list.• = included - = not included*2 O ptional additional functions with the packages GridVis ®-Professional, GridVis ®-Service and GridVis ®-Ultimate.7Fig.: RCM configuration, e.g. dynamicthreshold value formation, for load-dependent threshold value adaptationFig.: Summation current transformer for the acquisition of residual currents. Wide range with different configurations and sizes allow use in almost all applicationsMeasurement surge voltage Power consumption Overload for 1 sec.Sampling frequency per channel (50 / 60 Hz)Residual current inputAnalogue inputsMeasurement range, residual current input*Digital outputsSwitching voltage Switching current Response timePulse output (energy pulse)Comment:For detailed technical information please refer to the operation manual and the Modbus address list.•= included - = not included*3 E xample of residual current input 30 mA with 600/1 residual current transformer: 600 x 30 mA = 18,000 mA *4A ccurate device dimensions can be found in the operation manual.8Comment:For detailed technical information please refer to the operation manual and the Modbus address list.• = included - = not included。

超特克(Supertex)高压DC DC转换器应用注解说明书

Supertex inc.AN-H59Application NoteApplication CircuitHigh Voltage DC/DC Converter forSupertex Ultrasound Transmitter DemoboardsBy Afshaneh Brown, Applications Engineer,and Jimes Lei, Applications ManagerIntroductionThe Supertex AN-H59DB1 demoboard is a high voltage DC/DC converter. It can provide up to +90V voltage supply for V PP and -90V for V NN . It also provides +8.0 to +10V voltage supply for V DD , floating power supplies of V NN +8.0 to V NN +10V for V NF and V PP -8.0 to V PP -10V for V PF . The input supply voltage is 12V.The AN-H59DB1 circuitry consists of two high voltage PWM Current-Mode controllers, a DC/DC transformer driver, and three low dropout regulators. The Supertex AN-H59DB1 uses a high-voltage, current mode, PWM controller boost topology to generate +15 to +90V and a high-voltage current mode PWM controller buck-boost topology to generate -15 to -90V power supply voltage for Supertex HV738DB1 and HV748DB1 ultrasound transmitter demoboards.Each of the transmitter demoboards has slightly different operating voltages as summarized below.To accommodate all three demoboards, the AN-H59DB1 demoboard has adjustable V PP , V NN , V DD , V PF and V NF . The purpose of the AN-H59DB1 is to aid in the evaluation of the three transmitter demoboards. The intention of this application note is to provide a general circuit description on how each of the output voltages is generated.The VSUB pin on the HV738DB1 and HV748DB1 can either be connected to the most positive supply voltage on the demoboard, or can be left floating.To power up the AN-H59DB1, ensure that the 3.3V power supply will be powered up first, and then the 12V power supply. The sequences on the HV738DB1 and HV748DB1 took into consideration using the protection diodes on each power line.The circuit is shown in Figure 6, the component placement in Figure 5, and the bill of materials is at the end of thisapplication note.PP The circuit in Figure 1 shows U5, the Supertex high volt -age current mode PWM controller, being used to generate the high voltage power supply for V PP . The maximum output power for V PP was set for 10mA at 90V, which is 900mW. With an input voltage of 12V, a converter frequency of 110 kHz with a 100µH inductor was chosen to provide the de -sired output power.The converter frequency is set by an external resistor, R20, across OSC IN and OSC OUT pins of U5. A 154kΩ resistor will set the frequency to about 110 kHz. R24 is the current sense resistor. 2.2Ω was used to set the maximum peak current limit to about 450mA. An RC filter, R23 and C15, is added between the current sense resistor and the current sense terminal pin 3 of U5. This reduces the leading edge spike on R24 from entering the current sense pin.Inductor L1 is being charged from the 12V input by M3. When M3 turns off, the energy in L1 is discharged into C16, which is the V PP output through D8. The V PP voltage is di-vided down by feedback resistors R25, R26, and R27. The wiper of R26 is connected to pin 14 of U5. The overall con -verter will regulate the voltage on pin 14 to 4.0V. Different V PP output voltages can be obtained by adjusting R26.When the wiper for R26 is set to the top, V PP can be calcu-lated as:where V FB is 4.0VWhen the wiper for R26 is set to the bottom, V PP can be calculated as:By adjusting potentiometer R26, V PP meets the adjustable target range of 15 to parator U6 will turn on LED D7 when the V PP output is out of regulation due to excessive load. During initial power up, C16 will be at 0V. D7 is therefore expected to be on until C16 is charged to the desired regulation voltage.Figure 1: Adjustable V PP Power SupplyV PPGNDV PP = 4.0V x ( 232k + 100k + 14.3k )= 12.1V 100k + 14.3k V PP= V FBx ( R25 + R26 + R27 )R26 + R27V PP = 4.0V x ( 232k + 100k + 14.3k )= 96.9V 14.3kV PP = V FBx ( R25 + R26 + R27 )R27NN The circuit in Figure 2 shows U7, the Supertex high voltage current mode PWM controller, being used to generate the high voltage power supply for V NN . The function of U7 is very similar to what was described in the V PP circuit description for U5. However, in this circuit a negative voltage is gener -ated from a positive input voltage source, therefore requir-ing a buck-boost topology. The maximum output power for V NN was set for -10mA at -90V which is 900mW. With an input voltage of 12V, a converter frequency of 110 kHz with a 100µH inductor was chosen to provide the desired output power.Inductor L2 is being charged from the 12V input by the par-allel combination of M6 and M7. When M6 and M7 turn off, the energy in L2 is discharged into C23, which is the V NNoutput through D10. M6 and M7 are high voltage P-channel MOSFETs. U7 is designed to drive a high voltage N-chan -nel MOSFET. The drive output for U7 therefore needs to be inverted. This is accomplished by M4 and M5.The feedback voltage that U7 detects on pin 14 is +4.0V. The V NN that needs to be sensed is a negative voltage. A cir-cuit is needed to make sure the feedback voltage is positive. This is consists of Q4, Q5, R33, R34, R35, R37, and R38. Q4 becomes a constant current sink set by the V NN voltageand R35. The same current will be flowing through R33 and R34.The voltage on the base of Q5 will be V IN minus the voltage drop across the sum of R33 and R34. By varying R34, the base voltage on Q5 will change. Q5 becomes a constant current source with a value set by its base voltage and R37. The current source of Q5 is going into R38, which creates a positive voltage that is now proportional to the magnitude of V NN .where V BE = 0.6V, V FB = 4.0V.When R34 is set to 100k, V NN is calculated to be:= -4.0VWhen R34 is set to 0k, V NN is calculated to be:= -97.4V By adjusting potentiometer R34, V NN meets the adjustable target range of -15 to parator U8 will turn on LED D9 when the V NN output isout of regulation due to excessive load. During initial power up, C23 will be at 0V. D9 is therefore expected to be on until C23 is charged to the desired regulation voltage.Figure 2: Adjustable V NN Power SupplyVNN-15V to -90V GNDV NN = V BE - ( R35 ) x (V BE + V FB x R37 ), R33 + R34 R38V NN = 0.6V - ( 273k) x (0.6V + 4.0V x 14.7k ) 4.99k + 100k 40.2k V NN = 0.6V - ( 273k ) x (0.6V + 4.0V x 14.7k )4.99k + 0k 40.2kVPF and VNF Circuit DescriptionThe three transmitter demoboards require two floating low voltage supplies, V PF and V NF . The floating supplies need to be adjustable to accommodate the different operating re-quirements for the three different boards. The V PF is 8.0 to 10V below the high voltage V PP positive supply. The V NF is 8.0 to 10V above the high voltage V NN negative supply. The two floating supplies are generated by using two isolated transformers, T1 and T2, and an isolated transformer driver, U1, as shown in Figure 4. Both outputs utilize adjustable low dropout linear regulators, U2 and U3, as shown in Figure 3. U2 and U3 are both Linear Technology LT1521, which has a reference voltage of 3.75V on the ADJ pin. For V PF , resistors R6, R7, and R8 set the output V PF voltage. R7 is a potentiom -eter for adjusting V PF . V PF can be calculated with the following equation:When R7 is set to 20kΩ, V PF becomes:When R7 is set to 0Ω, V PF becomes:Please note that the OUT pin on U2 is referenced to V PP , thereby setting V PF to be 8.0 to 10V below V PP . V NF can also be calculated in a similar manner using resistors R12, R13, and R14. Please note that the GND pin on U3 is referenced to V NN thereby setting V NF to be 8.0 to 10V above V NN .LED indicators, D5 and D11, start to turn on when the input current to U2 and U3 reaches an arbitrary value of 40mA. This is set by Q1 and R3 for V PF and Q2 and R9 for V NF . The input current can be calculated with the following equation: Input current = V EB = 0.5V = 41.3mA R 12.1Ω50mA current limits are added to protect against output shorts. The current limiter is consists of a depletion-mode MOSFET and a series source resistor. The resistor sets the current limit and can be estimated with the following equa -tion:R SERIES = V TH x ( √I LIM / I DSS - 1) where, I LIMV TH = pinch-off voltage for M1 and M2: -2.5V I LIM = desired current limit: 50mAI DSS = saturation current for M1 and M2: 1.1A R SERIES = 39.3Ω. A 40.2Ω resistor was used.Figure 3: Adjustable V PF and V NF Power SupplyV VNFVFPV PF = 3.75V x ( 45.3k + 20k + 24.9k )= 7.53V 20k + 24.9kV PF = 3.75V x ( 45.3k + 0k + 24.9k )= 10.6V 0 +24.9kV PF= V ADJx ( R6 + R7 + R8 )R7 + R8V DD Circuit DescriptionThe V DD output voltage utilizes an adjustable low dropout lin -ear regulator, U4 LT1521, as shown in Figure 4. The desiredadjustable output voltage range is 8.0 to 10V to accommo-date the different operating V DD voltages for the three differ-ent transmitter demoboards.The LT1521 has a reference voltage of 3.75V on the adj pin. Resistors R17, R18, and R19 set the output V DD voltage. R18 is a potentiometer for adjusting V DD . V DD can be calcu-lated with the following equation:When R18 is set to 20kΩ, V DD becomes:When R18 is set to 0Ω, V DD becomes:An LED indicator, D6, is included in case of excessive input,I IN, current. D6 is starts to turn on when the input currentreaches an arbitrary value of 20mA. This is set by Q3 and R15. When the emitter-base junction of Q3 is forward biased (0.5V), Q3 will start to turn on, thereby forward biasing D6.The I IN value to turn D6 on can be calculated with the follow -ing equation: I IN = V EB = 0.5V= 20.6mAR1524.3Ω 3.3V Input TerminalThe AN-H59DB1 has a 3.3V input terminal that is directly connected to the output terminal, V CC . There is no circuitry on this board that uses the 3.3V supply. It is only there as a convenient connection to the 8-pin header. V CC is the logic supply voltage for HV738DB1 and HV748DB1 and can oper-ate from 1.2 to 5V. However, most users will operate V CC at either 3.0 or 3.3V.Input and Output PowerThe output voltages from the AH-H59DB1 are all generated from the 12V input line. With no load on the outputs, the measured input current was about 70mA. This input current can vary from board to board due to variations in the isolated transformer.The maximum output power is:P OUT(MAX) = P VPP(MAX) + P VNN(MAX) + P VPF(MAX) + P VNF(MAX) + P VDD(MAX)P OUT(MAX) = 0.9W + 0.9W + 0.4W + 0.4W + 0.2W P OUT(MAX) = 2.8WUnder this condition, the 12V input current was measured to be 340mA. Input power is therefore 4.08W. This gives an approximate overall efficiency of 69% at full load.Figure 4: Adjustable V DD Power SupplyV IN = 12VVDD+8.0 to 10V GNDV DD = 3.75V x ( 45.3k + 20k + 24.9k )= 7.53V20k + 24.9kV DD = 3.75V x ( 45.3k + 0k + 24.9k )= 10.6V 0 + 24.9k V DD = V ADJ x ( R17 + R18 + R19 )R18 + R19VPF and VNF Output CurrentThe AN-H59DB1 can supply more than 40mA of current for the V PF and V NF outputs. The I NF and I PF input currents for the HV738 or the HV748 can be found in their respective datasheet but are summarized below:This is for continuous 5.0 MHz operation. For ultrasound, thehigh voltage transmitter is operating at very low duty cycles; 1% or lower. At a 1% duty cycle, the average current is ex -pected to be a 100 times lower. The 40mA output current ca -pability on the AN-H59DB1 is more than sufficient to power up the HV738 or the HV748.ConclusionThe main purpose of AN-H59DB1 power supply demoboard is to help the evaluation of the Supertex HV738DB1 and HV748DB1 demoboards by reducing the number of power supplies needed. The AN-H59DB1 was designed to operate from a single 12V input which should be commonly available in any engineering laboratory.The five on-board LEDs allow the user to quickly determine whether there is an overload condition on each of the supplylines. The five potentiometers allow the user to easily adjust each supply to meet their particular needs.Figure 5: AN-H59 Component PlacementFigure 6: AN-H59 Circuit SchematicVPPVPFVNFSupertex inc. does not recommend the use of its products in life support applications, and will not knowingly sell them for use in such applications unless it receives an adequate “product liability indemnification insurance agreement.” Supertex inc. does not assume responsibility for use of devices described, and limits its liability to the replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions and inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications refer to the Supertex inc. (website: http//)©2012 Supertex inc. All rights reserved. Unauthorized use or reproduction is prohibited.Supertex inc.1235 Bordeaux Drive, Sunnyvale, CA 94089。

PDTA144VM,315;PDTA144VE,115;PDTA144VT,215;PDTA144VU,115;PDTA144VK,115;中文规格书,Datasheet资料

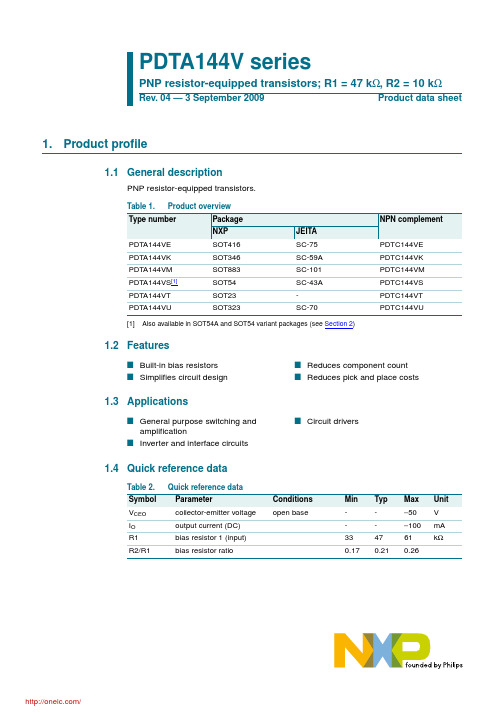

1.Product profile1.1General descriptionPNP resistor-equipped transistors.[1]Also available in SOT54A and SOT54 variant packages (see Section 2)1.2Features1.3Applications1.4Quick reference dataPDTA144V seriesPNP resistor-equipped transistors; R1 = 47 k Ω, R2 = 10 k ΩRev. 04 — 3 September 2009Product data sheetTable 1.Product overviewType number Package NPN complementNXPJEITA PDT A144VE SOT416SC-75PDTC144VE PDT A144VK SOT346SC-59A PDTC144VK PDT A144VM SOT883SC-101PDTC144VM PDT A144VS [1]SOT54SC-43A PDTC144VS PDT A144VT SOT23-PDTC144VT PDT A144VUSOT323SC-70PDTC144VUI Built-in bias resistors I Reduces component count I Simplifies circuit designI Reduces pick and place costsI General purpose switching and amplificationI Circuit driversI Inverter and interface circuitsTable 2.Quick reference data Symbol ParameterConditions Min Typ Max Unit V CEO collector-emitter voltage open base--−50V I O output current (DC)--−100mA R1bias resistor 1 (input)334761k ΩR2/R1bias resistor ratio0.170.210.262.Pinning informationTable 3.PinningPin Description Simplified outline SymbolSOT541input (base)2output (collector)3GND (emitter)SOT54A1input (base)2output (collector)3GND (emitter)SOT54 variant1input (base)2output (collector)3GND (emitter)SOT23, SOT323, SOT346, SOT416 1input (base)2GND (emitter)3output (collector)SOT8831input (base)2GND (emitter)3output (collector)001aab347123006aaa148R1R2231001aab348123006aaa148R1R2231001aab447123006aaa148R1R2231006aaa144123sym003321R1R2312Transparenttop viewsym003321R1R23.Ordering information[1]Also available in SOT54A and SOT54 variant packages (see Section 2 and Section 9).4.Marking[1]* = -: made in Hong Kong * = p: made in Hong Kong * = t: made in Malaysia * = W: made in ChinaTable 4.Ordering informationType numberPackage NameDescriptionVersion PDT A144VE SC-75plastic surface mounted package; 3 leads SOT416PDT A144VK SC-59A plastic surface mounted package; 3 leadsSOT346PDT A144VM SC-101leadless ultra small plastic package; 3 solder lands;body 1.0× 0.6× 0.5 mmSOT883PDT A144VS [1]SC-43A plastic single-ended leaded (through hole)package;3leadsSOT54PDT A144VT -plastic surface mounted package; 3 leads SOT23PDT A144VUSC-70plastic surface mounted package; 3 leadsSOT323Table 5.Marking codesType number Marking code [1]PDT A144VE 13PDT A144VK 12PDT A144VM E9PDT A144VS TA144V PDT A144VT *AG PDT A144VU*125.Limiting values[1]Refer to standard mounting conditions.[2]Reflow soldering is the only recommended soldering method.[3]Refer to SOT883 standard mounting conditions; FR4 printed-circuit board with 60µm copper strip line.6.Thermal characteristics[1]Refer to standard mounting conditions.[2]Reflow soldering is the only recommended soldering method.[3]Refer to SOT883 standard mounting conditions; FR4 printed-circuit board with 60µm copper strip line.Table 6.Limiting valuesIn accordance with the Absolute Maximum Rating System (IEC 60134).Symbol ParameterConditions Min Max Unit V CBO collector-base voltage open emitter -−50V V CEO collector-emitter voltage open base -−50V V EBO emitter-base voltage open collector-−15V V Iinput voltage positive -+15V negative-−40V I O output current (DC)-−100mA I CM peak collector current -−100mA P tottotal power dissipation T amb ≤ 25°CSOT416[1]-150mW SOT346[1]-250mW SOT883[2][3]-250mW SOT54[1]-500mW SOT23[1]-250mW SOT323[1]-200mW T stg storage temperature −65+150°C T j junction temperature -150°C T ambambient temperature−65+150°CTable 7.Thermal characteristics Symbol ParameterConditions Min Typ Max UnitR th(j-a)thermal resistance from junction to ambient in free airSOT416[1]--833K/W SOT346[1]--500K/W SOT883[2][3]--500K/W SOT54[1]--250K/W SOT23[1]--500K/W SOT323[1]--625K/W7.CharacteristicsTable 8.CharacteristicsT amb = 25°C unless otherwise specifiedSymbol Parameter Conditions Min Typ Max Unit I CBO collector-base cut-offcurrentV CB =−50 V; I E = 0 A--−100nAI CEO collector-emittercut-off current V CE =−30 V; I B = 0 A--−1µA V CE =−30 V; I B = 0 A;T j=150°C--−50µAI EBO emitter-base cut-offcurrentV EB =−5 V; I C = 0 A--−150µA h FE DC current gain V CE =−5 V; I C =−5 mA40--V CEsat collector-emittersaturation voltageI C =−10 mA; I B =−0.5mA--−150mV V I(off)off-state input voltage V CE =−5 V; I C =−100µA-−3.1−1V V I(on)on-state input voltage V CE =−300 mV; I C =−2mA−6−3.8-V R1bias resistor 1 (input)334761kΩR2/R1bias resistor ratio0.170.210.26C c collector capacitance V CB =−10 V; I E = i e = 0 A;f=1MHz--2pFV CE =−5 V (1)T amb = 100°C (2)T amb = 25°C (3)T amb =−40°CI C /I B = 20(1)T amb = 100°C (2)T amb = 25°C (3)T amb =−40°CFig 1.DC current gain as a function of collector current; typical valuesFig 2.Collector-emitter saturation voltage as a function of collector current; typical valuesV CE =−0.3 V (1)T amb =−40°C (2)T amb = 25°C (3)T amb = 100°CV CE =−5 V (1)T amb =−40°C (2)T amb = 25°C (3)T amb = 100°CFig 3.On-state input voltage as a function of collector current; typical valuesFig 4.Off-state input voltage as a function of collector current; typical valuesI C (mA)−10−1−102−10−1006aaa11110210103h FE1(1)(2)(3)I C (mA)−1−102−10006aaa112−10−1−1V CEsat (V)−10−2(1)(3)(2)006aaa113I C (mA)−10−1−102−10−1−10V I(on)(V)−1(1)(2)(3)006aaa114I C (mA)−10−1−10−1−10V I(off)(V)−1(1)(2)(3)8.Package outlineFig 5.Package outline SOT416 (SC-75)UNIT A 1max b p c D E e 1H E L p Q w REFERENCESOUTLINE VERSION EUROPEAN PROJECTIONISSUE DATE IECJEDECJEITA mm0.10.300.150.250.101.81.40.90.70.5e 11.751.450.2v 0.2DIMENSIONS (mm are the original dimensions)0.450.150.230.13SOT416SC-75w M b pD e 1eAA 1L pQdetail XH EE A B Bv M A00.5 1 mmscaleA 0.950.60cX123Plastic surface-mounted package; 3 leadsSOT41604-11-0406-03-16Fig 6.Package outline SOT346 (SC-59A/TO-236)UNIT A 1b p c D E e 1H E L p Q w v REFERENCESOUTLINE VERSION EUROPEAN PROJECTIONISSUE DATE IECJEDEC JEITA mm0.500.350.260.103.12.71.71.30.95e 1.93.02.50.330.230.20.2DIMENSIONS (mm are the original dimensions)0.60.2SOT346TO-236SC-59Ab pDe 1eAA 1L pQdetail XH EEw M v M ABAB01 2 mmscaleA 1.31.00.10.013cX123Plastic surface-mounted package; 3 leads SOT34604-11-1106-03-16Fig 7.Package outline SOT883 (SC-101)UNIT A 1max.A (1)b b 1e 1e L L 1 REFERENCESOUTLINE VERSION EUROPEAN PROJECTIONISSUE DATE IECJEDECJEITA mm0.500.460.200.120.550.470.030.620.550.350.65DIMENSIONS (mm are the original dimensions)Note1. Including plating thickness0.300.220.300.22SOT883SC-10103-02-0503-04-03D E 1.020.95LE231b b 1A 1A DL 100.5 1 mmscaleLeadless ultra small plastic package; 3 solder lands; body 1.0 x 0.6 x 0.5 mm SOT883ee 1Fig 8.Package outline SOT54 (SC-43A/TO-92)UNIT A REFERENCESOUTLINE VERSION EUROPEAN PROJECTIONISSUE DATE IECJEDEC JEITA mm5.25.0b 0.480.40c 0.450.38D 4.84.4d 1.71.4E 4.23.6L 14.512.7e 2.54e 11.27L 1(1)max.2.5b 10.660.55DIMENSIONS (mm are the original dimensions)Note1. Terminal dimensions within this zone are uncontrolled to allow for flow of plastic and terminal irregularities.SOT54TO-92SC-43A04-06-2804-11-16AL0 2.5 5 mmscalebcDb 1L 1dE Plastic single-ended leaded (through hole) package; 3 leads SOT54e 1e123分销商库存信息:NXPPDTA144VM,315PDTA144VE,115PDTA144VT,215 PDTA144VU,115PDTA144VK,115PDTA144VS,126。

金属化聚丙烯膜抗干扰电容器(X2型)产品规格承认书说明书

产品规格承认书Product Spec Certification客户名:品名:金属化聚丙烯抗干扰电容(X2)型号:MPX-224K275VAC-B-C3-35客户料号:C2856310日期:批准审核拟制产品外形尺寸客户料号容量(μF )容量误差(%)额定电压(VAC )1KDF (%)尺寸加工方式制造商料号W ±0.5MM H ±0.5MM T ±0.5MM P ±0.5MM L±0.3MM d ∮±0.05C28563100.22102750.113126103.50.6AMPX-224K275VAC-B-C3-35芯通电子科技有限公司拟定审核批准编码规则MPX 0.22μF K 275VAC 13*12*6mm P=10mm1、电容器型别2、电容量代码表示方法用电容单位法拉表达,前面两位代表容量大小,第三位数要制定跟随以下101=0.0001μF 104=0.1μF 102=0.001μF 105=1.0μF 103=0.01μF 106=10.0μF 3、电容量偏差4、额定电压代码025002750300030506301000120016002000类型250V275V 300V 305V 630V 1000V 1200V 1600V 2000V5、额定电压别6、脚距(mm)7、内部识别码外壳型号代码PEI-MPX-CBB22-CBB21-CL21-CL22-CBB81-类型PEIMPXCBB22CBB21CL21CL22CBB81代码G J K M 电容量偏差±2.5%±5%±10%±20%代码V VAC 类型DCAC代码AA A B C D E F G H I 类型≦57.510152022.52526.527.531.5MPX -224K 275V AC -B -C3-351234567金属化聚丙烯膜抗干扰电容器TYPE:MPX产生说明书Rev.11、应用本规范涵盖了金属化聚丙烯介质固定的要求。

计算机电缆标准

RVB铜芯聚氯乙烯平型连接电线

RVS铜芯聚氯乙烯绞型连接电线

RVV铜芯聚氯乙烯绝缘聚氯乙烯护套圆形连接软电缆

ARVV镀锡铜芯聚氯乙烯绝缘聚氯乙烯护套平形连接软电缆

RVVB铜芯聚氯乙烯绝缘聚氯乙烯护套平形连接软电缆

RV-105铜芯耐热105oC聚氯乙烯绝缘聚氯乙烯绝缘连接软电缆

NH—耐火型

WDZ—无卤低烟阻燃型

WDN—无卤低烟耐火型

例如:

SYV 75-5-1(A、B、C)

S:射频Y:聚乙烯绝缘V:聚氯乙烯护套A:64编B:96编C:128编

75:75欧姆5:线径为5MM 1:代表单芯SYWV 75-5-1

S:射频Y:聚乙烯绝缘W:物理发泡V:聚氯乙烯护套

75:75欧姆5:线缆外径为5MM 1:代表单芯来源:输配电设备网

其客户群涉及:政府机关、国家电网、系统集成商、通信运营商和跨国公司,服务亚太地区电力基础设施,光电通信设施等为用户提供完善的产品和服务。

凭借着“科技至上、品质至上,团队至上,服务至上”的理念,成为全球电缆通讯行业的领先品牌,并拥有实力雄厚的产品设计研发团队,系统方案解决团队,供应链管理团队以及市场营销团队。

矿用信号电缆……………………………………………………………………………39

信号电缆…………………………………………………………………………………42

射频电缆…………………………………………………………………………………44

补偿导线、电缆…………………………………………………………………………46

塑料绝缘安装屏蔽电线、电缆…………………………………………………………47

NH-ZR-YJS-C交联聚乙烯绝缘无卤低烟、阻燃热塑性聚烯烃衬垫(或护层)耐火型电力电缆

光缆产品资料GYTA-144B1

产品资料GYXTW-12B1(12芯及以下)有线电视系统中心束管式光缆GYTA-288B1.3(288芯及以下)有线电视系统层绞式光缆XXXXX有限公司目录一、产品描述 (2)二、产品执行标准 (2)三、产品特性 (2)四、光缆结构(包括截面图)及各部分的详细尺寸 (3)五、产品性能指标 (4)六、产品照片 (7)一、产品描述1.GYXTW-12B1(12芯及以下)有线电视系统中心束管式光缆结构是将光纤套入高模量材料制成的松套管中,松套管内填充防水化合物。

松套管外用一层双面涂塑钢带(PSP)纵包,钢带和松套管之间加阻水材料以保证光缆的紧凑和纵包阻水,两侧放置两根平行钢丝后挤制聚乙烯护套成缆。

2.GYTA-288B1.3(288芯及以下)有线电视系统层绞式光缆的结构是将光纤套入高模量材料制成的松套管中,缆芯的中心是一根金属加强芯,对于某些芯数的光缆来说,金属加强芯还需挤上一层聚乙烯(PE)。

松套管(和填充绳)围绕中心加强芯绞合成紧凑和圆形的缆芯,缆芯内的缝隙充以阻水填充物。

涂塑铝带(APL)纵包后挤制聚乙烯护套成缆。

二、产品执行标准1.GYXTW-12B1(12芯及以下)有线电视系统中心束管式光缆:光缆主要机械性能和环境性能符合YD/T769-2010标准。

单模光纤符合ITU-TG652标准和IEC最新要求。

2.GYTA-288B1.3(288芯及以下)有线电视系统层绞式光缆:光缆主要机械性能和环境性能符合YD/T901-2009标准。

单模光纤符合ITU-TG652标准和IEC最新要求。

三、产品特性1.GYXTW-12B1(12芯及以下)有线电视系统中心束管式光缆:✧具有很好的机械性能和温度特性;✧松套管材料本身具有良好的耐水解性能和较高的强度;✧管内充以特种油膏,对光纤进行了关键性保护;✧良好的抗压性和柔软性;✧双面涂塑钢带(PSP)提高光缆的抗透潮能力;✧两根平行钢丝保证光缆的抗拉强度;✧直径小、重量轻、容易敷设。

MAX144中文资料

SINAD

70

dB

Total Harmonic Distortion (including 5th-order harmonic)

THD

Spurious-Free Dynamic Range SFDR

80

Channel-to-Channel Crosstalk Small-Signal Bandwidth

ΞϓϦέʔγϣϯ _______________________

όοςϦۦಈثػ

ܭଌث

ϙʔλϒϧσʔλϩΪϯά

ࢼثػݧ

ઈԑσʔλऩू

ҩྍثػ

ϓϩηε੍ࢹޚ

γεςϜࢹ

ϐϯஔ _______________________________

TOP VIEW

VDD 1 CH0 (CH+) 2 CH1 (CH-) 3

µMAX (derate 4.1mW/°C above +70°C) .................... 330mW

Plastic DIP (derate 9.09mW/°C above +70°C) ............727mW CERDIP (derate 8.00mW/°C above +70°C) . .............. 640mW Operating Temperature Ranges (TA) MAX144/MAX145_C_A .......................................0°C to +70°C MAX144/MAX145_E_A. ...................................-40°C to +85°C MAX144/MAX145_M_A ................................ -55°C to +125°C Storage Temperature Range .............................-65°C to +150°C Lead Temperature (soldering, 10sec) .............................+300°C

达塔数据盘型PS6600WC商品说明书

Structure

IP66F, IP67F, UL 50/50E,Type 1, Type 4X (indoor use only),Type 12,Type 13 NOTE:On the front panel when properly installed in an enclosure.

Weight

Voltage Drop

5 ms or less

20 ms or less

5 ms or less

20 ms or less

Power Consumption*4

Panel Unit Only: 73 W When power is not supplied to external devices (Max 138 W) Box Unit Only: 56 W When power is not supplied to external devices (Max 121 W)

Projected capacitive (multi-touch)

261.12 x 163.2 mm (10.28 x 6.43 in)

White LED (not user replaceable. Please contact customer support.)

50,000 hours or more (continuous operation at 25 °C [77 °F] before backlight brightness decreases to 25%)

260-pin SODIMM socket x 2, DDR4-2133 (Up to 16 GB/socket, up to 32 GB for 2 sockets)

Intel® UHD Graphics 620 (built in CPU)

泓格数据采集卡PIOD144U快速选型手册

权利声明和友善提示

承诺

郑重承诺:凡泓格科技股份有限公司产品从购买即日起一年内无任何材料性缺损。

权利声明

泓格公司拥有本手册的所有权利,包括泓格公司的专利、著作权等产权利益。任何团体或个人,未 经泓格公司明确的授权,不得复制、传播或使用本手册全部或其中的内容进行商业活动,违者将要对造 成的任何损失承担责任。

3

ICP DAS PIO-D144U 用户手册 Version 1.0

5 ……………………………………………… 自我测试

1.使用 CA-5002(选购品) 将 CN5 连接至 CN6。

(Port12, Port13, Port14 连接至 Port15, Port16, Port17)

CN1

CN2

23

PB_4

21

PB_5

19

PB_6

17

PB_7

15

PC_0

13

PC_1

11

PC_2

9

PC_3

7

PC_4

5

PC_5

3

PC_6

1

PC_7

所有的信号皆符合 TTL 规范

TTL 高电位(1) 2.4 ~ 5.0 V (超过 5.0 V 后会有设备毁损的风险)

未定义

2.4 V ~ 0.8 V

低电位(0)

低于 0.8 V

CN3 CN4 CN5 CN6

CA-5002

2. 执行 PIO-D144U DIO 范列程序。 压缩文件案路径:

CD:\NAPDOS\PCI\PIO-DIO\DLL_OCX\Demo /pub/cd/iocard/pci/napdos/pci/pio-dio/dll_ocx/ demo/

技术手册 PD4-E (EtherCAT)说明书

技术手册 PD4-E现场总线: EtherCAT适用于以下设备:PD4-E591L42-E-65-1, PD4-E601L42-E-65-1, PD4-EB59CD-E-65-1适用于固件版本 FIR-v1748技术手册版本: 1.0.1内容1 简介 (7)1.1 版本信息 (7)1.2 版权、名称和联系信息 (7)1.3 预期用途 (7)1.4 保修和免责声明 (7)1.5 专业人员 (8)1.6 其他适用规则 (8)1.7 欧盟产品安全指令 (8)1.8 使用的图标 (8)1.9 文本中的强调 (8)1.10 数值 (9)1.11 位 (9)1.12 计数方向#箭头# (9)2 安全和警告通知 (10)3 技术细节和引脚分配 (11)3.1 环境条件 (11)3.2 尺寸图 (11)3.3 电性能和技术数据 (12)3.4 过热保护 (13)3.5 LED 信号 (15)3.6 引脚分配 (17)4 调试 (22)4.1 正在建立通信 (22)4.2 自动设置 (23)4.3 试运行 (26)4.4 特殊驱动模式#脉冲方向和模拟转速# (27)5 一般概念 (30)5.1 控制模式 (30)5.2 CiA 402 电源状态机 (33)5.3 用户定义单位 (38)5.4 运动范围限制 (42)5.5 循环时间 (42)6 工作模式 (44)6.1 标准定位 (44)6.2 速度 (52)6.3 标准速度 (53)6.6 插补位置模式 (65)6.7 循环同步位置 (66)6.8 循环同步速度 (68)6.9 循环同步转矩 (69)6.10 脉冲方向模式 (70)6.11 自动设置 (72)7 特殊功能 (73)7.1 数字输入和输出 (73)7.2 I2t 电机过载保护 (81)7.3 保存对象 (82)8 EtherCAT (87)9 使用NanoJ编程 (88)9.1 NanoJ 程序 (88)9.2 NanoJ 程序中的映射 (91)9.3 NanoJ 程序中的系统调用 (93)10 对象目录说明 (95)10.1 概述 (95)10.2 对象说明的结构 (95)10.3 对象说明 (95)10.4 数值说明 (96)10.5 说明 (97)1000h Device Type (98)1001h Error Register (98)1003h Pre-defined Error Field (99)1008h Manufacturer Device Name (103)1009h Manufacturer Hardware Version (104)100Ah Manufacturer Software Version (104)1010h Store Parameters (105)1011h Restore Default Parameters (108)1018h Identity Object (111)1020h Verify Configuration (113)1600h Receive PDO 1 Mapping Parameter (114)1601h Receive PDO 2 Mapping Parameter (117)1602h Receive PDO 3 Mapping Parameter (119)1603h Receive PDO 4 Mapping Parameter (121)1A00h Transmit PDO 1 Mapping Parameter (123)1A01h Transmit PDO 2 Mapping Parameter (126)1A02h Transmit PDO 3 Mapping Parameter (128)1A03h Transmit PDO 4 Mapping Parameter (131)1C00h Sync Manager Communication Type (133)1C12h Sync Manager PDO Assignment (135)1C13h Sync Manager PDO Assignment (136)1C32h Output Sync Manager Synchronization (138)1C33h Input Sync Manager Synchronization (139)1F50h Program Data (140)1F51h Program Control (142)1F57h Program Status (143)2034h Upper Voltage Warning Level (145)2035h Lower Voltage Warning Level (146)2036h Open Loop Current Reduction Idle Time (146)2037h Open Loop Current Reduction Value/factor (147)2038h Brake Controller Timing (147)2039h Motor Currents (149)203Ah Homing On Block Configuration (151)203Bh I2t Parameters (152)203Dh Torque Window (155)203Eh Torque Window Time Out (155)203Fh Max Slippage Time Out (156)2056h Limit Switch Tolerance Band (156)2057h Clock Direction Multiplier (157)2058h Clock Direction Divider (157)2059h Encoder Configuration (157)205Ah Absolute Sensor Boot Value (in User Units) (158)205Bh Clock Direction Or Clockwise/Counter Clockwise Mode (158)2084h Bootup Delay (159)2101h Fieldbus Module Availability (159)2102h Fieldbus Module Control (160)2103h Fieldbus Module Status (162)2110h EtherCAT Slave Status (164)2300h NanoJ Control (164)2301h NanoJ Status (165)2302h NanoJ Error Code (166)230Fh Uptime Seconds (167)2310h NanoJ Input Data Selection (168)2320h NanoJ Output Data Selection (169)2330h NanoJ In/output Data Selection (171)2400h NanoJ Inputs (172)2410h NanoJ Init Parameters (173)2500h NanoJ Outputs (174)2600h NanoJ Debug Output (175)2701h Customer Storage Area (176)2800h Bootloader And Reboot Settings (176)3202h Motor Drive Submode Select (178)3203h Feedback Selection (179)3204h Feedback Mapping (180)3210h Motor Drive Parameter Set (182)3212h Motor Drive Flags (186)3220h Analog Inputs (188)3221h Analogue Inputs Control (189)3240h Digital Inputs Control (189)3241h Digital Input Capture (192)3242h Digital Input Routing (194)3243h Digital Input Homing Capture (196)3250h Digital Outputs Control (197)3252h Digital Output Routing (200)3320h Read Analogue Input (201)3321h Analogue Input Offset (203)3322h Analogue Input Pre-scaling (204)33A0h Feedback Incremental A/B/I 1 (205)3700h Deviation Error Option Code (206)4012h HW Information (207)4013h HW Configuration (207)4014h Operating Conditions (208)4015h Special Drive Modes (210)4016h Factory Settings (212)6040h Controlword (214)6041h Statusword (215)6042h Vl Target Velocity (216)6043h Vl Velocity Demand (217)6044h Vl Velocity Actual Value (217)6046h Vl Velocity Min Max Amount (218)6048h Vl Velocity Acceleration (219)6049h Vl Velocity Deceleration (220)604Ah Vl Velocity Quick Stop (221)604Ch Vl Dimension Factor (222)605Ah Quick Stop Option Code (223)605Bh Shutdown Option Code (224)605Ch Disable Option Code (224)605Dh Halt Option Code (225)605Eh Fault Option Code (226)6060h Modes Of Operation (226)6061h Modes Of Operation Display (227)6062h Position Demand Value (227)6063h Position Actual Internal Value (228)6064h Position Actual Value (228)6065h Following Error Window (229)6066h Following Error Time Out (229)6067h Position Window (230)6068h Position Window Time (231)606Bh Velocity Demand Value (231)606Ch Velocity Actual Value (232)606Dh Velocity Window (232)606Eh Velocity Window Time (233)6071h Target Torque (233)6072h Max Torque (234)6074h Torque Demand (234)6075h Motor Rated Current (235)6077h Torque Actual Value (235)607Ah Target Position (236)607Bh Position Range Limit (236)607Ch Home Offset (237)607Dh Software Position Limit (238)607Eh Polarity (239)607Fh Max Profile Velocity (240)6080h Max Motor Speed (240)6081h Profile Velocity (241)6082h End Velocity (241)6083h Profile Acceleration (242)6084h Profile Deceleration (242)6085h Quick Stop Deceleration (243)6086h Motion Profile Type (243)6087h Torque Slope (244)608Fh Position Encoder Resolution (244)6090h Velocity Encoder Resolution (245)6091h Gear Ratio (246)6092h Feed Constant (247)6096h Velocity Factor (248)6097h Acceleration Factor (250)6098h Homing Method (251)6099h Homing Speed (251)609Ah Homing Acceleration (252)60A9h SI Unit Velocity (256)60B0h Position Offset (257)60B1h Velocity Offset (257)60B2h Torque Offset (258)60C1h Interpolation Data Record (258)60C2h Interpolation Time Period (259)60C4h Interpolation Data Configuration (260)60C5h Max Acceleration (262)60C6h Max Deceleration (263)60E4h Additional Position Actual Value (263)60E5h Additional Velocity Actual Value (264)60E6h Additional Position Encoder Resolution - Encoder Increments (265)60E8h Additional Gear Ratio - Motor Shaft Revolutions (266)60E9h Additional Feed Constant - Feed (268)60EBh Additional Position Encoder Resolution - Motor Revolutions (269)60EDh Additional Gear Ratio - Driving Shaft Revolutions (270)60EEh Additional Feed Constant - Driving Shaft Revolutions (271)60F2h Positioning Option Code (272)60F4h Following Error Actual Value (273)60F8h Max Slippage (274)60FAh Control Effort (274)60FCh Position Demand Internal Value (275)60FDh Digital Inputs (275)60FEh Digital Outputs (276)60FFh Target Velocity (277)6502h Supported Drive Modes (278)6503h Drive Catalogue Number (279)6505h Http Drive Catalogue Address (279)11 版权 (280)11.1 简介 (280)11.2 AES (280)11.3 MD5 (280)11.4 uIP (281)11.5 DHCP (281)11.6 CMSIS DSP Software Library (282)11.7 FatFs (282)11.8 Protothreads (282)11.9 lwIP (282)1 简介PD4-E 是一款带有集成控制器的无刷电机,防护等级为 IP65。

PDTC144EU中文资料

V

−

−10

V

−

100

mA

−

100

mA

−

200

mW

−65

+150

°C

−

150

°C

−65

+150

°C

THERMAL CHARACTERISTICS

SYMBOL

PARAMETER

Rth j-a

thermal resistance from junction to ambient

Note

1. Transistor mounted on an FR4 printed-circuit board.

1

3

2

MGA893 - 1

Fig.2 Equivalent inverter symbol.

MARKING

TYPE NUMBER

PDTC144EU

MARKING CODE(1)

∗08

Note

1. ∗ = - : Made in Hong Kong. ∗ = t : Made in Malaysia.

• Simplification of circuit design • Reduces number of components

and board space.

APPLICATIONS

• Especially suitable for space reduction in interface and driver circuits

SYMBOL

PARAMETER

CONDITIONS

VCBO VCEO VEBO VI

IO ICM Ptot Tstg Tj Tamb

FUJI 100 120 144 EA Nuvera 数字生产系统 产品手册

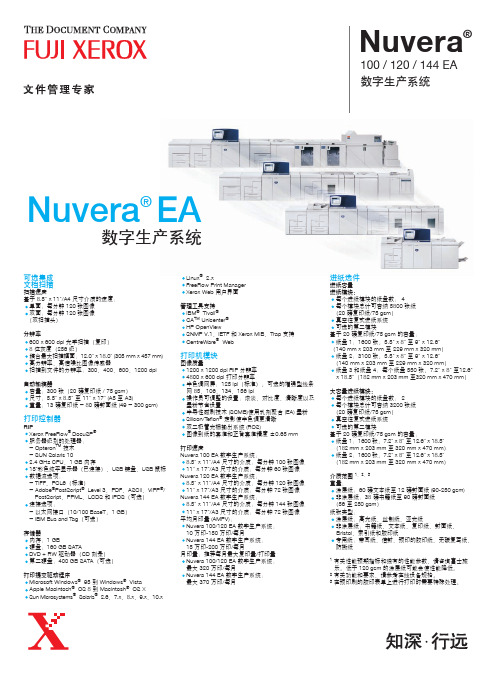

100 / 120 / 144 EANuvera数字生产系统®数字生产系统Nuvera® EA可选集成文档扫描扫描速度基于 8.5" x 11"/A4 尺寸介质的速度: 单面:每分钟 120 张图像 双面:每分钟 120 张图像 (双扫描头)分辨率 600 x 600 dpi 光学扫描(复印) 8 位灰度(256 级) 稿台最大扫描幅面:12.0" x 18.0" (305 mm x 457 mm) 高分辨率、高信噪比图像传感器 扫描到文件的分辨率:300、400、600、1200 dpi自动输稿器 容量:300 张(20 磅复印纸 / 75 gsm) 尺寸:5.5" x 8.5" 至 11" x 17" (A5 至 A3) 重量:13 磅复印纸- 80 磅封面纸 (49 - 300 gsm)打印控制器RIP Xerox FreeFlow® DocuSP® 服务器级别的处理器: - Opteron TM技术 - SUN Solaris 10 2.4 GHz CPU,1 GB 内存 15"彩色纯平显示器(已连接)、USB 键盘、USB 鼠标 数据流选项: - TIFF、PCL6(标准) - Adobe®PostScript® Level 3、PDF、ASCII、VIPP®/ PostScript、PPML、LCDS 和 IPDS(可选) 连接选项: -以太网接口(10/100 BaseT;1 GB) - IBM Bus and Tag(可选)存储器 内存:1 GB 硬盘:160 GB SATA DVD + RW 驱动器(CD 刻录) 第二硬盘:400 GB SATA(可选)打印提交驱动程序 Microsoft Windows® 95 到 Windows® Vista Apple Macintosh® OS 8 到 Macintosh® OS X Sun Microsystems® Solaris® 2.6、7.x、8.x、9.x、10.x Linux® 2.x FreeFlow Print Manager Xerox Web 用户界面管理工具支持 IBM® Tivoli® CA TM Unicenter® HP OpenView SNMP V.1、IETF 和 Xerox MIB,Trap 支持 CentreWare® Web打印机模块图像质量 1200 x 1200 dpi RIP 分辨率 4800 x 600 dpi 打印分辨率 半色调网屏:125 lpi(标准);可选的增强型线条 网 85、106、134、156 lpi 操作员可调整的设置:浓淡、对比度、清晰度以及 墨粉节省设置 半导性磁刷技术 (SCMB)使用乳剂聚合 (EA) 墨粉 Silicon/Teflon®定影使半色调更清晰 双二极管光栅输出系统 (ROS) 图像到纸的套准和正背套准精度±0.65 mm打印速度Nuvera 100 EA 数字生产系统: 8.5" x 11"/A4 尺寸的介质:每分钟 100 张图像 11" x 17"/A3 尺寸的介质:每分钟 60 张图像Nuvera 120 EA 数字生产系统: 8.5" x 11"/A4 尺寸的介质:每分钟 120 张图像 11" x 17"/A3 尺寸的介质:每分钟 72 张图像Nuvera 144 EA 数字生产系统: 8.5" x 11"/A4 尺寸的介质:每分钟 144 张图像 11" x 17"/A3 尺寸的介质:每分钟 72 张图像平均月印量 (AMPV): Nuvera 100/120 EA 数字生产系统: 10 万印-150 万印/每月 Nuvera 144 EA 数字生产系统: 15 万印-200 万印/每月月印量:推荐每月最大复印量/打印量 Nuvera 100/120 EA 数字生产系统: 最大 320 万印/每月 Nuvera 144 EA 数字生产系统: 最大 370 万印/每月进纸选件进纸容量进纸模块: 每个进纸模块的纸盘数: 4 每个模块总计可容纳 5800 张纸 (20 磅复印纸/75 gsm) 真空往复式进纸系统 可选的第二模块基于 20 磅复印纸/75 gsm 的容量: 纸盘 1:1600 张;5.5" x 8" 至 9" x 12.6"(140 mm x 203 mm 至 229 mm x 320 mm) 纸盘 2:3100 张;5.5" x 8" 至 9" x 12.6" (140 mm x 203 mm 至 229 mm x 320 mm) 纸盘 3 和纸盘 4:每个纸盘 550 张;7.2" x 8" 至12.6"x 18.5"(182 mm x 203 mm 至320 mm x 470 mm)大容量进纸模块: 每个进纸模块的纸盘数: 2 每个模块总计可容纳 3200 张纸 (20 磅复印纸/75 gsm) 真空往复式进纸系统 可选的第二模块基于 20 磅复印纸/75 gsm 的容量: 纸盘 1:1600 张;7.2" x 8" 至 12.6" x 18.5" (182 mm x 203 mm 至 320 mm x 470 mm) 纸盘 2:1600 张;7.2" x 8" 至 12.6" x 18.5" (182 mm x 203 mm 至 320 mm x 470 mm)介质范围1、2、3重量: 涂层纸:60 磅文本纸至 12 磅封面纸 (90-250 gsm) 非涂层纸:38 磅书籍纸至 90 磅封面纸 (56 至 250 gsm)纸张类型: 涂层纸:高光纸、丝制纸、亚光纸 非涂层纸:书籍纸、文本纸、复印纸、封面纸、 Bristol、索引纸和胶印纸 专用纸:带耳纸、信封、预印的胶印纸、无碳复写纸、 防撕纸1有关性能预期指标和独有的性能参数,请咨询富士施 乐。

大容量基带拉远型宏基站TDB144A产品说明书

18.3大容量基带拉远型宏基站TDB144A产品说明书目录1概述 (3)2系统结构及各单元功能介绍 (3)2.1产品结构 (4)2.2功能模块 (5)3产品规格参数 (6)3.1整机技术指标 (6)3.2整机工程参数 (8)3.3散热 (9)3.4电磁兼容 (9)4产品冗余配置及备份切换原理 (9)5防尘、抗震及运输环境条件 (10)5.1防尘要求 (10)5.2抗震要求 (10)5.3运输环境条件 (11)6安装环境条件 (11)7直流压降分配 (12)8走线要求 (12)1概述TDB144A(大容量基带拉远型宏基站)是大唐移动通信设备有限公司开发的一种室内型宏蜂窝基站,单机柜最大扩容能力144载频。

通过基带拉远技术,既可以支持本地覆盖,又可以支持远端覆盖,从而解决站址问题。

TDB144A还支持基带池功能,允许根据需要动态调整基带资源。

该产品可以用于解决密集城区、普通城区、郊区、乡村和公路沿线等室外广域网络覆盖,也可以解决城市热点地区、盲点地区的网络覆盖,如商场、大型体育馆、隧道、地铁站、楼宇、住宅小区等,在不大幅增加成本的情况下,改善网络覆盖、提高服务质量。

使用拉远技术可以低成本快速覆盖主要业务区域。

另外,TDB144A拉远型宏基站从软件和硬件上支持冗余备份机制,可以保证设备运行的稳定可靠性,并且具有组网灵活,操作维护方便的特点。

图1:TDB144A宏基站外观图2系统结构及各单元功能介绍TDB144A基带拉远型宏基站是TD-SCDMA RAN系统的重要组成部分。

它由室内主机柜和基带拉远模块组成,通过Iub接口与RNC连接,通过Uu接口与UE通信。

基带拉远模块的基站射频单元完成对射频信号的滤波、信号放大和上下变频处理并采用数字中频技术实现中频模拟信号到基带数字信号的转换处理;基带部分采用TD-SCDMA系统特有的智能天线和联合检测实现对基带信号的解调和扩频处理;在信道编解码上采用Viterbi和Turbo信道编码技术;在与RNC 的连接上采用基于A TM的Iub接口协议,实现NBAP协议和完成对整个基站系统的控制管理。

Nexperia PDZ-B系列单极性变压器谱的产品数据表说明书