SNC11C中文资料

SNC313中文资料

Direct Drive Voice/Dual Tone Melody Controller 1 INTRODUCTIONSNC313 is a 1-channel voice synthesizer and dual-tone melody IC with PWM direct drive circuit. It built-in a 4-bit tiny controller with one 4-bit input port and two 4-bit I/O ports. By programming through the tiny controller in SNC313, user’s varied applications including voice section combination, dual-tone melody, key trigger arrangement, output control, and other logic functions can be easily implemented.2 FEATURESSingle power supply 2.4V – 5.5V7 seconds voice capacity are provided (@6KHZ sample rate)Built in a 4-bit tiny controllerOne 4-bit input port and two 4-bit I/O ports are provided128*4 bits RAM are provided24K*10 ROM size are provided for voice data and programMaximum 16k program ROM is providedReadable ROM code dataIR carrier signal is providedBuilt in a high quality speech synthesizerAdaptive playing speed from 2.5k-20kHz is providedOne voice channel plus Dual-Tone MelodyBuilt in a PWM Direct Drive circuit and a fixed current D/A outputSystem clock : 2MHzLow Power ResetDirect Drive Voice/Dual Tone Melody Controller 3 Block Diagram4 PIN ASSIGNMENTSymbol I/O Function DescriptionP13 ~ P10 I Bit3 ~ Bit0 of Input port 1P23 ~ P20 I/O Bit3 ~ Bit0 of I/O port 2P33 ~ P30 I/O Bit3 ~ Bit0 of I/O port 3VDD P Positive power supplyGND P Negative power supplyRST I Reset pin (active high)OSC O Oscillator / Crystal OutOutput of PWM or DA outputPositiveBUO1/VO OBUO2 O Negative Output of PWMDirect Drive Voice/Dual Tone Melody Controller5 FUNCTION DESCRIPTIONS 5.1. OscillatorSNC313 accept RC type oscillator for system clock. The typical circuit diagram for oscillator is listed as follow.rOSCVCCRC Oscillator5.2. ROMSNC313 contains substantial 24K words (10-bit) internal ROM. Program, voices and other data are shared with this same 24K words ROM.5.3. RAMSNC313 contains 128 nibbles RAM. The 128 nibbles RAM are divided into eight pages (page 0 to page 7, 16 nibbles RAM on each page). In our programming structure, users can easily define and locate RAM page in the program. For instance, users can use the instructions, PAGEn (n=0 to 7) to switch and indicate the RAM page. Besides, users can use direct mode, M0 ~ M15 in the data transfer type instructions, to access all 16 nibbles of each page.5.4. Power Down Mode“End” instruction will power down SNC313 and enable IC to consume fewer current for power saving. (<3uA @VDD=3V and <5uA @VDD=5V) Please be aware that when the power down mode is activated in SNC313, any valid data transition (L H or H L) occurring on any input port (P1) or IO ports (P2 and P3) will lead SNC313 back to normal operation mode.5.5. Sampling Rate CounterThe unique sampling rate counter is designed in voice channel to be able to play diverse voices at different sample playing rates. The playing rate can be adaptively set up among from the wide ranges of 2.5KHz to 20KHz. This feature makes voice close to its original source and yield the better voice quality.5.6. Dual-Tone GeneratorA dual-tone melody generator is included to generate 2-channel music songs with a pleasant square-wave-like timbre. The pitch range of each tone generator is as wide as 4 octaves (48 different notes totally). The output of dual-tone generator can be mixed with the output of voice synthesizer to achieve voice playing with BGM (background music). Additionally, Sonix provides a numbered-musical-notation representation to help users compose their songs. Further, a MIDI (1.0) file translator can convert MIDI files into Sonix format.5.7. I/O PortsP1 is a 4-bit input port and P2/P3 are two 4-bit I/O ports. Any bit of P2 and P3 can be programmed as either input or output port individually. Any valid data transition (H L or L H) of P1, P2 and P3 can reactivate the chip when the chip is in power-down mode.Input Port Configuration (P10~P13)I/O Port Configuration (P20~P23, P30~P33)Note: weak N-MOS’s can serve as pull-low resistor.5.8. IR FunctionP33 can be modulated with 38.5KHz square wave before sent out to P33 pin. The IR signal can be achieved by this modulated signal.5.9. DAC & PWMSNC313 is an advanced chip to be designed having two optimal methods to play out the voices. One is DAC and the other is PWM. Upon user’s applications, user can select either DAC or PWM in his design. Please be aware that only one method can be activated at a time.DAC: A 7-bit current type digital-to-analog converter is built-in SNC313. The relationship between input digital data and output analog current signal is listed in the following table. Also, the recommended application circuit is illustrated as follows.Input data Typical value of output current (mA)0 01 3/127…N n*(3/127)…127 3DAC outputPWM: A PWM (pulse width modulation) circuit is built-in SNC313. PWM can convert input digital data into pulse trains with suitable different pulse width. The maximum resolution of PWM is 7 bits. Two huge output stage circuits are designed in SNC313. With this advanced circuit, the chip is capable of driving speaker directly without external transistors. The recommended application circuit is illustrated as follows.PWM OutputDirect Drive Voice/Dual Tone Melody Controller 6 ABSOLUTE MAXIMUM RATINGItems Symbol Min Max Unit.Supply Voltage V DD-V -0.3 6.0 VInput Voltage V IN V SS-0.3 V DD+0.3 VOperating Temperature T OP 0 55.0 o CStorage Temperature T STG -55.0 125.0 o C7 ELECTRICAL CHARACTERISTICSItem Sym. Min. Typ. Max. Unit Condition Operating Voltage V DD 2.4 3.0 5.5 VStandby current I SBY - 2.05.0 - u A V DD=3V , no loadV DD=4.5V, no loadOperating Current I OPR - 300700 - u A V DD=3V , no loadV DD=4.5V, no loadInput current ofP1, P2, P3I IH - 3.0 10.0 u A V DD=3V,V IN=3VDrive current ofP2, P3I OD- 4 - m A V DD=3V,V O=2.4VSink Current ofP2, P3I OS- 6 - m A V DD=3V,V O=0.4VDrive current ofP2, P3I OD- 5 - m A V DD=4.5V,V O=3.9VSink Current ofP2, P3I OS- 9 - m A V DD=4.5V,V O=0.4V Drive current of Buo1 I OD 100 120 - m A VDD=3V,Buo1=1.5V Sink Current of Buo1 I OS 100 120 - m A VDD=3V,Buo1=1.5V Drive Current of Buo2 I OD 100 120 - m A VDD=3V,Buo2=1.5V Sink Current of Buo2 I OS 100 120 - m A VDD=3V,Buo2=1.5V Oscillation Freq. F OSC - 2.0 - MHzV DD=3VIR Carrier Frequency Fir - 38.5 - KHz Fosc=2MHzDirect Drive Voice/Dual Tone Melody Controller 8 ROSC PerformanceROSC frequency vs VDD (Typical value, R=120KΩ)ROSC frequency vs. VDD (For various R)Direct Drive Voice/Dual Tone Melody Controller 9 APPLICATION CIRCUITD/A Speaker Output16 Scan KeysNote: The C1 (0.1uF) between Power and GND should be closed to VDD pin of SNC313 as possible.Direct Drive Voice/Dual Tone Melody Controller10 BONDING PAD12345678910111213141516171819P10P11P12P13P20P21OSCG N DB U O 1V D DB U O 2G N D P22P23P30P31P32P33RST (0.00,0.00)SNC313Note: The substrate MUST be connected to Vss in PCB layout.Direct Drive Voice/Dual Tone Melody Controller DISCLAIMERThe information appearing in SONiX web pages (“this publication”) is believed to be accurate.However, this publication could contain technical inaccuracies or typographical errors. The reader should not assume that this publication is error-free or that it will be suitable for any particular purpose. SONiX makes no warranty, express, statutory implied or by description in this publication or other documents which are referenced by or linked to this publication. In no event shall SONiX be liable for any special, incidental, indirect or consequential damages of any kind, or any damages whatsoever, including, without limitation, those resulting from loss of use, data or profits, whether or not advised of the possibility of damage, and on any theory of liability, arising out of or in connection with the use or performance of this publication or other documents which are referenced by or linked to this publication.This publication was developed for products offered in Taiwan. SONiX may not offer the products discussed in this document in other countries. Information is subject to change without notice. Please contact SONiX or its local representative for information on offerings available. Integrated circuits sold by SONiX are covered by the warranty and patent indemnification provisions stipulated in the terms of sale only. The application circuits illustrated in this document are for reference purposes only. SONIX DISCLAIMS ALL WARRANTIES, INCLUDING THE WARRANTY OF MERCHANTABILITY OR FITNESS FOR ANY PURPOSE. SONIX reserves the right to halt production or alter the specifications and prices, and discontinue marketing the Products listed at any time without notice. Accordingly, the reader is cautioned to verify that the data sheets and other information in this publication are current before placing orders.Products described herein are intended for use in normal commercial applications. Applications involving unusual environmental or reliability requirements, e.g. military equipment or medical life support equipment, are specifically not recommended without additional processing by SONIX for such application.Direct Drive Voice/Dual Tone Melody Controller。

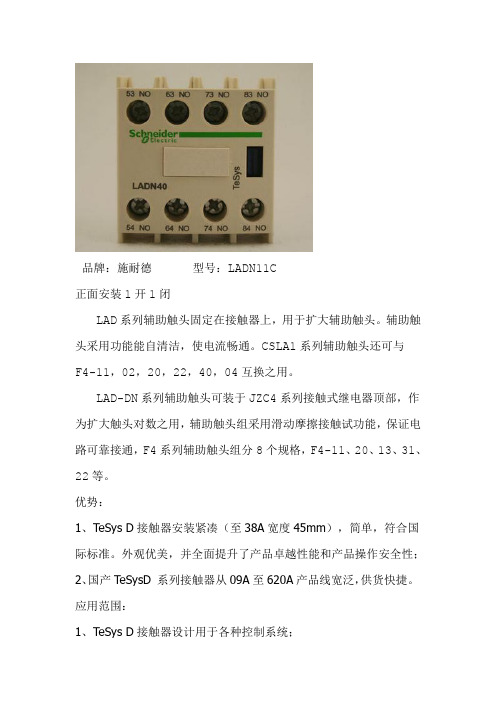

LADN11C施耐德

品牌:施耐德型号:LADN11C正面安装1开1闭LAD系列辅助触头固定在接触器上,用于扩大辅助触头。

辅助触头采用功能能自清洁,使电流畅通。

CSLA1系列辅助触头还可与F4-11,02,20,22,40,04互换之用。

LAD-DN系列辅助触头可装于JZC4系列接触式继电器顶部,作为扩大触头对数之用,辅助触头组采用滑动摩擦接触试功能,保证电路可靠接通,F4系列辅助触头组分8个规格,F4-11、20、13、31、22等。

优势:1、TeSys D接触器安装紧凑(至38A宽度45mm),简单,符合国际标准。

外观优美,并全面提升了产品卓越性能和产品操作安全性;2、国产TeSysD 系列接触器从09A至620A产品线宽泛,供货快捷。

应用范围:1、TeSys D接触器设计用于各种控制系统;2、能够作为各种应用情况下的电动机起动器。

性能描述:1紧凑安装> 至38A的接触器以及保护元件仅为45mm 宽度> 浪涌抑制器的安装无需工具,直接插入到接触器中,无需占用更多空间> 可逆接触器仅90mm 宽度,机械连锁不占用额外空间,安装几乎无需时间> 起动器元件提供预接线模块,起动器组装快捷方便,外形美观2高度集成> 至100A 接触器集成1常开/ 1常闭辅助触点> 直流线圈内置双向抑流二极管> 可逆接触器组内置双向抑流二极管> 创新直流低功耗接触器简化自动化系统设计3安全可靠> 控制与保护元件的主回路、控制回路区分明显> 符合安全标准的镜像触点设计,确保一亿次可靠动作> 保护罩防止接触器意外接通> 断路器、热继电器拨盘配置可挂锁面盖,防止意外改动4品质卓越> 直流线圈具有宽范围控制电压(0.7~1.25Uc)> 抗震性强> 更低噪音> 接线端子强度提高。

《SNC介绍》PPT课件

Electroloy Metal<shenzhen>Co.,Ltd

SN100C 无铅焊料

波峰焊接须知

无论是SN100C合金还是SAC305合金在使用过程中都会出现Cu超 标现象,在使用SN100C焊料时,如果锡槽内Cu含量超过0.85%时,易 造成锡桥、锡尖等其它焊接缺陷.

Cu超标是指铜与锡在高温下生成的两种金属间化合物 Cu6Sn5、Cu3Sn.

SN100C 无铅焊料

抗疲劳性实验对比

特性 SN100C SAC305 SnPb37

比较

疲劳 寿命 (Nf)

大约 3最高 600

Nf表示循环次数

抗疲劳实验: 焊点经过高低温冲击,其条件是:-45℃/12min--125℃/25min, 发生变化:焊点与焊盘结合部.

SN100C 无铅焊料

焊料表面张力对比

焊料表面张力 定义:

在棒表面附有粘 性大的液体

在棒表面没 有附有液体

粘性大的液体

粘性小的液体

通常指焊料的粘性,它是不利于焊接的一个重要因素.但 表面张力是物质特性,只能降低不能消除,在焊接过程中,通 过降低焊料表面张力来提高焊料的润湿性.

Electroloy Metal<shenzhen>Co.,Ltd

由于:

它的熔点是217-219℃即液相线与固相线相差2 ℃.

所以SAC305在冷却过程中一开始会有局部纯锡先固 化,并分散成枝状体.其它剩余焊料继续固化,并会 呈现体积收缩状,此时的焊料最后冷却中心处形成 微裂的收口.

Electroloy Metal<shenzhen>Co.,Ltd

SN100C 无铅焊料

SN100C 无铅焊料

反复伸缩实验对比

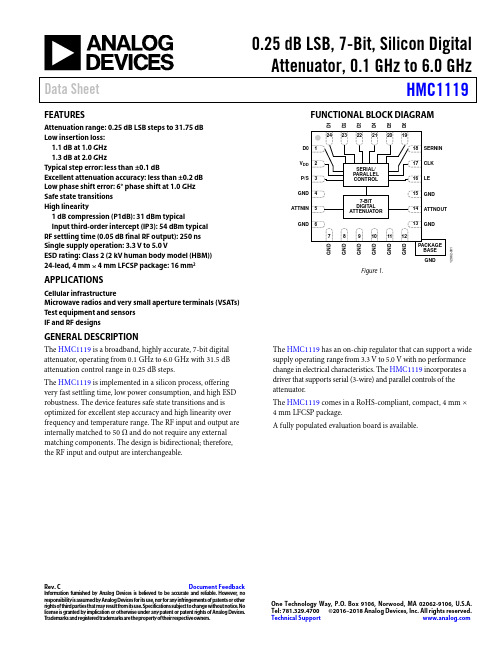

Silicon Digital Attenuator HMC1119数据手册说明书

0.25 dB LSB, 7-Bit, Silicon DigitalAttenuator, 0.1 GHz to 6.0 GHz Data Sheet HMC1119Rev. C Document FeedbackInformation furnished by Analog Devices is believed to be accurate and reliable. However, noresponsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners. O ne Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2016–2018 Analog Devices, Inc. All rights reserved. Technical Support FEATURESAttenuation range: 0.25 dB LSB steps to 31.75 dBLow insertion loss:1.1 dB at 1.0 GHz1.3 dB at2.0 GHzTypical step error: less than ±0.1 dBExcellent attenuation accuracy: less than ±0.2 dBLow phase shift error: 6° phase shift at 1.0 GHzSafe state transitionsHigh linearity1 dB compression (P1dB): 31 dBm typicalInput third-order intercept (IP3): 54 dBm typicalRF settling time (0.05 dB final RF output): 250 nsSingle supply operation: 3.3 V to 5.0 VESD rating: Class 2 (2 kV human body model (HBM))24-lead, 4 mm × 4 mm LFCSP package: 16 mm2 APPLICATIONSCellular infrastructureMicrowave radios and very small aperture terminals (VSATs) Test equipment and sensorsIF and RF designsFUNCTIONAL BLOCK DIAGRAMVGND65432112962-1Figure 1.GENERAL DESCRIPTIONThe HMC1119 is a broadband, highly accurate, 7-bit digital attenuator, operating from 0.1 GHz to 6.0 GHz with 31.5 dB attenuation control range in 0.25 dB steps.The HMC1119 is implemented in a silicon process, offering very fast settling time, low power consumption, and high ESD robustness. The device features safe state transitions and is optimized for excellent step accuracy and high linearity over frequency and temperature range. The RF input and output are internally matched to 50 Ω and do not require any external matching components. The design is bidirectional; therefore, the RF input and output are interchangeable. The HMC1119 has an on-chip regulator that can support a wide supply operating range from 3.3 V to 5.0 V with no performance change in electrical characteristics. The HMC1119 incorporates a driver that supports serial (3-wire) and parallel controls of the attenuator.The HMC1119 comes in a RoHS-compliant, compact, 4 mm ×4 mm LFCSP package.A fully populated evaluation board is available.HMC1119Data SheetRev. C | Page 2 of 15TABLE OF CONTENTSFeatures .............................................................................................. 1 Applications ....................................................................................... 1 Functional Block Diagram .............................................................. 1 General Description ......................................................................... 1 Revision History ............................................................................... 2 Specifications ..................................................................................... 3 Electrical Specifications ............................................................... 3 Timing Specifications .................................................................. 4 Absolute Maximum Ratings ....................................................... 5 ESD Caution .................................................................................. 5 Pin Configuration and Function Descriptions ............................. 6 Interface Schematics..................................................................... 7 Typical Performance Characteristics ............................................. 8 Insertion Loss, Return Loss, State Error, Step Error, andRelative Phase ................................................................................8 Input Power Compression and Third-Order Intercept ......... 10 Theory of Operation ...................................................................... 11 Serial Control Interface ............................................................. 11 RF Input Output ......................................................................... 11 Parallel Control Interface .......................................................... 12 Power-Up Sequence ................................................................... 12 Applications Information .............................................................. 13 Evaluation Printed Circuit Board ............................................ 13 Packaging and Ordering Information ......................................... 15 Outline Dimensions ................................................................... 15 Ordering Guide .. (15)REVISION HISTORY4/2018—Rev. B to Rev CChanges to Figure 23 ...................................................................... 12 Change to PCB Description, Table 7 ............................................ 13 Updated Outline Dimensions . (15)9/2017—Rev. A to Rev. BChanged CP-24-16 to HCP-24-3 ................................. Throughout Updated Outline Dimensions ....................................................... 15 Changes to Ordering Guide .......................................................... 15 8/2017—Rev. 0 to Rev. AAdded Timing Specifications Section ............................................. 4 Moved Table 2 .................................................................................... 4 Changes to Figure 5 and Figure 6 .................................................... 7 Changes to Serial Control Interface Section ............................... 11 Moved Figure 22 and Table 6 ........................................................ 11 Changes to Figure 23 ...................................................................... 12 Moved Parallel Control Interface Section, Direct Parallel Mode Section, Latched Parallel Mode Section, Power-Up Sequence Section, and Power-Up States Section ......................................... 12 Updated Outline Dimensions . (15)9/2016—Revision 0: Initial VersionData SheetHMC1119Rev. C | Page 3 of 15SPECIFICATIONSELECTRICAL SPECIFICATIONSV DD = 3.3 V to 5.0 V , T A = 25°C, 50 Ω system, unless otherwise noted. Table 1.ParameterTest Conditions/Comments Min Typ Max Unit FREQUENCY RANGE0.1 6.0 GHz INSERTION LOSS 0.1 GHz to 1.0 GHz 1.1 1.8 dB 0.1 GHz to 2.0 GHz 1.3 2.0 dB 0.1 GHz to 4.0 GHz 1.6 2.3 dB0.1 GHz to 6.0 GHz 2.0 2.8 dB ATTENUATION 0.2 GHz to 6.0 GHzRange Delta between minimum and maximum attenuation states31.75dB AccuracyReferenced to insertion loss; all attenuation states−(0.05 + 4% of attenuation setting) +(0.05 + 4% of attenuation setting) dB Step Error All attenuation states±0.1 dB Overshoot Between all attenuation states ≤0.1 dB RETURN LOSSAll attenuation states ATTNIN, ATTNOUT 1.0 GHz 23 dBm 2.0 GHz 22 dBm 4.0 GHz 19 dBm6.0 GHz 17 dBm RELATIVE PHASE 1.0 GHz 6 Degrees 2.0 GHz 18 Degrees 4.0 GHz 38 Degrees6.0 GHz 58 Degrees SWITCHING CHARACTERISTICSt RISE , t FALL 10%/90% RF output60 ns t ON , t OFF50% CTL to 10%/90% RF output 150 ns Settling Time 50% CTL to 0.05 dB final RF output 250 ns50% CTL to 0.10 dB final RF output 200 ns INPUT LINEARITYAll attenuation states, 0.2 GHz to 6 GHz 0.1 dB Compression (P0.1dB) 30 dBm 1 dB Compression (P1dB)31 dBm Input Third-Order Intercept (IP3) Two-tone input power = 16 dBm/tone, ∆f = 1 MHz 54 dBm SUPPLY CURRENT (I DD ) V DD = 3.3 V 0.3 mAV DD = 5.0 V 0.6 mA CONTROL VOLTAGE THRESHOLD <1 µA typical Low V DD = 3.3 V 0 0.5 VV DD = 5.0 V 0 0.8 V High V DD = 3.3 V 2.0 3.3 VV DD = 5.0 V 3.5 5.0 V RECOMMENDED OPERATING CONDITIONS Supply Voltage Range (V DD )3.0 5.4 V Digital Control Voltage Range For P/S, CLK, SERNIN, LE, D0 to D6 pins 0 V DD V RF Input PowerAll attenuation states, T CASE = 85°C 24 dBm Case Temperature (T CASE )−40+85°CHMC1119 Data SheetTIMING SPECIFICATIONSSee Figure 23 and Figure 24 for the timing diagrams.Table 2.Parameter Description Min Typ Max Unitt SCK Minimum serial period, see Figure 23 70 nst CS Control setup time, see Figure 23 15 nst CH Control hold time, see Figure 23 20 nst LN LE setup time, see Figure 23 15 nst LEW Minimum LE pulse width, see Figure 24 10 nst LES Minimum LE pulse spacing, see Figure 23 630 nst CKN Serial clock hold time from LE, see Figure 23 0 nst PH Hold time, see Figure 24 10 nst PS Setup time, see Figure 24 2 nsRev. C | Page 4 of 15Data SheetHMC1119Rev. C | Page 5 of 15ABSOLUTE MAXIMUM RATINGSTable 3.ParameterRating RF Input Power (T CASE = 85°C) 25 dBmDigital Control Inputs (P/S, CLK, SERNIN, LE, D0 to D6) −0.3 V to V DD + 0.5 V Supply Voltage (V DD )−0.3 V to +5.5 V Continuous Power Dissipation (P DISS ) 0.31 W Thermal Resistance (at Maximum Power Dissipation) 156°C/WTemperatureChannel Temperature 135°CStorage−65°C to +150°C Maximum Reflow Temperature 260°C (MSL3 Rating) ESD Sensitivity (HBM)2 kV (Class 2)Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.ESD CAUTIONHMC1119Data SheetRev. C | Page 6 of 15PIN CONFIGURATION AND FUNCTION DESCRIPTIONSV SERNIN NOTES1. THE EXPOSED PAD AND GND PINS MUST BE CONNECTED TO RF DC GROUND.CLK LE GND ATTNOUT GNDG N G N G N G N G N G N D 6D 5D 4D 3D 2D 112962-002Figure 2. Pin ConfigurationTable 4. Pin Function DescriptionsPin No. Mnemonic Description1, 19 to 24 D0, D6 to D1 Parallel Control Voltage Inputs. These pins attain the required attenuation (see Table 6). There is no internal pull-up or pull-down on these pins; therefore, these pins must always be kept at a valid logic level (V IH or V IL ) and must not be left floating. 2 V DD Supply Voltage Pin.3P/S Parallel/Serial Control Input. There is no internal pull-up or pull-down on this pin; therefore, this pin must always be kept at a valid logic level (V IH or V IL ) and must not be left floating. For parallel mode, set Pin 3 to low; for serial mode, set Pin 3 to high.4, 6 to 13, 15 GND Ground. The package bottom has an exposed metal pad that must connect to the printed circuit board (PCB) RF/dc ground. See Figure 4 for the GND interface schematic.5 ATTNIN Attenuator Input. This pin is dc-coupled and matched to 50 Ω. A blocking capacitor is required. Select the value of the capacitor based on the lowest frequency of operation. See Figure 5.14 ATTNOUT Attenuator Output. This pin is dc-coupled and matched to 50 Ω.A blocking capacitor is required. Select the value of the capacitor based on the lowest frequency of operation. See Figure 5.16 LE Serial/Parallel Interface Latch Enable Input. There is no internal pull-up or pull-down on this pin; therefore, this pin must always be kept at a valid logic level (V IH or V IL ) and must not be left floating. See the Theory of Operation section for more information.17 CLK Serial Interface Clock Input. There is no internal pull-up or pull-down on this pin; therefore, this pin must always be kept at a valid logic level (V IH or V IL ) and must not be left floating. See the Theory of Operation section for more information.18 SERNIN Serial interface Data Input. There is no internal pull-up or pull-down on this pin; therefore, this pin must always be kept at a valid logic level (V IH or V IL ) and must not be left floating. See the Theory of Operation section for more information.EPADExposed Pad. The exposed pad must be connected to RF/dc ground.Data SheetHMC1119Rev. C | Page 7 of 15INTERFACE SCHEMATICSD0TO D512962-021Figure 3. D0 to D6 Interface12962-022Figure 4. GND Interface12962-023Figure 5. ATTIN and ATTOUT InterfaceV 12962-024Figure 6. P/S, LE, CLK, and SERNIN InterfaceHMC1119Data SheetRev. C | Page 8 of 15TYPICAL PERFORMANCE CHARACTERISTICSINSERTION LOSS, RETURN LOSS, STATE ERROR, STEP ERROR, AND RELATIVE PHASE–4–3–2–1I N S E R T I O N L O S S (d B )FREQUENCY (GHz)12962-003Figure 7. Insertion Loss vs. Frequency at Various TemperaturesFREQUENCY (GHz)–50–40–30–20–100I N P U T R E T U R N L O S S (d B)12962-004Figure 8. Input Return Loss (Major States Only)–2.0–1.6–1.2–0.8–0.400.40.81.21.62.0043281216202428S T A T E E R R O R (d B )ATTENUATION STATE (dB)12962-007Figure 9. State Error vs. Attentuation State, 0.1 GHz to 0.5 GHzFREQUENCY (GHz)–35–30–25–20–15–10–50N O R M A L I Z E D A T T E N U A T I O N (d B )12962-005Figure 10. Normalized Attenuation (Major States Only)FREQUENCY (GHz)–60–50–40–30–20–10O U T P U T R E T U R N L O S S (d B )12962-006Figure 11. Output Return Loss (Major States Only)–1–0.8–0.6–0.4–0.200.20.40.60.81S T A T E E R R O R (d B )043281216202428ATTENUATION STATE (dB)12962-009Figure 12. State Error vs. Attentuation State, 1 GHz to 6 GHzData SheetHMC1119Rev. C | Page 9 of 15–2.0–1.5–1.0–0.500.51.01.52.0S T A T E E R R O R (d B )FREQUENCY (GHz)12962-008Figure 13. State Error vs. Frequency, Major States Only–60–40–20020406080R E L A T I V E P H A S E (d e g )FREQUENCY (GHz)12962-011Figure 14. Relative Phase vs. Frequency, Major States Only–1.0–0.8–0.6–0.4–0.200.20.40.60.81.0S T E P E R R O R (d B )FREQUENCY (GHz)12962-010Figure 15. Step Error vs. Frequency, Major States OnlyHMC1119Data SheetRev. C | Page 10 of 15INPUT POWER COMPRESSION AND THIRD-ORDER INTERCEPT152025303540P 1d B(d B m )FREQUENCY (GHz)12962-012Figure 16. P1dB vs. Frequency at Various Temperatures, MinimumAttentuation State, 0.05 GHz to 1 GHz152025303540P 0.1d B(d B m )FREQUENCY (GHz)12962-013Figure 17. P0.1dB vs. Frequency at Various Temperatures, MinimumAttentuation State, 0.05 GHz to 1 GHzFREQUENCY (GHz)3040506070I P 3(d B m )0.200.40.60.8 1.012962-014Figure 18. IP3 vs. Frequency at Various Temperatures, MinimumAttentuation State, 0.1 GHz to 1 GHz 152025303540P 1d B (dB m )FREQUENCY (GHz)12962-015Figure 19. P1dB vs. Frequency at Various Temperatures, MinimumAttentuation State, 0.05 GHz to 6 GHz152025303540P 0.1d B (dB m )FREQUENCY (GHz)12962-016Figure 20. P0.1dB vs. Frequency at Various Temperatures, MinimumAttentuation State, 0.05 GHz to 6 GHzFREQUENCY (GHz)3040506070I P 3(d B m )12962-017Figure 21. IP3 vs. Frequency at Various Temperatures, MinimumAttentuation State, 0.1 GHz to 6 GHzTHEORY OF OPERATIONThe HMC1119 incorporates a 7-bit fixed attenuator array that offers an attenuation range of 0.25 dB to 31.75 dB, with 0.25 dB steps. An integrated driver provides both serial and parallel mode control of the attenuator array (see Figure 22).The HMC1119 can be in either serial or parallel mode control by setting the P/S pin to high or low, respectively (see Table 5). The 7-bit data, loaded in either serial or parallel mode, then latches with the control signal, LE, to determine the attenuator value. Table 5. Mode Selection Table 1P/S Pin State Control Mode Low Parallel HighSerial1The P/S pin must always be kept at a valid logic level (V IH or V IL ) and must not be left floating.SERIAL CONTROL INTERFACEThe HMC1119 utilizes a 3-wire serial to parallel (SPI)configuration, as shown in the serial mode timing diagram (see Figure 23): serial data input (SERNIN), clock (CLK), and latch enable (LE). The serial control interface activates when the P/S pin is set to high.In serial mode, the 7-bit SERNIN data is clocked MSB first on rising CLK edges into the shift register; then, LE must betoggled high to latch the new attenuation state into the device. The LE must be set low to clock a set of 7-bit data into the shift register because CLK is masked to prevent the attenuator value from changing if LE is kept high.In serial mode operation, both the serial control inputs (LE, CLK, SERNIN) and the parallel control inputs (D0 to D6) must always be kept at a valid logic level (V IH or V IL ) and must not be left floating. It is recommended to connect the parallel control inputs to ground and to use pull-down resistors on all serial control input lines if the device driving these input lines goes high impedance during hibernation.RF INPUT OUTPUTThe attenuator in the HMC1119 is bidirectional; the ATTNIN and ATTNOUT pins are interchangeable as the RF input and output ports. The attenuator is internally matched to 50 Ω at both input and output; therefore, no external matching components are required. The RF pins are dc-coupled; therefore, dc blocking capacitors are required on RF lines.SERNIND0D1D2D3D4D5D6CLK P/S LERFOUTPUT12962-018Figure 22. Attenuator Array Functional Block DiagramTable 6. Truth TableDigital Control Input 1Attenuation State (dB) D6 D5 D4 D3 D2 D1D0 Low Low Low Low Low Low Low 0 (reference) Low Low Low Low Low Low High 0.25 Low Low Low Low Low High Low 0.5 Low Low Low Low High Low Low 1.0 Low Low Low High Low Low Low 2.0 Low Low High Low Low Low Low 4.0 Low High Low Low Low Low Low 8.0 High Low Low Low Low Low Low 16.0 HighHighHigh High HighHigh High 31.751Any combination of the control voltage input states shown in Table 6 provides an attenuation equal to the sum of the bits selected.12962-19 P/SSERNINCLKLEFigure 23. Serial Control Timing DiagramPARALLEL CONTROL INTERFACEThe parallel control interface has seven digital control input lines(D6 to D0) to set the attenuation value. D6 is the most significantbit (MSB) that selects the 16 dB attenuator stage, and D0 is theleast significant bit (LSB) that selects the 0.25 dB attenuator stage(see Figure 22).In parallel mode operation, both the serial control inputs (LE, CLK,SERNIN) and the parallel control inputs (D0 to D6) must always bekept at a valid logic level (V IH or V IL) and must not be left floating. Itis recommended to connect the serial control inputs to ground andto use pull-down resistors on all parallel control input lines ifthe device driving these input lines goes high impedance duringhibernation.Setting P/S to low enables parallel mode. There are two modes ofparallel operation: direct parallel mode and latched parallel mode.Direct Parallel ModeFor direct parallel mode, the latch enable (LE) pin must be kepthigh. Change the attenuation state using the control voltage inputs(D0 to D6) directly. This mode is ideal for manual control of theattenuator and using hardware, switches, or a jumper.Latched Parallel ModeThe latch enable (LE) pin must be low when changing thecontrol voltage inputs (D0 to D6) to set the attenuation state.When the desired state is set, LE must be toggled high to transferthe 7-bit data to the bypass switches of the attenuator array, thentoggled low to latch the change into the device (see Figure 24).LED6TO D0P/S12962-2Figure 24. Latched Parallel Mode Timing DiagramPOWER-UP SEQUENCEThe ideal power-up sequence is as follows:1.Power up GND.2.Power up V DD.3.Power up the digital control inputs (the relative order ofthe digital control inputs is not important).4.Power up the RF input.For latched parallel mode operation, LE must be toggled. Therelative order of the digital inputs is not important as long as theinputs are powered up after GND and V DD.Power-Up StatesThe logic state of the device is at maximum attenuation when, atpower up, LE is set to low. The attenuator latches in the desiredpower-up state approximately 200 ms after power up.APPLICATIONS INFORMATIONEVALUATION PRINTED CIRCUIT BOARDThe schematic of the evaluation board, EV2HMC1119LP4M , is shown in Figure 25. The PCB is four-layer material with a copper thickness of 0.7 mils on each layer. Each copper layer is separated with a dielectric material. The top dielectric material is 10-mil RO4350 with a typical dielectric constant of 3.48. The middle and bottom dielectric materials are FR-4 material, used for mechanical strength and to meet the overall board thickness of approximately 62 mils, which allows SMA connectors to beAll RF and dc traces are routed on the top copper layer. The RF transmission lines are designed using coplanar waveguide model (CPWG) with a width of 18 mils, spacing of 17 mils, and dielectric thickness of 10 mils to maintain 50 Ω characteristic impedance. The inner and bottom layers are solid ground planes. For optimal electrical and thermal performance, an ample number of vias are populated around the transmission lines and under the package exposed pad. The evaluation board layout serves as a recommenda-tion for the optimal performance on both electrical and thermal aspects.12962-026Figure 25. EV2HMC1119LP4M Evaluation PCBTable 7. Bill of MaterialsItem Value 1 DescriptionManufacturer 2 J1, J2 PCB mount SMA connector J318-pin dc connectorTP1, TP2Through hole mount test point C1, C3 100 pF Capacitor, 0402 package C6 10 μF Capacitor, 0603 package C71000 pF Capacitor, 0402 package R1 to R11 0 Ω Resistor, 0402 package R12 to R25 100 kΩ Resistor, 0402 packageSW1, SW2 SPDT four-position DIP switchU1 HMC1119 digital attenuator Analog Devices, Inc.PCB 3600-01280-00-1 evaluation PCB EV2HMC1119LP4M 4 from Analog Devices1 Blank cells in the Value column indicate that there is no specific value recommendation for the listed component.2Blank cells in the Manufacturer column indicate that there is no specific manufacturer recommendation for the listed component. 3Circuit board material is Arlon 25FR. 4Reference this number when ordering the full evaluation PCB. See the Ordering Guide section.12962-027Figure 26. Applications CircuitPACKAGING AND ORDERING INFORMATIONOUTLINE DIMENSIONS0.50BSC0.500.400.30BOTTOM VIEWTOP VIEWSIDE VIEW4.104.00 SQ 3.900.950.850.750.05 MAX 0.02 NOM0.20 REFCOPLANARITY0.08PIN 1INDICATORFOR PROPER CONNECTION OF THE EXPOSED PAD, REFER TO THE PIN CONFIGURATION AND FUNCTION DESCRIPTIONSSECTION OF THIS DATA SHEET.12-08-2017-C0.300.250.180.20 MIN2.852.70 SQ 2.55EXPOSED PAD00SEATING PLANEDETAIL A (JEDEC 95)Figure 27. 24-Lead Lead Frame Chip Scale Package [LFCSP]4 mm × 4 mm Body and 0.85 mm Package Height(HCP-24-3)Dimensions shown in millimetersORDERING GUIDEModel 1Temperature Range MSL Rating 2 Package DescriptionPackage Option HMC1119LP4ME −40°C to +85°C MSL3 24-Lead Lead Frame Chip Scale Package [LFCSP] HCP-24-3 HMC1119LP4METR −40°C to +85°C MSL3 24-Lead Lead Frame Chip Scale Package [LFCSP] HCP-24-3 EV2HMC1119LP4MEvaluation Board1 All models are RoHS compliant.2See the Absolute Maximum Ratings section.©2016–2018 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D12962-0-4/18(C)。

SNC 系列(带LCD屏)中文说明书(User_Manual_SNC_CHS)

- 5 m v /℃/ 2 V

12V(12V); 24V/(24V)

11V(12V); 22/24V;

12.6V(12V), 25.2/(24V);

充 电 为P W M脉 宽 调 制

SNC20 20A 20A

SNC30 30A 30A

SNC40 40A 40A

以上规格,仅供参考,如有变动恕不另行通知

减 小 电压值,按 一 次减小0 .01 V

充电容量 (闪烁)

短按 SET

充电容量清零

环境温度单位 (闪烁)

华 氏度(F)和摄 氏度( ℃)循 环却换

产品规格

型号 额定充电电流 额定负载电流 系统电压 过载、短路保护 空载电流 过压保护 工作温度: 强充电压 均衡充电压 浮充电压 充电恢复电压 温度补偿 欠压电压 蓄电池低压保护 负载恢复工作电压 控制方式

2. 在设置状态时,参数会闪烁,当参数停止闪烁时候,用户设定的 参数会自动保存。

SET

开始

长 按5秒 SET

增加电 压 值,按一次 增 加0. 0 1 V

最高充电电压 (闪烁)

减 小 电压值,按 一 次减小0 .01 V

增加电 压 值,按一次 增 加0. 0 1V

短按 SET

低压截止电压 (闪烁)

短按 SET

安装方法

141.5 152.2

85.8 117.5

注意事项:

1. 建议把产品安装在室内,避免阳光直射,如果一定要安装在室外, 请做好防雨措施。

2. 建议用户把控制器和蓄电池装在同一个地方,以便控制器能随时 检测蓄电池的温度。调整充放电的参数。

3. 本控制器只适用于太阳能电池板。不能用于柴油发电、市电、风 力发电等充电控制,否则会导致控制器损坏。

11C90中文资料

VIL

Input LOW Voltage

0C mV

a 25 C a 75 C a 25 C a 25 C a 25 C a 25 C

IIH

Input HIGH Current CP Input (Note 1) MS Input M1 and M2 Input Input LOW Current Power Supply Current Operating Supply Voltage Range Reference Voltage 05

b 1060 b 1025 b 980 b 1820 b 1135 b 1095 b 1035 b 1870 b 1850 b 1830

Typ

b 995 b 960 b 910 b 1705

Max

b 905 b 880 b 805 b 1620 b 840 b 810 b 720 b 1500 b 1485 b 1460

b 110 b 119 b5 7 b 1550 b 75 b5 2

400 400 250

mA mA mA

IIL IEE VEE VREF

VIN e VILB Pins 6 7 13 not connected

Units mV

TA 0C

a 25 C a 75 C

Conditions Load e 50X to b2V

VOL VIH

mV

0 C to

a 75 C

0C mV

a 25 C a 75 C

Guaranteed Input HIGH Signal (Note 6) Guaranteed Input LOW Signal VIN e VIHA

元器件交易网

11C90 11C91 650 MHz Prescalers

VC11 + 过程信号源(PROSSE SOURCE)概要说明

OP 11C 功能简介

Meridian 1 Option 11C简介对于许多世界顶级公司来说,北电网络的Meridian 1意味着帮助决策人获得更多信息的能力,最重要的是,它提供了客户获得更为可靠、周到、专业化服务的机会。

如今,借助Option 11C这一先进的商业通信系统,即使是小型的商户或大公司的分支机构,亦可获得同样超凡的竞争优势。

Option 11C-Meridian 1 IP Enabled 小型用户交换机专门为中小型商户或大公司的分支机构设计,支持Meridian 1 家族全部功能,其高度的集成和精巧的设计可以使它方便地置于办公桌上或挂在办公室的墙上。

Option 11C 采用先进的32位微处理芯片,BHCC 值高达58,000 。

CPU 采用冗余设计,每一机柜均可放置CPU ,具有多种选择,配置灵活便利,便于集中管理。

可提供多点PSTN 接入,具有超强网络能力,可支持多达45 条数字中继。

可提供基于IP网络的连接方式以及基于IP的远端接入,充分利用公司现有的数据网络资源,实现语音和数据的一体化传输,特别适合高话务量的商业环境和一机多点的解决方案。

内置式集成电源,可直接连接220V交流或48V直流电源,功率容量考虑了备用电池的浮充;每个机柜都有独立的电源模块,提高了可靠性。

自然风冷和壁挂式设计,以及很宽的环境温湿度适应范围,保证了它可以适应任何的使用环境。

灵活的容量配置,可根据用户需求灵活配置机柜。

主机柜可通过光纤或100Mbps IP 网络接口连接至扩展机柜,若采用光纤连接,主机柜和扩展机柜之间的距离可达 3 公里之远,而采用IP 网络接口可将主机柜和扩展机柜接入IP 网络,充分利用现有的数据网络资源来实现话音和数据的一体化传输。

并且在扩展机柜上亦有维护管理接口,既为多点办公的用户节约了线路资源,同时又极大地方便了管理人员的维护操作。

由于扩展机柜均也可配备CPU,可靠性大大增加。

Option 11C 可自动监视主机柜与扩展机柜的连接,一旦连接终端,扩展机柜将独立运行,通话不受影响。

湖南万通汽修学校,三菱维修手册11C-1~35

36.99 45.0 0.03 —— 119.9-120.1 97.4 1.0 1.2 6.0 0.02-0.05 0.03-0.07 45°-45.5° 112.30 114.11

单位:毫米

限值 —— —— 37.00 36.49

0.2 * 0.2

≤99.4 0.5 0.7 —— 0.10 0.15 —— 111.80 113.61

0.5 0.35 0.35 0.3

11C-9

11C-10

发动机

新的拧紧方法-螺栓塑性区域拧紧法

一种新的拧紧方法-塑性区域拧紧法被用于发 动机的某些零件中。这些螺栓的拧紧方法不同于传统 的方法。

11C-6

形式 气缸数 燃烧室 总排量 缸径 行程 压缩比 气门定时

润滑系统 油泵形式 冷却系统 水泵形式

项目

进气门 排气门

发动机

概述

毫升 毫米 毫米

开 闭 开 闭

规范 4G64 S4 MPI 直列式 OHV,SOHC 4 屋脊形燃烧室 2351 86.5 100.0 9.0 上止点前 18° 下止点后 53° 下止点前 50° 上止点后 18° 压力供给,全流过滤 齿轮式 水冷强制循环 离心叶轮式

11C-1

11C 组

2.4 升电控发动机

目录

总则 ....................................................................................................................................................11C-1 发动机 ................................................................................................................................................11C-5

SHT10,SHT11,SHT15,SHT71,SHT75中文资料pdf[1]

![SHT10,SHT11,SHT15,SHT71,SHT75中文资料pdf[1]](https://img.taocdn.com/s3/m/98865afc700abb68a982fb80.png)

DATA(恢复高电平)。

命令代码

预留

0000x

温度测量

00011

湿度测量

00101

读状态寄存器

00111

写状态寄存器

00110

预留

0101x-1110x

软复位,复位接口、清空状态寄存

器, ,即清空为默认值

下一次命令前等待至少

14bit(温度)、12bit(湿

度),也可分别降至

12bit和

8bit。通常在高速或超

低功耗的应用中采用该功能。

2.3.2 电量不足

“电量不足”功能可监测到

Vdd电压低于

2.47V的

状态。精度为±0.05V。

2.3.3 加热元件

芯片上集成了一个可通断的加热元件。接通后,可将

(2) 0.04 0.01 0.01 °C

0.07 0.02 0.02 °F

12 14 14 Bit

重复性

±0.1 °C

±0.2 °F

精度(3)参见图 1

量程范围

-40 123.8 °C

-40 254.9 °F

响应时间

1/e (63%) 5 30 s

时序只复位串口,状态寄存器内容仍然保留。

DATA

SCK

Transmission Start

1 2 3 4 -8 9

表 2 SHTxx命令集

2.2.4 测量时序(RH 和 T)

发布一组测量命令(‘

00000101’表示相对湿度

RH,

‘00000011’表示温度

封装。特殊封装形式可根据用户需求而提供。

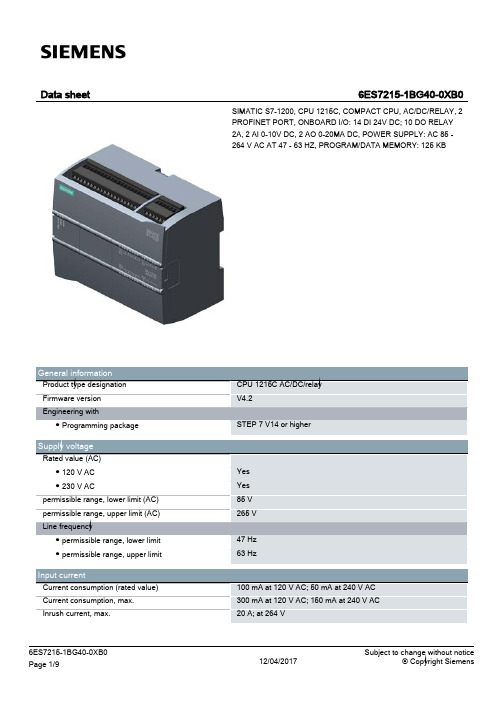

西门子SIMATIC S7-1200 CPU 1215C 产品数据表说明书

Yes Yes 85 V 265 V

47 Hz 63 Hz

100 mA at 120 V AC; 50 mA at 240 V AC 300 mA at 120 V AC; 150 mA at 240 V AC 20 A; at 264 V

12/04/2017

Subject to change without notice © Copyright Siemens

General information Product type designation Firmware version Engineering with ● Programming package

Supply voltage Rated value (AC) ● 120 V AC ● 230 V AC permissible range, lower limit (AC) permissible range, upper limit (AC) Line frequency ● permissible range, lower limit ● permissible range, upper limit

Yes

Single phase: 3 @ 100 kHz & 3 @ 30 kHz, differential: 3 @ 80 kHz & 3 @ 30 kHz

500 m; 50 m for technological functions 300 m; For technological functions: No

0.8 A²·s

1 600 mA; Max. 5 V DC for SM and CM

20.4 to 28.8V

14 W

125 kbyte No 4 Mbyte with SIMATIC memory card Yes Yes Yes

C 11 标准

C++11[编辑](重定向自C++0x)C++11,先前被称作C++0x,即ISO/IEC14882:2011,是C++编程语言的一个标准。

它取代第二版标准ISO/IEC14882:2003(第一版ISO/IEC14882:1998公开于1998年,第二版于2003年更新,分别通称C++98以及C++03,两者差异很小),且已被C++14取代。

相比于C++03,C++11标准包含核心语言的新机能,而且扩展C++标准程序库,并入了大部分的C++ Technical Report1程序库(数学的特殊函数除外)。

ISO/IEC JTC1/SC22/WG21C++标准委员会计划在2010年8月之前完成对最终委员会草案的投票,以及于2011年3月召开的标准会议完成国际标准的最终草案。

然而,WG21预期ISO将要花费六个月到一年的时间才能正式发布新的C++标准。

为了能够如期完成,委员会决定致力于直至2006年为止的提案,忽略新的提案[1]。

最终于2011年8月12日公布,并于2011年9月出版。

2012年2月28日的国际标准草案[1]是最接近于C++11标准的草案,差异仅有编辑上的修正。

像C++这样的编程语言,通过一种演化的的过程来发展其定义。

这个过程不可避免地将引发与现有代码的兼容问题,在C++的发展过程中偶尔会发生。

不过根据比雅尼·斯特劳斯特鲁普(C++的创始人并且是委员会的一员)表示,新的标准将几乎100%兼容于现有标准。

目录[隐藏]1候选变更2C++核心语言的扩充3核心语言的运行期表现强化3.1右值引用和move语义3.2泛化的常数表示式3.3对POD定义的修正4核心语言构造期表现的加强4.1外部模板5核心语言使用性的加强5.1初始化列表5.2统一的初始化5.3类型推导5.4以范围为基础的for循环5.5Lambda函数与表示式5.6回返类型后置的函数声明5.7对象构造的改良5.8显式虚函数重载5.9空指针5.10强类型枚举5.11角括号5.12显式类型转换子5.13模板的别名5.14无限制的unions6核心语言能力的提升6.1变长参数模板6.2新的字符串字面值6.3用户自定义的字面值6.4多任务内存模型6.5thread-local的存储期限6.6使用或禁用对象的默认函数6.7long long int类型6.8静态assertion6.9允许sizeof运算符作用在类的数据成员上,无须明确的对象6.10垃圾回收机制7C++标准程序库的变更7.1标准库组件上的升级7.2线程支持7.3多元组类型7.4散列表7.5正则表达式7.6通用智能指针7.7可扩展的随机数功能7.8包装引用7.9多态函数对象包装器7.10用于元编程的类型属性7.11用于计算函数对象回返类型的统一方法8已被移除或是不包含在C++11标准的特色9被移除或废弃的特色10编译器实现11关系项目12参考资料12.1C++标准委员会文件12.2文章13外部链接§候选变更[编辑]C++的修订包含核心语言以及标准程序库。

FPGA可编程逻辑器件芯片EP4CE115F29C8L中文规格书

Mode 0 (continuous frame mode) is popular for camera pipe operation. Often, the camera pipe is enabled statically, and updates to the coefficients are only required from time to time. On demand software may enable the configuration DMA in stop mode to trigger the fetch of one single BCL. In this mode, the PVP_IPFn_TAG register is useful to match status results with a respective configuration. The new BCL only updates coefficients of processing blocks. The BCL does not alter the pipe configuration.Mode 1 (back-to-back mode) is useful in camera pipe mode when coefficients have to change every N th frame. This mode supports on-the-fly reprogramming of coefficients, but it does not support on-the-fly reprogramming of pipe configurations. The following settings must not change unless the DRAIN bit is set:•Pipe structure (PVP_xxx_CFG registers)•Fundamental operating modes (such as 1st-derivative to 2nd-derivative mode of PEC)•Input format and OPORT configuration (PVP_IPFn_CTL registers)•Horizontal size of input frame (HCNT)If any of the above settings change on-the-fly, the PVP_IPFn_PIPECTL.DRAIN bit must be set for proper operation to use Mode 2. In memory pipe mode, the PVP_IPFn_PIPECTL.DRAIN bit causes of few clock cycles of overhead depending to pipeline depth. In camera pipe mode, the PVP_IPFn_PIPECTL.DRAIN bit causes the loss of an entire frame. Operation stops after the pipe has been drained and resumes with the next incoming VSYNC signal.Whenever the next PVP job stalls until the completion event of the data output DMA is flagged either as an interrupt or as a system trigger, setting the PVP_IPFn_PIPECTL.DRAIN bit is a requirement at the appli-cation level. The data output DMA work unit does not complete as long as related data sticks in the pipe. The data in the pipe does not progress until the configuration DMA and data source grant. Such deadlock situations can be avoided by using Mode 2. Once a deadlock occurs, it can be resolved by Mode 3 opera-tion.Mode 3 (drain now instruction) is more similar to a one-time instruction than an operating mode. This mode is used whenever software needs to respond to unpredictable events. For example, while the camera >01Mode 2: Auto-Completion ModeFCNT frames are requested by the IPFn, and these feed the pipe. The last datawords are automatically pushed out, and the operation automatically completes.If a new configuration is granted by DMA or by MMR writes, the configuration isapplied for the next FCNT set of frames.All processing blocks auto-disable. A new configuration must set all wanted STARTbits again.01Mode 3: Drain Now InstructionThis combination instructs the IPFn to flush all content out of the pipe.All processing blocks auto-disable. A new configuration must set all wanted STARTbits again.Table 30-47:Operating Modes by FCNT and DRAIN Selections (Continued)FCNT DRAINModeConfiguring with Daisy Chain MethodConfiguration and coefficient memory mapped registers (MMRs) of all processing blocks are double buff-ered. Whenever PVP_IPFn_FCNT is zero and the PVP_IPF0_CFG.START and PVP_IPF1_CFG.START bits =1, the values are copied from MMR registers into application buffers at the frame boundary. Due to the pipe-lined nature of the PVP, not all values are copied at the same time. Rather, the timing of value copying is closely related to how the VSYNC of the next frame progresses through the pipe. New settings apply to the first pixel of the new frame immediately after the last pixel of the old frame has been processed. The update command is daisy chained through the pipe, starting from the IPFn blocks through to the OPFn blocks. While sequencing through the daisy chain operation, hardware clears the PVP_xxx_CFG.START bits of all involved processing blocks in MMR space. Write conflicts can occur if software attempts to write the PVP_xxx_CFG registers during the daisy chain operation.The PVP_STAT register provides two status bits that report whether a daisy chain operation is ongoing in the camera pipes (PVP_STAT.CPDC ) or in the memory pipe (PVP_STAT.MPDC ). These bits are set along with the PVP_IPF0_CFG.START or PVP_IPF1_CFG.START bit and are cleared if the output formatters have been updated.In camera pipe mode, the PVP_STAT.CPDC bit is cleared only after the daisy chain progresses through the furthest of the enabled OPFn blocks. During this time, software should not write the PVP registers. If soft-ware mistakenly does write to these registers, the event is reported by the PVP_STAT.CPWRERR and PVP_STAT.MPWRERR flags. While all status bits in the PVP_STAT register are self clearing, the PVP_ILAT register latches the events until cleared by a software handshake.A PVP block which is enabled in either the camera pipe or memory pipe can be moved to the other pipe only after the drain done command is received for the former pipe. This restriction ensures that the PVP completely processes all the pixels in one pipe and disables the PVP block, before the PVP is enables the PVP block for pixel processing in the next pipe.NOTE :Camera pipes and memory pipes can be configured by MMR writes or BCL fetches. These are sepa-rate control mechanisms and are not intended to be mixed for a given pipe during ongoing opera-tion. Before switching from one method to the other, inspect the daisy chain and drain status bits in the PVP_STAT register to ensure no operation from the other method is pending.PMA5ACU7PEC2x HCNT + 11 if 2nd derivative mode with ZCRSS=0, otherwise 1xHCNT + 6IIMn6UDS varies with settingsTable 30-48:Block Latencies (Continued)PVP Block Latency [Data Clocks]P IPELINED V ISION P ROCESSOR (PVP)P ROGRAMMING M ODELto handle the three data flows, BCS, data IN, data OUT, and optionally status data OUT. If the descrip-tors are all completed by the core, multiple PVP memory pipe jobs can be chained without any further core intervention as the DMA operations run through the chained lists and handle the multiple dataflows autonomously. The following description assumes the memory pipe is inactive, (a non initialized state PVP_CTL.MPEN =0).To run a PVP memory pipe job from the PVP memory pipe job list, the PVP first loads the memorypipe configuration into the respective shadow registers of the respective PCP elements to build the PVP memory pipe. The configuration within the shadow register is activated (transferred from shadowregister to active register) using hardware triggers (staggered transfer). This configuration stream into the shadow registers is handled by DMA 45 which is controlled by a linked descriptor list. The last valid descriptor must contain a DMA_CFG.FLOW field =0 (STOP Mode) to gracefully stop the DMA 45 aftercompleting the PVP memory pipe job list and avoid loading non valid data into PVP memory pipeconfiguration register. All DMA_CFG descriptor fields within the linked list have DMA_CFG.FLOW =6 or =7 (descriptor list mode) or alternatively DMA_CFG.FLOW =4 (descriptor array mode).A 1-dimensional DMA operation is shown in the following figure. Note however, a 2-dimensionalDMA operation can also be used.Figure 30-55:Static Linked Descriptor List for Configuration Data (BCL Data)•Job List Global TriggerAfter the first initialization of the linked descriptor list the parameter registers of DMA 45 have to beinitialized, particularly the DMA_DSCPTR_NXT and DMA_CFG register. The DMA 45 is started but thenstalls until the PVP memory pipe is enabled and the PVP_IPFn_FCNT =0.To generate a unique synchronization signal that synchronizes the Data Out (DMA 42) and Data In(DMA 43) stream, all DMA_CFG descriptor fields of DMA 45 should have the bit field DMA_CFG.TRIG =1.This generates a trigger signal after a new configuration is loaded into the shadow registers.•Job List StartAfter setting up the three DMA linked lists, the memory pipe has to be activated (PVP_CTL.MPEN =1).。

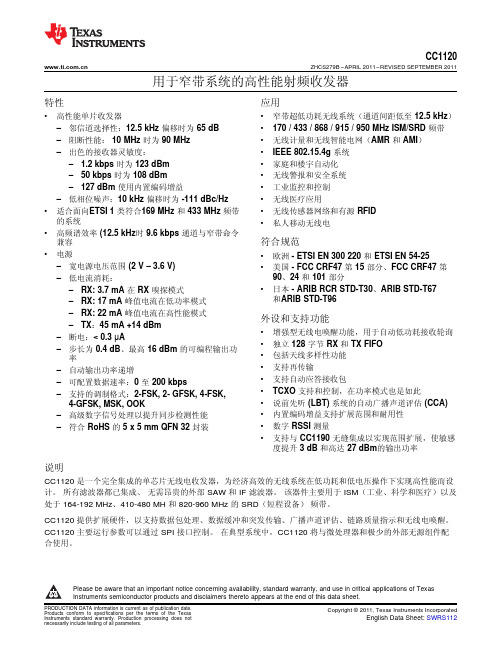

cc1120中文资料

Digital Input/Output

General purpose IO

Power

3 V VDD to internal digital regulator

Power

Digital regulator output to external C

Digital Input

Serial data in

• 增强型无线电唤醒功能,用于自动低功耗接收轮询 • 独立 128 字节 RX 和 TX FIFO • 包括天线多样性功能 • 支持再传输 • 支持自动应答接收包 • TCXO 支持和控制,在功率模式也是如此 • 说前先听 (LBT) 系统的自动广播声道评估 (CCA) • 内置编码增益支持扩展范围和耐用性 • 数字 RSSI 测量 • 支持与 CC1190 无缝集成以实现范围扩展,使敏感

• 适合面向ETSI 1 类符合169 MHz 和 433 MHz 频带 的系统

• 高频谱效率 (12.5 kHz时 9.6 kbps 通道与窄带命令 兼容

• 电源 – 宽电源电压范围 (2 V – 3.6 V) – 低电流消耗: – RX: 3.7 mA 在 RX 嗅探模式 – RX: 17 mA 峰值电流在低功率模式 – RX: 22 mA 峰值电流在高性能模式 – TX:45 mA +14 dBm – 断电:< 0.3 µA – 步长为 0.4 dB、最高 16 dBm 的可编程输出功 率 – 自动输出功率递增 – 可配置数据速率:0 至 200 kbps – 支持的调制格式:2-FSK, 2- GFSK, 4-FSK, 4-GFSK, MSK, OOK – 高级数字信号处理以提升同步检测性能 – 符合 RoHS 的 5 x 5 mm QFN 32 封装

Arista Networks C-110 产品说明书

HeadquartersSales 5453 Great Amer i ca Parkway Santa Clara, CA 95054 USA+ 1 408 547-5500+1408547-5501+ 1 866 Support +1408547-5502+ 1866 4 76-0000support-w ******************************© Copyright 2019 A rista Networks , Inc. The information contained here i n is subject to change without notice. Arista Networks and the Arista logo are trademarks of Arista Networks, Inc in the United States and other countries. Other product or serv i ce names may be trademarks or service marks of others .ContentsChapter 1. About This Guide (3)Chapter 2. Package Content (4)Chapter 3. C-110 Overview (5)Front Panel of C-110 (5)Rear Panel of C-110 (5)Chapter 4. Install the C-110 (7)Connect the C-110 to the Network (7)Connect the C-110 using PoE (8)Mount the C-110 (8)Power On the C-110 (9)Using the C-100 with Power Adapter (9)Chapter 5. C-110 Troubleshooting (10)Chapter 6. Appendix A: AP-Server Mutual Authentication (11)Chapter 1. About This GuideThis installation guide explains how to deploy the C-110 access point (AP).Important: Please read the EULA before installing C-110. You can download and read the EULA from https:// /en/support/product-documentation.Installing the AP constitutes your acceptance of the terms and conditions of the EULA mentioned above in this document.Intended AudienceThis guide can be referred by anyone who wants to install and configure the C-110 access point.Document OverviewThis guide contains the following chapters:•Package Content (page 4)•C-110 Overview (page 5)•Installing the C-110 (page 7)•C-110 Troubleshooting (page 10)Note: All instances of the term 'server' in this document refer to the Wireless Manager, unless the server name or type is explicitly stated.Product and Documentation UpdatesTo receive important news on product updates, please visit our website at https:///en/support/product-documentation. We continuously enhance our product documentation based on customer feedbackChapter 2. Package ContentThe C-110 package must contain the components shown in the figure below.Figure 1: C-110 Package ComponentsImportant: The MAC address of the device is printed on a label at the bottom of the product and the packaging box. Note down the MAC address, before mounting the device on the ceiling or at a location that is difficult to access. If the package is not complete, please contact the Arista Networks Technical Support Team at ***********************, or return the package to the vendor or dealer where you purchased the product.Chapter 3. C-110 OverviewC-110 is a 2x2 802.11a/b/g/n/ac access point.This chapter provides an overview of the C-110 and describes:•The Front Panel of the C-110 (page 5).•The Rear Panel of the C-110 (page 5).Front Panel of C-110The front panel of the C-110 has 5 functional LEDs that indicate the working of the device.Figure 2: C-110 Front Panel LEDsThe following table indicates the device states based on the LEDs.Table 1: C-110 LED Status DescriptionLED Status DescriptionPowerSolid Green Power ONOFF Power OFF5 GHzSolid Green No activity on 5 GHz radioBlinking Green Wireless activity on 5 GHz radio2.4 GHzSolid Green No activity on 2.4 GHz radioBlinking Green Wireless activity on 2.4 GHz radioRadio 3Blinking Green Activity on third radioLAN1/2Solid Green Wired Extension/VLAN Extension enabledRear Panel of C-110The rear panel of the C-110 provides an PoE Ethernet port that enables you to connect the device to a wired LAN through a switch or a hub and power the device by using the 802.3af standard.C-110 | 3 - C-110 Overview | 6Figure 3: C-110 Rear PanelPortDescription Connector Type Speed/Protocol Ethernet (LAN1/PoE)Gigabit Ethernet port used to connect to the wired LAN and communicate with the Arista cloud or server. This port can also be used to power the device using the 802.3af Power over Ethernet (PoE) standard.RJ45•10/100/1000 Mbps Gigabit Ethernet •802.3af Class 0 PoE •PoE input voltage: 48V Ethernet (LAN2)Gigabit Ethernet port that can be used for wired extension for an SSID.RJ4510/100/1000 Mbps Gigabit Ethernet Reset Pin HoleReset to factory default settings. To reset the device, press and hold the Reset Pin Hole for 10 sec until all LEDs go off which indicates that the device has rebooted. Pressing the Reset Pin Hole while the device is booting up will not have any effect.You should perform this operation only when the device is running.Pin hole push button Hold down and power cycle the device to reset DC IN Enables you to connect to and power on device using 12 V DC power with1.5 ampere. 6.3 mm barrel--When you reset the device, the following settings are reset:•Config shell password is reset to config .•Server discovery value is erased and changed to the default, (primary) and wifi-security-server (secondary).•All the VLAN configurations are lost.•If static IP is configured on the device, the IP address is erased and DHCP mode is set. The factory default IP address ofthe device is 169.254.11.74.Chapter 4. Install the C-110This chapter contains the stepwise procedure to install the C-110 device.Zero-Configuration of C-110 as Access PointZero-configuration is supported under the following conditions:•The device is in AP mode with background scanning on and no SSID configured.• A DNS entry wifi-security-server is set up on all the DNS servers. This entry should point to the IP address of the server.By default, the device looks for the DNS entry wifi-security-server.•The device is placed on a subnet that is DHCP enabled.Important: If the device is placed on a network segment that is separated from the server by a firewall, you must first open port 3851 for User Datagram Protocol (UDP) and Transport Control Protocol (TCP) bidirectional traffic on that firewall. This port number is assigned to Arista Networks. If multiple devices are set up to connect to multiple servers, zero-configuration is not possible. In this case, you must manually configure the APs. See the Access Point Configuration Guide on our website at https:///en/support/product-documentation .Take a configured C-110, that is, ensure that a static IP is assigned to the device or the settings have been changed for DHCP. Note down the MAC address and the IP address of the device in a safe place before it is installed in a hard-to-reach location. The MAC address of the device is printed on a label at the bottom of the product.The steps to install the device with no configuration (zero-configuration) are as follows:1.Mount the device. (page 8)2.Power On the device. (page 9)3.Connect device to the network. (page 7)Connect the C-110 to the NetworkTo connect C-110 to the network, perform the following steps:1.Ensure that a DHCP server is available on the network to enable network configuration of the C-110.2.Add the DNS entry wifi-security-server on all DNS servers. This entry should point to the IP address of the server.3.Ensure that DHCP is running on the subnet to which the device will be connected.4.Check the status LEDs on the device. If all LEDs glow green, then the device is operational and connected to the server.5.Log on to the server using ssh and run the get sensor list command.You will see a list of all Arista devices that are recognized by the server. Single Sign-On users can go to the Devices tab in Wireless Manager and check whether the device is visible under the Devices tab.The device is connected and ready to go operational.Note: If the zero configuration is not successful, the device must be configured manually.Important: If DHCP is not enabled on a subnet, the device cannot connect to that subnet with zero-configuration. If the DNS entry is not present on the DNS servers or if you do not have the DHCP serverrunning on the subnet, you must manually configure the device. See the Access Point Configuration guide onour website at https:///en/support/product-documentation .C-110 | 4 - Install the C-110 | 8Connect the C-110 using PoEIf you are using a PoE injector, make sure the data connection is plugged into a suitable switch port with proper network connectivity.Mount the C-110The C-110 mounting procedure can be divided into two parts:1.Affix the bracket to the T -grid: Use the mounting bracket to install the C-110 on the ceiling. Fix the bracket to the T-grid and rotate the bracket so that it snaps on the T-grid. The bracket is now parallel to an arm of the T-grid. Ensure that the bracket is properly snapped to the T-grid. Refer to the images given below.2.Mounting C-110 on the bracket: Place the first mounting post on the rear-side of the device on to the lower notch of thebracket. Rotate the device such that the center mounting post fits in to the center notch on the bracket. Ensure that all the mounting posts on the rear-side of the device are snapped in to the respective notches on the bracket. The mounting posts on the rear-side of the device are now properly fit in the respective notches of the bracket and device is mounted properly.Mounting Instructions using the Silhouette/Interlude Bracket Mount: The Silhouette/Interlude mounting bracket is not a part of the standard package and must be procured separately. The mounting instructions for the Silhouette/ Interlude Bracket Mount are similar to the Standard Package Content's mounting instructions.C-110 | 4 - Install the C-110 | 9 Note: You should label the devices using MAC addresses or at least your own convention. For example, use serial numbers, so that you can easily identify the devices.Power On the C-110The C-110 device can be powered on by plugging one end of the Ethernet cable into the PoE (802.3af) switch or injector andthe other end into the Ethernet/PoE port on the C-110. Ensure the PoE source you are using is turned ON.As an alternative to PoE, you can insert a compatible power adaptor plug into an AC power outlet and the other end into the power input port on the C-110.Note: If you are not using PoE, ensure that you use only an AC power adaptor supported by the C-110 access point (AP).Using the C-100 with Power AdapterTo power up the device with power adapter, perform the following steps:1.Plug the power cable into the DC power receptacle at the rear of the device.2.Plug the other end of the power cable into an 110V~240V 50/60 Hz AC power source.3.Wait until the device is ready. Refer to the LED details table.Chapter 5. C-110 TroubleshootingThe table below lists some of the troubleshooting guidelines for C-110.Diagnosis SolutionThe device did not receive a valid IP address via the DHCP.Ensure that the DHCP server is on and available on the VLAN/subnetto which the device is connected. If the device still fails to get a valid IPaddress, you can reboot it to see if the problem is resolved.The Ethernet cable is loose. The device is probably disconnected from theEnsure that the Ethernet cable is connected.network.Unable to connect to the server Ensure that the server is running and is reachable from the network to whichthe device is attached. If there is a firewall or a router with ACLs enabledbetween the device and the server, ensure that the traffic is allowed onUDP port 3851. Use the server IP-based discovery and ensure that youhave correctly entered the DNS name, wifi-security-server , on the DNSserver. Also, ensure that the DNS server IP addresses are either correctlyconfigured on the, or are provided by the DHCP server. It is also possiblethat the AP is unable to connect to the server because it has failed toauthenticate with the server. In this case, an 'Authentication failed for ' eventis raised on the server. Refer to the event for recommended action.The AP has encountered a problem.If you are using Arista Cloud Services, then open the TCP port 443 (SSL).If you have an on-premises installation, then open the ports UDP 3851 andport 80. If you are using a Proxy, Web Accelerator or URL Content Filter inbetween the AP and the Internet, ensure the settings allow communicationbetween the AP and Arista Cloud Services. If your configuration requiresyou to specify an exact IP address or IP range for Arista Cloud Services,************************************.Chapter 6. Appendix A: AP-Server Mutual AuthenticationThe AP-server communication begins with a mutual authentication step in which the AP and server authenticate each other using a shared secret. The AP-server communication takes place only if this authentication succeeds.After the authentication succeeds, a session key is generated. All communication between the AP and server from this point on is encrypted using the session key.The AP and server are shipped with the same default value of the shared secret. The CLI commands are provided on both server and AP for changing the shared secret.Note: After the shared secret (communication key) is changed on the server, all APs connected to the server will automatically be set up to use the new communication key. APs that are not connected to the server at this time must be manually set up with the same communication key to enable communication with this server.Note: Although the server is backward compatible, that is, older version APs can connect to a newer version server, this is not recommended.。

中微半导体CMS89F11x MCU用户手册V1.3说明书

CMS89F11x用户手册AD型MCUV1.3请注意以下有关CMS知识产权政策*中微半导体公司已申请了专利,享有绝对的合法权益。

与中微半导体公司MCU或其他产品有关的专利权并未被同意授权使用,任何经由不当手段侵害中微半导体公司专利权的公司、组织或个人,中微半导体公司将采取一切可能的法律行动,遏止侵权者不当的侵权行为,并追讨中微半导体公司因侵权行为所受的损失、或侵权者所得的不法利益。

*中微半导体公司的名称和标识都是中微半导体公司的注册商标。

*中微半导体公司保留对规格书中产品在可靠性、功能和设计方面的改进作进一步说明的权利。

然而中微半导体公司对于规格内容的使用不负责任。

文中提到的应用其目的仅仅是用来做说明,中微半导体公司不保证和不表示这些应用没有更深入的修改就能适用,也不推荐它的产品使用在会由于故障或其它原因可能会对人身造成危害的地方。

中微半导体公司的产品不授权适用于救生、维生器件或系统中作为关键器件。

中微半导体公司拥有不事先通知而修改产品的权利,对于最新的信息,请参考我们的网站目录使用注意事项 (1)1.产品概述 (2)1.1功能特性 (2)1.2系统结构框图 (3)1.3管脚分布 (4)1.4管脚描述 (6)1.5系统配置寄存器 (7)1.6在线串行编程 (8)2.中央处理器(CPU) (9)2.1内存 (9)2.1.1程序内存 (9)2.1.2数据存储器 (14)2.2寻址方式 (16)2.2.1直接寻址 (16)2.2.2立即寻址 (16)2.2.3间接寻址 (16)2.3堆栈 (18)2.4工作寄存器(ACC) (19)2.4.1概述 (19)2.4.2ACC应用 (19)2.5程序状态寄存器(STATUS) (20)2.6预分频器(OPTION_REG) (21)2.7程序计数器(PC) (23)2.8看门狗计数器(WDT) (24)2.8.1WDT周期 (24)3.系统时钟 (25)3.1概述 (25)3.2系统振荡器 (26)3.2.1内部RC振荡 (26)3.2.2外部XT振荡 (26)3.3起振时间 (26)4.复位 (27)4.1上电复位 (27)4.2掉电复位 (28)4.2.1掉电复位的改进办法 (29)4.3看门狗复位 (29)5.1休眠模式 (30)5.1.1休眠模式应用举例 (30)5.1.2休眠模式的唤醒 (31)5.1.3休眠模式唤醒时间 (31)6.I/O端口 (32)6.1I/O口结构图 (33)6.2I/O口模式及上、下拉电阻 (34)6.2.1P0口 (34)6.2.2P1口 (36)6.2.3P2口 (38)6.2.4写I/O口 (39)6.2.5读I/O口 (39)6.3I/O口使用注意事项 (40)7.中断 (41)7.1中断概述 (41)7.2中断控制寄存器 (42)7.3中断请求寄存器 (43)7.4总中断使能控制寄存器 (44)7.5中断现场的保护方法 (45)7.6外部中断 (46)7.6.1外部中断控制寄存器 (46)7.6.2外部中断0 (47)7.6.3外部中断1 (48)7.6.4外部中断2 (48)7.6.5外部中断的响应时间 (48)7.6.6外部中断的应用注意事项 (48)7.7P0电平变化中断 (49)7.8内部定时中断 (50)7.8.1TMR1中断 (50)7.8.2TMR2中断 (51)7.9ADC中断 (52)7.10中断的优先级,及多中断嵌套 (54)8.定时计数器TMR0 (56)8.1定时计数器TMR0概述 (56)8.2与TMR0相关寄存器 (58)8.3使用外部时钟作为TMR0的时钟源 (59)8.4TMR0做定时器的应用 (60)8.4.1TMR0的基本时间常数 (60)8.4.2TMR0操作流程 (60)9.1TMR1概述 (61)9.2TMR1相关寄存器 (62)9.3TMR1的时间常数 (63)9.3.1TMR1基本时间参数 (63)9.4TMR1的应用 (63)9.4.1TMR1作定时器使用 (63)9.4.2TMR1作计数器使用 (64)10.定时计数器TMR2 (65)10.1TMR2概述 (65)10.2TMR2相关的寄存器 (67)10.3TMR2的时间常数 (68)10.3.1TMR2基本时间参数 (68)10.3.2T2DATA初值计算方法 (68)10.4TMR2应用 (69)10.5T2OUT输出 (70)10.5.1T2OUT的周期 (70)10.5.2T2OUT基本时间参数 (70)10.5.3T2OUT应用 (70)11.模数转换(ADC) (71)11.1ADC概述 (71)11.2与ADC相关寄存器 (72)11.3内部电压基准 (74)11.4ADC应用 (75)11.4.1用查询模式做AD转换流程 (75)11.4.2AD中断模式流程 (76)12.LCD驱动模块 (78)12.1LCD功能使能 (78)12.2LCD相关设置 (78)13.内置比较器 (79)13.1内置比较器概述 (79)13.2与比较器相关的寄存器 (80)13.3比较器0应用 (81)13.4比较器1应用 (82)14.数据EEPROM控制 (83)14.1数据EEPROM概述 (83)14.2相关寄存器 (84)14.2.1EEADR寄存器 (84)14.2.2EECON1和EECON2寄存器 (84)14.3读数据EEPROM存储器 (86)14.4写数据EEPROM存储器 (87)14.5数据EEPROM操作注意事项 (88)14.5.1写校验 (88)14.5.2避免误写的保护 (88)15.8位PWM(PWM0) (89)15.18位PWM概述 (89)15.2与8位PWM相关寄存器 (90)15.38位PWM的周期 (91)15.3.18位PWM调制周期 (91)15.3.28位PWM输出周期 (91)15.48位PWM占空比算法 (92)15.4.16+2模式PWM占空比 (92)15.4.27+1模式PWM占空比 (93)15.58位PWM应用 (93)16.10位PWM(PWM1) (94)16.110位PWM概述 (94)16.2与10位PWM相关寄存器 (95)16.310位PWM调制周期 (96)16.3.110位PWM调制周期 (96)16.3.210位PWM输出周期 (96)16.410位PWM占空比算法 (97)16.510位PWM应用 (98)17.高频时钟(CLO)输出 (99)17.1高频时钟(CLO)输出概述 (99)17.2高频时钟(CLO)输出波形 (99)17.3高频时钟(CLO)应用 (100)18.蜂鸣器输出(BUZZER) (101)18.1BUZZER概述 (101)18.2与BUZZER相关的寄存器 (102)18.3BUZZER输出频率 (103)18.3.1BUZZER输出频率计算方法 (103)18.3.2BUZZER输出频率表 (103)18.4BUZZER应用 (103)19.电气参数 (104)19.1DC特性 (104)19.2AC特性 (105)20.指令 (106)20.1指令一览表 (106)20.2指令说明 (108)21.封装 (124)21.1SOP8 (124)21.2SOP14 (125)21.3SOP16 (126)21.4DIP20 (127)21.5SOP20 (128)22.版本修订说明 (129)使用注意事项振荡方式选择外部XT振荡时,P2.2口只能作为输入口;选择内部RC振荡时P2.2口可作为普通IO口。

CC1110 无线部分中文参考手册

CC1110无线部分中文参考手册版本:V1.002009年3月23日·andyla·ZigBee&IAR学习小组无线CC1110Fx/CC1111Fx的简化结构图如上Figure47.低中频(10w-IF)接收是CC1110的特性之一。

CC1110'收到的RF信号被低噪声放大器(LNA)放大,并且将收到的同相信号和正交相位信号(1/Q)降频转换为中频(IF)信号。

过滤掉残余在中频(2MHz)信号中的1/Q信号后,放大中频信号。

在中频信号中通过ADC数字化、自动增益控制,以及精细信道的过滤、解调字节和包同步(byte synchronization)等,所有这些都通过数字逻辑完成。

CC1110的发射端基于RF频率直接合成。

频率合成器包括一套完整的片上电感器电容器(LC)、电压控制振荡器(VCO)和一个90度移相器,用来产生同相信号、正交相位信号(I/Q)和本地振荡器(LO)信号给接收端的降频合成器。

26M的晶振作为频率合成器产生参考频率,同时为ADC和数字部分提供时钟脉冲。

一个特殊寄存器作为CPU访问的数据缓冲区。

配置和状态寄存器统一映射到外部XDATA区的寄存器进行访问。

数字基频包括频带配置支持,数据包处理和数据缓冲。

一个片上电压管理器用来调节传递1.8V的供电电压.15.1CPU使用了一系列选通命令来控制CC1110的无线操作。

选通命令可以看成是单字节指令,每条命令用来控制某个无线模块的功能。

这些命令可以实现使能频率合成器、使能接收模式、使能发送模式,以及其他功能。

图33简化状态表及典型用法和电流消耗上图33中展示了一个简化状态表及典型用法和电流消耗。

该表表明了在选通控制命令下的状态转换。

想看完整的状态转换机图可参考15.12节图中命令简介:FSTXON:快速TX准备TX_OFF_MODE:发送完数据时下一步选择做什么RX_OFF_MODE:接收到数据后下一步选择做什么选通命令通过写RFST寄存器发出。

HR11C Mic Processor业务描述说明书

7/02

HR11C

Mic Processor

OWNERS MANUAL

Introduction

The HR11C Mic Processor is a microphone and line level preamp for individual control of a signal before a main mixing console or as a single channel in a distributes system or even as part of a single channel P.A.. Parameters under control are high/low impedance, phantom power, compression/limiting, anti feedback notch filter, 10 band ISO equalizer and level control. It also includes a signal present, overload, and power LED’s. Switches on the rear are for XLR phantom power and MIC/line in/out. It is powered by a 12 VAC adapter, which contributes to its low noise level.

Using the HR11C

Compressor After plugging the signal source into the input jack, push the switch to the right of the compressor knob. The compressor is now engaged. With the knob at 0 dB it works as a limiter, supplying no gain reduction below its threshold. It has a soft “knee” as is hardly noticeable when engaged. As you rotate the knob toward 10 dB there is more gain for helping maintain a more constant output level as the input signal is varied.

NESC 概述 (NESC_overview.pdf)说明书

Updated and published every five years by The Institute of Electrical and Electronics Engineers (IEEE) and approved by the American National Standards Institute (ANSI), the NESC has been in continuous use since the first edition was issued in 1915. 2The current edition of the NESC is available in digital, printed, and mobile-app formats and is structured with initial sections covering scope, purpose, and grounding methods, followed by four main parts that contain specific rules for electric supply stations, overhead lines, underground lines and safety-related work practices. A companion document–the NESC Handbook–is also available and provides users with insights and commentary on the rules and how to apply them from the experts who helped develop the Code.From a code enforcement perspective, the NESC differs substantially from the National Fire Protection Association’s National Electrical Code ® (NEC ®) rules that apply to the premises wiring in residential, commercial, and industrial structures. The NESC is primarily applied by the nation’s electric and communications utilities and may be adopted by state regulatory commissions for investor-owned utilities. The NEC primarily applies to installations of nonutility electrical equipment, such as in-building wiring. The NEC code is enforced largely by local building and electrical inspectors, who are tasked with approving building electrical systems.T H E N E S CTHE NESC EMBODIES THE BASIC STANDARDS REQUIRED FOR THE SAFE INSTALLATION, OPERATION, AND MAINTENANCE OF POWER AND COMMUNICATIONS UTILITY SYSTEMS.As the definitive safety standard for more than a century,the National Electrical Safety Code continues to be the go-to resource for utility companies of all sizes and ownership structures. Within the utility environment, the NESC is usedby individuals in a myriad of roles–business leadership, operations management, engineering and line design, crew supervisors, and safety trainers to name just a few.The service utilities that depend on the National Electrical Safety Code are also diverse, and include providers of power, telecommunications, cable TV, wireless, and internet service, as well as transportation providers such as railroads that look to the NESC for guidance on their railway power and signaling systems. Beyond utilities, there is a broad ecosystem of companies that are key users of the NESC. These stakeholders include the manufacturers of electrical equipment and associated product testing agencies, the consultants and contractors that assist in the design and construction of utility lines and infrastructure,as well as the state and federal regulatory agencies that provide industry oversight. The NESC is focused on the end-to-end safety of utility systems from their point of origin (such as a power generating plantor communications central office), across transmission and distribution facilities, and ending at the service point(or communications network interface unit), which actsto separate the supply side (or network side) coming fromthe utility, to the premises side where the service is finally utilized by the end-user.The requirements within the NESC directly influence the capital cost of new utility facilities, as well as guide how and when maintenance is performed. As a further reflection ofits influence, the NESC is often used as a basis for the OSHA rules that govern the construction and maintenance of power supply and communications facilities, as well as the joint-use of structures, rights-of-way, and other facilities.Although the National Electrical Safety Code is published as a voluntary standard in the United States, it is typically adopted into law by individual state legislatures and public utility commissions and at the federal level for all cooperatives financed by the Rural Utilities Service (USDA). Outside ofthe U.S., the NESC is also used as an authoritative referencein more than 100 countries around the world.3NESC VALUEV A L U E46C O N S E N S U S NESC INVOLVEMENT The NESC is a consensus standard that depends on the involvement of motivated volunteers to provide the industry with accurate and impactful guidance. The NESC code-making process is well defined and clearly structured, with guiding principles that help ensure the inclusion of all viewpoints during an open and fair process for reaching agreement and anizationally, the NESC has a central oversight Main Committee made up of awell-balanced representation of member organizations, along with seven standing technical subcommittees which are maintained to provide recommended revisions to NESC rules for the Main Committee.The technical subcommittees meet to create change proposals, consider change proposals submitted by others, and are empowered to establish Working Groups and Task Forces to conduct in-depth research on specific technical topics and issues.The NESC’s core principles of inclusion and openness also extend to the public, with any interested party being able to submit their ideas for a new rule or modification of an existing rule. In addition to actively soliciting input from all NESC members, an open comment period is built into each revision cycle to help ensure the broadest possible set of perspectives.SHAPING THE FUTURE T hese are very exciting times in the industry, with unprecedented levels of technological change presenting huge opportunities as well as challenges for all participants. As an NESC member, you can play a hands-on role in helping to decide what the Code needs to be–both now and into the future.If this sounds intriguing and you are up for a challenge at the cutting edge of our industry, please visit ieeesa.io/nesc. We look forward to hearing from you.SUBCOMMITTEE PRIMARY RESPONSIBILITY SECTION/PART 1Scope, Purpose, Definitions & Coordination Sections 1, 2, and 32Grounding Methods Section 93Electric Supply Stations Part 14Overhead Line Clearances Part 2/Sections 20-235Overhead Line Strength and Loading Part 2/Sections 24-287Underground Lines Part 38Rules for Safeguarding Workers and the Public Part 4NESC PRODUCTS• NESC 2023 Edition• NESC 2023 Handbook• NESC 2023 eLearnings• NESC 2017 Edition• NESC 2017 Premier Edition Handbook• NESC 2017 Handbook Spanish Translation• NESC 2017 Handbook Chinese Translation• Mobile AppFor more details, links to purchase and subscribeto updates on the NESC, visit ieeesa.io/nescFor more information about organizationalaccess to the NESC, please contact**********************7RAISING THE WORLD’S STANDARDSConnect with us:Facebook: /ieeesaTwitter: @ieeesaLinkedIn: /company/ieee-sa-ieee-standards-association Instagram: /ieeesaYouTube: /ieeesa。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。