DS8913中文资料

891型测振仪使用说明书

国家级新产品891 型测振仪使用说明书中国地震局工程力学研究所中国·哈尔滨目录一.用途及特点二.技术指标三.原理四.使用方法五.仪器的成套性891 型测振仪一、用途及特点891型测振仪是701型测振仪的换代型。

它主要用于测量地面、结构物的脉动或工程振动。

每套测振仪包括891型拾振器六台(四台水平向、两台铅垂向)和891型六线放大器一台。

891型拾振器分为891-1、891-2和891-4三种型号,每种拾振器设有小速度、中速度、大速度和加速度四档。

放大器分891型和891-4型两种,它具有放大,积分,滤波和阻抗变换的功能,891型放大器配接891-1和891-2型拾振器,891-4型放大器配接891-4型拾振器。

用户可根据需要,选取拾振器上微型拨动开关及放大器上参数选择开关相应的档位,即可获取被测点的加速度、速度及位移参量。

本仪器具有体积小、重量轻、使用方便、动态范围大及一机多用的特点,且拾振器簧片不易损坏,不用调节零位。

本仪器可直接与任何记录仪器及数据采集系统配接。

二、技术指标891型放大器(包括891型和891-4型)放大倍数:当参数选择开关置于档1:K=10至5000,当参数选择开关置于档2:K=1至500,当参数选择开关置于档3:K=5至2500, K I1=30(积分增益) 当参数选择开关置于档4:K=1至500, K I2=10(积分增益)输入阻抗(kΩ):1000U 0图1 拾振器原理输出负荷 (k Ω):≥1 输入噪声 (μV ):≤1通频带(Hz,-3dB):0.15-100 (参数选择档1和2) 0.35-50 (参数选择档3) 0.2-50 (参数选择档4)电 源:±6~±18V,DC (正负电源差≤0.5V )或220VAC 耗 电:55mA(±12DC 时) 尺 寸:380×240×110mm 重 量:5kg 使用环境:温 度:-10℃~+50℃ 湿 度: ≤85%三、原理(一)拾振器891型拾振器属于动圈往复式拾振器。

DS-9121A 振荡式超高速中心机解决方案说明书

Increase Ease-of-Use withcentrifugation that deliversprecision and performance for sub-op-loading design that provides positive bucket-Both the SW 32 Ti and SW 28 series rotors accept the same variety of tube types, including Quick-Seal ®and Open-T op. The SW 32 Ti accommodates the same large selection of tube sizes as the SW 28 (from 38.5 mL to 8.5 mL volume forSW 32/28 and from 17 mL to 4.2 mL volume for SW 32.1/28.1).T o discover how you can optimize your separations with top-loading swinging bucket rotors, call your Beckman Coulterrepresentative today or visit .SW 32 Ti and SW 28 Series RotorsThe ideal solution for applications in the cellomics and proteomics fields involving rate-zonal and differential centrifugation of sub-cellular fractions and viruses.Relative Centrifugal Field (RCF) is the ratio of the centrifugal acceleration at specified radius and speed (rw 2) to the standardacceleration of gravity (g) according to the following formula: RCF = rw 2where r is the radius in millimeters, w is the angular velocity in g radians per second (2 πRPM/60), and g is the standard acceleration of gravity (9807 mm/s 2). After substitution: RCF = 1.12 r RPM 21000The SW 28, 28.1, 32 Ti and 32.1 Ti rotors are for use in Optima ™L, XL, and LE series ultracentrifuges, as well as L7 and L8M ultracentrifuges (H, R, and S classes).References:These references do not imply endorsement of Beckman Coulter products by the authors.1 Stamatatos L., Werner A., Cheng-Mayer C., J. Virol. 68, 4973-4979 (1994)2 Barr V .A., Scott L.J., Hubbard A.L., J. Biol. Chem. 270, 27834-27844 (1995)3 Shyjan A.W ., Levenson R., Biochemistry 28, 4531-4535 (1989)4 Meier P .J., Boyer J.L., Methods in Enzymology v. 192, 534-545 (1990)5 Wright L.C., et al., Eur. J. Biochem. 243, 328-335 (1997)6 Halford W .P ., Gebhardt B.M., Carr D. J., J. Immunol. 157, 3542-3549 (1996)Sales:1-800-742-2345 • Service:1-800-551-1150 • Telex:678413 • Fax:1-800-643-4366 • Worldwide Life Science Research Division Offices:Australia (61) 2 9844-6000Canada (905) 819-1234China (86) 10 6515 6028Eastern Europe, Middle East, Africa (41) 22 994 07 07 France 01 49 90 90 00Germany (89) 35870-0Hong Kong (852) 2814 7431/2814 0481Italy 02-953921Japan 03-5404-8359 Mexico 525-605-77-70Netherlands 0297-230630Singapore (65) 339 3633South Africa (27) 11-805-2014/5Spain (34)91 3836080Sweden 08-564 85 900Switzerland 0800 850 810Taiwan (886) 2 2378 3456Turkey 90 216 309 1900 U.K.01494 441181U.S.A.1-800-742-2345B2002-4935-PO-10K©2002 Beckman Coulter, Inc .Printed in U.S.A. on recycled paper .†。

100kw光伏并网逆变器中文操作手册

操作与安装手册 (PVI-CENTRAL-100-IT Rev:1.1)

第 5 页,共 54 页

目录

1. 基本安全信息 ..................................................................................................................................9 1.1 前言 .......................................................................................................................................9 1.2 一般信息................................................................................................................................9 1.3 装配 .......................................................................................................................................9 1.4 运输 .....................................................................................................................................10 1.5 电气连接..............................................................................................................................10 1.6 操作 .....................................................................................................................................10 1.7 维护与维修 ..........................................................................................................................11

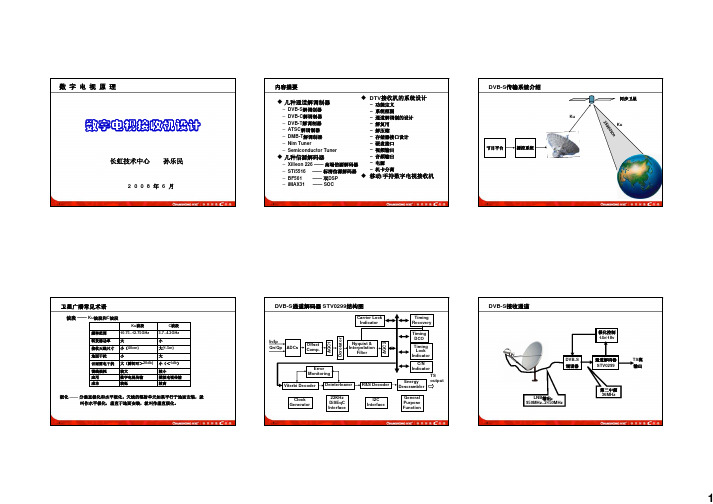

数字电视原理——接收机设计

—1—长虹技术中心孙乐民数字电视接收机设计数字电视原理 2 0 0 8年 6 月—2—内容提要几种通道解调制器–DVB-S 解调制器–DVB-C 解调制器–DVB-T 解调制器–ATSC 解调制器–DMB-T 解调制器–Nim Tuner–Semiconductor Tuner几种信源解码器–Xilleon 226 ——高端信源解码器–STi5516 ——标清信源解码器–BF561 ——双DSP–iMAX31 ——SOCDTV 接收机的系统设计–功能定义–系统框图–通道解调制的设计–解复用–解压缩–存储器接口设计–硬盘接口–视频输出–音频输出–电源–机卡分离移动/手持数字电视接收机—3—DVB-S 传输系统介绍节目平台播控系统同步卫星35860K m KuKu—4—卫星广播常见术语波段——Ku 波段和C 波段较高较低成本模拟电视传输数字电视传输应用较小较大馈线损耗小(<1db )大(瞬间可>20db)云雨雷电干扰大小地面干扰大(1.5m)小(40cm)接收天线尺寸小大转发器功率 3.7~4.2GHz10.75~12.75GHz 频率范围C 波段Ku 波段极化——分垂直极化和水平极化。

天线的辐射单元如果平行于地面安装,就叫作水平极化,垂直于地面安装,就叫作垂直极化。

—5—DVB-S 通道解码器STV0299结构图ADCsOffset Comp.A G C 1D e r o t a t o rNyquist &InterpolationFilterTiming Recovery Timing DCOTiming Lock Indicator C/N IndicatorCarrier Lock IndicatorA G C 2General Purpose FunctionI2C Interface22KHz DiSEqC InterfaceClock GeneratorIn/Ip Qn/QpViterbi Decoder Deinterleaver R&S DecoderEnergy Descrambler Error MonitoringTS output—6—DVB-S 接收通道DVB-S 调谐器通道解码器STV0299TS 流输出LNB 输出:950MHz~2150MHz极化控制14v/18v第二中频36MHz—7—DVB-C 通道解码器STV0297结构图—8—DVB-C 通道解码器STV0297主要功能指标Decodes DVB-C/ITU J83-A and ITU J83-C bit streams.High performance integrated A/D converter suitable for direct IF architecture in all QAM modesSupports 16, 32, 64, 128 and 256 point constellation Small footprint package (10 X 10mm 2,64TQFP).Very low power consumption(400mW TYP. AT 6.9 Msymb/s). Fully digital demodulation.Variable Symbol rates from 0.87 Mbaud to 11.7 Mbaud. Robust integrated adaptive equalizer.On-chip FEC with individually by-passable blocks.Two AGC output suitable for delayed AGC applications (SIGMA-DELTA outputs).Integrated signal quality monitors, plus lock indicator and interrupt pins. System clock can be generated on-chip from quartz crystal.Easy control and monitoring via I2C bus. Aaaitional private I2C bus dedicated to tuner control for minimum tuner disturbance.Programmable clock derived fromsystem clock and avaliable for eternal use Parallel and serial output interfaces, with DBV Common Interface support. CMOS technology, 3.3V operation.—9—DVB-T 通道解码器uPD51640结构图I 2C AGC1AGC2CKAMPOSCPLLCGTPS SYNC CPUGPIOADC1IQAFCFFTEQFECIn/IpQn/Qp TS OutI 2CTuner I 2CProgramable PortAGC1AGC2XTAL—10—DVB-T ETS 300-744 compliantNon-hierchical and hierchical modulation mode Serial and parallel TS output A/D converter integrated2K and 8K COFDM Carrier/Clock Recovery integratedViterbi decoder, bit de-interleave function (code rate: 1/2, 2/3, 3/4, 5/6, 7/8)Reed-Solomon decoder(204, 188, 8), byte de-interleave and de-randomizer functionEach function controllable via I2C bus (3.3V) I2C signal control terminal in tuner part Two supply voltages: 1.5 V and 3.3 V Algorithm to reduce impulsive noise 64 pins TQFP package ,10mm ×10mmDVB-T 通道解码器uPD51640主要功能指标—11—DMB-T 解调制器LGS8913结构图—12—DMB-T 解调制器LGS8913主要参数Single frequency network or Multiple frequency networkTransmission network5.95,6.95,7.94MHz Occupied bandwidths 6, 7 ,8MHzChannel bandwidths Alpha = 0.05Square root raised cosine Pulse sgarping filter 4QAM, 16QAM or 64QAM Sub-carrier modulation Time = 1/9 or ¼of fram length 420 or 945 symbols Guard interval duration For 6, 7, 8MHz1.5, 1.75,2.0KHz Sub-carrier spacing For 6, 7 ,8MHz 666.67, 571.43, 500us Frame length 3744 + 363780Symbol per frame 4QAM, 36 symbols 72bits/Each OFDM frame TPS modulation Block size = 3780Symbol-wiseTime interleaving (Intra-frame)Mode 0:offMode 3:depth = 720 symbols Symbol-wise convolution Time interleaving (Inter-frame)Outer=BCH, Inner = LDPC FEC-Outer188*8bitsPlayload NotesSpecification Parameter—13—ATSC 通道解码器Nxt2004结构图ADCAGCFront EndEqualizerFECuPROMRAMI 2COSCCrystalIFn IFpIF AGCRF AGC Tuner controlTS output—14—TS 流输出的数据信号TS 输出的格式:串行输出和并行输出 TS 输出的数据信号,由11条信号线组成CLK ——数据时钟信号P_SYNC ——包同步信号VALID ——数据有效信号D[0:7] ——数据信号D7 ——串行数据线0x470x47CLK D[0:7]P_SYNC VALID188 byte—15—DBV-C NIM Tuner ——CU1216Passive LTMOPLL IC AGC PLLQAM demodulator TDA10023I 2CAGCI 2CTS output33V/5V+5VAGCRF out—16—CU1216外形尺寸图—17—Semiconductor tuner ——MxL5003—18—Features of MxL5003CMOS 0.18µm processTuning range from 44 to 885 MHzIntegrated channel filtering requiring no external SAW filters On-chip 75 dB AGC with single AGCLow power consumption :165 mA typical ( UHF mode) Programmable IF from low to high IFFlexible support for different demodulator requirements Programmable channel bandwidths from 6, 7, and 8MHz Programmable IF spectrum inversionClock output available to drive demodulator to save crystal componentsOn-chip regulator input 2.3-3.6V ,Can be bypassed with 1.8V supply I2C-compatible digital interface 6 x 6 mm 240-pin QFN package—19—Applications of MxL5003High-performance DVB-T,DVB-H,ISDB-T,ATSC, and64/246-QAM television receiversFlat-screen TVs with low power and small form-factorrequirements such as LCD monitorsPortable applications such as laptops,automobiles,portable DVD playersHandheld applications such as cellular phones andPDAs—20—信源解码器—21—Xilleon 系列集成电路电路功能409BGA409BGA409BGA 571BGAPackageY Y DVI Out Y Y RGB Input for DVI IN YY YY Improve deinterlacing Y Y Y Y Nand Flash3No of DACs for 2nd display 4664No of DACs for 1st display Mux Mux Y Y PIC/EIDE/Flexbus22PVRY Y Y TV & VCR out Y Y Y PIP1124SD decode 12HD decode X210D X210H X216X226Function—22—X226结构图—23—集成度更高的数字电视芯片——X240—24—i.MX31结构图Function EPIT ×2 PWM WDOG RTC GPT ×3RAM,ROMARM11 PlatformARM1136JF-SVFP I Cache D Cache L2 CacheETMAVICConnectivity MSCH ×2GPIO ×3FIRSIMMMC/SD ×2KPP CSPI ×3UART ×51-WIREI 2C ×3USBOTG,HSUSB Host ×2IOMUXC SecurityRTIC SCC IIMRNGAMultimedia PeripheralsMPEG4 EncoderSSI ×2 I 2SAUDMUX IPUSensor InterfaceResize/CSCDeblock/DeringBlendingDisplay/TV controlMBX R-S Graphics AcceleratorSystem control JTAG, Debug System Boot PLL and PWR Management Reset APIS ×2SDMA SPBA MAX—25—i.MX31应用—26—我国数字电视产业发展的瓶颈内容贫乏垄断经营——数字电视机顶盒由各地运营商赠送,终端制造企业不堪重负 各地运营商和软件商采用多种不同的CA 、EPG 、下载器、中间件和应用软件系统 运营商被业务平台厂商锁定 数字电视机顶盒无法大批量生产 数字电视一体机无法生产和上市数字电视用户使用成本高、无从选择、重复购买 标准制定落后于市场—27—机卡分离的目标将各地运营商主导的差异性功能可以从数字电视接收机/接收器中分离,使接收机/接收器可以统一批量生产 降低机顶盒/一体机成本 使机顶盒/一体机具有升级接口使数字电视一体机机/机顶盒最终能够在水平市场上销售—28—USB机卡分离Uti200集成电路结构图—29—美国数字电视接收机设计实例—30—数字电视一体机设计明确市场目标z 了解目标市场的需求z 了解目标市场的技术规范z 了解运营商的特殊要求z 了解目标用户的使用习惯 定义产品的功能 确定产品的技术规格—31—美国数字电视接收机的特殊要求兼容ATSC (数字)/ NTSC (模拟)标准参考标准:a_53d_ATSC(2000)采用虚拟频道管理,参考标准:a_65b(2003) 电子节目指南分为带内和带外(OOB )传送参考标准:a_55_EPG(2003)具有POD (Point Of Deployment )CA 接口参考标准:具备美国Close Caption Display (CCD )功能按美国电影/电视节目内容分级控制标准设计的家长控制(Parent Control )功能具备美国内容保护(HDMI 、HDCP 、Macrovision )接口和要求 显示不低于1280 ×720P 精度,兼容18种格式 至少英语、法语、西班牙三种OSD 语言—32—系统功能设计(部分)显示分辨率:1280×720p或1920 ×1080i;内置数字高频头,具有ATSC/NTSC接收功能,能够兼容接收美国18种数字高清电视信号格式 采用FS调谐器,181个电视节目的存储(AIR 2-69、CABLE 1-125); 频率调谐方式:自动搜索、Air/Cable切换、Skip ON/OFF设置;节目选择方式:虚拟频道管理,直接数字键(一位、两位或三位数字),节目回调(Recall)功能; EPG显示(带内),7天双视窗、PIP功能:具有PIP开关、PIP节目+/-、PIP窗口2级大小变化、PIP位置、AV信号源切换,PIP静止、PIP与主画面直接交换等功能画质调整功能:亮度、色度、清晰度、对比度和色调可调整;PIP/POP/TWIN亮度、对比度和色调可调整。

891-2型拾振器使用说明书V2016公司版

益 4 K12 (1/s)

通道

9

积 参数选择档

分 3 K11 (1/s) 增 参数选择档

益 4 K12 (1/s)

2

3

4

5

6

7

8

10

11

12

13

14

15

16

输入阻抗(KΩ):≥1000 输出负荷(KΩ):≥1 输入噪声(μv):直流供电时≤1;交流供电时≤10。

4

891-2 型拾振器

通 频 带:

通频带选择开关档位 1 2

关于拾振器的保护:拾振器在非使用状态时,均应将“1”档置于“ON”或 把输出端短路,以保护拾振器的运动部件。 2. 放大器使用方法 1) 接通电源

放大器采用 12VDC 供电,配有专用电源适配器,可为放大器提供标准 12V 直

9

891-2 型拾振器

IEM

流电源。

2) 连接线缆

将传感器连接至放大器后面板的“信号输入”端口,将放大器后面板的“信

7

8

9 10

参数

1直

通 10 20 50 100 200 500 1000 2000 4000 5000

2直

通

1 2 5 10 20 50 100 200 400 500

3 积分(KI1=20) 5 10 25 50 100 250 500 1000 2000 2500 4 积分(KI2=4) 1 2 5 10 20 50 100 200 400 500

号输出”端口连接到数据采集仪;

3) 打开电源开关,此时电源开关发出蓝色灯光;

4) 设置放大器各功能开关的位置

根据测量要求,设置放大器前面板的“频带”、“参数”和“放大”三个档

DS8911中文资料

元器件交易网

Connection Diagram

Plastic Chip Carrier

TL F 7398–8

Top View Order Number DS8911V DS8913V See NS Package Number V28A

Pin Descriptions

General Description

The DS8911 is a digital Phase-Locked Loop (PLL) frequency synthesizer intended for use as a Local Oscillator (LO) in electronically tuned radios The device is used in conjunction with a serial data controller a loop filter some varactor diodes and several passive elements to provide the local oscillator function for both AM and FM tuning The conventional superheterodyne AM receiver utilizes a low IF or down conversion tuning approach whereby the IF is chosen to be below the frequencies to be received The DS8911 PLL on the other hand utilizes an up-conversion technique in the AM mode whereby the first IF frequency is chosen to be well above the RF frequency range to be tuned This approach eliminates the need for tuned circuits in the AM frontend since the image half IF and other spurious responses occur far beyond the range of frequencies to be tuned Sufficient selectivity and second IF image protection is provided by a crystal filter at the output of the first mixer A significant cost savings can be realized utilizing this upconversion approach to tuning Removal of the AM tuned circuits eliminates the cost of expensive matched varactor diodes and reduces the amount of labor required for alignment down from 6 adjustments to 2 Additional cost savings are realized because up-conversion enables both the AM and FM bands to be tuned using a single Voltage Controlled Oscillator (VCO) operating between 98 and 120 MHz (The 2 to 1 LO tuning range found in conventional AM down conversion radios is reduced to a 10% tuning range 9 94 MHz to 11 02 MHz) Up-conversion AM tuning is accomplished by first dividing the VCO signal down by a modulus 10 to obtain the LO signal This LO in turn is mixed on chip with the RF signal to obtain a first IF at the MIXER output pins This first IF after crystal filtering is mixed (externally) with a reference frequency provided by the PLL to obtain a 450 kHz second IF frequency The DS8911 derives the 450 kHz second IF by mixing an 11 55 MHz first IF with a 12 00 MHz reference frequency FM and WB (weather band) tuning is done using the conventional down conversion approach Here the VCO signal is buffered to produce the LO signal and then mixed on chip with the RF signal to obtain an IF frequency at the MIXER output pins This IF frequency is typically chosen to be 10 7 MHz although placement at 11 50 MHz can further enhance AM mode performance and minimize IF circuitry The PLL provides phase comparator reference frequencies of 10 12 5 25 and 100 kHz The tuning resolutions resulting from these reference frequencies are determined by dividing the reference by the premix modulus Table II shows the tuning resolutions possible The DS8911 contains the following logic elements a voltage controlled oscillator a reference oscillator a 14-bit programmable dual-modulus counter a reference frequency divider chain a premix divider a mixer a phase comparator a charge pump an operational amplifier and control circuitry for latched serial data entry The DS8913 includes all the above logic elements except that it requires a 10 MHz reference frequency instead of 12 MHz

BD9833KV资料

(Contact address for overseas customers in Japan)

Yokohama

As of 18th. April 2005

United Kingdom / London TEL : +44(1)908-282-666 France / Paris China / Hong Kong Shanghai Dilian Beijing Taiwan / Taipei Korea / Seoul Singapore Malaysia / Kuala Lumpur Philippines / Manila Thailand / Bangkok

The products listed in this document are designed to be used with ordinary electronic equipment or devices (such as audio visual equipment, office-automation equipment, communications devices, electrical appliances and electronic toys). Should you intend to use these products with equipment or devices which require an extremely high level of reliability and the malfunction of with would directly endanger human life (such as medical instruments, transportation equipment, aerospace machinery, nuclear-reactor controllers, fuel controllers and other safety devices), please be sure to consult with our sales representative in advance. About Export Control Order in Japan Products described herein are the objects of controlled goods in Annex 1 (Item 16) of Export Trade Control Order in Japan. In case of export from Japan, please confirm if it applies to "objective" criteria or an "informed" (by MITI clause) on the basis of "catch all controls for Non-Proliferation of Weapons of Mass Destruction.

DS1923中文资料

Standard speed, VPUP > 4.5V

tMSP

Standard speed

Overdrive speed

65 71.5

8

75

75

µs

9

2 of 52

PARAMETER IO Pin, 1-Wire Write

SYMBOL

Write-0 Low Time (Note 1)

tW0L

Write-1 Low Time (Notes 1, 13)

DS1923: 带 8kB 数据记录存储器的 Hygrochron 温度/湿度记录器 iButton

CONDITIONS

MIN TYP MAX UNITS

Standard speed

60

Overdrive speed, VPUP > 4.5V (Note 11)

6

Overdrive speed (Note 11)

-20°C to +85°C, 0%RH to 100%RH

(See Safe Operating Range Chart)

Storage Temperature and Humidity Range

-40°C to +85°C, 0%RH to 100%RH

(See Safe Operating Range Chart)

DS1923 ELECTRICAL CHARACTERISTICS

PARAMETER

SYMBOL

(VPUP = 3.0V to 5.25V, TA = -20°C to +85°C)

CONDITIONS

MIN TYP MAX UNITS

IO Pin General Data

海康威视传输产品系列说明书

OPTICAL MODULENETWORK CABLESRECOMMENDED OPTIONSWIRELESS BRIDGEAGGREGATION & CORE ETHERNET SWITCHINDUSTRIAL POE ETHERNET SWITCH≤ 100-ch IPCTypeModel Aggregation switchDS-3E0524TFAccess switch DS-3E01(3)xxP-E(B)Access switchDS-3E01(3)xxP-E/M(B)Access switch DS-3E05xxP-E Access switch DS-3E05xx-EOptical moduleHK-SFP-1.25G-1310-DF-MM100-ch < IPC ≤ 300-chTypeModel Aggregation switch DS-3E2528Access switch DS-3E13xxP-E Access switch DS-3E01(3)xxP-E(B)Access switch DS-3E05xxP-E Access switch DS-3E05xx-E Optical moduleHK-SFP-1.25G-20-1310HK-SFP-1.25G-20-1550300-ch < IPC ≤ 500-chType Model Core switch DS-3E3756TF Core switch DS-3E3740Aggregation switchDS-3E2528Access switch DS-3E23xxP-E Access switch DS-3E05xxP-E Access switch DS-3E01(3)xxP-E(B)Optical moduleHK-SFP-1.25G-20-1310HK-SFP-1.25G-20-1550ModelImageDescriptionHK-SFP-1.25G-20-1310TX 1310 nm/1.25G, RX 1550 nm/1.25G, LC, single mode and single fiber, 20 km, 0~70°C, SFPHK-SFP-1.25G-20-1550TX 1550 nm/1.25G, RX 1310 nm/1.25G, LC, single mode and single fiber, 20 km, 0~70°C, SFPHK-SFP-1.25G-1310-DF-MMTX 1310 nm/1.25G, RX 1310 nm/1.25G, LC, Multi mode and duplex fiber, 1 km, 0~70°C, SFPHK-SFP-1.25G-20-1310-DF TX 1310 nm/1.25G, RX 1310 nm/1.25G, LC, Single mode and duplex fiber, 20 km, 0~70°C, SFPHK-SFP+-10G-20-1270TX 1270 nm/10G, RX 1330 nm/10G, LC, single mode and single fiber, 20 km, 0~70°C, SFP+HK-SFP+-10G-20-1330TX 1330 nm/10G, RX 1270 nm/10G, LC, single mode and single fiber, 20 km, 0~70°C, SFP+Outdoor wireless bridgeElevator wireless bridgeModelDS-3WF01C-2N/ODS-3WF02C-5N/ODS-3WF03CDS-3WF0AC-2NTDS-3WF01C-2NDescriptionSupports point-to-point &point-to-multipoint;Range up to 3 km; 802.11 b/g/n, Built-in 12 dBiantenna up to 150 Mbps; Output power 27 dBm; Angle Horizontal: 60° Vertical: 30°; IP65;Supports point-to-point & point-to-multipoint; Range up to 5 km; 802.11 a/n, Built-in 10 dBi 2×2 MIMO antenna up to 300 Mbps; Output power 24 dBm; Angle Horizontal: 60° Vertical: 16°; IP65;Supports point-to-point & point-to-multipoint; Range up to 15 km; 802.11a/n, Built-in 15dBi 2×2 MIMO antenna with 300 Mbps; Output power 27 dBm; Angle Horizontal: 40° Vertical: 15°; IP65;Supports point-to-point, distance 100 m; IEEE 802.11b/g/n, Built-in 8dBi antenna; Output power 20 dBm; Angle Horizontal: 60° Vertical: 30°; Working temperature: -30 ~65°C; Plug and play, no initial setting;Supports point-to-point, distance 500 m; IEEE 802.11b/g/n, Built-in 6dBi antenna; Output power 27 dBm; Angle Horizontal: 65° Vertical: 60°; Working temperature: -30 ~65°C;Plug and play, no initial setting;ModelDS-1LN5E-SDS-1LN6-UUDS-1LN5E-E/EDS-1LN6-UE-WDescriptionUTP CAT 5E, 305 meters Core diameter: 0.5 mm Solid copper,CM,grayUTP CAT 6, 305 meters Core diameter: 0.565 mm Solid copper, CM, orangeUTP CAT 5E, 305 meters Core diameter: 0.45 mm Solid copper, CMX,grayUTP CAT 6, 305 meters, Core diameter: 0.53 mm Solid copper, CM,whiteModelDS-3E0524TFDS-3E2528DS-3E3740DS-3E3756TFManagement Unmanaged Full-managed Full-managed Full-managed Ports12 × Gigabit RJ45 ports 12 × Gigabit SFP ports24 × Gigabit RJ45 ports 4 × Gigabit SFP ports32 × Gigabit RJ45 ports 8 × 10G SFP+ ports24 × Gigabit RJ45 ports 24 × Gigabit SFP ports 8 × 10G SFP+ portsPacket Forwarding Rate 35.7 Mpps 42 Mpps 136 Mpps 136 Mpps Switching Capacity 48 Gbps 56 Gbps 224 Gbps 256 GbpsMAC Address Table 16 K 8 K64 K64 KManagement Mode -Console, Telnet, SSH2.0, Web, SNMP v1/v2/v3, TFTP, RMONOther Software Features-STP, VLAN, Mirroring, IGMP Snoopingand IGMP v1/v2, L2/L3/L4 ACL, LACP,EAPS, ERPSSTP, VLAN, Mirroring, IGMP Snooping and IGMP v1/v2, L2/L3/L4 ACL, LACP, EAPS,Operating Temperature -5°C~50°C0°C~45°C0°C~45°C0°C~45°C Dimension (440 × 186.5 × 44.5) mm (440 × 230 × 45) mm (442.5 × 315 × 44) mm (442.5 × 350 × 44) mmPower SupplyModelELG-150-48AImageOutput Voltage 48 VRated Current 3.13 ARated Power 150 WOperating Temperature-40~90°CIP Rating IP65AccessoryOptional accessory for industrial PoEswitchIndustrial switchModelDS-3T0306PDS-3T0310PManagement UnmanagedUnmanagedPorts 4 × 10/100 Mbps PoE RJ45 ports2 × Gigabit uplink SFP ports 8 × 10/100 Mbps PoE RJ45 ports 2 × Gigabit uplink SFP ports PoE Standards IEEE 802.3af, IEEE802.3atIEEE 802.3af, IEEE802.3atPoE Budget≤ 120 W ≤ 240 W Packet Forwarding Rate 3.6 Mpps 4.2 Mpps Switching Capacity 8.8 Gbps 8.8 Gbps MAC Address Table 4 K 4 K Surge Protection 2 KV 2 KV Operating Temperature -40°C~75°C -40°C~75°C Dimension(155 × 130 × 42) mm(170 × 156 × 42) mmUNMANAGED NON-POE ETHERNET SWITCHUNMANAGED POE ETHERNET SWITCHMANAGED POE ETHERNET SWITCHUNMANAGED SWITCHIEEE 802.3bt Standard Hi-PoE, Max. 90 W for One PortIEEE 802.3bt standard Hi-PoE port provides max. 90 W power supply for high power devices such as domes.Up to 300 m Long Range PoE TransmissionBased on all series of camera tests with Hikvisionnetwork cables, up to 300 m long range PoE transmission is provided.Intelligent PoE ManagementWhen the power supply exceeds the limit, PoE ports intelligently manage the power supply, which extends the switch lifetime.4/8-Core Adaptive Power Supply with Less Power Loss8-core power supply reduces the power loss on cables.6KV Surge Protection to Improve Reliability in Harsh EnvironmentThe built-in surge protection device protects the switch from the sudden lightning surge in harsh environment.Design for Video TransmissionVIP port ensures important data transmission when network congestion occurs.Hi-PoE SwitchesModelDS-3E0106HP-EDS-3E0310HP-EPorts1 × 10/100 Mbps Hi-PoE port 3 × 10/100 Mbps PoE ports2 × 10/100 Mbps RJ45 ports 1 × 10/100 Mbps Hi-PoE port 7 × 10/100 Mbps PoE ports 2 × Gigabit RJ45 ports PoE Standards Port 1: IEEE 802.3af, IEEE 802.3at, IEEE802.3btPorts 2 to 4: IEEE 802.3af, IEEE 802.3atPort 1: IEEE 802.3af, IEEE 802.3at, IEEE802.3btPorts 2 to 8: IEEE 802.3af, IEEE 802.3atPoE Budget 60 W 110 W Max. port PoE power Port 1: 60 W Ports 2 to 4: 30 W Port 1: 90 W Ports 2 to 8: 30 W PoE Extend Mode Max. 300 m, Port 1-4Max. 300 m, Port 1-8Packet Forwarding Rate 0.893 Mpps 4.166 Mpps Switching Capacity 1.2 Gbps 5.6 Gbps MAC Address Table 2 K 16 K Surge Protection 6 KV 6 KV Operating Temperature-10°C~55°C -10°C~55°CDimension(145 × 25.6 × 68.45) mm(217.6 × 27.8 × 103.35) mm10/100 Mbps SwitchesModelDS-3E0105P-E/M(B)DS-3E0109P-E/M(B)DS-3E0318P-E/M(B)DS-3E0326P-E/M(B)DS-3E0105P-E(B)DS-3E0109P-E(C)DS-3E0318P-E(B)DS-3E0326P-E(B)Ports4 × 10/100 Mbps PoE RJ45 ports 1 × 10/100 Mbps uplink RJ45 port8 × 10/100 Mbps PoE RJ45 ports 1 × 10/100 Mbps uplink RJ45 port16 × 10/100 Mbps PoE RJ45 ports 1 × Gigabit uplink RJ45 port 1 × Gigabit uplink SFP port 24 × 10/100 Mbps PoE RJ45 ports1 × Gigabit uplink RJ45 port1 × Gigabit uplink SFP port4 × 10/100 Mbps PoE RJ45 ports1 × 10/100 Mbps uplink RJ45 port8 × 10/100 Mbps PoE RJ45 ports1 × 10/100 Mbps uplink RJ45 port16 × 10/100 Mbps PoE RJ45 ports 2 × Gigabit comb ports (2 RJ45 Ports and 2 SFP Ports)24 × 10/100 Mbps PoE RJ45 ports 2 × Gigabit comb ports (2 RJ45Ports and 2 SFP Ports)PoE Standards IEEE 802.3af, IEEE802.3atIEEE 802.3af, IEEE802.3atIEEE 802.3af, IEEE802.3atIEEE 802.3af, IEEE802.3atIEEE 802.3af, IEEE802.3atIEEE 802.3af, IEEE802.3atIEEE 802.3af, IEEE802.3atIEEE 802.3af, IEEE802.3atPoE Budget35 W60 W130 W230 W60 W115 W 230 W370 WPoE Extend Mode Max.300 m, Port 1-4Max. 300 m, Port 1-8Max. 300 m, Port 9-16Max. 300 m, Port 17-24Max 300 m, Port 1-4Max 300 m, Port 1-8Max. 300 m, Port 9-16Max. 300 m, Port 17-24Packet Forwarding Rate0.744 Mpps 1.34 Mpps 5.36 Mpps 6.55 Mpps 0.74 Mpps 1.34 Mpps 5.36 Mpps 6.55 Mpps Switching Capacity1 Gbps 1.8 Gbps 7.2 Gbps 8.8 Gbps 1 Gbps 1.8 Gbps 7.2 Gbps 8.8 Gbps MAC Address Table 1 K 2 K 4 K 4 K 1 K 2 K 4 K 4 K Surge Protection 6 KV 6 KV 6 KV 6 KV 6 KV 6 KV 6 KV 6 KV Operating Temperature-10°C~55°C -10°C~55°C -10°C~55°C -10°C~55°C -10°C~55°C -10°C~55°C -10°C~55°C -10°C~55°C Dimension(105 × 27.6 × 83.1)mm(170 × 27.6 × 93.1) mm(266 × 44.5 × 220.8) mm(335 × 44.5 × 226) mm(105 × 27.6 × 83.1) mm(170 × 27.6 × 93.1) mm(440 × 44 × 220.8) mm(440 × 44 × 220.8) mmGigabit SwitchesModel DS-3E0505P-EDS-3E0510P-EDS-3E0518P-EDS-3E0526P-EPorts4 × Gigabit PoE RJ45 ports1 × Gigabit RJ45 port 8 × Gigabit PoE RJ45 ports 1 × Gigabit RJ45 port 1 × Gigabit SFP port 16 × Gigabit PoE RJ45 ports 1 × Gigabit RJ45 port 1 × Gigabit SFP port 24 × Gigabit PoE RJ45 ports 1 × Gigabit RJ45 port 1 × Gigabit SFP port PoE Standards IEEE 802.3af, IEEE802.3atIEEE 802.3af, IEEE802.3atIEEE 802.3af, IEEE802.3atIEEE 802.3af, IEEE802.3atPoE Budget60 W 110 W 230 W 370 W Packet Forwarding Rate 7.44 Mpps 14.88 Mpps 26.784 Mpps 38.688 Mpps Switching Capacity 10 Gbps 20 Gbps 36 Gbps 52 Gbps MAC Address Table 2 K 4 K 8 K 8 K Surge Protection6 KV 6 KV 6 KV 6 KV Operating Temperature-10°C~55°C -10°C~55°C-10°C~55°C -10°C~55°C Dimension(105 × 27.6 × 83.1) mm(217.6 × 27.8 × 108.55) mm(440 × 44 × 220.8) mm(440 × 44 × 220.8) mmModel DS-3E0105D-EDS-3E0108D-EDS-3E0505D-EDS-3E0508D-EDS-3E0508-EDS-3E0516-EDS-3E0524-EPorts 5 × 10/100 Mbps RJ45 ports 8 × 10/100 Mbps RJ45 ports 5 × Gigabit RJ45 ports 8 × Gigabit RJ45 ports 8 × Gigabit RJ45 ports 16 × Gigabit RJ45 ports 24 × Gigabit RJ45 portsSwitching Capacity 1 Gbps 1.6 Gbps 10 Gbps 16 Gbps 16 Gbps 32 Gbps 48 GbpsPacket Forwarding Rate 0.744 Mpps 1.1904 Mpps 7.44 Mpps 11.904 Mpps 11.9 Mpps 23.8 Mpps 35.7 MppsMAC Address Table 1 K 1 K 2 K 4 K 4 K 8 K 8 KSurge Protection ---- 4 KV 4 KV 4 KVOperating Temperature 0°C~40°C 0°C~40°C 0°C~40°C 0°C~40°C 0°C~40°C 0°C~40°C 0°C~40°CDimension (82 × 52 × 22.4) mm (124 × 59 × 23.2) mm (92.8 × 65.8 × 22.8) mm (142 × 90 × 23) mm (186.7 × 106.7 × 33.3) mm (440 × 178.8 × 44) mm (440 × 178.8 × 44) mmModel DS-3E1310P-EDS-3E1318P-EDS-3E1326P-EDS-3E2310PDS-3E2318PDS-3E2326PDS-3E2510PDS-3E2528PManagement Web-managed Web-managed Web-managed Full-managed Full-managed Full-managed Full-managed Full-managed Ports 8 × 10/100 Mbps PoE RJ45 ports 2 × Gigabit comb ports (2 RJ45 Ports and 2 SFP Ports)16 × 10/100 Mbps PoE RJ45 ports 2 × Gigabit comb ports (2 RJ45 Ports and 2 SFP Ports)24 × 10/100 Mbps PoE RJ45 ports 2 × Gigabit comb ports (2 RJ45 Ports and 2 SFP Ports)8 × 10/100 Mbps PoE RJ45 ports 2 × Gigabit comb ports (2 RJ45 Ports and 2 SFP Ports)16 × 10/100 Mbps PoE RJ45 ports 2 × Gigabit comb ports (2 RJ45 Ports and 2 SFP Ports)24 × 10/100 Mbps PoE RJ45 ports 2 × Gigabit comb ports (2 RJ45Ports and 2 SFP Ports)8 × Gigabit PoE RJ45 ports 2 × Gigabit SFP ports 24 × Gigabit PoE RJ45 ports 4 × Gigabit SFP ports PoE Standards IEEE 802.3af, IEEE802.3atIEEE 802.3af, IEEE802.3atIEEE 802.3af, IEEE802.3atIEEE 802.3af, IEEE802.3atIEEE 802.3af, IEEE802.3atIEEE 802.3af, IEEE802.3atIEEE 802.3af, IEEE802.3atIEEE 802.3af, IEEE802.3atPoE Budget 123 W 230 W370 W125 W 300 W 380 W 125 W 380 W PoE Extend Mode Max. 250 m, Port 1-8Max. 250 m, Port 1-16Max. 250 m, Port 1-24-----Packet Forwarding Rate 1.34 Mpps 5.36 Mpps 6.55 Mpps 5.6 Mpps 8.4 Mpps 9.6 Mpps 15 Mpps 42 Mpps Switching Capacity5.4 Gbps 7.2 Gbps 8.8 Gbps 10 Gbps 21.2 Gbps 22.8 Gbps 20 Gbps 56 Gbps MAC Address Table 4 K4 K4 K8 K8 K8 K8 K8 KManagement Mode SNMP v1/v2, WEB managementConsole, Telnet, SSH2.0, Web, SNMP v1/v2/v3, TFTP, RMONOther Software Features STP, VLAN, Mirroring, IGMP Snooping and IGMP v1/v2STP, VLAN, Mirroring, IGMP Snooping and IGMP v1/v2, L2/L3/L4 ACL, LACP, EAPS, ERPSSurge Protection 4 KV 4 KV 4 KV 4 KV 4 KV 4 KV 4 KV 4 KV Operating Temperature 0°C~40°C 0°C~40°C 0°C~40°C 0°C~40°C 0°C~40°C 0°C~40°C 0°C~45°C 0°C~45°C Dimension(294 × 165.8 × 44) mm(440 × 285 × 43) mm(440 × 285 × 43) mm(280 × 179 × 45) mm(440 × 232 × 44) mm(440 × 232 × 44) mm(280 × 179 × 45) mm(440 × 232 × 45) mm。

诺瓦科技LED交通多媒体播放器JT100规格书

非经本公司书面许可,任何单位和个人不得擅自摘抄、复制本文档内容的部分或全部,并不得以任何形式传播。

i

JT100交通多媒体播放器

规格书目录

目录

1.1产品简介...................................................................................................................................................... 1

5

6.1图片........................................................................................................................................................... 10

1.2应用场景...................................................................................................................................................... 1

2

2.1处理性能强大.............................................................................................................................................. 2

2.2.3 WiFi AP+Sta模式................................................................................................ 3

Bridgelux 2835 1W 9V Thrive 产品数据表 DS310说明书

Product Data Sheet DS310Bridgelux Thrive™ combines unique chip, phosphor and packaging technology to closely match the spectra of natural light over the visible wavelength range. Thrive can be used in constant color point luminaires to bring full spectrum natural light indoors or in tunable white luminaires to incorporate circadian elements that may impact human well-being. The high fidelity spectral output of Thrive creates stunning environments with excellent color rendering and outstanding TM30 metrics. Thrive is available in both SMD components and LED arrays to enable a broad range of lighting applications including retail, hospitality, office, education, architectural, museums, healthcare and residential lighting.Features• Engineered spectra to closely match natural light • CRI > 95, R1-R15 >90, high Rf and Rg values• High efficiency full spectrum solution• No violet chip augmentation• Hot color targeted• Industry standard 2835 footprint• Broad product platform availability (SMDs and COBs)Benefits• Full consistent spectrum with fewer spectral spikes • Natural and vivid color rendering• Greater energy savings, lower utility costs• Economical, high efficiency solution• Uniform and consistent white light under application conditions• Ease of design and rapid go-to-market• Enables greater design flexibility and platform color consistencyContentsProduct Feature Map2 Product Nomenclature2 Product Test Conditions2 Product Selection Guide3 Spectrum Characteristics4 Electrical Characteristics7 Absolute Maximum Ratings8 Product Bin Definitions9 Performance Curves12 Typical Radiation Pattern13 Mechanical Dimensions14 Reliability 15 Reflow Characteristics16 Packaging17 Design Resources19 Precautions19 Disclaimers19 About Bridgelux20Product Feature MapYellow phosphor Light Emitting Surface (LES)Product NomenclatureThe part number designation for Bridgelux SMD 2835 is explained as follows:Product Test ConditionsBridgelux SMD 2835 LEDs are tested and binned with a 10ms pulse of 100mA at T j (junction temperature)=T sp (solder point temperature) =25°C. Forward voltage and luminous flux are binned at a T j =T sp =25°C, while color is hot targeted at a T sp of 85°C.1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16Product FamilyColor Bin OptionsFlux BinsMinimum CRIS = ThriveForward Voltage Bins Nominal CCT27 = 2,700K 30 = 3,000K 35 = 3,500K 40 = 4,000K 50 = 5,000K 57 = 5,700K 65 = 6,500KBXEN – 27 S – 1 3 H – 9 C –00 – 0 – 0Product VersionHigh PowerDie count in parallelTypical Forward Voltage Die count in series Bridgelux SMD LED products come in industry standard package sizes and follow ANSI binning standards. These LEDs are optimized for cost and performance, helping to ensure highly competitive system lumen per dollar performance while addressing the stringent efficacy and reliability standards required for modern lighting applications.The following product configurations are available:7,8Notes for Tables 1 & 2:1. The last 6 characters (including hyphens ‘-’) refer to flux bins, forward voltage bins, and color bin options, respectively. “00-0-0” denotes the full distribution of flux, forward voltage, and 6 SDCM color.Example: BXEN-27S-13H-9C-00-0-0 refers to the full distribution of flux, forward voltage, and color within a 2700K 6-step ANSI standardchromaticity region with a minimum of 95 CRI, 1x3 die configuration, high power, 9.1V typical forward voltage.2. Product CCT is hot targeted at Tsp= 85°C. Nominal CCT as defined by ANSI C78.377-2011.3. Listed CRIs are minimum values and include test tolerance.4. Products tested under pulsed condition (10ms pulse width) at nominal drive current where Tj =Tsp=25°C.5. Bridgelux maintains a ±7.5% tolerance on luminous flux measurements, ±0.1V tolerance on forward voltage measurements, and ±2 tolerance onCRI measurements for the SMD 2835.6. Refer to Table 6 and Table 7 for Bridgelux SMD 2835 Luminous Flux Binning and Forward Voltage Binning information.7. Typical pulsed test performance values are provided as reference only and are not a guarantee of performance.8. Typical performance is estimated based on operation under pulsed current with LED emitter mounted onto a heat sink with thermal interfacematerial and the solder point temperature maintained at 85°C. Based on Bridgelux test setup, values may vary depending on the thermal design of the luminaire and/or the exposed environment to which the product is subjected.9. Photosynthetic Photon Flux is measure of photon flux in the 400nm-700nm region.Product Selection Guide1Note for Table 3:1. Bridgelux maintains a tolerance of ± 3 on Color Rendering Index R1-R15 measurements and TM-30 measurements. Figure 1: 2700K Thrive TM-30 GraphsFigure 2: 3000K Thrive TM-30 GraphsFigure 3: 3500K Thrive TM-30 GraphsFigure 4: 4000K Thrive TM-30 GraphsFigure 5: 5000K Thrive TM-30 GraphsFigure 6: 5700K Thrive TM-30 GraphsFigure 7: 6500K Thrive TM-30 GraphsFigure 8: Typical Color SpectrumNote for Figure 8:1. Color spectra measured at nominal current for T sp = 85°C.Spectral Matching to Natural LightHumans have evolved and thrived for millions of years under the sun’s natural daylight. While discussions continue regarding the development of LED prod-ucts with artificial spectra aimed at increasing productivity and focus or helping with relaxation, the long-term physiological effects of such altered environ -ments on humans remains unknown.Bridgelux Thrive is engineered to provide the closest match to natural light using proprietary chip, phosphor and packaging technology. Bridgelux is working with our customers and industry partners to define new metrics to describe and quantify this spectral matching; going beyond today’s quality of light metrics such as CRI and TM-30.To quantify spectral matching, Bridgelux has defined a new term; Average Spectral Difference (ASD). ASD is calculated by measuring the absolute difference between the LED spectrum and a natural light source spectrum at discrete wavelengths. These values are then averaged across different wavelength ranges and reported as a percentage. Natural light is defined by the Black Body Curve for sources below 5000K or by the CIE Standard Illuminant D for sources of 5000K or above (D50 for example).Bridgelux Thrive has an ASD between 3% and 7% for all color points (2700K – 6500K) across the typical LED wavelength range of 440-650nm. This includes a very close spectral match, with an ASD of only 2% for some color point options, in the blue/cyan color range where most other LED light sources suffer. For comparison purposes, standard 80, 90 and 98 CRI light sources have an ASD that is 2-6 times larger than Thrive over the same wavelength range and up to 20 times greater in the cyan wavelength range.As the industry evolves toward human centric lighting, Bridgelux will work with our customers and industry experts to educate the market about the benefits of the ASD metric to further quantify the quality of light.0%20%40%60%80%100%120%140%380400420440460480500520540560580600620640660680700720740760780R e l a t i v e R a d i a n t P o w e r (%)Wavelength (nm)4000K Spectral ComparisonThrive 4000K BBC 90 CRI 80 CRI0%20%40%60%80%100%350400450500550600650700750800R e l a t i v e R a d i a n t P o w e r (%)Wavelength(nm)2700K3000K3500K 4000K0%20%40%60%80%100%350400450500550600650700750800R e l a t i v e R a d i a n t P o w e r (%)Wavelength(nm)5000K 5700K 6500KTable 4:Electrical Characteristics1. The last 6 characters (including hyphens ‘-’) refer to flux bins, forward voltage bins, and color bin options, respectively. “00-0-00” denotes the full distribution of flux, forward voltage, and 6 SDCM color.Example: BXEN-27S-13H-9C-00-0-0 refers to the full distribution of flux, forward voltage, and color within a 2700K 6-step ANSI standardchromaticity region with a minimum of 95 CRI, 1x3 die configuration, high power, 9.1V typical forward voltage.2. Bridgelux maintains a tolerance of ± 0.1V on forward voltage measurements. Voltage minimum and maximum values at the nominal drive current are guaranteed by 100% test.3. Products tested under pulsed condition (10ms pulse width) at nominal drive current where Tsp = 25°C.4. Thermal resistance value was calculated using total electrical input power; optical power was not subtracted from input power.Absolute Maximum RatingsNotes for Table 5:1. Bridgelux recommends a maximum duty cycle of 10% and pulse width of 10 ms when operating LED SMD at maximum peak pulsed current specified. Maxi-mum peak pulsed current indicate values where LED SMD can be driven without catastrophic failures.2. Light emitting diodes are not designed to be driven in reverse voltage and will not produce light under this condition. no rating is provided.Product Bin DefinitionsTable 6 lists the standard photometric luminous flux bins for Bridgelux SMD 2835 LEDs. Although several bins are listed, product availability in a particular bin varies by production run and by product performance. Not all bins are available in all CCTs.Note for Table 6:1. Bridgelux maintains a tolerance of ± 7.5% on luminous flux measurements.Note for Table 7:1. Bridgelux maintains a tolerance of ± 0.1V on forward voltage measurements.Product Bin DefinitionsNotes for Table 8:=85°C unless otherwise specified1. Color binning at Tsp2. Bridgelux maintains a tolerance of ± 0.007 on x and y color coordinates in the CIE 1931 color space.Product Bin Definitions=85°C) Figure 9: C.I.E. 1931 Chromaticity Diagram (Color Targeted at TspPerformance CurvesNote for Figures 11-14:1. Bridgelux does not recommend driving high power LEDs at low currents. Doing so may produce unpredictable results. Pulse width modulation (PWM) is recommended for dimming effects.2. Characteristics shown for warm white based on 2700K.3. Characteristics shown for neutral white based on 4000K.4. Characteristics shown for cool white based on 5000K.5. For other color SKUs, the shift in color will vary. Please contact your Bridgelux Sales Representative for more information .Figure 10: Drive Current vs. Voltage (T sp =25°C)Figure 11: Typical Relative Luminous Flux vs. Drive Current (T sp =25°C)1Figure 12: Typical Relative Flux vs. Solder Point Temperature 2,3,4,5Figure 13: Typical ccx Shift vs. Solder Point Temperature 2,3,4,5Figure 14: Typical ccy Shift vs. Solder Point Temperature 2,3,4,50204060801001207.98.18.38.58.78.99.19.3F o r w a r d C u r r e n t (m A )Forward Voltage (V)00.250.50.7511.2520406080100120R e l a t i v e L u m i n o u s F l u xForward Current (mA)0.850.8750.90.9250.950.97510255075100125R e l a t i v e L u m i n o u s F l u xSolder Point Temperature(℃)Warm White Neutral White Cool White-0.004-0.003-0.002-0.0010.0010.002255075100125c c x S h i f tSolder Point Temperature(℃)Warm White Neutral White Cool White-0.007-0.006-0.005-0.004-0.003-0.002-0.0010.0000.0010255075100125c c y S h i f tSolder Point Temperature(℃)Warm White Neutral White Cool WhiteTypical Radiation PatternFigure 15: Typical Spatial Radiation Pattern at 100mA, T sp =25°CFigure 16: Typical Polar Radiation Pattern at 100mA, T sp =25°CNotes for Figure 15:1. Typical viewing angle is 116⁰.2.The viewing angle is defined as the off axis angle from the centerline where luminous intensity (Iv) is ½ of the peak value.Mechanical Dimensions Figure 17: Drawing for SMD 2835Notes for Figure 17:1. Drawings are not to scale.2. Drawing dimensions are in millimeters.3. Unless otherwise specified, tolerances are ± 0.10mm.ReliabilityTable 9:Reliability Test Items and ConditionsNotes for Table 9:1. Measurements are performed after allowing the LEDs to return to room temperature2. Tsld : reflow soldering temperature; Ta: ambient temperatureFigure 18 : Reflow ProfileReflow CharacteristicsFigure 19 : Pick and PlaceNote for Figure 19:1. When using a pick and place machine, choose a nozzle that has a larger diameter than the LED’s emitting surface. Using a Pick-and-Place nozzle witha smaller diameter than the size of the LEDs emitting surface will cause damage and may also cause the LED to not illuminate.Is greater than LEDsemitting surfacePackagingFigure 20: Emitter Reel DrawingsNote for Figure 20:1. Drawings are not to scale. Drawing dimensions are in millimeters. Figure 21: Emitter Tape DrawingsNote for Figure 21:1. Drawings are not to scale. Drawing dimensions are in millimeters.PackagingFigure 22: SMD 2835 Packaging and LabelingNote for Figure 22:1. Drawings are not to scale.Design ResourcesDisclaimersPrecautionsPlease contact your Bridgelux sales representative for assistance.MINOR PRODUCT CHANGE POLICYThe rigorous qualification testing on products offered by Bridgelux provides performance assurance. Slight cosmetic changes that do not affect form, fit, or function may occur as Bridgelux continues product optimization.CAUTION: CHEMICAL EXPOSURE HAZARDExposure to some chemicals commonly used in luminaire manufacturing and assembly can cause damage to the LED emitter. Please consult Bridgelux Application Note AN51 for additional information.CAUTION: EYE SAFETYEye safety classification for the use of Bridgelux SMD LED emitter is in accordance with IECspecification EN62778: Application of IEC 62471 for the assessment of blue light hazard to light sources and luminaires are classified as Risk Group 1 when operat -ed at or below the maximum drive current. Please use appropriate precautions. It is important that employees working with LEDs are trained to use them safely.CAUTION: RISK OF BURNDo not touch the SMD LED emitter during operation. Allow the emitter to cool for a sufficient period of time before handling. The SMD LED emitter may reachelevated temperatures such that could burn skin when touched.CAUTIONCONTACT WITH LIGHT EMITTING SURFACE (LES) Avoid any contact with the LES. Do not touch the LES of the emitter or apply stress to the LES (yellow phosphor resin area). Contact may cause damage to the emitterOptics and reflectors must not be mounted in contact with the LES (yellow phosphor resin area).STANDARD TEST CONDITIONSUnless otherwise stated, LED emitter testing is performed at the nominal drive current.About Bridgelux: Bridging Light and Life ™© 2019 Bridgelux, Inc. Product specifications are subject to change without notice. Bridgelux and the Bridgelux stylized logo design are registered trademarks of Bridgelux, Inc. Thrive is a trademark of Bridgelux, Inc. All other trademarks are the property of their respective owners.46430 Fremont Boulevard Fremont, CA 94538 USA Tel (925) At Bridgelux, we help companies, industries and people experience the power and possibility of light. Since 2002, we’ve designed LED solutions that are high performing, energy efficient, cost effective and easy to integrate. Our focus is on light’s impact on human behavior, delivering products that create better environments, experiences and returns—both experiential and financial. And our patented technology drives new platforms for commercial and industrial luminaires.For more information about the company, please visit /Bridgelux /Bridgelux/company/bridgelux-inc-_/user/Bridgelux WeChat ID: BridgeluxInChina。

LGS-8913-A1-PS-2.8

DMB-TH Demodulator ASICLGS-8913-A1“Kona-Digital”Preliminary Product SpecificationsSeptember 2006Revision 2.8This document contains information that is proprietary and confidential to Legend Silicon Corp. and is intended for the specific use of the recipient, for the purpose of evaluating or using Legend Silicon products. This document is provided to the recipient with the expressed understanding that the recipient will not divulge its contents to other parties or otherwise misappropriate the information contained herein.US Patents Pending. DMB-TH and The Legend Silicon logo are registered trademarks of Legend Silicon Corp.© 2006 Legend Silicon Corp. All rights reserved. All information is subject to change without notice.TABLE OF CONTENTS1. OVERVIEW (3)2. THEORY OF OPERATION (4)2.1 Summary (4)2.2 Block Diagram (4)2.3 Main DMB-TH Parameters (5)2.4 Framing Structure (5)2.5 Forward Error Correction (8)2.6 Guard Interval and PN Sequence (8)2.7 Time De-Interleaver Modes (9)2.8 Automatic Parameter Detection (9)3. PIN INFORMATION (10)3.1 Pin Map – Top View (10)3.2 Pin Table (11)4. FUNCTIONAL DESCRIPTION (13)4.1 I2C Interface (13)4.2 Tuner I2C Interface (14)4.3 Clock Management (15)4.4 ADC (16)4.5 IF Tuner Selection (17)4.6 BB Tuner Selection (17)4.7 AGC Tuner Interface (17)4.8 Time De-Interleaver Memory Interface (18)4.9 MPEG-2 Interface (18)4.10 Indicators (20)4.11 Power-Up Sequence (20)5. REGISTER DESCRIPTIONS (21)6. REGISTER SETTINGS & APPLICATION INFORMATION (32)6.1 Switching to Manual Mode after Auto-Detect is Complete (34)7 ELECTRICAL CHARACTERISTICS (35)7.1 Absolute Maximum Ratings (35)7.2 Thermal Data (35)7.3 DC Electrical Characteristics (36)7.4 SDRAM Interface Timing Characteristics (37)7.5 MPEG Interface Timing Characteristics (38)7.6 I2C Interface Characteristics (39)8. PACKAGE MECHANICAL DATA (40)9. PACKAGE HANDLING GUIDELINES (41)1. OVERVIEWThis LGS-8913-A1 is a single chip TDS-OFDM (Time Domain Synchronous – Orthogonal Frequency Division Multiplexing) demodulator. The demodulator is fully compliant with DMB-TH (Digital Multimedia Broadcasting – Terrestrial/Handheld) specifications and may be integrated into appropriate product designs such as television receivers or set top boxes. It uses a 1.8V core power supply. The device is also compatible with the China DTV standard, with minimal software intervention required (see Appendix for more details)The chip takes Digital IF or Dual Base-band IQ signal as an input, converts and then performs the necessary demodulation, and then provides an MPEG-2 transport stream output in parallel or serial format. With optional time de-interleaver memory, a complete DMB-TH RF to MPEG front-end can be designed.The following figure shows a typical receiver application using the LGS-8913-A1:KEY FEATURES• Optimized DMB-TH compliant single chip demodulator• Optimized for maximum signal resiliency in all conditions (impulse noise, echoes, fading, etc.)• Supports 64QAM, 16QAM and QPSK sub-carriers for both fixed and mobile applications• FEC rates of 0.4, 0.6, or 0.8 and guard intervals of 420 (1/9) and 945 (1/4) symbols • Time de-interleaving supported• MPEG-2 transport stream output in parallel or serial • Automatic parameter discovery & update• Integrated bit error rate and signal to noise monitoring • Full I2C bus support with up to eight addresses• 128 pin LQFP (20 mm x 14 mm x 1.4 mm)APPLICATIONS• Digital terrestrial set-top boxes and televisions for home reception of SD/HD TV and related services • Digital terrestrial receivers for mobile & portable reception of multimedia and related services2. THEORY OF OPERATION2.1 SummaryThe LGS-8913-A1 in digital mode uses an external terrestrial tuner which converts the analog VHF/UHF signal through an external 10-bit analog to digital ADC(s). The digital output(s) of the ADC(s) is sent to ASIC. Following conversion to base-band, TDS-OFDM demodulation is performed according to the DMB-TH specifications. The output of the channel estimation/correction block is sent to a time de-interleaver and then to the FEC. The output is a parallel or serial MPEG-2 transport stream including data valid, sync, and clock.LGS-8913 is a drop in replacement for LGS-8813 for boards designed to use Digital IF inputs.The main parameters may be detected and configured automatically or they may be set manually. The main configurable parameters are:• Sub-carrier demodulation: QPSK, 16QAM, or 64QAM• Forward error correction rate: 0.4,0.6, or 0.8• Guard interval: 420 (1/9) or 945 (1/4) symbols• Time de-interleaver: None or 720 symbols• Control frame detection• Channel bandwidth: 6, 7, or 8 MHz (manual set only)2.2 Block DiagramMPEG-2transportstream2.3 Main DMB-TH Parameters for China DTVPARAMETER SPECIFICATION NOTES DATAPayload format MPEG-2 transport stream 188 bytes per packetPayload rate formula (188 bytes * 8 bits/byte * N) /(frame length + guard interval) N = 2, 3, or 4 for 4QAM, 4, 6 or 8 for 16QAM, 6, 9 or 12 for 64QAMFORWARD ERROR CORRECTION - OUTERFormat BCH FORWARD ERROR CORRECTION – INNERLDPC (7493,3048 / 4752 / 6096)INTERLEAVING – INNERTime interleaving (inter-frame): transport stream data only Symbol-wise convolutional,branches = 52Tm 1: NoneTm 2: depth = 720 symbolsFrequency interleaving (intra-frame):transport stream data and control dataSymbol-wise block block size = 3780TRANSMISSION PARAMETER SIGNALING (TPS)TPS frequency each OFDM frameTPS length 72 bitsTPS modulation 4QAM 36 symbolsOFDM FRAME STRUCTURESymbols per frame 3780 3744 (FEC) + 36 (TPS)Frame length 666.67, 571.43, or 500 µs For 6, 7, or 8 MHzSub-carrier spacing 1.5, 1.75, or 2.0 kHz For 6, 7, or 8 MHzGuard interval duration 420 or 945 symbols(1/9 or 1/4 of 3780)Time = 1/9 or 1/4 of frame lengthSub-carrier modulation 4QAM, 16QAM, or 64QAM UniformRFChannel bandwidths 6 MHz, 7 MHz, or 8 MHzOccupied bandwidths 5.95 MHz, 6.95 MHz, or 7.94 MHzPulse shaping filter Square Root Raised Cosine alpha = 0.05Transmission network Single Frequency Network orMultiple Frequency Network2.4 Framing StructureDMB-TH signals are grouped in a series of hierarchical frames. The most basic element is the frame. In the frame there are 3744 symbols that carry the data and 36 symbols that carry the Transmission Parameter Signaling (TPS). The TPS carries information for the demodulator to automatically adapt to the incoming transmission such as: FEC inner code rate, time interleaver length, etc.In an 8 MHz channel, the 3780 sub-carriers are spaced at 2 kHz for a total occupied bandwidth of 7.56 MHz. In a 7 MHz channel, the 3780 sub-carriers are spaced at 1.75 kHz for a total occupied bandwidth of 6.615 MHz. And in a 6 MHz channel , the 3780 sub-carriers are spaced at 1.5 kHz for a total occupied bandwidth of 5.67 MHz.A signal frame consists of a frame plus a guard interval. The guard interval length can either be the frame length dividedby 9 (420 symbols) or the frame length divided by 4 (945 symbols). See section 2.7 for more on the guard interval.One Signal Frame6 MHz7 MHz8 MHzFrame length 666.67 µs 571.43µs 500µs420 symbol (1/9) guard interval length 74.07 µs 63.49µs 55.56µs945 symbol (1/4) guard interval length 166.67 µs 142.86µs 125µs Signal frame groups per second 6 7 8A super-frame duration is exactly one minute.An optional control frame can be added to each signal frame group. Each control frame consists of two 188 byte MPEG-2 packets with PID 0x17. The control frame is different from the rest of the signal frames in the signal frame group because it is always modulated with QPSK and FEC 0.4 without any interleaving, even if the rest of the signal frames are being sent in 16QAM or 64QAM. The control frame is always designated as frame zero.Channel Bandwidth 6 MHz 7 MHz 8 MHzControl frame payload 18,048 bps 21,056 bps 24,064 bpsChannel BandwidthGuardIntervalControlFrameSignal Frames perSuper Frame GroupSignal Frames perMinuteframe6 MHz 420 Yes 224 224*480*6/8No 225 225*480*6/8945 Yes 199 199*480*6/8No 200 200*480*6/87 MHz 420 Yes 224 224*480*7/8No 225 225*480*7/8945 Yes 199 199*480*7/8No 200 200*480*7/88 MHz 420 Yes 224 224*480No 225 225*480945Yes 199 199*480No 200 200*480Control frame packets are proposed to indicate the time slicing between T and H modes.Payload Data RatesSUB-CARRIER MODULATION FEC PAYLOADRATEMPEG packetsper minuteframe4QAM 0.4 1/4 945 125 µs 4,812,800 bps1/942055.56 µs 5,414,400 bps0.6 1/4 945 125 µs 7,219,200 bps1/942055.56 µs 8,121,600 bps0.8 1/4 945 125 µs 9,625,600 bps1/942055.56 µs 10,828,800 bps16 QAM 0.4 1/4 945 125 µs 9,625,600 bps1/942055.56 µs 10,828,800 bps0.6 1/4 945 125 µs 14,438,400 bps1/9 420 55.56 µs 16,243,200 bps0.8 1/4 945 125 µs 19,251,200 bps1/9 420 55.56 µs 21,657,600 bps64 QAM 0.4 1/4 945 125 µs 14,438,400 bps1/942055.56 µs 16,243,200 bps0.6 1/4 945 125 µs 21,657,600 bps1/9 420 55.56 µs 24,364,800 bps0.8 1/4 945 125 µs 28,876,800 bps1/942055.56 µs 32,486,400 bpsFor 8 MHz, the exact guard interval time for a guard interval of 420 is calculated by: 0.1 / (8 * 225) which rounds to 55.56 µs. For a guard interval of 945, the equation is: 0.2 / (8 * 200) which is 125 µs exactly.2.5 Forward Error CorrectionINNERThe inner FEC depends on three quasi-cyclic LDPC codes (QC-LDPC), LDPC(7493,3048); LDPC(7493,4752); andLDPC(7493,6096) corresponding to rates 0.4, 0.6 and 0.8OUTERBCH(762,752) is the shortened BCH code of BCH(1023,1013). The generator polynomial is x^10+x^3+1RANDOMIZERTDS-OFDM scrambles the payload with a pseudo-random binary sequence (PRBS or PN sequence) that is 32,767 symbols long (or PN-15). This is done in the modulator prior to the FEC encoding. In the demodulator, the PN-15 sequence is recovered and is used to decode the payload.2.6 Guard Interval and PN SequenceTraditionally, information on channel estimation and synchronization is mixed together with the payload but in TDS-OFDM this information is carried on a separate PN sequence and is transmitted separately in the guard interval.A PN-9 sequence is used, which is 511 symbols long and then repeats within the frame. Each successive frame gets a newstart value for the PN-9. There are two selectable guard interval lengths of 420 and 945, and the PN sequence fits into the guard intervals differently.The 420 guard interval contains the 255 bit PN sequence followed by 165 symbols of the same PN sequence repeated.4203780The 945 guard interval contains the 511 bit PN sequence followed by the same PN repeated as above.9453780While the payload can be expressed in the frequency domain as 3780 sub-carriers spaced 1.5, 1.75 or 2 kHz apart (respectively for 6, 7, or 8 MHz channel bandwidth), the guard interval information is only relevant in the time domain.From the frequency domain perspective, the guard interval has a flat spectrum within the occupied bandwidth.2.7 Time De-Interleaver ModesTime interleaving and de-interleaving also increases the resilience to spurious noise, and thus improves overall system performance in noisy environments. It requires the use of an external DRAM memory on the receiver.Symbol DepthMaxMemory(symbols)MaxDemodulatorMemory(bits)SignalFramesofDelayGUARDINTERVALRatio SymbolsTime Interleave &720 954,720 22,913,280 510 1/4 945 425 ms 364.29 ms 318.75 ms1/9 420 377.78 ms 323.81 ms 283.33 ms The delay in signal propagation caused by the symbol-wise convolutional time interleaving and de-interleaving is calculated by: B * (B-1) * M where B is the number of branches (52) and M is the depth. This delay includes the interleaving and de-interleaving times. If byte interleaving and de-interleaving is also on, then the delay values from section 2.8 must be added to the above numbers to get the total delay due to time and byte interleaving/de-interleaving.The amount of memory required to support the de-interleaving is equal to half of the depth. At maximum interleaving depth of 720, from the above table 954,720 symbols are required in memory and thus the delay will be twice that or 1,909,440 symbols. This is then divided by 3744 symbols per frame (TPS is not interleaved) to get 510 signal frames of delay.At its maximum time de-interleaving, the DMB-TH demodulator uses 954,720 symbols x 24 = 22,913,280 bits. External DRAM memory capable of supporting this interleaving size must be included with the demodulator ASIC if time de-interleaving is to be used. Note that if the modulator is using time interleaving, then the demodulator must use time de-interleaving. See Section 4.8 for implementing the time de-interleaving memory using external memory chips.2.8 Automatic Parameter DetectionWhen put into auto-detect mode, the demodulator automatically detects the following parameters:• Sub carrier modulation type: QPSK, 16QAM, 64QAM• Guard interval: 420 or 945 symbols• Control framesWhen put into auto-detect from TPS mode, the demodulator automatically detects the following parameters from the TPS:• FEC rate: 0.4, 0.6 and 0.8• Time interleaver mode: None or 720 symbols3. PIN INFORMATION 3.1 Pin Map – Top ViewLGS-8913-ES1M P E M P E M P M M M M M M M M T X V P L DGND VDD1.8AGC IFCLK IF0IF1IF2IF3IF4DGND VDD3.3IF5IF6IF7IF8IF9Q0Q1Q2Q3Q4Q5Q6Q7Q8Q93.2 Pin Table• All signal pins are 3.3V LVTTL compatible.• All input/output (IO) and output (O) pins can drive 4 mA, unless noted otherwise below.I2C Interface (see Sections 4.1 & 4.2)Pin #Name Type Description70 SCLI I2C clock71 SDAIOI2C data (open drain)66 SCLTOI2C clock pass-through for tuner67 SDATIOI2C data pass-through for tuner 24, 72, 73 CE_A2, CE_A1, CE_A0 I I2C address selection (3 bits) Clocks and Resets (see Section 4.3)Front End & Tuner Interface (see Sections 4.4 through 4.7)Pin #Name Type Description62 AGC O AGC output to tuner (PWM format)49, 50, 51, 52, 53, 56, 57, 58, 59, 60 IF9 – IF0 IIF input from ADC –or- I input from ADC inBaseband mode39, 40, 41, 42, 43, 44, 45, 46, 47, 48 Q9-Q0 IDrive to constant value in IF mode –or-Q input from ADC in baseband mode61 IFCLK I IF clk @ 30.4 Mhz Time De-Interleaver Memory Interface (see Section 4.8)(The pin ordering is optimized to facilitate trace routing to the SDRAM)MPEG Interface (see Section 4.9)Pin #Name Type Description6, 7, 10, 11,12, 15, 16, 17 MPEG_D7 –MPEG_D0OMPEG data outputs(8 bits, D7 is MSB)5 MPEG_CLK O MPEG clock output4 MPEG_VALID O MPEG data valid signal3 MPEG_SYNC O MPEG sync signalTest Pins & Indicators (see Section 4.10)Pin #Name Type Description128 BLKERRN O LDPC Block error indicator, active low20 GPIO0O BCH Block error indicator, active low25 LOCK O Demodulator lock signal, active high65 IFTESTIReserved, connect to DGND through 4.7 kΩ resistor30 SM I Reserved, connect to DGND115 BIST I Reserved, connect to DGND29 TESTCLK I Reserved, connect to DGND26, 27 BP1, BP2 I To enable Digital clock conn, connect to VDD21, 22 GPIO1, GPIO2 O GPIO1 provides 30.4Mhz clk output; GPIO2 is Reserved, do not connect23 GPIO3IReserved, connect to DGND through 4.7 kΩ resistor Power and GroundPin #Name Type Description8, 18, 54, 68, 81, 94, 103, 124 VDD3.3 Supply3.3V power for digital I/O(8 pins)1, 13, 31, 63, 74, 88, 98, 108, 119 VDD1.8 Supply1.8V power for digital core(9 pins)2, 9, 14, 19, 38, 55, 64, 69,75, 82, 89, 95, 99, 104, 109, 113, 114, 120, 125 DGND GroundDigital ground(19 pins)35 VCCXTAL1.8 Supply 1.8V analog oscillator supply 32 GNDXT Ground 1.8V analog oscillator ground36 PLLVDD1.8 Supply 1.8V analog PLL supply37 PLLGND Ground 1.8V analog PLL ground4. FUNCTIONAL DESCRIPTION4.1 I2C InterfaceThere are eight possible I2C slave addresses for each ASIC. Three bits of the address are selected by CE_A2, CE_A1 & CE_A0. Inside the chip, the registers are accessed in two different sections. Each section has its own I2C section address, but they share CE_A2, CE_A1 & CE_A0. The LSB of the address should be set to zero for writing and one for reading.Section1 & Section0 are hard-coded as: 01 for Demod, & 11 for Fec.Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0CE_A2 CE_A1 CE_A0 Section1 Section0 R/W*0 0For more details on the I2C specification, please visit the Philips website: /i2cWRITE OPERATION – SINGLE BYTEA normal single-byte write operation using I2C control is done by:I2C start condition, with clock hi make data go hi→lo I2C_Start ‘generatean WriteByte (section_write_address) ‘ write the byte “section_write_address” (LSB is zero)GetACK ‘ check that I2C data line is pulled low, signals transfer OKWriteByte (register_address) ‘ write the byte “register_address” with the desired registerGetACKWriteByte (write_data) ‘ write the byte “write_data” with the desired dataGetACKI2C stop condition, with clock hi make data go lo→hian I2C_Stop ‘generateREAD OPERATION – SINGLE BYTEA normal single-byte read operation using I2C control is done by:I2C_StartWriteByte (section_write_address)GetACKWriteByte (register_address)GetACKI2C_StopI2C_StartWriteByte (section_read_address) ‘ write the byte “section_read_address” (LSB is one)GetACKReadByte (read_data) ‘ read the desired data into “read_data”I2C_StopWRITE OPERATION – MULTIPLE BYTESMultiple bytes can be written into consecutive registers by using the following:I2C_Start ‘ generate an I2C start condition, with clock hi make data go hi→loWriteByte (section_write_address) ‘ write the byte “section_write_address” (LSB is zero)GetACK ‘ check that I2C data line is pulled low, signals transfer OKWriteByte (register_address) ‘ write the byte “register_address” with the desired registerGetACKWriteByte (write_data0) ‘ write the byte “write_data0” with the desired data, goes into “register_address”GetACKWriteByte (write_data1) ‘ write the byte “write_data1” with the desired data, goes into “register_address+1”GetACKWriteByte (write_data2) ‘ write the byte “write_data2” with the desired data, goes into “register_address+2”GetACKI2C_Stop ‘ generate an I2C stop condition, with clock hi make data go lo→hiCan continue as long as the register address is validREAD OPERATION – MULTIPLE BYTESMultiple bytes can be read from consecutive registers by using the following:I2C_StartWriteByte (section_write_address) ‘ write the byte “section_write_address” (LSB is zero)GetACKWriteByte (register_address)GetACKI2C_StopI2C_StartWriteByte (section_read_address) ‘ write the byte “section_read_address” (LSB is one)GetACKReadByte (read_data0) ‘ read the desired data from “register_address” into “read_data0”DoACK (0) ‘ send an ACK signal (pull SDA low)ReadByte (read_data1) ‘ read the desired data from “register_address+1” into “read_data1”DoACK (0)ReadByte (read_data2) ‘ read the desired data from “register_address+2” into “read_data2”I2C_StopCan continue as long as the register address is valid. Follow the last read with I2C_Stop.PULL-UP RESISTORSThe SCL, SDA, SCLT, and SDAT pins should each be pulled up to 3.3V with 4.7 kΩ resistors.4.2 Tuner I2C InterfaceIn order to isolate the tuner from a potentially noisy I2C bus, there are dedicated I2C lines between the demodulator and the tuner. The demodulator is connected to the main I2C bus on pins SDA and SDL. Rather than connect the main I2C bus to the tuner, the SDAT and SDLT lines should be connected between the demodulator and the tuner.The demodulator intercepts all I2C traffic, keeping the I2C noise from interfering with tuner performance. To write to or read from the tuner, the register 0x01 must be set prior to issuing the I2C command. The register must then be cleared after the communication with the tuner is complete.Example: read the tuner lock flag from a tuner with I2C address 0xC0:I2C_StartWriteByte (section_write_address)GetACKWriteByte (0x01) ‘ register address for the tuner I2C controlGetACKWriteByte (0xE0) ‘ turn on the tuner I2C bus and specify address 0xC0 for the tuner,subsequent I2C commands are echoed on the SDAT & SCLT pins GetACKI2C_StopI2C_StartWriteByte (0xC1) ‘ tuner read addressGetACKReadByte (locked) ‘ read the tuner data into “locked”I2C_StopI2C_StartWriteByte (section_write_address)GetACKWriteByte (0x01)GetACKWriteByte (0x00) ‘ now turn off the tuner I2C bus; SDAT & SCLT shut offGetACKI2C_Stop4.3 Clock ManagementIt is recommended that a 60.8 Mhz XO be connected to the XTALIN pin. If this is used, then the BP1, BP2 , pins#26, 27 external PLL and XTAL bypass pins need to be set high.Example 60.8 XO devices are M-tron () M3H16FCD-60.800Mhz 25ppmImproper usage of crystal with internal PLL may lead to lower performance, so use this mode after testing to see if performance is satisfied. In this mode an external parallel resonant crystal may be connected between XTALIN (pin 33) and XTALOUT (pin 34) with external 12 pF capacitors as shown, or an external clock may be forced onto the XTALIN pin. A 50 ppm or better crystal or clock source is recommended. Inside the ASIC, a 2x clock is generated for most of the digital logic. The ADC uses a 1x clock to sample the IF input. The value of the crystal depends on the desired channel bandwidth.Channel Bandwidth 7 MHz 8 MHzCrystal Fundamental Frequency 26.6 MHz 30.4 MHzSurface mount 26.6MHz and 30.4 MHz fundamental parallel resonant crystals are available from:Fox Electronics (): manufacturers part number: HC49SD 278-30.4-1 orM-tron (): manufacturer’s part number: ATSM49-30.4000MHz/12pf/fundThe TBD resistor is in case the oscillator has a start-up problem. The pads should be on the board in case the resistor is needed. Note the bypass caps are not to ground.XTALINXTALOUTFor 6 MHz operation, an external 45.6 MHz crystal oscillator (3.3V) should be connected directly to XTALIN (pin 33) with no capacitors or resistors. Available from SaRonix NCHA89A3-45.6000.GPIO1 (pin21) provides a 30.4Mhz output clock which can be connected to the CLK pin of an external ADC4.4 ADCUsing the IF inputs, the external 10 bit ADC samples the analog IF input at the crystal clock rate, or 30.4 MHz for an 8 MHz channel. Note that the input signal sampling will be non-coherent, and Nyquist’s theorem applies to the bandwidth of the signal, not the highest frequency. This is why a 30.4 MHz sample rate can be used on the tuner IF signal which is typically 36 MHz. Using the universal rule for noncoherent sampling, the total energy of the signal must be contained in a continuous spectrum of width W = (f H – f L), and a sampling frequency F S must be chosen so that the interval f L to f H falls within two adjacent harmonics of F S/2. With F S = 30.4 MHz, we can see below that the entire energy of the signal must fall between 30.4 MHz and 45.6 MHz. In all cases, the resultant baseband signal will have a center frequency determined bythe IF frequency minus the sampling frequency.nFs/2 = 30.4 MHz (n+1)Fs/2 = 45.6 MHzA tuner with a 36 MHz IF frequency will present all of its energy in the 8 MHz bandwidth from 32 MHz to 40 MHz, which falls well within the range above. The resultant baseband center frequency will be 36 MHz – 30.4 MHz = 5.6 MHz.For 7 MHz, the sampling frequency F S becomes 26.6 MHz, f L = 26.6 MHz, and f H = 39.9 MHz. A tuner with an IF frequency of 36 MHz will present all of its energy in the 7 MHz bandwidth from 32.5 MHz to 39.5 MHz. The resultant baseband center frequency will be 36 MHz – 26.6 MHz = 9.4 MHz.For 6 MHz, the sampling frequency F S is 45.6 MHz. Thus f L = 22.8 MHz and f H = 45.6 MHz. A tuner with an IF frequency of 36.125 MHz will present all of its energy in the 6 MHz bandwidth from 33.125 MHz to 39.125 MHz. The resultant baseband center frequency will be 36.125 MHz – 45.6 MHz = -9.475 MHz, which is an inverted spectrum signal centered at 9.475 MHz.4.5 IF Tuner SelectionThe following requirements should be observed when selecting a tuner for use with this demodulator:• Designed for digital terrestrial applications, such as DVB-T• VHF/UHF 75 Ω antenna input (with antenna loop through depending on the application) • Bandwidth set to 6, 7, or 8 MHz accordingly• Fixed IF output center frequency of 36 MHz (36.125 & 36.167 MHz also OK) • Differential output level of 1 V peak-to-peak into 1 k Ω load • For Can tuner: Has one or two internal SAW filters • Maximum noise figure of 8 dB• Has an internal RF AGC that requires no intervention, but uses an external input for the IF AGC control • Can be controlled via I 2C•Example tuners: Thomson DTT 7578 (vertical mount) or Thomson 7579 (horizontal mount) for 7 or 8 MHz or theThomson DTT 7581 for 6 MHz and Analog Devices Silicon Tuners.4.6 BB Tuner SelectionThe following requirements should be observed when selecting a Baseband Silicon tuner for use with this demodulator:• Designed for digital terrestrial applications, such as DVB-T • Bandwidth set to 6, 7, or 8 MHz accordingly• Differential output level of 1 V peak-to-peak into 1 k Ω load • Maximum noise figure of 8 dB• Has an internal RF AGC that requires no intervention, but uses an external input for the IF AGC control • Can be controlled via I 2C•Examples are tuners from ADI, Maxim ,Freescale and MicrotuneUsing Baseband Silicon tuners, there is a requirement for dual 10-bit external ADC.4.7 AGC Tuner InterfaceIn order to control the signal amplification from the tuner, a pulse width modulated (PWM) signal is presented on the output pin AGC (pin 62). By comparing the ADC input to a target AGC level (programmed by a set of registers), this signal increases when the demodulator determines that the tuner should provide more gain, and correspondingly decreases when the gain is too large. This pin should be connected to the AGC input of the tuner by using the following low pass filter circuit. The device does not support RFAGC, so the tuner’s RFAGC needs to be controlled seperatelyTuner external IF AGC inputDEMODULATORAGCThe following block diagram is an overview of the complete AGC circuit. See Section 5 for more detail on setting the AGC related registers.4.8 Time De-Interleaver Memory InterfaceAs described in Section 2.7, at its maximum time de-interleaving the demodulator uses 954,720 symbols x 24 = 22,913,280 bits. The data is broken up into 13 bit wide words in 1,909,400 locations in order to fit into 16 bit wide commercial DRAMs. A 2M x 16 external DRAM is thus required to support time de-interleaving. The memory must be capable of running at 100 MHz (access time < 10 ns).The 2M x 16 DRAM requirement can be satisfied using a 4M x 16 device available from the following manufacturers (less than $1.75 in volume):• Samsung: k4s641632f-tc75/tl75: 133 MHz• Micron: MT48LC4M16A2-7: 133 MHzWhen selecting a DRAM, be sure to enquire with the manufacturer about the end-of-life because these memories change frequently.4.9 MPEG-2 InterfaceThe demodulator provides a DVB common interface compliant bitstream in either parallel or serial format.PARALLEL OUTPUT (bit 0 of register C2 is set to zero)• The MPEG-2 transport stream data output is presented in parallel on the eight pins MPEG_D7 (MSB) to MPEG_D0 (LSB).• The MPEG_SYNC pin goes high during the first byte of each packet (0x47), and low otherwise.• The MPEG_VALID pin is high only when the data is valid, and low otherwise.• The MPEG_CLK pin presents the clock that should be used to latch the parallel data. The polarity of this signal can be switched by toggling bit 0 of register C2. By default, MPEG_CLK is gated with the MPEG_VALID signal internally so it shuts off when the data is not valid. This ensures compatibility in receiver designs that do not use the MPEG_VALID signal. It can be changed to a free running clock by setting bit 2 of register CE to one.SERIAL OUTPUT (bit 0 of register C2 is set to one)。

Motorola MR886、MR890和MR891数据手册说明书

/MR896-datasheet.html

Cross Reference Datasheet

/MR910-datasheet.html

Shortform IC and Component Datasheets (Plus Cross Reference Data)

1/9

Products Catalog Index

PART NO. MR910 MR910 MR911 MR911

MR911 MR911 MR911 MR911 MR912 MR912

MR912 MR912 MR912 MR912 MR914 MR914

MR914 MR914 MR914 MR914 MR916 MR916

Motorola Semiconductor Datasheet Library

/MR892-datasheet.html

The European Selection Data Book 1976

/MR892-datasheet.html

/MR894-datasheet.html

The European Selection Data Book 1976

/MR894-datasheet.html

Shortform IC and Component Datasheets (Plus Cross Reference Data)

Cross Reference Datasheet

/MR914-datasheet.html

Shortform IC and Component Datasheets (Plus Cross Reference Data)

/MR914-datasheet.html

European Master Selection Guide 1986

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。