使用FPGA和IP Core实现定制缓冲管理

fpga缓存数据的方法

fpga缓存数据的方法

在FPGA中,缓存数据的常用方法有以下几种:

1. 分布式RAM缓存:FPGA通常包含大量的分布式RAM资源,可以将数据存储在RAM中进行缓存。

这种方法通过编写硬件描述语言代码来实现,将数据存储在分布式RAM中,并通过适当的地址控制来读取和写入数据。

2. 块RAM缓存:除了分布式RAM,FPGA还通常包含一些较大的块RAM资源,这些块RAM通常具有更高的容量和性能。

可以将数据存储在块RAM中进行缓存。

与分布式RAM 不同,块RAM具有更高的带宽和更低的延迟。

3. FIFO缓存:FPGA中的FIFO(First-In-First-Out)模块可以用作数据缓存。

通过使用FIFO模块,可以实现数据的有序读取和写入,并且具有先进先出的特性。

FIFO模块通常用于数据的临时存储和数据流的调整。

4. 内部寄存器缓存:FPGA内部一般会有大量的可用寄存器资源,可以使用这些寄存器作为数据的缓存。

通过在逻辑电路中添加寄存器,可以实现数据的存储和缓存。

这种方法通常适用于较小的数据量和低延迟要求的应用。

需要注意的是,FPGA的缓存策略和实现方法会因具体应用和需求而有所不同。

选择合适的缓存方法需要综合考虑数据量、性能、延迟和资源利用等因素。

基于FPGA的PWM与定时计数器IP核的设计

基于FPGA的PWM与定时计数器IP核的设计前言PWM是脉冲宽度调制(Pulse Width Modulation)的简称,在自动控制系统和计算机技术领域都有非常广泛的应用。

在许多硬核式的嵌入式CPU中都有PWM和定时计数器模块的I/O 口供用户使用,在交流检测、电机控制等实际应用系统中,PWM是整个系统的技术核心,在嵌入式操作系统中定时计数器也是不可缺少的部分。

而在FPGA中的SOPC中,很多时候并没有提供这种模块供用户使用,因此设计出支持PWM输出的IP核具有很大的实用价值。

针对市场上使用的FPGA情况,本文所提出的IP功能实现是基于Altera公司的cyclone II芯片,该功能模块不仅可以作为独立的模块使用,而且可以嵌入到Altera公司提供的NIOS II处理器中,并通过NIOS II对该模块进行控制。

HDL语言是一种通用性很强的语言,因此这个模块具有很高的移植性,不仅可以用于大多数的Altera芯片,而且对于其它公司生产的FPGA芯片同样适用。

本设计中给出了模块与主系统的接口电路、功能逻辑电路以及外部输出端口。

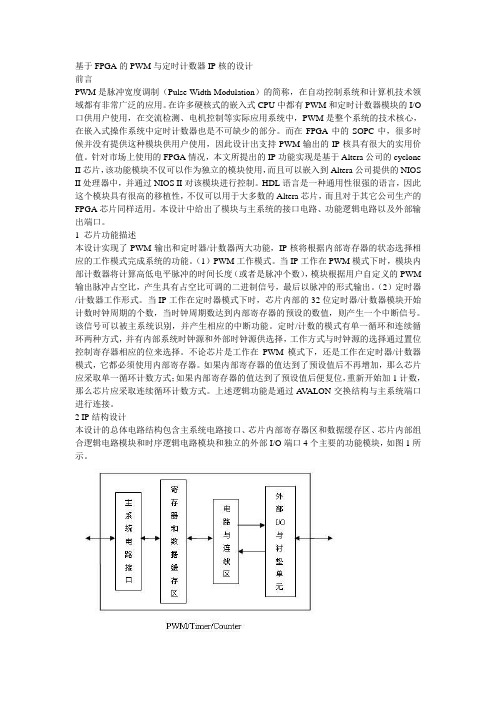

1 芯片功能描述本设计实现了PWM输出和定时器/计数器两大功能,IP核将根据内部寄存器的状态选择相应的工作模式完成系统的功能。

(1)PWM工作模式。

当IP工作在PWM模式下时,模块内部计数器将计算高低电平脉冲的时间长度(或者是脉冲个数),模块根据用户自定义的PWM 输出脉冲占空比,产生具有占空比可调的二进制信号,最后以脉冲的形式输出。

(2)定时器/计数器工作形式。

当IP工作在定时器模式下时,芯片内部的32位定时器/计数器模块开始计数时钟周期的个数,当时钟周期数达到内部寄存器的预设的数值,则产生一个中断信号。

该信号可以被主系统识别,并产生相应的中断功能。

定时/计数的模式有单一循环和连续循环两种方式,并有内部系统时钟源和外部时钟源供选择,工作方式与时钟源的选择通过置位控制寄存器相应的位来选择。

FPGA FFT_IP核函数的使用说明

FPGA FFT_IP核函数的使用说明一.基本性能特点:(1)采用基-4算法和基-4/2混合基算法;采用频域抽取方式(DIF)的FFT算法;(2)输入数据采用定点方式输入(输入数据为real、imag ,但没有exponent),在运算过程中采用块浮点方式进行运算,使用块浮点结构能够获得最大的SNR 和最少逻辑需求之间的平衡;输出采用指数形式输出(即包含real、imag、exponent),输出结果为:“数据”×(2^(-“指数”));(3)可以完成的FFT变换长度为2^m(6≤m≤14),即64~16384点;数据位宽为8~24bits;(4)如果输入的数据向量不够N点(FFT设置中的转换长度,例如:1024等),则FFT_IP核函数会在输入数据的后面自动进行补0填充,扩展成N点的数据。

(5)输入、输出数据采用有符号复数表示,都采用自然排序方式;(6)支持单倍输出(Signal-output)和四输出(Quad-output)引擎(engine);(7)多路I/O数据流模式:流(Streaming)、缓冲突发(Buffer Burst)、突发(Burst);(8)Version_2.1.0版本的FFT_IP核函数采用的是Atlantic Interface接口协议;Version_7.2版本的FFT_IP核韩式采用的是Avalon Streaming(ST) Interface接口协议。

(9)Version_2.1.0版本不支持RTL级Modelsim仿真,Version_7.2版本支持。

也就是说,2.1.0版本的FFT_IP核函数不能再自己新建的工程中通过QuartusII调用Modelsim进行RTL的仿真。

二.IP_Core的参量设置:(1)Twiddle Precision表示的是旋转因子的位宽精度;Data Precision表示的是输入、输出数据位宽精度。

注意:旋转因子的位宽精度必须小于或等于数据的位宽精度;(2)在Complex Multiplier Implementation选择栏中的Structure列表中选择期望的复数乘法器结构复数乘法器可以使用4个实数乘法器和2个加法/减法器完成,或使用3个乘法器、5个加法器和一些附加的延时单元完成。

fpga ip核设计流程

fpga ip核设计流程

FPGA IP核设计流程一般包括以下步骤:

1. 需求分析:明确IP核的设计要求和功能,为后续设计提供指导。

2. 架构设计:根据需求分析,设计IP核的架构,包括数据路径、控制逻辑、接口等。

3. 硬件描述语言编写:根据架构设计,使用硬件描述语言(如Verilog或VHDL)编写IP核的代码。

4. 仿真测试:使用仿真工具对IP核代码进行测试,确保其功能正确。

5. 综合:将硬件描述语言代码转化为FPGA上的逻辑门级网表,以便于布局布线。

6. 布局布线:将综合后的网表在FPGA上布局布线,生成配置文件。

7. 配置加载:将配置文件下载到FPGA中,进行实际测试验证。

8. 文档编写:编写IP核的使用手册和技术文档,便于用户使用和维护。

以上是FPGA IP核设计的基本流程,具体实现过程可能会因不同的设计需

求和工具而有所差异。

FPGA设计技巧与案例开发详解

FPGA设计技巧与案例开发详解FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,它可以根据用户的需求重新配置其内部的电路结构,从而实现不同的功能。

在FPGA设计中,有一些技巧和案例开发的经验可以帮助设计者提高设计效率和设计质量。

本文将详细介绍一些常用的FPGA设计技巧和案例开发的方法。

一、FPGA设计技巧1. 合理分配资源:FPGA拥有有限的资源,包括逻辑单元(LUTs)、寄存器、DSP(Digital Signal Processing)等。

在设计过程中,需要合理分配这些资源,以充分利用FPGA的性能。

可以通过对设计进行优化,如减少逻辑层数、使用更小的数据宽度等,来减少资源的使用。

2.使用IP核:FPGA提供了许多现成的IP核,如UART、SPI、I2C等。

使用这些IP核可以减少设计的复杂性,加快设计的速度。

同时,使用IP核还可以提高设计的可重用性,便于后续的维护和升级。

3.时序约束:FPGA设计中的时序是一个重要的考虑因素。

通过合理设置时序约束,可以确保时序要求的满足,避免出现时序失效的问题。

时序约束包括时钟频率、时钟延迟、数据到达时间等方面的要求。

4.时钟域划分:在FPGA设计中,会存在多个时钟域的情况。

为了确保时钟域之间的同步和数据的正确流动,需要进行时钟域划分。

可以使用时钟域划分器件(如时钟分频器、时钟锁相环等)来实现时钟域的划分和同步。

5.状态机设计:FPGA设计中经常会使用状态机来实现复杂的控制逻辑。

在状态机设计中,需要考虑状态的转移条件、状态的数量、状态的稳定性等因素。

合理设计状态机可以使设计更加简洁、高效。

1. UART通信:UART(Universal Asynchronous Receiver Transmitter)是一种常用的串行通信接口。

在FPGA设计中,可以使用UART实现FPGA与外部设备的通信。

具体实现过程包括接收和发送数据的时序控制、数据格式的解析等。

基于fpga的tdmoip方案设计与实现

基于fpga的tdmoip方案设计与实现一、tdmoip的介绍TDMOIP(Time Division Multiplexing Over IP)是一种基于H.Űã.A.V/IP的电话网络通信技术,它结合了TDM(时分复用)和IP技术,通过虚拟网络把传输的数据按一定的流程时序分享发送出去,具有一体化的特性。

TDMOIP的优势是它可以在传统TDM网络和IP网络间,提供一条简单可行的连接,满足各种多媒体业务的需要。

二、FPGA上TDMOIP基本实现原理TDMOIP在FPGA上的实现原理,就是在FPGA装入应用服务器所提供的一个IP核(IP Core)进行通信。

IP Core是一个可以处理各种网络服务的芯片,它综合了TCP、IP、UDP等多种传输协议,通过对网络封装数据的解析、传输和排序,完成通信双方之间的相互传送。

IP Core把信息封话以IP数据包传送,需要是把IP数据包里的信息提取出来,然后经过解析和排序,根据TDM方式进行复用,最后再以网络数据包传送给另外一方。

三、实现原理设计1、将网络相关设计模块加入FPGA系统中,包括以太网、以太太网MAC控制器、TWDT(Time Division Multiplexing Over IP)原语、以及Ethernet MACs 。

2、使用Time Division服务器技术为FPGA的网络功能提供基础支持,为网络应用提供便利。

3、使用FPGA作为IP核,在FPGA系统中实现TDMOIP。

4、建立所需要的网络通信模块,支持TCP/IP协议.5、建立网络解析和传输模块,实现对IP数据的解析和传输,并经过校验,确保信息的可靠性和安全性。

6、使用多种方式实现TDM复用功能,根据时序进行网络信息的多路传输和映射,同时处理多个传输流。

7、使用增强的网络调度模块,实现资源共享,以及设备状态和路径信息的管理。

四、FPGA实现TDMOIP步骤1、设置以太网头,实现网络IP数据包的传输和接收。

FPGA与CPLD应用案例

FPGA与CPLD应用案例FPGA(Field Programmable Gate Array)和CPLD(Complex Programmable Logic Device)是现代数字电路设计中常用的可编程逻辑设备。

它们的灵活性和适应性使得它们在各种应用场景中发挥重要作用。

本文将介绍FPGA和CPLD的工作原理,并通过具体的应用案例,说明它们在不同领域中的应用。

一、FPGA和CPLD的工作原理FPGA是由可编程逻辑单元和可编程连线网络组成的可编程电路芯片。

它的内部结构由大量的逻辑块组成,每个逻辑块包含查找表、触发器和多路选择器等元件。

通过在逻辑块之间建立连线,可以实现不同的逻辑功能。

FPGA的逻辑配置是通过存储在外部存储器中的配置位流(Configuration Bitstream)来实现的。

CPLD也是一种可编程逻辑器件,其结构相对简单,由AND/OR门和触发器构成。

CPLD的逻辑配置使用EEPROM(Electrically Erasable Programmable Read-Only Memory)存储,并且在启动时进行加载。

二、FPGA和CPLD的应用案例1. 通信领域FPGA和CPLD在通信领域中广泛应用。

例如,无线通信系统中的调制解调器模块可以使用FPGA来实现,通过对不同调制算法的配置,可以满足不同的通信标准。

CPLD也可以用于数据处理和时序控制等任务。

2. 图像处理FPGA和CPLD在图像处理领域也有广泛的应用。

通过FPGA的灵活性,可以实现各种图像处理算法,如边缘检测、滤波和图像压缩等。

CPLD可以用于时序控制,确保图像数据的正确传输和处理。

3. 工业自动化在工业自动化领域,FPGA和CPLD常被用于控制系统中。

通过FPGA实现的控制器可以满足实时性要求,同时支持多种输入输出接口,如模拟输入输出、数字输入输出和串行通信接口等。

CPLD则可用于实现各种精确的时序控制和逻辑判断。

fpga中ip核的作用

fpga中ip核的作用FPGA中IP核的作用在FPGA(Field-Programmable Gate Array)设计中,IP (Intellectual Property)核是一种预先设计好的模块,可以在FPGA 中进行复用。

它们是经过验证和优化的硬件功能模块,可以直接集成到FPGA设计中,以提供特定的功能和性能。

IP核在FPGA设计中起到了至关重要的作用。

它们可以加快设计开发过程,提高设计的可靠性和稳定性,同时降低功耗和成本。

下面将介绍IP核在FPGA设计中的几个主要作用。

1.功能扩展:IP核可以为FPGA设计提供各种功能扩展,例如数字信号处理(DSP)、存储控制器、通信接口、图像处理、加密解密等。

通过使用这些现成的IP核,设计者可以快速实现复杂的功能,减少设计周期。

2.性能优化:IP核经过了精心的设计和验证,可以提供高性能的硬件加速功能。

通过使用高效的IP核,设计者可以实现更高的运算速度和吞吐量,满足实时性要求,提高系统性能。

3.资源节约:IP核的复用性使得设计者可以避免重复开发相同的功能模块,节省了宝贵的设计资源和时间。

此外,由于IP核是经过验证和优化的,可以更好地利用FPGA的资源,减少功耗和成本。

4.可靠性保证:IP核经过了严格的验证和测试,可以提供高可靠性的功能模块。

设计者可以信赖这些经过验证的IP核,降低设计中的错误率,提高系统的可靠性。

5.易用性:IP核通常提供了友好的接口和文档,使得设计者可以方便地集成到FPGA设计中。

设计者只需要了解IP核的功能和接口,而无需深入了解底层的硬件实现细节。

然而,在使用IP核时也需要注意一些问题。

首先,IP核的质量和可靠性取决于供应商。

因此,在选择IP核时,设计者应该选择有良好声誉的供应商,并认真评估其性能和可靠性。

此外,由于IP核是现成的模块,可能无法完全满足特定的设计需求。

在这种情况下,设计者可能需要自行定制IP核,以满足特定的性能和功能要求。

FPGA设计的IP和算法应用

5.7 FPGA设计的IP和算法应用基于IP的设计已成为目前FPGA设计的主流方法之一,本章首先给出IP的定义,然后以FFT IP核为例,介绍赛灵思IP核的应用。

5.7.1 IP核综述IP(Intelligent Property) 核是具有知识产权核的集成电路芯核总称,是经过反复验证过的、具有特定功能的宏模块,与芯片制造工艺无关,可以移植到不同的半导体工艺中。

到了SOC 阶段,IP核设计已成为ASIC电路设计公司和FPGA提供商的重要任务,也是其实力体现。

对于FPGA 开发软件,其提供的IP核越丰富,用户的设计就越方便,其市场占用率就越高。

目前,IP核已经变成系统设计的基本单元,并作为独立设计成果被交换、转让和销售。

从IP核的提供方式上,通常将其分为软核、硬核和固核这3类。

从完成IP核所花费的成本来讲,硬核代价最大;从使用灵活性来讲,软核的可复用使用性最高。

( 这部分内容前面已经阐述,这里再重申一下)软核(Soft IP Core)软核在EDA设计领域指的是综合之前的寄存器传输级(RTL) 模型;具体在FPGA设计中指的是对电路的硬件语言描述,包括逻辑描述、网表和帮助文档等。

软核只经过功能仿真,需要经过综合以及布局布线才能使用。

其优点是灵活性高、可移植性强,允许用户自配置;缺点是对模块的预测性较低,在后续设计中存在发生错误的可能性,有一定的设计风险。

软核是IP 核应用最广泛的形式。

固核(Firm IP Core)固核在EDA设计领域指的是带有平面规划信息的网表;具体在FPGA设计中可以看做带有布局规划的软核,通常以RTL 代码和对应具体工艺网表的混合形式提供。

将RTL描述结合具体标准单元库进行综合优化设计,形成门级网表,再通过布局布线工具即可使用。

和软核相比,固核的设计灵活性稍差,但在可靠性上有较大提高。

目前,固核也是IP核的主流形式之一。

硬核(Hard IP Core)硬核在EDA 设计领域指经过验证的设计版图;具体在FPGA 设计中指布局和工艺固定、经过前端和后端验证的设计,设计人员不能对其修改。

基于FPGA的VHDL语言设计控制器SJA1000的IP软核设计

基于FPGA 的VHD1语言设计控制器SJA1000的IP 软核设计 分析了CAN 控制器SJA1ooO 的特点及CAN 协议通信格式。

设计了控制器SJA1OOO 的IP 软核,能为应用提供一个性能优良的、易于移植的控制器SJA1000,实现了对步进电机的控制。

控制局域网(CAN )属于现场总线的范畴,它是一种有效支持分布式控制或实时控制的串行通信网络。

与一般的通信总线相比,CAN 总线的数据通信可靠性、实时性和灵活性好,应用领域非常广泛,通常基于ARM 或51单片机,实现与CAN 控制器的通信联络。

与GA /SoPC 技术是实现嵌入式系统的最高形式,基于IP 软核的设计与应用也必将成为替代硬核的一种发展趋势。

凭借QUartUSI1和NiosII 工具,基于FPGA 的VHD1(或VeriIog )语言设计的IP 核能够提供灵活性和性能更好的控制器。

图1为一个基于FPGA 的控制器的CAN 总线节点。

其中PCA82C251是CAN 总线接收器,SJA1OOO 是CAN 总线通信控制器,PMM8713是驱动步进电机的脉冲分配器,FPGA 模块在节点模型中对SJAIooO 进行控制,并将接收到的帧信息进行处理,发送给脉冲分配器,以驱动步进电机。

在设计中采用自顶向下的设计方法。

通过分析SJΛ1000常用的控制芯片51单片机的功能,将其分为主要的4个模块:初始化模块、位查询模块、数据处理模块和缓冲区释放模块。

对SJA1000完成控制功能的过程用状态图描述如图2所示,这也是系统的主状态机。

4个状态对应上述的4个功能模块,首先在ini11a1_st-ate 完成对SJA1OOO 的初始化,在由init_end 值号给出初始化完成标志后,进入查询状态,即queerRBS 状态,由位看询模块完成此时对SJA1OO0的状态查询。

如果查询到SJA1OOo 缓冲区有帧信息,将qRBSend 置“1”,进入下一个状态frame_cope,即帧处理状态,此时由数据处理模块完成对缓冲区的数据读取,并作处理。

基于FPGA实现的减小DRAM延迟的Cache的设计

基于FPGA实现的减小DRAM延迟的Cache的设计[摘要] 本文的Cache是本人为网络安全加速卡NSA所设计的,它主要用来消除DRAM(Dynamic Random Access Memory)的延迟时间,加快系统运行速度.由于此项目是用FPGA实现的,所以本文采用FPGA内部的CAM(Content Addressable Memory)和RAM(Random Access Memory)来实现Cache以达到减小DRAM延迟的目的。

与传统Cache相比它简单容易实现、节省FPGA内部资源而且性能又不比传统Cache差。

它加快了数据的返回速度,提升了系统性能。

[关键词] CAM RAM Cache FPGA[Abstract] The Cache in this article is designed for the Network Security Accelerator card named NSA, which is mainly used to eliminate delay time of the DRAM (Dynamic Random Access Memory) and accelerate the system speed.This project is achieved with FPGA, so this paper uses CAM (Content Addressable Memory) and RAM (Random Access Memory) in FPGA to realize the Cache in order to implement the purpose of reducing the DRAM latency. Compared with the traditional Cache, it is simple and easy to comply, saving resources within the FPGA ,and the performance is not worse than traditional Cache. It not only accelerates the return speed of data, but also improves system performance.[Keywords] CAM RAM Cache FPGA一、绪论电子技术的飞速发展,CPU性能的不断提升,为Cache的产生奠定了基础,Cache从出现到现在已有将近30年的历史了。

Ethernet-IP核的设计和FPGA实现

Ethernet IP核的设计和FPGA实现随着网络通信技术和微电子技术的发展,日常生活中所遇到的设备的信息化和智能化不断加强。

而且,结构单一功能简单的设备已经不能满足使用者的需求。

这就使得设备的发展趋势朝着结构复杂化,功能多样化,高度集成化,高度智能化方向发展。

如今随着我国经济社会的发展,soc产品和嵌入式技术得到了广泛的推广和普及。

特别是随着国家提出物联网发展规划以来,Internet和消费电子的智能化迅速发展。

由此产生了嵌入式设备的联网问题。

本文就是基于这样的背景,采用Verilog HDL程序设计语言对Ethernet IP核进行编程设计,并以FPGA实现。

整个IP核的系统设计采用了Top-Down的设计思想。

在每个设计层次之上都可以把系统分为很多个功能模块,该层次的电路的硬件行为可以由这些功能模块来描述,同时下一层次的模块又描述这一层次的模块的行为。

整个设计过程使用Altera的工具软件Quartus II 13.0对Ethernet IP核各模块进行编译和综合,分析各模块的结构以及相互之间的关系,并采用ModelSim 10.1软件对部分模块进行功能仿真和功能分析,验证Ethernet IP核的功能。

关键词:嵌入式,物联网,Ethernet IP核,FPGA,Verilog HDL绪论在如今科学技术日新月异飞速发展的时代里,发展最快的领域当属电子科学与技术。

而在这一领域飞速发展的背后是以微电子技术为代表的半导体技术的快速发展来作为支撑和推动的。

尤其是随着微电子技术及其制造工艺的发展,使得芯片的集成度更高,设备的功能更加多样化。

这也就推动了各种消费电子,工业设备,环境监测仪器等的快速发展,如智能手机,平板电脑,车载导航仪,网络仪表,污染检测器等等。

这些设备都需要联网,也就都提出了连入网络的要求。

相对于嵌入式系统的RS232,RS485等串口通信接口相比,Ethernet技术更加普及通用,还能够连入Internet,具有明显的优势。

基于FPGA的IP Core设计

C r)和基 于物理 描述 并经 过工 艺验 证的 “ I oe” 硬 P内核(ad hr

85 2 3有 3个 独 立 的 计 数 器 . 每 个 计 数 器 有 6种 工 作 模 式 . 成 不 同 的 功 能 它 可 划 分 为 两 个 字 模 块 : 数 控 完 计 制 模 块 和 工 作 单 元 模 块 基 于 以 上 的 分 析 . 合 VH 结 DL语 言 的 特 点 , 着 简 洁 本

关键 词 : I P核 ; VHDL F GA ;P

中 图 分 类 号 :P 9 T 3

1 引 言

文献 标识 码 : A

文 章 编 号 :6 4 5 8 (0 10 - 1 1 0 17 - 7 7 2 1 )5 0 5 — 2

22 计 数 通 道 部 分 设 计 _

I( tl cH l rpr 1 核 模 块 是 一 种 预 先 设 计 好 PI e eta Po et 内 n l v

网表 . 可 以 进 行后 续 结 构 设 计 . 有 最 大 的 灵 活性 , 并 具 可

以很 容 易 地 借 助 于 E A 综 合 ¨ 与其 他外 部 逻 辑 电路 D T具 结合 成一 体 . 据 各种 不 同 的半 导体 工 艺 . 计成 不 同性 根 设 能 的器 件 本 文设 计 的 软 I P核 以 8 5 2 3的 工作 原 理 为依

的具 有某 种 确定 功能 的集 成 电路 、 件或 部 件l P内核 器 l l I

TSK51微处理器IP核在FPGA中的实现与应用

TSK51微处理器IP核在FPGA中的实现与应用MCS51是应用最广,了解的用户最多,使用最流行的8位单片机系列。

FPGA在复杂逻辑电路以及数字信号处理领域中扮演着越来越重要的角色,SOPC(片上系统)以其低功耗,高性能,低成本,高可靠性等优点成为嵌入式系统的发展趋势,随着大容量FPGA器件的使用,使得在一片FPGA芯片上可以定制MCU处理器和其它逻辑功能模块,从而缩短了开发周期,同时也提高了系统稳定性。

TSK51是ALTIUM公司Altium Designer6.9开发环境内部的一款8位处理器软核,本文介绍如何将其应用在Altera公司的CycloneII FPGA芯片上。

1 TSK51核功能特性TASK51内部采用了哈佛结构是一款高速、单片的微处理器内核,完全兼容了ASM51的指令集,并得到了KEIL C编译器的支持,其特性如下。

控制单元包含一个8位指令译码器;内部ALU单元支持8位算术译码器、支持8位逻辑运算、支持布尔类型运算、支持8位乘法运算、支持8位除法运算;提供了两个16位定时器/计数器;具有32位通用I/O 输入/输出端口(P0、P1、P2、P3);提供一个全双工串行接口;支持两个外部中断(INT0、INT1);具有五级内部中断源(ES、ET1、EX1、ET0、EX0);支持内部256字节数据存储空间;最大支持64KB外部程序寻址空间;最大支持64KB外部数据寻址空间;最大支持107个用户自定义特殊功能寄存器。

2 TSK51硬件模块表1列出了TSK51硬件模块主要引脚功能,在TSK51微处理器内核中所有端口定义均为单向输入/输出口,便于用户在复杂系统中的设计。

3 制作TSK51的RTL封装[2]为了方便在QuartusII中使用TSK51核,可以在Altium Designer6.9中将TSK51核综合成RTL封装文件.vqm。

(1)打开Altium Designer6.9,建立一个新的FPGA工程,在工程中加入原理图文件(Schematic),并保存工程文件和原理图文件。

fpga 封装三态门ip核注意事项

fpga 封装三态门ip核注意事项FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,可以通过用户自定义的逻辑电路来完成特定的功能。

在FPGA设计中,IP核(Intellectual Property Core)是一种可重复使用的逻辑模块,用于实现常见的功能模块。

本文将重点介绍在FPGA设计中封装三态门IP核的注意事项。

一、三态门的基本原理三态门是一种具有三种逻辑状态的逻辑门,包括高电平状态、低电平状态和高阻态。

在高电平状态下,输出端与输入端之间存在低电平的电平差;在低电平状态下,输出端与输入端之间存在高电平的电平差;而在高阻态下,输出端与输入端之间呈现高阻状态,相当于断开连接。

通过控制三态门的使能信号,可以实现输入输出之间的连接与断开。

二、封装三态门的IP核的目的在FPGA设计中,封装三态门的IP核有如下几个目的:1. 提高设计的可重用性:将常用的逻辑模块封装成IP核,可以在不同的设计中重复使用,提高开发效率。

2. 简化设计流程:使用IP核可以简化设计流程,减少设计人员的工作量,降低出错的概率。

3. 优化资源利用:通过使用IP核,可以在FPGA中选择性地实例化三态门,减少资源的占用,提高设计的性能和效率。

三、选择合适的三态门IP核在选择合适的三态门IP核时,需要考虑以下几个因素:1. 引脚数量和功能:不同的三态门IP核可能具有不同数量和功能的引脚,需要根据具体的设计需求选择合适的IP核。

2. 时钟频率:不同的三态门IP核可能支持不同的时钟频率,在设计中需要根据时钟频率要求选择合适的IP核。

3. IP核质量和可靠性:选择来自可靠厂商的高质量IP核,可以提高设计的可靠性和稳定性。

四、正确使用三态门IP核的方法在使用三态门IP核时,需要注意以下几个方面:1. 确定控制信号:在使用三态门IP核之前,需要确定好控制信号的来源和逻辑关系,确保能够正确地控制三态门的使能和禁止。

FPGA详细教程IP复用

FPGA详细教程IP复用

一、IP复用

1、什么是IP复用?

IP复用(IP Reuse)是一种芯片体系结构设计方法,它可以将特定功能需求的不同IP设计合并、组合和重用,以最大程度的提升系统效率、减少芯片设计和验证的时间和成本,一般采用IP复用的芯片系统都包括微处理器、片上存储器、外设接口、I/O等IP块组成,它能够提高芯片的集成度和性能,为客户提供更快捷方便的芯片设计方案。

2、IP复用的优势

(1)减少设计时间。

利用微处理器的IP复用,可以大大缩短芯片设计和验证的时间,有了IP复用,设计者可以把时间花在产品开发上,而不用将时间浪费在重复的设计上,从而提高效率。

(2)减少设计成本。

IP复用可以将电路原件的数量减少,减少了电路设计的成本,降低了相关维护的总成本,而且提高了系统的重用性,使得系统的可伸缩性得到提升,可以更好的满足不断变化的需求。

(3)减少代码量。

IP复用也可以减少自定义的代码量,通过使用已经存在的IP,减少新代码的编写,同时还可以改善系统代码的可编程性和可移植性,进一步提高系统性能。

(4)降低故障率。

fpga中ip核的作用

fpga中ip核的作用FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,它可以通过编程来实现不同的功能。

在FPGA中,IP核(Intellectual Property core)是一种可重用的模块,它可以被用来实现特定的功能,例如数字信号处理、图像处理、通信等。

IP核可以被看作是FPGA中的“黑盒子”,它可以被直接使用,而无需了解其内部实现细节。

IP核的作用在于简化FPGA设计的过程。

在FPGA设计中,通常需要实现一些常见的功能,例如乘法器、加法器、存储器等。

这些功能可以通过编写Verilog或VHDL代码来实现,但这需要设计者具备较高的技术水平。

而使用IP核,设计者可以直接将其插入到设计中,从而省去了编写代码的过程。

这不仅可以节省时间,还可以降低设计的难度和错误率。

另外,IP核还可以提高设计的可重用性。

在FPGA设计中,通常需要实现多个功能模块,这些模块可能会在不同的设计中被重复使用。

使用IP核,设计者可以将这些模块封装成IP核,从而方便在不同的设计中重复使用。

这不仅可以提高设计的效率,还可以降低设计的成本。

除了常见的功能模块,IP核还可以实现一些特定的功能。

例如,通信系统中常用的协议(如Ethernet、USB等)可以通过IP核来实现。

这些IP核通常由FPGA厂商或第三方开发商提供,设计者可以直接使用它们,从而简化设计过程。

总之,IP核是FPGA设计中不可或缺的一部分。

它可以简化设计过程,提高设计的可重用性,同时还可以实现一些特定的功能。

在FPGA设计中,设计者应该充分利用IP核,从而提高设计的效率和质量。

基于IP Core的FIR数字滤波器的FPGA实现

(c ol f l tcl n ie r g& Ifr ai ,A h i nvri f eh o g, nh n2 3 0 , hn ) Sh o o e r a E g ei E ci n n nom t n n u iesyo T c n ly Ma sa 4 0 2 C ia o U t o a

中 图分 类 号 : P 7 T 24 文 献 标 识 码 : B

F GA Re l ain o I Dii l i e a e n I r P ai t fF R gt l rB s d o P Coe z o aF t

XU i - h n ,ZHOU u - u , Jn s e g Ch n x e ZHAO n - i Co g y

域, 各大 F G P A器件厂商以及第三方都陆续推 出专门的数字信号处理 I( tl t r e y Crs使得基 PI ee u Po r ) o , n lc a p t l e 于 FG P A的数字信号处理 D PDga S n r e i ) S (it i a Po sn 系统的开发更加便捷 。 il gl c s g D P系统的开发通常包括建立 系统模型 、 S 设计实现 、 验证等步骤 , 作为基本 的 D P S 单元【基于 F G l 1 , P A的

号。使用 F A ol D To工具设计 F I 字滤波器 , 现有 的 I C r在 F G R数 利用 P oe P A器件上实现滤波 器设 计 , 助 Ci cp P 工具 验 借 h Soe r p o

证实现结果 。整个过程方便 、 快捷 ; 去伪 延迟控制器效果明显。 关键词 : 可编程逻辑 门陈列; 限冲击 响应 ;P核; 有 I 伪信号

FR数 字滤波器 系统 的开发 也不 例外 。文 中介绍使 用 Xl x 司提供 的 F G I in 公 i P A集 成开 发环境 IEr e S fh I 1

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

应用天地:通信电子

能 乱序 ,数据包 有大有小 ,经过 S G模 系 如 图 2 示 。 E 所 块 所 分 割成 的 数据 块 的数 目也 有 多 有

模块提 出写请 求 , 同时 更新P A 中的 R M

Fe i o to模块 t 在P RAM 中存 在 两种 链表 形式 , 内容 。 reLs c nrl 负责管理

为 了成本最低 、系统 最优化的 方案 ,一

S G模块为数据切 分块 ,根据交换 数据包类 型及优先级和端 口分配的带宽 E

般采 用 F GA来实现 ,TM 的常规结 构 网的数据结构要 求 ,在上交换 网的方 向 P 进行调 度 ,TM 流量整形 、QO S等功 能

通过调 度模块实现 。 C L — DI E L E T模块 完成输 出数据 的

通过 B A C nrl R M o to B 模块 中基于 包的数据结构 方面 L s需 要记 录数据 包的最后 一个 数据 块 度 器的调度结 果 , M i t

封装 , 由DRAM中读出的数据 封装后 把

发送 出去 。 在 T 中需 要基 于数据 服务策略对 M

于 不同服务等级 的数据 包进 行不 同的管

图 1T M的常规结构 图

理 策略 ,同时 要保证流 媒体的数据包不

今 E 电子 ・ 2 0 t 0 6年 1 月 1

维普资讯

成协议处理 , TM负责 完成队列调 度 、 缓 据 通道的抖 动 , 包含时 钟的抖动 ) 以控 冲管理模块 , 理 T 的缓 冲单 元 ,完 难 管 M 存管理 、流量 整形 、QO S等功能 ,T M 制 ,在 常规 情 况下 很 难 做到 很 高 的速 成 DRAM 的存取 操作 。外部 DRAM 的 与转 发协议 无关 。 率 。S I一 2 口为达到高速 率同时避 控制部分可 使用使用DD DRAM P P4 P 接 RS I

维普资讯

艘

地

德 子

使用F G 和I C r实现定制缓冲管理 P A oe P

A ea 司 Mak Wag h r公 r n

在 通信 网络 系统 中 . |管 理的核 心是 缓存 管理 。队到 管 流

上 负责把I 包或 数据包切分 为固定大小 P 的数据块 ,方便后期 的存储调度 以及 交 换 网的操 作处理 , E S G模块可 配合使 用 S I P I C r 来 实现 。 与S G模 P4 2 P oe E

Q it i o to模 t 少 ,这样就 必须有一套行 之有效的数据 P L s 代表 已经存储 的数据 包链表 。 空 闲地 址列表 ,提 供 Wr eC nrl

结 构 基 于 链表 的 方 地址 ,回 为方便 数据 读 出,P it Q L s 需要 记录 数 块的 写 B

e d C nrl Q M模块基于业务、数据流的方式管理 据 包 的第 一 个数 据 块 地 址 ,即首 指 针 收经R a o to 模块读出数据块后

队 列 ,包的管理 便 由 B 模块完成 。 M

R a oto模块根据调 P — t ,为方便新 的数 据写入 ,P 释敬的地址。 e d C nrl q Hp r Q

目前主流 的TM接 口均为 S I- 2 交换 网下来 的数据块重新组 合成 完整的 P4 P

En ne,协议 引擎 ) TM ( a fC 接 口形式 ,S I 一 2接 口信 号速率高 , I gi 和 Tr f i P4 P P包或数据包 。 Ma a e n ,流量管理 ) n g me t 。其 中 P E完 TCC ( h n e— o h n e s e 数 S C a n l t—c a n l k w, B B f rMa a e n ) 为缓 M( u e n g me t模块

随 着通信协 议的发 展及多样化 ,协 免 TCC 问题在 很多情况下都 对接收端 C r 现 。 S o e实 议 处理部分P 在硬 件转发 实现方面 , E 普 提 出了 DP 动态相 位调整) A( 的要 求。对 QM 模块 为队列管理 模块 ,负责 完

遍 采用 现有 的商用芯 片 NP( t r 于S I一 2 口形式 可直接采用 Al r 成端 口的数据队列 管理功能 ,接收 B Ne wo k P4 P 接 ta e M P o es r r c so ,网络处理 器) 完成 ,流量 公 司 的 I Co e实 现 。 Ale a的 主 流 模块读 写D 来 P r tr RAM时的数据 人队 、 出队请 管理部 分需要根据 系统 的需要进行 定制 FPGA 均 实 现 了 硬 件 DPA 功 能 , 以 求 ,TM 所能 支持的数据 流的数 目、业 tai I A的情 务类型 数 目、端 口的数 目等性能指标 在 或 采用商用 芯片来完成 。在很多情况下 S rtx I 器件为例 ,在使 能 DP

理和调度程序。 本文结合使用 FG P A及 I oe P C r阐述缓存管理的 结构 .I作原 理及 设计 方法

目前硬件高速转 发技术的趋势 是将 如 图 1 所示 。 整个转 发分成两 个部分 :P P o o o E( r t c l

块对应 的是 RS 模块 ,RS 模块将 从 M M

M NP芯片 、 TM芯片 、交换 网芯片无法 选 况下使 用 SP 4 I 一P2 P I C0 e可 实现 Q 模 块 处 体 现 出 来 。 r

用同一家厂 商的芯片 ,这时定制 T 成 1 G / 的接 口数据速率 。 M 6bs

S h d lr c e u e 模块为调 度模块 ,根 据