HC244中文资料

关于74HC244芯片的中文资料

电源电压Vcc 54 4.5 5 5.5 V

74 4.75 5 5.25

输入高电平电ViH 2 V

输入低电平电ViL 54 0.7 V

74 0.8

输出高电平电流IOH 54 -12 mA

74 -15

输出低电平电流IOL 54 12 mA

74 24

求关于74HC244线接收器(3S,两组控制)

简要说明:

244为三态输出的八组缓冲器和总线驱动器,其主要电器特性的典型值如下(不同厂家具体值有差别):

型号 tPLH tphl PD

54LS241/74LS241 12ns 12ns 110mW

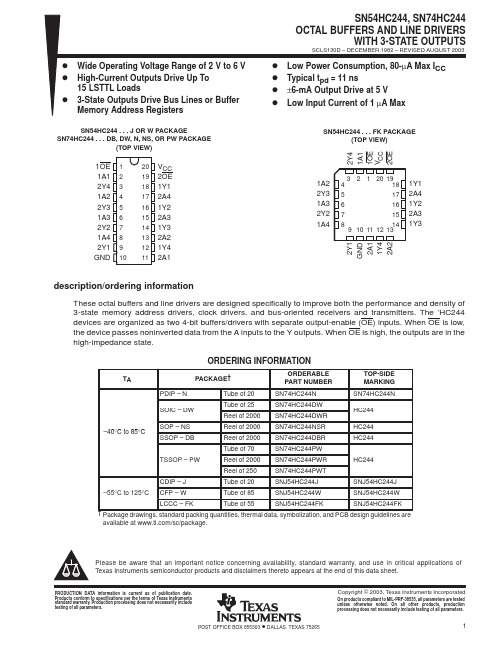

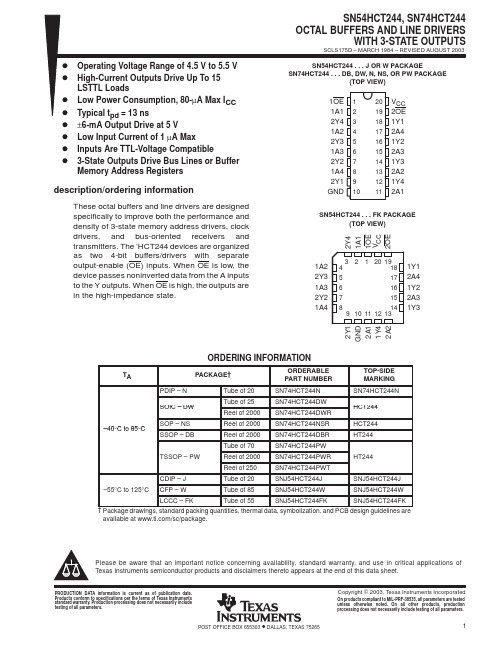

引出端符号:

1A1~1A4,2A1~2A4 输入端

/1G, /2G 三态允许端(低电平有效)

1Y1~1Y4,2Y1~2Y4 输出端

逻辑图:

双列直插封装

极限值:

电源电压 …………………………………………. 7V

输入电压 …………………………………………. 5.5V

tPHZ输出由高到高阻态禁止时间 Vcc=5V CL=5pF

RL=90 Ω 18 ns

tPLZ输出由低到高阻态禁止时间 25 ns

静态特性(TA为工作环境温度范围)

参 数 测 试 条 件【1】 LS244 单位

最小 最大

VIK输入嵌位电压 Vcc=最小,Iik=-18mA -1.5 V

输出高阻态时高电平电压 …………………………. 5.5V

工作环境温度

54XXX …………………………………. -55~125℃

74XXX …………………………………. 0~70℃

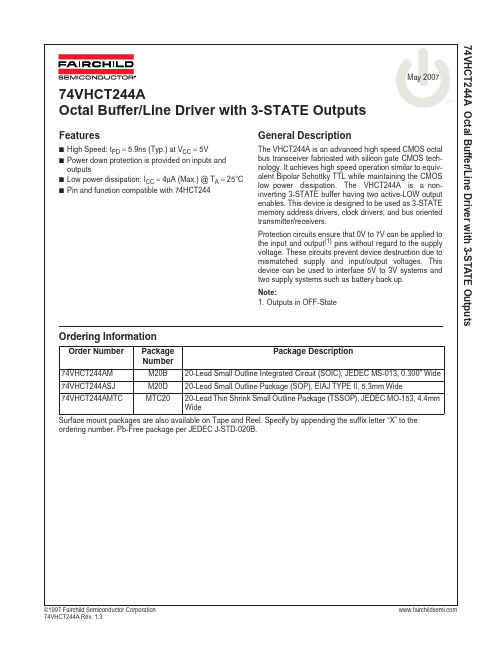

74AHCT244中文资料

TEST CONDITIONS

Tamb (°C)

SYMBOL PARAMETER

OTHER

25

−40 to +85 −40 to +125 UNIT

VCC (V)

MIN. TYP. MAX. MIN. MAX. MIN. MAX.

VIH

HIGH-level input

voltage

2.0

1.5 −

−

For TSSOP packages: above 60 °C the value of PD derates linearly with 5.5 mW/K.

1999 Sep 28

5

元器件交易网

Philips Semiconductors

Octal buffer/line driver; 3-state

CO

output capacitance

4.0 4.0 pF

CPD

power dissipation CL = 50 pF;

10

12

pF

capacitance

f = 1 MHz;

notes 1 and 2

Notes 1. CPD is used to determine the dynamic power dissipation (PD in µW).

IO

DC output source or sink current −0.5 V < VO < VCC + 0.5 V

ICC

DC VCC or GND current

Tstg

storage temperature range

PD

power dissipation per package for temperature range: −40 to +125 °C; note 2

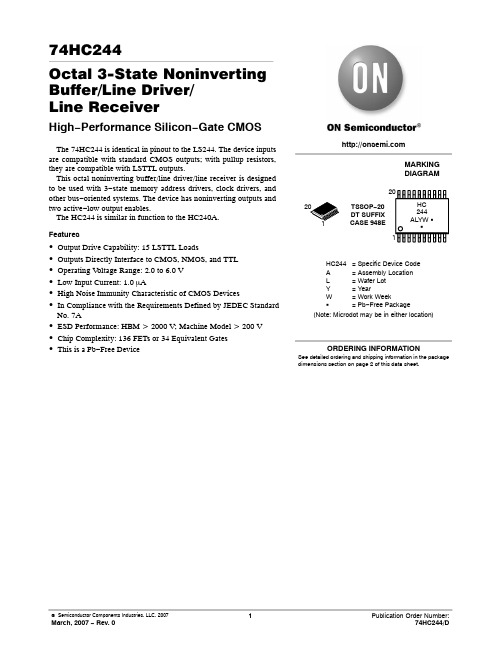

M74HC244B1R中文资料

M54HC240/241/244M74HC240/241/244October 1993HC240:INVERTED -HC241/244NON INVERTEDOCTAL BUS BUFFER WITH 3STATE OUTPUTS B1R(Plastic Package)ORDER CODES :M54HCXXXF1R M74HCXXXM1R M74HCXXXB1R M74HCXXXC1RF1R(Ceramic Package)M1R(Micro Package)C1R (Chip Carrier)PIN CONNECTION (top view).HIGH SPEEDt PD =10ns (TYP.)at V CC =5V .LOW POWER DISSIPATIONI CC =4µA (MAX.)at T A =25oC .HIGH NOISE IMMUNITYV NIH =V INL =28%V CC (MIN.).OUTPUT DRIVE CAPABILITY 15LSTTL LOADS.SYMMETRICAL OUTPUT IMPEDANCE |I OH |=I OL =6mA (MIN).BALANCED PROPAGATION DELAYS t PLH =t PHL.WIDE OPERATING VOLTAGE RANGE V CC (OPR)=2V to 6V.PIN AND FUNCTION COMPATIBLE WITH 54/74LS240/241/244DESCRIPTIONThe M54/74HC240,HC241and HC244are highspeed CMOS OCTAL BUS BUFFERs fabricated in silicon gate C 2MOS technology.They have the same high speed performance of LSTTL combined with true CMOS low power consumption.The designer has a choise of select combination of inverting and non-inverting outputs,symmetrical G (active low output control)input,and complementary G and G inputs.Each control inputgoverns four BUS BUFFERs.These devices are designed to be used with 3state memory address drivers,etc.All inputs are equipped with protection circuits against static discharge and transient excess voltage.HC244HC241HC2401/12CHIP CARRIERINPUT AND OUTPUT EQUIVALENT CIRCUIT PIN DESCRIPTION (HC240)PIN No SYMBOL NAME AND FUNCTION 11G Output Enable Input 2,4,6,81A1to 1A4Data Inputs 9,7,5,32Y1to 2Y4Data Outputs 11,13,15,172A1to 2A4Data Inputs 18,16,14,121Y1to 1Y4Data Outputs 192G Output Enabel Input 10GND Ground (0V)20V CCPositive Supply VoltagePIN DESCRIPTION (HC244)PIN No SYMBOL NAME AND FUNCTION 11G Output Enable Input 2,4,6,81A1to 1A4Data Inputs 9,7,5,32Y1to 2Y4Data Outputs 11,13,15,172A1to 2A4Data Inputs 18,16,14,121Y1to 1Y4Data Outputs 192G Output Enabel Input 10GND Ground (0V)20V CCPositive Supply VoltagePIN DESCRIPTION (HC241)PIN No SYMBOL NAME AND FUNCTION 11G Output Enable Input 2,4,6,81A1to 1A4Data Inputs 9,7,5,32Y1to 2Y4Data Outputs 11,13,15,172A1to 2A4Data Inputs 18,16,14,121Y1to 1Y4Data Outputs 192G Output Enabel Input 10GND Ground (0V)20V CCPositive Supply VoltageHC244HC241HC240M54/M74HC240/241/2442/12IEC LOGIC SYMBOLSTRUTH TABLEINPUTOUTPUTG G (HC241)An Yn (HC240)Yn (HC241)Yn (HC244)L H L H L L L HH LHHHLXZZZX:”H”or ”L”Z:High impeda nceCIRCUIT SCHEMATIC (1/8PACKAGE)HC244HC241HC240HC240HC241/244M54/M74HC240/241/2443/12ABSOLUTE MAXIMUM RATINGSSymbol Parameter Value Unit V CC Supply Voltage-0.5to+7V V I DC Input Voltage-0.5to V CC+0.5V V O DC Output Voltage-0.5to V CC+0.5VI IK DC Input Diode Current±20mAI OK DC Output Diode Current±20mAI O DC Output Source Sink Current Per Output Pin±35mAI CC or I GND DC V CC or Ground Current±70mAP D Power Dissipation500(*)mW T stg Storage Temperature-65to+150o C T L Lead Temperature(10sec)300o C Absolute Maximum Ratings are those values beyond whichdamage to the device may occu r.Functiona l ope ration und er these cond ition isnotimplied. (*)500mW:≅65o C derate to300mW by10mW/o C:65o C to85o CRECOMMENDED OPERATING CONDITIONSSymbol Parameter Value Unit V CC Supply Voltage2to6V V I Input Voltage0to V CC V V O Output Voltage0to V CC VT op Operating Temperature:M54HC SeriesM74HC Series -55to+125-40to+85o Co Ct r,t f Input Rise and Fall Time V CC=2V0to1000nsV CC=4.5V0to500V CC=6V0to400M54/M74HC240/241/2444/12DC SPECIFICATIONSSymbol ParameterTest Conditions ValueUnit V CC(V)T A=25o C54HC and74HC-40to85o C74HC-55to125o C54HCMin.Typ.Max.Min.Max.Min.Max.V IH High Level InputVoltage 2.0 1.5 1.5 1.5V 4.5 3.15 3.15 3.156.0 4.2 4.2 4.2V IL Low Level InputVoltage 2.00.50.50.5V 4.5 1.35 1.35 1.356.0 1.8 1.8 1.8V OH High LevelOutput Voltage 2.0V I=V IHorV ILI O=-20µA1.92.0 1.9 1.9V 4.5 4.4 4.5 4.4 4.46.0 5.9 6.0 5.9 5.94.5I O=-6.0mA 4.18 4.31 4.13 4.106.0I O=-7.8mA 5.68 5.8 5.63 5.60V OL Low Level OutputVoltage 2.0V I=V IHorV ILI O=20µA0.00.10.10.1V 4.50.00.10.10.16.00.00.10.10.14.5I O=6.0mA0.170.260.330.406.0I O=7.8mA0.180.260.330.40I I Input LeakageCurrent 6.0V I=V CC or GND±0.1±1±1µAI OZ3State OutputOff State Current 6.0V I=V IH or V ILV O=V CC or GND±0.5±5±10µAI CC Quiescent SupplyCurrent 6.0V I=V CC or GND44080µAM54/M74HC240/241/2445/12AC ELECTRICAL CHARACTERISTICS(C L=50pF,Input t r=t f=6ns)Symbol ParameterTest Conditions ValueUnit V CC(V)C L(pF)T A=25o C54HC and74HC-40to85o C74HC-55to125o C54HCMin.Typ.Max.Min.Max.Min.Max.t TLH t THL Output TransitionTime2.05025607590ns4.571219186.06101315t PLH t PHL PropagationDelay Time2.0503690115135ns4.5121823276.0101520232.015051130165195ns4.5172633396.014222833t PZL t PZH Output EnableTime2.050R L=1KΩ48125155190ns4.5162531386.0142126322.0150R L=1KΩ63165205250ns4.5213341506.018283543t PLZ t PHZ Output DisableTime2.050R L=1KΩ32125155190ns4.5152531386.014212632C IN Input Capacitance5101010pFC OUT OutputCapacitance 10pFC PD(*)Power DissipationCapacitanceHC240HC241/2443133pF(*)C PD is defined as the value of the IC’s internal equivalent capac itanc e which is calculated from the operating current con sump tion without load. (Refer to Test Circuit).Average operting current can be obtained by the following equ ation.I CC(opr)=C PD•V CC•f IN+I CC/8(per circuit)TEST CIRCUIT I CC(Opr.)HC240M54/M74HC240/241/2446/12M54/M74HC240/241/244 SWITCHING CHARACTERISTICS TEST CIRCUITHC240HC241/HC2447/12M54/M74HC240/241/244Plastic DIP20(0.25)MECHANICAL DATAmm inch DIM.MIN.TYP.MAX.MIN.TYP.MAX.a10.2540.010B 1.39 1.650.0550.065b0.450.018b10.250.010D25.4 1.000 E8.50.335e 2.540.100e322.860.900F7.10.280I 3.930.155L 3.30.130Z 1.340.053P001J 8/12M54/M74HC240/241/244 Ceramic DIP20MECHANICAL DATAmm inchDIM.MIN.TYP.MAX.MIN.TYP.MAX.A250.984B7.80.307D 3.30.130E0.5 1.780.0200.070e322.860.900F 2.29 2.790.0900.110G0.40.550.0160.022I 1.27 1.520.0500.060L0.220.310.0090.012M0.51 1.270.0200.050N14°(min.),15°(max.)P7.98.130.3110.320Q 5.710.225P057H9/12M54/M74HC240/241/244SO20MECHANICAL DATAmm inch DIM.MIN.TYP.MAX.MIN.TYP.MAX.A 2.650.104a10.100.200.0040.007 a2 2.450.096 b0.350.490.0130.019 b10.230.320.0090.012 C0.500.020c145°(typ.)D12.6013.000.4960.512 E10.0010.650.3930.419e 1.270.050e311.430.450F7.407.600.2910.299 L0.50 1.270.190.050 M0.750.029 S8°(max.)P013L 10/12M54/M74HC240/241/244PLCC20MECHANICAL DATAmm inchDIM.MIN.TYP.MAX.MIN.TYP.MAX.A9.7810.030.3850.395B8.899.040.3500.356D 4.2 4.570.1650.180d1 2.540.100d20.560.022E7.378.380.2900.330e 1.270.050e3 5.080.200F0.380.015G0.1010.004M 1.270.050M1 1.140.045P027A11/12M54/M74HC240/241/244Information furnished is believed to be accurate and reliable.However,SGS-THOMSON Microelectronics assumes no responsability for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may results from its use.No license is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics.Specificationsmentioned in this publication are subject to change without notice.This publication supersedes and replaces all information previously supplied.SGS-THOMSON Microelectronics products are not authorized for use ascritical components in life support devices or systems without express written approval of SGS-THOMSON Microelectonics.©1994SGS-THOMSON Microelectronics-All Rights ReservedSGS-THOMSON Microelectronics GROUP OF COMPANIESAustralia-Brazil-France-Germany-Hong Kong-Italy-Japan-Korea-Malaysia-Malta-Morocco-The Netherlands-Singapore-Spain-Sweden-Switzerland-Taiwan-Thailand-United Kingdom-U.S.A12/12。

MCS51单片机接口扩展HC377P0p2地址口HC244扩展技术研究

MCS51单片机接口扩展HC377P0p2地址口HC244扩展技术研究标签: P0 HC244 地址 MCS 接口扩展 p2 HC377 数据总线输出接口 Ram (浏览 17次 ID:1350040)MCS-51单片机P0口扩展技术研究在单片机家族的众多成员中,MCS-51系列单片机以其优越的性能、成熟的技术、高可靠性和高性价比,占领了工业测控和自动化工程应用的主要市场,并成为国内单片机应用领域中的主流机型。

MCS-51单片机的并行口有P0、P1、P2和P3,由于P0口是地址/数据总线口,P2口是高8位地址线,P3口具有第二功能,这样,真正可以作为双向I/O口应用的就只有P1口了。

这在大多数应用中是不够的,因此,大部分MCS-51单片机应用系统设计都不可避免的需要对P0口进行扩展。

由于MCS-51单片机的外部RAM和I/O口是统一编址的,因此,可以把单片机外部64K字节RAM空间的一部分作为扩展外围I/O口的地址空间。

这样,单片机就可以像访问外部RAM存储器单元那样访问外部的P0口接口芯片,以对P0口进行读/写操作。

用于P0口扩展的专用芯片很多。

如8255可编程并行P0口扩展芯片、8155可编程并行P0口扩展芯片等。

本文重点介绍采用具有三态缓冲的74HC244芯片和输出带锁存的74HC377芯片对P0口进行的并行扩展的具体方法。

1 输入接口的扩展MCS-51单片机的数据总线是一种公用总线,不能被独占使用,。

这就要求接在上面的芯片必须具备“三态”功能,因此扩展输入接口实际上就是要找一个能够用于控制且具备三态输出的芯片。

以便在输入设备被选通时,它能使输入设备的数据线和单片机的数据总线直接接通;。

而当输入设备没有被选通时,它又能隔离数据源和数据总线(即三态缓冲器为高阻抗状态)。

1.1 74HC244芯片的功能 74ls244 74hc244 pdf如果输入的数据可以保持比较长的时间(比如键盘),简单输入接口扩展通常使用的典型芯片为74HC244,由该芯片可构成三态数据缓冲器。

74VHC244MTCX资料

© 2005 Fairchild Semiconductor Corporation DS011522November 1992Revised April 200574VHC244 Octal Buffer/Line Driver with 3-STATE Outputs74VHC244Octal Buffer/Line Driver with 3-STATE OutputsGeneral DescriptionThe VHC244 is an advanced high speed CMOS octal bus buffer fabricated with silicon gate CMOS technology. It achieves high speed operation similar to equivalent Bipolar Schottky TTL while maintaining the CMOS low power dissi-pation. The VHC244 is a non-inverting 3-STATE buffer hav-ing two active-LOW output enables. These devices are designed to be used as 3-STATE memory address drivers,clock drivers, and bus oriented transmitter/receivers.An input protection circuit ensures that 0V to 7V can be applied to the input pins without regard to the supply volt-age. This device can be used to interface 5V to 3V systems and two supply systems such as battery back up. This cir-cuit prevents device destruction due to mismatched supply and input voltages.Featuress High Speed: t PD 3.9ns (typ) at V CC 5V s High noise immunity: V NIH V NIL 28% V CC (min)s Power down protection is provided on all inputs s Low noise: V OLP 0.6V (typ)s Low power dissipation: I CC 4 P A (max) @ T A 25q C s Pin and function compatible with 74HC244Ordering Code:Surface mount packages are also available on T ape and Reel. Specify by appending the suffix letter “X” to the ordering code.Pb-Free package per JEDEC J-STD-020B.Logic SymbolIEEE/IECConnection DiagramOrder Number Package NumberPackage Description74VHC244M M20B 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300" Wide 74VHC244SJ M20D Pb-Free 20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide74VHC244MTC MTC2020-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide 74VHC244NN20A20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide 274V H C 244Pin DescriptionsTruth TablesH HIGH Voltage Level L LOW Voltage Level I ImmaterialZ High ImpedancePin NamesDescriptionOE 1, OE 23-STATE Output Enable Inputs I 0–I 7InputsO 0–O 73-STATE OutputsInputsOutputsOE 1I n (Pins 12, 14, 16, 18)L L L L H H HXZ InputsOutputsOE 2I n (Pins 3, 5, 7, 9)L L L L H H HXZ74VHC244Absolute Maximum Ratings (Note 1)Recommended Operating Conditions (Note 2)Note 1: Absolute Maximum Ratings are values beyond which the devicemay be damaged or have its useful life impaired. The databook specifica-tions should be met, without exception, to ensure that the system design is reliable over its power supply, temperature, and output/input loading vari-ables. Fairchild does not recommend operation outside databook specifica-tions.Note 2: Unused inputs must be held HIGH or LOW. They may not float.DC Electrical CharacteristicsNoise CharacteristicsNote 3: Parameter guaranteed by design.Supply Voltage (V CC ) 0.5V to 7.0V DC Input Voltage (V IN ) 0.5V to 7.0V DC Output Voltage (V OUT ) 0.5V to V CC 0.5VInput Diode Current (I IK ) 20 mA Output Diode Current (I OK )r 20 mA DC Output Current (I OUT )r 25 mA DC V CC /GND Current (I CC )r 75 mAStorage Temperature (T STG ) 65q C to 150q CLead Temperature (T L )(Soldering, 10 seconds)260q CSupply Voltage (V CC ) 2.0V to 5.5VInput Voltage (V IN )0V to 5.5VOutput Voltage (V OUT )0V to V CCOperating Temperature (T OPR ) 40q C to 85q C Input Rise and Fall Time (t r , t f )V CC 3.3V r 0.3V 0 ns/V a 100 ns/V V CC 5.0V r 0.5V0 ns/V a 20 ns/VSymbol ParameterV CC T A 25q C T A 40q C to 85q C Units Conditions(V)Min TypMaxMin MaxV IH HIGH Level 2.0 1.5 1.5V Input Voltage 3.0 5.50.7 V CC0.7 V CCV IL LOW Level 2.00.50.5VInput Voltage 3.0 5.50.3 V CC0.3 V CC V OHHIGH Level 2.0 1.9 2.0 1.9V IN V IH I OH 50 P AOutput Voltage3.0 2.9 3.0 2.9Vor V IL4.5 4.4 4.54.43.0 2.58 2.48VI OH 4 mA 4.53.943.80I OH 8 mAV OLLOW Level 2.00.00.10.1V IN V IH I OL 50 P AOutput Voltage3.00.00.10.1V or V IL4.50.00.10.13.00.360.44V I OL 4 mA 4.50.360.44I OL 8 mAI OZ 3-STATE Output 5.5r 0.25r 2.5P AV IN V IH or V IL Off-State Current V OUT V CC or GND I IN Input Leakage Current 0 5.5r 0.1r 1.0P A V IN 5.5V or GND I CCQuiescent Supply Current5.54.040.0P AV IN V CC or GND Symbol ParameterV CC T A 25q C Units Conditions(V)Typ Limits V OLP Quiet Output Maximum 5.00.60.9VC L 50 pF(Note 3)Dynamic V OLV OLV Quiet Output Minimum 5.00.60.9VC L 50 pF(Note 3)Dynamic V OLV IHD Minimum HIGH Level 5.03.5VC L 50 pF(Note 3)Dynamic Input Voltage V ILD Maximum HIGH Level 5.01.5VC L 50 pF(Note 3)Dynamic Input Voltage 474V H C 244AC Electrical CharacteristicsNote 4: Parameter guaranteed by design. t OSLH |t PLHmax t PLHmin |; t OSHL |t PHLmax t PHLmin |.Note 5: C PD is defined as the value of the internal equivalent capacitance which is calculated from the operating current consumption without load. Average operating current can be obtained by the equation: I CC (OPR.) C PD * V CC * f IN I CC /8 (per bit).Symbol ParameterV CC T A 25q C T A 40q C to 85q C Units Conditions(V)MinTyp Max Min Max t PLH Propagation Delay 3.3 r 0.35.88.4 1.010.0ns C L 15 pF t PHLTime8.311.9 1.013.5C L 50 pF 5.0 r 0.53.9 5.5 1.0 6.5ns C L 15 pF 5.47.5 1.08.5C L 50 pF t PZL 3-STATE Output 3.3 r 0.3 6.610.6 1.012.5nsR L 1 k :C L 15 pF t PZHEnable Time9.114.1 1.016.0C L 50 pF 5.0 r 0.54.77.3 1.08.5ns C L 15 pF 6.29.3 1.010.5C L 50 pF t PLZ 3-STATE Output 3.3 r 0.310.314.0 1.016.0ns R L 1 k :C L 50 pF t PHZ Disable Time5.0 r 0.56.79.2 1.010.5C L 50 pF t OSLH Output to Output 3.3 r 0.3 1.5 1.5ns (Note 4)C L 50 pF t OSHL Skew5.0 r 0.51.0 1.0C L 50 pFC IN Input Capacitance 41010pF V CC Open C OUT Output Capacitance6pF V CC 5.0V C PDPower Dissipation Capacitance19pF(Note 5)74VHC244Physical Dimensions inches (millimeters) unless otherwise noted20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300" WidePackage Number M20B 674V H C 244Physical Dimensionsinches (millimeters) unless otherwise noted (Continued)Pb-Free 20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm WidePackage Number M20D 74VHC244Physical Dimensions inches (millimeters) unless otherwise noted (Continued)20-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm WidePackage Number MTC20874V H C 244 O c t a l B u f f e r /L i n e D r i v e r w i t h 3-S T A T E O u t p u t sPhysical Dimensions inches (millimeters) unless otherwise noted (Continued)20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" WidePackage Number N20AFairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.LIFE SUPPORT POLICYFAIRCHILD ’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:1.Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be rea-sonably expected to result in a significant injury to the user. 2. A critical component in any component of a life support device or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.。

ST 74VHC244 数据手册

1/12November 2004s HIGH SPEED: t PD = 3.9 ns (TYP.) at V CC = 5V sLOW POWER DISSIPATION:I CC = 4 µA (MAX.) at T A =25°C sHIGH NOISE IMMUNITY:V NIH = V NIL = 28% V CC (MIN.)s POWER DOWN PROTECTION ON INPUTS sSYMMETRICAL OUTPUT IMPEDANCE:|I OH | = I OL = 8 mA (MIN)sBALANCED PROPAGATION DELAYS:t PLH ≅ t PHLsOPERATING VOLTAGE RANGE:V CC (OPR) = 2V to 5.5VsPIN AND FUNCTION COMPATIBLE WITH 74 SERIES 244s IMPROVED LATCH-UP IMMUNITY sLOW NOISE: V OLP = 0.9V (MAX.)DESCRIPTIONThe 74VHC244 is an advanced high-speed CMOS OCTAL BUS BUFFER (3-STATE)fabricated with sub-micron silicon gate and double-layer metal wiring C 2MOS technology.G output enable governs four BUS BUFFERs.This device is designed to be used with 3 state memory address drivers, etc.Power down protection is provided on all inputs and 0 to 7V can be accepted on inputs with no regard to the supply voltage. This device can be used to interface 5V to 3V.All inputs and outputs are equipped with protection circuits against static discharge, giving them 2KV ESD immunity and transient excess voltage.74VHC244OCTAL BUS BUFFERWITH 3 STATE OUTPUTS (NON INVERTED)Figure 1: Pin Connection And IEC Logic SymbolsTable 1: Order CodesPACKAGE T & R SOP 74VHC244MTR TSSOP74VHC244TTR74VHC2442/12Figure 2: Input Equivalent CircuitTable 2: Pin DescriptionTable 3: Truth TableX : Don‘t CareZ : High ImpedanceTable 4: Absolute Maximum RatingsAbsolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions isnot impliedTable 5: Recommended Operating Conditions1) V IN from 30% to 70% of VCCPIN N°SYMBOL NAME AND FUNCTION 11G Output Enable Input 2, 4, 6, 81A1 to 1A4Data Inputs 9, 7, 5, 32Y1 to 2Y4Data Outputs 11, 13, 15,172A1 to 2A4Data Inputs 18, 16, 14,121Y1 to 1Y4Data Outputs192G Output Enable Input 10GND Ground (0V)20V CCPositive Supply VoltageINPUTSOUTPUTG An Yn L L L L H H HXZSymbol ParameterValue Unit V CC Supply Voltage -0.5 to +7.0V V I DC Input Voltage -0.5 to +7.0V V O DC Output Voltage -0.5 to V CC + 0.5V I IK DC Input Diode Current - 20mA I OK DC Output Diode Current ± 20mA I ODC Output Current± 25mA I CC or I GND DC V CC or Ground Current± 75mA T stgStorage Temperature -65 to +150°C T LLead Temperature (10 sec)300°CSymbol ParameterValue Unit V CC Supply Voltage 2 to 5.5V V I Input Voltage 0 to 5.5V V O Output Voltage 0 to V CC V T op Operating Temperature-55 to 125°C dt/dvInput Rise and Fall Time (note 1) (V CC = 3.3 ± 0.3V) (V CC = 5.0 ± 0.5V)0 to 1000 to 20ns/V74VHC2443/12Table 6: DC SpecificationsSymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.V IHHigh Level Input Voltage2.0 1.5 1.5 1.5V3.0 to 5.50.7V CC0.7V CC0.7V CCV ILLow Level Input Voltage2.00.50.50.5V3.0 to 5.50.3V CC0.3V CC0.3V CCV OHHigh Level Output Voltage2.0I O =-50 µA 1.9 2.0 1.9 1.9V3.0I O =-50 µA 2.9 3.0 2.9 2.94.5I O =-50 µA 4.4 4.54.4 4.43.0I O =-4 mA 2.58 2.48 2.44.5I O =-8 mA 3.943.83.7V OLLow Level Output Voltage2.0I O =50 µA 0.00.10.10.1V3.0I O =50 µA 0.00.10.10.14.5I O =50 µA 0.00.10.10.13.0I O =4 mA 0.360.440.554.5I O =8 mA 0.360.440.55I OZHigh Impedance Output Leakage Current5.5V I = V IH or V IL V O = V CC or GND ±0.25± 2.5± 2.5µA I I Input Leakage Current0 to 5.5V I = 5.5V or GND ± 0.1± 1± 1µA I CCQuiescent Supply Current5.5V I = V CC or GND44040µA74VHC2444/12Table 7: AC Electrical Characteristics (Input t r = t f = 3ns)(*) Voltage range is 3.3V ± 0.3V (**) Voltage range is 5.0V ± 0.5VNote 1: Parameter guaranteed by design. t soLH = |t pLHm - t pLHn |, t soHL = |t pHLm - t pHLn |Table 8: Capacitive Characteristics1) C PD is defined as the value of the IC’s internal equivalent capacitance which is calculated from the operating current consumption without load. (Refer to Test Circuit). Average operating current can be obtained by the following equation. I CC(opr) = C PD x V CC x f IN + I CC /8 (per circuit)SymbolParameterTest ConditionValue UnitV CC (V)C L (pF)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.t PLH t PHLPropagation Delay Time3.3(*)15 5.88.4 1.010.0 1.010.0ns 3.3(*)508.311.9 1.013.5 1.013.55.0(**)15 3.9 5.5 1.0 6.5 1.0 6.55.0(**)50 5.47.5 1.08.5 1.08.5t PZL t PZHOutput Enable Time3.3(*)15R L = 1K Ω 6.610.6 1.012.5 1.012.5ns 3.3(*)50R L = 1K Ω9.114.1 1.016.0 1.016.05.0(**)15R L = 1K Ω 4.77.3 1.08.5 1.08.55.0(**)50R L = 1K Ω 6.29.3 1.010.5 1.010.5t PLZ t PHZ Output Disable Time 3.3(*)50R L = 1K Ω10.314.0 1.016.0 1.016.0ns 5.0(**)50R L = 1K Ω6.79.2 1.010.5 1.010.5t OSLH t OSHL Output to Output Skew time (note 1)3.3(*)50 1.5 1.5 1.5ns 5.0(**)501.01.01.0SymbolParameterTest ConditionValue UnitT A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.C IN Input Capacitance 4101010pF C OUT OutputCapacitance6pF C PDPower Dissipation Capacitance (note 1)19pF74VHC2445/12Table 9: Dynamic Switching Characteristics1) Worst case package.2) Max number of outputs defined as (n). Data inputs are driven 0V to 5.0V, (n-1) outputs switching and one output at GND.3) Max number of data inputs (n) switching. (n-1) switching 0V to 5.0V. Inputs under test switching: 5.0V to threshold (V ILD ), 0V to threshold (V IHD ), f=1MHz.Table 10: Test CircuitC L =15/ 50pF or equivalent (includes jig and probe capacitance)R L = R 1 = 1K Ω or equivalentR T = Z OUT of pulse generator (typically 50Ω)SymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.V OLP Dynamic Low Voltage Quiet Output (note 1, 2) 5.0C L = 50 pF0.60.9VV OLV -0.9-0.6V IHD Dynamic High Voltage Input (note 1, 3) 5.0 3.5VV ILDDynamic Low Voltage Input (note 1, 3)5.0 1.5VTESTSWITCH tPLH , t PHL Open t PZL , t PLZ V CC t PZH , t PHZGND74VHC244Figure 3: Waveform - Propagation Delays (f=1MHz; 50% duty cycle)Figure 4: Waveform - Output Enable And Disable Time (f=1MHz; 50% duty cycle)6/1274VHC2447/12DIM.mm.inch MIN.TYPMAX.MIN.TYP.MAX.A 2.35 2.650.0930.104A10.10.300.0040.012B 0.330.510.0130.020C 0.230.320.0090.013D 12.6013.000.4960.512E 7.47.60.2910.299e 1.270.050H 10.0010.650.3940.419h 0.250.750.0100.030L 0.4 1.270.0160.050k 0°8°0°8°ddd0.1000.004SO-20 MECHANICAL DATA0016022D74VHC2448/12DIM.mm.inchMIN.TYPMAX.MIN.TYP.MAX.A 1.20.047A10.050.150.0020.0040.006A20.81 1.050.0310.0390.041b 0.190.300.0070.012c 0.090.200.0040.0079D 6.4 6.5 6.60.2520.2560.260E 6.2 6.4 6.60.2440.2520.260E1 4.34.4 4.480.1690.1730.176e 0.65 BSC0.0256 BSCK 0˚8˚0˚8˚L0.450.600.750.0180.0240.030TSSOP20 MECHANICAL DATAcEbA2AE1D1PIN 1 IDENTIFICATIONA1LK e0087225C74VHC244 Tape & Reel SO-20 MECHANICAL DATAmm.inchDIM.MIN.TYP MAX.MIN.TYP.MAX.A33012.992C12.813.20.5040.519D20.20.795N60 2.362T30.4 1.197Ao10.8110.4250.433Bo13.213.40.5200.528Ko 3.1 3.30.1220.130Po 3.9 4.10.1530.161P11.912.10.4680.4769/1274VHC244Tape & Reel TSSOP20 MECHANICAL DATAmm.inch DIM.MIN.TYP MAX.MIN.TYP.MAX.A33012.992 C12.813.20.5040.519 D20.20.795N60 2.362T22.40.882 Ao 6.870.2680.276 Bo 6.97.10.2720.280 Ko 1.7 1.90.0670.075 Po 3.9 4.10.1530.161 P11.912.10.4680.47610/1274VHC244 Table 11: Revision HistoryDate Revision Description of Changes 12-Nov-20043Order Codes Revision - pag. 1.11/1274VHC244Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.The ST logo is a registered trademark of STMicroelectronicsAll other names are the property of their respective owners© 2004 STMicroelectronics - All Rights ReservedSTMicroelectronics group of companiesAustralia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America12/12。

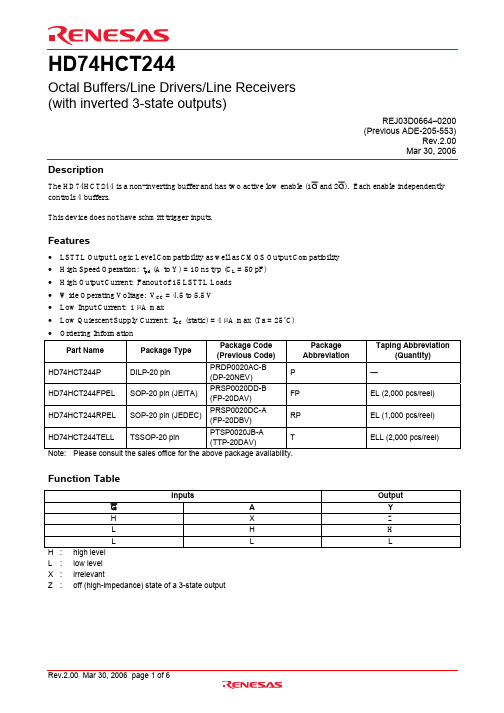

HD74HCT244FPEL中文资料

HD74HCT244Octal Buffers/Line Drivers/Line Receivers(with inverted 3-state outputs)REJ03D0664–0200(Previous ADE-205-553)Rev.2.00Mar 30, 2006 DescriptionThe HD74HCT244 is a non-inverting buffer and has two active low enable (1G and 2G). Each enable independently controls 4 buffers.This device does not have schmitt trigger inputs.Features• LSTTL Output Logic Level Compatibility as well as CMOS Output Compatibility• High Speed Operation: t pd (A to Y) = 10 ns typ (C L = 50 pF)• High Output Current: Fanout of 15 LSTTL Loads• Wide Operating Voltage: V CC = 4.5 to 5.5 V• Low Input Current: 1 µA max• Low Quiescent Supply Current: I CC (static) = 4 µA max (Ta = 25°C)• Ordering InformationPart Name Package TypePackage Code(Previous Code)PackageAbbreviationTaping Abbreviation(Quantity)HD74HCT244P DILP-20pin PRDP0020AC-B(DP-20NEV)P —HD74HCT244FPEL SOP-20 pin (JEITA) PRSP0020DD-B(FP-20DAV)FP EL (2,000 pcs/reel)HD74HCT244RPEL SOP-20 pin (JEDEC) PRSP0020DC-A(FP-20DBV)RP EL (1,000 pcs/reel)HD74HCT244TELL TSSOP-20pin PTSP0020JB-A(TTP-20DAV)T ELL (2,000 pcs/reel)Note: Please consult the sales office for the above package availability.Function TableInputs OutputG A YH X ZL H HL L LH : high levelL : low levelX : irrelevantZ : off (high-impedance) state of a 3-state outputPin ArrangementLogic DiagramAbsolute Maximum RatingsUnit Item SymbolRatingsSupply voltage range V CC–0.5 to 7.0 VInput / Output voltage V IN, V OUT–0.5 to V CC +0.5 VInput / Output diode current I IK, I OK±20 mA Output current I O±35 mAV CC, GND current I CC or I GND±75 mAmW Power dissipation P T 500Storage temperature Tstg –65 to +150 °CNote: The absolute maximum ratings are values, which must not individually be exceeded, and furthermore, no two of which may be realized at the same time.Recommended Operating ConditionsItem Symbol Ratings Unit ConditionsSupply voltage V CC 4.5 to 5.5 V Input / Output voltage V IN , V OUT 0 to V CC V Operating temperature Ta –40 to 85 °CInput rise / fall time *1t r , t f 0 to 500 ns V CC = 4.5 V Notes: 1. This item guarantees maximum limit when one input switches. Waveform: Refer to test circuit of switching characteristics.Electrical CharacteristicsTa = 25°C Ta = –40 to+85°CItem Symbol V CC (V)Min Typ Max Min MaxUnit Test ConditionsV IH4.5 to5.5 2.0 — — 2.0 — V Input voltage V IL 4.5 to 5.5 — — 0.8 — 0.8 V4.5 4.4 — — 4.4 — I OH = –20 µA V OH 4.5 4.18 — — 4.13 — V Vin = V IH or V IL I OH = –6 mA 4.5 — — 0.1 — 0.1 I OL = 20 µA Output voltageV OL4.5 — — 0.26 — 0.33 V Vin = V IH or V IL I OL = 6 mAOff-state output currentI OZ 5.5— — ±0.5 — ±5.0 µAVin = V IH or V IL ,Vout = V CC or GND Input currentIin 5.5 — — ±0.1 — ±1.0 µAVin = V CC or GNDQuiescent current I CC 5.5 — — 4.0 — 40 µAVin = V CC or GND, Iout = 0 µASwitching Characteristics(C L = 50 pF, Input t r = t f = 6 ns)Ta = 25°C Ta = –40 to +85°CItem Symbol V CC (V) Min Typ Max Min MaxUnit TestConditionst PHL 4.5 — 11 20 — 25 Propagation delay time t PLH 4.5 — 9 20 — 25nst ZL 4.5 — 13 30 — 38 Output enable time t ZH 4.5 — 12 30 — 38nst LZ 4.5 — 14 30 — 38 Output disable time t HZ 4.5 — 17 30 — 38nsOutput rise/fall time t TLH / t THL 4.5 — 4 12 — 15 ns Input capacitance Cin — — 5 10 — 10 pFTest CircuitWaveformsPackage Dimensions RENESAS SALES OFFICESRefer to "/en/network" for the latest and detailed information.Renesas Technology America, Inc.450 Holger Way, San Jose, CA 95134-1368, U.S.ATel: <1> (408) 382-7500, Fax: <1> (408) 382-7501Renesas Technology Europe LimitedDukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K.Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900Renesas Technology (Shanghai) Co., Ltd.Unit 204, 205, AZIACenter, No.1233 Lujiazui Ring Rd, Pudong District, Shanghai, China 200120Tel: <86> (21) 5877-1818, Fax: <86> (21) 6887-7898Renesas Technology Hong Kong Ltd.7th Floor, North Tower, World Finance Centre, Harbour City, 1 Canton Road, Tsimshatsui, Kowloon, Hong KongTel: <852> 2265-6688, Fax: <852> 2730-6071Renesas Technology Taiwan Co., Ltd.10th Floor, No.99, Fushing North Road, Taipei, TaiwanTel: <886> (2) 2715-2888, Fax: <886> (2) 2713-2999Renesas Technology Singapore Pte. Ltd.1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632Tel: <65> 6213-0200, Fax: <65> 6278-8001Renesas Technology Korea Co., Ltd.Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, KoreaTel: <82> (2) 796-3115, Fax: <82> (2) 796-2145Renesas Technology Malaysia Sdn. BhdUnit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jalan Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, MalaysiaTel: <603> 7955-9390, Fax: <603> 7955-9510© 2006. Renesas Technology Corp., All rights reserved. Printed in Japan.。

74HC244中文资料

-12

mA

74

-15

输出低电平电流IOL

54

12

mA

74

24

动态特性(TA=25℃)

参数

测试条件

LS244

单位

最大

tPLH输出由低到高传输延迟时间

Vcc =5V

CL=45pF

RL=667Ω

18

ns

tPHL输出由高到低传输延迟时间

18

ns

tPZH输出由高阻态到高允许时间

23

ns

tPZL输出由高阻态到低允许时间

/1G, /2G三态允许端(低电平有效)

1Y1~1Y4,2Y1~2Y4输出端

逻辑图:

双列直插封装

极限值:

电源电压………………………………………….7V

输入电压………………………………………….5.5V

输出高阻态时高电平电压………………………….5.5V

工作环境温度

54XXX………………………………….-55~125℃

1Y,2Y均为低电平

46

1Y,2Y均为高阻态

54

[1]:测试条件中的“最小”和“最大”用推荐工作条件中的相应值。

54/74LS244

三态八缓冲器/线驱动器/线接收器(3S,两组控制)

简要说明:

244为三态输出的八组缓冲器和总线驱动器,其主要电器特性的典型值如下(不同厂家具体值有差别):

型号

tPLH

tphl

PD

54LS241/74LS241

12ns

12ns

110mW

引出端符号:

1A1~1A4,2A1~2A4输入端

30

ns

tPHZ输出由高到高阻态禁止时间

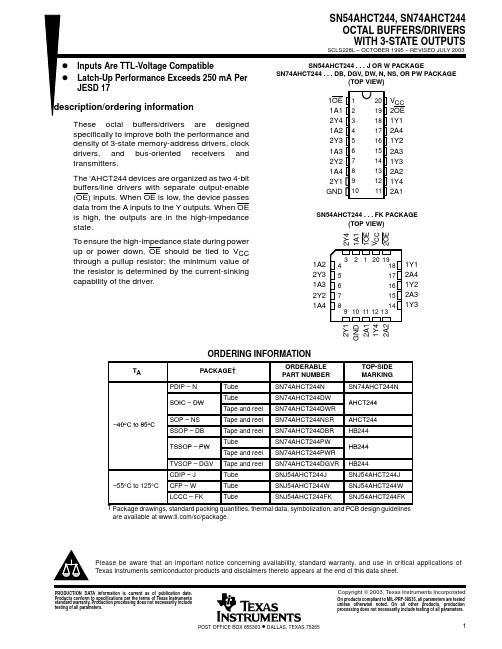

SN54AHCT244中文资料

PACKAGING INFORMATIONOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)5962-9678301Q2A ACTIVE LCCC FK201TBD Call TI Level-NC-NC-NC 5962-9678301QRA ACTIVE CDIP J201TBD Call TI Level-NC-NC-NC 5962-9678301QSA ACTIVE CFP W201TBD Call TI Level-NC-NC-NC SN74AHCT244DBLE OBSOLETE SSOP DB20TBD Call TI Call TISN74AHCT244DBR ACTIVE SSOP DB202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AHCT244DBRE4ACTIVE SSOP DB202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AHCT244DGVR ACTIVE TVSOP DGV202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AHCT244DGVRE4ACTIVE TVSOP DGV202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AHCT244DW ACTIVE SOIC DW2025Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AHCT244DWE4ACTIVE SOIC DW2025Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AHCT244DWR ACTIVE SOIC DW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AHCT244DWRE4ACTIVE SOIC DW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AHCT244N ACTIVE PDIP N2020Pb-Free(RoHS)CU NIPDAU Level-NC-NC-NCSN74AHCT244NE4ACTIVE PDIP N2020Pb-Free(RoHS)CU NIPDAU Level-NC-NC-NCSN74AHCT244NSR ACTIVE SO NS202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AHCT244NSRG4ACTIVE SO NS202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AHCT244PW ACTIVE TSSOP PW2070Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AHCT244PWE4ACTIVE TSSOP PW2070Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AHCT244PWLE OBSOLETE TSSOP PW20TBD Call TI Call TISN74AHCT244PWR ACTIVE TSSOP PW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AHCT244PWRE4ACTIVE TSSOP PW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AHCT244PWRG4ACTIVE TSSOP PW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SNJ54AHCT244FK ACTIVE LCCC FK201TBD Call TI Level-NC-NC-NC SNJ54AHCT244J ACTIVE CDIP J201TBD Call TI Level-NC-NC-NC SNJ54AHCT244W ACTIVE CFP W201TBD Call TI Level-NC-NC-NC (1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan-The planned eco-friendly classification:Pb-Free(RoHS)or Green(RoHS&no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free(RoHS):TI's terms"Lead-Free"or"Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all6substances,including the requirement that lead not exceed0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Green(RoHS&no Sb/Br):TI defines"Green"to mean Pb-Free(RoHS compatible),and free of Bromine(Br)and Antimony(Sb)based flame retardants(Br or Sb do not exceed0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.元器件交易网元器件交易网IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications,enhancements, improvements, and other changes to its products and services at any time and to discontinueany product or service without notice. Customers should obtain the latest relevant information before placingorders and should verify that such information is current and complete. All products are sold subject to TI’s termsand conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale inaccordance with TI’s standard warranty. T esting and other quality control techniques are used to the extent TIdeems necessary to support this warranty. Except where mandated by government requirements, testing of allparameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible fortheir products and applications using TI components. T o minimize the risks associated with customer productsand applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right,copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or processin which TI products or services are used. Information published by TI regarding third-party products or servicesdoes not constitute a license from TI to use such products or services or a warranty or endorsement thereof.Use of such information may require a license from a third party under the patents or other intellectual propertyof the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is withoutalteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproductionof this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable forsuch altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for thatproduct or service voids all express and any implied warranties for the associated TI product or service andis an unfair and deceptive business practice. TI is not responsible or liable for any such statements.Following are URLs where you can obtain information on other Texas Instruments products and applicationsolutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetworkMicrocontrollers Security /securityTelephony /telephonyVideo & Imaging /videoWireless /wirelessMailing Address:Texas InstrumentsPost Office Box 655303 Dallas, Texas 75265Copyright 2005, Texas Instruments Incorporated。

CD54HCT244中文资料

CD74HCT244M

-55 to 125

20 Ld SOIC

CD74HCT244M96

-55 to 125

20 Ld SOIC

NOTE: When ordering, use the entire part number. The suffixes 96 and R denote tape and reel. The suffix T denotes a small-quantity reel of 250.

DC Supply Voltage, VCC . . . . . . . . . . . . . . . . . . . . . . . . -0.5V to 7V DC Input Diode Current, IIK

For VI < -0.5V or VI > VCC + 0.5V . . . . . . . . . . . . . . . . . . . . . .±20mA DC Output Diode Current, IOK

1OE 1 1A0 2 2Y3 3 1A1 4 2Y2 5 1A2 6 2Y1 7 1A3 8 2Y0 9 GND 10

20 VCC VCC 19 2OE (241) 2OE (240, 244) 18 1Y0 1Y0 17 2A3 2A3 16 1Y1 1Y1 15 2A2 2A2 14 1Y2 1Y2 13 2A1 2A1 12 1Y3 1Y3 11 2A0 2A0

• Wide Operating Temperature Range . . . -55oC to 125oC

• Balanced Propagation Delay and Transition Times

• Significant Power Reduction Compared to LSTTL Logic ICs

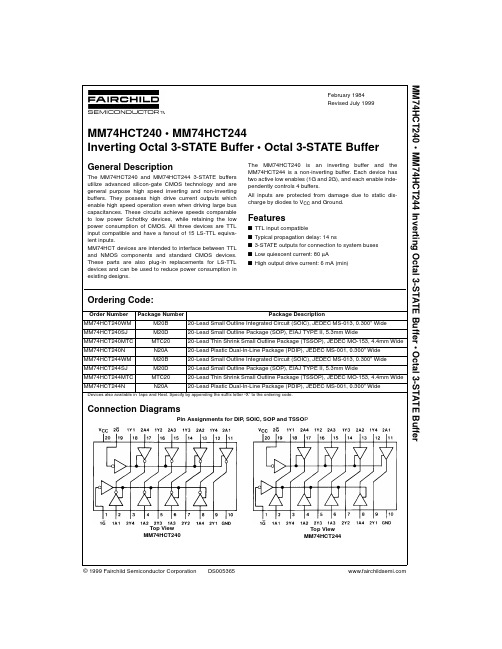

MM74HCT244中文资料

元器件交易网

February 1984 Revised July 1999

MM74HCT240 • MM74HCT244 Inverting Octal 3-STATE Buffer • Octal 3-STATE Buffer

Logic Diagrams

MM74HCT240

MM74HCT244 1G 1A 1Y 2G 2A 2Y LLLLLL L HH L HH HL ZHL Z HHZHHZ

MM74HCT244

2

MM74HCT240 • MM74HCT244

元器件交易网

|IOUT| = 6.0 mA, VCC = 4.5V

|IOUT| = 7.2 mA, VCC = 5.5V

VOL

Maximum LOW Level

VIN = VIH or VIL

Voltage

|IOUT| = 20 µA

|IOUT| = 6.0 mA, VCC = 4.5V

|IOUT| = 7.2 mA, VCC = 5.5V

Supply Current

IOUT = 0 µA

VIN = 2.4V or 0.5V (Note 4)

Note 4: Measured per input. All other inputs at VCC or GND.

TA = 25°C Typ

2.0

TA = −40 to 85°C TA = −55° to 125°C

(Note 3)

S.O. Package only

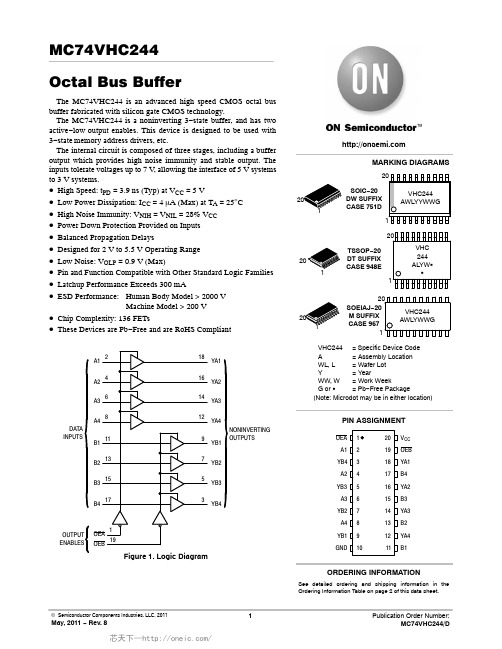

MC74VHC244DWR2G,MC74VHC244DT,MC74VHC244DTR2,MC74VHC244DWR2,MC74VHC244MELG, 规格书,Datasheet 资料

MC74VHC244Octal Bus BufferThe MC74VHC244 is an advanced high speed CMOS octal bus buffer fabricated with silicon gate CMOS technology.The MC74VHC244 is a noninverting 3−state buffer, and has two active −low output enables. This device is designed to be used with 3−state memory address drivers, etc.The internal circuit is composed of three stages, including a buffer output which provides high noise immunity and stable output. The inputs tolerate voltages up to 7 V , allowing the interface of 5 V systems to 3 V systems.•High Speed: t PD = 3.9 ns (Typ) at V CC = 5 V•Low Power Dissipation: I CC = 4 m A (Max) at T A = 25°C •High Noise Immunity: V NIH = V NIL = 28% V CC •Power Down Protection Provided on Inputs •Balanced Propagation Delays•Designed for 2 V to 5.5 V Operating Range •Low Noise: V OLP = 0.9 V (Max)•Pin and Function Compatible with Other Standard Logic Families •Latchup Performance Exceeds 300 mA•ESD Performance:Human Body Model > 2000 VMachine Model > 200 V•Chip Complexity: 136 FETs•These Devices are Pb −Free and are RoHS CompliantDATA INPUTSYB4YB3YB2YB1YA4YA3YA2YA1NONINVERTING OUTPUTSFigure 1. Logic Diagram201120MARKING DIAGRAMSSOIC −20DW SUFFIX CASE 751DTSSOP −20DT SUFFIX CASE 948ESOEIAJ −20M SUFFIX CASE 967VHC244AWLYWWGVHC244= Specific Device Code A = Assembly Location WL, L = Wafer Lot Y= Year WW, W = Work Week G or G = Pb −Free Package(Note: Microdot may be in either location)VHC 244ALYW G G A3A2YB4A1OEA GNDYB1A4YB2YB3YA2B4YA1OEB V CC B1YA4B2YA3B3PIN ASSIGNMENTORDERING INFORMATIONSee detailed ordering and shipping information in the Ordering Information Table on page 2 of this data sheet.FUNCTION TABLEINPUTS OUTPUTSOEA, OEB A, B YA, YBL L LL H HH X ZORDERING INFORMATIONDevice Package Shipping†MC74VHC244DW − OBSOLETE*SOIC−20 WB38 Units/RailMC74VHC244DWR2G SOIC−20 WB(Pb−Free)1000/T ape & ReelMC74VHC244DTG TSSOP−20(Pb−Free)75 Units/RailMC74VHC244DTR2G TSSOP−20(Pb−Free)2500/T ape & ReelMC74VHC244M − OBSOLETE*SOIC EIAJ−20(Pb−Free)1600 Units/BoxMC74VHC244MELG SOIC EIAJ−20(Pb−Free)2000/T ape & Reel*This device is obsolete, information available for reference.†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.MAXIMUM RATINGS (Note 1)Symbol Parameter Value UnitV CC Positive DC Supply Voltage−0.5 to +7.0VV IN Digital Input Voltage−0.5 to +7.0VV OUT DC Output Voltage−0.5 to V CC +0.5VI IK Input Diode Current−20mAI OK Output Diode Current$20mAI OUT DC Output Current, per Pin$25mAI CC DC Supply Current, V CC and GND Pins$75mAP D Power Dissipation in Still Air SOICTSSOP 500450mWT STG Storage Temperature Range−65 to +150°CV ESD ESD Withstand Voltage Human Body Model (Note 2)Machine Model (Note 3)Charged Device Model (Note 4)>2000>200>2000VI LATCHUP Latchup Performance Above V CC and Below GND at 125°C (Note 5)$300mAq JA Thermal Resistance, Junction−to−Ambient SOICTSSOP 96128°C/WStresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.1.V in and V out should be constrained to the range GND v (V in or V out) v V CC. Unused inputs must always be tied to an appropriate logic voltagelevel (e.g., either GND or V CC). Unused outputs must be left open.2.Tested to EIA/JESD22−A114−A3.Tested to EIA/JESD22−A115−A4.Tested to JESD22−C101−A5.Tested to EIA/JESD78RECOMMENDED OPERATING CONDITIONSSymbol Characteristics Min Max Unit V CC DC Supply Voltage 2.0 5.5V V IN DC Input Voltage0 5.5V V OUT DC Output Voltage0V CC V T A Operating Temperature Range, all Package Types−55125°Ct r, t f Input Rise or Fall Time V CC = 3.3 V + 0.3 VV CC = 5.0 V + 0.5 V 010020ns/VDEVICE JUNCTION TEMPERATURE VERSUS TIME TO 0.1% BOND FAILURESJunctionTemperature °C Time, Hours Time, Years 801,032,200117.890419,30047.9100178,70020.411079,6009.4 12037,000 4.2 13017,800 2.0 1408,900 1.011101001000TIME, YEARSNORMALIZEDFAILURERATEFigure 2. Failure Rate vs. Time Junction TemperatureDC CHARACTERISTICS (Voltages Referenced to GND)V CC T A = 25°C T A≤ 85°C−55°C ≤ T A≤ 125°C Symbol Parameter Condition(V)Min Typ Max Min Max Min Max UnitV IH Minimum High−LevelInput Voltage2.03.0 to5.51.5V CCX0.71.5V CCX0.71.5V CCX0.71.5V CCX0.7VV IL Maximum Low−LevelInput Voltage2.03.0 to5.50.5V CCX0.30.5V CCX0.30.5V CCX0.3VV OH Maximum High−LevelOutput Voltage V IN = V IH or V ILI OH = −50 m A2.03.04.51.92.94.42.03.04.51.92.94.41.92.94.4VV IN = V IH or V ILI OH = −4 mAI OH = −8 mA3.04.52.583.942.483.82.343.66V OL Maximum Low−LevelOutput Voltage V IN = V IH or V ILI OL = 50 m A2.03.04.50.00.00.00.10.10.10.10.10.10.10.10.1VV IN = V IH or V ILI OH = 4 mAI OH = 8 mA3.04.50.360.360.440.440.520.52I IN Input Leakage Current V IN = 5.5 V or GND0 to5.5±0.1±1.0±1.0m AI OZ Maximum 3−StateLeakage Current V IN = V IH or V ILV OUT = V CC or GND5.5±0.25±2.5±2.5m AI CC Maximum QuiescentSupply Current(per package)V IN = V CC or GND 5.5 4.040.040.0m AAC ELECTRICAL CHARACTERISTICS (Input t r = t f= 3.0 ns)Symbol Parameter Test ConditionsT A = 25°C T A3 85°C−55°C 3 T A3 125°CUnit Min Typ Max Min Max Min Maxt PLH, t PHL Maximum PropagationDelay, A to YA orB to YBV CC = 3.3 ± 0.3 V C L = 15 pFC L = 50 pF5.88.38.411.91.01.010.013.51.01.011.014.5nsV CC = 5.0 ± 0.5 V C L = 15 pFC L = 50 pF3.95.45.57.51.01.06.58.51.01.07.59.5t PZL, t PZH Output Enable TimeOEA to YA orOEB to YBV CC = 3.3 ± 0.3 V C L = 15 pFR L = 1 k W C L = 50 pF6.69.110.614.11.01.012.516.01.01.013.517.0nsV CC = 5.0 ± 0.5 V C L = 15 pFR L = 1 k W C L = 50 pF4.76.27.39.31.01.08.510.51.01.09.511.5t PLZ, t PHZ Output Disable TimeOEA to YA orOEB to YBV CC = 3.3 ± 0.3 V C L = 50 pFR L = 1 k W10.314.0 1.016.0 1.017.0nsV CC = 5.0 ± 0.5 V C L = 50 pFR L = 1 k W6.79.2 1.010.5 1.011.5t OSLH, t OSHL Output to Output Skew V CC = 3.3 ± 0.3 V C L = 50 pF(Note 6)1.5 1.5 1.5nsV CC = 5.0 ± 0.5 V C L = 50 pF(Note 6)1.0 1.0 1.5C in Maximum InputCapacitance4101010pFC out Maximum Three−StateOutput Capacitance(Output in High−ImpedanceState)6pFC PD Power Dissipation Capacitance (Note 7)Typical @ 25°C, V CC = 5.0VpF196.Parameter guaranteed by design. t OSLH = |t PLHm− t PLHn|, t OSHL = |t PHLm− t PHLn|.7.C PD is defined as the value of the internal equivalent capacitance which is calculated from the operating current consumption without load.Average operating current can be obtained by the equation: I CC(OPR) = C PD V CC f in + I CC/8 (per bit). C PD is used to determine the no−load dynamic power consumption; P D = C PD V CC2 f in + I CC V CC.NOISE CHARACTERISTICS (Input t r = t f = 3.0 ns, C L = 50 pF, V CC = 5.0 V)Symbol ParameterT A = 25°CUnit Typ MaxV OLP Quiet Output Maximum Dynamic V OL0.60.9V V OLV Quiet Output Minimum Dynamic V OL−0.6−0.9V V IHD Minimum High Level Dynamic Input Voltage 3.5V V ILD Maximum Low Level Dynamic Input Voltage 1.5VFigure 3. Switching Waveform Figure 4. Switching WaveformV CCGNDOEA or OEBYA or YBYA or YBV CCGNDHIGHIMPEDANCEHIGHIMPEDANCE*Includes all probe and jig capacitance C L *TEST POINTFigure 5. Test Circuit *Includes all probe and jig capacitanceTEST POINTFigure 6. Test CircuitCONNECT TO V CC WHEN TESTING t PLZ AND t PZL .CONNECT TO GND WHEN TESTING t PHZ AND t PZH .TEST CIRCUITSSWITCHING WAVEFORMSFigure 7. Input Equivalent CircuitINPUTSOIC−20 WB DW SUFFIX CASE 751D−05 ISSUE GM0.25SA SBTDIM MIN MAXMILLIMETERSA 2.35 2.65A10.100.25B0.350.49C0.230.32D12.6512.95E7.407.60e 1.27 BSCH10.0510.55h0.250.75L0.500.90q0 7NOTES:1.DIMENSIONS ARE IN MILLIMETERS.2.INTERPRET DIMENSIONS AND TOLERANCESPER ASME Y14.5M, 1994.3.DIMENSIONS D AND E DO NOT INCLUDE MOLDPROTRUSION.4.MAXIMUM MOLD PROTRUSION 0.15 PER SIDE.5.DIMENSION B DOES NOT INCLUDE DAMBARPROTRUSION. ALLOWABLE PROTRUSIONSHALL BE 0.13 TOTAL IN EXCESS OF BDIMENSION AT MAXIMUM MATERIALCONDITION.__TSSOP −20CASE 948E −02ISSUE CDIM A MIN MAX MIN MAX INCHES 6.600.260MILLIMETERS B 4.30 4.500.1690.177C 1.200.047D 0.050.150.0020.006F 0.500.750.0200.030G 0.65 BSC 0.026 BSCH 0.270.370.0110.015J 0.090.200.0040.008J10.090.160.0040.006K 0.190.300.0070.012K10.190.250.0070.010L 6.40 BSC 0.252 BSC M 0 8 0 8 ____NOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION:MILLIMETER.3.DIMENSION A DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE.4.DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.INTERLEAD FLASH OR PROTRUSIONSHALL NOT EXCEED 0.25 (0.010) PER SIDE.5.DIMENSION K DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08(0.003) TOTAL IN EXCESS OF THE K DIMENSION AT MAXIMUM MATERIAL CONDITION.6.TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY .7.DIMENSION A AND B ARE TO BE DETERMINED AT DATUM PLANE −W −.DETAIL E6.400.252------16X0.360.65PITCHSOLDERING FOOTPRINTSOEIAJ −20CASE 967−01ISSUE ADIM MIN MAX MIN MAX INCHES --- 2.05---0.081MILLIMETERS 0.050.200.0020.0080.350.500.0140.0200.150.250.0060.01012.3512.800.4860.5045.10 5.450.2010.2151.27 BSC 0.050 BSC 7.408.200.2910.3230.500.850.0200.0331.10 1.500.0430.0590 0.700.900.0280.035---0.81---0.032A 1H E Q 1L E _10 _0 _10 _NOTES: 1.DIMENSIONING AND TOLERANCING PER ANSIY14.5M, 1982. 2.CONTROLLING DIMENSION: MILLIMETER. 3.DIMENSIONS D AND E DO NOT INCLUDEMOLD FLASH OR PROTRUSIONS AND AREMEASURED AT THE PARTING LINE. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.15(0.006) PER SIDE. 4.TERMINAL NUMBERS ARE SHOWN FORREFERENCE ONLY. 5.THE LEAD WIDTH DIMENSION (b) DOES NOTINCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 (0.003)TOTAL IN EXCESS OF THE LEAD WIDTHDIMENSION AT MAXIMUM MATERIAL CONDITION.DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACEBETWEEN PROTRUSIONS AND ADJACENT LEAD TO BE 0.46 ( 0.018).DETAIL PA b c D E e L M ZON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

74HC244中文资料_数据手册_参数

*1'

2( < $ < $ < $ <

*1' $

DDH

7UDQVSDUHQWWRSYLHZ

(1) This is not a supply pin. The substrate is attached to this pad using conductive die attach material. There is no electrical or mechanical requirement to solder this pad. However, if it is soldered, the solder land should remain floating or be connected to GND.

- mA +150 C 500 mW

[1] For SO20 packages: Ptot derates linearly with 8 mW/K above 70 C. For SSOP20 and TSSOP20 packages: Ptot derates linearly with 5.5 mW/K above 60 C. For DHVQFN20 packages: above 60 C, Ptot derates linearly with 4.5 mW/K.

2. Features and benefits

Input levels: For 74HC244: CMOS level For 74HCT244: TTL level

Octal bus interface Non-inverting 3-state outputs Complies with JEDEC standard no. 7 A ESD protection:

AiP74HC244中文资料

新制/修订内容

新制

江苏省无锡市蠡园经济开发区滴翠路 100 号 9 栋 2 层

http://www.i-core. cn

邮编:214072

第 1 页 共 12 页 版本:2012-02-A1

表 733-11-I

无锡中微爱芯电子有限公司

Wuxi I-CORE Electronics Co., Ltd. 编号:AiP74HC244-AX-BJs Co., Ltd. 编号:AiP74HC244-AX-BJ-168

3、电特性

3.1、极限参数 (符合 IEC 60134 标准, GND=0)

参数名称

符号

条件

最小 最大 单位

电源电压

VCC

-0.5

+7.0

V

输入钳位电流

Ilk

VI<-0.5V orVI>Vcc+0.5V

最小 1.5 3.15 4.2 - - - 1.9 4.4 5.9 3.84 5.34 - - - -

典型 - - - - - - - - - - - - - - -

最大 - - - 0.5 1.35 1.8 - - - - - 0.1 0.1 0.1 0.33

单位 V V V V V V V V V V V V V V V

2.3、引脚说明

引脚 符 号

1

1 OE

2

1A0

3

2Y0

4

1A1

5

2Y2

6

1A2

7

2Y2

8

1A3

9

2Y3

10

GND

2.4、真值表 控制

n OE

L

i-core 图2、引脚排列图

74VHCT244AMX中文资料

元器件交易网74VHCT244A Octal Buffer/Line Driver with 3-STATE Outputs74VHCT244A Octal Buffer/Line Driver with 3-STATE OutputsConnection DiagramPin DescriptionLogic SymbolTruth TablesH = HIGH Voltage Level L = LOW Voltage Level Z = High ImpedancePin NamesDescriptionOE 1 , OE 2 3-STATE Output Enable InputsI 0 –I 7 InputsO 0 –O 73-STATE OutputsInputs Outputs(Pins 12, 14, 16, 18)OE 1I nL L L L H H HXZInputs Outputs (Pins 3, 5, 7, 9)OE 2I nL L L L H H HXZ元器件交易网74VHCT244A Octal Buffer/Line Driver with 3-STATE OutputsAbsolute Maximum RatingsStresses exceeding the absolute maximum ratings may damage the device. The device may not function or beoperable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.Recommended Operating Conditions (5)The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to absolute maximum ratings.Notes:2.HIGH or LOW state. I OUT absolute maximum rating must be observed.3.When outputs are in OFF-STATE or when V CC = 0V.4.V OUT < GND, V OUT > V CC (Outputs Active).5.Unused inputs must be held HIGH or LOW. They may not float.Symbol ParameterRatingV CC Supply Voltage –0.5V to +7.0V V IN DC Input Voltage –0.5V to +7.0V V OUTDC Output Voltage Note 2 Note 3–0.5V to V CC + 0.5V–0.5V to +7.0VI IK Input Diode Current –20mA I OK Output Diode Current (4) ±20mA I OUT DC Output Current ±25mA I CC DC V CC /GND Current ±75mAT STG Storage Temperature–65°C to +150°CT LLead Temperature (Soldering, 10 seconds)260°CSymbol ParameterRatingV CC Supply Voltage 4.5V to +5.5V V IN Input Voltage 0V to +5.5V V OUTOutput Voltage Note 2 Note 30V to V CC 0V to +5.5V T OPR Operating Temperature–40°C to +85°C t r , t fInput Rise and Fall Time, V CC =5.0V ± 0.5V0ns/V ~ 20ns/V元器件交易网74VHCT244A Octal Buffer/Line Driver with 3-STATE OutputsDC Electrical CharacteristicsNoise CharacteristicsNote:6.Parameter guaranteed by design.SymbolParameterV CC (V)Conditions T A = 25°CT A = –40°C to +85°C UnitsMin.Typ.Max.Min.Max. V IH HIGH Level Input Voltage4.5 2.0 2.0V5.5 2.02.0V IL LOW Level Input Voltage4.50.80.8V5.50.80.8V OH HIGH Level Output Voltage4.5V IN = V IH or V ILI OH = –50µA 4.40 4.50 4.40V I OH = –8mA 3.943.80V OL LOW Level Output Voltage4.5V IN = V IH or V ILI OL = 50µA 0.00.10.1V I OL = 8mA 0.360.44I OZ 3-STATE Output OFF-STATE Current 5.5V IN = V IH or V IL , V OUT = V CC or GND ±0.25±2.5µA I IN Input Leakage Current0–5.5V IN = 5.5V or GND ±0.1±1.0µA I CC Quiescent Supply Current5.5V IN = V CC or GND 4.040.0µA I CCT Maximum I CC /Input 5.5V IN = 3.4V , Other Input = V CC or GND 1.35 1.50mA I OFFOutput Leakage Current (Power Down State)0.0V OUT = 5.5V0.55.0µA SymbolParameterV CC (V)ConditionsT A = 25°CUnitsTyp.LimitsV OLP (6)Quiet Output Maximum Dynamic V OL5.0C L = 50pF 0.9 1.1V V OLV (6)Quiet Output Minimum Dynamic V OL5.0C L = 50pF –0.9–1.1V V IHD (6)Minimum HIGH Level Dynamic Input Voltage5.0C L = 50pF 2.0V V ILD (6)Maximum HIGH Level Dynamic Input Voltage5.0C L = 50pF0.8V元器件交易网74VHCT244A Octal Buffer/Line Driver with 3-STATE OutputsAC Electrical CharacteristicsNotes:7.Parameter guaranteed by design. t OSLH = |t PLH max – t PLH min |; t OSHL = |t PHL max – t PHL min |8.C PD is defined as the value of the internal equivalent capacitance which is calculated from the operating current consumption without load. Average operating current can be obtained by the equation:I CC (Opr.) = C PD • V CC • f IN + I CC / 8 (per F/F). The total C PD when n pcs. of the Octal D Flip-Flop operates can be calculated by the equation: C PD (total) = 20 + 12nSymbolParameterV CC (V)ConditionsT A = 25°CT A = –40°C to +85°CUnitsMin.Typ.Max.Min.Max.t PLH , t PHL Propagation Delay Time5.0 ± 0.5C L = 15pF 5.47.4 1.08.5nsC L = 50pF 5.98.41.09.5t PZL , t PZH 3-STATE Output Enable Time 5.0 ± 0.5R L = 1k ΩC L = 15pF 7.710.4 1.012.5ns C L = 50pF 8.211.4 1.013.5t PLZ , t PHZ3-STATE Output Disable Time5.0 ± 0.5R L = 1k ΩC L = 50pF8.811.4 1.013.0ns t OSLH , t OSHL Output to OutputSkew5.0 ± 0.5(7)1.01.0ns C IN Input Capacitance V CC = Open 41010pF C OUT Output Capacitance V CC = 5.0V9pF C PDPower Dissipation Capacitance(8)18pFFigure 1. 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300" WidePackage Number M20B74VHCT244A Octal Buffer/Line Driver with 3-STATE Outputs The™TinyBoost。

SN54HC244中文资料

PACKAGING INFORMATIONOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)5962-8409601VRA ACTIVE CDIP J201TBD Call TI Level-NC-NC-NC 5962-8409601VSA ACTIVE CFP W201TBD Call TI Level-NC-NC-NC 84096012A ACTIVE LCCC FK201TBD Call TI Level-NC-NC-NC 8409601RA ACTIVE CDIP J201TBD Call TI Level-NC-NC-NC 8409601SA ACTIVE CFP W201TBD Call TI Level-NC-NC-NCJM38510/65705B2A ACTIVE LCCC FK201TBD Call TI Level-NC-NC-NCJM38510/65705BRA ACTIVE CDIP J201TBD Call TI Level-NC-NC-NCJM38510/65705BSA ACTIVE CFP W201TBD Call TI Level-NC-NC-NC SN54HC244J ACTIVE CDIP J201TBD Call TI Level-NC-NC-NC SN74HC244ADBLE OBSOLETE SSOP DB20TBD Call TI Call TISN74HC244APWLE OBSOLETE TSSOP PW20TBD Call TI Call TISN74HC244DBLE OBSOLETE SSOP DB20TBD Call TI Call TISN74HC244DBR ACTIVE SSOP DB202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC244DBRE4ACTIVE SSOP DB202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC244DW ACTIVE SOIC DW2025Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC244DWE4ACTIVE SOIC DW2025Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC244DWG4ACTIVE SOIC DW2025Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC244DWR ACTIVE SOIC DW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC244DWRE4ACTIVE SOIC DW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC244DWRG4ACTIVE SOIC DW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC244N ACTIVE PDIP N2020Pb-Free(RoHS)CU NIPDAU Level-NC-NC-NC SN74HC244N3OBSOLETE PDIP N20TBD Call TI Call TISN74HC244NE4ACTIVE PDIP N2020Pb-Free(RoHS)CU NIPDAU Level-NC-NC-NCSN74HC244NSG4ACTIVE SO NS2040Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC244NSR ACTIVE SO NS202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC244NSRE4ACTIVE SO NS202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC244NSRG4ACTIVE SO NS202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC244PW ACTIVE TSSOP PW2070Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC244PWE4ACTIVE TSSOP PW2070Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC244PWLE OBSOLETE TSSOP PW20TBD Call TI Call TISN74HC244PWR ACTIVE TSSOP PW202000Green(RoHS&CU NIPDAU Level-1-260C-UNLIMOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)no Sb/Br)SN74HC244PWRE4ACTIVE TSSOP PW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC244PWT ACTIVE TSSOP PW20250Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC244PWTE4ACTIVE TSSOP PW20250Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SNJ54HC244FK ACTIVE LCCC FK201TBD Call TI Level-NC-NC-NC SNJ54HC244J ACTIVE CDIP J201TBD Call TI Level-NC-NC-NC SNJ54HC244W ACTIVE CFP W201TBD Call TI Level-NC-NC-NC (1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan-The planned eco-friendly classification:Pb-Free(RoHS)or Green(RoHS&no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free(RoHS):TI's terms"Lead-Free"or"Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all6substances,including the requirement that lead not exceed0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Green(RoHS&no Sb/Br):TI defines"Green"to mean Pb-Free(RoHS compatible),and free of Bromine(Br)and Antimony(Sb)based flame retardants(Br or Sb do not exceed0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.元器件交易网IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications,enhancements, improvements, and other changes to its products and services at any time and to discontinueany product or service without notice. Customers should obtain the latest relevant information before placingorders and should verify that such information is current and complete. All products are sold subject to TI’s termsand conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale inaccordance with TI’s standard warranty. T esting and other quality control techniques are used to the extent TIdeems necessary to support this warranty. Except where mandated by government requirements, testing of allparameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible fortheir products and applications using TI components. T o minimize the risks associated with customer productsand applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right,copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or processin which TI products or services are used. Information published by TI regarding third-party products or servicesdoes not constitute a license from TI to use such products or services or a warranty or endorsement thereof.Use of such information may require a license from a third party under the patents or other intellectual propertyof the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is withoutalteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproductionof this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable forsuch altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for thatproduct or service voids all express and any implied warranties for the associated TI product or service andis an unfair and deceptive business practice. TI is not responsible or liable for any such statements.Following are URLs where you can obtain information on other Texas Instruments products and applicationsolutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetworkMicrocontrollers Security /securityTelephony /telephonyVideo & Imaging /videoWireless /wirelessMailing Address:Texas InstrumentsPost Office Box 655303 Dallas, Texas 75265Copyright 2005, Texas Instruments Incorporated。

SN54HCT244J中文资料

PACKAGING INFORMATIONOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)5962-8513001VRA ACTIVE CDIP J201None Call TI Level-NC-NC-NC 5962-8513001VSA ACTIVE CFP W201None Call TI Level-NC-NC-NC 85130012A ACTIVE LCCC FK201None Call TI Level-NC-NC-NC 8513001RA ACTIVE CDIP J201None Call TI Level-NC-NC-NC JM38510/65755B2A ACTIVE LCCC FK201None Call TI Level-NC-NC-NC JM38510/65755BRA ACTIVE CDIP J201None Call TI Level-NC-NC-NC SN54HCT244J ACTIVE CDIP J201None Call TI Level-NC-NC-NC SN74HCT244DBLE OBSOLETE SSOP DB20None Call TI Call TISN74HCT244DBR ACTIVE SSOP DB202000Pb-Free(RoHS)CU NIPDAU Level-2-260C-1YEAR/Level-1-235C-UNLIMSN74HCT244DW ACTIVE SOIC DW2025Pb-Free(RoHS)CU NIPDAU Level-2-250C-1YEAR/Level-1-235C-UNLIMSN74HCT244DWR ACTIVE SOIC DW202000Pb-Free(RoHS)CU NIPDAU Level-2-250C-1YEAR/Level-1-235C-UNLIMSN74HCT244N ACTIVE PDIP N2020Pb-Free(RoHS)CU NIPDAU Level-NC-NC-NC SN74HCT244N3OBSOLETE PDIP N20None Call TI Call TISN74HCT244NSR ACTIVE SO NS202000Pb-Free(RoHS)CU NIPDAU Level-2-260C-1YEAR/Level-1-235C-UNLIMSN74HCT244PW ACTIVE TSSOP PW2070Pb-Free(RoHS)CU NIPDAU Level-1-250C-UNLIMSN74HCT244PWLE OBSOLETE TSSOP PW20None Call TI Call TISN74HCT244PWR ACTIVE TSSOP PW202000Pb-Free(RoHS)CU NIPDAU Level-1-250C-UNLIMSN74HCT244PWT ACTIVE TSSOP PW20250Pb-Free(RoHS)CU NIPDAU Level-1-250C-UNLIM SNJ54HCT244FK ACTIVE LCCC FK201None Call TI Level-NC-NC-NC SNJ54HCT244J ACTIVE CDIP J201None Call TI Level-NC-NC-NC (1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan-May not be currently available-please check /productcontent for the latest availability information and additional product content details.None:Not yet available Lead(Pb-Free).Pb-Free(RoHS):TI's terms"Lead-Free"or"Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all6substances,including the requirement that lead not exceed0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Green(RoHS&no Sb/Br):TI defines"Green"to mean"Pb-Free"and in addition,uses package materials that do not contain halogens, including bromine(Br)or antimony(Sb)above0.1%of total product weight.(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDECindustry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it isprovided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.元器件交易网IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications,enhancements, improvements, and other changes to its products and services at any time and to discontinueany product or service without notice. Customers should obtain the latest relevant information before placingorders and should verify that such information is current and complete. All products are sold subject to TI’s termsand conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale inaccordance with TI’s standard warranty. T esting and other quality control techniques are used to the extent TIdeems necessary to support this warranty. Except where mandated by government requirements, testing of allparameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible fortheir products and applications using TI components. T o minimize the risks associated with customer productsand applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right,copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or processin which TI products or services are used. Information published by TI regarding third-party products or servicesdoes not constitute a license from TI to use such products or services or a warranty or endorsement thereof.Use of such information may require a license from a third party under the patents or other intellectual propertyof the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is withoutalteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproductionof this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable forsuch altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for thatproduct or service voids all express and any implied warranties for the associated TI product or service andis an unfair and deceptive business practice. TI is not responsible or liable for any such statements.Following are URLs where you can obtain information on other Texas Instruments products and applicationsolutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetworkMicrocontrollers Security /securityTelephony /telephonyVideo & Imaging /videoWireless /wirelessMailing Address:Texas InstrumentsPost Office Box 655303 Dallas, Texas 75265Copyright 2005, Texas Instruments Incorporated。

74HC244DTR2G资料