FIFO Generator v2.3

National Instruments cRIO-9049 1.60 GHz Quad-Core

SPECIFICA TIONScRIO-90491.60 GHz Quad-Core CPU, 4 GB DRAM, 16 GB Storage, Kintex-7 325T FPGA, 8-Slot CompactRIO ControllerDefinitionsWarranted specifications describe the performance of a model under stated operating conditions and are covered by the model warranty.Characteristics describe values that are relevant to the use of the model under stated operating conditions but are not covered by the model warranty.•Typical specifications describe the performance met by a majority of models.•Nominal specifications describe an attribute that is based on design, conformance testing, or supplemental testing.Specifications are Typical unless otherwise noted.ConditionsSpecifications are valid for -20 °C to 55 °C unless otherwise noted.ProcessorCPU Intel Atom E3940Number of cores4CPU frequency 1.6 GHz (base), 1.8 GHz (burst)On-die L2 cache 2 MBSoftwareNote For minimum software support information, visit /info and enter theInfo Code swsupport.Supported operating system NI Linux Real-Time (64-bit)Supported C Series module programming modes Real-Time (NI-DAQmx)Real-Time Scan (I/O Variables) LabVIEW FPGAApplication softwareLabVIEW1LabVIEW 2017 or later,LabVIEW Real-Time Module 2017 or later,LabVIEW FPGA Module 2017 or later, C/C++ Development Tools forNI Linux Real-Time2Eclipse Edition 2014 or laterDriver software NI CompactRIO Device DriversDecember 2017 or laterNetwork/Ethernet PortNumber of ports2Network interface10Base-T, 100Base-TX, and1000Base-T EthernetCompatibility IEEE 802.3Communication rates10 Mb/s, 100 Mb/s, 1000 Mb/s auto-negotiated Maximum cabling distance100 m/segment1LabVIEW FPGA Module is not required when using Real-Time Scan (I/O Variables) mode orReal-Time (NI-DAQmx) mode. To program the user-accessible FPGA on the cRIO-9049, theLabVIEW FPGA Module is required.2C/C++ Development Tools for NI Linux Real-Time is an optional interface for C/C++programming of the cRIO-9049 processor. Visit /info and enter Info Code RIOCdev formore information about the C/C++ Development Tools for NI Linux Real-Time.2| | cRIO-9049 SpecificationsNetwork Timing and SynchronizationProtocol IEEE 802.1AS-2011IEEE 1588-2008 (default end-to-end profile) Supported ethernet ports Port 0, port 1Network synchronization accuracy3<1 μsNote The cRIO-9049 employs time-aware transmission support. For moreinformation about time-aware transmission support, visit /info and enter InfoCode timeaware.RS-232 Serial PortMaximum baud rate115,200 b/sData bits5, 6, 7, 8Stop bits1, 2Parity Odd, even, mark, spaceFlow control RTS/CTS, XON/XOFF, DTR/DSRRI wake maximum low level0.8 VRI wake minimum high level 2.4 VRI overvoltage tolerance±24 VRS-485 Serial PortMaximum baud rate230,400 b/sData bits5, 6, 7, 8Stop bits1, 2Parity Odd, even, mark, spaceFlow control XON/XOFF3Network synchronization is system-dependent. For information about network synchronizationaccuracy, visit /info and enter Info Code criosync.cRIO-9049 Specifications| © National Instruments| 3Wire mode4-wire, 2-wire, 2-wire autoIsolation voltage60 V DC continuous, port to earth ground Note The RS-485 serial port ground and shield are functionally isolated fromchassis ground to prevent ground loops, but do not meet IEC 61010-1 for safetyisolation.Cable requirement Unshielded, 30 m maximum length (limited byEMC/surge)Note RS-485 is capable of 1.2 km (4,000 ft) length without surge limitation.USB PortsPort 1:Type USB Type-A, host portUSB interface USB 2.0, Hi-SpeedMaximum data rate480 Mb/sMaximum current900 mAType USB Type-C, host portUSB interface USB 3.1 Gen1, SuperSpeedMaximum data rate 5 Gb/sMaximum current900 mAAlternate modes DisplayPortPort 3:Type USB Type-C, dual role port (device or host) USB interface USB 3.1 Gen1, SuperSpeedMaximum data rate 5 Gb/sMaximum current900 mADisplayPort over USB Type-CMaximum resolution3840 × 2160 at 60 HzSupported standard DisplayPort 1.2Supported USB ports4| | cRIO-9049 SpecificationsSD Card SlotSD card support SD and SDHC standardsSupported interface speeds UHS‐I SDR50 and DDR50Notice Full and high speed SD cards are prohibited for use with the cRIO-9049.MemoryNonvolatile (SSD)Nonvolatile memory (SSD)16 GBNonvolatile memory (SSD) type Planar SLC NANDNote Visit /info and enter the Info Code ssdbp for information about thelife span of the nonvolatile memory and about best practices for using nonvolatilememory.V olatile (DRAM)Processor memoryDensity 4 GBType DDR3LMaximum theoretical data rate12.8 GB/sFPGA memory (DRAM)Density256 MBType DDR3Maximum theoretical data rate 1.6 GB/sReconfigurable FPGAFPGA type Xilinx Kintex-7 7K325TNumber of flip-flops407,600Number of 6-input LUTs203,800840Number of DSP slices(18 × 25 multipliers)Available block RAM16,020 kbitscRIO-9049 Specifications| © National Instruments| 5Number of DMA channels16Number of logical interrupts32Internal Real-Time ClockAccuracy200 ppm; 40 ppm at 25 °CController PFI 0Maximum input or output frequency 1 MHzCable length 3 m (10 ft)Cable impedance50 ΩPFI 0 connector SMBPower-on state High impedanceI/O standard compatibility 5 V TTLI/O voltage protection±30 VMaximum operating conditionsI OL output low current8 mA maximumI OH output high current-8 mA maximum6| | cRIO-9049 SpecificationsTable 2. DC Output Characteristics (Continued)Real-Time Streaming PerformanceData throughput is dependent on the application, system, and performance of the removable storage media. For information about optimizing data throughput on the cRIO-9049 visit/info and enter Info Code optdata.Data throughput from system memory to targetSD card40 MB/sUSB Type-C100 MB/sReal-Time (NI-DAQmx) ModeThe following specifications are applicable for modules and slots programmed in Real-Time (NI-DAQmx) mode. For more information about using modules in LabVIEW FPGA mode or Real-Time Scan (I/O Variables) mode, visit /info and enter Info Code swsupport. Analog InputInput FIFO size253 samples per slotMaximum sample rate4Determined by the C Series module or modules Timing accuracy550 ppm of sample rateTiming resolution12.5 nsNumber of channels supported Determined by the C Series module or modules Number of hardware-timed tasks8Analog OutputHardware-timed tasksNumber of hardware-timed tasks84Performance dependent on type of installed C Series module and number of channels in the task.5Does not include group delay. For more information, refer to the documentation for each C Series module.cRIO-9049 Specifications| © National Instruments| 7Number of channels supportedOnboard regeneration16Non-regeneration Determined by the C Series module or modules Non-hardware-timed tasksNumber of non-hardware-timed tasks Determined by the C Series module or modules Number of channels supported Determined by the C Series module or modules Maximum update rate 1.6 MS/sNote Streaming applications are limited by system-dependent factors and thecapability of C Series modules.Timing accuracy50 ppm of sample rateTiming resolution12.5 nsWaveform onboard regeneration FIFO8,191 samples shared among channels used Waveform streaming FIFO253 samples per slotDigital WaveformWaveform acquisition (DI) FIFOParallel modules255 samples per slotSerial modules127 samples per slotWaveform onboard regeneration (DO) FIFOParallel modulesSlots 1 to 42,047 samples shared among slots usedSlots 5 to 81,023 samples shared among slots used Waveform streaming (DO) FIFOParallel modules255 samples per slotSerial modules127 samples per slotSample clock frequencyDigital input0 MHz to 10 MHz8| | cRIO-9049 SpecificationsDigital outputot0:6 timing engine0 MHz to 3.5 MHzot7 timing engine0 MHz to 10 MHzNote Streaming applications are limited by system-dependent factors and thecapability of C Series modules.Timing accuracy50 ppm8Number of digital input hardware-timedtasksNumber of digital output hardware-timed8tasksGeneral-Purpose Counters/TimersNumber of counters/timers4Resolution32 bitsCounter measurements Edge counting, pulse, semi-period, period,two-edge separation, pulse widthPosition measurements X1, X2, X4 quadrature encoding withChannel Z reloading; two-pulse encoding Output applications Pulse, pulse train with dynamic updates,frequency division, equivalent time sampling Internal base clocks80 MHz, 20 MHz, 13.1072 MHz, 12.8 MHz,10 MHz, 100 kHzExternal base clock frequency0 MHz to 20 MHzBase clock accuracy50 ppmOutput frequency0 MHz to 20 MHzInputs Gate, Source, HW_Arm, Aux, A, B, Z,Up_DownRouting options for inputs Any module PFI, controller PFI, analogtrigger, many internal signalsFIFO Dedicated 127-sample FIFO Frequency GeneratorNumber of channels1Base clocks20 MHz, 10 MHz, 100 kHzDivisors 1 to 16 (integers)cRIO-9049 Specifications| © National Instruments| 9Base clock accuracy50 ppmOutput Any controller PFI or module PFI terminal Module PFIFunctionality Static digital input, static digital output, timinginput, and timing outputTiming output sources6Many analog input, analog output, counter,digital input, and digital output timing signals Timing input frequency0 MHz to 20 MHzTiming output frequency0 MHz to 20 MHzDigital T riggersSource Any controller PFI or module PFI terminal Polarity Software-selectable for most signalsAnalog input function Start Trigger, Reference Trigger,Pause Trigger, Sample Clock,Sample Clock TimebaseAnalog output function Start Trigger, Pause Trigger, Sample Clock,Sample Clock TimebaseCounter/timer function Gate, Source, HW_Arm, Aux, A, B, Z,Up_DownModule I/O StatesAt power-on Module-dependent. Refer to the documentationfor each C Series module.Time-Based T riggers and TimestampsNote Time-based triggers and timestamps are only supported in NI-DAQmx 18.1or later.Number of time-based triggers5Number of timestamps6Analog inputTime-based triggers Start Trigger, Sync PulseTimestamps Start Trigger, Reference Trigger, First Sample6Actual available signals are dependent on type of installed C Series module.10| | cRIO-9049 SpecificationsAnalog outputTime-based triggers Start Trigger, Sync PulseTimestamps Start Trigger, First SampleDigital inputTime-based triggers Start TriggerTimestamps Start Trigger, Reference Trigger, First Sample Digital outputTime-based triggers Start TriggerTimestamps Start Trigger, First SampleCounter/timer inputTime-based triggers Arm Start TriggerTimestamps Arm Start TriggerCounter/timer outputTime-based triggers Start Trigger, Arm Start TriggerTimestamps Start Trigger, Arm Start TriggerCMOS Battery10 yearsTypical battery life with power applied topower connector7.8 yearsTypical battery life when stored attemperatures up to 25 °C5.4 yearsTypical battery life when stored attemperatures up to 85 °CPower RequirementsNote Some C Series modules have additional power requirements. For moreinformation about C Series module power requirements, refer to the C Seriesmodule(s) documentation.Note Sleep mode for C Series modules is not supported in Real-Time (DAQmx)Mode.V oltage input range (measured at the cRIO-9049 power connector)V19 V to 30 VV29 V to 30 VcRIO-9049 Specifications| © National Instruments| 11Maximum power consumption60 WNote The C terminal of the power connector is functionally isolated from chassisground to prevent ground loops, but does not meet IEC 61010-1 for safety isolationNote The maximum power consumption specification is based on a fully populatedsystem running a high-stress application at elevated ambient temperature and withall C Series modules and USB devices consuming the maximum allowed power. Typical standby power consumption 3.4 W at 24 V DC inputRecommended power supply100 W, 24 V DCTypical leakage current from secondary power input (V2) while system is powered from primary power input (V1)At 9 V0.4 mAAt 30 V 1.93 mANotice Do not connect V2 to a DC Mains supply or to any supply that requires aconnecting cable longer than 3 m (10 ft). A DC Mains supply is a local DCelectricity supply network in the infrastructure of a site or building. V1 may beconnected to DC Mains.Notice Include a switch or circuit breaker in the installation to disconnect thesystem from DC Mains. The switch or circuit breaker must be suitably rated,accessible, and marked as the disconnecting device for the system.EMC ratings for inputs as described in IEC 61000V1Short lines, long lines, and DC distributednetworksV2Short lines onlyPower input connector4-position, 3.5 mm pitch, pluggable screwterminal with screw locks,Sauro CTF04BV8-AN000APhysical CharacteristicsWeight (unloaded)2,250 g (4 lbs, 15 oz)Dimensions (unloaded)328.8 mm × 88.1 mm × 121.2 mm (12.94 in. ×3.47 in. ×4.77 in. )12| | cRIO-9049 SpecificationsPower connector wiringGauge0.5 mm 2 to 2.1 mm2 (20 AWG to 14 AWG)copper conductor wireWire strip length 6 mm (0.24 in.) of insulation stripped from theendTemperature rating85 °CTorque for screw terminals0.20 N · m to 0.25 N · m (1.8 lb · in. to2.2 lb · in.)Wires per screw terminal One wire per screw terminalConnector securementSecurement type Screw flanges providedTorque for screw flanges0.20 N · m to 0.25 N · m (1.8 lb · in. to2.2 lb · in.)Insulation rating300 V, maximumSafety VoltagesConnect only voltages that are below these limits.V1 terminal to C terminal30 V, maximumV2 terminal to C terminal30 V, maximumChassis ground to C terminal30 V, maximumEnvironmentalTemperature (Tested in accordance with IEC 60068-2-1 and IEC 60068-2-2) Operating-20 °C to 55 °CStorage-40 °C to 85 °CIngress protection IP2010% RH to 90% RH, noncondensing Operating humidity(Tested in accordance with IEC 60068-2-30)Storage humidity5% RH to 95% RH, noncondensing (Tested in accordance with IEC 60068-2-30)Pollution Degree2Maximum altitude5,000 mIndoor use only.cRIO-9049 Specifications| © National Instruments| 13Hazardous LocationsU.S. (UL)Class I, Division 2, Groups A, B, C, D, T4;Class I, Zone 2, AEx nA IIC T4 GcCanada (C-UL)Class I, Division 2, Groups A, B, C, D, T4; ExnA IIC T4 GcEurope (ATEX) and International (IECEx)Ex nA IIC T4 GcShock and VibrationTo meet these specifications, you must mount the cRIO-9049 system directly on a flat, rigid surface as described in the user manual, affix ferrules to the ends of the terminal wires, and use retention accessories for the USB 2.0 host port (NI USB Extender Cable, 152166-xx), USB type-C ports (NI Locking USB Cables, 143556-xx; NI USB Extender Cable, 143555-xx; NI USB Display Adapters, 143557-xx or 143558-xx). All cabling should be strain-relieved near input connectors. Take care to not directionally bias cable connectors within input connectors when applying strain relief.Operating vibrationRandom (IEC 60068-2-64) 5 g rms, 10 Hz to 500 HzSinusoidal (IEC 60068-2-6) 5 g, 10 Hz to 500 HzOperating shock (IEC 60068-2-27)30 g, 11 ms half sine; 50 g, 3 ms half sine;18 shocks at 6 orientationsSafety Compliance and Hazardous Locations StandardsThis product is designed to meet the requirements of the following electrical equipment safety standards for measurement, control, and laboratory use:•IEC 61010-1, EN 61010-1•UL 61010-1, CSA C22.2 No. 61010-1•EN 60079-0:2012, EN 60079-15:2010•IEC 60079-0: Ed 6, IEC 60079-15; Ed 4•UL 60079-0; Ed 6, UL 60079-15; Ed 4•CSA C22.2 No. 60079-0, CSA C22.2 No. 60079-15Note For UL and other safety certifications, refer to the product label or theProduct Certifications and Declarations section.14| | cRIO-9049 SpecificationsElectromagnetic CompatibilityThis product meets the requirements of the following EMC standards for electrical equipment for measurement, control, and laboratory use:•EN 61326-1 (IEC 61326-1): Class A emissions; Industrial immunity•EN 55011 (CISPR 11): Group 1, Class A emissions•AS/NZS CISPR 11: Group 1, Class A emissions•FCC 47 CFR Part 15B: Class A emissions•ICES-001: Class A emissionsNote In the United States (per FCC 47 CFR), Class A equipment is intended foruse in commercial, light-industrial, and heavy-industrial locations. In Europe,Canada, Australia and New Zealand (per CISPR 11) Class A equipment is intendedfor use only in heavy-industrial locations.Note Group 1 equipment (per CISPR 11) is any industrial, scientific, or medicalequipment that does not intentionally generate radio frequency energy for thetreatment of material or inspection/analysis purposes.Notice For EMC declarations and certifications, and additional information, referto the Product Certifications and Declarations section.CE ComplianceThis product meets the essential requirements of applicable European Directives, as follows:•2014/35/EU; Low-V oltage Directive (safety)•2014/30/EU; Electromagnetic Compatibility Directive (EMC)•2014/34/EU; Potentially Explosive Atmospheres (ATEX)•2011/65/EU; Restriction of Hazardous Substances (RoHS)Product Certifications and DeclarationsRefer to the product Declaration of Conformity (DoC) for additional regulatory compliance information. To obtain product certifications and the DoC for NI products, visit / certification, search by model number or product line, and click the appropriate link in the Certification column.Environmental ManagementNI is committed to designing and manufacturing products in an environmentally responsible manner. NI recognizes that eliminating certain hazardous substances from our products is beneficial to the environment and to NI customers.cRIO-9049 Specifications| © National Instruments| 15For additional environmental information, refer to the Minimize Our Environmental Impact web page at /environment. This page contains the environmental regulations and directives with which NI complies, as well as other environmental information not included in this document.Waste Electrical and Electronic Equipment (WEEE) EU Customers At the end of the product life cycle, all NI products must bedisposed of according to local laws and regulations. For more information abouthow to recycle NI products in your region, visit /environment/weee. Battery Replacement and DisposalBattery Directive This device contains a long-life coin cell battery. If you need toreplace it, use the Return Material Authorization (RMA) process or contact anauthorized National Instruments service representative. For more information aboutcompliance with the EU Battery Directive 2006/66/EC about Batteries andAccumulators and Waste Batteries and Accumulators, visit /environment/batterydirective.电子信息产品污染控制管理办法(中国RoHS)中国客户National Instruments符合中国电子信息产品中限制使用某些有害物质指令(RoHS)。

Soc实验3 AHB主机接口模块

实验3 AHB主机接口模块1实验简介预备知识:为了完成该实验,同学们需要掌握AHB传输协议以及一定的使用Verilog HDL进行硬件设计的能力。

目标:该实验的主要目标是通过设计AHB主机接口模块使同学们巩固AHB 传输协议以及提高使用Verilog HDL进行硬件设计的能力。

2实验类容实验3.1设有一个主机(激励,由testbench给出),通过AHB总线向从机Memory 地址8'h00~8'h07发送数据32'h00000008~32'h0000000f。

试设计一个AHB主机接口模块,提供主机到AHB总线的接口,使得主机发送的数据通过AHB总线发往Memory相应地址。

要求AHB主机接口模块发起一次八拍增量突发传输。

AHB主机接口模块框图见附录图1,AHB主机接口模块端口见附录表1。

该设计的验证需要加入实验2设计的仲裁器和实验1设计的AHB从机接口模块。

要求:初始情况下该主机总线授予信号为0,需要向仲裁器申请访问总线;HADDR[31:28]==4'h4时,Memory从机选择信号为1。

为简化设计,HSIZE设定为3'b010,HPROT设定为4'b0001,HRESP设定为OKEY。

该实验提供一个32位宽度256位深度的RAM模块,将RAM.v、RAM.ngc、RAM.mif、BLK_MEM_GEN_V7_3.v放入工程所在目录,将RAM.v和BLK_MEM_GEN_V7_3.v加入工程,编译后即可使用RAM。

实验3.2不同IP间可通过NoC或总线进行通信。

设有一个NoC和AMBA总线互联的系统,NoC上的一个数据包通过解包模块存入FIFO,一个AHB主机接口从FIFO中读出数据发往存储器相应地址(该地址由NoC源节点地址译码得到,NoC 源节点地址与存储器地址对应关系如附录表2所示)。

该系统框图如附录图2所示。

设解包模块写入FIFO的数据依次为NoC源节点地址、数据长度以及相应的数据。

异步fifo的uvm验证原理

异步fifo的uvm验证原理异步FIFO(First-In-First-Out,先进先出)是一种常用的数据缓冲区结构,常用于解决不同速率的数据传输问题。

UVM (Universal Verification Methodology,通用验证方法学)是一种系统级验证方法学,用于验证硬件设计。

在UVM中,对异步FIFO的验证需要对FIFO的功能和时序进行验证。

以下是异步FIFO的UVM验证原理:1. 创建FIFO模型:首先,需要创建一个FIFO模型,包括FIFO的输入端口和输出端口,以及FIFO的内部数据存储器。

可以使用SystemVerilog语言创建FIFO模型。

2. 编写验证环境:在UVM中,需要编写一个验证环境(testbench),用于生成测试用例,驱动输入数据到FIFO中,并验证FIFO的输出数据是否符合预期。

验证环境包括以下组件:- 驱动(driver):负责将测试向量输入到FIFO中。

- 监视器(monitor):监控FIFO的输出数据,并将其与预期结果进行比较。

- 预测器(predictor):根据输入数据预测FIFO的输出结果。

- 生成器(generator):生成各种测试用例。

3. 设置时序约束:对于异步FIFO的验证,需要设置时序约束,以确保FIFO的输入和输出数据能够按照预期的时序要求进行传输。

时序约束包括FIFO的读写时钟频率和时钟间隔等参数。

4. 进行功能验证:验证FIFO的功能,包括数据的读写操作是否正确,数据的顺序是否符合FIFO原则等。

可以通过在测试用例中使用不同的输入数据和读写操作顺序来验证FIFO的功能。

5. 进行时序验证:验证FIFO的时序,包括输入数据的时序要求是否满足,输出数据的时序是否符合预期。

可以通过在测试用例中使用不同的时序生成输入数据来验证FIFO的时序。

6. 进行性能验证:验证FIFO的性能,包括写入速率和读出速率是否满足要求,以及FIFO的深度是否足够。

xilinx fifo generator 用法 -回复

xilinx fifo generator 用法-回复Xilinx FIFO Generator 是一种常用的工具,用于在Xilinx FPGA 设计中生成和配置先进先出(FIFO)缓冲器。

FIFO 缓冲器是一种在不同速率的数据流之间进行数据传输的常见方法。

本文将介绍Xilinx FIFO Generator 的用法,从安装到配置和实例设计的各个方面,详细解释每个步骤。

第一步是安装Xilinx FIFO Generator。

安装Xilinx FIFO Generator 时,首先需要确保已经安装了Xilinx Vivado 设计套件。

Vivado 是Xilinx FPGA 设计工具集的核心,因此它是使用FIFO Generator 的前提条件。

在确保已安装Vivado 的前提下,可以继续安装FIFO Generator。

要安装Xilinx FIFO Generator,可以前往Xilinx 官方网站("Downloads" 页面,并搜索"FIFO Generator"。

找到相应的下载选项并下载适用于您的操作系统的版本。

一旦下载完成,按照安装向导的指示进行安装。

安装完成后,可以在Vivado 中使用FIFO Generator 开始设计。

第二步是在Vivado 中打开FIFO Generator。

启动Vivado 设计套件,并在"Welcome" 界面上选择"Create New Project"。

按照安装向导的指示填写项目名称、路径和项目设置。

完成设置后,单击"Finish" 创建新项目。

在新项目创建完成后,将出现Vivado 主界面。

在主界面中,可以看到项目资源管理器、设计视图和其他工具选项。

为了使用FIFO Generator,请单击"Flow Navigator" 中的"IP INTEGRATOR"。

Silicon Laboratories C8051F380 1 2 3 4 5 6 7 C USB

-10 位 ADC(仅 C8051F380/1/2/3/C)•高达 500ksps•内建模拟多路复用器,单端和差分模式•VREF 来自外部引脚、内部参考或 V DD•内建温度传感器•外部转换启动输入选项-两个比较器-内部参考电压(仅 C8051F380/1/2/3/C)-掉电检测器和上电复位电路USB 功能控制器-符合 USB 规格 2.0-全速 (12Mbps) 或低速 (1.5Mbps) 运行-集成时钟恢复;全速或低速无需外部晶体-支持八个灵活的终端-1kB USB 缓冲存储器-集成收发器;无需外部电阻片上调试-片上调试电路提供全速、非侵入式的系统内调试(无需仿真器)-提供断点、单步执行、检查/修改内存和寄存器-比使用 ICE 芯片、目标仿真头和仿真插座的仿真系统有更优越的性能电源电压输入: 2.7 至 5.25V-使用片内稳压器时,支持的电压范围为 2.7~5.25V -流水线指令体系结构;70% 指令的执行时间为 1 个或2个系统时钟-高达 48 MIPS 的操作-扩展的中断处理程序内存-4352 或 2304字节 RAM-64、32 或 16kB 闪存;可在系统内编程的 512 字节扇区数字外围设备-40/25 个端口 I/O;全部能承受 5V 高灌电流-硬件增强型SPI™、两个 I2C/SMBus™ 和两个增强型UART 串口-六个通用 16 位计数器/定时器-16 位可编程计数器阵列 (PCA),有五个采集/比较模块-外部存储器接口 (EMIF)时钟源-内部振荡器:启用时钟恢复时精度为 ±0.25%。

支持所有USB 和 UART 模式-外部振荡器:晶体、RC、C 或时钟(1 或 2 引脚模式)-低频 (80kHz) 内部振荡器-在运行中可切换时钟源封装-48 引脚 TQFP (C8051F380/2/4/6)-32 引脚 LQFP (C8051F381/3/5/7/C)-5x5mm 32 引脚 QFN (C8051F381/3/5/7/C)温度范围: –40 至 +85°CC8051F380/1/2/3/4/5/6/7/CC8051F380/1/2/3/4/5/6/7/CTable of Contents1. System Overview (16)2. C8051F34x Compatibility (20)2.1. Hardware Incompatibilities (21)3. Pinout and Package Definitions (22)4. Typical Connection Diagrams (34)4.1. Power (34)4.2. USB (36)4.3. Voltage Reference (VREF) (36)5. Electrical Characteristics (37)5.1. Absolute Maximum Specifications (37)5.2. Electrical Characteristics (38)6. 10-Bit ADC (ADC0, C8051F380/1/2/3/C only) (46)6.1. Output Code Formatting (47)6.3. Modes of Operation (50)6.3.1. Starting a Conversion (50)6.3.2. Tracking Modes (51)6.3.3. Settling Time Requirements (52)6.4. Programmable Window Detector (56)6.4.1. Window Detector Example (58)6.5. ADC0 Analog Multiplexer (C8051F380/1/2/3/C only) (59)7. Voltage Reference Options (62)8. Comparator0 and Comparator1 (64)8.1. Comparator Multiplexers (71)9. Voltage Regulators (REG0 and REG1) (74)9.1. Voltage Regulator (REG0) (74)9.1.1. Regulator Mode Selection (74)9.1.2. VBUS Detection (74)9.2. Voltage Regulator (REG1) (74)10. Power Management Modes (76)10.1. Idle Mode (76)10.2. Stop Mode (77)10.3. Suspend Mode (77)11. CIP-51 Microcontroller (79)11.1. Instruction Set (80)11.1.1. Instruction and CPU Timing (80)11.2. CIP-51 Register Descriptions (85)12. Prefetch Engine (88)13. Memory Organization (89)13.1. Program Memory (91)13.2. Data Memory (91)13.3. General Purpose Registers (92)13.4. Bit Addressable Locations (92)13.5. Stack (92)C8051F380/1/2/3/4/5/6/7/C14. External Data Memory Interface and On-Chip XRAM (93)14.1. Accessing XRAM (93)14.1.1. 16-Bit MOVX Example (93)14.1.2. 8-Bit MOVX Example (93)14.2. Accessing USB FIFO Space (94)14.3. Configuring the External Memory Interface (95)14.4. Port Configuration (95)14.5. Multiplexed and Non-multiplexed Selection (98)14.5.1. Multiplexed Configuration (98)14.5.2. Non-multiplexed Configuration (98)14.6. Memory Mode Selection (100)14.6.1. Internal XRAM Only (100)14.6.2. Split Mode without Bank Select (100)14.6.3. Split Mode with Bank Select (101)14.6.4. External Only (101)14.7. Timing (102)14.7.1. Non-multiplexed Mode (104)14.7.1.1. 16-bit MOVX: EMI0CF[4:2] = 101, 110, or 111 (104)14.7.1.2. 8-bit MOVX without Bank Select: EMI0CF[4:2] = 101 or 111 (105)14.7.1.3. 8-bit MOVX with Bank Select: EMI0CF[4:2] = 110 (106)14.7.2. Multiplexed Mode (107)14.7.2.1. 16-bit MOVX: EMI0CF[4:2] = 001, 010, or 011 (107)14.7.2.2. 8-bit MOVX without Bank Select: EMI0CF[4:2] = 001 or 011 (108)14.7.2.3. 8-bit MOVX with Bank Select: EMI0CF[4:2] = 010 (109)15. Special Function Registers (111)15.1. 13.1. SFR Paging (111)16. Interrupts (118)16.1. MCU Interrupt Sources and Vectors (119)16.1.1. Interrupt Priorities (119)16.1.2. Interrupt Latency (119)16.2. Interrupt Register Descriptions (119)16.3. INT0 and INT1 External Interrupt Sources (127)17. Reset Sources (129)17.1. Power-On Reset (130)17.2. Power-Fail Reset / VDD Monitor (131)17.3. External Reset (132)17.4. Missing Clock Detector Reset (132)17.5. Comparator0 Reset (132)17.6. PCA Watchdog Timer Reset (133)17.7. Flash Error Reset (133)17.8. Software Reset (133)17.9. USB Reset (133)18. Flash Memory (135)18.1. Programming The Flash Memory (135)18.1.1. Flash Lock and Key Functions (135)C8051F380/1/2/3/4/5/6/7/C18.1.2. Flash Erase Procedure (135)18.1.3. Flash Write Procedure (136)18.2. Non-Volatile Data Storage (137)18.3. Security Options (137)19. Oscillators and Clock Selection (142)19.1. System Clock Selection (143)19.2. USB Clock Selection (143)19.3. Programmable Internal High-Frequency (H-F) Oscillator (145)19.3.1. Internal Oscillator Suspend Mode (145)19.4. Clock Multiplier (147)19.5. Programmable Internal Low-Frequency (L-F) Oscillator (148)19.5.1. Calibrating the Internal L-F Oscillator (148)19.6. External Oscillator Drive Circuit (149)19.6.1. External Crystal Mode (149)19.6.2. External RC Example (151)19.6.3. External Capacitor Example (151)20. Port Input/Output (153)20.1. Priority Crossbar Decoder (154)20.2. Port I/O Initialization (158)20.3. General Purpose Port I/O (161)21. Universal Serial Bus Controller (USB0) (172)21.1. Endpoint Addressing (172)21.2. USB Transceiver (173)21.3. USB Register Access (175)21.4. USB Clock Configuration (179)21.5. FIFO Management (181)21.5.1. FIFO Split Mode (181)21.5.2. FIFO Double Buffering (182)21.5.1. FIFO Access (182)21.6. Function Addressing (183)21.7. Function Configuration and Control (183)21.8. Interrupts (186)21.9. The Serial Interface Engine (193)21.10. Endpoint0 (193)21.10.1. Endpoint0 SETUP Transactions (193)21.10.2. Endpoint0 IN Transactions (193)21.10.3. Endpoint0 OUT Transactions (194)21.11. Configuring Endpoints1-3 (196)21.12. Controlling Endpoints1-3 IN (197)21.12.1. Endpoints1-3 IN Interrupt or Bulk Mode (197)21.12.2. Endpoints1-3 IN Isochronous Mode (198)21.13. Controlling Endpoints1-3 OUT (201)21.13.1. Endpoints1-3 OUT Interrupt or Bulk Mode (201)21.13.2. Endpoints1-3 OUT Isochronous Mode (201)22. SMBus0 and SMBus1 (I2C Compatible) (205)C8051F380/1/2/3/4/5/6/7/C22.1. Supporting Documents (206)22.2. SMBus Configuration (206)22.3. SMBus Operation (206)22.3.1. Transmitter Vs. Receiver (207)22.3.2. Arbitration (207)22.3.3. Clock Low Extension (207)22.3.4. SCL Low Timeout (207)22.3.5. SCL High (SMBus Free) Timeout (208)22.4. Using the SMBus (208)22.4.1. SMBus Configuration Register (208)22.4.2. SMBus Timing Control Register (210)22.4.3. SMBnCN Control Register (214)22.4.3.1. Software ACK Generation (214)22.4.3.2. Hardware ACK Generation (214)22.4.4. Hardware Slave Address Recognition (217)22.4.5. Data Register (221)22.5. SMBus Transfer Modes (223)22.5.1. Write Sequence (Master) (223)22.5.2. Read Sequence (Master) (224)22.5.3. Write Sequence (Slave) (225)22.5.4. Read Sequence (Slave) (226)22.6. SMBus Status Decoding (226)23. UART0 (232)23.1. Enhanced Baud Rate Generation (233)23.2. Operational Modes (234)23.2.1. 8-Bit UART (234)23.2.2. 9-Bit UART (235)23.3. Multiprocessor Communications (236)24. UART1 (240)24.1. Baud Rate Generator (241)24.2. Data Format (242)24.3. Configuration and Operation (243)24.3.1. Data Transmission (243)24.3.2. Data Reception (243)24.3.3. Multiprocessor Communications (244)25. Enhanced Serial Peripheral Interface (SPI0) (250)25.1. Signal Descriptions (251)25.1.1. Master Out, Slave In (MOSI) (251)25.1.2. Master In, Slave Out (MISO) (251)25.1.3. Serial Clock (SCK) (251)25.1.4. Slave Select (NSS) (251)25.2. SPI0 Master Mode Operation (251)25.3. SPI0 Slave Mode Operation (253)25.4. SPI0 Interrupt Sources (254)25.5. Serial Clock Phase and Polarity (254)25.6. SPI Special Function Registers (256)26. Timers (263)26.1. Timer 0 and Timer 1 (266)26.1.1. Mode 0: 13-bit Counter/Timer (266)26.1.2. Mode 1: 16-bit Counter/Timer (267)26.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload (267)26.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only) (268)26.2. Timer 2 (274)26.2.1. 16-bit Timer with Auto-Reload (274)26.2.2. 8-bit Timers with Auto-Reload (275)26.2.3. Timer 2 Capture Modes: USB Start-of-Frame or LFO Falling Edge (275)26.3. Timer 3 (281)26.3.1. 16-bit Timer with Auto-Reload (281)26.3.2. 8-bit Timers with Auto-Reload (282)26.3.3. Timer 3 Capture Modes: USB Start-of-Frame or LFO Falling Edge (282)26.4. Timer 4 (288)26.4.1. 16-bit Timer with Auto-Reload (288)26.4.2. 8-bit Timers with Auto-Reload (289)26.5. Timer 5 (293)26.5.1. 16-bit Timer with Auto-Reload (293)26.5.2. 8-bit Timers with Auto-Reload (294)27. Programmable Counter Array (298)27.1. PCA Counter/Timer (299)27.2. PCA0 Interrupt Sources (300)27.3. Capture/Compare Modules (301)27.3.1. Edge-triggered Capture Mode (302)27.3.2. Software Timer (Compare) Mode (303)27.3.3. High-Speed Output Mode (304)27.3.4. Frequency Output Mode (305)27.3.5. 8-bit Pulse Width Modulator Mode (306)27.3.6. 16-Bit Pulse Width Modulator Mode (307)27.4. Watchdog Timer Mode (308)27.4.1. Watchdog Timer Operation (308)27.4.2. Watchdog Timer Usage (309)27.5. Register Descriptions for PCA0 (311)28. C2 Interface (316)28.1. C2 Interface Registers (316)28.2. C2 Pin Sharing (319)Document Change List (320)Contact Information (321)List of FiguresFigure1.1. C8051F380/2/4/6 Block Diagram (18)Figure1.2. C8051F381/3/5/7/C Block Diagram (19)Figure3.1. TQFP-48 Pinout Diagram (Top View) (25)Figure3.2. TQFP-48 Package Diagram (26)Figure3.3. TQFP-48 Recommended PCB Land Pattern (27)Figure3.4. LQFP-32 Pinout Diagram (Top View) (28)Figure3.5. LQFP-32 Package Diagram (29)Figure3.6. LQFP-32 Recommended PCB Land Pattern (30)Figure3.7. QFN-32 Pinout Diagram (Top View) (31)Figure3.8. QFN-32 Package Drawing (32)Figure3.9. QFN-32 Recommended PCB Land Pattern (33)Figure4.1. Connection Diagram with Voltage Regulator Used and No USB (34)Figure4.2. Connection Diagram with Voltage Regulator Not Used and No USB (34)Figure4.3. Connection Diagram with Voltage Regulator Used and USB Connected (Bus-Powered) (35)Figure4.4. Connection Diagram with Voltage Regulator Used and USB Connected (Self-Powered) (35)Figure4.5. Connection Diagram for USB Pins (36)Figure4.6. Connection Diagram for Internal Voltage Reference (36)Figure6.1. ADC0 Functional Block Diagram (46)Figure6.2. Typical Temperature Sensor Transfer Function (48)Figure6.3. Temperature Sensor Error with 1-Point Calibration (49)Figure6.4. 10-Bit ADC Track and Conversion Example Timing (51)Figure6.5. ADC0 Equivalent Input Circuits (52)Figure6.6. ADC Window Compare Example: Right-Justified Data (58)Figure6.7. ADC Window Compare Example: Left-Justified Data (58)Figure7.1. Voltage Reference Functional Block Diagram (62)Figure8.1. Comparator0 Functional Block Diagram (64)Figure8.2. Comparator1 Functional Block Diagram (65)Figure8.3. Comparator Hysteresis Plot (66)Figure8.4. Comparator Input Multiplexer Block Diagram (71)Figure11.1. CIP-51 Block Diagram (79)Figure13.1. On-Chip Memory Map for 64kB Devices (C8051F380/1/4/5) (89)Figure13.2. On-Chip Memory Map for 32kB Devices (C8051F382/3/6/7) (90)Figure13.3. On-Chip Memory Map for 16kB Devices (C8051F38C) (91)Figure14.1. USB FIFO Space and XRAM Memory Map with USBFAE set to ‘1’ (94)Figure14.2. Multiplexed Configuration Example (98)Figure14.3. Non-multiplexed Configuration Example (99)Figure14.4. EMIF Operating Modes (100)Figure14.5. Non-Multiplexed 16-bit MOVX Timing (104)Figure14.6. Non-multiplexed 8-bit MOVX without Bank Select Timing (105)Figure14.7. Non-multiplexed 8-bit MOVX with Bank Select Timing (106)Figure14.8. Multiplexed 16-bit MOVX Timing (107)C8051F380/1/2/3/4/5/6/7/CFigure14.9. Multiplexed 8-bit MOVX without Bank Select Timing (108)Figure14.10. Multiplexed 8-bit MOVX with Bank Select Timing (109)Figure17.1. Reset Sources (129)Figure17.2. Power-On and VDD Monitor Reset Timing (130)Figure18.1. Flash Program Memory Map and Security Byte (137)Figure19.1. Oscillator Options (142)Figure19.2. External Crystal Example (150)Figure20.1. Port I/O Functional Block Diagram (Port 0 through Port 3) (153)Figure20.2. Port I/O Cell Block Diagram (154)Figure20.3. Peripheral Availability on Port I/O Pins (155)Figure20.4. Crossbar Priority Decoder in Example Configuration(No Pins Skipped) (156)Figure20.5. Crossbar Priority Decoder in Example Configuration (3 Pins Skipped) (157)Figure21.1. USB0 Block Diagram (172)Figure21.2. USB0 Register Access Scheme (175)Figure21.3. USB FIFO Allocation (181)Figure22.1. SMBus Block Diagram (205)Figure22.2. Typical SMBus Configuration (206)Figure22.3. SMBus Transaction (207)Figure22.4. Typical SMBus SCL Generation (209)Figure22.5. Typical Master Write Sequence (223)Figure22.6. Typical Master Read Sequence (224)Figure22.7. Typical Slave Write Sequence (225)Figure22.8. Typical Slave Read Sequence (226)Figure23.1. UART0 Block Diagram (232)Figure23.2. UART0 Baud Rate Logic (233)Figure23.3. UART Interconnect Diagram (234)Figure23.4. 8-Bit UART Timing Diagram (234)Figure23.5. 9-Bit UART Timing Diagram (235)Figure23.6. UART Multi-Processor Mode Interconnect Diagram (236)Figure24.1. UART1 Block Diagram (240)Figure24.2. UART1 Timing Without Parity or Extra Bit (242)Figure24.3. UART1 Timing With Parity (242)Figure24.4. UART1 Timing With Extra Bit (242)Figure24.5. Typical UART Interconnect Diagram (243)Figure24.6. UART Multi-Processor Mode Interconnect Diagram (244)Figure25.1. SPI Block Diagram (250)Figure25.2. Multiple-Master Mode Connection Diagram (252)Figure25.3. 3-Wire Single Master and 3-Wire Single Slave Mode Connection Diagram (252)Figure25.4. 4-Wire Single Master Mode and 4-Wire Slave Mode Connection Diagram (253)Figure25.5. Master Mode Data/Clock Timing (255)Figure25.6. Slave Mode Data/Clock Timing (CKPHA = 0) (255)C8051F380/1/2/3/4/5/6/7/C Figure25.7. Slave Mode Data/Clock Timing (CKPHA = 1) (256)Figure25.8. SPI Master Timing (CKPHA = 0) (260)Figure25.9. SPI Master Timing (CKPHA = 1) (260)Figure25.10. SPI Slave Timing (CKPHA = 0) (261)Figure25.11. SPI Slave Timing (CKPHA = 1) (261)Figure26.1. T0 Mode 0 Block Diagram (267)Figure26.2. T0 Mode 2 Block Diagram (268)Figure26.3. T0 Mode 3 Block Diagram (269)Figure26.4. Timer 2 16-Bit Mode Block Diagram (274)Figure26.5. Timer 2 8-Bit Mode Block Diagram (275)Figure26.6. Timer2 Capture Mode (T2SPLIT = 0) (276)Figure26.7. Timer2 Capture Mode (T2SPLIT = 0) (277)Figure26.8. Timer 3 16-Bit Mode Block Diagram (281)Figure26.9. Timer 3 8-Bit Mode Block Diagram (282)Figure26.10. Timer3 Capture Mode (T3SPLIT = 0) (283)Figure26.11. Timer3 Capture Mode (T3SPLIT = 0) (284)Figure26.12. Timer 4 16-Bit Mode Block Diagram (288)Figure26.13. Timer 4 8-Bit Mode Block Diagram (289)Figure26.14. Timer 5 16-Bit Mode Block Diagram (293)Figure26.15. Timer 5 8-Bit Mode Block Diagram (294)Figure27.1. PCA Block Diagram (298)Figure27.2. PCA Counter/Timer Block Diagram (299)Figure27.3. PCA Interrupt Block Diagram (300)Figure27.4. PCA Capture Mode Diagram (302)Figure27.5. PCA Software Timer Mode Diagram (303)Figure27.6. PCA High-Speed Output Mode Diagram (304)Figure27.7. PCA Frequency Output Mode (305)Figure27.8. PCA 8-Bit PWM Mode Diagram (306)Figure27.9. PCA 16-Bit PWM Mode (307)Figure27.10. PCA Module 4 with Watchdog Timer Enabled (308)Figure28.1. Typical C2 Pin Sharing (319)List of TablesTable1.1. Product Selection Guide (17)Table2.1. C8051F38x Replacement Part Numbers (20)Table3.1. Pin Definitions for the C8051F380/1/2/3/4/5/6/7/C (22)Table3.2. TQFP-48 Package Dimensions (26)Table3.3. TQFP-48 PCB Land Pattern Dimensions (27)Table3.4. LQFP-32 Package Dimensions (29)Table3.5. LQFP-32 PCB Land Pattern Dimensions (30)Table3.6. QFN-32 Package Dimensions (32)Table3.7. QFN-32 PCB Land Pattern Dimensions (33)Table5.1. Absolute Maximum Ratings (37)Table5.2. Global Electrical Characteristics (38)Table5.3. Port I/O DC Electrical Characteristics (39)Table5.4. Reset Electrical Characteristics (39)Table5.5. Internal Voltage Regulator Electrical Characteristics (40)Table5.6. Flash Electrical Characteristics (40)Table5.7. Internal High-Frequency Oscillator Electrical Characteristics (41)Table5.8. Internal Low-Frequency Oscillator Electrical Characteristics (41)Table5.9. External Oscillator Electrical Characteristics (41)Table5.10. ADC0 Electrical Characteristics (42)Table5.11. Temperature Sensor Electrical Characteristics (43)Table5.12. Voltage Reference Electrical Characteristics (43)Table5.13. Comparator Electrical Characteristics (44)Table5.14. USB Transceiver Electrical Characteristics (45)Table11.1. CIP-51 Instruction Set Summary (81)Table14.1. AC Parameters for External Memory Interface (110)Table15.1. Special Function Register (SFR) Memory Map (112)Table15.2. Special Function Registers (113)Table16.1. Interrupt Summary (120)Table21.1. Endpoint Addressing Scheme (173)Table21.2. USB0 Controller Registers (178)Table21.3. FIFO Configurations (182)Table22.1. SMBus Clock Source Selection (209)Table22.2. Minimum SDA Setup and Hold Times (210)Table22.3. Sources for Hardware Changes to SMBnCN (217)Table22.4. Hardware Address Recognition Examples (EHACK = 1) (218)Table22.5. SMBus Status Decoding: Hardware ACK Disabled (EHACK = 0) (227)Table22.6. SMBus Status Decoding: Hardware ACK Enabled (EHACK = 1) (229)Table23.1. Timer Settings for Standard Baud Rates Using Internal Oscillator (238)Table24.1. Baud Rate Generator Settings for Standard Baud Rates (241)Table25.1. SPI Slave Timing Parameters (262)Table27.1. PCA Timebase Input Options (299)Table27.2. PCA0CPM Bit Settings for PCA Capture/Compare Modules (301)Table27.3. Watchdog Timer Timeout Intervals1 (310)List of RegistersSFR Definition6.1. ADC0CF: ADC0 Configuration (53)SFR Definition6.2. ADC0H: ADC0 Data Word MSB (54)SFR Definition6.3. ADC0L: ADC0 Data Word LSB (54)SFR Definition6.4. ADC0CN: ADC0 Control (55)SFR Definition6.5. ADC0GTH: ADC0 Greater-Than Data High Byte (56)SFR Definition6.6. ADC0GTL: ADC0 Greater-Than Data Low Byte (56)SFR Definition6.7. ADC0LTH: ADC0 Less-Than Data High Byte (57)SFR Definition6.8. ADC0LTL: ADC0 Less-Than Data Low Byte (57)SFR Definition6.9. AMX0P: AMUX0 Positive Channel Select (60)SFR Definition6.10. AMX0N: AMUX0 Negative Channel Select (61)SFR Definition7.1. REF0CN: Reference Control (63)SFR Definition8.1. CPT0CN: Comparator0 Control (67)SFR Definition8.2. CPT0MD: Comparator0 Mode Selection (68)SFR Definition8.3. CPT1CN: Comparator1 Control (69)SFR Definition8.4. CPT1MD: Comparator1 Mode Selection (70)SFR Definition8.5. CPT0MX: Comparator0 MUX Selection (72)SFR Definition8.6. CPT1MX: Comparator1 MUX Selection (73)SFR Definition9.1. REG01CN: Voltage Regulator Control (75)SFR Definition10.1. PCON: Power Control (78)SFR Definition11.1. DPL: Data Pointer Low Byte (85)SFR Definition11.2. DPH: Data Pointer High Byte (85)SFR Definition11.3. SP: Stack Pointer (86)SFR Definition11.4. ACC: Accumulator (86)SFR Definition11.5. B: B Register (86)SFR Definition11.6. PSW: Program Status Word (87)SFR Definition12.1. PFE0CN: Prefetch Engine Control (88)SFR Definition14.1. EMI0CN: External Memory Interface Control (96)SFR Definition14.2. EMI0CF: External Memory Interface Configuration (97)SFR Definition14.3. EMI0TC: External Memory TIming Control (103)SFR Definition15.1. SFRPAGE: SFR Page (111)SFR Definition16.1. IE: Interrupt Enable (121)SFR Definition16.2. IP: Interrupt Priority (122)SFR Definition16.3. EIE1: Extended Interrupt Enable 1 (123)SFR Definition16.4. EIP1: Extended Interrupt Priority 1 (124)SFR Definition16.5. EIE2: Extended Interrupt Enable 2 (125)SFR Definition16.6. EIP2: Extended Interrupt Priority 2 (126)SFR Definition16.7. IT01CF: INT0/INT1 ConfigurationO (128)SFR Definition17.1. VDM0CN: VDD Monitor Control (132)SFR Definition17.2. RSTSRC: Reset Source (134)SFR Definition18.1. PSCTL: Program Store R/W Control (139)SFR Definition18.2. FLKEY: Flash Lock and Key (140)SFR Definition18.3. FLSCL: Flash Scale (141)SFR Definition19.1. CLKSEL: Clock Select (144)C8051F380/1/2/3/4/5/6/7/CSFR Definition19.2. OSCICL: Internal H-F Oscillator Calibration (145)SFR Definition19.3. OSCICN: Internal H-F Oscillator Control (146)SFR Definition19.4. CLKMUL: Clock Multiplier Control (147)SFR Definition19.5. OSCLCN: Internal L-F Oscillator Control (148)SFR Definition19.6. OSCXCN: External Oscillator Control (152)SFR Definition20.1. XBR0: Port I/O Crossbar Register 0 (159)SFR Definition20.2. XBR1: Port I/O Crossbar Register 1 (160)SFR Definition20.3. XBR2: Port I/O Crossbar Register 2 (161)SFR Definition20.4. P0: Port 0 (162)SFR Definition20.5. P0MDIN: Port 0 Input Mode (162)SFR Definition20.6. P0MDOUT: Port 0 Output Mode (163)SFR Definition20.7. P0SKIP: Port 0 Skip (163)SFR Definition20.8. P1: Port 1 (164)SFR Definition20.9. P1MDIN: Port 1 Input Mode (164)SFR Definition20.10. P1MDOUT: Port 1 Output Mode (165)SFR Definition20.11. P1SKIP: Port 1 Skip (165)SFR Definition20.12. P2: Port 2 (166)SFR Definition20.13. P2MDIN: Port 2 Input Mode (166)SFR Definition20.14. P2MDOUT: Port 2 Output Mode (167)SFR Definition20.15. P2SKIP: Port 2 Skip (167)SFR Definition20.16. P3: Port 3 (168)SFR Definition20.17. P3MDIN: Port 3 Input Mode (168)SFR Definition20.18. P3MDOUT: Port 3 Output Mode (169)SFR Definition20.19. P3SKIP: Port 3 Skip (169)SFR Definition20.20. P4: Port 4 (170)SFR Definition20.21. P4MDIN: Port 4 Input Mode (170)SFR Definition20.22. P4MDOUT: Port 4 Output Mode (171)SFR Definition21.1. USB0XCN: USB0 Transceiver Control (174)SFR Definition21.2. USB0ADR: USB0 Indirect Address (176)SFR Definition21.3. USB0DAT: USB0 Data (177)USB Register Definition21.4. INDEX: USB0 Endpoint Index (179)USB Register Definition21.5. CLKREC: Clock Recovery Control (180)USB Register Definition21.6. FIFOn: USB0 Endpoint FIFO Access (182)USB Register Definition21.7. FADDR: USB0 Function Address (183)USB Register Definition21.8. POWER: USB0 Power (185)USB Register Definition21.9. FRAMEL: USB0 Frame Number Low (186)USB Register Definition21.10. FRAMEH: USB0 Frame Number High (186)USB Register Definition21.11. IN1INT: USB0 IN Endpoint Interrupt (187)USB Register Definition21.12. OUT1INT: USB0 OUT Endpoint Interrupt (188)USB Register Definition21.13. CMINT: USB0 Common Interrupt (189)USB Register Definition21.14. IN1IE: USB0 IN Endpoint Interrupt Enable (190)USB Register Definition21.15. OUT1IE: USB0 OUT Endpoint Interrupt Enable (191)USB Register Definition21.16. CMIE: USB0 Common Interrupt Enable (192)USB Register Definition21.17. E0CSR: USB0 Endpoint0 Control (195)USB Register Definition21.18. E0CNT: USB0 Endpoint0 Data Count (196)C8051F380/1/2/3/4/5/6/7/C USB Register Definition21.19. EENABLE: USB0 Endpoint Enable (197)USB Register Definition21.20. EINCSRL: USB0 IN Endpoint Control Low (199)USB Register Definition21.21. EINCSRH: USB0 IN Endpoint Control High (200)USB Register Definition21.22. EOUTCSRL: USB0 OUT Endpoint Control Low Byte 202 USB Register Definition21.23. EOUTCSRH: USB0 OUT Endpoint Control High Byte (203)USB Register Definition21.24. EOUTCNTL: USB0 OUT Endpoint Count Low (203)USB Register Definition21.25. EOUTCNTH: USB0 OUT Endpoint Count High (204)SFR Definition22.1. SMB0CF: SMBus Clock/Configuration (211)SFR Definition22.2. SMB1CF: SMBus Clock/Configuration (212)SFR Definition22.3. SMBTC: SMBus Timing Control (213)SFR Definition22.4. SMB0CN: SMBus Control (215)SFR Definition22.5. SMB1CN: SMBus Control (216)SFR Definition22.6. SMB0ADR: SMBus0 Slave Address (218)SFR Definition22.7. SMB0ADM: SMBus0 Slave Address Mask (219)SFR Definition22.8. SMB1ADR: SMBus1 Slave Address (219)SFR Definition22.9. SMB1ADM: SMBus1 Slave Address Mask (220)SFR Definition22.10. SMB0DAT: SMBus Data (221)SFR Definition22.11. SMB1DAT: SMBus Data (222)SFR Definition23.1. SCON0: Serial Port 0 Control (237)SFR Definition23.2. SBUF0: Serial (UART0) Port Data Buffer (238)SFR Definition24.1. SCON1: UART1 Control (245)SFR Definition24.2. SMOD1: UART1 Mode (246)SFR Definition24.3. SBUF1: UART1 Data Buffer (247)SFR Definition24.4. SBCON1: UART1 Baud Rate Generator Control (248)SFR Definition24.5. SBRLH1: UART1 Baud Rate Generator High Byte (248)SFR Definition24.6. SBRLL1: UART1 Baud Rate Generator Low Byte (249)SFR Definition25.1. SPI0CFG: SPI0 Configuration (257)SFR Definition25.2. SPI0CN: SPI0 Control (258)SFR Definition25.3. SPI0CKR: SPI0 Clock Rate (259)SFR Definition25.4. SPI0DAT: SPI0 Data (259)SFR Definition26.1. CKCON: Clock Control (264)SFR Definition26.2. CKCON1: Clock Control 1 (265)SFR Definition26.3. TCON: Timer Control (270)SFR Definition26.4. TMOD: Timer Mode (271)SFR Definition26.5. TL0: Timer 0 Low Byte (272)SFR Definition26.6. TL1: Timer 1 Low Byte (272)SFR Definition26.7. TH0: Timer 0 High Byte (273)SFR Definition26.8. TH1: Timer 1 High Byte (273)SFR Definition26.9. TMR2CN: Timer 2 Control (278)SFR Definition26.10. TMR2RLL: Timer 2 Reload Register Low Byte (279)SFR Definition26.11. TMR2RLH: Timer 2 Reload Register High Byte (279)SFR Definition26.12. TMR2L: Timer 2 Low Byte (279)SFR Definition26.13. TMR2H Timer 2 High Byte (280)SFR Definition26.14. TMR3CN: Timer 3 Control (285)C8051F380/1/2/3/4/5/6/7/CSFR Definition26.15. TMR3RLL: Timer 3 Reload Register Low Byte (286)SFR Definition26.16. TMR3RLH: Timer 3 Reload Register High Byte (286)SFR Definition26.17. TMR3L: Timer 3 Low Byte (286)SFR Definition26.18. TMR3H Timer 3 High Byte (287)SFR Definition26.19. TMR4CN: Timer 4 Control (290)SFR Definition26.20. TMR4RLL: Timer 4 Reload Register Low Byte (291)SFR Definition26.21. TMR4RLH: Timer 4 Reload Register High Byte (291)SFR Definition26.22. TMR4L: Timer 4 Low Byte (291)SFR Definition26.23. TMR4H Timer 4 High Byte (292)SFR Definition26.24. TMR5CN: Timer 5 Control (295)SFR Definition26.25. TMR5RLL: Timer 5 Reload Register Low Byte (296)SFR Definition26.26. TMR5RLH: Timer 5 Reload Register High Byte (296)SFR Definition26.27. TMR5L: Timer 5 Low Byte (296)SFR Definition26.28. TMR5H Timer 5 High Byte (297)SFR Definition27.1. PCA0CN: PCA Control (311)SFR Definition27.2. PCA0MD: PCA Mode (312)SFR Definition27.3. PCA0CPMn: PCA Capture/Compare Mode (313)SFR Definition27.4. PCA0L: PCA Counter/Timer Low Byte (314)SFR Definition27.5. PCA0H: PCA Counter/Timer High Byte (314)SFR Definition27.6. PCA0CPLn: PCA Capture Module Low Byte (315)SFR Definition27.7. PCA0CPHn: PCA Capture Module High Byte (315)C2 Register Definition28.1. C2ADD: C2 Address (316)C2 Register Definition28.2. DEVICEID: C2 Device ID (317)C2 Register Definition28.3. REVID: C2 Revision ID (317)C2 Register Definition28.4. FPCTL: C2 Flash Programming Control (318)C2 Register Definition28.5. FPDAT: C2 Flash Programming Data (318)。

xilinx fifo generator 用法

xilinx fifo generator 用法Xilinx FIFO Generator是一款强大的工具,它能够根据用户的需求自动生成FIFO(First-In-First-Out)数据缓冲器。

FIFO是一种常用的存储结构,用于在数据输入和输出之间提供缓冲,以解决数据同步和延迟问题。

本文将详细介绍Xilinx FIFO Generator的使用方法。

一、安装与配置首先,确保你已经正确安装了Xilinx Vivado工具,并且你的设计项目已经创建并配置好。

接下来,打开Vivado并进入你的设计项目。

二、使用FIFO Generator1. 打开Xilinx FIFO Generator对话框:在Vivado主界面,选择“Library”>“Generic Memory Block”>“FIFO Generator”。

2. 输入参数:在生成的对话框中,你需要输入一些参数,包括输入数据位宽、输出数据位宽、深度等。

确保根据你的设计需求设置这些参数。

3. 生成FIFO:点击“Generate”按钮,Xilinx FIFO Generator将根据你提供的参数生成相应的FIFO数据缓冲器。

三、在设计中使用FIFO1. 导入生成的文件:在Vivado主界面,选择“Project Navigator”>“导入”>“文件系统”,找到你生成的FIFO文件并导入。

2. 配置连接:根据你的设计需求,配置FIFO与输入和输出信号的连接。

通常,FIFO的输入和输出信号是通过引脚连接的。

3. 放置并连接:在设计中找到合适的位置放置FIFO,并使用适当的线缆将FIFO的输入和输出引脚连接到你的设计。

4. 验证连接:在完成布局后,使用仿真工具验证FIFO与你的设计之间的连接是否正确。

四、使用注意事项在使用Xilinx FIFO Generator时,有一些注意事项需要了解:1. 确保你的设计项目已经正确配置了Xilinx Vivado工具,并且已经安装了所需的Xilinx IP核。

FPGA高速ADC接口实战——250MSPS采样率ADC9481

FPGA⾼速ADC接⼝实战——250MSPS采样率ADC9481⼀、前⾔ 最近忙于硕⼠毕业设计和论⽂,没有太多时间编写博客,现总结下之前在某个项⽬中⽤到的⼀个⾼速ADC接⼝设计部分。

ADC这⼀器件经常⽤于⽆线通信、传感、测试测量等领域。

⽬前数字系统对⾼速数据采集的需求与⽇俱增,本⽂使⽤了⽶联客的⼀款速率较⾼的AD/DA模块ADQ9481来阐述利⽤FPGA设计⾼速ADC接⼝的技术要点。

⼆、ADC硬件特性分析 ⾸先必须通过datasheet分析其核⼼参数、接⼝定义和时序要求。

ADC9481的采样率为250MSPS,精度8bit。

其原理结构图如下: 主要引脚说明: CLK+-:差分时钟输⼊,信号频率为250MHz VIN+-:模拟信号输⼊,范围是1Vpp VREF:电压参考输⼊/输出,这⾥使⽤内部固定参考电压模式 SENSE:参考模式选择 D7A~D0A:通道A数字信号输出 D7B~D0B:通道B数字信号输出 DCO+-:数字差分时钟输出,信号频率为125MHz S1:数据格式选择,该接⼝电压决定数格式时原码还是补码 PDWN:低功耗选通 接下来看看接⼝时序: 很容易看出A和B两个数字输出通道是交替输出的,通道A在DCO+上升沿输出,B在DCO-上升沿输出。

DCO+-的频率仅是采样率250MHz的⼀半,也就是降低了对数字系统处理速率的要求。

三、ADC接⼝设计 根据上述时序关系可知,FPGA端需要在DCO+上升沿采集通道B数据,在DCO-上升沿采集通道A数据。

并且由于在DCO+-同⼀变化沿时刻,通道A为前⼀个数据,因此要注意数据的采集顺序。

这类数据采集的普遍做法是将数据存⼊到RAM中,然后利⽤本地时钟同步。

具体⽅法是:按照两通道的数据顺序对数据进⾏拼接,之后缓存到异步FIFO中。

本地PLL⽣成的125MHz时钟作为读侧和后续处理时钟信号。

这⾥就要利⽤Xilinx FPGA的“原语”中的IBUFDS+BUFG,依次是差分输⼊缓冲器和全局缓冲器。

vivado FIFO使用总结

概述在新型地检项目中使用FIFO进行数据传输,记录使用中遇到的问题vivado中调用IP及介绍运行环境vivado2017.41.在IP Catalog中查找FIFO,选择FIFO Generator2.弹出界面中,根据需要选择异步FIFO或同步FIFO,本项目中选择异步FIFO。

(一般选择带有1、2、4、5的选项)[MISSING IMAGE: , ]3.选择Native Ports,a部分表示是两种模式,一种标准FIFO,一种First Word Fall Through,这两种模式的区别在于标准模式下数据在读使能置1之后延迟一拍输出,First Word Fall Through模式下,读使能与数据同步输出。

b部分设置输入输出的数据位宽。

c部分,设置复位引脚,如果选中Reset Pin,则默认是异步复位,如果想单独复位读写,取消选中的 Enable Reset Synchronization,默认复位之后FULL标志为1,数据输出0,用户需要可自行在C部分更改。

4.选择Status Flags,在Handshaking Options中选中Valid Flag,默认拉高,有效利用此标志位,可以简化程序。

5.Data Counts,读写计数,可以不勾选。

6.最后一栏是设置好的一些状态。

问题及解决方法1.问题:使能与数据不是在相同钟下产生,数据写不进去。

解决:若使用读写时钟不同的FIFO,需要让写时钟、写使能、写数据同步,读时钟、读使能、读数据同步。

2.问题:标准FIFO数据延迟解决:如图所示,标准FIFO在rd_en拉高之后,延迟一个时钟周期,dout输出数据,此时若将数据再写入寄存器,则还需要延迟一个时钟周期,。

3. 对于异步FIFO,在使用时需要将复位的时间拉长,仿真中发现若FULL标志在设置IP核时置1,在37us左右才会置0,此时才可以将数据写入FIFO,将复位设置40us,仿真结果正确出现。

异步FIFO的实现

异步FIFO的实现2012-05-01 01:41:47| 分类:实例分享| 标签:异步fifo 格雷码跨时钟域 function 函数|字号大中小订阅以下是一个异步FIFO的实现代码,实现的是一个FWFT的异步FIFO功能,与Xilinx CORE Generator生成FIFO功能、时序一模一样。

其中,simple_dual_port_ram 是一个Xilinx的简单双端口RAM,可以很简单的移植到其他厂商的FPGA中。

在产生空满信号的判断时,需要将读操作侧的地址传递到写操作侧,将写操作地址传递读操作侧,为了减少读写地址的位翻转率,从而减少亚稳态的发生,在将地址跨越时钟域之前首先转换成格雷码,跨越时钟域并正常采样以后再恢复成二进制的地址。

由于模块中多次使用到将格雷码转换成二进制码以及将二进制码转换成格雷码,所以将格雷码与二进制码的转换使用了两个函数(function)来实现,方便在代码中不同处调用。

跨越时钟域时,为了隔断亚稳态的传递,首先要用两级寄存器对另一时钟域产生的地址打两拍,这样子即使有亚稳态发生,也能被阻隔在两级寄存器中。

尽管打两拍能阻断亚稳态的传递,但是不能避免跨时钟域时采样错误的发生,使用格雷码的作用是使得错误仅发生在其中一个位上。

代码中RAM输入和输出都没有使用到寄存器,读者可以根据自己的需要定制满足自己要求的FIFO,在写操作侧或读操作侧加寄存器。

代码中数据的位宽和地址的位宽,亦可以根据读者的需要修改。

尽管本文提供了异步FIFO的完整实现代码,博主还是建议各位读者在使用FIFO 时尽量多用CORE Generator生成的FIFO,那样会更加可靠稳定,使用起来也更方便。

代码://********************************************************************************************************** ******// Copyright(c) 2012, Technology Endless - Creative Boundless , All right reserved// Filename : asynfifo.v// Author : lucien// Email : intellectuallib@// Date : Apr 22th, 2012// Version : 1.0// Company :// Description : asynchronous FIFO(first in first out)// Modification History// Date By Revision Change Description// ---------------------------------------------------------------------------------------// 2012/04/22 Lucien 1.0 Original//********************************************************************************************************** ******`timescale 1ns/1psmodule asynfifo(rst ,wr_clk ,wr_en ,din ,full ,rd_clk ,rd_en ,dout ,empty);input wire rst ;//reset signalinput wire wr_clk ;//clock of read clock fieldinput wire wr_en ;//write enableinput wire [7:0] din ;output wire full ;input wire rd_clk ;//clock of write clock fieldinput wire rd_en ;output wire [7:0] dout ;output wire empty ;/********************************************************************************************************** ****//********************************************************************************************************** ****\* define internal signals * \********************************************************************************************************** ****/reg [7:0] waddr; //write address in write clock fieldreg [7:0] raddr; //read address in read clock fieldwire [7:0] waddr_gray_wclk; //the gray code of write address in write clock fieldwire [7:0] raddr_gray_rclk; //the gray code of read address in read clock fieldreg [7:0] waddr_gray_rclk_0; //the dealyed gray codes of write address in read clock field reg [7:0] waddr_gray_rclk_1;reg [7:0] raddr_gray_wclk_0; //the dealyed gray codes of read address in write clock field reg [7:0] raddr_gray_wclk_1;wire [7:0] waddr_rclk; //write address in read clock fieldwire [7:0] raddr_wclk; //read address in write clock fieldreg [8:0] count_wclk; //the data counter in write clock fieldreg [8:0] count_rclk; //the data counter in read clock fieldfunction [7:0] binary_to_gray;input [7:0] binary_code ;beginbinary_to_gray[0]=binary_code[0]^binary_code[1];binary_to_gray[1]=binary_code[1]^binary_code[2];binary_to_gray[2]=binary_code[2]^binary_code[3];binary_to_gray[3]=binary_code[3]^binary_code[4];binary_to_gray[4]=binary_code[4]^binary_code[5];binary_to_gray[5]=binary_code[5]^binary_code[6];binary_to_gray[6]=binary_code[6]^binary_code[7];binary_to_gray[7]=binary_code[7];endendfunctionfunction [7:0] gray_to_binary;input [7:0] gray_code ;begingray_to_binary[7]=waddr_gray_rclk_1[7];gray_to_binary[6]=waddr_gray_rclk_1[6]^gray_to_binary[7];gray_to_binary[5]=waddr_gray_rclk_1[5]^gray_to_binary[6];gray_to_binary[4]=waddr_gray_rclk_1[4]^gray_to_binary[5];gray_to_binary[3]=waddr_gray_rclk_1[3]^gray_to_binary[4];gray_to_binary[2]=waddr_gray_rclk_1[2]^gray_to_binary[3];gray_to_binary[1]=waddr_gray_rclk_1[1]^gray_to_binary[2];gray_to_binary[0]=waddr_gray_rclk_1[0]^gray_to_binary[1]; endendfunctionsimple_dual_port_ram U_simple_dual_port_ram(.clka (wr_clk ),.wea (wr_en ),.addra (waddr ),.dina (din ),.clkb (rd_clk ),.addrb (raddr ),.doutb (dout ));assign empty = (count_rclk[8:0] == 9'h0);assign full = (count_rclk[8:0] == 9'h100);assign waddr_gray_wclk = binary_to_gray(waddr);assign raddr_gray_rclk = binary_to_gray(raddr);assign waddr_rclk = gray_to_binary(waddr_gray_rclk_1);assign raddr_wclk = gray_to_binary(raddr_gray_wclk_1);always@(posedge wr_clk or posedge rst)beginif(rst == 1'b1)waddr <= 8'h0;elseif(wr_en==1'b1)waddr <= waddr + 8'h1;elsewaddr <= waddr;endalways@(posedge rd_clk or posedge rst)beginif(rst == 1'b1)raddr <= 8'h0;elseif(wr_en==1'b1)raddr <= raddr + 8'h1;elseraddr <= raddr;endalways@(posedge wr_clk or posedge rst)beginif(rst == 1'b1)beginraddr_gray_wclk_0<=8'b0;raddr_gray_wclk_1<=8'b0;endelsebeginraddr_gray_wclk_0<=raddr_gray_rclk;raddr_gray_wclk_1<=raddr_gray_wclk_0;endendalways@(posedge rd_clk or posedge rst)beginif(rst == 1'b1)beginwaddr_gray_rclk_0<=8'b0;waddr_gray_rclk_1<=8'b0;endelsebeginwaddr_gray_rclk_0<=waddr_gray_wclk;waddr_gray_rclk_1<=waddr_gray_rclk_0;endendalways@(posedge wr_clk or posedge rst)beginif(rst == 1'b1)count_wclk <= 9'h0;elseif(waddr < raddr_wclk)count_wclk <= waddr + 9'h100 - raddr_wclk;else if((count_wclk > 9'h0) && (waddr == raddr_wclk)) count_wclk <= 9'h100;elsecount_wclk <= waddr - raddr_wclk;endalways@(posedge rd_clk or posedge rst)beginif(rst == 1'b1)count_rclk <= 9'h0;elseif(waddr_rclk < raddr)count_rclk <= waddr_rclk + 9'h100 - raddr;else if((count_rclk > 9'h0) && (waddr_rclk == raddr)) count_rclk <= 9'h100;elsecount_rclk <= waddr_rclk - raddr;endendmodule。

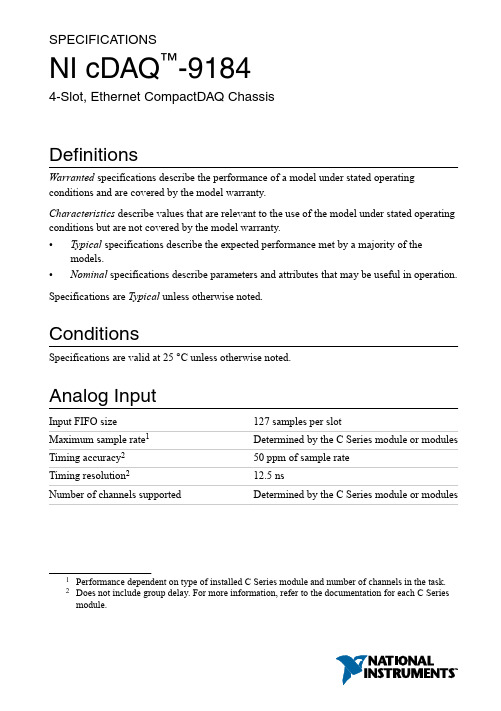

NI cDAQ

SPECIFICA TIONSNI cDAQ™-91844-Slot, Ethernet CompactDAQ ChassisDefinitionsWarranted specifications describe the performance of a model under stated operating conditions and are covered by the model warranty.Characteristics describe values that are relevant to the use of the model under stated operating conditions but are not covered by the model warranty.•Typical specifications describe the expected performance met by a majority of the models.•Nominal specifications describe parameters and attributes that may be useful in operation. Specifications are Typical unless otherwise noted.ConditionsSpecifications are valid at 25 °C unless otherwise noted.Analog InputInput FIFO size127 samples per slotMaximum sample rate1Determined by the C Series module or modules Timing accuracy250 ppm of sample rateTiming resolution212.5 nsNumber of channels supported Determined by the C Series module or modules 1Performance dependent on type of installed C Series module and number of channels in the task.2Does not include group delay. For more information, refer to the documentation for each C Series module.Analog OutputNumber of channels supportedHardware-timed taskOnboard regeneration16Non-regeneration Determined by the C Series module or modules Non-hardware-timed task Determined by the C Series module or modules Maximum update rateOnboard regeneration 1.6 MS/s (multi-channel, aggregate)Non-regeneration Determined by the C Series module or modules Timing accuracy50 ppm of sample rateTiming resolution12.5 nsOutput FIFO sizeOnboard regeneration8,191 samples shared among channels used Non-regeneration127 samples per slotAO waveform modes Non-periodic waveform,periodic waveform regeneration mode fromonboard memory,periodic waveform regeneration from hostbuffer including dynamic updateDigital Waveform CharacteristicsWaveform acquisition (DI) FIFOParallel modules511 samples per slotSerial modules63 samples per slotWaveform generation (DO) FIFOParallel modules2,047 samples per slotSerial modules63 samples per slotDigital input sample clock frequencyStreaming to application memory System-dependentFinite0 MHz to 10 MHz2| | NI cDAQ-9184 SpecificationsDigital output sample clock frequencyStreaming from application memory System-dependentRegeneration from FIFO0 MHz to 10 MHzFinite0 MHz to 10 MHzTiming accuracy50 ppmGeneral-Purpose Counters/TimersNumber of counters/timers4Resolution32 bitsCounter measurements Edge counting, pulse, semi-period, period,two-edge separation, pulse widthPosition measurements X1, X2, X4 quadrature encoding withChannel Z reloading; two-pulse encoding Output applications Pulse, pulse train with dynamic updates,frequency division, equivalent time sampling Internal base clocks80 MHz, 20 MHz, 100 kHzExternal base clock frequency0 MHz to 20 MHzBase clock accuracy50 ppmOutput frequency0 MHz to 20 MHzInputs Gate, Source, HW_Arm, Aux, A, B, Z,Up_DownRouting options for inputs Any module PFI, analog trigger, many internalsignalsFIFO Dedicated 127-sample FIFOFrequency GeneratorNumber of channels1Base clocks20 MHz, 10 MHz, 100 kHzDivisors 1 to 16 (integers)Base clock accuracy50 ppmOutput Any module PFI terminalNI cDAQ-9184 Specifications| © National Instruments| 3Module PFI CharacteristicsFunctionality Static digital input, static digital output, timinginput, and timing outputTiming output sources3Many analog input, analog output, counter,digital input, and digital output timing signals Timing input frequency0 MHz to 20 MHzTiming output frequency0 MHz to 20 MHzDigital TriggersSource Any module PFI terminalPolarity Software-selectable for most signalsAnalog input function Start Trigger, Reference Trigger,Pause Trigger, Sample Clock,Sample Clock TimebaseAnalog output function Start Trigger, Pause Trigger, Sample Clock,Sample Clock TimebaseCounter/timer function Gate, Source, HW_Arm, Aux, A, B, Z,Up_DownModule I/O StatesAt power-on Module-dependent. Refer to the documentationfor each C Series module.Network InterfaceNetwork protocols TCP/IP, UDPNetwork ports used HTTP:80 (configuration only), TCP:3580;UDP:5353 (configuration only), TCP:5353(configuration only); TCP:31415; UDP:7865(configuration only), UDP:8473 (configurationonly)Network IP configuration DHCP + Link-Local, DHCP, Static,Link-Local3Actual available signals are dependent on type of installed C Series module.4| | NI cDAQ-9184 SpecificationsHigh-performance data streams7Data stream types available Analog input, analog output, digital input,digital output, counter/timer input,counter/timer output, NI-XNET4Default MTU size1500 bytesJumbo frame support Up to 9000 bytesEthernetNetwork interface1000 Base-TX, full-duplex; 1000 Base-TX,half-duplex; 100 Base-TX, full-duplex;100 Base-TX, half-duplex; 10 Base-T,full-duplex; 10 Base-T, half-duplex Communication rates10/100/1000 Mbps, auto-negotiated Maximum cabling distance100 m/segmentPower RequirementsCaution The protection provided by the NI cDAQ-9184 chassis can be impaired ifit is used in a manner not described in the NI cDAQ-9181/9184/9188/9191 UserManual.Note Some C Series modules have additional power requirements. For moreinformation about C Series module power requirements, refer to the documentationfor each C Series module.Note Sleep mode for C Series modules is not supported in the NI cDAQ-9184.V oltage input range9 V to 30 VMaximum power consumption515 W4When a session is active, CAN or LIN (NI-XNET) C Series modules use a total of two data streams regardless of the number of NI-XNET modules in the chassis.5Includes maximum 1 W module load per slot across rated temperature and product variations.NI cDAQ-9184 Specifications| © National Instruments| 5Note The maximum power consumption specification is based on a fully populatedsystem running a high-stress application at elevated ambient temperature and withall C Series modules consuming the maximum allowed power.Power input connector 2 positions 3.5 mm pitch mini-combicon screwterminal with screw flanges, SauroCTMH020F8-0N001Power input mating connector Sauro CTF020V8, Phoenix Contact 1714977,or equivalentPhysical CharacteristicsWeight (unloaded)Approximately 643 g (22.7 oz)Dimensions (unloaded)178.1 mm × 88.1 mm × 64.3 mm(7.01 in. × 3.47 in. × 2.53 in.) Refer to thefollowing figure.Screw-terminal wiringGauge0.5 mm 2 to 2.1 mm2 (20 AWG to 14 AWG)copper conductor wireWire strip length 6 mm (0.24 in.) of insulation stripped from theendTemperature rating85 °CTorque for screw terminals0.20 N · m to 0.25 N · m (1.8 lb · in. to2.2 lb · in.)Wires per screw terminal One wire per screw terminalConnector securementSecurement type Screw flanges providedTorque for screw flanges0.20 N · m to 0.25 N · m (1.8 lb · in. to2.2 lb · in.)If you need to clean the chassis, wipe it with a dry towel.6| | NI cDAQ-9184 SpecificationsFigure 1. NI cDAQ-9184 Dimensions30.6 mm 47.2 mm Safety VoltagesConnect only voltages that are within these limits.V terminal to C terminal30 V maximum, Measurement Category IMeasurement Category I is for measurements performed on circuits not directly connected to the electrical distribution system referred to as MAINS voltage. MAINS is a hazardous liveNI cDAQ-9184 Specifications | © National Instruments | 7electrical supply system that powers equipment. This category is for measurements of voltages from specially protected secondary circuits. Such voltage measurements include signal levels, special equipment, limited-energy parts of equipment, circuits powered by regulatedlow-voltage sources, and electronics.Caution Do not connect the system to signals or use for measurements withinMeasurement Categories II, III, or IV.Note Measurement Categories CAT I and CAT O (Other) are equivalent. These testand measurement circuits are not intended for direct connection to the MAINsbuilding installations of Measurement Categories CAT II, CAT III, or CAT IV.Environmental-20 °C to 55 °C6Operating temperature (IEC 60068-2-1and IEC 60068-2-2)Caution To maintain product performance and accuracy specifications when theambient temperature is between 45 and 55 °C, you must mount the chassishorizontally to a metal panel or surface using the screw holes or the panel mount kit.Measure the ambient temperature at each side of the CompactDAQ system 63.5 mm(2.5 in.) from the side and 25.4 mm (1.0 in.) from the rear cover of the system. Forfurther information about mounting configurations, go to /info and enterthe Info Code cdaqmounting.-40 °C to 85 °CStorage temperature (IEC 60068-2-1 andIEC 60068-2-2)Ingress protection IP 30Operating humidity (IEC 60068-2-56)10% to 90% RH, noncondensingStorage humidity (IEC 60068-2-56)5% to 95% RH, noncondensingPollution Degree (IEC 60664)2Maximum altitude5,000 mIndoor use only.6When operating the NI cDAQ-9184 in temperatures below 0 °C, you must use the PS-15 powersupply or another power supply rated for below 0 °C.8| | NI cDAQ-9184 SpecificationsHazardous LocationsU.S. (UL)Class I, Division 2, Groups A, B, C, D, T4;Class I, Zone 2, AEx nA IIC T4Canada (C-UL)Class I, Division 2, Groups A, B, C, D, T4;Class I, Zone 2, Ex nA IIC T4Europe (ATEX) and International (IECEx)Ex nA IIC T4 GcShock and VibrationTo meet these specifications, you must direct mount the NI cDAQ-9184 system and affix ferrules to the ends of the terminal lines.Operational shock30 g peak, half-sine, 11 ms pulse (Tested inaccordance with IEC 60068-2-27. Test profiledeveloped in accordance withMIL-PRF-28800F.)Random vibrationOperating 5 Hz to 500 Hz, 0.3 g rmsNon-operating 5 Hz to 500 Hz, 2.4 g rms (Tested in accordancewith IEC 60068-2-64. Non-operating testprofile exceeds the requirements ofMIL PRF-28800F, Class 3.)Safety and Hazardous Locations StandardsThis product is designed to meet the requirements of the following electrical equipment safety standards for measurement, control, and laboratory use:•IEC 61010-1, EN 61010-1•UL 61010-1, CSA C22.2 No. 61010-1•EN 60079-0:2012, EN 60079-15:2010•IEC 60079-0: Ed 6, IEC 60079-15; Ed 4•UL 60079-0; Ed 6, UL 60079-15; Ed 4•CSA 60079-0:2011, CSA 60079-15:2012Note For UL and other safety certifications, refer to the product label or the OnlineProduct Certification section.NI cDAQ-9184 Specifications| © National Instruments| 9Electromagnetic CompatibilityThis product meets the requirements of the following EMC standards for electrical equipment for measurement, control, and laboratory use:•EN 61326-1 (IEC 61326-1): Class A emissions; Basic immunity•EN 55011 (CISPR 11): Group 1, Class A emissions•EN 55022 (CISPR 22): Class A emissions•EN 55024 (CISPR 24): Immunity•AS/NZS CISPR 11: Group 1, Class A emissions•AS/NZS CISPR 22: Class A emissions•FCC 47 CFR Part 15B: Class A emissions•ICES-001: Class A emissionsNote In the United States (per FCC 47 CFR), Class A equipment is intended foruse in commercial, light-industrial, and heavy-industrial locations. In Europe,Canada, Australia and New Zealand (per CISPR 11) Class A equipment is intendedfor use only in heavy-industrial locations.Note Group 1 equipment (per CISPR 11) is any industrial, scientific, or medicalequipment that does not intentionally generate radio frequency energy for thetreatment of material or inspection/analysis purposes.Note For EMC declarations and certifications, and additional information, refer tothe Online Product Certification section.CE ComplianceThis product meets the essential requirements of applicable European Directives, as follows:•2014/35/EU; Low-V oltage Directive (safety)•2014/30/EU; Electromagnetic Compatibility Directive (EMC)•2014/34/EU; Potentially Explosive Atmospheres (ATEX)Online Product CertificationRefer to the product Declaration of Conformity (DoC) for additional regulatory compliance information. To obtain product certifications and the DoC for this product, visit / certification, search by model number or product line, and click the appropriate link in the Certification column.10| | NI cDAQ-9184 SpecificationsEnvironmental ManagementNI is committed to designing and manufacturing products in an environmentally responsible manner. NI recognizes that eliminating certain hazardous substances from our products is beneficial to the environment and to NI customers.For additional environmental information, refer to the Minimize Our Environmental Impact web page at /environment. This page contains the environmental regulations and directives with which NI complies, as well as other environmental information not included in this document.Waste Electrical and Electronic Equipment (WEEE) EU Customers At the end of the product life cycle, all NI products must bedisposed of according to local laws and regulations. For more information abouthow to recycle NI products in your region, visit /environment/weee.电子信息产品污染控制管理办法(中国RoHS)中国客户National Instruments符合中国电子信息产品中限制使用某些有害物质指令(RoHS)。

xilinx fifo generator 用法

xilinx fifo generator 用法(原创版)目录1.Xilinx FIFO Generator 简介2.Xilinx FIFO Generator 的使用方法3.Xilinx FIFO Generator 的优点正文【1.Xilinx FIFO Generator 简介】Xilinx FIFO Generator 是 Xilinx 公司提供的一种用于生成 FIFO (First In First Out,先进先出)的工具,可以帮助用户快速方便地创建和管理 FIFO。

在 FPGA 设计和开发过程中,FIFO 常用于数据缓存、数据传输等场景,可以有效提高系统的运行效率。

【2.Xilinx FIFO Generator 的使用方法】使用 Xilinx FIFO Generator 的方法如下:1) 打开 Xilinx Vivado 工具,并在工具栏中选择“FIFO Generator”。

2) 在弹出的 FIFO Generator 对话框中,设置 FIFO 的相关参数,包括深度、宽度、读写时钟等。

用户可以根据实际需求进行设置。

3) 点击“OK”按钮,Xilinx FIFO Generator 会自动生成对应的 FIFO 模块,并将其添加到设计中。

4) 在 Vivado 工具中,用户可以对生成的 FIFO 模块进行进一步的编辑和优化,以满足具体的设计需求。

【3.Xilinx FIFO Generator 的优点】1) 简化开发流程:使用 Xilinx FIFO Generator 可以快速生成 FIFO 模块,降低了开发难度,节省了开发时间。

2) 高效的资源利用:Xilinx FIFO Generator 会根据用户设置的参数,自动优化 FIFO 模块的资源分配,从而实现更高的资源利用率。

3) 易于维护:生成的 FIFO 模块可以在 Vivado 工具中进行直观的编辑和调试,方便用户进行后期维护和优化。

学习笔记1——如何使用IP code

学习笔记1——如何使用IP code1、使用IP code1、1打开IP创建界面(已经先将需要的代码加入到里面,这里是加入IP核文件)Project——IP Catalog-------memories & storage Elements----------FIFOs----------FIFO Generator1、2 给IP命名、设置其余按缺省模块,不改变,弹出对话框会看到对这个IP进行综合综合完成后,IP source里面看到生成的一些东西比如一些实例化模板、综合后的约束文件、仿真需要的代码、dcp文件和给第三方综合工具用到的文件(char_fifo_stub.v)1、3、然后我们要把这个IP在我们的设计中实例化比如在wave_gen.v内实例化实例化时,我们可以利用它实例化模板,比如下面左边的模板里面的代码(右边圈),只需要把这部分代码拷贝到wave_gen.v中,然后把相应的引脚改成我们自己的引脚。

比如如下代码,就是我们需要的,放入wave_gen.v中的代码2、可以让IP核生成.dcp文件2、1假设我们先让它reset2、2我们重新生成这里选上生成综合检查文件仿真完成后,可以看到没有采用ooc的方式2、3此时运行综合2、4此时我们可以看到IP会和我们的设计整体进行综合2、5综合完毕,我们可以通过以下方式来观察我们的IP是否应该升级到新的版本3、我们也可以通过manager IP的设计方式把我们设计中所用的IP建立独立的IP工程进行管理。

3、1打开vivado,点击manager IP,点击New IP location我们选自己需要的芯片选好芯片,选择编程语言和IP所在地方3、2此时会打开一个IP Catalog,假设我们此时需要用到一个FIFO Generator会打开如下界面,我们的设置和1中的设置一样(下面省略,往前看这部分设置),这个时候要生成dcp3.3这里仿真完,我们看下具体工程的一些属性,输入以下命令report_property [current_project]这里我们如果想更改使用的编程语言用set_propertyTARGET_LANGUAGE[current_project]因为有修改,所有需要重新生成一遍(用managing output products)3、4、此时我们需要用到这个IP文件,我们进行如下操作:加入.dcp文件并把.dcp拷贝到当前文件下注意,这里也需要实例化,把模板里面的代码拷入顶层文件(注意引脚)重点:4、如何把自己的代码封装成一个IP,并加入到IP Catalog里面4、1假设我们这里有一个vivado工程,是实现负数乘法的工程(箭头部分是工程案例)其他弹出窗口暂时不管(比如summary窗口),直接按ok。

simulink的fwft fifo ram模块的使用方法

simulink的fwft fifo ram模块的使用方法FWFT(First Word Fall Through)FIFO RAM(Random Access Memory)模块是Simulink中的一个存储模块,用于存储并管理数据。

以下是使用FWFT FIFO RAM模块的步骤:1. 打开Simulink并创建一个模型。

2. 在模型中添加FWFT FIFO RAM模块。

可以在Simulink库中找到该模块,也可以通过搜索框搜索。

3. 右击FWFT FIFO RAM模块,选择"FIFO configuration"来配置FIFO RAM的属性。

4. 在弹出的对话框中,设置FIFO RAM的大小、数据类型以及其它参数。

确定后关闭对话框。

5. 连接FWFT FIFO RAM模块的输入和输出。

输入端口用于写入数据,输出端口用于读取数据。

6. 在模型中的其它部分生成数据,将数据输入到FWFT FIFO RAM的输入端口。

可以使用Constant模块生成固定数据、使用Signal Generator模块生成信号等。

7. 使用From block模块将FWFT FIFO RAM模块的输出连接到其它模块,以读取存储在FIFO RAM中的数据。

可以使用Scope模块查看输出数据,或者将其连接到其它计算模块进行进一步处理。

8. 设置仿真参数并运行模型。

模拟仿真时,输入数据将会写入FIFO RAM模块,输出端口将读取FIFO RAM中的数据。

注意:FWFT FIFO RAM模块是一种虚拟存储器,用于存储中间结果或需要在特定时间点使用的数据。

数据在存储器中的存储方式一般是先进先出(FIFO)结构,即最先写入的数据最先读取。

fifo generator count

fifo generator countFIFO Generator CountFIFO(First In First Out)是一种常见的数据结构,它按照先进先出的原则对数据进行存储和访问。

在计算机科学中,FIFO生成器计数是指在FIFO中的元素数量。

本文将探讨FIFO生成器计数的概念、应用以及相关的算法。

一、FIFO生成器计数的概念FIFO生成器计数是指在FIFO中的元素数量。

在FIFO中,新的元素被添加到队列的末尾,而从队列中移除元素时,总是从队列的开头开始。

FIFO生成器计数可以用来衡量FIFO队列中的元素数量,从而帮助我们了解队列中的数据流动情况。

二、FIFO生成器计数的应用FIFO生成器计数在计算机科学中有着广泛的应用。

一种常见的应用是在操作系统中的进程调度中使用FIFO队列来管理进程的执行顺序。

在这种情况下,FIFO生成器计数可以用来统计当前正在等待执行的进程数量,从而帮助操作系统选择下一个要执行的进程。

FIFO生成器计数还可以用于网络数据包的传输和处理。

在网络中,数据包通常按照FIFO的原则进行传输,因此通过监控FIFO生成器计数可以了解当前网络中的数据流量情况,从而进行网络拥塞控制和优化。

FIFO生成器计数还在存储系统中起着重要的作用。

在存储系统中,数据通常按照FIFO的方式进行读写,通过监控FIFO生成器计数可以实时了解存储系统的负载情况,从而进行性能调优和资源分配。

三、FIFO生成器计数的算法FIFO生成器计数的算法有多种实现方式,下面介绍两种常见的算法。

1. 链表实现链表是一种常用的数据结构,可以用来实现FIFO生成器计数。

通过在链表的末尾添加新元素,并在链表的头部移除元素,我们可以方便地维护FIFO队列。

FIFO生成器计数可以通过链表的长度来获取。

2. 数组实现数组也可以用来实现FIFO生成器计数。

我们可以使用两个指针,一个指向FIFO队列的开头,另一个指向队列的末尾。

Gowin先进先出队列(FIFO HS) 用户指南说明书

Gowin先进先出队列(FIFO HS)用户指南IPUG760-1.2,2021-07-01版权所有© 2021广东高云半导体科技股份有限公司、、Gowin、GowinSynthesis以及高云均为广东高云半导体科技股份有限公司注册商标, 本手册中提到的其他任何商标,其所有权利属其拥有者所有。

未经本公司书面许可,任何单位和个人都不得擅自摘抄、复制、翻译本文档内容的部分或全部,并不得以任何形式传播。

免责声明本文档并未授予任何知识产权的许可,并未以明示或暗示,或以禁止发言或其它方式授予任何知识产权许可。

除高云半导体在其产品的销售条款和条件中声明的责任之外,高云半导体概不承担任何法律或非法律责任。

高云半导体对高云半导体产品的销售和/或使用不作任何明示或暗示的担保,包括对产品的特定用途适用性、适销性或对任何专利权、版权或其它知识产权的侵权责任等,均不作担保。

高云半导体对文档中包含的文字、图片及其它内容的准确性和完整性不承担任何法律或非法律责任,高云半导体保留修改文档中任何内容的权利,恕不另行通知。

高云半导体不承诺对这些文档进行适时的更新。

版本信息目录目录 (i)图目录 (iii)表目录 (v)1关于本手册 (1)1.1 手册内容 (1)1.2 相关文档 (1)1.3 术语、缩略语 (1)1.4 技术支持与反馈 (2)2FIFO概述 (3)2.1 FIFO简介 (3)2.2 FIFO HS/FIFO SC HS IP简介 (4)2.3 FIFO HS/FIFO SC HS IP功能及特征 (5)2.3.1 FIFO HS IP功能及特征 (5)2.3.2 FIFO SC HS IP功能及特征 (6)2.4 FIFO HS IP最大频率和资源利用率 (6)2.5 FIFO SC HS IP最大频率和资源利用率 (8)3端口描述 (10)3.1 FIFO HS IP端口 (10)3.2 FIFO SC HS IP端口 (11)4时序说明 (12)4.1 FIFO HS IP信号时序 (12)4.2 FIFO SC HS IP信号时序 (19)5FIFO HS/FIFO SC HS IP配置 (26)5.1 FIFO HS IP配置 (26)5.2 FIFO SC HS IP配置 (30)6参考设计 (34)图目录图2-1 FIFO HS IP结构示意图 (4)图2-2 FIFO SC HS IP结构示意图 (4)图4-1 FIFO HS配置 (12)图4-2 FIFO HS IP配置时序 (13)图4-3 FIFO HS配置 (13)图4-4 FIFO HS IP配置时序 (14)图4-5 FIFO HS配置 (14)图4-6 FIFO HS IP配置时序 (15)图4-7 FIFO HS配置 (15)图4-8 FIFO HS IP配置时序 (16)图4-9 FIFO HS配置 (17)图4-10 FIFO HS IP配置时序 (17)图4-11 FIFO HS配置 (18)图4-12 FIFO HS IP配置时序 (18)图4-13 FIFO SC HS配置 (19)图4-14 FIFO SC HS IP配置时序 (19)图4-15 FIFO SC HS配置 (20)图4-16 FIFO SC HS IP配置时序 (20)图4-17 FIFO SC HS配置 (21)图4-18 FIFO SC HS IP配置时序 (21)图4-19 FIFO SC HS配置 (22)图4-20 FIFO SC HS IP配置时序 (23)图4-21 FIFO SC HS配置 (23)图4-22 FIFO SC HS IP配置时序 (24)图4-23 FIFO SC HS配置 (24)图4-24 FIFO SC HS IP配置时序 (25)图5-1 FIFO HS IP配置界面 (26)图5-2 FIFO_SC HS IP 配置界面 (30)表目录表目录表1-1术语、缩略语 (1)表2-1 FIFO HS/ FIFO SC HS IP概览 (5)表2-2未配置可选特性的FIFO HS IP (7)表2-3已配置可选特性的FIFO HS IP (8)表2-4未配置可选特性的FIFO SC HS IP (9)表2-5已配置可选特性的FIFO SC HS IP (9)表3-1 FIFO HS IP的IO端口列表 (10)表3-2 FIFO SC HS IP的IO端口列表 (11)表5-1 FIFO HS IP配置界面参数 (27)表5-2 FIFO SC HS IP配置界面参数 (31)1关于本手册 1.1 手册内容1关于本手册1.1手册内容本手册主要描述FIFO HS的功能特性、端口、时序、相关配置及参考设计,旨在帮助用户快速了解Gowin FIFO HS IP的产品特点及使用方法。

异步FIFO的设计与实现

摘要随着数字系统规模的不断增大,单时钟域设计会极大地限制数字系统性能,现代数字系统为了提升性能,常采用多时钟域的设计。

跨时钟域的信号在传输时会遇到亚稳态现象,如何保持系统稳定地传输数据是多时钟域系统设计者重点关注的问题,在跨时钟域传递数据的系统中,常采用异步FIFO(First In First Out,先进先出队列)口来缓冲传输的数据,以克服亚稳态产生的错误,保证数据的正确传输。

常规的异步FIFO 设计采用先同步读写指针后比较产生空/满标志和用先比较读写指针产生空/满标志,再同步到相应时钟域的方法,但由于常规异步FIFO 模块中的RAM 存储器读写寻址指针常采用格雷码计数器以与“空满”控制逻辑的存在,工作频率低,面积大,将使通过这两个模块的信号通路延时对整个模块的工作频率造成制约。

本文提出了一种新型异步FIFO 的设计方法,该方法省略“了满”信号产生模块和多余的存储器位深来简化常规的FIFO 模块,而只保留“空”信号产生模块,避免使用大量的同步寄存器,减少了面积空间。

FPGA 验证的结果表明,改进后的异步 FIFO 性能有了显著的提高。

关键词:现场可编程门阵列(FPGA )亚稳态空/满标志产高速FIFOABSTRACTWith the increasing of digital system size, a single clock domain designwill greatly limit the digital system performance. To enhance the performance of modern digital systems, multiple clock domain design is conventionally adopted. While being transmitted, Cross-clock domain signals will come across the phenomenon of metastability, hence it will be a major concern for the multi -clock domain system designers to probe how to maintain the system stability and to have data transmission conducted smoothly. As to the bus system data transmission in the system where the two data interface clocks don’t match, one of super and effective solutions is to use asynchronous FIFO buffer memory. How To solve the key and difficult issue that metastability and how to generate empty and full flag correctly in asynchronous FIFO design. Traditional FIFO design often synchronizes write/read address first, then compares them to generate empty/full signals or empty / full flag first compare the read and write pointer, and then synchronized to the clock domain, This design takes on too much area and can only work at a low frequency,this will allow the signaling pathways of these two modules delay caused by constraints of the operating frequency of the entire module. A new method of asynchronous FIFO is proposed to overcome these problems,omit the "full" signal generator module and redundant memory bit depth to simplify the conventional FIFO module, leaving only the "empty" signal generation module,avoid the use of a large number of synchronization registers, reducing the area of space. FPGA verification results show that the asynchronous FIFO improved performance has been significantly improved.Keywords: Field Programmable Gate Array (FPGA); Metastable; Mmpty / Full Flag production; High-speed FIFO目录摘要 (I)ABSTRACT (I)第一章绪论 (1)1.1研究背景和意义 (1)1.2研究现状 (1)1.3本文的主要工作 (3)1.4论文结构 (3)第二章跨时钟域设计的挑战与实现方法 (3)2.1跨时钟域设计的挑战 (4)2.1.1亚稳态问题 (4)2.1.2亚稳态产生的原因 (5)2.1.3亚稳态的危害 (5)2.2 跨时钟域的实现方法 (6)2.2.1同步器 (6)2.2.2握手机制 (9)第三章开发环境 (11)3.1硬件平台 (11)3.2软件平台 (11)第四章异步FIFO的设计与实现 (13)4.1异步FIFO (13)4.1.1异步FIFO工作原理 (13)4.1.2异步FIFO设计的难点 (14)4.2常见异步 FIFO 的设计 (16)4.2.1 读写地址产生逻辑 (18)4.2.2空/满标志的产生与代码的实现 (19)4.3.3改进的异步 FIFO 设计方法分析 (22)4.4高速异步FIFO的设计与实现 (23)4.4.1常见FIFO模块分析 (23)4.4.2高速异步FIFO 设计 (25)第五章结论 (28)第六章参考文献 (29)致谢 (30)附录高速异步FIFO设计仿真分析 (31)附1. 设计工作流程 (31)附.1.1 设计输入 (31)附.1.2 设计编译 (35)附.1.3 设计仿真 (36)第一章绪论1.1研究背景和意义作为21 世纪最重要的科学领域之一,超级计算机是体现科技竞争力和综合国力的重要标志。

Modelsim独立仿真Vivado的IP核

Modelsim独立仿真vivado带IP核的工程Tools: Vivado 2015.4 && Modelsim 10.2 ——By 我有风衣在使用vivado进行工程代码仿真时,有2种方法可实现功能仿真。

第一种是在vivado 下直接调用Modelsim进行功能仿真,另外一种是单独使用Modelsim进行功能仿真。

一般对于在vivado下使用了IP核的工程,此时直接调用Modelsim进行仿真会方便很多,这时首先按照下图所示的方法,先编译好vivado的仿真库,再进行相关设置,即可用vivado 直接调用Modelsim进行功能仿真。

但是打开vivado本身电脑就会比较卡顿,当工程较大时,再调用Modelsim仿真有时候会非常慢,因此本文会结合一个简例(fifo_test.xpr),介绍直接利用Modelsim仿真vivado 带IP核的工程。

首先说明如何在vivado下直接调用Modelsim进行功能仿真(1)首先用vivado的Tools下的Compile Simulation Libraries编译vivado仿真库一般在Modelsim的安装目录下新建一个文件夹,比如D:\modeltech64_10.2\vivado_libs_201504。

接着在Compile Simulation Libraries下进行相关设置后点击Compile。

接着等待编译结束。

一般i7的电脑几分钟就编译好了(本人的电脑是i7 4790 + 16G 内存,嘻嘻),编译完成后会在D:\modeltech64_10.2\vivado_libs_201504下生成大约2.5G左右的仿真库文件。

接着在vivado下进行仿真设置。

图中划线的地方注意根据你自己的设置来确定。

主要是仿真激励文件的指定(tb_fifo_test)、编译库文件的位置指定(D:\modeltech64_10.2\vivado_libs_201504)。

xilinx 跨时钟域设计 概述及解释说明

xilinx 跨时钟域设计概述及解释说明1. 引言:1.1 概述跨时钟域设计是现代电路设计中一个重要且复杂的问题。

在集成电路中,不同的模块可能会使用不同频率的时钟信号进行操作,这就导致了时钟信号之间存在着不同的域。

在进行数据传输或者协同工作时,跨越不同时钟域之间的数据传输问题变得非常重要。

1.2 文章结构本文将首先介绍跨时钟域设计的概念和相关背景知识。

接下来,我们将详细讨论为什么需要对时钟域进行划分以及Xilinx跨时钟域设计的意义。

然后,我们将介绍跨时钟域设计的原理与方法,包括同步与异步信号传输方式、锁存器与触发器的使用注意事项以及时序约束设置与优化策略。

此外,我们还会提供一些实际案例来演示Xilinx跨时钟域设计的实践应用和效果展示。

最后,我们将总结文章,并提出对于跨时钟域设计在Xilinx器件中应用前景的展望。

1.3 目的本文的目标是为读者提供关于Xilinx跨时钟域设计相关知识和技术方案,并通过实例和案例展示,帮助读者更好地理解并应用这些技术。

同时,我们也希望引起读者对跨时钟域设计的重视,并认识到其在现代电路设计中的重要性和必要性。

通过本文的阅读,读者将能够掌握Xilinx跨时钟域设计的基本原理与方法,并应用于实际工程项目中,提高电路的可靠性和性能。

2. 跨时钟域设计概述:2.1 什么是时钟域:时钟域是指由一个主时钟信号驱动的一组逻辑电路。

在数字电路设计中,系统通常包含多个时钟域,每个时钟域都有独立的主时钟信号。

由于不同时钟域之间存在着频率和相位差异,因此跨越不同时钟域的信号传输需要特殊的设计策略和技术支持。

2.2 时钟域划分的必要性:在复杂的数字系统中,为了提高系统性能和可靠性,常常需要将整个系统划分为多个独立的时钟域。

这种划分可以使各模块按照不同的时间精度进行操作,并且能够减少信号互联、功耗消耗以及故障引入等问题。

同时,通过合理地划分和管理时钟域,能够降低系统开发复杂度,并确保数据在稳定状态下进行正确传输。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

The FIFO Generator supports the Virtex-4 built-in FIFO modules, enabling large FIFOs to be created by cascading the built-in FIFOs in both width and depth. The core expands the capabilities of the built-in FIFOs by utilizing the FPGA fabric to create optional status flags not implemented in the built-in FIFO macro.

• Independent or common clock domains

• Selectable memory type (block RAM, distributed RAM, shift register, or Virtex-4 built-in FIFO)

• First-word fall-through (FWFT)

Figure Top x-ref 1