A MONOLITHIC 19-BIT 800 HZ LOW POWER MULTI-BIT SIGMA DELTA CMOS ADC USING DATA WEIGHTED AVE

AT89S52单片机应用中英文翻译

本科毕业设计(论文)AT89S52单片机应用中英文翻译专业名称:电气工程及其自动化年级班级:学生姓名:指导老师:二O一二年六月九日AT89S52 MCU ApplicationsFunction Characteristic DescriptionThe AT89S52 is a low-power, high-performance CMOS 8-bit microcontroller with 8K bytes of in-system programmable Flash memory. The device is manufactured using Atmel’s high-density nonvolatile memory technology and is compatible with the indus-try-standard 80C51 instruction set and pinout. The on-chip Flash allows the program memory to be reprogrammed in-system or by a conventional nonvolatile memory pro-grammer. By combining a versatile 8-bit CPU with in-system programmable Flash on a monolithic chip, the Atmel AT89S52 is a powerful microcontroller which provides a highly-flexible and cost-effective solution to many embedded control applications.The AT89S52 provides the following standard features: 8K bytes of Flash, 256 bytes of RAM, 32 I/O lines, Watchdog timer, two data pointers, three 16-bit timer/counters, a six-vector two-level interrupt architecture, a full duplex serial port, on-chip oscillator, and clock circuitry. In addition, the AT89S52 is designed with static logic for operation down to zero frequency and supports two software selectable power saving modes. The Idle Mode stops the CPU while allowing the RAM, timer/counters, serial port, and interrupt system to continue functioning. The Power-down mode saves the RAM con-tents but freezes the oscillator, disabling all other chip functions until the next interrupt or hardware reset.Pin DescriptionVCC :Supply voltage.GND :Ground.Port 0:Port 0 is an 8-bit open drain bidirectional I/O port. As an output port, each pin can sink eight TTL inputs. When 1s are written to port 0 pins, the pins can be used as high-impedance inputs. Port 0 can also be configured to be the multiplexed low-order address/data bus during accesses to external program and data memory. In this mode, P0 has internal pull-ups. Port 0 also receives the code bytes during Flash programming and outputs the code bytes dur-ing program verification. External pull-ups are required during program verification.Port 1:Port 1 is an 8-bit bidirectional I/O port with internal pull-ups. The Port 1 outputbuffers can sink/source four TTL inputs. When 1s are written to Port 1 pins, they are pulled high by the inter-nal pull-ups and can be used as inputs. As inputs, Port 1 pins that are externally being pulled low will source current (IIL) because of the internal pull-ups. In addition, P1.0 and P1.1 can be configured to be the timer/counter 2 external count input (P1.0/T2) and the timer/counter 2 trigger input (P1.1/T2EX), respectively, as shown in the follow-ing table 1. Port 1 also receives the low-order address bytes during Flash programming and verification.Port 2:Port 2 is an 8-bit bidirectional I/O port with internal pull-ups. The Port 2 output buffers can sink/source four TTL inputs. When 1s are written to Port 2 pins, they are pulled high by the inter-nal pull-ups and can be used as inputs. As inputs, Port 2 pins that are externally being pulled low will source current (IIL) because of the internal pull-ups. Port 2 emits the high-order address byte during fetches from external program memory and dur-ing accesses to external data memory that use 16-bit addresses (MOVX @ DPTR). In this application, Port 2 uses strong internal pull-ups when emitting 1s. During accesses to external data memory that use 8-bit addresses (MOVX @ RI), Port 2 emits the contents of the P2 Special Function Register. Port 2 also receives the high-order address bits and some control signals during Flash program-ming and verification.Port 3:Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. The Port 3 output buffers can sink/source four TTL inputs. When 1s are written to Port 3 pins, they are pulled high by the inter-nal pull-ups and can be used as inputs. As inputs, Port 3 pins that areexternally being pulled low will source current (IIL) because of the pull-ups. Port 3 receives some control signals for Flash programming and verification. Port 3 also serves the functions of various special features of the AT89S52, as shown in the fol-lowing table 2.RST:Reset input. A high on this pin for two machine cycles while the oscillator is running resets the device. This pin drives high for 98 oscillator periods after the Watchdog times out. The DISRTO bit in SFR AUXR (address 8EH) can be used to disable this feature. In the default state of bit DISRTO, the RESET HIGH out feature is enabled.ALE/PROG:Address Latch Enable (ALE) is an output pulse for latching the low byte of the address during accesses to external memory. This pin is also the program pulse input (PROG) during Flash programming. In normal operation, ALE is emitted at a constant rate of 1/6 the oscillator frequency and may be used for external timing or clocking purposes. Note, however, that one ALE pulse is skipped dur-ing each access to external data memory. If desired, ALE operation can be disabled by setting bit 0 of SFR location 8EH. With the bit set, ALE is active only during a MOVX or MOVC instruction. Otherwise, the pin is weakly pulled high. Setting the ALE-disable bit has no effect if the microcontroller is in external execution mode.PSEN:Program Store Enable (PSEN) is the read strobe to external program memory. When the AT89S52 is executing code from external program memory, PSEN is activated twice each machine cycle, except that two PSEN activations are skipped during eachaccess to exter-nal data memory.EA/VPP:External Access Enable. EA must be strapped to GND in order to enable the device to fetch code from external program memory locations starting at 0000H up to FFFFH. Note, however, that if lock bit 1 is programmed, EA will be internally latched on reset. EA should be strapped to VCC for internal program executions. This pin also receives the 12-volt programming enable voltage (VPP) during Flash programming.XTAL1:Input to the inverting oscillator amplifier and input to the internal clock operating circuit.XTAL2:Output from the inverting oscillator amplifier.Program MemoryIf the EA pin is connected to GND, all program fetches are directed to external memory. On the AT89S52, if EA is connected to VCC, program fetches to addresses 0000H through 1FFFH are directed to internal memory and fetches to addresses 2000H through FFFFH are to external memory.Data MemoryThe AT89S52 implements 256 bytes of on-chip RAM. The upper 128 bytes occupy a parallel address space to the Special Function Registers. This means that the upper 128 bytes have the same addresses as the SFR space but are physically separate from SFR space. When an instruction accesses an internal location above address 7FH, the address mode used in the instruction specifies whether the CPU accesses the upper 128 bytes of RAM or the SFR space. Instructions which use direct addressing access the SFR space. For example, the following direct addressing instruction accesses the SFR at location 0A0H (which is P2). MOV 0A0H, #data. Instructions that use indirect addressing access the upper 128 bytes of RAM. For example, the following indirect addressing instruction, where R0 contains 0A0H, accesses the data byte at address 0A0H, rather than P2 (whose address is 0A0H).MOV @R0, #data. Note that stack operations are examples of indirect addressing, so the upper 128 bytes of data RAM are available as stack space.Watchdog TimerThe WDT is intended as a recovery method in situations where the CPU may be subjected to software upsets. The WDT consists of a 14-bit counter and the Watchdog Timer Reset (WDTRST) SFR. The WDT is defaulted to disable from exiting reset. To enable the WDT, a user must write 01EH and 0E1H in sequence to the WDTRST register (SFR location 0A6H). When the WDT is enabled, it will increment every machine cycle while the oscillator is running. The WDT timeout period is dependent on the external clock frequency. There is no way to disable the WDT except through reset (either hardware reset or WDT overflow reset). When WDT over-flows, it will drive an output RESET HIGH pulse at the RST pin.In Power-down mode the oscillator stops, which means the WDT also stops. While in Power-down mode, the user does not need to service the WDT. There are two methods of exiting Power-down mode: by a hardware reset or via a level-activated external interrupt which is enabled prior to entering Power-down mode. When Power-down is exited with hardware reset, servicing the WDT should occur as it normally does whenever the AT89S52 is reset. Exiting Power-down with an interrupt is significantly different. The interrupt is held low long enough for the oscillator to stabilize. When the interrupt is brought high, the interrupt is serviced. To prevent the WDT from resetting the device while the interrupt pin is held low, the WDT is not started until the interrupt is pulled high. It is suggested that the WDT be reset during the interrupt service for the interrupt used to exit Power-down mode. To ensure that the WDT does not overflow within a few states of exiting Power-down, it is best to reset the WDT just before entering Power-down mode. Before going into the IDLE mode, the WDIDLE bit in SFR AUXR is used to determine whether the WDT continues to count if enabled. The WDT keeps counting during IDLE (WDIDLE bit = 0) as the default state. To prevent the WDT from resetting the AT89S52 while in IDLE mode, the user should always set up a timer that will periodically exit IDLE, service the WDT, and reenter IDLE mode. With WDIDLE bit enabled, the WDT will stop to count in IDLE mode and resumes the count upon exit from IDLE.Timer 0 and 1Timer 0 and Timer 1 in the AT89S52 operate the same way as Timer 0 and Timer 1 in the AT89C51 and AT89C52. For further information o n the timers’ operation, please click on the document link below:/dyn/resources/prod_documents/DOC4316.PDFTimer 2Timer 2 is a 16-bit Timer/Counter that can operate as either a timer or an event counter. The type of operation is selected by bit C/T2in the SFR T2CON. Timer 2 has three operating modes: capture, auto-reload (up or down counting), and baud rate generator. The modes are selected by bits in T2CON, as shown in Table 6-1. Timer 2 consists of two 8-bit registers, TH2 and TL2. In the Timer function, the TL2 register is incremented every machine cycle. Since a machine cycle consists of 12 oscillator periods, the count rate is 1/12 of the oscil-lator frequency.In the Counter function, the register is incremented in response to a 1-to-0 transition at its corre-sponding external input pin, T2. In this function, the external input is sampled during S5P2 of every machine cycle. When the samples show a high in one cycle and a low in the next cycle, the count is incremented. The new count value appears in the register during S3P1 of the cycle following the one in which the transition was detected. Since two machine cycles (24 oscillator periods) are required to recognize a 1-to-0 transition, the maximum count rate is 1/24 of the oscillator frequency. To ensure that a given level is sampled at least once before it changes, the level should be held for at least one full machine cycle.InterruptsThe AT89S52 has a total of six interrupt vectors: two external interrupts (INT0and INT1), three timer interrupts (Timers 0, 1, and 2), and the serial port interrupt. Each of these interrupt sources can be individually enabled or disabled by setting or clearing a bit in Special Function Register IE. IE also contains a global disable bit, EA, which disables all interrupts at once. Note that bit position IE.6 is unimplemented. User software should not write a 1 to this bit position, since it may be used in future AT89 products. Timer 2 interrupt is generated by the logical OR of bits TF2 and EXF2 in register T2CON. Nei-ther of these flags is cleared by hardware when the service routine is vectored to. In fact, the service routine may have to determine whether it was TF2 or EXF2 that generated the interrupt, and that bit will have to be cleared in software. The Timer 0 and Timer 1 flags, TF0 and TF1, are set at S5P2 of the cycle in which the timers overflow. The values are then polled by the circuitry in the next cycle. However, the Timer 2 flag, TF2, is set at S2P2 and is polled in the same cycle in which the timer overflows.Oscillator CharacteristicsXTAL1 and XTAL2 are the input and output, respectively, of an inverting amplifier that can be configured for use as an on-chip oscillator. Either a quartz crystal or ceramic resonator may be used. To drive the device from an external clock source, XTAL2 should be left unconnected while XTAL1 is driven,. There are no requirements on the duty cycle of the external clock signal, since the input to the internal clock-ing circuitry is through a divide-by-two flip-flop, but minimum and maximum voltage high and low time specifications must be observed.Power-down ModeIn the Power-down mode, the oscillator is stopped, and the instruction that invokes Power-down is the last instruction executed. The on-chip RAM and Special Function Registers retain their values until the Power-down mode is terminated. Exit from Power-down mode can be initiated either by a hardware reset or by an enabled external interrupt. Reset redefines the SFRs but does not change the on-chip RAM. The reset should not be activated before VCC is restored to its normal operating level and must be heldactive long enough to allow the oscillator to restart and stabilize.Idle ModIn idle mode, the CPU puts itself to sleep while all the on-chip peripherals remain active. The mode is invoked by software. The content of the on-chip RAM and all the special functions regis-ters remain unchanged during this mode. The idle mode can be terminated by any enabled interrupt or by a hardware reset. Note that when idle mode is terminated by a hardware reset, the device normally resumes pro-gram execution from where it left off, up to two machine cycles before the internal reset algorithm takes control. On-chip hardware inhibits access to internal RAM in this event, but access to the port pins is not inhibited. To eliminate the possibility of an unexpected write to a port pin when idle mode is terminated by a reset, the instruction following the one that invokes idle mode should not write to a port pin or to external memory.AT89S52单片机应用功能特征描述AT89S52是一种低功耗、高性能CMOS8位微控制器,具有8K 在系统可编程Flash 存储器。

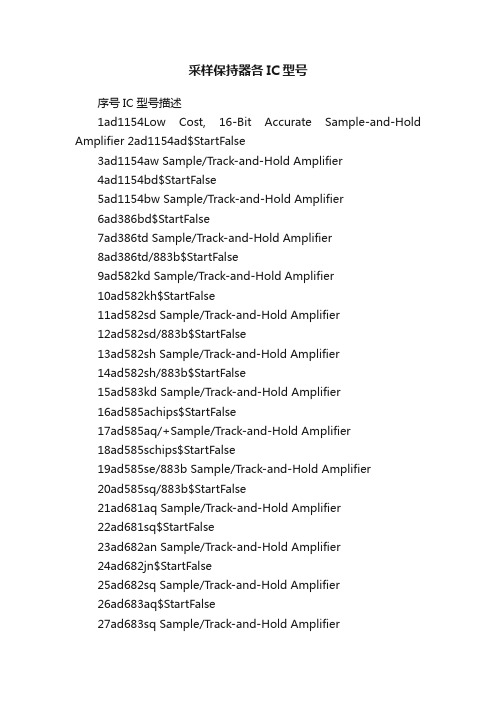

采样保持器各IC型号

采样保持器各IC型号序号IC型号描述1ad1154Low Cost, 16-Bit Accurate Sample-and-Hold Amplifier 2ad1154ad$StartFalse3ad1154aw Sample/Track-and-Hold Amplifier4ad1154bd$StartFalse5ad1154bw Sample/Track-and-Hold Amplifier6ad386bd$StartFalse7ad386td Sample/Track-and-Hold Amplifier8ad386td/883b$StartFalse9ad582kd Sample/Track-and-Hold Amplifier10ad582kh$StartFalse11ad582sd Sample/Track-and-Hold Amplifier12ad582sd/883b$StartFalse13ad582sh Sample/Track-and-Hold Amplifier14ad582sh/883b$StartFalse15ad583kd Sample/Track-and-Hold Amplifier16ad585achips$StartFalse17ad585aq/+Sample/Track-and-Hold Amplifier18ad585schips$StartFalse19ad585se/883b Sample/Track-and-Hold Amplifier20ad585sq/883b$StartFalse21ad681aq Sample/Track-and-Hold Amplifier22ad681sq$StartFalse23ad682an Sample/Track-and-Hold Amplifier24ad682jn$StartFalse25ad682sq Sample/Track-and-Hold Amplifier26ad683aq$StartFalse27ad683sq Sample/Track-and-Hold Amplifier28ad684sq/883b$StartFalse29ad783an Sample/Track-and-Hold Amplifier30ad783jn$StartFalse31ad783sq Sample/Track-and-Hold Amplifier32ad783sq/883b$StartFalse33ad9100Ultrahigh Speed Monolithic Track-and-Hold 34ad9100*$StartFalse35ad9100ad Ultrahigh Speed Monolithic Track-and-Hold 36ad9100jd$StartFalse37ad9100sd Ultrahigh Speed Monolithic Track-and-Hold 38ad9100se/883b$StartFalse39ad9101125 MSPS Monolithic Sampling Amplifier40ad9101ae$StartFalse41ad9101ar125 MSPS Monolithic Sampling Amplifier 42ad9101se$StartFalse43adh-050Sample/Track-and-Hold Amplifier44adh-050-883b$StartFalse45adh-051Sample/Track-and-Hold Amplifier46adh-051-883b$StartFalse47ah20016Sample/Track-and-Hold Amplifier48ah201-1$StartFalse49ah201-2Sample/Track-and-Hold Amplifier50al1210ar$StartFalse51al1210-die Sample/Track-and-Hold Amplifier52al1210es$StartFalse53al1210jr Sample/Track-and-Hold Amplifier54al1210se$StartFalse55al1210sj Sample/Track-and-Hold Amplifier56cds-1401mc$StartFalse57cds-1401mm Sample/Track-and-Hold Amplifier59cs3101-kd Sample/Track-and-Hold Amplifier60cs3101-td$StartFalse61cs3112-bd1Sample/Track-and-Hold Amplifier62cs3112-kd1$StartFalse63cs3112-kd2Sample/Track-and-Hold Amplifier64cs3112-td1$StartFalse65cs31412-bc1Sample/Track-and-Hold Amplifier66cs31412-bd$StartFalse67cs31412-kc1Sample/Track-and-Hold Amplifier68cs31412-kc2$StartFalse69cs31412-kd Sample/Track-and-Hold Amplifier70cs31412-tc1$StartFalse71cs31412-td Sample/Track-and-Hold Amplifier72dgl-13-1$StartFalse73dgl-13-1-883b Sample/Track-and-Hold Amplifier74dgl-13-3$StartFalse75dgl-13-3-883b Sample/Track-and-Hold Amplifier76ha1-2420-2$StartFalse77ha1-2425-5 3.2レs Sample and Hold Amplifiers78ha1-5320-2$StartFalse79ha1-5320-5 1 Microsecond Precision Sample and Hold Amplifier 80ha1-5330-2$StartFalse81ha1-5330-5650ns Precision Sample and Hold Amplifier82ha-2420$StartFalse83ha-2425 3.2レs Sample and Hold Amplifiers84ha3-2425-5$StartFalse85ha3-5320-5 1 Microsecond Precision Sample and Hold Amplifier 86ha3-5330-5$StartFalse87ha4p2425-5 3.2レs Sample and Hold Amplifiers89ha-5330650ns Precision Sample and Hold Amplifier90ha9p2425-5$StartFalse91ha9p5320-5 1 Microsecond Precision Sample and Hold Amplifier 92ha9p5320-9$StartFalse93hs346b Sample/Track-and-Hold Amplifier94hs346c$StartFalse95hs9704b Sample/Track-and-Hold Amplifier96hs9704c$StartFalse97hs9705b Sample/Track-and-Hold Amplifier98hs9705c$StartFalse99hs9714k Sample/Track-and-Hold Amplifier100hs9714tb$StartFalse101hs9716k Sample/Track-and-Hold Amplifier102hs9716tb$StartFalse103hs9720k Sample/Track-and-Hold Amplifier104hs9720tb$StartFalse105htc-0300a Ultrahigh-Speed Hybrid Track-and-Hold Amplifiers106htc-0300am$StartFalse107htc-0300am/883b Ultrahigh-Speed Hybrid Track-and-Hold Amplifiers108htc-0300atd/883b$StartFalse109htc-0500am Sample/Track-and-Hold Amplifier110htc-0500sm$StartFalse111hts-0010Ultra High Speed Hybird Track-and Hold Amplifiers112hts-0010kd$StartFalse113hts-0010sd Ultra High Speed Hybird Track-and Hold Amplifiers115hts-0025m Ultra High Speed Hybird Track-and Hold Amplifiers116hv257$StartFalse117hv257fg32 CHANNEL HIGH VOLTAGE SAMPLE AND HOLD AMPLIFIER ARRAY 118hv257x$StartFalse119lf198MONOLITHIC SAMPLE AND HOLD CIRCUITS120lf198/bgc$StartFalse121lf198a Precision Sample and Hold Amplifier122lf198ah Monolithic Sample-and-Hold Circuits123lf198al Sample/Track-and-Hold Amplifier124lf198fe$StartFalse125lf198h Monolithic Sample-and-Hold Circuits126lf198h/883Monolithic Sample-and-Hold Circuits127lf198l$StartFalse128lf298MONOLITHIC SAMPLE AND HOLD CIRCUITS129lf298fe Sample-and-hold amplifiers130lf298h$StartFalse131lf298hb Sample/Track-and-Hold Amplifier132lf298m$StartFalse133lf298n Sample-and-hold amplifiers134lf398$StartFalse135lf398a$StartFalse136lf398ah$StartFalse137lf398ah/a+$StartFalse138lf398al Sample/Track-and-Hold Amplifier139lf398an$StartFalse140lf398an/a+Sample/Track-and-Hold Amplifier141lf398an/b+$StartFalse142lf398an8Precision Sample and Hold Amplifier143lf398d$StartFalse144lf398d-t Sample/Track-and-Hold Amplifier145lf398fe$StartFalse146lf398h Monolithic Sample-and-Hold Circuits 147lf398h/a+Sample/Track-and-Hold Amplifier148lf398hb$StartFalse149lf398jg Sample/Track-and-Hold Amplifier150lf398l$StartFalse151lf398m Monolithic Sample-and-Hold Circuits 152lf398mx$StartFalse153lf398n MONOLITHIC SAMPLE AND HOLD CIRCUITS 154lf398n/a+Sample/Track-and-Hold Amplifier155lf398n/b+$StartFalse156lf398n8Precision Sample and Hold Amplifier 157lf398nb$StartFalse158lf398p Sample/Track-and-Hold Amplifier159lf398s8$StartFalse160lf39j8Precision Sample and Hold Amplifier 161lf6197$StartFalse162lf6197ccj$StartFalse163lf6197j$StartFalse164lh0053g-mil Sample/Track-and-Hold Amplifier165max5165$StartFalse166max5165lccm 32-Channel Sample/Hold Amplifier with a Single Multiplexed Input167max5165lecm$StartFalse168max5165mccm 32-Channel Sample/Hold Amplifier with a Single Multiplexed Input169max5165mecm$StartFalse170max5165nccm 32-Channel Sample/Hold Amplifier with aSingle Multiplexed Input171max5165necm$StartFalse172max516632-Channel Sample/Hold Amplifier with Four Multiplexed Inputs173max5166lccm$StartFalse174max5166lecm 32-Channel Sample/Hold Amplifier with Four Multiplexed Inputs175max5166mccm$StartFalse176max5166mecm 32-Channel Sample/Hold Amplifier with Four Multiplexed Inputs177max5166nccm$StartFalse178max5166necm 32-Channel Sample/Hold Amplifier with Four Multiplexed Inputs179max5167lccm$StartFalse180max5167lecm SAMPLE/TRACK-AND-HOLD AMPLIFIER|32-CHANNEL|BICMOS|QFP|48PIN|PLASTIC 181max5167mccm$StartFalse182max5167mecm SAMPLE/TRACK-AND-HOLD AMPLIFIER|32-CHANNEL|BICMOS|QFP|48PIN|PLASTIC 183max5167nccm$StartFalse184max5167necm SAMPLE/TRACK-AND-HOLD AMPLIFIER|32-CHANNEL|BICMOS|QFP|48PIN|PLASTIC 185max5168$StartFalse186max5168lccm SAMPLE/TRACK-AND-HOLD AMPLIFIER|32-CHANNEL|BICMOS|QFP|48PIN|PLASTIC 187max5168lecm$StartFalse188max5168mccm SAMPLE/TRACK-AND-HOLD AMPLIFIER|32-CHANNEL|BICMOS|QFP|48PIN|PLASTIC 189max5168mecm$StartFalse190max5168nccm SAMPLE/TRACK-AND-HOLDAMPLIFIER|32-CHANNEL|BICMOS|QFP|48PIN|PLASTIC 191max5168necm$StartFalse192ne5537Sample-and-hold amplifier193ne5537d$StartFalse194ne5537n Sample-and-hold amplifier195se5537$StartFalse196se5537fe Sample-and-hold amplifier197vn1025cc$StartFalse198vn1025ci Sample/Track-and-Hold Amplifier 199vn1025cm$StartFalse200vn1025dc Sample/Track-and-Hold Amplifier 201vn1025di$StartFalse202vn1025dm Sample/Track-and-Hold Amplifier 203vn1025mc$StartFalse204vn1025mi Sample/Track-and-Hold Amplifier 205vn1025mm$StartFalse206vn1025sc Sample/Track-and-Hold Amplifier 207vn1225cc$StartFalse208vn1225ci Sample/Track-and-Hold Amplifier 209vn1225cm$StartFalse210vn1225dc Sample/Track-and-Hold Amplifier 211vn1225di$StartFalse212vn1225dm Sample/Track-and-Hold Amplifier 213vn1225sc$StartFalse厂家Analog DevicesAnalog Devices Analog Devices Analog Devices Analog Devices Analog DevicesIntersil CorporationIntersil CorporationIntersil Corporation Intersil CorporationIntersil Corporation Intersil CorporationIntersil Corporation Intersil CorporationAnalog Devices Analog DevicesAnalog Devices Analog Devices Analog Devices Supertex, Inc ETCLinear Technology National Semiconductor National Semiconductor National SemiconductorETCPhilips Semiconductors Philips SemiconductorsLinear Technology National SemiconductorNational Semiconductor ETCLinear Technology Linear Technology Maxim IntegratedProductsMaxim Integrated ProductsMaxim Integrated ProductsMaxim Integrated ProductsMaxim Integrated ProductsMaxim Integrated ProductsMaxim Integrated ProductsMaxim Integrated ProductsMaxim Integrated ProductsMaxim Integrated ProductsMaxim Integrated ProductsMaxim Integrated ProductsMaxim Integrated ProductsPhilips SemiconductorsPhilips SemiconductorsPhilips Semiconductors。

Digital electronic weigher(数字电子秤的中英文资料)

Digital electronic weigherAbstractwith the rapid development of Microelectronics technology in the new century,the using traditional tools in the market have been completely unable to meet the needs of people。

People have been expecting cheap portable electronic scales which can measure accurately、smaller and easily reading for many years.Electronic scales have come into being。

the electronic scale posses the function which traditional scale can not replace , such as weighing convenience, high accuracy, automatic control, simple operation, widely used in people's lives, industrial production, scientific research。

voltage outputted by the he resistance strain sensor bridge make use of ADC0832 Built-in amplifier,8-bit speed A / D converter, Convert Corresponding Digital signal。

The digital signal will be dealt by the program in the MCU, then displayed the weight of the object on the LM4229LCD. User can input the price of the object through keyboard, then the value of the object will be calculated and displayed。

单片机篮球计分器毕业论文中英文资料外文翻译文献

单片机篮球计分器外文翻译一英文原文:DescriptionThe AT89C51 is a low-power, high-performance CMOS 8-bit microcomputer with 4K bytes of Flash Programmable and Erasable Read Only Memory (PEROM) and 128 bytes RAM. The device is manufactured using Atmel’s high density nonvolatile memory technology and is compatible with the industry standardMCS-51™ instruction set and pinout. The chip combines a versatile 8-bit CPU with Flash on a monolithic chip, the Atmel AT89C51 is a powerful microcomputer which provides a highly flexible and cost effective solution to many embedded control applications.Features:• Compatible with MCS-51™ Products• 4K Bytes of In-System Reprogrammable Flash Memory• Endurance: 1,000 Write/Erase Cycles• Fully Static Operation: 0 Hz to 24 MHz• Th ree-Level Program Memory Lock• 128 x 8-Bit Internal RAM• 32 Programmable I/O Lines• Two 16-Bit Timer/Counters• Six Interrupt Sources• Programmable Serial Channel• Low Power Idle and Power Down ModesThe AT89C51 provides the following standard features: 4K bytes of Flash, 128 bytes of RAM, 32 I/O lines, two 16-bit timer/counters, a five vector two-level interrupt architecture, a full duplex serial port, on-chip oscillator and clock circuitry. In addition, the AT89C51 is designed with static logic for operation down to zero frequency and supports two software selectable power saving modes. The Idle Mode stops the CPU while allowing the RAM, timer/counters, serial port and interrupt system to continue functioning. The Power Down Mode saves the RAM contents but freezes the oscillator disabling all other chip functions until the next hardware reset. Pin Description:VCC Supply voltage.GND Ground.Port 0Port 0 is an 8-bit open drain bidirectional I/O port. As an output port each pin can sink eight TTL inputs. When is are written to port 0 pins, the pins can be used as high impedance inputs.Port 0 may also be configured to be the multiplexed loworder address/data bus during accesses to external program and data memory. In this mode P0 has internal pullups.Port 0 also receives the code bytes during Flash programming, and outputs the code bytes during program verification. External pullups are required during program verification.Port 1Port 1 is an 8-bit bidirectional I/O port with internal pullups. The Port 1 output buffers can sink/source four TTL inputs. When 1s are written to Port 1 pins they are pulled high by the internal pullups and can be used as inputs. As inputs, Port 1 pins that are externally being pulled low will source current (IIL) because of the internal pullups.Port 1 also receives the low-order address bytes during Flash programming and verification.Port 2Port 2 is an 8-bit bidirectional I/O port with internal pullups. The Port 2 output buffers can sink/source four TTL inputs. When 1s are written to Port 2 pins they are pulled high by the internal pullups and can be used as inputs. As inputs, Port 2 pins that are externally being pulled low will source current (IIL) because of the internal pullups.Port 2 emits the high-order address byte during fetches from external program memory and during accesses to external data memory that use 16-bit addresses (MOVX @ DPTR). In this application it uses strong internal pull-ups when emitting 1s. During accesses to external data memory that use 8-bit addresses (MOVX @ RI), Port 2 emits the contents of the P2 Special Function Register.Port 2 also receives the high-order address bits and some control signals during Flash programming and verification.Port 3Port 3 is an 8-bit bidirectional I/O port with internal pullups. The Port 3 output buffers can sink/source four TTL inputs. When 1s are written to Port 3 pins they are pulled high by the internal pullups and can be used as inputs. As inputs, Port 3 pins that are externally being pulled low will source current (IIL) because of the pullups.Port 3 also serves the functions of various special features of the AT89C51 as listed below:receives somecontrol signals forFlash programmingand verification.RSTReset input. Ahigh on this pin fortwo machine cycles while the oscillator is running resets the device.ALE/PROGAddress Latch Enable output pulse for latching the low byte of the address during accesses to external memory. This pin is also the program pulse input (PROG) during Flash programming.In normal operation ALE is emitted at a constant rate of 1/6 the oscillator frequency, and may be used for external timing or clocking purposes. Note, however, that one ALE pulse is skipped during each access to external Data Memory.If desired, ALE operation can be disabled by setting bit 0 of SFR location 8EH. With the bit set, ALE is active only during a MOVX or MOVC instruction. Otherwise, the pin is weakly pulled high. Setting the ALE-disable bit has no effect if the microcontroller is in external execution mode.PSENProgram Store Enable is the read strobe to external program memory.When the AT89C51 is executing code from external program memory, PSEN is activated twice each machine cycle, except that two PSEN activations are skipped during each access to external data memory.EA/VPPExternal Access Enable. EA must be strapped to GND in order to enable the device to fetch code from external program memory locations starting at 0000H up to FFFFH. Note, however, that if lock bit 1 is programmed, EA will be internally latched on reset.EA should be strapped to VCC for internal program executions.This pin also receives the 12-volt programming enable voltage(VPP) during Flash programming, for parts that require 12-volt VPP.XTAL1Input to the inverting oscillator amplifier and input to the internal clock operating circuit.XTAL2Output from the inverting oscillator amplifier.Oscillator CharacteristicsXTAL1 and XTAL2 are the input and output, respectively, of an invertingamplifier which can be configured for use as an on-chip oscillator, as shown in Figure1. Either a quartz crystal or ceramic resonator may be used. To drive the device from an external clock source, XTAL2 should be left unconnected while XTAL1 is driven as shown in Figure2. There are no requirements on the duty cycle of the external clock signal, since the input to the internal clocking circuitry is through adivide-by-two flip-flop, but minimum and maximum voltage high and low time specifications must be observed.Idle ModeIn idle mode, the CPU puts itself to sleep while all the onchip peripherals remain active. The mode is invoked by software. The content of the on-chip RAM and all the special functions registers remain unchanged during this mode. The idle mode can be terminated by any enabled interrupt or by a hardware reset.It should be noted that when idle is terminated by a hard ware reset, the device normally resumes program execution, from where it left off, up to two machine cycles before the internal reset algorithm takes control. On-chip hardware inhibits access to internal RAM in this event, but access to the port pins is not inhibited. To eliminate the possibility of an unexpected write to a port pin when Idle is terminated by reset, the instruction following the one that invokes Idle should not be one that writes to aport pin or to external memory.二中文翻译:AT89C51是美国ATMEL公司生产的低电压,高性能CMOS8位单片机,片内含4Kbytes的快速可擦写的只读程序存储器(PEROM)和128 bytes 的随机存取数据存储器(RAM),器件采用ATMEL公司的高密度、非易失性存储技术生产,兼容标准MCS-51产品指令系统,片内置通用8位中央处理器(CPU)和flish 存储单元,功能强大AT89C51单片机可为您提供许多高性价比的应用场合,可灵活应用于各种控制领域。

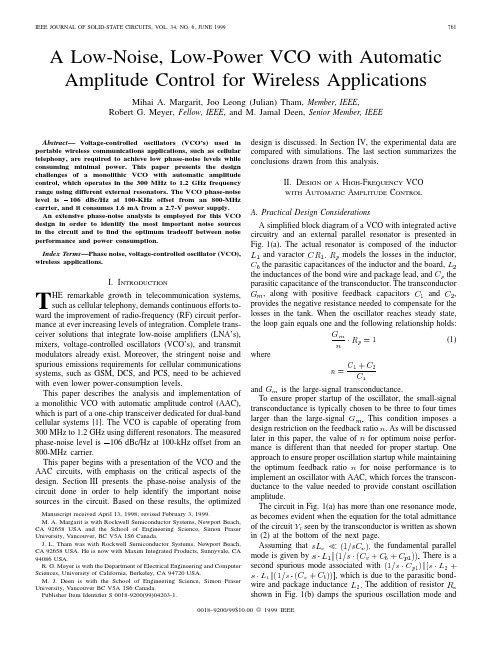

A low-noise, low-power VCO

A Low-Noise,Low-Power VCO with AutomaticAmplitude Control for Wireless ApplicationsMihai A.Margarit,Joo Leong(Julian)Tham,Member,IEEE,Robert G.Meyer,Fellow,IEEE,and M.Jamal Deen,Senior Member,IEEE Abstract—Voltage-controlled oscillators(VCO’s)used inportable wireless communications applications,such as cellulartelephony,are required to achieve low phase-noise levels whileconsuming minimal power.This paper presents the designchallenges of a monolithic VCO with automatic amplitudecontrol,which operates in the300MHz to1.2GHz frequencyrange using different external resonators.The VCO phase-noiselevel is0106dBc/Hz at100-KHz offset from an800-MHzcarrier,and it consumes1.6mA from a2.7-V power supply.An extensive phase-noise analysis is employed for this VCOdesign in order to identify the most important noise sourcesin the circuit and tofind the optimum tradeoff between noiseperformance and power consumption.Index Terms—Phase noise,voltage-controlled oscillator(VCO),wireless applications.I.I NTRODUCTIONT HE remarkable growth in telecommunication systems,such as cellular telephony,demands continuous efforts to-ward the improvement of radio-frequency(RF)circuit perfor-mance at ever increasing levels of plete trans-ceiver solutions that integrate low-noise amplifiers(LNA’s),mixers,voltage-controlled oscillators(VCO’s),and transmitmodulators already exist.Moreover,the stringent noise andspurious emissions requirements for cellular communicationssystems,such as GSM,DCS,and PCS,need to be achievedwith even lower power-consumption levels.This paper describes the analysis and implementation ofa monolithic VCO with automatic amplitude control(AAC),which is part of a one-chip transceiver dedicated for dual-bandcellular systems[1].The VCO is capable of operating from300MHz to1.2GHz using different resonators.The measuredphase-noise level is(a)(b)Fig.1.(a)Simplified diagram of a voltage-controlled oscillator.(b)V oltage-controlled oscillator with damping resistor R s:has negligible effect on the fundamental mode[2].However,care needs to be taken in the design,since too large a valueoffor the differential amplifier in order to maintain constantMARGARIT et al.:LOW-NOISE,LOW-POWER VCO763Fig.2.Schematic of the VCO with AAC.gain.for minimum phase-noise levels largely independent of considerations for proper oscillation startup. In steady-state operation,the AAC loop forces the dc signal provided by the rectifier and the low-passfilter at the sensing input to track the reference level applied at the reference input.This leads to the second advantage of using the AAC circuit of enabling the VCO to provide constant output power independent of theresonator(3)Since the system is timevariant,and observation timein(3)with theequivalent noise source of each individual node,the phase-noise contribution of each node can be calculated[5].To explore the oscillator excess phase response,each nodeof the circuit needs to be excited at evenly distributed timesteps of the oscillation period.Due to thehighis an integer chosen such that the oscillation waveform hassettled before the next pulse is applied.The ramp generator isreset by thefirst positive-going zero crossing of the oscillation.The ramp is then compared in COMP2with a staircase voltage,which is incremented ateachis the number of pulses to be injected.In this way,pulses areinjected with a period equalto764IEEE JOURNAL OF SOLID-STATE CIRCUITS,VOL.34,NO.6,JUNE1999(a)(b)(c)Fig.3.(a)Sequence of pulses used to excite the oscillator.(b)Block diagram of the behavioral test generator.(c)VCO test points for phase sensitivity to injectedcharge.Fig.4.Impulse shape.is almost constant from DC to 25GHz,which is sufficient for this design that uses a bipolar processwithCurrentsourcethe effect of thenoise voltage generatedbytheeffect of the resistive losses in theresonator(5)(6)The collector shot noise oftransistormA).Thecyclostationarityofis8.6MARGARIT et al.:LOW-NOISE,LOW-POWER VCO765Fig.5.Tail-current noise spectrum.(a)(b)Fig.6.(a)VCO output waveform.(b)Simulated function h8;I(t; )(vertical axis in degrees/pC).across the nodes“out”and“outb”(Fig.2),and it has thevaluefor current pulsesinjected at the tail of the emitter-coupled pair.This functionhas a periodicity that is half the oscillation period.To obtainmore meaningful information on the phase sensitivity forperturbations in the tail current of the VCO,the functionis plotted together with the oscillation outputwaveform.It can be seen that for perturbations injectedaround the zero crossings and the peaks of the oscillation,the phase sensitivity is close to zero and reaches its maxima766IEEE JOURNAL OF SOLID-STATE CIRCUITS,VOL.34,NO.6,JUNE1999Fig.7.Frequency spectrum of h 8;I (t; )(vertical axis in dBV).forwhereis shown in Fig.7.As expected,there areharmonics at multiples of double the oscillation frequency.The harmonics mix with the noise around these frequencies and contribute to the total phase noise.For calculation of the phase-noise contribution from the tail current,the Fourier coefficientsof[4]th harmonic of the oscillation fre-quency.In this analysis,the summation is performed over the first five harmonics.Higher order harmonics have insignificant contribution to the phase noise.Of particular interest is the dc component,coefficientregion of the phase noiseintersectstheis definedas(9)In the aboveequation,andhas a period equalto the oscillation period.Again,in order to see the effect of this noise source,the oscillation output waveform and the collector currentofreaches its maximum when the collector currentis close to the peak,and it reaches the minimumwhenin Fig.9show that thecollector shot noise is mixed mostly with the first and second harmonics of the oscillation frequency to contribute to the total phase noise.However,the collector shot noiseofwas performed.Todo this,theratioMARGARIT et al.:LOW-NOISE,LOW-POWER VCO767(a)(b)(c)Fig.8.(a)VCO output waveform.(b)Collector current of Q1.(c)Simulated functions h8;IIt768IEEE JOURNAL OF SOLID-STATE CIRCUITS,VOL.34,NO.6,JUNE 1999Fig.9.Frequency spectrum of h 8e (t; )(vertical axis in dBV).Fig.10.Phase noise (continuous line)and figure of merit (dashed line)versus feedback ratio n:TABLE IN OISE C ONTRIBUTIONS AT100-kHz O FFSET FROM AN 800-MHz C ARRIERAlthough the noise contribution from the tail current is not important at this offset frequency,it becomes the major noise source at offset frequencies less than 3kHz.The factor of two for some of the noise sources in Table I accounts for noise sources that are considered twice due to the circuit symmetry [5].The sum of these values gives a noise-to-signal ratio ofregion of the spectrum.SpectreRFpredicts a phase-noise level ofMARGARIT et al.:LOW-NOISE,LOW-POWER VCO769parison of the phase noise calculated with phase noise simulated in SpectreRF.Fig.12.Microphotograph of the VCO with AAC.However,the current version of SpectreRF did not predictthe43dBc and the third harmonic is106dBc/Hz at100-770IEEE JOURNAL OF SOLID-STATE CIRCUITS,VOL.34,NO.6,JUNE1999Fig.13.VCO outputspectrum.Fig.14.Measured phase noise.kHz offset for a carrier frequency of 800MHz,which is in agreement with the analysis presented in this paper (Fig.14).The VCO core consumes 1.6mA from a 2.7-V power supply.The remaining circuits used for the AAC (rectifier,voltage reference,and amplifier)consume 0.25mA.If better phase-noise performance is desired,only the current consumption inthe VCO core needs to be increased,while the consumption of the AAC circuits remains unchanged.V.C ONCLUSIONSIn this paper,the possibilities of developing a low-noise,low-power VCO with capabilities for wireless applicationsMARGARIT et al.:LOW-NOISE,LOW-POWER VCO 771have been explored.An automatic amplitude control circuit was implemented,which allows the choice of the optimum oscillator feedback ratio for noise performance without being constrained by startup considerations.At the same time,the automatic amplitude control allows proper VCO operation for a wide range of the resonator quality factor.A novel method was used to study the phase-noise performance of the VCO.The method predicts results that are close to the measurements and allows the designer to obtain detailed information about the processes that contribute to oscillator phase noise.A CKNOWLEDGMENTThe authors would like to thank Dr.C.Hull and R.Magoon for helpful discussions.R EFERENCES[1]J.L.Tham,M.Margarit,B.Pregardier, C.Hull,and F.Carr,“A2.7V 900MHz/1.9GHz dual-band transceiver IC for digital wireless communication,”in Proc.CICC ,1998,p.559.[2]J.L.Tham,“Integrated radio frequency LC voltage-controlled oscil-lators,”College of Engineering,University of California,Berkeley,Electronics Research Laboratory Memo.,1995.[3]P.Davis,P.Smith,E.Campbell,J.Lin,K.Gross,G.Bath,Y.Low,M.Lau,Y.Degani,J.Gregus,R.Frye,and K.Tai,“Si-on-Si integration of a GSM transceiver with VCO resonator,”in Proc.ISSCC 1998,vol.41,Feb.1998,p.248.[4] A.Hajimiri and T.H.Lee,“A general theory of phase noise in electricaloscillators,”IEEE J.Solid-State Circuits ,vol.33,pp.179–194,Feb.1998.[5] C.D.Hull and R.G.Meyer,“A systematic approach to the analysisof noise in mixers,”IEEE Trans.Circuits Syst.I ,vol.40,pp.909–919,Dec.1993.Mihai A.Margarit received the Dipl.Ing.degree in electrical engineering from the “Politehnica”Uni-versity Bucharest,Romania,in 1984.He currently is pursuing the Ph.D.degree in electrical engineering at Simon Fraser University,Burnaby,B.C.,Canada.Since 1984,he has worked in analog circuit design for the National Institute for Microelectron-ics,Bucharest,the Fraunhofer Institute,Erlangen,Germany,and Simon Fraser University,Vancouver,Canada.He is currently with Rockwell Semicon-ductor Systems,Newport Beach,CA,where he isa Senior Design Engineer working on high-frequency circuits for wireless communicationapplications.Joo Leong (Julian)Tham (S’88–M’96)received the B.S.degree in electrical engineering (with high-est honors)from the University of California,Santa Barbara,and the M.S.degree in electrical engineer-ing from the University of California,Berkeley.He has worked at Raytheon and Trimble Navi-gation.His previous work includes autocalibration systems and global positioning system receivers.From 1993to 1999,he was with Rockwell Semi-conductor Systems,Newport Beach,CA,where he was a Principal Design Engineer and Managerworking on radio-frequency integrated circuits for wireless communication applications.He currently is with Maxim Integrated Products,Sunnyvale,CA.His current interests are in the areas of high-frequency circuit design and integrated transceiver architectures.Mr.Tham is a member of Eta Kappa Nu,Tau Beta Pi,and the Golden Key Honor Society.He was named Rockwell Semiconductor Systems Engineer of the Year in1995.Robert G.Meyer (S’64–M’68–SM’74–F’81)was born in Melbourne,Australia,on July 21,1942.He received the B.E.,M.Eng.Sci.,and Ph.D.degrees in electrical engineering from the University of Melbourne in 1963,1965,and 1968,respectively.In 1968,he was an Assistant Lecturer in electrical engineering at the University of Melbourne.Since September 1968,he has been with the Department of Electrical Engineering and Computer Sciences,University of California,Berkeley,where he is now a Professor.His current research interests are high-frequency analog integrated-circuit design and device fabrication.He has been a Consultant on electronic circuit design for numerous companies in the electronics industry.He is a coauthor of Analysis and Design of Analog Integrated Circuits (New York:Wiley,1993)and Editor of Integrated Circuit Operational Amplifiers (New York:IEEE Press,1978).Dr.Meyer was President of the IEEE Solid-State Circuits Council and was an Associate Editor of the IEEE J OURNAL OF S OLID -S TATE C IRCUITS and of the IEEE T RANSACTIONS ON C IRCUITS AND S YSTEMS.M.Jamal Deen (S’81–M’86–SM’92)was born in Georgetown,Guyana.He received the B.Sc.degree in physics and mathematics from the University of Guyana in 1978and the M.S.and Ph.D.degrees in electrical engineering and applied physics from Case Western Reserve University,Cleveland,OH,in 1982and 1985,respectively.From 1978to 1980,he was an Instructor of physics at the University of Guyana.From 1980to 1983,he was a Research Assistant at Case Western Reserve University.He was a Research Engineer(1983–1985)and an Assistant Professor (1985–1986)at Lehigh University,Bethlehem,PA.In 1986,he joined the School of Engineering Science,Simon Fraser University,Vancouver,BC,Canada,as an Assistant Professor and since 1993has been a full Professor.He was a Visiting Scientist at the Herzberg Institute of Astrophysics,National Research Council,Ottawa,Ont.,Canada,in summer 1986,and he spent his sabbatical leave as a Visiting Scientist at Northern Telecom,Ottawa,in 1992–1993.He was also a Guest Professor in the Faculty of Electrical Engineering,Delft University of Technology,The Netherlands,in summer 1997and a CNRS scientist at the Physics of Semiconductor Devices Laboratory,Grenoble,France,in summer 1998.His current research interests include integrated devices and circuits;device physics,modeling,and characterization;and low-power,low-noise,high-frequency circuits.Dr.Deen is a member of Eta Kappa Nu,the American Physical Society,and the Electrochemical Society.He was a Fulbright-Laspau Scholar from 1980to 1982,an American Vacuum Society Scholar from 1983to 1984,and an NSERC Senior Industrial Fellow in 1993.。

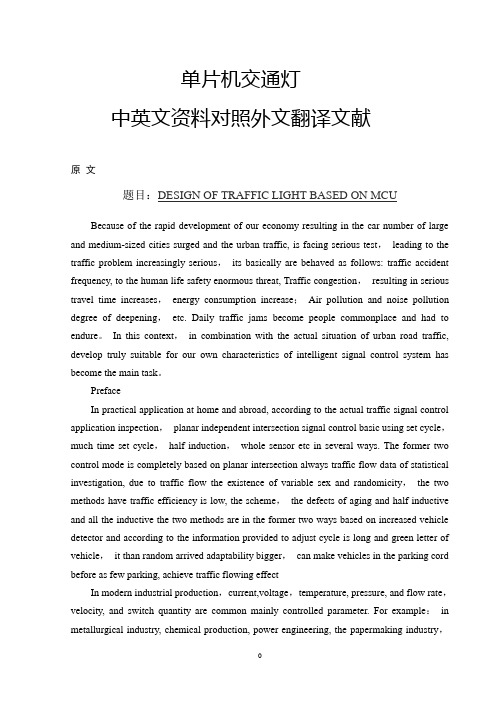

单片机交通灯中英文资料对照外文翻译文献

单片机交通灯中英文资料对照外文翻译文献原文题目:DESIGN OF TRAFFIC LIGHT BASED ON MCUBecause of the rapid development of our economy resulting in the car number of large and medium-sized cities surged and the urban traffic, is facing serious test,leading to the traffic problem increasingly serious,its basically are behaved as follows: traffic accident frequency, to the human life safety enormous threat, Traffic congestion,resulting in serious travel time increases,energy consumption increase;Air pollution and noise pollution degree of deepening,etc. Daily traffic jams become people commonplace and had to endure。

In this context,in combination with the actual situation of urban road traffic, develop truly suitable for our own characteristics of intelligent signal control system has become the main task。

PrefaceIn practical application at home and abroad, according to the actual traffic signal control application inspection,planar independent intersection signal control basic using set cycle,much time set cycle,half induction,whole sensor etc in several ways. The former two control mode is completely based on planar intersection always traffic flow data of statistical investigation, due to traffic flow the existence of variable sex and randomicity,the two methods have traffic efficiency is low, the scheme,the defects of aging and half inductive and all the inductive the two methods are in the former two ways based on increased vehicle detector and according to the information provided to adjust cycle is long and green letter of vehicle,it than random arrived adaptability bigger,can make vehicles in the parking cord before as few parking, achieve traffic flowing effectIn modern industrial production,current,voltage,temperature, pressure, and flow rate,velocity, and switch quantity are common mainly controlled parameter. For example:in metallurgical industry, chemical production, power engineering, the papermaking industry,machinery and food processing and so on many domains,people need to transport the orderly control. By single chip microcomputer to control of traffic,not only has the convenient control,configuration simple and flexible wait for an advantage, but also can greatly improve the technical index by control quantity,thus greatly improve product quality and quantity. Therefore,the monolithic integrated circuit to the traffic light control problem is an industrial production we often encounter problems.In the course of industrial production, there are many industries have lots of traffic equipment, in the current system, most of the traffic control signal is accomplished by relays, but relays response time is long,sensitivity low,long—term after use,fault opportunity increases greatly,and adopts single-chip microcomputer control,the accuracy of far greater than relays, short response time,software reliability, not because working time reduced its performance sake, compared with,this solution has the high feasibility。

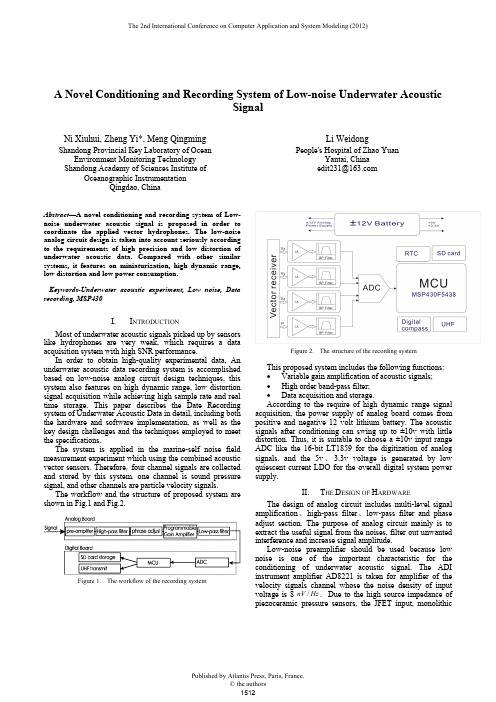

低噪声下海音频信号条件和记录系统说明书

A Novel Conditioning and Recording System of Low-noise Underwater AcousticSignalNi Xiuhui, Zheng Yi*, Meng Qingming Shandong Provincial Key Laboratory of Ocean Environment Monitoring Technology Shandong Academy of Sciences Institute of Oceanographic InstrumentationQingdao, ChinaLi Weidong People's Hospital of Zhao YuanYantai, ChinaAbstract—A novel conditioning and recording system of Low-noise underwater acoustic signal is proposed in order to coordinate the applied vector hydrophones. The low-noise analog circuit design is taken into account seriously according to the requirements of high precision and low distortion of underwater acoustic data. Compared with other similar systems, it features on miniaturization, high dynamic range, low distortion and low power consumption.Keywords-Underwater acoustic experiment, Low noise, Data recording, MSP430I.I NTRODUCTIONMost of underwater acoustic signals picked up by sensors like hydrophones are very weak, which requires a data acquisition system with high SNR performance.In order to obtain high-quality experimental data, An underwater acoustic data recording system is accomplished based on low-noise analog circuit design techniques, this system also features on high dynamic range, low distortion signal acquisition while achieving high sample rate and real time storage. This paper describes the Date Recording system of Underwater Acoustic Data in detail, including both the hardware and software implementation, as well as the key design challenges and the techniques employed to meet the specifications.The system is applied in the marine-self noise field measurement experiment which using the combined acoustic vector sensors. Therefore, four channel signals are collected and stored by this system. one channel is sound pressure signal, and other channels are particle velocity signals.The workflow and the structure of proposed system are shown in Fig.1 and Fig.2.Figure 1.The workflow of the recording systemFigure 2. The structure of the recording systemThis proposed system includes the following functions:•Variable gain amplification of acoustic signals;•High order band-pass filter;•Data acquisition and storage.According to the require of high dynamic range signal acquisition, the power supply of analog board comes from positive and negative 12 volt lithium battery. The acoustic signals after conditioning can swing up to ±10v with little distortion. Thus, it is suitable to choose a ±10v input range ADC like the 16-bit LT1859 for the digitization of analog signals. and the 5v、3.3v voltage is generated by low quiescent current LDO for the overall digital system power supply.II.T HE D ESIGN OF H ARDWAREThe design of analog circuit includes multi-level signal amplification、high-pass filter、low-pass filter and phase adjust section. The purpose of analog circuit mainly is to extract the useful signal from the noises, filter out unwanted interference and increase signal amplitude.Low-noise preamplifier should be used because low noise is one of the important characteristic for the conditioning of underwater acoustic signal. The ADI instrument amplifier AD8221 is taken for amplifier of the velocity signals channel whose the noise density of input voltage is 8 /nV Hz. Due to the high source impedance of piezoceramic pressure sensors, the JFET input, monolithicinstrumentation amplifier AD8220 is selected instead. Using JFET transistors, the AD8220 offers extremely high input impedance, extremely low bias currents, therefore, minimize the current noise which is the main problem of high source impedance sensors.The useful signal needs to be extracted form a variety of background noises by appropriate filters. Low-frequency signal is eliminated by the high-pass filter in order to avoid the output saturation cause by the low frequency marine hydrodynamic noise, and then the high frequency noise is almost completely removed by the 8th-order order low-pass Butterworth filter which has the least attenuation for all frequencies in the pass band. The Sallen–Key topology is used to implement both the 6-order high-pass and 8-order low-pass Butterworth filters that are particularly valued for its simplicity. Just one single amplifier, two resistors and two capacitors are needed by the 2-order filter of SK topology structure at the unit gain as are shown in Fig.3. The RC value can be calculated through the assisted tools of filter design, and pay attention to that the metal film resistors of smallerresistance value help to reduce system noise [1].Figure 3. A unity-gain low-pass filter implemented with a Sallen–Keytopology.Where the undamped natural frequency fo and Q factor (i.e., damping ratio ζ) are given by(1) And, (2)So,(3) The intensity of underwater acoustic signal is in the range of 104 orders of magnitude [2], The PGA section amplification circuit of this system carry out the adjustment of the overall gain from 20dB-80dB by different feedback resistors which are selected by analog switch DG211, so that the signal sampling of a large dynamic range is achieved. Besides, this system also includes amplifier circuits used in the impedance isolation and RC phase adjustment circuit. It is better that it is independent for four-channel analog board or a PCB board is made for the minimum interference among four channels, and the even channels of ADC are grounded to achieve the previous purpose. In the noise test of the electronic system, the analog signal input is grounded, the electronic system is configured to 4000 times amplification, and we found the output noise is about 10mv. Therefore, the valid noise of input terminal is 10mv/4000=2.5uv. The analog circuits are fully tested for low noise (less than 10uV noise).By the way, the high order filters also contribute to the low noise performance because it filtered out most of the high frequency noise. The low-pass and high-pass filters are cascade by SK topology using the low-noise amplifier OP2177. The magnitude-frequency characteristic is shown in Fig4. (The pass band is 10-500Hz in this case, and it canbe adjusted as needed to design)Figure 4. Amplitude frequency response of analog circuitsThe design of digital circuit includes MCU and interfacewith various peripherals.The Texas Instruments MSP430 family of ultra low power microcontrollers consists of several devices featuring lower power consumption, and 25MIPS CPU speed [3]. The5xx series MSP430 chip -Msp430F5438A have beenselected for governing digital system. This kind of devicesare complete system on-a-chip and in clued many integrated peripherals like Direct Memory Access (DMA) modules,UARTs, etc. All these characteristics make them a very attractive choice for this design.The media chosen to store the experimental data acquiredduring an inspection is a Secure Digital cards. Which is removable Flash-based storage devices that are gaining in popularity in small consumer devices such as digital cameras. Their small size, relative simplicity, low power consumption, and low cost make them an ideal solution for many applications. This interface combined with the MSP430, can form the foundation for a low-cost, long-life data logger. So, the SD card is a good choice for the underwater acoustic signal recording system when the data collection system takes a long time to collect and record huge amounts of data. It has two optional protocols: the SD mode and the SPI mode. All of data exchange can be completed by the four lines in the SPI mode, which greatly simplify the design of hardware circuit. The interface between SD and the MCU is use the SPI protocol which is shown in Fig.5.Figure 5. SD Card Schematic-SPI ModeThis system takes the 16bit softspan ADC chip LTC1859 in order to meet the 10V sampling of positive and negative analog signal. 16-bit resolution analog to digital conversion provides a responsive instrument capable of registering changes as small as one part in 65536 (0.000015% of the full scale measurement range). Besides, the voltage reference of chip internal is 10ppm, the SNR is 87dB, these features are all very important for a high-quality data acquisition system. It is connected to MCU through SPI interface, as is shown in Fig.6.Figure 6. ADC chip interface with the MCUThe electronic compass, with a pointing accuracy of 1º rms, uses the low-power three-dimensional digital compass of the PNI Company, and it is linked to MCU through RS232 interface.All the interfaces like SPI and 232 are industrial standard and therefore very convenient for firmware development and debug.III. T HE D ESIGN OF F IRMWAREThe mount of data to be collected can be estimated as shown in Equation 4. Fs is the sampling frequency, Word_Size is the number of bytes needed to store one single sensor read (2bytes for a16-bit resolution), N ch the number of sensor. T is the recording time in seconds. As at 10k sampling rate from four channels for an hour , the amount of data to be collected is:Data_Size = fs*Word_Size* N ch *T(4) =10240*2*4*3600=294912000bytes=280Mbytes The 32G SD card can fulfill 4 days deployment storage.The data from this recording system is writing directly in the sector rather than through the creation of file system storage, which results in higher writing speed.The writing sector of SD card consists of three procedures: sent the writing sector command to the SD card; transmit data to the SD card; the SD card internal programming. Here I must say The SD card programming internal needn’t the CPU intervention, however, the time-consuming of one sector can reach up to hundreds of mill-seconds [5]. So in order to achieve the high-speed writing of SD card, big RAM caches are essential. And The DMA capabilities available in the MSP430 MCU, that permit fast data transfers without CPU intervention, are of a great advantage in applications where high sampling rates are required. The strategy of high-speed recording proposed below also relies on the exploitation of the DMA capabilities The classic double-buffer strategy is adopted, Two array of memory buffers of 512*12 bytes each is used to temporarily store the acquired data while is being transferred to the SD card. Let us focus on the data acquisition strategy implemented in the MCU: 1. 0.1ms timer interrupts is established for the sampling rate of 10k. The four channels is sampled once the interrupts is carried out, all of eight bytes from 2 bytes per channel is continuously written in the established AdcBuffer; 2. After 768 interrupts, the AdcBuffer of 6K is full, and the DMA is opened so that the data in the AdcBuffer is transmitted to the MMCBuffer of the same capacity; 3. Meanwhile, the new sampled data is over write in AdcBuffer. 4. The 6K bytes data will be transmitted to the SD card once the DMA transmission is completed;The flow chart of this strategy is shown in Fig.7. With the 16K RAM and DMA modules of Msp430F5438A combined with 25Mips processing speed, the real-time data recording up to 20ksps four channels is achieved. The high-speed SD card is used in this Stand-alone data logger with configurable sample rate from as low as 0.001 Hz up to as high as 10,000 samples per second.Figure 7. The system sampling and real-time handlingIV.C ONCLUSIONSeveral tests have been performed in order to ensure the low-noise performance on the analog circuits and check the effectiveness of the strategies adopted to optimize the SD real-time writing performance of the recording system.The system provides a reliable data acquisition platform for the underwater acoustic experiment, satisfying the requirements derived from the targeted application, in terms of sampling rate, resolution, data storage capabilities and power consumption. Besides, the dynamic range of signal is greater than 70dB, and the equivalent input noise is less than 10μv, the pass-band ripple is less than 0.1dB, the phase difference among channels is small. Also, the operating current of the whole system is about 80mA, the entire system is lightweight and portable if the high-energy lithium-ion battery is adopted, and it is convenient to be placed in equipment and deploy. In a word, this system is very feasible in the marine environment noise field measurement experiment for the use on underwater acoustic signal logging.A CKNOWLEDGMENTThe first author wishes to thank Zheng yi and Yang guang for their valuable comments that improved the qualityof this paper. And this paper was supported by the National Natural Science Foundation of China under Grant 40806044, and supported by the QingDao Science and Technology Planning Project Fund of China under Grant 10-3-4-9-2-jch, and supported by Research Fund for the Doctoral Program of the Shandong Academy of Sciences under Grant Y09-2.R EFERENCES[1]Henry, Wang pei-qing, etc. The noise suppression and attenuationtechnology of electronic systems[M]. Electronic industry press, 2003(In Chinese).[2]Liu bo-sheng, Lei jia-yu etc. Underwater acoustic principle [M].Harbin engineering university press, 2010 (In Chinese).[3]Texas Instruments Incorporated. MSP430 Family User's Guideslau208g. /.[4]Linear Technology Corporation. LTC1859 Datasheet./.[5]SanDisk. Secure Digital Card Product Manual - Revision 1.7,September 2003.。

外文翻译:智能开关电源

Intelligent switch power supply英文:With the rapid development of electronic technology, application field of electronic system is more and more extensive, electronic equipment, there are more and more people work with electronic equipment, life is increasingly close relationship. Any electronic equipment are inseparable from reliable power supply for power requirements, they more and more is also high. Electronic equipment miniaturized and low cost in the power of light and thin, small and efficient for development direction. The traditional transistors series adjustment manostat is continuous control linear manostat. This traditional manostat technology more mature, and there has been a large number of integrated linear manostat module, has the stable performance is good, output ripple voltage small, reliable operation, etc. But usually need are bulky and heavy industrial frequency transformer and bulk and weight are big filter.In the 1950s, NASA to miniaturization, light weight as the goal, for a rocket carrying the switch power development. In almost half a century of development process, switch power because of its small volume, light weight, high efficiency, wide range, voltage advantages in electric, control, computer, and many other areas of electronic equipment has been widely used. In the 1980s, a computer is made up of all of switch power supply, the first complete computer power generation. Throughout the 1990s, switching power supply in electronics, electrical equipment, home appliances areas to be widely, switch power technology into the rapid development. In addition, large scale integrated circuit technology, and the rapid development of switch power supply with a qualitative leap, raised high frequency power products of, miniaturization, modular tide.Power switch tube, PWM controller and high-frequency transformer is an indispensable part of the switch power supply. The traditional switch power supply is normally made by using high frequency power switch tube division and the pins, such as using PWM integrated controller UC3842 + MOSFET is domestic small powerswitch power supply, the design method of a more popularity.Since the 1970s, emerged in many function complete integrated control circuit, switch power supply circuit increasingly simplified, working frequency enhances unceasingly, improving efficiency, and for power miniaturization provides the broad prospect. Three end off-line pulse width modulation monolithic integrated circuit TOP (Three switch Line) will Terminal Off with power switch MOSFET PWM controller one package together, has become the mainstream of switch power IC development. Adopt TOP switch IC design switch power, can make the circuit simplified, volume further narrowing, cost also is decreased obviouslyMonolithic switching power supply has the monolithic integrated, the minimalist peripheral circuit, best performance index, no work frequency transformer can constitute a significant advantage switching power supply, etc. American PI (with) company in Power in the mid 1990s first launched the new high frequency switching Power supply chip, known as the "top switch Power", with low cost, simple circuit, higher efficiency. The first generation of products launched in 1994 represented TOP100/200 series, the second generation product is the TOP Switch - debuted in 1997 Ⅱ. The above products once appeared showed strong vitality and he greatly simplifies thedesign of 150W following switching power supply and the development of new products for the new job, also, high efficiency and low cost switch power supply promotion and popularization created good condition, which can be widely used in instrumentation, notebook computers, mobile phones, TV, VCD and DVD, perturbation VCR, mobile phone battery chargers, power amplifier and other fields, and form various miniaturization, density, on price can compete with the linear manostat AC/DC power transformation module.Switching power supply to integrated direction of future development will be the main trend, power density will more and more big, to process requirements will increasingly high. In semiconductor devices and magnetic materials, no new breakthrough technology progress before major might find it hard to achieve, technology innovation will focus on how to improve the efficiency and focus onreducing weight. Therefore, craft level will be in the position of power supply manufacturing higher in. In addition, the application of digital control IC is the future direction of the development of a switch power. This trust in DSP for speed and anti-interference technology unceasing enhancement. As for advanced control method, now the individual feels haven't seen practicability of the method appears particularly strong,perhaps with the popularity of digital control, and there are some new control theory into switching power supply.(1)The technology: with high frequency switching frequencies increase, switch converter volume also decrease, power density has also been boosted, dynamic response improved. Small power DC - DC converter switch frequency will rise to MHz. But as the switch frequency unceasing enhancement, switch components and passive components loss increases, high-frequency parasitic parameters and high-frequency EMI and so on the new issues will also be caused.(2)Soft switching technologies: in order to improve the efficiency of non-linearity of various soft switch, commutation technical application and hygiene, representative of soft switch technology is passive and active soft switch technology, mainly including zero voltage switch/zero current switch (ZVS/ZCS) resonance, quasi resonant, zero voltage/zero current pulse width modulation technology (ZVS/ZCS - PWM) and zero voltage transition/zero current transition pulse width modulation (PWM) ZVT/ZCT - technical, etc. By means of soft switch technology can effectively reduce switch loss and switch stress, help converter transformation efficiency (3)Power factor correction technology (IC simplifies PFC). At present mainly divided into IC simplifies PFC technology passive and active IC simplifies PFC technology using IC simplifies PFC technology two kinds big, IC simplifies PFC technology can improve AC - DC change device input power factor, reduce the harmonic pollution of power grid.(4)Modular technology. Modular technology can meet the needs of the distributed power system, enhance the system reliability.(5)Low output voltage technology. With the continuous development of semiconductor manufacturing technology, microprocessor and portable electronic devices work more and more low, this requires future DC - DC converter can provide low output voltage to adapt microprocessor and power supply requirement of portable electronic devicesPeople in switching power supply technical fields are edge developing related power electronics device, the side of frequency conversion technology, development of switch between mutual promotion push switch power supply with more than two year growth toward light, digital small, thin, low noise and high reliability, anti-interference direction. Switching powersupply can be divided into the AC/DC and DC/DC two kinds big, also have AC/AC DC/AC as inverter DC/DC converter is now realize modular, and design technology and production process at home and abroad, are mature and standardization, and has approved by users, but the AC/DC modular, because of its own characteristics in the process of making modular, meet more complex technology and craft manufacture problems. The following two types of switch power supply respectively on the structure and properties of this.Switching power supply is the development direction of high frequency, high reliability, low consumption, low noise, anti-jamming and modular. Because light switch power, small, thin key techniques are changed, so high overseas each big switch power supply manufacturer are devoted to the development of new high intelligent synchronous rectifier, especially the improvement of secondary devices of the device, and power loss of Zn ferrite (Mn) material? By increasing scientific and technological innovation, to enhance in high frequency and larger magnetic flux density (Bs) can get high magnetic under the miniaturization of, and capacitor is a key technology. SMT technology application makes switching power supply has made considerable progress, both sides in the circuitboard to ensure that decorate components of switch power supply light, small, thin. The high frequency switching power supply of the traditional PWM must innovate switch technology, to realize the ZCS ZVS, soft switch technology hasbecome the mainstream of switch power supply technical, and greatly improve the efficiency of switch power. For high reliability index, America's switch power producers, reduce by lowering operating current measures such as junction temperature of the device, in order to reduce stress the reliability of products made greatly increased.Modularity is of the general development of switch power supply trend can be modular power component distributed power system, can be designed to N + 1 redundant system, and realize the capacity expansion parallel. According to switch power running large noise this one defect, if separate the pursuit of high frequency noise will increase its with the partial resonance, and transform circuit technology, high frequency can be realized in theory and can reduce the noise, but part of the practical application of resonant conversion technology still have a technical problem, so in this area still need to carry out a lot of work, in order to make the technology to practional utilization.Power electronic technology unceasing innovation, switch power supply industry has broad prospects for development. To speed up the development of switch power industry in China, we must walk speed of technological innovation road, combination with Chinese characteristics in the joint development path, for I the high-speed development of national economy to make the contribution. The basic principle and component functionAccording to the control principle of switch power to classification, we have the following 3 kinds of work mode:1) pulse width adjustment type, abbreviation Modulation Pulse Width pulse width Modulation (PWM) type, abbreviation for. Its main characteristic is fixed switching frequency, pulse width to adjust by changing voltage 390v, realize the purpose. Its core is the pulse width modulator. Switch cycle for designing filter circuit fixed provided convenience. However, its shortcomings is influenced by the power switch conduction time limit minimum of output voltage cannot be wide range regulation; In addition, the output will take dummy loads commonly (also called pre load), in order to prevent the drag elevated when output voltage. At present, most ofthe integrated switch power adopt PWM way.2) pulse frequency Modulation mode pulse frequency Modulation (, referred to Pulse Frequency Modulation, abbreviation for PFM) type. Its characteristic is will pulse width fixed by changing switch frequency to adjust voltage 390v, realize the purpose. Its core is the pulse frequency modulator. Circuit design to use fixed pulse-width generator to replace the pulse width omdulatros and use sawtooth wave generator voltage?Frequency converter (for example VCO changes frequency VCO). It on voltage stability principle is: when the output voltage Uo rises, the output signal controller pulse width unchanged and cycle longer, make Uo 390v decreases, and reduction. PFM type of switch power supply output voltage range is very wide, output terminal don't meet dummy loads. PWM way and way of PFM respectively modulating waveform is shown in figure 1 (a), (b) shows, tp says pulse width (namely power switch tube conduction time tON), T represent cycle. It can be easy to see the difference between the two. But they have something in common: (1) all use time ratio control (TRC) on voltage stability principle, whether change tp, finally adjustment or T is pulse 390v. Although adopted in different ways, but control goals, is all rivers run into the sea. (2) when load by light weight, or input voltage respectively, from high changed by increasing the pulse width, higher frequency method to make the output voltage remained stable.3) mix modulation mode, it is to point to the pulse width and switching frequency is not fixed, each other can change, it belongs to the way the PWM and PFM blend mode. It contains a pulsewidthomdulatros and pulse frequency modulator. Because and T all can adjust alone, so occupies emptiescompared to adjust the most wide range, suitable for making the output voltage for laboratories that use a wide range of can adjust switching power supply. Above 3 work collectively referred to as "Time Ratio Control" (as a Control, from TRC) way. As noted, pulse width omdulatros either as a independent IC use (for example UC3842 type pulse width omdulatros), can also be integrated in DC/DC converter (for example LM2576 type switching voltage regulators integrated circuit), still can integration in AC/DC converter (for exampleTOP250 type monolithic integrated circuit switching power supply. Among them, the switching voltage regulators belong to DC/DC power converter, switching power supply general for AC/DC power converter.The typical structure of switch power as figure1shows, its working principle is: the first utility into power rectifier and filtering into high voltage dc and then through the switch circuit and high-frequency switch to high frequency low pressure pulse transformer, and then after rectification and filter circuits, finally output low voltage dc power. Meanwhile in the output parts have a circuit feedback to control circuit, through the control PWM occupies emptiescompared to achieve output voltage stability.Figure 1 typical structure of switch power supplySwitching power supply by these four components:1) the main circuit: exchange network input, from the main circuit to dc output. Mainly includes input filter, rectifier and filtering, inverter, and output rectifier and filtering.(1) input filter: its effect is the power grid existing clutter filtering, also hinder the machine produces clutter feedback to public power grid.(2) rectifier and filter: the power grid ac power directly for a smooth dc rectifier, for the next level transformation.(3) inverter: will the dc after rectifying a high-frequency ac, this is the core of high frequency switching power supply, the higher the frequency, the volume, weight and the ratio of power output and smaller.(4) Out put rectifier and filter: according to load needs, providing stable and reliable dc power supply. 2) control circuit: on the one hand, from the output bysampling with set standards to compare, and then to control inverter, changing its frequency or pulse width, achieve output stability, on the other hand, according to data provided by the test circuit, the protection circuit differential, provide control circuit to the machine to various protection measures. Including the output feedback circuit and sampling circuit, pulse width modulator. 3) the detection and protection circuit: detection circuit had current detection, over-voltage detection, owe voltage detection, overheat detection, etc.; Protection circuit can be divided over current protection, over-voltage protection, owe voltage protection, the ground-clamp protection, overheating protection, automatic restart, soft start, slow startup, etc. Various types. 4) Other circuit: if the sawtooth wave generator, offset circuit, optical coupler, etc.智能开关电源中文:随着电子技术的高速发展,电子系统的应用领域越来越广泛,电子设备的种类也越来越多,电子设备与人们的工作、生活的关系日益密切。

linearsyetems全系列参数查询替换对照表

2

Junction Field Effect Transistors

Monolithic Dual Amplifiers

N Channel

P/N en ∆VGS BVGSS V min IDSS IGSS gfs µS min PKG. nV/√Hz mV max max mA pA min max

F4,F7 F4,F7 F4,F7

HIGH FREQUENCY

2N/PN/SST4416 2N/PN/SST4416A J/SST210 J/SST211 J/SST212 J/SST/U308 J/SST/U309 J/SST/U310 6 6 10 10 10 6 6 6 -6.0 -6.0 -3.0 -4.5 -6.0 -6.5 -4.0 -6.5 -30 -35 -25 -25 -25 -25 -25 -25 5 -100 4500 5 -100 4500 2 -100 4000 7 -100 6000 15 -100 7000 12 -1000 8000 12 -1000 10000 24 -1000 8000

Selection Guide and Cross Reference

Linear Integrated Systems

SMALL SIGNAL DISCRETE SEMICONDUCTORS

JFETs

DMOS Switches

BJTs

MOSFETs

Linear Integrated Systems

F3,F6,F7 F3,F6,F7 F4,F7 F4,F7 F4,F7 F1,F4,F7 F1,F4,F7 F1,F4,F7

HIGH FREQUENCY

2N/SST5911 2N/SST5912 2N/SST5912C U/SST440 U/SST441 20 20 20 20 20 10 15 40 10 20 -25 -25 -25 -25 -25 7 7 7 6 6 -50 -50 -50 4000 4000 4000

各种LED驱动芯片

意法半导体(ST)推出一款驱动电流高达80mA的24在一个7x7mm的TQFP48封装内,新产品效能相当于三个普通的8路输出驱动器。

STP24DP05内置SPI端口提供精确的控制诊断功能。