基于FPGA实现FIR滤波器的研究

基于FPGA的FIR数字滤波器的实现

G r a p h ) 算法进 一步 简化 C S D编码 . 然后采 用 A l t e r a 公

司的 F P G A芯片来实现信号处理中的 F I R数字滤波器.

实验证 明这是 一种 F I R数 字 滤 波 器 的 较 好 的 设 计 选 择, 具 有 应 用 价值

HUA Z e , ZHAO Xi n g -h a n g , F U Z h a o - y a n g , L U Yo u , Z HANG Ni

( 1 ) 从最低有效位开始 . 用 1 0 …( ) - 1 取 代 所 有 大 于 2的 1 序 列 。此 外 还 需 用 1 1 0 — 1 取代 1 0 1 1 。 ( 2 ) 从最高有效位开始 , 用0 1 1 代替 1 0 - 1 。 例如 :

( 9 1 ) 1 0 = ( 1 0 1 1 0 1 1 ) 2 - ( 1 1 0 旷1 0 - 1 ) 佳c s D

收稿 日期 : 2 01 3 — 0 9 —1 0 修稿 日期 : 2 0 1 3 —1 0 —1 0

作 者 简介 : 陈剑 冰 , 男, 本科 , 研 究 方 向 为信 号 处理

④ 现 代 计算 机 2 0 1 3 . 1 0 中

Ap p l i c a t i o n o f He t e r O g e n e Ou S Sy s t e m I n t e g r a t i o n i n I n t e l l i g en t Tr a n s p or t a t i o n I n t e g r a t e d I n f o r ma t i o n PI a t f Or m

★基 金 项 目: 广 东省 科 技 厅 产 学研 项 目( No _ 2 0 1 2 B 0 9 1 1 0 0 3 4 9 ) 、 广 东省 经 信 委 项 目( No . G DE I D2 0 1 0 I s 0 3 4 ) 、 广 州市 越 秀 区科 技 项 目 ( No . 2 0 1 2 一 G X一 0 0 4 )

基于FPGA的通用FIR滤波器设计

-

495 6

. . . . . . . . . . . . . . — —

实

验

技

术

与

管

理

第 2 7卷

第 1 0期

21 0 0年 1 O月

.

CN1 — 2 3 T 1 0 4/

Ex e i nt lTe hnM n g me t n

中 图分 类号 : N7 3 T 1 文献标志码 : A 文 章编 号 : 0 2 4 5 ( 0 0 1 — 0 9 0 1 0— 96 2 1 )0 0 6 — 4

Dein o nvra I ftrb sdo P sg fu iesl R i e ae n F GA F l

V0 . 7 NO 0 Oc .20 0 12 .1 t 1

基 于 F G 的通 用 FR滤 波器 设 计 PA I

聂 伟 ,杨 胜 姚 ,王 岩 嵩

( 京 化 工 大 学 计 算机 系统 与 通信 实验 中心 ,北 京 10 2 ) 北 0 0 9

摘

要 :提 出 了一 种 基 于 FP GA(il r g a f dp o rmma l aea ry 的 通 用 F R(iiei us e p n e 滤 波 器 设 e beg t ra ) I fnt mp lers o s )

b n —t p。a d i h st ea v n a e fhg r q e c e ou in a d ls e o ren e e .Th o g alb a d FP a d so n t a h d a t g so i h fe u n y rs l t n s r s u c e d d o e r u h M ta n — GA i lt n 。t er s l h w h tt i f t rme t h e in r q i me t . smu a i s h e ut s o t a h s i e e st ed sg e ur o s l e ns Ke r s n v r a R f t r i i l i e ;FP y wo d :u ie s lFI i e ;dg t l r l a ft GA;wi d w t o n o me h d

基于FPGA乘法器的FIR滤波器系统设计

基于FPGA乘法器的FIR滤波器系统设计FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,可以根据设计者的需求和要求进行编程,实现各种数字电路功能。

FIR (Finite Impulse Response)滤波器是一种常用的数字滤波器,其特点是能够对输入信号的有限长度的响应进行滤波处理。

本文将介绍基于FPGA乘法器的FIR滤波器系统设计。

首先,介绍FIR滤波器的原理。

FIR滤波器是一种线性时不变系统,其输出信号由输入信号的加权和组成。

FIR滤波器的输入经过一串系数的加权运算后,得到滤波器的输出。

FIR滤波器的传输函数为:H(z) = b0 + b1*z^(-1) + b2*z^(-2) + ... + bn*z^(-n)其中,bi是滤波器的系数,n是滤波器的阶数,z为单位延迟。

FIR 滤波器的输出信号可以表示为:y(n) = b0*x(n) + b1*x(n-1) + b2*x(n-2) + ... + bn*x(n-n)其中,x是输入信号,y是输出信号。

FIR滤波器的阶数决定了滤波器的性能,阶数越高,滤波器的频率响应越陡峭。

接下来,介绍基于FPGA乘法器的FIR滤波器系统设计。

FPGA乘法器是FPGA中的一种硬件资源,通常用于实现乘法运算。

FPGA乘法器的乘法操作可以并行地执行,可以大大提高FIR滤波器的运算速度。

在设计基于FPGA乘法器的FIR滤波器系统时,首先需要确定FIR滤波器的阶数和系数。

根据滤波器的需求,可以选择不同的阶数和系数。

然后,根据FIR滤波器的传输函数,可以将其转化为差分方程形式。

差分方程形式如下:y(n) = b0*x(n) + b1*x(n-1) + b2*x(n-2) + ... + bn*x(n-n)然后,将差分方程形式转化为数据流形式。

数据流形式中的每一步计算只涉及到少量的数据,可以并行地执行。

数据流形式如下:y(n) = b0*x(n) + b1*x(n-1) + b2*x(n-2) + ... + bn*x(0)接下来,需要将数据流形式转化为硬件电路。

基于FPGA的FIR滤波器设计

基于FPGA 的FIR 滤波器设计一 、设计目的为了帮助学生深入理解和消化基本理论、进一步提高综合应用能力并且锻炼独立解决问题的能力,我们将《数字信号处理》、《集成电路原理与应用》和《《FPGA 系统设计与应用》几门课程融合在一起开设的FPGA 综合实验课程设计。

本次完成的是利用FPGA 来完成FIR 滤波器的设计、程序设计和实验调试任务。

二、设计要求(1)基本要求利用所学知识,采用VHDL 语言完成FIR 滤波器的设计仿真。

要求用VHDL 编程设计底层文件,顶层文件可任意(可用原理图方式或文本方式);完成仿真文件(包括MATLAB 和QUARTUSII 两种仿真)并对其结果比较。

具体设计指标如下: (1)采样频率S F =80KHz ;(2)截止频率KHz F C 10=;(3)输入序列为10位(最高位为符号位); (4)窗口类型为kaiser 窗,β=0.5 ; (5)滤波器长度为16 ; (6)输出结果保留10位。

(2)提高部分根据所学知识,设计出一个具有频率控制功能DDS ,要求输出频率分别为10KHz 和100KHz ,将输出的两路数字信号进行叠加,并通过所设计的FIR 滤波器进行滤波,将滤波输出的数字信号通过D/A 转换电路输出波形,并用示波器观察输出波形,并完成测试结果分析。

结构框图如图1-1所示。

图2-1 整体结构框图三、设计原理3.1 FIR 滤波器由线性系统理论可知,在某种适度条件下,输入到线性系统的一个冲击完全可以表征系统。

当我们处理有限的离散数据时,线形系统的响应(包括对冲击的响应)也是有限的。

若线性系统仅是一个空间滤波器,则通过简单地观察它对冲击的响应,我们就可以完全确定该滤波器。

通过这种方式确定的滤波器称为有限冲击响应(FIR)滤波器。

3.2 线性FIR 滤波器原理FIR 滤波器响应(简称FIR )系统的单位脉冲响应()h n 为有限长序列,系统函数()H z 在有限z 平面上不存在极点,其运算结构中不存在反馈支路,即没有环路。

基于FPGA的FIR滤波器设计与仿真

数字滤波器; 分布 式 算 法 ;P A FG 中图分 类 号 T 3 1 P 1 文 献标 志 码 A

滤波器需 要执行 无 限数量 卷 积 , 能得 到较 好 的 幅度特性 , 相位 特性 其 是非线性 的 ; I 波器 由有 限个 采样 值 组 成 , 构 成 的系 统总 是稳 FR滤 其 定 的 , 易于实现 线性相 位 …. 且 由于 在语音 信 号处 理 、 图像 处理 、 数字 通信等传 输过程 中不能有 明显 的相位失真 , FR滤波器在 满足一定 而 I 对称条件 下可 以实现 I I R滤波器 难 以实 现 的线 性相 位 , 因而得 到广泛

特 别适合如 FR、丌 等数 字信号处 理任务 . I F 利用 F G P A可 以重 复配置 高精 度的 FR滤波器 , 用 V D I 使 H L硬件 描述语 言改变滤 波器 的系数和

阶数 , 能实 现大 量 的卷 积运 算算 法 J 结合 M xls 具软 件 的辅 并 . apu 工

案速 度 快 、 时性 好 、 省 硬 件 资 源 , 实 节 具 有重 要 的 工程 应 用价 值 . 关 键 词

实 现数字化 是 控 制 系统 的重 要发 展 方 向 , 而数 字 信 号处 理 已在

通信 、 语音 、 图像 、 自动控 制 、 达 、 事 、 空 航 天等 领 域 广 泛应 用 . 雷 军 航 数 字信号 处 理 方 法 通 常 涉 及 变 换 、 波 、 谱 分 析 、 码 解 码 等 处 滤 频 编 理¨. 数字滤 波是数 字信号处 理重 要 环节 , 它能 满 足滤 波器 对幅度 和 相 位特性 的严格 要 求 , 克服 模 拟 滤 波器 所 无 法解 决 的 电压 和 温度 漂 移 以及噪声 等 问题 , 而有 限冲激 响应 FR滤 波器在设计 任意 幅频 特性 I 的同时能够保证 严格 的线性相 位特性 . 数 字滤波器 根 据其 冲激 响应 函数 的 时域 特性 , 分 为无 限 长 冲 可

基于FPGA设计的FIR滤波器的实现与对比

从 FR 公 式 出发 , 以得 道 m 滤 波 器 的 输 出 是 输 人 数 I 可

据 和 系 数相 卷 积 得 到 的 , 公 式 ( ) 示 。 如 1所

L I 波器 分 为两类 : R和 F R滤波器 。 数据 通讯 , T滤 I I I 在 语音 信 号处 理 , 图像 处理 , 达信 号处 理 中 , 能有 明显 的相位 失 真 , 雷 不 而 有 限长 单 位 冲 激 相 应 F R具 有 严 格 的 线 性 相 位 的特 点 : I 此 外 ,I F R滤 波器 的单 位抽 样 响 应 序 列是 有 限 长 的 .因此 是 一 个

法) 。在 文 中是 以 一 3 2阶 F R滤 波 器 进 行 比较 的 。 I

^L l

∑s) Ⅳ ∑ ( s ) o ( - = ) ) ( ( + ( ) (= 0 )

i0 - i0 -

s 1 x 1 ( ) h( +…+ ( 1  ̄ N-1 ( ) h( ) 2 x 2) 5 ) h( )

稳 定 的系 统 , FR 滤 波 器 在 上 述 领 域 中 得 到 广 泛 应用 [。 故 I ห้องสมุดไป่ตู้ 1

ysn () 2 si hN i =() n= ( x ( -) )

() 1

具 有 严 格 线 性 相 位 FR滤 波 器 具有 对 称 的性 质 .即 满 足 I

偶 对称 性 或 奇 对 称 , 在这 里 介 绍 下 偶 对 称 的 结构 , 满 足 公 式 即

Re lz to nd c m pa io ft e FI ft r b s d o FPGA aiai n a o rs n o h R le a e n

CUILin a g,ZHANG — in Zhixa

基于FPGA的FIR数字滤波器设计概要

基于FPGA的FIR数字滤波器设计摘要:文章介绍了CSD编码和流水线技术,将它们运用到VHDL语言编程中,设计了一个16阶8位输入17位输出的线性相位结构FIR数字滤波器,仿真结果符合要求。

最后比较了两种方法的使用在硬件资源和系统处理速度上的优缺点。

有限冲激响应(FIR数字滤波器和无限冲激响应(IIR数字滤波器广泛应用于数字信号处理系统中。

IIR数字滤波器方便简单,但它相位的非线性,要求采用全通网络进行相位校正,且稳定性难以保障。

FIR滤波器具有很好的线性相位特性,使得它越来越受到广泛的重视。

This article introduces CSD coding and production line technique, will they use to VHDL language programming, design of a 16th order 8-bit input 17 output of linear phase FIR digital filters, structural simulation results accord with the requirement. Last two methods were compared, the use of the system hardware resources and processing speed on the advantages and disadvantages. Finite impulse response (FIR digital filters and infinite impulse response (IIR digital filters widely used in digital signal processing system. IIR digital filter convenience simple, but it phase of the nonlinear requirements adopts full ventilation network phase calibration, and stability difficulty safeguards. FIR filters have very good linear phase characteristic, making it more and more extensive attention.关键词:FIR数字滤波器;线性相位;CSD编码;流水线技术1.引言数字滤波在图像处理、语音识别和模式识别等数字信号处理中占有重要地位。

基于FPGA的FIR滤波器设计

—

s j — q u a n 一 1 2 =r o u n d ( s j/ m a x ( s j ) ) ( 2 ( b i n l o n g 一 1 ) 一

1 ) ) :

量化 完 成 后 , 还 需 要把 参 数 写成 文 件 , 等待 F P G A的调 用 。 M A T L A B中把测 试文 件写 成文 件如 下 :

f i d o u t = f o p e n( ’ r e s u l t . t x t ’ , ’ w ’ ) : % o p e n r e s u l t f i l e

an d wai t f o r wri t e

1 基本流 程

一

f o r i = l : l e n g t h ( s jq u a n 一 1 2 )

2 1 5 0 0 6;

摘 要 介 绍 了基 于 F P G A芯片进 行 F I R 滤 波 器的设 计过 程 , 具体 涉及 到 M A T L A B 对F I R滤波 器 的仿真 、数据 的量化 和 生成 ; F P G A对 F I R滤 波器 的设 计 、仿真 和数 据 生成 , 最后 形 成 F P G A和 M A T L A B 联 合设 计 F I R滤 波器 。 关键词 F G P A; F I R; M A T L A B 中图 分类 号 : T N 9 1 1 文 献标 识码 : A 文 章编 号 : 1 6 7 1 — 7 5 9 7( 2 0 1 4 )0 3 — 0 0 3 4 - 0 1

w n: 表 示滤 波器 的截 至频 率 。

P O R T(

rs t :I N s t d

基于fpga的滤波器设计与实现

基于fpga的滤波器设计与实现基于FPGA的滤波器设计与实现一、引言滤波器是信号处理中常用的一种工具,它可以通过剔除或增强信号中的特定频率分量来改变信号的特性。

而基于FPGA的滤波器是一种利用可编程逻辑器件FPGA来实现滤波功能的方法。

本文将介绍基于FPGA的滤波器的设计与实现过程。

二、滤波器的基本原理滤波器主要通过改变信号的频谱特征来实现滤波效果。

它可以分为两类:低通滤波器和高通滤波器。

低通滤波器通过剔除高频分量,保留低频分量;高通滤波器则相反,剔除低频分量,保留高频分量。

滤波器的设计需要根据具体的需求选择合适的滤波器类型和参数。

三、基于FPGA的滤波器设计与实现基于FPGA的滤波器设计与实现可以分为以下几个步骤:1. 确定滤波器类型和参数:根据实际需求,选择合适的滤波器类型和参数。

例如,如果需要设计一个低通滤波器,需要确定截止频率和滤波器阶数等参数。

2. 数字滤波器设计:将滤波器的模拟设计转化为数字滤波器的设计。

常见的数字滤波器设计方法有FIR滤波器设计和IIR滤波器设计。

FIR滤波器是一种无反馈的滤波器,具有线性相位特性;IIR滤波器则具有反馈结构,可以实现更高阶的滤波器。

3. 将数字滤波器转化为FPGA可实现的结构:将数字滤波器转化为FPGA可实现的结构,可以采用直接形式实现、级联形式实现或者管线化实现等方法。

其中,直接形式实现是最简单直观的方法,但其硬件资源占用较多;级联形式实现可以减少硬件资源的占用,但增加了延迟;管线化实现则可以兼顾硬件资源和延迟。

4. 使用HDL语言进行FPGA设计:使用HDL语言,如VHDL或Verilog,进行FPGA设计。

根据设计的结构和功能,编写相应的HDL代码。

在编写代码时,需要注意代码的可重用性和可维护性,以便后续的设计和调试。

5. 硬件验证和性能优化:完成HDL代码后,进行FPGA的硬件验证和性能优化。

通过仿真和验证,确保设计的正确性和稳定性。

同时,可以根据实际需求对硬件进行优化,如减小资源占用、降低功耗等。

FPGA实现FIR抽取滤波器的设计

FPGA实现FIR抽取滤波器的设计之蔡仲巾千创作FIR(fini te impulse response)滤波器是数字信号处理系统中最基本的元件,它可以在包管任意幅频特性的同时具有严格的线性相频特性,同时其单位冲激响应是有限的,没有输入到输出的反馈,系统稳定。

因此,FIR滤波器在通信、图像处理、模式识别等领域都有着广泛的应用。

在工程实践中,往往要求对信号处理要有实时性和灵活性,而已有的一些软件和硬件实现方式则难以同时达到这两方面的要求。

随着可编程逻辑器件的发展,使用FPGA来实现FIR滤波器,既具有实时性,又兼顾了一定的灵活性,越来越多的电子工程师采取FPGA器件来实现FIR滤波器。

1 FIR滤波器工作原理在进入FIR滤波器前,首先要将信号通过A/D器件进行模数转换,使之成为8bit的数字信号,一般可用速度较高的逐次逼进式A/D转换器,不管采取乘累加方法还是分布式算法设计FIR 滤波器,滤波器输出的数据都是一串序列,要使它能直观地反应出来,还需经过数模转换,因此由FPGA构成的FIR滤波器的输出须外接D/A模块。

FPGA有着规整的内部逻辑阵列和丰富的连线资源,特别适合于数字信号处理任务,相对于串行运算为主导的通用DSP芯片来说,其并行性和可扩展性更好,利用FPGA乘累加的快速算法,可以设计出高速的FIR数字滤波器。

2 16阶滤波器结构在滤波过程中实现抽取,对于抽取率为N的抽取滤波器而言,当进来N个数据时滤波器完成1次滤波运算,输出1次滤波结果。

抽取滤波器的结果和先滤波后抽取的结果是一致的,只是对于同样的数据,进行滤波运算的次数大大减少。

在数字系统中采取拙取滤波器的最大优点是增加了每次滤波的可处理时间,从而达到实现高速输入数据的目的。

采样数据与滤波器系数在控制电路的作用下,分别对应相乘并与前一个乘积累加,经过多次(有多少阶就要多少次)反复的乘累加最后输出滤波结果,将相同系数归类,16阶滤波器公式:乘法器的数量减少一半,但加法器的数量增多了,但相对乘法运算来说,加法运算所占用的资源少的多,运算的速度也快得多。

FIR数字滤波器的FPGA实现研究

( . colfIsrm n S i c 1 S ho nt e t c n e& E gneig S uhat nvri, ajn 10 6 C i ; o u e nier , otes U i sy N n g 20 9 , hn n e t i a

基于FPGA的FIR数字滤波器的设计和实现

基于FPGA的FIR数字滤波器的设计和实现摘要:本文基于FPGA平台实现了一种FIR数字滤波器,通过对滤波器的设计与实现过程的详细介绍,展示了FPGA在数字滤波器中的应用优势。

首先介绍了数字滤波器的原理及其在信号处理中的重要性,并对FPGA及其特点进行了概述。

接着,详细介绍了FIR滤波器的原理以及其在FPGA上的实现步骤,分析了滤波器设计中需要考虑到的各种因素。

最后,通过实验验证了FPGA上实现的FIR滤波器的性能,并对优化策略进行了讨论。

关键词:FPGA,FIR滤波器,数字信号处理,性能优化1. 引言数字滤波器是现代信号处理的重要组成部分,通过选择性地传递或抑制输入信号的特定频率组成部分,对信号进行处理和改善。

FIR滤波器是数字滤波器中最常用的一种类型,具有线性相位特性、稳定性较强以及易于实现等优势。

而FPGA作为一种可编程逻辑器件,具有灵活性高、可重构性强等特点,成为实现数字滤波器的理想平台。

2. FIR滤波器的原理FIR滤波器是一种线性时不变系统,其输出仅和当前输入值以及过去若干个输入值有关。

该滤波器的输出可以通过输入信号的线性加权和来计算,其中,每个输入值的加权系数通过FIR 滤波器的系数来确定。

FIR滤波器的系数决定了它对不同频率分量的响应,从而实现了信号的滤波目的。

3. FIR滤波器在FPGA上的实现步骤(1)选择合适的FPGA平台和开发工具,如Xilinx FPGA平台和Vivado开发工具。

(2)根据所要设计的滤波器的需求,确定其采样频率、截止频率和滤波器类型等参数,并进行系统级设计。

(3)根据所选参数,设计FIR滤波器的传递函数,并确定滤波器的阶数和系数。

(4)通过数学运算或者通过滤波器设计软件生成滤波器的差分方程。

(5)根据生成的差分方程,使用HDL(HardwareDescription Language)进行滤波器的编写。

(6)进行FPGA的综合、布局与布线、下载与验证,完成滤波器的硬件实现。

基于FPGA的FIR滤波器的设计(毕业设计) 可用

目录摘要 (2)英文摘要 (3)1 引言 (3)1.1国内外研究现状 (4)1.2本论文的研究内容及主要工作 (6)2 FIR数字滤波器设计 (6)2.1数字滤波器基础 (6)2.1.1 数字滤波器简介 (6)2.1.2 FIR数字滤波器的结构 (7)2.2 FIR数字滤波器设计方法 (8)2.2.1 窗函数法 (8)2.2.2 频率采样法 (9)2.2.3 等波纹最佳逼近法 (11)2.2.4 三种设计方法的比较......................... 错误!未定义书签。

3 FPGA 设计优点以及分布式算法 (12)3.1 使用FPGA器件进行开发的优点 (13)3.2分布式算法 (14)3.2.1 分布式算法基础 (14)3.2.2 有符号的DA系统 (15)4 基于FPGA的FIR滤波器设计 (15)4.1基于M ATLAB的FIR数字低通滤波器抽头系数的提取 (16)4.1.1 滤波器的设计指标 (16)4.1.2 滤波器的具体设计方法 (16)4.1.3 参数提取与量化 (17)4.2FIR滤波器的FPGA实现 (19)4.2.1 模块划分 (19)4.2.2 FIR滤波器各模块的实现 (20)4.2.3 FIR滤波器的顶层设计 (30)4.3FIR滤波器的系统仿真验证 (32)4.4系统硬件 (36)4.4.1 系统框图 (36)4.4.2 部分芯片简介 (36)4.4.3 AD、DA电路原理图 (39)4.5测试波形及现场照片 (39)4.6数据误差分析 (40)结论 (41)参考文献 (41)附件 (42)基于FPGA的FIR滤波器的设计摘要:本文设计了一个基于FPGA的16阶FIR低通滤波器,使用分布式算法作为滤波器的硬件实现算法,并对其进行了详细的讨论。

针对分布式算法中LUT规模过大的缺点,采用多块查找表的方式减小硬件规模。

在设计中采用了自顶向下的层次化、模块化的设计思想,将整个滤波器划分为多个模块,利用VHDL语言的描述方法进行了各个功能模块的设计,最终完成了FIR数字滤波器的系统设计。

基于FPGA的FIR滤波器的实现

0 0 O1

0 1 00 0l O1 {

,

f1 ・l f c lc1 [ +【】 0 c 】 [ 2

l O 0l l 1 O1 lO 10

c +I】 … c 3 cO+ [】c3 [lc1+【】 J c2+【】 【Jc3

B一1

xn= 2x () 2x() bn∈ ,J {)- aBn+ hbn, () 1 x

b- - o

l… l… I~ 卜 ◆ x 一

将式( ) 人式( ) : 2代 1得

B—I 、一 I

y) 2 (・ (+ t c)h) : In n ∑2 ∑[ ・( n一} )B) 【 c 】 , ( xn ・ n ]

N— I

统算法是等到所有乘 积已经 产生之后再来相加来完成乘 累加运算 的 , 分 布式 算 法 是 一 次 完 成 多 次乘 法 运 算 。同 时 , 布 式 算 法将 乘 法 运 算 转 分 换 成加法运算 , 一方 面可以有效 地提高处理速度 , 另一方 面, 可以有 还 效地节省资源。缺点是查 找表 的大小随滤波器 的阶数的增加呈指数增 长 , 时可 以采用分割查找表 的方法来降低逻辑资源的消耗 。 这 3基 于 F GA的 FR滤 波 器 的 结构 . P I F G 是一 种 基 于 N输 入 查 找 表 技 术 的现 场 可 编 程 门 阵 列 ,具 有 PA 丰富而规则的逻辑资源和布线资源。由于 F G P A内部结构的特点 , 我们 可 以根 据 不 同 的设 计 需 要 ,灵 活 定 制 硬 件 实 现 结 构 。 使用 F G 实 现 PA FR滤波器 , 要考虑计算速度和芯 片面积两个相互制约 的因素 , 实 I 需 在 现过程 中主要运用多级流水线技术 , 采用分布是算法设计乘累加器, 可 极大地减少硬件电路规模 ,而且容易实现流水线技术提高电路的运行 速 度I ” 。在 F G P A中 实 现 的 流程 如 图 3所示 。

基于FPGA的FIR数字滤波器设计

基于FPGA的数字滤波器设计院系:信息科学与工程学院专业班:通信工程1102班姓名:李羚学号:20111181082指导教师:周忠强王军舰2015年5月基于FPGA的FIR数字滤波器设计摘要随着公元的第二十一个世纪的到来,今天我们进入了一个科技日新月异的时代。

在现代电子数字系统中,滤波器都以一个不可缺少的身份出现。

其中,FIR数字滤波器又以其良好的线性特性被广泛和有针对性的大量使用。

众所周知,灵活性和实时性是工程实践中对数字信号处理的基本要求。

在以往使用的各种滤波器技术中,不难发现有许许多多的问题。

但是,随着现代计算机技术在滤波问题上的飞跃,派生出一个全新的分支——数字滤波器。

利用可编程逻辑器件和EDA技术,使用FPGA来实现FIR 滤波器,可以同时兼顾实时性和灵活性。

基于FPGA的FIR数字滤波器的研究势在必行。

本论文讨论基于FPGA的FIR数字滤波器设计,针对该毕业设计要做的基本工作有如下几点:(一)掌握有限冲击响应FIR(Finite Impulse Response,FIR)的基本结构,研究现有的实现方法。

对各种方案和步骤进行比较和论证分析,然后针对目前FIR数字滤波器需要的特点,速度快和硬件规模小,作为指导思想进行设计计算。

(二)基于硬件FPGA的特点,利用Matlab软件以及窗函数法设计滤波器。

对整个FPGA 元件,计划采用模块化、层次化设计思想,从而对各个部分功能进行更为详细的理解和分工设计。

最终FIR数字滤波器的设计语言选择VHDL硬件编程语言。

(三)设计中的软件仿真使用Altera公司的综合性PLD开发软件Quartus II,并且利用Matlab工具进行对比仿真,在仿真的过程中,对比证明,本论文设计的滤波器的技术指标已经全部达标。

关键词:数字滤波器Matlab 可编程逻辑元件模块化算法Based On FPGA Design Of FIR Digital FiltersMajor:Electronic And Information Engineering Department(Information Engineering)Student: YangChengjie Supervisor:FengLiuAbstractAs we have entered the twenty first century,our technology is changing continuously with the times. In the modern electronic digital systems,filters are indispensable. Among them,the FIR digital filters are widely used with the excellent linear characteristic. As is well-known to us all,flexibility and real-time quality are the basic requirements in digital signal processing of engineering practice. Since we have used a variety of filter technology in the past,it is not difficult for us to find many problems in it. Moreover,with the development of modern computer technology in filter,a new branch - digital filter has derived. We make use of the programmable logic devices and EDA technology,together with the FPGA to design the FIR filter,which is real-time and flexible. In a nutshell,it is imperative to do the research in the FIR digital filters based on the technology of FPGA. This thesis is focused on the design of the FIR digital filters based on the technology of FPGA. Several points are worth mentioning here:(1)To understand and master the basic structure of the limited shock Response FIR (Finite Impulse Response,FIR),research existing realization method,to use various solutions to compare and analyze the steps and demonstrations; then,to do the self design and correction concerning the characteristics of the present FIR digital filters,that is,fast in speed and small scale in hardware.(2) To design FIR filter based on the characteristics of FPGA hardware. In the design process,ready to use of Matlab software and window function method design filter. As far as the whole FPGA components are concerned,we plan to carry on the modularized and hierarchic design,in order to have a more detailed understanding of the function of eachpart and make a division of design. Eventually,FIR digital filters will adopt the VHDL hardware programming language.(3) To adopt the comprehensive PLD development software Quartus II of the Altera company in the design of the software simulation. And we will use of the Matlab tools for the simulation 。

基于FPGA的FIR滤波器系统的设计

针对 F R滤 波器 电路 系 统 , 计 了一个 与 之 I 设 专 门配套 的 串 口通 信 软 件 , 软件 能 读 取 串 口数 该 据 , 把 串 口数 据保 存在 以 D T为 后 缀名 的文 件 并 A

个滤 波 系数 , 这些 滤波 系数 来 生成 FR低 通滤 用 I

波器 。

2 FR滤波器 系统硬 件设计 I

F r f r ,% 1. fn ,of) pi ( d ’ 60\ ’ce ; n i

FR滤波器 硬件 电路 主要 由 A D转换 器 、 P I / F—

F l e r ) c s( d ; o i

图 2 F a o 导 出 系数 窗 口 dt l o

在 图 2的 菜单 中 点击 E p r 这 样 就 可 以对 x ot , 系 数 进 行 量 化 。 在 窗 口 中 输 入 “ of ce f=ru d o n

1 2 FR滤波器 系数 的产 生 。 I

F A ol Fl r D s n & A a s ro )是 D T o ( ie ei t g nl i r 1 ys 0

正弦信号进行 A D转换 , / 然后送至 F G P A内部进

一

步处 理 。本 设 计 中采 用 了 A D公 司 的 高性 能

A D转 换 芯 片 A 7 9 , D 6 1每 秒 可 采 样 2 / D 6 1 A 79 5 万 次具有 1 bt 8 i的线性度 ,8位 的串行 数据 输 出 , l 采用 2 7 . V或 5 V单 电源 供 电。与 A I 司推 出 D公 l i 6b t和 1 i 单 端 到 差 分 A C 驱 动 器 8 bt的 D A A 9 11配 合 使 用 , D 4 4 — D 44 - A A 9 11与 A 7 9 D 6 1的 外 围电路连 接 如 图 4 5所 示 , D 4 4 — 、 A A 9 11是一 款 低功耗 、 噪声 差分 驱 动器 。它 采 用易 于 使用 的 低

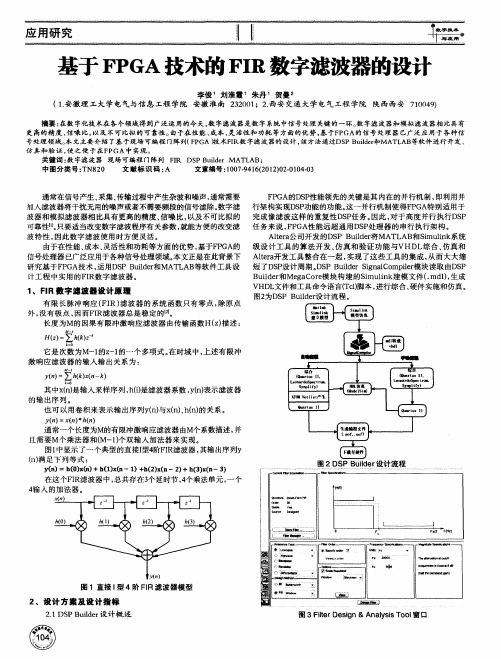

基于FPGA技术的FIR数字滤波器的设计

通常一个长度为M的有 限冲激响应滤波器 由M个系数描述 , 并 静 且需要M个乘法器和( M—1个双输入加法器 来实现 。 ) 图l 中显示 了一个典型的直 接I 阶F R 型4 I 滤波器 , 其输出序列y 执 束瓣 一 ~ () 足 下 列 等 式 : n满

应 用 研 究

基于 F G P A技术的 F R数字滤波器的设计 I

李俊 ’刘淮霞 ,朱丹 ,贺曼2

(. 1 安徽理工大学电气与信息工程 学院 安徽淮南 22 0 ;2西安交通大学电气工程学院 陕西西安 70 4) 30 1 . 10 9

摘要 : 数 字化技 术在 各 个领 域得 到广 泛 运 用的今 天 , 字滤波 器是 数 字 系统 中信 号 处理 关键 的一 环 。 字滤 波器和 模拟 滤 波 器相 比具有 在 数 数 更 高的精 度 、 噪 比 , 及不 可 比拟 的 可 靠性 。 于在 性 能 、 信 以 由 成本 、 活性和 功耗 等方 面 的优 势 , 于F GA的信 号 处 理 器 已广泛 应 用 于各 种信 灵 基 P

: ;

yn ()=h O xn +h 1xn一1 h 2x n一2 +h S xn一3 () () ( ) ( )+ ( ) ( ) () ( )

图 2D ule 设 计 流 程 SP B i r d

在这个FR滤波器 中 , I 总共存 在3 个延时节,个乘法单元, 4 一个 4 入 的加 法 器 。 输

1 I 、FR数字滤波器设计原理

有 限长脉冲响 应( I 滤波器 的系统 函数 只有零点 , F R) 除原 点 外 , 有 极 点 , 而 FR滤 波 器 总 是 稳 定 的【 没 因 I 长度 为M的因果有 限冲激 响应滤波器 由传 输函数H() z 描述 :

基于FPGA的系数可调FIR滤波器设计

l e a j s bec e ce t w r u o f ce t a j sme t i du t l o f ins eep t r ad d pi o f ins du t n n ie tc e ins du t n.Ad p n a i f v i i a—

so e c e ce t , a he c n tt ts o f ce t lo — p t b e mo e s Th a r s f l o u a l i h n e t t r o f i n s nd t n o siu e c e i n s o k u a l d l. i i e dd e s o o k— p t be s c a g d o a a tt e d fe e tfle e u ss I h spa e ,af u — r e le d l t o rfle o e te s d sg e d p h ifr n trr q e t. n t i p r o ro d rf trmo e h f u trpr p riswa e in d i i wi i

Ab ta t sr c :Ac odn ot edf rn ii l in l rc sigrq et wokn so einp oe t o I l r t n c rigt h iee t gt g a o e s e u s,t id fd s rjcs fF R ft ho — f d as p n g i e wi

陈 虹 , 崔 葛瑾

( 东华 大学 信 息科 学与 技术 学 院 , 上海 205 ) 00 1

摘 要 : 据 不 同的数 字信 号 处理要 求 , 出了两种 滤波 系数 在 线 实时调 整 FR 滤波 器 的设 计 方 案 : 根 提 I 自 适应调 整 和直接 设 定调整 。 滤波 系数 自适应 调整 利 用控 制 算 法对 滤波 器的 实 际输 出信 号和期 望信 号的

基于FPGA的线性相移FIR滤波器的实现

目 标等空间分布和运行 状况信息 . 进行动态监测 . 分析风险隐患 , 对可 能发生的突发公共事件进行预测预警 。 453 突发公 共事件发生后 . .- 通过汇总分析相关地区和部门的预测结 果, 结合事件进展情况 , 对事件影响 范围 、 影响方式 、 持续 时间和危害 程度等后果进行综合研 判 4 . 根据有关应 急预案 . .4 5 利用对 突发公共事件的研判结果 . 通过应 急平 台对有关法律法 规 、 政策 、 安全 技术 要求以及处理类似事 件的案 例等进行智能检索 和分析 , 并咨 询专 家意见 , 提供应对 突发 公共事件 的指导流程和辅助决策方案 455 记录事件 的应 对过程 . .. 根据有 关评价指标 . 对应 急过程 和能力 进行综合评估 。 同时 . 可在应急平 台上进行应急处 置模拟推演 . 提高相 关人员突发事件处置的能力和效率 。 在应急管理模块 与调度指挥模块联合部署的情况下 . 急管理模 应

[] 4蒋小 燕捌、 晓薇, 阳, 基于 F G 胡恒 等. P A的 FR数 字滤波器 的设计 与实现 . I 常卅I 院学报. 1 . ( : — 6 工学 2 1 4 )3 1. 0 221 [] 5李书华憎 以成 . 基于分布式算法 的高阶 FR滤波 器及其 F G I P A实现Il 计算 J l 机工程与应用, 1. ( ) 3 — 3 . 2 0 61 : 6 19 0 4 21 [] 6 田耘, 文波 .i x P A开发使用教程f ] 徐 Xl G i F n M. 北京: 清华大学 出版社, 0 , . 2 81 0 1

科技信 息

S IN E&T C N L GY F MA I N CE C E H O O 0R T O

21 年 01

第3 5期

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于FPGA实现FIR滤波器的研究

摘要:针对在FPGA中实现FIR滤波器的关键--乘法运算的高效实现进行了研究,给了了将乘法化为查表的DA算法,并采用这一算法设计了FIR滤波器。

通过FPGA仿零点验证,证明了这一方法是可行和高效的,其实现的滤波器的性能优于用DSP和传统方法实现FIR滤波器。

最后介绍整数的CSD表示和还处于研究阶段的根据FPGA实现的要求改进的最优表示。

关键词:FPGA DA FIR滤波器 CSD

数字滤波器是语音与图像处理、模式识别、雷达信号处理、频谱分析等应用中的一种基本的处理部件,它能满足波器对幅度和相位特性的严格要求,避免模拟乙波器所无法克服的电压漂移、温度漂移和噪声等问题。

有限冲激响应(FIR)滤波器能在设计任意幅频特性的同时保证严格的线性相位特性。

目前FIR滤波器的实现方法有三种:利用单片通用数字滤波器集成电路、DSP器件和可编程逻辑器件实现。

单片通用数字滤波器使用方便,但由于字长和阶数的规格较少,不能完全满足实际需要。

使用DSP器件实现虽然简单,但由于程序顺序执行,执行速度必然不快。

FPGA有着规整的内部逻辑阵列和丰富的连线资源,特别适合于数字信号处理任务,相对于串行运算为主导的通用DSP芯片来说,其并行性和可扩展性更好。

但长期以来,FPGA一直被用于系统逻辑或时序控制上,很少有信号处理方面的应用,其原因主要是因为在FPGA中缺乏实现乘法运算的有效结构。

现在这个问题得到了解决,使FPGA在数字信号处理方面有了长足的发展。

1 分布式运算原理

分布式算法(DA)早在1973年就已经被Croisier提出来了,但是直到FPGA出现以后,才被广泛地应用在FPGA中计算乘积和。

一个线性时不变网络的输出可以用下式表示:

=c[0]x[0]+c[1]x[1]+…+c[N-1]x[N-1]

假设系数c[n]是已知常数,x[n]是变量,在有符号DA系统中假设变量x[n]的表达式如下:

式中,xb[n]表示z[叫的第b位,而x[n]也就是x的第n次采样。

于是,内积y可以表示为:

重新分别求和(也就是分布式算法的由来),其结果如下:

从(1)式可以发现,分布式算法是一种以实现乘加运算为目的的运算方法。

它与传统算法实现乘加运算的不同在于执行部分积运算的先后顺序不同。

分布式算法在实现乘加功能时,是通过将各输入数据的每一对应位产生的部分积预先进行相加形成相应的部分积,然后再对各个部分积累加形成最终结果的,而传统算法是等到所有乘积已经产生之后再来相加完成乘加运算的。

与传统串行算法相比,分布式算法可极大地减少硬件电路的规模,提高电路的执行速度。

它的实现框图如图1(虚线为流水线寄存器)所示。

2 用分布式原理实现FIR滤波器

2.1 串行方式

当系统对速度的要求不高时,可以采用串行的设计方法,即采用一个DA表、一个并行累加器和少量的寄存器就可以了。

在用LUT实现串行分布式算法的时候,假设系数为8位,则DA表的规模为2N×8位。

可以看到如果抽头系数N过多,则DA表的规模将十分庞大。

这是因为LUT的规模随着地址空间的变化(也就是N的增加)而呈指数增加。

例如EPFl0K20包含1152个LC,而一个27×7位的表就需要394个LC。

当N过大时,一个FPGA器件就不够用了。

为了减小规模,可以利用部分表计算,然后将结果相加。

假定长度为LN的内积为:

将和分配到L个独立的N阶并行DA的LUT之中结果如下:

如图2所示,实现一个4N的DA设计需要3个次辅助加法器。

表格的规模从一个2 N×B位的LUT降到4个2 N×B的位表。

如果再加上流水线寄存器,由于EPFl0K20每个LC后面都跟有一个寄存器,所以并没有增加电路规模,而速度却得到了提高。

2.2 并行方式

采用并行方式的好处是处理速度得到了提高。

由于数据是并行输入,所以计算速度要比串行方式快,但它的代价是硬件规模更大了。

下面举出全并行的例子。

设sum[0]=c[0]x0+[0]+c[1]x0[1]+…+c[N-1]x0[N-1]

sum[B-1]=c[B-1]xB-1[0]+c[1]xB-1[1]+…c[N-1]+xB-1[N-1]

可将(1)式改写成如下形式

y=su m[0]+sum[1]2 1+sum[2] 2+…+sum[B-1]2 B-1 (2)

利用式(2)可得一种直观的加法器树,如图3所示。

虽然硬件规模加大了,但是如果把系数的个数限制在4个或8个,再加上流水线寄存器,这个代价还是值得的。

而且每张表都是相同的,不用为每个采样都设计一张表,减小了设计量。

DA算法的主要特点,是巧妙地利用ROM查找表将固定系数的MAC运算转化为查表操作,其运算速度不随系数和输入数据位数的增加而降低,而且相对直接实现乘法器而言在硬件规模上得到了极大的改善。

利用ALTERA的FLEXl0K实现的16阶8位系数的并行FIR滤波器,其时钟频率可以达到101MHz,而实现的16阶8位系数的串行FIR滤波器,其时钟频率可以达到63MHz,每9个时钟周期可完成一次计算。

但是其系数是传统二进制的,造成了很大的冗余(对于用逐位相加法实现的乘法器,当系数有一位为零时不用相加,零位越多,冗余越大),而且查找表的大小随着滤波器阶数的增加成指数增加,虽然可以采用将大查找表分解为小查找表,但是无法从根本上解决这一问题,这些都是DA方法的缺点。

后面将对FIR滤波器实现给出新的设计方法,进一步降低逻辑资源的消耗。

3 CSD码及最优化方法

一个整数X与另一整数Y的乘积的二进制表示可以写成:

对于标准二进制,由于sn=0时的对应项Y2n并不参与累加运算,所以可以用另一种表示方法使非零元素的数量降低,从而使加法器的数目减少,降低硬件规模。

有符号数字量(SD)有三重值{0,-1,+1},如果任意两个非零位均不相邻,即为标准有符号数字量(CSD)。

可以证明CSD表示对给定数是唯一的并且是最少非零位的。

CSD表示相对于标准二进制表示的改进在于引入了负的符号位,从而降低了非零位个数,大大降低了逻辑资源的占用(大约平均降低33%的逻辑资源)。

当用硬件实现时,常常限制系数位数,即每个系数与N个正(负)2的幂次之和近似。

标准二进制数在整数轴上是紧密和均匀分布的,而CSD码是非均匀分布的,其对实系数的量化误差比标准二进制大,虽然增加N可以减小量化误差,但是会增大逻辑资源的消耗;而且CSD表示无法应用流水线结构,从而降低处理速度。

还可采用优化的方法将系数先拆分成几个因子,再实现具体因子。

这就是最优化的代码。

例如对系数93,93=10111012=1100101CSD。

用最优化法,系数93可以表示成93=3·31,每个因子需要一个加法器,如图4所示。

从图中可以看出,CSD码需要三个加法器,而最优法只需要两个加法器;CSD码的重要缺陷在于每一级加法都需要初节点参与,而最优表示仅依赖上一级加法的结果,因此也就更适合流水线处理。

Dempster等人提出了需要1到4个加法器的所有可能配置表。

利用这张表,就可以合成成本在0与4个加法器之间的所有8位二进制整数。

本文首先给出了一种巧妙利用FPGA的查找表,将乘法转化为查找表运算的DA算法,并用ALTERA 的FLEXlOK器件分别实现了一个8位16阶的串行与并行FIR滤波器,系统频率分别达到63MHz 与101MHz,采样速度分别达到7MSPS与101MSPS。

而DSP实现的FIR滤波器只能达到5MSPS,明显低于FPGA。

用传统的位串行方法实现的一个8阶8位FIR滤波器,也只能达到5MSPS,明显低于串行式DA方法;接着,针对系数的二进制表示非零位不是最少(即实现系数乘法的加法器不是最少)的问题,介绍了整数的CSD表示以及最优表示,它们可以用较小的代价和与加法器级数无关的处理速度实现整数乘法运算,能比DA方法用更少的逻辑资源实现FIR滤波器。

这些算法都不同于传统的设计观念,为基于FPGA的DSP设计提出了新的思路,必将在高速FIR滤波器设计、高速FFT设计中得到广泛的应用。

随着FPCA集成规模的不断提高,许多复杂的数学运算已经可以用FPCA来实现,利用单片FPGA实现系统的设想即将变为现实。