基于FPGA的FIR滤波器设计

基于FPGA的FIR数字滤波器设计

1、F PGA技术简介现场可编程门阵列FPGA是80年代末开始使用的大规模可编程数字IC器件,它充分利用EDA技术进行器件的开发与应用。

用户借助于计算机不仅能自行设计自己的专用集成电路芯片,还可在计算机上进行功能仿真和时序仿真,及时发现问题,调整电路,改进设计方案。

这样,设计者不必动手搭接电路、调试验证,只需短时间内在计算机上操作即可设计出与实际系统相差无几的理想电路。

而且,FPGA器件采用标准化结构,体积小、集成度高、功耗低、速度快,可无限次反复编程,因此成为科研产品开发及其小型化的首选器件,其应用极为广泛。

3.1 FPGA工作原理FPGA采用了逻辑单元阵列LCA(Logic Cell Array)这样一个概念,内部包括可配置逻辑模块CLB(Configurable Logic Block)、输入输出模块IOB(Input Output Block)和内部连线(Interconnect)三个部分。

现场可编程门阵列(FPGA)是可编程器件,与传统逻辑电路和门阵列(如PAL,GAL及CPLD器件)相比,FPGA具有不同的结构。

FPGA利用小型查找表(16×1RAM)来实现组合逻辑,每个查找表连接到一个D触发器的输入端,触发器再来驱动其他逻辑电路或驱动I/O,由此构成了既可实现组合逻辑功能又可实现时序逻辑功能的基本逻辑单元模块,这些模块间利用金属连线互相连接或连接到I/O模块。

FPGA的逻辑是通过向内部静态存储单元加载编程数据来实现的,存储在存储器单元中的值决定了逻辑单元的逻辑功能以及各模块之间或模块与I/O间的联接方式,并最终决定了FPGA所能实现的功能,FPGA允许无限次的编程。

3.2 FIR滤波器特点1)采用FPGA设计ASIC电路(专用集成电路),用户不需要投片生产,就能得到合用的芯片。

2)FPGA可做其它全定制或半定制ASIC电路的中试样片。

3)FPGA内部有丰富的触发器和I/O引脚。

基于FPGA的高速FIR滤波器设计

基于FPGA的高速FIR滤波器设计摘要在数字无线电中,高速的FIR滤波器起到重要的作用。

因此,提出了一种基于FPGA的高速FIR滤波器设计方案,并采用Quartus II软件和Matlab 软件对该方案进行了开发、仿真和验证。

该方案设计的FIR滤波器具有运算速度快、实时性好和节省硬件资源的特点,能广泛应用于各种滤波领域。

关键词FPGA;FIR滤波器;Verilog HDL;Matlab在现代信号处理和电子应用技术领域,系统的设计正朝着高速、实时的方向发展。

在数字系统中,特别是在无线通信系统中,除A/D转换前的抗混叠滤波和D/A转换之后的抗镜像滤波必须采用模拟滤波器外,其它场合可以优先采用数字滤波器。

而滤波器主要作为系统的前端部分,对信号进行预处理。

滤波性能的优劣直接影响着下一级的信号处理。

因此,高性能的滤波器在系统中占据着重要位置。

FIR滤波器由于具有严格的线性相位特性以及易于实现等特点在数字信号处理中被广泛应用。

目前FIR滤波器主要有3种实现方式:第1种,采用DSP 处理器实现;第2种,采用专用信号处理芯片实现;第3种,采用可编程逻辑器件FPGA实现。

第1种实现方式使用灵活,但是由于其结构的限制不能进行并行运算,对于FIR阶数较高或者数据位宽较宽的情形,处理速度通常无法满足实时性的要求;第2种实现方式实时性好,由于其通用性差,经常无法满足特定的滤波需求;第3种实现方式,由于FPGA具有高逻辑密度、可编程以及能够可并行计算等优点,能够很好地满足通用性和实时性的要求。

因此,采用FPGA实现FIR滤波器成为高性能FIR滤波器的优选方案。

1 数字滤波器的原理分析1.1 数字滤波器的分类数字滤波器是从分析信号提取用户需要的信息,滤去不需要的信号成分或者干扰成分。

可以从时域或频域进行信号滤波设计。

时域滤波主要是根据信号和噪声之间的统计特性差异完成滤波的。

频域滤波是要提取或抑制所分析信号中某些频带的信号成分,要求信号和被滤除的信号在频域具有可分性。

基于FPGA的FIR滤波器设计

FIR滤波器设计1项目背景1.1FIR和IIR滤波器FIR(Finite Impulse Response)Filter:有限冲激响应滤波器,又称为非递归线性滤波器。

FIR滤波器,顾名思义,其脉冲响应由有限个采样值构成。

长度(抽头数)为N、阶数为N−1的FIR系统的转移函数、差分方程和单位冲激响应分别如下列三式所示。

图510IIR(Infinite Impulse Response)Filter:无限冲激响应滤波器,又称为递归线性滤波器。

FIR相对与IIR来说,具有如下的优点:可以具备线性相位特性线性相位的概念:如果滤波器的N个实值系数为对称或者反对称结构,该滤波器具有线性相位。

W(n)=±W(N−1−n)W(n)=±W(N−1−n)线性相位的特性:通过线性相位滤波器的信号的所有频率部分具有相同的延迟量。

易于设计但FIR也有自身的缺点:同样指标的滤波器,FIR需要更多的参数,即实现时消耗更多的计算单元,产生更大的延迟。

1.2FIR滤波器的原理信号通过一个FIR滤波器其实就是信号与FIR滤波器的系数进行卷积(即乘累加)的过程。

我们以一个简单信号模型为例,了解一下FIR波形器的原理。

现在有三组信号,分别是:信号1:低频信号,即在时域上变化慢的信号,其输入先后为11112222。

信号2:直流信号,其输入先后为1111111。

信号3:高频信号,即在时域上变化快的信号,其输入先后为12121212。

简单的滤波器模型低通滤波器:11信号1与低通滤波器进行卷积运算,其结果再除以2,得到如下数据:111 1.5222。

可以看到,低频信号经过低通滤波器后,各个点仍然保持了其形状,而且在1变成2时,还变平缓了。

信号2与低通滤波器进行卷积运算,其结果再除以2,得到如下数据:1111111。

可以看到,直流信号与输入的信号完成相同。

信号3与低通滤波器进行卷积运算,其结果再除以2,得到如下数据:1.5 1.5 1.5 1.5 1.5 1.51.5。

基于FPGA乘法器的FIR滤波器系统设计

基于FPGA乘法器的FIR滤波器系统设计FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,可以根据设计者的需求和要求进行编程,实现各种数字电路功能。

FIR (Finite Impulse Response)滤波器是一种常用的数字滤波器,其特点是能够对输入信号的有限长度的响应进行滤波处理。

本文将介绍基于FPGA乘法器的FIR滤波器系统设计。

首先,介绍FIR滤波器的原理。

FIR滤波器是一种线性时不变系统,其输出信号由输入信号的加权和组成。

FIR滤波器的输入经过一串系数的加权运算后,得到滤波器的输出。

FIR滤波器的传输函数为:H(z) = b0 + b1*z^(-1) + b2*z^(-2) + ... + bn*z^(-n)其中,bi是滤波器的系数,n是滤波器的阶数,z为单位延迟。

FIR 滤波器的输出信号可以表示为:y(n) = b0*x(n) + b1*x(n-1) + b2*x(n-2) + ... + bn*x(n-n)其中,x是输入信号,y是输出信号。

FIR滤波器的阶数决定了滤波器的性能,阶数越高,滤波器的频率响应越陡峭。

接下来,介绍基于FPGA乘法器的FIR滤波器系统设计。

FPGA乘法器是FPGA中的一种硬件资源,通常用于实现乘法运算。

FPGA乘法器的乘法操作可以并行地执行,可以大大提高FIR滤波器的运算速度。

在设计基于FPGA乘法器的FIR滤波器系统时,首先需要确定FIR滤波器的阶数和系数。

根据滤波器的需求,可以选择不同的阶数和系数。

然后,根据FIR滤波器的传输函数,可以将其转化为差分方程形式。

差分方程形式如下:y(n) = b0*x(n) + b1*x(n-1) + b2*x(n-2) + ... + bn*x(n-n)然后,将差分方程形式转化为数据流形式。

数据流形式中的每一步计算只涉及到少量的数据,可以并行地执行。

数据流形式如下:y(n) = b0*x(n) + b1*x(n-1) + b2*x(n-2) + ... + bn*x(0)接下来,需要将数据流形式转化为硬件电路。

基于FPGA的FIR数字滤波器的设计

基于FPGA的FIR数字滤波器的设计The Design Of FIR Digital Filter Based On FPGA系(院)名称:电子信息与电气工程系QQ 号:309810851目录摘要 (I)Abstract (II)引言 (1)第一章FIR数字滤波器设计 (2)1.1 FIR数字滤波器 (2)1.1.1数字滤波器简介 (2)1.1.2 FIR数字滤波器 (3)1.1.3 FIR数字滤波器的结构 (4)1.2 FIR数字滤波器设计方法 (6)1.2.1时窗函数法 (6)1.2.2频率采样法 (8)1.2.3等波纹最佳逼近法 (10)1.2.4三种设计方法的比较 (11)第二章基于MA TLAB的FIR数字滤波器的设计与仿真 (12)2.1 MATLAB软件 (12)2.2使用MATLAB函数进行FIR数字滤波器的设计 (12)2.2.1时窗函数设计法 (12)2.2.2频率采样设计法 (13)2.2.3等波纹最佳逼近设计法 (14)2.3使用FDATool设计FIR数字滤波器 (15)2.4使用Simulink进行仿真 (16)第三章EDA技术与分布式算法 (19)3.1 EDA技术 (19)3.1.1 EDA技术简介 (19)3.1.2 QUARTUS II软件介绍 (19)3.1.3 FPGA介绍 (20)3.2 FPGA设计方法 (22)3.3分布式算法 (23)3.3.1分布式算法基础 (23)3.3.2并行的分布式算法 (24)3.3.3串行的分布式算法 (24)第四章 15阶并行FIR数字滤波器的设计与仿真 (26)4.1顶层文件的设计 (26)4.2并行FIR各个模块的设计 (28)4.2.1输入数据预处理模块 (28)4.2.3预相加模块 (30)4.2.4查找表模块 (32)4.2.5加法器模块 (35)4.2.6移位累加器模块 (37)4.2.7输出处理模块 (38)4.3顶层综合与仿真 (38)4.4数据误差分析 (41)结论 (43)致谢 (44)参考文献 (45)基于FPGA的FIR数字滤波器的设计摘要:线性相位是FIR数字滤波器设计中的一个重要条件。

基于FPGA的高速FIR数字滤波器设计的开题报告

基于FPGA的高速FIR数字滤波器设计的开题报告一、选题意义数字信号处理是一种关键技术,广泛应用于通信、雷达、音视频处理等领域。

而数字滤波器是数字信号处理的重要组成部分之一,用于移除信号中的噪声、加强特定频率成分等。

FIR数字滤波器是一种广泛应用的数字滤波器,它具有运算速度快、实现简单等特点。

FPGA作为一种可编程逻辑器件,具有可重构性、高速度、低功耗、高可靠性等优点,在数字信号处理领域得到了广泛应用。

本课题旨在利用FPGA高性能特点,设计开发一种基于FPGA的高速FIR数字滤波器,满足在特定应用场景下对信号的快速处理需求,具有重要的理论意义和实际应用价值。

二、主要内容1. 对FIR数字滤波器的算法原理进行分析和设计,包括常见的窗函数设计、有限脉冲响应设计等,选择比较优的算法。

2. FPGA数字滤波器的硬件设计,包括数据的输入输出接口、滤波算法实现和时序控制器设计。

3. FPGA数字滤波器的仿真设计,包括基于MATLAB的算法仿真和基于ModelSim的硬件仿真等。

4. FPGA数字滤波器的实现与验证,包括采用相应工具对FPGA数字滤波器进行编译下载,将实验结果与仿真结果进行比较与分析。

5. 对设计的FPGA数字滤波器进行性能测试,包括运算速度、滤波效果等方面的测试,将其结果与已有的数字滤波器进行对比分析。

三、技术路线1. 确定常见的FIR数字滤波器设计算法,并选择较优的算法设计数字滤波器。

2. 设计FPGA数字滤波器的硬件结构,包括输入输出模块、滤波模块和时序控制模块等;并根据所选算法设计硬件逻辑。

3. 采用MATLAB进行设计算法的理论分析,从理论上验证算法的优越性。

4. 采用ModelSim进行硬件电路仿真,进行设计参数调整和错误修正,保证硬件逻辑的正确性和同步性。

5. 采用Quartus II进行编译下载,将设计的FPGA数字滤波器实现于FPGA芯片中,测试其性能。

四、研究难点1. 在设计算法时,需要充分了解各种滤波器设计算法的优缺点,并选择适合特定场景的算法。

基于FPGA的FIR滤波器设计书

基于FPGA的FIR滤波器设计书1 概述我们学生通过这次的课设深入理解和消化了基本理论、进一步提高综合应用能力并且锻炼独立解决问题的能力,我们将《数字信号处理》、《集成电路原理与应用》和《FPGA 系统设计与应用》几门课程融合在一起综合应用设计一个实用的数字FIR 滤波器。

本报告中首先讲解了这次设计的具体内容,以及所要求的数字 FIR 滤波器的技术指标。

然后,数字滤波器的一些设计方法,并具体确定我这次设计所用的设计方案。

滤波器在matlab 中的设计方法应用。

通过matlab 得到所需滤波器的具体参数h(n),然后用这些所设计的参数,通过Quartus ii 工具编程具体实现滤波器功能。

这次滤波器实现过程中,用到以下小模块:延时器,加法器,乘法器,减法器。

2 课程设计要求及注意事项1.设计过程以小组为单位,各组设一个组长,负责组织和协调本小组的讨论、任务分工等;2.设计过程必须在本组内独立完成,不得跨组参考或抄袭,避免方案出现雷同;3.设计书一律采用专用报告纸,用统一封面装订;4.课程设计原则上在3 周内做完;5.最后一周周五进行优秀设计方案评选,在各组推选代表进行方案介绍的基础上,推选出2-3 个优秀设计方案。

6.学有余力的学生在完成必做设计内容的基础上,可对内容进一步展开设计,以提高综合应用能力,锻炼独立解决问题的能力。

3 课程设计内容3.1 课程设计题目及要求3.1.1 设计题目:基于 FPGA 的 FIR 滤波器设计3.1.2 设计要求利用所学知识,采用MATLAB 和FPGA 相结合完成FIR 滤波器的设计仿真。

采用直接法或分布式算法实现FIR 数字滤波器,了解两种算法的优缺点,选择其中一种算法,得出用它来实现FIR 滤波器的硬件结构,对其实现方式进行研究,分别采用合适的方法来设计,最后利用FPGA 器件实现FIR 数字滤波器的硬件电路,并用Matlab 对实现的结果进行仿真分析。

设计指标:1)类型:FIR 低通2)系统采样频率:Fs=10KHz;3)输入序列位宽为8 位的有符号数(最高位为符号位);4)输出结果保留8 位5)窗口类型为 kaiser 窗,β=0.5; 6)滤波器长度为N=16;3.2 数字滤波器简介及结构3.2.1 简介 滤波器是用来进行频率选择或频率分辨操作的线性时不变系统的通称。

基于FPGA的FIR数字滤波器的设计及仿真设计

1 绪论本章主要论述该课题的研究意义,目前在世界上的发展情况,以及我在这篇论文中所用到的主要的设计方法与设计工作。

1.1 课题研究的意义许多工程领域都涉及到如何能在强背景的噪声信号和干扰信号中提取到真正的信号。

如:遥感和遥测系统,通信系统,雷达系统,航天系统等,这就要求有信号的滤波。

滤波器的带宽等性能,处理速度的要求随着现在对高速,宽带,实时信号处理的要求越来越高,也随之提高。

系统的稳定性和后续信号的处理受滤波器的性能好坏程度影响常大。

[1]1.2 国内外研究动态1.2.1 数字信号处理的发展动态一般可以用两类方法来实现FIR滤波器的设计。

一类通过软件来设计实现,使用常见的电脑语言如高层次的C / C + +跟MATLAB语言。

此方法用于教学或算法仿真。

但是采用软件的方法不能实现实时性。

目前可以通过以下几种方式在硬件中来实现,。

一种是使用可编程的主要数学单位是一个乘法累加器(MAC)的通用DSP 芯片编程。

实时数字信号能够实现高速的处理,是因为MAC在一台机器时钟周期就能完成乘法累加操作,同时在硬件上还辅助与不同的流水结构和哈佛架构。

然而,在应用时受到了限制,是由于硬件结构和流水结构是固定不变的。

一种是使用专用的ASIC数字信号处理芯片。

这种方法是芯片尺寸小,高性能,保密性好。

其缺点是一个单一功能的芯片,多是针对一定的功能而设计,灵活性不够。

另一种方法是使用可编程逻辑器件(FPGA / CPLD)。

FPGA所具有得可编程逻辑的灵活性突破了流水线结构和并行处理的局限性,可以很好的实现实时信号处理功能。

研发过程中它的可移植性更好,可以缩短开发周期。

[2~11]1.2.2 FIR数字滤波器的FPGA实现使用FPGA技术设计的FIR数字滤波器在目前通常采用的是乘法器结构和分布式算法结构。

乘法器结构,有乘累加结构与并行乘法器结构两种形式。

乘累加结构是最简单的一种,占用资源少,缺点是处理速度慢;并行乘法器结构比较复杂,但是如果能够加上流水结构,信号就能够实现高速的处理,但是它还是会受到处理速度和数量的限制。

基于FPGA的FIR数字滤波器的设计

毕业设计(论文)任务书基于FPGA的FIR数字滤波器的设计摘要在现代电子系统中,FIR数字滤波器以其良好的线性特性被广泛使用,属于数字信号处理的基本模块之一。

在工程实践中,往往要求对信号处理要有实时性和灵活性,而己有的一些软件和硬件实现方式则难以同时达到这两方面的要求。

随着可编程逻辑器件和FDA技术的发展,使用FPGA来实现FIR滤波器,既具有实时性,又兼顾了一定的灵活性,越来越多的电子工程师采用FPGA器件来实现FIR 滤波器。

本文对基于FPGA的FIR数字滤波器实现进行了研究。

主要工作如下:(1)以FIR数字滤波器的基本理论为依据,使用分布式算法为滤波器的硬件实现算法,并对其进行了详细的讨论。

针对分布式算法中查找表规模过大的缺点,采用多块查找表和OBC编码方式使得硬件规模极大的减小。

(2)在设计中采用了层次化、模块化的设计思想,将整个滤波器划分为多个功能模块,利用VHDL语言和原理图输入两种设计技术进行了各个功能模块的设计,最终完成了FIR数字滤波器的系统设计。

(3)最后给出了采用FLEX10K系列器件实现一个16阶的FIR低通滤波器的设计实例,用QuartusII软件进行了仿真,并对仿真结果进行了分析,证明所设计的FIR数字滤波器功能正确。

仿真结果表明,本论文设计的滤波器硬件规模较小,采样率达到了8.8MHz。

同时只要将查找表进行相应的改动,就能分别实现低通、高通、带通FIR滤波器,体现了设计的灵活性。

关键词:FIR数字滤波器;FPGA;分布式算法;OBC编码;查找表Design of the FIR Digital Filter Based on FPGAAbstractIn the modern electrical system,the FIR digital filter is used form any practical applications for its good linear phase character, and it provide an important function in digital signal processing design. In engineering practice, there is always a real-time and flexible requirement for signal processing. However, software and hardware techniques available for implementation are difficult to meet the demand for the two aspects in the same time. Along with the development of PLD device and EDA technology, more and more electrical engineers use FPGA to implement FIR filter, as it not only meet the real-time requirement, but also has some flexibility.In this paper, a method to implement the FIR filter using FPGA is proposed. The work mainly as follow:(1) According to the basic theory of FIR filters, a scheme of hardware implementation is worked out using distributed arithmetic algorithm. As the scale of the LUT in the distributed arithmetic algorithm is so large, the thesis reduces it with the use of multiple coefficient memory banks.(2) From the clew of implementing a top-down stratified, modular design, the thesis describes the hard ware design of all functional modules and the FIR system with the VHDL and schematic diagram design methods.(3) At last, a sixteen-tapped low-pass FIR filter is taken as an example, and the simulation design carried out using QuartusII. And analyzed the result, and it proved that the function of the design is correct.The result of the simulation indicates that the scale of the design is small, and the sample rate of the FIR filter can reach 8.8MHZ.Modifying the LUT can realize the low-pass, high-pass and band-pass FIR filters respectively, and incarnates the flexibility of the design.Key words:FIR digital filter;FPGA;Distributed Arithmetic;Offset-Binary Coding;LUT目录毕业设计(论文)任务书 (I)摘要............................................................................................................................... I I Abstract. (III)第1章绪论 (1)1.1 本课题的研究意义和应用背景 (1)1.2 国内外的研究现状 (1)1.3 研究思路 (3)1.4 本论文的主要内容和主要工作 (4)第2章FIR数字滤波器简介 (5)2.1 FIR数字滤波器 (5)2.1.1 数字滤波器的概述 (5)2.1.2 FIR滤波器的原理 (6)2.1.3 FIR滤波器的基本结构 (7)2.1.4 线性相位FIR数字滤波器的系统结构 (7)2.1.5 FIR数字滤波器的设计方法 (8)2.2 实现FIR数字滤波器的硬件算法——分布式算法 (10)2.2.1 分布式算法 (10)2.2.2 分布式算法的优化 (12)第3章EDA技术和可编程逻辑器件 (17)3.1 EDA技术 (18)3.2 EDA技术的主要内容 (18)3.2.1 大规模可编程器件 (18)3.2.2 硬件描述语言VHDL (19)3.3 基于EDA技术的“自顶向下”的设计方法 (21)3.4 基于EDA技术的电子电路设计流程 (21)3.5 可编程逻辑器件 (23)3.5.1 可编程逻辑器件简介 (23)3.5.2 使用FPGA器件进行开发的优点 (24)3.5.3 FPGA设计的开发流程 (25)3.6 FLEX10K系列芯片介绍 (26)3.6.1 FLEX10k的结构 (27)3.6.2 FLEX10K系列器件的特点 (28)3.7 开发工具QuartusII介绍 (28)第4章FIR滤波器的设计与仿真 (29)4.1 FIR滤波器的模块划分 (29)4.1.1 滤波器模块的划分 (29)4.1.2 方案确定 (29)4.2 FIR滤波器各模块功能的实现 (30)4.2.1 控制模块 (30)4.2.2 输入模块 (31)4.2.3 乘累加模块 (33)4.2.4 锁存模块 (35)4.2.5 顶层设计 (35)4.3 FIR数字滤波器的系统设计 (36)4.4 FIR滤波器的综合 (39)4.4.1 数字系统综合概述 (39)4.4.2 本设计的综合 (39)4.5 FIR滤波器各模块的仿真 (41)4.5.1 控制模块的仿真 (41)4.5.2 输入模块时序仿真 (42)4.5.3 乘累加模块时序仿真 (45)4.5.4 锁存模块时序仿真 (48)第5章结束语 (51)5.1 总结 (51)5.2 展望 (51)参考文献 (53)致谢 (55)附录 (I)第1章绪论1.1本课题的研究意义和应用背景几乎在所有的工程技术领域中都会涉及到信号的处理问题,其信号表现形式有电、磁、机械以及热、光、声等。

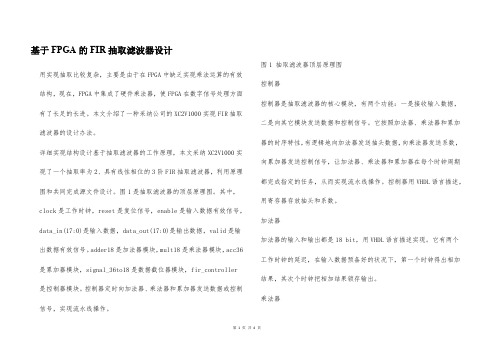

基于FPGA的FIR抽取滤波器设计

基于FPGA的FIR抽取滤波器设计用实现抽取比较复杂,主要是由于在FPGA中缺乏实现乘法运算的有效结构,现在,FPGA中集成了硬件乘法器,使FPGA在数字信号处理方面有了长足的长进。

本文介绍了一种采纳公司的XC2V1000实现FIR抽取滤波器的设计办法。

详细实现结构设计基于抽取滤波器的工作原理,本文采纳XC2V1000实现了一个抽取率为2、具有线性相位的3阶FIR抽取滤波器,利用原理图和共同完成源文件设计。

图1是抽取滤波器的顶层原理图。

其中,clock是工作时钟,reset是复位信号,enable是输入数据有效信号,data_in(17:0)是输入数据,data_out(17:0)是输出数据,valid是输出数据有效信号。

adder18是加法器模块,mult18是乘法器模块,acc36是累加器模块,signal_36to18是数据截位器模块,fir_controller是控制器模块。

控制器定时向加法器、乘法器和累加器发送数据或控制信号,实现流水线操作。

图1 抽取滤波器顶层原理图控制器控制器是抽取滤波器的核心模块,有两个功能:一是接收输入数据,二是向其它模块发送数据和控制信号。

它按照加法器、乘法器和累加器的时序特性,有逻辑地向加法器发送抽头数据,向乘法器发送系数,向累加器发送控制信号,让加法器、乘法器和累加器在每个时钟周期都完成指定的任务,从而实现流水线操作。

控制器用VHDL语言描述,用寄存器存放抽头和系数。

加法器加法器的输入和输出都是18 bit,用VHDL语言描述实现。

它有两个工作时钟的延迟,在输入数据预备好的状况下,第一个时钟得出相加结果,其次个时钟把相加结果锁存输出。

乘法器乘法器为18 bit输入,36 bit输出,用库元件MULT18X18S和36 bit 锁存器实现。

MULT18X18S是XC2V1000自带的18×18 bit硬件乘法器,单个时钟就可完成乘法运算。

36 bit锁存器工作于时钟的升高沿,用VHDL语言描述。

基于FPGA的FIR滤波器设计

数字滤波器由数字乘法器、加法器和延时单元组成的一种算法或装置。

数字滤波器的功能是对输入离散信号的数字代码进展运算处理,以到达改变信号频谱的目的。

数字滤波器是一个离散系统,该系统能对输入的离散信号进展处理,从而获取所需的有用信息。

在数字信号处理中,FIR 数字滤波器是最常用的单元之一。

它用于将输入信号x [n ]的频率特性进展特定的修改,转换成另外的输出序列y [n ]。

FIR(Finite Impulse Response)滤波器:有限长单位冲激响应滤波器,是数字信号处理系统中最根本的元件,它可以在保证任意幅频特性的同时具有严格的线性相频特性,同时其单位抽样响应是有限长的,因而滤波器是稳定的系统。

因此,FIR 滤波器在通信、图像处理、模式识别等领域都有着广泛的应用。

有限长脉冲响应〔FIR 〕滤波器的系统函数只有零点,除原点外,没有极点,因而FIR 滤波器总是稳定的。

如果他的单位脉冲响应是非因果的,总能够方便的通过适当的移位得到因果的单位脉冲响应,所以FIR 滤波器不存在稳定性和是否可实现的问题。

它的另一个突出的优点是在满足一定的对称条件时,可以实现严格的线性相位。

由于线性相位滤波器不会改变输入信号的形状,而只是在时域上使信号延时,因此线性相位特性在工程实际中具有非常重要的意义,如在数据通信、图像处理等应用领域,往往要求信号在传输和处理过程中不能有明显的相位失真,因而线性相位FIR 滤波器得到了广泛的应用。

长度为M 的因果有限冲激响应滤波器由传输函数H 〔z 〕描述:10()()M k k H z h k z --==∑它是次数为M-1的z -1的一个多项式。

在时域中上述有限冲激响应输入输出关系为:10()()()M k y n h k x n k -==-∑其中y〔n〕和x〔n〕分别是输出和输入序列。

有限冲激响应滤波器的一种直接型实现,如下图。

通常一个长度为M的有限冲激响应滤波器由M个系数描述,并且需要M个乘法器和(M-1)个双输入加法器来实现。

基于FPGA的FIR数字滤波器的设计和实现

基于FPGA的FIR数字滤波器的设计和实现摘要:本文基于FPGA平台实现了一种FIR数字滤波器,通过对滤波器的设计与实现过程的详细介绍,展示了FPGA在数字滤波器中的应用优势。

首先介绍了数字滤波器的原理及其在信号处理中的重要性,并对FPGA及其特点进行了概述。

接着,详细介绍了FIR滤波器的原理以及其在FPGA上的实现步骤,分析了滤波器设计中需要考虑到的各种因素。

最后,通过实验验证了FPGA上实现的FIR滤波器的性能,并对优化策略进行了讨论。

关键词:FPGA,FIR滤波器,数字信号处理,性能优化1. 引言数字滤波器是现代信号处理的重要组成部分,通过选择性地传递或抑制输入信号的特定频率组成部分,对信号进行处理和改善。

FIR滤波器是数字滤波器中最常用的一种类型,具有线性相位特性、稳定性较强以及易于实现等优势。

而FPGA作为一种可编程逻辑器件,具有灵活性高、可重构性强等特点,成为实现数字滤波器的理想平台。

2. FIR滤波器的原理FIR滤波器是一种线性时不变系统,其输出仅和当前输入值以及过去若干个输入值有关。

该滤波器的输出可以通过输入信号的线性加权和来计算,其中,每个输入值的加权系数通过FIR 滤波器的系数来确定。

FIR滤波器的系数决定了它对不同频率分量的响应,从而实现了信号的滤波目的。

3. FIR滤波器在FPGA上的实现步骤(1)选择合适的FPGA平台和开发工具,如Xilinx FPGA平台和Vivado开发工具。

(2)根据所要设计的滤波器的需求,确定其采样频率、截止频率和滤波器类型等参数,并进行系统级设计。

(3)根据所选参数,设计FIR滤波器的传递函数,并确定滤波器的阶数和系数。

(4)通过数学运算或者通过滤波器设计软件生成滤波器的差分方程。

(5)根据生成的差分方程,使用HDL(HardwareDescription Language)进行滤波器的编写。

(6)进行FPGA的综合、布局与布线、下载与验证,完成滤波器的硬件实现。

基于FPGA的FIR滤波器设计

1 绪论改革开放以来,国家的科学技术水平一直在稳步上升,在科研过程中,经常会用到模拟滤波器,而现如今,它的缺点渐渐暴露,比如,当参数稍有改变,那么模拟滤波器此时就需要变换电容和电感的某些参数。

但是,当数字滤波器遇到类似情况时,仅仅将系数修改就能达到目的。

众所周知,当模拟滤波器遇到类似于温漂、噪声漂移、电压漂移问题时就无计可施,但数字滤波器却可以处理。

1.1 课题背景及意义信号处理会以电、磁、机械等形式表现出来,对此许多工程技术范围都会有所涉及。

信号处理一般是以对信号进行分析、变换、综合、估值、识别等为目的,特别值得注意的是,信号处理要首先能够在较复杂的情境中,将研究所涉及的信号包括其特征找出并应用于实际工程。

现如今,数字信号处理技术越来越成熟了,而且应用的领域也在渐渐的扩大,这使得传统的模拟信号处理系统已逐步被取代。

进行滤波时,其输入输出信号均为数字信号,便可称其为数字滤波。

数字滤波能够找到并提取出所要的内容,所以,把它看成现代信号处理的重要内容已成为很多人的共识,而它的应用领域也在逐步扩大,比如自动控制、数字通信、语音处理等都用到此项技术。

在实际的工程中,数字滤波器没有漂移,在研究过程中,频率响应特性是很重要的,而数字滤波器的频率响应特性使其无限度的接近于理想特性。

数字滤波器的精度非常高,能够去处理一些低频信号,同时,数字滤波器特别容易集成[1]。

人们所熟知的DSP处理器和FPGA技术发展的越来越迅速,这也使得数字滤波器向更高的层次在发展着。

当然,使用FPGA的方法来设计FIR滤波器是一个比较新颖的方法,还正处于发展阶段,所以技术仍旧稍有不成熟。

相比较而言,基于DSP 的FPGA的方法就稍显成熟,这一方法需要一定的基础,在许多方面,它都表现了其独有的优势。

虽然如此,人们还是更多的把研究的眼光放到了用FPGA的方法去设计FIR滤波器,因为它有着广泛的用途以及巨大的实用价值。

1.2 国内外研究现状在如今的科研中,越来越多的使用到数字信号处理器。

基于FPGA的FIR滤波器的设计(毕业设计) 可用

目录摘要 (2)英文摘要 (3)1 引言 (3)1.1国内外研究现状 (4)1.2本论文的研究内容及主要工作 (6)2 FIR数字滤波器设计 (6)2.1数字滤波器基础 (6)2.1.1 数字滤波器简介 (6)2.1.2 FIR数字滤波器的结构 (7)2.2 FIR数字滤波器设计方法 (8)2.2.1 窗函数法 (8)2.2.2 频率采样法 (9)2.2.3 等波纹最佳逼近法 (11)2.2.4 三种设计方法的比较......................... 错误!未定义书签。

3 FPGA 设计优点以及分布式算法 (12)3.1 使用FPGA器件进行开发的优点 (13)3.2分布式算法 (14)3.2.1 分布式算法基础 (14)3.2.2 有符号的DA系统 (15)4 基于FPGA的FIR滤波器设计 (15)4.1基于M ATLAB的FIR数字低通滤波器抽头系数的提取 (16)4.1.1 滤波器的设计指标 (16)4.1.2 滤波器的具体设计方法 (16)4.1.3 参数提取与量化 (17)4.2FIR滤波器的FPGA实现 (19)4.2.1 模块划分 (19)4.2.2 FIR滤波器各模块的实现 (20)4.2.3 FIR滤波器的顶层设计 (30)4.3FIR滤波器的系统仿真验证 (32)4.4系统硬件 (36)4.4.1 系统框图 (36)4.4.2 部分芯片简介 (36)4.4.3 AD、DA电路原理图 (39)4.5测试波形及现场照片 (39)4.6数据误差分析 (40)结论 (41)参考文献 (41)附件 (42)基于FPGA的FIR滤波器的设计摘要:本文设计了一个基于FPGA的16阶FIR低通滤波器,使用分布式算法作为滤波器的硬件实现算法,并对其进行了详细的讨论。

针对分布式算法中LUT规模过大的缺点,采用多块查找表的方式减小硬件规模。

在设计中采用了自顶向下的层次化、模块化的设计思想,将整个滤波器划分为多个模块,利用VHDL语言的描述方法进行了各个功能模块的设计,最终完成了FIR数字滤波器的系统设计。

基于FPGA的FIR滤波器设计

一、概述在通信与信息技术领域,数字信号处理显得越来越重要了,数字滤波器在数字信号处理中起到重要作用并能够获得广泛应用。

数字滤波器根据频域特性可以分为低通、高通、带通和带阻四种基本类型,根据时域特性可以分为无限脉冲响应IIR(Infinte Impulse Response)和有限脉冲响应FIR(Finite Impulse Response)。

FIR滤波器具有良好的线性相位特性,因此在数据通信、图像处理方面有广泛的应用。

FPGA(Field Programmable Gate Array),即现场可编程门阵列,由于具有用户可编程性,能够实现用户规定的各种用途,因此又被称为可编程专用集成电路,在电子系统的设计中得到广泛的应用。

利用FPGA实现FIR数字滤波器的设计,是本次课程设计需要解决的问题,利用学过的知识实现FIR数字滤波器是本次课程设计的主要内容。

二、方案论证1.FIR数字滤波器是一种线性时不变系统(LTI),如果FIR数字滤波器的单位脉冲响应h(n)的长度为N,其传递函数和差分方程分别为:H(z) = ∑=-1-0 n1 ) (Nznhy(n) = x(n)*h(n) =∑-=-1)()(Nmmnxmh其中,x(n)和y(n)分别为输入和输出序列。

如果FIR数字滤波器的单位脉冲响应h(n)是实数序列,而且满足偶对称或者奇对称条件,即h(n) = h(N-1-n)或者h(n) = -h(N-1-n)则滤波器具有严格的线性相位特点。

正是因为这种特点,在滤波器的设计过程中,可使乘法器的数量减半。

对于n阶滤波器,当n是偶数时,乘法器的个数为n/2个,当n 为奇数时,乘法器的个数为(n+1)/2个。

由传递函数和差分方程可以直接画出FIR滤波器的直接型结构如图1所示。

1-1-1-1-y(n)图1 FIR滤波器的直接型结构2.FIR滤波器的实现方法有多种,通常有串行算法、半并行算法和并行算法,在串行算法中,常见的有单乘法器MAC FIR滤波器和对称MAC FIR滤波器。

基于FPGA的FIR滤波器优化设计

基于FPGA的FIR滤波器优化设计FPGA技术是一种灵活和可重配置的硬件设计技术,具有高度的并行性和可定制性。

其中,FIR(Finite Impulse Response)滤波器是一种常见的数字滤波器,可以用于信号处理和数据通信等领域。

在本文中,我们将讨论基于FPGA的FIR滤波器的优化设计。

首先,我们将介绍FIR滤波器的基本原理。

FIR滤波器是一种非递归滤波器,其输出只与当前输入和有限数量的以前输入相关。

其主要特点是具有线性相位响应和稳定性。

FIR滤波器通过卷积运算来实现滤波的功能,其中滤波器的系数是其关键部分。

接下来,我们将讨论如何将FIR滤波器设计为基于FPGA的硬件实现。

在FPGA设计中,我们可以使用硬件描述语言(如VHDL或Verilog)来描述FIR滤波器的功能和行为。

然后,我们可以使用FPGA设计工具(如Xilinx Vivado)将这些硬件描述转换为可在FPGA芯片上实现的逻辑电路。

在进行优化设计时,可以采用以下几种方法:1.并行计算:由于FPGA具有高度的并行性,我们可以利用并行计算来加速FIR滤波器的运算。

可以将输入信号分成多个并行通道,并在每个通道上独立地进行滤波计算。

2.流水线设计:流水线设计可以进一步提高FIR滤波器的运算效率。

可以将滤波器的计算分成多个阶段,并使每个阶段的计算互相重叠。

这样可以实现更高的吞吐量。

3.系数优化:FIR滤波器的计算涉及到滤波器的系数乘法和累加操作。

可以通过使用定点算法和优化系数位宽等方法来减少计算的复杂度。

此外,还可以使用现成的IP核来实现FIR滤波器。

例如,Xilinx Vivado中提供了用于FIR滤波器的IP核。

这些IP核具有预先优化的代码和配置选项,可以帮助我们更方便地实现FIFO滤波器。

另一方面,我们还可以采用硬件/软件协同设计的方法来优化FIR滤波器的设计。

在这种方法中,可以将一部分滤波器的计算任务转移到CPU上进行处理,以减轻FPGA上的计算负载。

基于FPGA的FIR滤波器设计

基于FPGA的FIR滤波器设计一、设计目的为了帮助学生深入理解和消化基本理论、进一步提高综合应用能力并且锻炼独立解决问题的能力,我们将《数字信号处理》、《集成电路原理与应用》和《《FPGA 系统设计与应用》几门课程融合在一起开设的FPGA综合实验课程设计。

本次完成的是利用FPGA来完成FIR滤波器的设计、程序设计和实验调试任务。

二、设计要求(1)基本要求利用所学知识,采用VHDL语言完成FIR滤波器的设计仿真。

要求用VHDL 编程设计底层文件,顶层文件可任意(可用原理图方式或文本方式);完成仿真文件(包括MATLAB和QUARTUSII两种仿真)并对其结果比较。

具体设计指标如下:(1)采样频率SF=80KHz;(2)截止频率KHzFC10=;(3)输入序列为10位(最高位为符号位);(4)窗口类型为kaiser窗,β=0.5 ;(5)滤波器长度为16 ;(6)输出结果保留10位。

(2)提高部分根据所学知识,设计出一个具有频率控制功能DDS,要求输出频率分别为10KHz和100KHz,将输出的两路数字信号进行叠加,并通过所设计的FIR滤波器进行滤波,将滤波输出的数字信号通过D/A转换电路输出波形,并用示波器观察输出波形,并完成测试结果分析。

结构框图如图1-1所示。

图2-1 整体结构框图三、设计原理3.1 FIR 滤波器由线性系统理论可知,在某种适度条件下,输入到线性系统的一个冲击完全可以表征系统。

当我们处理有限的离散数据时,线形系统的响应(包括对冲击的响应)也是有限的。

若线性系统仅是一个空间滤波器,则通过简单地观察它对冲击的响应,我们就可以完全确定该滤波器。

通过这种方式确定的滤波器称为有限冲击响应(FIR)滤波器。

3.2 线性FIR 滤波器原理FIR 滤波器响应(简称FIR )系统的单位脉冲响应()h n 为有限长序列,系统函数()H z 在有限z 平面上不存在极点,其运算结构中不存在反馈支路,即没有环路。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

长春理工大学毕业设计摘要在现代电子系统中,FIR数字滤波器以其良好的线性特性被广泛使用, 随着可编程逻辑器件和EDA技术的发展,使用FPGA来实现FIR滤波器,既具有实时性,又兼顾了一定的灵活性,越来越多的电子工程师采用FPGA器件来实现FIR 滤波器。

本论文对基于FPGA的FIR数字滤波器实现进行了研究,以FIR数字滤波器的基本理论为依据,并且采用查找表以及线性FIR波器的对称性特点使得硬件规模极大的减小。

为了验证仿真结果的正确性,文中应用了MATLAB和VHDL联合仿真方法对设计的电路进行仿真测试,结果达到设计指标。

并用MATLAB对仿真结果进行了分析,证明了所设计的FIR数字滤波器功能正确。

关键词: 有限脉冲响应现场可编程门阵列查找表窗函数仿真ABSTRACTIn the modern electrical system, the FIR digital filter is used for many practical applications for its good linear phase character, Along with the development of PLD device and EDA technology, more and more electrical engineers use FPGA to implement FlR filter, as it not only meet the real-time requirement, but also has some flexibility.In this paper, a method to implement the FIR filter using FPGA is proposed. According to the basic theory of FIR filters, the thesis reduces it with the use of multiple coefficient memory banks and the symmetry characteristic of linear FIR filter. In order to make the verification more available, the complex simulation with Matlab and VHDL is used to testify the design whether fulfills the requirement. And also the result of the simulation is analyzed with the use of MATLAB, and it proved that the function of the design is correct.KEYWORDS: FIR FPGA Windows Function Simulation目录第一章绪论 (1)1.1背景和选题依据 (1)1.2国内外研究现状和发展动态 (2)1.3论文研究的目的和主要内容 (2)第二章FIR滤波器的结构及设计 (4)2.1 FIR数字滤波器基础 (4)2.2 FIR数字滤波器的基本结构 (5)2.3 FIR数字滤波器的设计 (7)第三章FPGA在设计中的具体应用 (10)3.1硬件电路的设计方式 (10)3.2 FPGA简介 (11)第四章基于FPGA 设计FIR滤波器 (17)4.1指标的确定 (17)4.2 Matlab在设计中的应用 (17)4.3 16阶FIR滤波器的结构 (20)4.4 采用查找表方式的FIR滤波器 (23)第五章总结与展望 (30)5.1总结 (30)5.2发展 (30)参考文献 (31)致谢 (32)第一章绪论1.1背景和选题依据本课题的研究背景是针对数字信号处理实验室的需要而开展的工作。

由于信号在复杂的环境中经常受到大量的干扰及噪声的影响,因而设计高性能的FIR滤波器来滤掉这些干扰及噪声起着非常关键的作用。

在数字处理中,滤波占有重要的地位。

数字滤波在语音和图像处理、HDTV(High-Definition Television)、模式识别、谱分析等应用中经常用到。

与模拟滤波相比,数字滤波具有很突出的优点。

例如它可以满足滤波器对幅度和相位特性的严格要求,可以避免模拟滤波所无法克服的电压漂移、温度漂移和噪声等问题。

根据数字滤波器冲激响应函数的时域特性,可将数字滤波器分为无限长冲激响应(IIR)滤波器和有限长冲激响应(FIR)滤波器两种。

由于FIR系统只有零点、系统稳定,便于实现FFT算法、运算速度快、线性相位的特性和设计更为灵活等突出优点而在工程实际中获得广泛应用[1]。

FPGA (Field Program Gate Array)是可编程逻辑器件中一种比较复杂的形式,它正处于革命性数字信号处理的前沿。

全新的FPGA系列正在越来越多的替代ASIC(Application-Specific Integrated Circuit)和PDSP(Programmable Digital signal processors)用作前端数字信号处理的运算。

FPGA具有许多与ASIC相同的特点。

例如:在规模、重量和功耗等方面都有所降低。

而且吞吐量更高、能更好的防止未授权复制、元器件和开发成本的进一步降低,开发时间也大大缩短。

还具有在线路中可重复编程的特性。

它允许电路设计者利用基于计算机的开发平台,经过设计输入、仿真、测试和校验,直至达到预期的效果,从而可以产生更为经济的设计。

更吸引人的是,采用FPGA器件可以将原来的电路板级产品集成为芯片级产品。

正如我们现在所看到的,随着FPGA在数字信号处理中的大规模应用,正在日渐深入地影响我们的生产和生活,也必将在这领域引起深刻的变革。

在本课题的研究中,采用超大规模集成电路硬件描述语言(VHDL)对设计进行描述。

在程序设计的过程中,将不同功能代码分别存放,以利于设计的后期更新和维护。

可以使用Leonardo Spectrum或FPGA Express对设计进行综合处理,将产生的.edf文件放在Max plus II平台上进行仿真,如果仿真通过并符合要求,就可以将代码下载到具体的芯片中,完成FIR滤波器的设计[2]。

1.2国内外研究现状和发展动态在现代信号处理和电子应用技术领域,滤波器作为一种必不可少的组成部分处在了一个十分重要的位置,并日益显示出其巨大的应用价值。

尽管滤波技术的发展到现在只有七十多年的历史,但它的发生与发展已经历了诸多变化,作为一种信号处理的技术已相当完善,并不断发挥着其重要的作用。

长期以来,人们不断地探索滤波器的设计与实现方法,努力地追求着简化设计、减少体积、改善性能、提高灵活性和可靠性、便于制作等问题。

随着微电子学迅速发展,以单个芯片进行FIR滤波器的设计正在发展和应用中。

如今FIR滤波器的硬件设计有多种实现方法。

第一种是采用单片机来实现,但单片机的处理速度比较慢。

第二种是采用专用的DSP芯片,但是DSP的串行指令执行发式,使其工作速度和效率大打折扣,因此当滤波器的系数增加或字长增长时,计算时间会成倍增加,从而降低了最大有效数据采样率。

而且在一些高速的应用中,系统性能不断增长,而DSP性能的提高却落后于需求的增长。

第三种是采用市场上通用的FIR滤波器集成电路,但由于它的通用性,很难满足设计者独特的要求。

第四种是采用可编程逻辑器件(PLD)的方法来实现。

可编程逻辑器件在电子技术领域中的应用,为数字硬件电路系统的设计带来了极大的灵活性。

由于可编程逻辑器件可以通过软件编程而对其硬件结构和工作方式进行重构,使得硬件的设计可以如同软件设计那样方便快捷。

这一切极大地改变了传统的数字硬件电路系统设计方法、设计过程、乃至设计观念。

纵观可编程逻辑器件的发展史,它在结构原理、集成规模、下载方式、逻辑设计手段等方面的每一次进步都为现代电子设计技术的革命与发展提供了不可或缺的强大动力。

自从1989年美国Xilinx公司率先发明FPGA(现场可编程门阵列)的概念以来,FPGA技术以其现场设计、现场修改、现场验证、现场实现的可达数万门级的数字系统单片化的应用优势,随着亚微米CMOS集成电路制作技术的成熟和发展,器件集成度不断增大,器件价格不断下降的趋势,逐渐受到各国电子系统应用领城的设计工程师的广泛关注和欢迎。

时至今口,FPGA技术不再是ASIC 技术领域的一个点缀和补充,而跃为电子应用(包括通讯技术、计算机应用、自动控制、仪器仪表、ASIC设计)等诸多领域受欢迎的实用技术,成为数字系统科研实验、样机试制、小批量产品即时实现的最佳途径。

1.3论文研究的目的和主要内容本文研究的主要目的是为数字信号处理实验室设计出性能指标优良的滤波器,使其在复杂的环境中快速过滤掉无用信号及噪声。

并根据此目的进行进一步的研究及拓展。

为了确定使用的方法在设计FIR滤波器上是有效并且是高效的,因此在本文中对比了两种不同的FIR滤波器的设计方法,通过对比得知,采用查找表的FIR滤波器无论在速度上和所占用的资源上均优于普通的设计方式,因此可以确定采用查找表来设计FIR滤波器占有优势。

本文主要内容分为五部分:第一章简要介绍背景、选题以及文章的概要;第二章对FIR滤波器的原理,尤其是线性相位的FIR滤波器进行了详细的说明;第三章对FPGA进行了介绍,并具体说明在设计中用到的数字及部件在设计中是如何实现的;第四章进行具体的设计论述,详细说明了每一步是如何进行并给出了对比结果;第五章对全文进行了总结并指出本设计的发展方向。

第二章 FIR 滤波器的结构及设计数字滤波器通常都是应用于修正或改变时域或频域中信号的属性。

最为普通的数字滤波器就是线性时间不变量(linear time- invariant ,LTI)滤波器。

LTI 与其输入信号之间相互作用,经过一个称为线性卷积的过程。

表示为y=f *x,其中f 是滤波器的脉冲响应,x 是输入信号,而y 是卷积输出。

线性卷积过程的正式定义如下:[][][][][][][]k f k n x k n f n x n f n x n y kk ∑∑-=-=*=LTI 数字滤波器通常分成有限脉冲响应(finite impulse response ,也就是FIR)和无限脉冲响应(infinite impulse response ,也就是IIR)[3]两大类。

顾名思义,FIR 滤波器由有限个采样值组成,将上述卷积的数量降低到在每个采用时刻为有限个。

而IIR 滤波器需要执行无限数量次卷积。