DMA、UART、AD、IIS寄存器

dma编程步骤

dma编程步骤DMA编程步骤DMA(Direct Memory Access)是一种数据传输方式,可以在不占用CPU的情况下进行高速数据传输。

在嵌入式系统中,DMA被广泛应用于外设和存储器之间的数据传输。

本文将介绍DMA编程的步骤。

一、确定DMA控制器和外设在进行DMA编程之前,首先要确定使用的DMA控制器和外设。

常见的DMA控制器有ARM Cortex-M系列芯片中的DMAC、STM32系列芯片中的DMA等。

而外设则包括UART、SPI、I2C等。

二、配置外设在进行DMA编程之前,需要先对外设进行配置。

以UART为例,需要配置波特率、数据位数、停止位等参数,并使能接收或发送中断。

三、初始化DMA控制器初始化DMA控制器包括以下几个步骤:1. 选择传输方向:选择是从内存到外设还是从外设到内存。

2. 配置传输模式:选择是单次传输还是循环传输。

3. 配置数据宽度:根据实际情况选择8位或16位或32位数据宽度。

4. 配置地址增量模式:根据实际情况选择是否需要自动递增地址。

5. 配置传输数量:设置需要传输的字节数量。

6. 配置中断:根据实际情况选择是否需要传输完成中断。

四、配置DMA通道DMA控制器可以有多个通道,每个通道可以独立配置。

在进行DMA 编程之前,需要先选择一个可用的通道,并进行如下配置:1. 配置DMA源地址:设置数据传输的源地址,可以是内存地址或外设寄存器地址。

2. 配置DMA目的地址:设置数据传输的目的地址,可以是内存地址或外设寄存器地址。

3. 配置传输数量:设置需要传输的字节数量。

4. 配置优先级:根据实际情况选择优先级高低。

5. 配置传输完成后的处理方式:选择停止传输或重新启动传输等方式。

五、启动DMA传输在进行完以上配置之后,即可启动DMA传输。

启动DMA传输需要调用相应的API函数,并将外设和通道作为参数传入。

例如,在STM32系列芯片中,可以调用HAL_DMA_Start_IT()函数启动DMA传输,并在中断服务函数中处理数据。

DMA简介

10DMA控制器(DMA)小容量产品是指闪存存储器容量在16K至32K字节之间的STM32F101xx、STM32F102xx和STM32F103xx微控制器。

中容量产品是指闪存存储器容量在64K至128K字节之间的STM32F101xx、STM32F102xx和STM32F103xx微控制器。

大容量产品是指闪存存储器容量在256K至512K字节之间的STM32F101xx和STM32F103xx 微控制器。

互联型产品是指STM32F105xx和STM32F107xx微控制器。

除非特别说明,本章描述的模块适用于整个STM32F10xxx微控制器系列。

10.1DMA简介直接存储器存取(DMA)用来提供在外设和存储器之间或者存储器和存储器之间的高速数据传输。

无须CPU干预,数据可以通过DMA快速地移动,这就节省了CPU的资源来做其他操作。

两个DMA控制器有12个通道(DMA1有7个通道,DMA2有5个通道),每个通道专门用来管理来自于一个或多个外设对存储器访问的请求。

还有一个仲裁器来协调各个DMA请求的优先权。

10.2DMA主要特性●12个独立的可配置的通道(请求):DMA1有7个通道,DMA2有5个通道●每个通道都直接连接专用的硬件DMA请求,每个通道都同样支持软件触发。

这些功能通过软件来配置。

●在同一个DMA模块上,多个请求间的优先权可以通过软件编程设置(共有四级:很高、高、中等和低),优先权设置相等时由硬件决定(请求0优先于请求1,依此类推)。

●独立数据源和目标数据区的传输宽度(字节、半字、全字),模拟打包和拆包的过程。

源和目标地址必须按数据传输宽度对齐。

●支持循环的缓冲器管理●每个通道都有3个事件标志(DMA半传输、DMA传输完成和DMA传输出错),这3个事件标志逻辑或成为一个单独的中断请求。

●存储器和存储器间的传输●外设和存储器、存储器和外设之间的传输●闪存、SRAM、外设的SRAM、APB1、APB2和AHB外设均可作为访问的源和目标。

UART寄存器介绍

UART寄存器介绍UART(Universal Asynchronous Receiver/Transmitter)是一种串行通信协议,常用于各种微控制器和外围设备之间的通信。

UART寄存器是用来配置和控制UART模块的寄存器,包括数据传输、波特率、中断、状态等方面。

本文将从这几个方面详细介绍UART寄存器。

1.数据传输寄存器:数据传输寄存器用来存储和传输数据。

在发送数据时,将要发送的数据写入数据寄存器,发送完毕后,数据寄存器将被清空准备接收下一个数据。

在接收数据时,接收到的数据会存储在数据寄存器中,供读取或进一步处理。

2.波特率寄存器:波特率寄存器用来设置UART通信的波特率,它决定了数据传输的速率。

波特率寄存器通常是一个16位寄存器,低8位用来表示分频器的分频值,高8位用来表示分频器的倍频值。

通过设置不同的分频值和倍频值,可以实现不同的波特率。

具体的计算公式如下:波特率=时钟频率/(分频值*倍频值)3.中断寄存器:中断寄存器用来配置和控制UART模块的中断。

通过设置中断使能位和中断标志位,可以实现在特定事件发生时触发相应的中断处理程序。

常见的中断包括接收到数据中断、发送数据完成中断、数据溢出中断等。

4.状态寄存器:状态寄存器用来提供UART模块的状态信息。

常见的状态包括发送缓冲区为空、接收缓冲区不为空、接收缓冲区溢出、发送完成等。

通过读取状态寄存器的值,可以了解UART模块的当前状态,并进行相应的处理。

5.控制寄存器:控制寄存器用来配置和控制UART模块的行为。

它可以设置UART模块的工作方式、数据位数、停止位数、校验方式等。

通过写入控制寄存器的不同值,可以改变UART的工作模式,并对数据进行校验等处理。

6.波特率发生器寄存器:波特率发生器寄存器用来配置UART模块的波特率发生器。

波特率发生器根据设置的时钟频率和波特率,产生传输数据时所需要的时钟信号。

通过修改波特率发生器寄存器的值,可以调整UART模块的波特率。

uart寄存器

3>具体寄存器的配置(1) U0FCRA作用:控制UART0 Rx和Tx的操作。

B长度:8位寄存器。

C:每一位的含义:l 第0位:表示FIFO使能置1:表示使能对UART0 Rx和Tx 的FIFO以及U0FCR[7:1]的访问。

置0:表示不能使用Rx和Tx的FIFO以及步能对U0FCR[7:1]的访问。

注:该位的任何变化都将使UART0 FIFO清空。

l 第1位:表示Rx FIFO的复位。

置1:会清零UART0 RxFIFO中的所有字节并复位指针逻辑。

该位自动清零。

l 第2位:表示Tx FIFO的复位。

置1:会清零UART0 TxFIFO中的所有字节并复位指针逻辑。

改位自动清零。

l 第[5:3]位:保留位,用户不能对其进行操作。

从保留位读出的值未被定义。

l 第[7:6]位:表示Rx 触发选择00:触发点为0(默认为1字节)01:触发点为1(默认为4字节)10:触发点为2(默认为8字节)11: 触发点为3(默认为14字节)注:这两个位决定在激活中断之前,接收UART0 FIFO必须写入个字符。

(2) U0IER(中断使能寄存器)A 作用:U0IER用于使能4个UART0中断源B 长度:8位寄存器C每一位的含义:l 第0位:表示RBR中断使能置1:使能RDA中断置0:禁止RDA中断注:U0IEER 第零位使能UART0接收数据可用中断。

它还控制(CTI)字符接收超时中断。

l 第1位:表示THRE中断使能置1:使能THRE中断置0:禁止THRE中断l 第2位:表示Rx线状态中断使能置1:使能Rx线状态中断置0:禁止RX线状态中断注:U0IER第二位使能UART0 Rx线状态中断。

该中断的状态可从U0LSR[4:1]读出l 第[7:3]位:是保留位注:用户不能向其写入1.。

BLE协议栈——UARTDMA工作方式

BLE协议栈——UARTDMA工作方式BLE(蓝牙低功耗)协议栈是一种用于无线通信的协议,并且非常利于低能耗的设备之间的通信,如物联网设备。

BLE协议栈包含了多个层次的协议,其中包括物理层、链路层和主机控制器接口层等。

在BLE协议栈中,UARTDMA(串口直接内存访问)是一种常见的工作方式,下面我们将详细介绍UARTDMA的工作原理和流程。

UARTDMA是一种使用DMA技术进行数据传输的串口通信方式。

DMA(直接内存访问)是一种用于高速数据传输的技术,其通过在外设和内存之间建立直接的数据通路,减少了处理器的介入,提高了数据传输的效率。

在UARTDMA工作方式下,首先需要初始化DMA控制器和串口控制器。

DMA控制器负责管理数据在内存和外设之间的传输,而串口控制器负责串口的配置和数据的发送和接收。

在数据发送过程中,首先将要发送的数据写入到内存缓冲区中。

然后,通过配置DMA控制器的相关寄存器,将内存缓冲区的地址设置为源地址,将串口数据寄存器的地址设置为目的地址,并设置数据长度。

当DMA控制器检测到数据发送请求时,会自动将数据从内存缓冲区传输到串口数据寄存器中,并通过串口发送出去。

在数据接收过程中,首先配置DMA控制器,将串口数据寄存器的地址设置为源地址,将内存缓冲区的地址设置为目的地址,并设置数据长度。

当DMA控制器检测到数据接收请求时,会自动将数据从串口数据寄存器中传输到内存缓冲区中。

UARTDMA工作方式的主要优点是降低了CPU的负载,提高了数据传输的效率。

由于DMA可以在不影响CPU的情况下进行数据传输,所以CPU可以将更多的时间用于其他任务处理,提高了系统的性能。

然而,UARTDMA工作方式也存在一些局限性。

首先,由于DMA的使用需要占用一部分系统资源,所以在资源有限的嵌入式系统中可能无法使用。

其次,在数据传输过程中,如果DMA控制器和串口控制器之间没有很好的同步机制,可能会导致数据传输错误或数据丢失的问题。

stm32 uart dma 接收原理 -回复

stm32 uart dma 接收原理-回复STM32 UART DMA 接收原理一、引言串行通信是一种常用的数据传输方式,UART(通用异步收发传输器)是其中一种常见的串行通信接口。

对于STM32微控制器,它支持使用DMA (直接内存访问)来处理UART的接收和发送操作。

本文将重点讨论STM32 UART DMA 接收的原理,详细介绍DMA的工作原理以及如何在STM32中配置和使用DMA来实现UART的接收功能。

二、DMA 简介DMA是一种由硬件支持的直接内存访问技术,它可以在不依赖CPU的情况下,实现外设和内存之间的数据传输。

在传统的方式中,CPU需要花费大量的时间和资源来处理数据的传输,而DMA可以减轻CPU的负担,提高数据传输的效率。

对于STM32微控制器,它提供了多个DMA通道,可以与不同的外设进行数据传输。

三、UART 接收过程UART的接收过程通常分为两步:接收数据和处理数据。

1. 接收数据:UART接收数据的原理是通过接收数据寄存器(Receive Data Register)将接收到的数据保存在寄存器中,然后CPU读取该寄存器以获得接收到的数据。

在传统的方式中,CPU需要不断地查询是否有接收到的数据,并进行读取操作。

但这种方式会浪费CPU的时间和资源。

2. 处理数据:接收到的数据通常需要进行处理,例如判断数据的格式是否正确、提取有效的数据等。

这些处理过程需要CPU的参与,因此如果CPU在不断查询接收数据的过程中被占用,那么处理数据的效率将会大大降低。

四、DMA 接收原理DMA 可以在不依赖CPU的情况下自动执行数据传输操作,因此可以大大提高数据传输的效率。

对于UART的接收过程,STM32提供了DMA 来进行数据的接收,并提供了相应的寄存器和寄存器位来进行配置。

1. 配置UART DMA 模式:首先需要配置UART和DMA的工作模式。

通过UART的控制寄存器和DMA的配置寄存器,可以设置相关的模式。

USART模块寄存器使用说明

UART是通用异步串行接口的简称。

串行通信接口是用来与单片机外界系统进行通信桥梁,比如可以吧单片机ADC转换的数据通过串口发送给PC机(上位机),经上位机处理之后在发回给单片,达到通信的目的。

TI公司的MSP430系列单片机均具有UART功能,其中大部分还和SPI,I2C功能复用,通过相关寄存器的配置,可以很轻松地就实现了UART,SPI,I2C的通信功能。

在此以MSP430x149为例介绍UART功能及其实现过程。

1.异步通信的结构:2.UART数据格式(数据协议):异步通信再不发送数据的时候,通信线路上总是呈现高电平状态,称为空闲状态。

当有数据发送是,信号线变成低电平,并持续一位的时间用于表示发送字符的开始,该为称为起始位。

起始位之后在信号线上依次出现发送的数据。

起始位,数据位由高到低7/8位,地址位 0/1位,奇偶校验位奇偶或无,停止位1/2位。

数据位位数、地址位、奇偶校验位、停止位均可由单片机内部寄存器控制;这款单片机都有两个USART模块,有两套独立的寄存器组;以下寄存器命中出现x代表0或是1,0代表对应0模块的寄存器,1代表对应1模块的寄存器;其中,与串口模式设置相关的控制位都位于UxCTL 寄存器,与接收相关的控制位都位于UxRCTL寄存器,与发送相关的控制位都位于UxTCTL寄存器;波特率设置用UxBR0、UxBR1、UxMCTL三个寄存器;接收与发送有独立的缓存UxRXBUF、UxTXBUF,并具有独立的移位寄存器和独立的中断;中断允许控制位位于IE1/2寄存器,中断标志位位于IFG1/2寄存器。

3.波特率设置:430的波特率设置用三个寄存器实现:UxBR0:波特率发生器分频系数低8位。

UxBR1:波特率发生器分频系数高8位。

UxMCTL:波特率发生器分频系数的小数部分实现。

设置波特率时,首先要选择合适的时钟源:USART模块可以设置的时钟源有UCLK引脚、ACLK、SMCLK;对于较低的波特率(9600以下),可选ACLK作为时钟源,这样,在LPM3(低功耗3)模式下,串口仍能正常发送接收数据;另外,由于串口接收过程有一个三取二判决逻辑,这至少需要三个时钟周期,因此分频系数必须大于3;波特率高于9600时,将不能使用ACLK作为时钟源,要调为频率较高的SMCLK作为时钟源;另外还可以外部输入UCLK时钟。

微机接口名词解释

《微机原理与接口技术》名词解释CPU:微处理器,包括运算器、控制器和寄存器组。

EU:执行部件,包括8个16位寄存器、算术逻辑部件ALU、标志寄存位FR、暂存器和EU 控制系统。

它负责全部指令执行,同时向BIU输出数据,并对寄存器和标志寄存器进行管理。

BIU:总线接口部件,包括4段寄存器、IP、内部通信寄存器、指令队列、总线控制逻辑和地址加法器组成。

它负责执行所有外部总线周期,提供系统总线控制信号,形成实际地址。

IP:指令指针寄存器,用来控制CPU的指令执行顺序。

SP:堆栈指针寄存器,与堆栈段寄存器一起确定堆栈在内存中的位置。

CS:代码段寄存器,规定并控制程序区。

DS:数据段寄存器,控制数据区。

SS:堆栈段寄存器,控制堆栈区。

时钟周期:加在CPU芯片引线CLK上时钟信号的周期。

总线周期:CPU通过其系统总线时存储器/接口进行一次访问所需时间。

指令周期:CPU完整地执行一条指令所用的时间。

段寄存器:16位,包括CS、DS、SS和ES,其内容+有效地址偏移量可确定内存的物理地址。

字节:相邻的8位二进制数称为1个字节。

物理地址:1MB存储区域中的某一单元的实际地址。

物理地址=段基地址*16+偏移地址逻辑地址:编制程序时采用,由段基地址和偏移量组成。

BCD码:二进制编码的十进制数,即一位十进制数用4位二进制码表示。

ASCII码:美国标准信息交换码。

堆栈:内存中临时保存的返回地址和中间结果。

汇编程序:用汇编语言编写的,使微机系统实现一系列操作的源程序。

指令性语句:为可执行语句,在汇编语言中要产生对应的目标代码,CPU根据这些代码才能执行相应的操作。

指示性语句:即伪指令,用来指示汇编程序应该如何处理汇编语言程序,是不可执行语句,汇编时不产生目标代码。

OFFSET:分析运算符之一,返回变量或标号的偏移地址。

ASSUME:段定义语句之一,告诉汇编程序关于段寄存器与逻辑段之间的对应关系。

SEGMENT:与ENDS一起构成段定义语句,用于定义一个逻辑段,给逻辑段赋予一个段名,并以后面的任选项规定该逻辑段的其他特性。

串行通信编程相关的寄存器

串行通信编程相关的寄存器1. UART寄存器(通用异步收发器寄存器),UART是一种常用的串行通信协议,它使用一个寄存器来控制和配置串行通信的参数。

UART寄存器通常包括数据寄存器、状态寄存器、控制寄存器等。

数据寄存器用于存放待发送或接收的数据,状态寄存器用于表示当前的通信状态,控制寄存器用于配置通信的参数,如波特率、数据位数、停止位等。

2. SPI寄存器(串行外设接口寄存器),SPI是一种常用的串行通信协议,它使用一组寄存器来控制和配置串行通信的参数。

SPI寄存器通常包括控制寄存器、状态寄存器、数据寄存器等。

控制寄存器用于配置通信的参数,如时钟极性、时钟相位等,状态寄存器用于表示当前的通信状态,数据寄存器用于存放待发送或接收的数据。

3. I2C寄存器(串行外设接口寄存器),I2C是一种常用的串行通信协议,它使用一组寄存器来控制和配置串行通信的参数。

I2C寄存器通常包括控制寄存器、状态寄存器、数据寄存器等。

控制寄存器用于配置通信的参数,如时钟频率、地址模式等,状态寄存器用于表示当前的通信状态,数据寄存器用于存放待发送或接收的数据。

4. USART寄存器(通用同步异步收发器寄存器),USART是一种常用的串行通信协议,它结合了UART和SPI的特点,使用一组寄存器来控制和配置串行通信的参数。

USART寄存器通常包括数据寄存器、状态寄存器、控制寄存器等。

数据寄存器用于存放待发送或接收的数据,状态寄存器用于表示当前的通信状态,控制寄存器用于配置通信的参数,如波特率、数据位数、停止位等。

这些寄存器在串行通信编程中起着重要的作用,通过对这些寄存器的配置和读取,可以实现串行通信的各个功能和特性。

在编程中,我们需要根据具体的硬件和通信协议,对这些寄存器进行合适的设置,以实现可靠和高效的串行通信。

串口uart的寄存器功能

SCON0:UART0 控制寄存器R/W R/W R/W R/W R/W R/W R/W R/W 复位值SM00/FE0 SM10/RXOV0 SM20/TXCOL0 REN0 TB80 RB80 TI0 RI0 00000000位7 位6 位5 位4 位3 位2 位1 位0(可位寻址)SFR地址:0x98位7-6:这些位的功能由PCON 中的SSTAT0 位决定。

如果SSTAT0 为逻辑‘1’,这些位是UART0 的状态指示位,见20.3 节。

如果SSTAT0 为逻辑‘0’,这些位选择串行口的工作方式。

SM00-SM10:串行口工作方式SM00 SM10 方式0 0 方式0:同步方式0 1 方式1:8 位UART,可变波特率1 0 方式2:9 位UART,固定波特率1 1 方式3:9 位UART,可变波特率位5:SM20:多处理器通信允许如果SSTAT0 为逻辑‘1’,该位是UART0 的状态指示位,见20.3 节。

如果SSTAT0 为逻辑‘0’,该位的功能取决于串行口的工作方式。

方式0:无作用。

方式1:检查有效停止位0:停止位的逻辑电平被忽略。

1:只有当停止位为逻辑电平1 时RI0 激活。

方式2 和方式3:多机通信允许0:第九位的逻辑电平被忽略。

1:只有当第九位为逻辑1 并且接收到的地址与UART0 地址或广播地址匹配时RI0 才被置位并产生中断。

位4:REN0:接收允许该位允许/禁止UART0 接收。

0:UART0 接收禁止1:UART0 接收允许位3:TB80:第九发送位该位的逻辑电平被赋值给方式2 和3 的第九发送位。

在方式0 和1 中未用。

跟据需要用软件置位或清0。

位2:RB80:第九接收位该位被赋值为方式2 和3 中第九接收位的逻辑电平。

在方式1,如果SM20 为逻辑0,则RB80 被赋值为所接收到的停止位的逻辑电平。

RB80 在方式0 中未用。

位1:TI0:发送中断标志当UART0 发送完一个字节数据时(方式0 时是在发送完第8 位后,其它方式在停止位的开始)该位被硬件置1。

UART寄存器介绍

UART寄存器介绍UART(通用异步收发器)是一种常用的串行通信接口,可以实现计算机与外部设备之间的数据传输。

在UART的工作过程中,寄存器是起着重要作用的,它们用于控制和管理数据的收发、存储和传输。

本文将介绍常用的UART寄存器,并详细说明它们的功能和用途。

1.UART状态寄存器(USR):UART状态寄存器用于存储UART当前的状态信息,包括数据收发状态、错误标志等。

常见的状态标志位包括接收缓冲区满(RXF)标志、发送缓冲区空(TXE)标志、奇偶校验错误(PERR)标志、帧错误(FERR)标志等。

通过读取该寄存器的状态位,可以实时监测UART的状态。

2.数据寄存器(DR):数据寄存器用于存储UART接收和发送的数据。

当UART接收到数据时,数据将存储在该寄存器中;当UART发送数据时,数据将从该寄存器中传输出去。

通过读取和写入该寄存器,可以实现数据的收发操作。

3.波特率寄存器(BAUD):波特率寄存器用于设置UART的数据传输速率,即波特率。

波特率是指UART每秒钟发送或接收的数据位数。

通过修改该寄存器的值,可以调整UART的波特率,以适应不同的数据传输需求。

4.控制寄存器(CR):控制寄存器用于设置和控制UART的工作模式和功能。

常见的控制位包括发送使能(TXE)位、接收使能(RXE)位、奇偶校验使能(PAREN)位、奇偶校验选择(PSEL)位等。

通过设置和清除这些位的值,可以实现UART的各种功能配置。

5.时钟寄存器(CLK):时钟寄存器用于设置UART的时钟源和时钟分频系数,从而控制UART的时钟频率。

通过调整该寄存器的值,可以改变UART时钟的频率,以满足不同的通信需求。

6.中断使能寄存器(IER):中断使能寄存器用于设置UART的中断功能。

通过设置该寄存器的中断使能位,可以开启或关闭UART的中断功能。

常见的中断使能位包括接收中断使能(RXIE)位、发送中断使能(TXIE)位、错误中断使能(ERIE)位等。

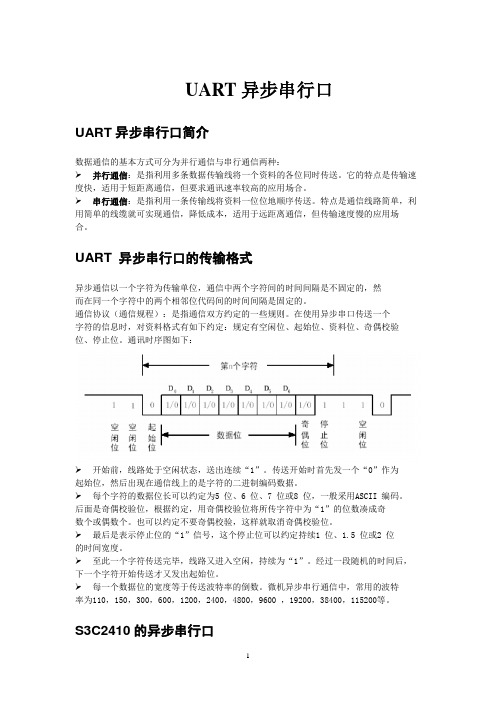

UART串行口简介

UART异步串行口UART异步串行口简介数据通信的基本方式可分为并行通信与串行通信两种:并行通信:是指利用多条数据传输线将一个资料的各位同时传送。

它的特点是传输速度快,适用于短距离通信,但要求通讯速率较高的应用场合。

串行通信:是指利用一条传输线将资料一位位地顺序传送。

特点是通信线路简单,利用简单的线缆就可实现通信,降低成本,适用于远距离通信,但传输速度慢的应用场合。

UART 异步串行口的传输格式异步通信以一个字符为传输单位,通信中两个字符间的时间间隔是不固定的,然而在同一个字符中的两个相邻位代码间的时间间隔是固定的。

通信协议(通信规程):是指通信双方约定的一些规则。

在使用异步串口传送一个字符的信息时,对资料格式有如下约定:规定有空闲位、起始位、资料位、奇偶校验位、停止位。

通讯时序图如下:开始前,线路处于空闲状态,送出连续“1”。

传送开始时首先发一个“0”作为起始位,然后出现在通信线上的是字符的二进制编码数据。

每个字符的数据位长可以约定为5 位、6 位、7 位或8 位,一般采用ASCII 编码。

后面是奇偶校验位,根据约定,用奇偶校验位将所传字符中为“1”的位数凑成奇数个或偶数个。

也可以约定不要奇偶校验,这样就取消奇偶校验位。

最后是表示停止位的“1”信号,这个停止位可以约定持续1 位、1.5 位或2 位的时间宽度。

至此一个字符传送完毕,线路又进入空闲,持续为“1”。

经过一段随机的时间后,下一个字符开始传送才又发出起始位。

每一个数据位的宽度等于传送波特率的倒数。

微机异步串行通信中,常用的波特率为110,150,300,600,1200,2400,4800,9600 ,19200,38400,115200等。

S3C2410的异步串行口1S3C2410 的UART(通用异步串行口)单元提供三个独立的异步串行I/O 端口,每个都可以在中断和DMA 两种模式下进行。

UART支持的最高波特率达230.4kbps。

《单片机原理与实践》 UART模块介绍

《单片机原理与实践》Cortex-M4 TM4C1294XL微处理器UART模块的介绍摘要:数据传输的接线方式大体上就是两种:一种是并行接口,一种是串行接口。

本组就串行接口展开研究,所谓串行接口是指数据在有限的几个IO上按照顺序,一位一位的进行传输。

UART、IIC、SPI、CAN、USB等只要是串行传输的接口,都是串口的一种,本文重点讨论的是其中的UART口。

一.UART定义通用异步收发器(Universal Asynchronous Receiver/ Transmitter, UART)是一个异步的串行通信接口。

UART模块将处理器内部的并行数据转换为串行数据,通过串行总线UnTX以异步通信的方式发送出去;另一方面它也可以接收UnRX 总线上的串行数据,转换为并行数据后返回给处理器进行处理。

异步模式是一种常用的通信方式,相对于同步模式,异步模式不需要一个专门的时钟信号来控制数据的收发,因此发送数据时位与位的间隙可以任意改变。

UART总线采用双向通信,可以实现全双工的发送和接收。

嵌入式设计中,UART用来与计算机或其他设备进行通信。

二.UART的优点这种通信方式使用的数据线少,在远距离通信中可以节约通信成本,但其传输速度比并行传输低。

它很简单并且能够实现远距离通信。

比如IEEE488定义并行通行状态时,规定设备线总长不得超过20米,并且任意两个设备间的长度不得超过2米;而对于串口而言,长度可达1200米。

通信使用3根线完成:(1)地线,(2)发送,(3)接收。

由于串口通信是异步的,端口能够在一根线上发送数据同时在另一根线上接收数据。

串口通信最重要的参数是波特率、数据位、停止位和奇偶校验。

对于两个进行通信的端口,这些参数必须匹配。

三.UART与IIC、SPI的区别1、UART就是两线,一根发送一根接收,可以全双工通信,线数也比较少。

数据是异步传输的,对双方的时序要求比较严格,通信速度也不是很快。

uart dma编程案例

uart dma编程案例UART(通用异步收发器)是一种常见的串行通信接口,而DMA (直接内存存取)是一种用于数据传输的高效方式。

在嵌入式系统中,使用DMA来处理UART通信可以减轻CPU负担,提高系统整体性能。

下面我将从UART和DMA的基本原理、相关寄存器的配置以及一个简单的编程案例来回答你的问题。

首先,让我们简要了解一下UART和DMA的基本原理。

UART是一种异步串行通信协议,它通过发送和接收数据位来进行通信。

DMA是一种用于数据传输的技术,它可以在不需要CPU干预的情况下直接在外设和内存之间传输数据。

在进行UART DMA编程时,首先需要配置UART和DMA的相关寄存器。

对于大多数嵌入式系统,这涉及到设置GPIO引脚、时钟、波特率、数据位和停止位等UART参数,以及配置DMA通道、传输方向、数据宽度等DMA参数。

下面是一个简单的UART DMA编程案例,假设我们要从UART接收数据并通过DMA传输到内存中:1. 首先,配置UART相关寄存器,包括GPIO引脚、时钟、波特率、数据位和停止位等参数。

2. 然后,配置DMA相关寄存器,包括DMA通道、传输方向、数据宽度等参数。

3. 初始化DMA传输的目的地址为内存地址。

4. 启动UART接收,并配置DMA开始传输。

5. 当DMA传输完成时,触发DMA传输完成中断,并在中断服务程序中处理接收到的数据。

这只是一个简单的示例,实际的UART DMA编程可能涉及更多的细节和错误处理。

在实际的项目中,还需要考虑数据的完整性、错误处理、中断处理等方面。

总的来说,UART DMA编程需要深入理解UART和DMA的工作原理,以及相关寄存器的配置方法。

同时,需要注意处理好数据的完整性和错误处理。

希望这个回答能够帮助你更好地理解UART DMA编程。

DMA和UART学习笔记(嵌入式)

DMA和UART学习笔记一、DMA定义DMA(直接存储器存取)是一种完全由硬件执行数据交换的工作方式。

它由DMA控制器而不是CPU控制在存储器和存储器、存储器和外设之间的批量数据传输。

二、DMA传输过程(1)DMA请求。

CPU初始化DMA控制器,外设(1/O接口)发出DMA请求。

(2)DMA响应DMA控制器判断DMA请求的优先级及屏蔽,向总线仲裁器提出总线请求。

当CPU执行完当前总线周期时,可释放总线控制权。

此时,总线仲裁器输出总线应答,表示DMA已经响应,DMA控制器从CPU接管对总线的控制,并通知外设开始DMA传输。

(3)DMA传输。

DMA数据以规定的传输单位(通常是字)传输,每个单位的数据传送完成后,DMA控制器修改地址,并对传送单位的个数进行计数,继而开始下一个单位数据的传送,如此循环往复,直至达到预先设定的传送单位数量为止。

(4)DMA结束。

当规定数量的DMA数据传输完成后,DMA控制器通知外设停止传输,并向CPU发送一个信号(产生中断或事件)报告DMA数据传输操作结束,同时释放总线控制权。

三、STM32F103的DMA工作原理从微观上看,DMA模块由AHB从设备、仲被器和若干个通道(DMA1有7调通道DMA2有5条通道)等部分组成。

从宏观上看,DMA控制器和Cortex-M3内核共享系统数据总线。

当CPU和DMA同时访问相同的目标(存储器或外设)时,DMA请求会暂停CPU访问系统总线达若干个周期,总线钟裁器执行循环调度,保证CPU至少可以得到一半的系统总线(存储器或外设)带宽。

四、STM32的USARTSTM32F103系列微控制器中的UART模块被称为USART。

从名称上看,相比UART,多了一个字母S,它代表Synchronous。

因此,STM32F103系列微控制器内部集成的USART模块在具备UART异步全双工串行通信传输基本功能的同时,还具有同步单向通信的功能。

STM32F103系列微控制器的USART还可以支持多处理器通信、LIN(局部互联网)协议、智能卡协议、ITDASIR编码/解码等。

STM32学习笔记,定时器,PWM,ADC,UART,DMA

RCC_APB2Periph_GPIOC | RCC_APB2Periph_GPIOD,\ ENABLE); //启动 AFIO RCC_APB2PeriphClockCmd(RCC_APB2Periph_AFIO, ENABLE); //启动 TIM1 RCC_APB2PeriphClockCmd(RCC_APB2Periph_TIM1, ENABLE);

//Step2. GPIO 做相应设置,为 AF 输出 //PA.8/9 口设置为 TIM1 的 OC1 输出口 GPIO_InitStructure.GPIO_Pin = GPIO_Pin_8 | GPIO_Pin_9; GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF_PP; GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz; GPIO_Init(GPIOA, &GPIO_InitStructure);

}

关于 TIM 的操作,要注意的是 STM32 处理器因为低功耗的需要,各模块需要分别独立开启时钟,所以, 一定不要忘记给用到的模块和管脚使能时钟,因为这个原因,浪费了我好多时间阿~~!

STM32 笔记(二)TIM 模块产生 PWM 这个是 STM32 的 PWM 输出模式,STM32 的 TIM1 模块是增强型的定时器模块,天生就是为电机控制而生,可 以产生 3 组 6 路 PWM,同时每组 2 路 PWM 为互补,并可以带有死区,可以用来驱动 H 桥。

uart接收 dma原理

UART(Universal Asynchronous Receiver/Transmitter)是一种常见的串行通信协议,用于异步传输数据。

DMA(Direct Memory Access)是一种数据传输方式,允许外设直接访问内存,而不需要经过CPU。

在UART接收中,DMA的原理可以简要概括为以下几点:

1. 数据传输:当UART接收到数据时,DMA控制器会接收到这个信号,并自动开始将接收到的数据从UART接口传输到指定的内存区域。

2. 不占用CPU资源:在DMA传输过程中,CPU可以继续执行其他任务,而不需要对数据传输进行干预。

这大大减轻了CPU的负担,提高了系统的整体性能。

3. 自动传输:DMA控制器会自动处理数据的传输,包括数据的打包、解包、校验等。

这使得数据的传输更加可靠和高效。

4. 中断处理:当DMA传输完成时,会产生一个中断信号给CPU。

CPU可以响应这个中断,并处理接收到的数据。

这样,数据传输和处理可以并行进行,提高了系统的效率。

5. 优先级和通道管理:DMA控制器具有多个数据流和通道,可以配置不同的优先级和通道,以满足不同的数据传输需求。

这使得DMA传输更加灵活和高效。

总之,在UART接收中,DMA的原理是利用DMA控制器自动完成数据的传输和处理,从而释放CPU资源,提高系统的整体性能和效率。

协议中UART的两种模式

^^…… 协议栈中 UART 有两种模式: 1、中断 2、DMA 对于这两种模式具体运用在哪一步 ,纠结了很久.通过 UART 配置结构: typedef struct { uint8 *rxBuf; uint8 rxHead; uint8 rxTail; uint8 rxMax; uint8 rxCnt; uint8 rxTick; uint8 rxHigh; uint8 *txBuf; #if HAL_UART_BIG_TX_BUF uint16 txHead; uint16 txTail; uint16 txMax; uint16 txCnt; #else uint8 txHead; uint8 txTail;

PDF 文件使用 "pdfFactory Pro" 试用版本创建

/************************************** 中断函数完成了把 U0DBUF 里一字节的数据传送到 rxBuf[ ]存储空间去.这里 rxHead 是指 向 rxBuf[ ]的指针,看单词像是指在数组的头,其实应理解为 rxBuf[ ]接收数据的个数(以 字节为单位).rxMax 是 rxBuf[ ]可以存储最大字节数,为128.而后面当用 HalUARTRead() 来读取 rxBuf[ ]时,rxTail 应理解为 rxBuf[]转移出去数据的个数 (同样以字节为单位).那数 据传送到 rxBuf[ ]存储空间去后呢?先看下 pollISR() *****************************************************************************/ //大概每200ms 调用 pollISR()函数.当串口 UxDBUF 接收到一字节数据产生中断,在中断 //程序中把 UxDBUF 中数据传送到 rxbuf[ ]中(这有个坎要跨过来,pollISR()200ms 才被调 用一次, 而不是每次中断后都调用一次 , 如果串口接收的是大的数据包, 则200ms 内 rxbuf[ ] 已经接收了约48字节(这个后面分析),中断了48次??.当然如果串口没有接收到数据,也就 是说没有发生串口接收中断,cfg 应为是为空的,则 cnt=0).此后 pollISR()进行轮询,主要 是重置超时时间和计算 rxbuf[ ]还有多少数据没有读走(即 cnt).然后再跳回到 HalUARTPoll()函数进行下一步处理. static void pollISR( uartCfg_t *cfg ) { uint8 cnt = UART_RX_AVAIL( cfg );//计算 rxBuf[]中还有多少数据没有读出(以字节为 单位) if ( !(cfg->flag & UART_CFG_RXF) ) //UART_CFG_RXF:Rx flow is disabled.rx 流控 制未关闭 { // If anything received, reset the Rx idle timer. //如果又有新的数据接收到,则重置超时时间 if ( cfg->rxCnt != cnt ) { cfg->rxTick = HAL_UART_RX_IDLE; cfg->rxCnt = cnt;

芯片驱动原理

芯片驱动原理芯片驱动原理芯片驱动是指通过软件控制硬件芯片的工作,实现对设备的控制和管理。

芯片驱动是计算机系统中非常重要的一部分,它直接影响着设备的性能和稳定性。

芯片驱动的原理主要包括以下几个方面:1. 硬件接口芯片驱动需要通过硬件接口与设备进行通信。

硬件接口包括物理接口和逻辑接口两部分。

物理接口是指芯片与设备之间的物理连接方式,例如USB、PCI、SATA等接口。

逻辑接口是指芯片与设备之间的通信协议,例如SPI、I2C、UART等协议。

2. 软件控制芯片驱动需要通过软件控制芯片的工作。

软件控制包括驱动程序的编写和操作系统的支持。

驱动程序是指控制芯片工作的软件程序,它需要与操作系统进行交互,通过操作系统提供的接口实现对芯片的控制。

操作系统的支持是指操作系统提供的芯片驱动框架,包括设备管理、中断处理、内存管理等功能。

3. 芯片寄存器芯片驱动需要通过访问芯片寄存器来控制芯片的工作。

芯片寄存器是指芯片内部的寄存器,用于存储芯片的状态和控制信息。

芯片驱动需要通过读写芯片寄存器来实现对芯片的控制。

4. 中断处理芯片驱动需要通过中断处理来响应设备的事件。

中断是指设备向芯片发出的信号,用于通知芯片设备的状态发生了变化。

芯片驱动需要通过中断处理程序来响应设备的事件,并进行相应的处理。

5. DMA传输芯片驱动需要通过DMA传输来实现高速数据传输。

DMA是指直接内存访问,它可以实现芯片与内存之间的高速数据传输,提高数据传输效率。

总之,芯片驱动是计算机系统中非常重要的一部分,它直接影响着设备的性能和稳定性。

芯片驱动的原理包括硬件接口、软件控制、芯片寄存器、中断处理和DMA传输等方面。

只有深入理解芯片驱动的原理,才能编写出高效、稳定的芯片驱动程序,提高设备的性能和稳定性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

DMA 初始源寄存器DMA 初始源控制寄存器寄存器 地址 读/写描述复位值DISRCC0 0x4B000004 读/写 DMAn 初始源控制寄存器。

位[1]:0—源数据在AHB 总线上 1—源数据在APB 总线上 位[0]:0—传送数据后,源地址增加 1—地址固定不变0x0000 0000DISRCC1 0x4B000044 DISRCC2 0x4B000084 DISRCC30x4B0000C4DMA 初始目标地址寄存器寄存器 地址 读/写描述复位值DIDST0 0x4B00 0008 读/写 DMA0初始目标地址寄存器 0x0000 0000 DIDST1 0x4B00 0048 DMA1初始目标地址寄存器 DIDST2 0x4B00 0088 DMA2初始目标地址寄存器 DIDST30x4B00 00C8DMA3初始目标地址寄存器DMA 初始目标控制寄存器寄存器 地址 读/写描述复位值DIDSTC00x4B00 000C 读/写 DMAn 初始目标控制寄存器。

位[1]:0—目标在AHB 总线(先进高性能总线)上1—目标在APB 总线(先进外围总线)上 位[0]:0—传送数据后,目标地址增加 1—地址固定不变0x0000 0000DIDSTC10x4B00 004C DIDSTC20x4B00 008C DIDSTC30x4B00 00CCDMA 控制寄存器寄存器 地址 读/写描述复位值DCON0 0x4B00 0010 读/写 DMA0控制寄存器 0x0000 0000 DCON1 0x4B00 0050 DMA1控制寄存器 DCON2 0x4B00 0090 DMA2控制寄存器 DCON30x4B00 00D0DMA3控制寄存器寄存器 地址 读/写描述复位值DISRC0 0x4B00 0000 读/写 DMA0初始源寄存器 0x0000 0000 DISRC1 0x4B00 0040 DMA1初始源寄存器 DISRC2 0x4B00 0080 DMA2初始源寄存器 DISRC30x4B00 00C0DMA3初始源寄存器DMA(DCONn)控制寄存器的位描述DCONn 位描述DMD_HS [31] 选择请求模式或是握手模式。

0:请求模式1:握手模式SYNC [30] 选择同步模式0: DREQ和DACK与APB时钟同步1: DREQ和DACK与AHB时钟同步INT [29] 当计数器到达0时是否使能中断。

0:禁止中断1:使能中断TSZ [28] 选择传输单位的大小。

0:单位传输1:长度为4的猝发式传输SERVMODE [27] 选择服务模式。

0:单个服务模式1:整体服务模式HWSRCSEL Advanced RISC Machines [26:24] 为DMA设置DMA请求源。

DCON0: 000—nXDREQ0 001—UART0 010—SDI011—定时器100—USB设备EP1DCON1: 000—nXDREQ1 001—UART1 010—I2SSDI011—SPI 100—USB设备EP2DCON2: 000—I2SSDO 001—I2SSDI 010—SDI011—定时器100—USB 设备EP3DCON3: 000—UART2 001—SDI 010—SPI011—定时器100—USB设备EP4SWHW_SEL [23] 在DMA软件请求源和硬件请求源之间选择。

0:软件请求模式,DMA通过设置DMASKTRIG寄存器SW_TRIG位触发1:硬件请求模式,DMA通过设置该寄存器的HWSRCSEL位触发。

RELOAD [22] 当前计数器值等于零以后是否重新加载。

0:自动加载1:DMA通道关闭,不重新加载DSZ [21:20] 传输数据的大小。

00:字节01:半字10:字11:保留TC [19:0] 初始化计数器,在这里设置计数器的值。

DMA状态寄存器寄存器地址读/写描述复位值DSTAT0 0x4B00 0014只读DMAn计数寄存器。

位[21:20]:0—DMA控制器就绪1—DMA控制器忙位[19:0]:传输计数的当前值0x0000 0000DSTAT1 0x4B00 0054 DSTAT2 0x4B00 0094 DSTAT3 0x4B00 00D4DMA当前源寄存器寄存器地址读/写描述复位值DCSRC0 0x4B00 0018只读DMA0当前源寄存器0x0000 0000DCSRC1 0x4B00 0058 DMA1当前源寄存器DCSRC2 0x4B00 0098 DMA2当前源寄存器DCSRC3 0x4B00 00D8 DMA3当前源寄存器DMA(直接存储器存取)当前目标寄存器寄存器地址读/写描述复位值DCDST0 0x4B00 001C只读DMA0当前目标寄存器0x0000 0000DCDST1 0x4B00 005C DMA1当前目标寄存器DCDST2 0x4B00 009C DMA2当前目标寄存器DCDST3 0x4B00 00DC DMA3当前目标寄存器DMA(Direct Memory Access)屏蔽触发寄存器寄存器地址读/写描述复位值DMASKTRIG0 0x4B00 0020读/写DMAn屏蔽触发寄存器。

位[2]:STOP位,停止DMA操作1:当前原子传输操作结束后DMA停止。

如果当前没有原子传输操作,DMA立即停止,CURR_TC将取值为0。

位[1]:ON_OFF位,DMA通道开关位0:通道关闭,忽略DMA请求。

1:通道打开。

位[0]:SW_TRIG位,DMA通道通过软件请求模式触发1:对这个DMA控制器请求一次DMA操作。

注:这个位只有在DCONn[23]置1并且ON_OFF位也置1时才能生效。

当DMA操作开始后,本位自动清0。

0x0000 0000DMASKTRIG1 0x4B00 0060 DMASKTRIG2 0x4B00 00A0 DMASKTRIG3 0x4B00 00E0UARTUART行控制寄存器(推荐使用值为0x3)寄存器地址读/写描述复位值ULCON00x5000 0000读/写UART通道0行控制寄存器0x00ULCON10x5000 4000UART通道1行控制寄存器ULCON20x5000 8000UART通道2行控制寄存器UART行控制寄存器(ULCONn)位描述位描述[7] 保留[6] 红外/正常模式选择。

0:正常模式,1:红外模式[5:3] 奇偶校验模式选择。

0xx :无奇偶校验;100:奇校验;101:偶校验 110:强制校验/校验1;111强制校验/校验0[2] 停止位选择。

0:1个停止位;1:2个停止位[1:0] 字长。

00:5位; 01:6位; 10:7位; 11:8位UART控制寄存器(推荐使用值为0x245)寄存器地址读/写描述复位值UCON00x5000 0004读/写UART通道0控制寄存器0x00UCON10x5000 4004 UART通道1控制寄存器UCON20x5000 8004 UART通道2控制寄存器UART控制寄存器(UCONn)位描述位描述[10] 选择使用的时钟。

0:使用PCLK;1:使用UEXTCLK[9] 发送中断请求类型。

0:脉冲;1:电平[8] 接收中断请求类型。

0:脉冲;1:电平[7] 使能/禁止Rx超时中断。

0:禁止;1:使能[6] 使能/禁止UART错误中断。

0:禁止;1:使能[5] 回送模式选择。

0:正常模式;1:回送模式[4] 保留。

[3:2] 确定将Tx数据写入发送缓冲寄存器的模式。

00:禁止;01:中断请求或查询模式;10:DMA0请求(仅UART0),DMA3请求(仅UART2);11:DMA1请求(仅UART1)[1:0] 确定从UART接收缓冲寄存器读数据的模式。

00:禁止;01:中断请求或查询模式;10:DMA0请求(仅UART0),DMA3请求(仅UART2)11:DMA1请求(仅UART1)UART FIFO控制寄存器(推荐使用值为0x0)寄存器地址读/写描述复位值UFCON0 0x5000 0008读/写UART通道0FIFO控制寄存器0x0UFCON10x5000 4008UART通道1FIFO控制寄存器UFCON20x5000 8008UART通道2FIFO控制寄存器UART FIFO控制寄存器(UFCONn)位描述位描述[7:6] 确定发送FIFO的触发条件。

00:空;01:4字节;10:8字节;11:12字节[5:4] 确定接收FIFO的触发条件。

00:4字节;01:8字节;10:12字节;11:16字节[3] 保留[2] Tx FIFO复位位,该位在FIFO复位后自动清除。

0:正常;1:Tx FIFO复位[1] RX FIFO复位位,该位在FIFO复位后自动清除。

0:正常;1:Rx FIFO复位[0] FIFO使能位。

0:禁止;1:使能UART Modem控制寄存器(推荐使用值为0x0)寄存器地址读/写描述复位值UMCON0 0x5000 000C 读/写UART通道0Modem控制寄存器0x0 UMCON1 0x5000 400C 读/写UART通道1Modem控制寄存器0x0 保留0x5000 800C —保留未定义UART Modem控制寄存器(UMCONn)位描述位描述取指译码执行[7:5] 保留,这些位必须是0[4] AFC使能位。

0:禁止;1:使能[3:1] 保留,这些位必须是0[0] 如果AFC使能位为1,则忽略该位,此时S3C2310A将自动控制nRTS;如果AFC使能位为0,nRTS必须由软件控制。

0:高电平(禁止nRTS);1:低电平(激活nRTS)S3C2410A的A/D转换器1、ADC控制寄存器(ADCCON)该是一个可读/写的寄存器,地址为0x5800 0000,复位后的初始值为0x3FC4ADC控制寄存器(ADCCON)位描述ADCCON位名位描述初始状态0 ECFLG[15]A/D转换状态标志(只读)0:A/D转换中1:A/D转换结束0 PRSCEN[14]A/D转换器预分频因子使能0:禁止1:使能PRSCVL[13:6]A/D转换器预分频因子值设置0xFF数据取值范围:1~2550 SEL-MUX[5:3]模拟输入通道选择000:AIN0;001:AIN1;010:AIN2;011:AIN3;100AIN4;101:AIN5;110:AIN6;111:AIN71 STDBM[2]休眠模式选择0:正常模式1:休眠模式0 READ-START[1]A/D转换通过读来启动0:通过读操作关闭1:通过读操作启动ENABLE-START[0]A/D转换通过将该位设置1来启动,如果READ-START位为1,则该位无效0:关闭1:A/D转换开始,之后该位自动清除2、ADC触摸屏控制寄存器(ADCTSC)该寄存器是一个可读/写的寄存器,地址为0x5800 0004,复位后的初始值为0x058。