用真正差分激励信号来测试平衡器件

[课程]传输线巴伦的原理设计、制作及测试

![[课程]传输线巴伦的原理设计、制作及测试](https://img.taocdn.com/s3/m/0006ce740a1c59eef8c75fbfc77da26925c59613.png)

传输线平衡器(巴伦)的原理、设计、制作及测试一、平衡器(巴伦)的由来平衡器即Balancing Device,其主要作用是完成由单端传输(如:同轴线、微带线等)变换为差分传输(如:半波振子天线,推挽电路等)之间的变换,又称为平衡-不平衡变换器即Balance-Unbalance,英文将其合并缩写成一个新词Balun,音译为巴伦。

以下文中所提到的平衡器、平衡-不平衡变换器、巴伦,都是指这一类器件。

巴伦在无线电中有着广泛的用途,由于其原理结构多种多样,并且可以互相组合,使得许多朋友在自制巴伦时有无从下手的感觉,哪种结构适合?如何选择材料?如何计算制作参数?如何衡量巴伦的性能?对于我们业余爱好者,主要就是用在天线的馈电和高频功放中,完成平衡-不平衡及阻抗变换的作用,工作在短波1.8MHZ~30MHZ,并要求取材和制作容易。

结合我对巴伦的认识理解,认为传输线结构的巴伦,更适合短波通信,其性能好、取材方便、制作容易,但其理论不易理解,造成很多朋友将其搞成了磁耦合变压器结构,出现频带窄、功率容量小、驻波不平坦的问题,结果当然达不到传输线变换器的效果。

下面就我个人对传输线变换器的粗浅理解,简单描述一下做巴伦的情况,如需要更深入的了解可以参考有关文献资料,有不当之处,还请各位前辈指正,谢谢!二、传输线平衡器(巴伦)的简单原理平衡器有很多种,按平衡条件可以分为四大类:扼流式(扼制不平衡电流)、对称式(对地阻抗平衡)、倒相式(电压倒相)、磁耦合式(电流共扼)。

我这里主要描述一下基于传输线变换器的平衡-不平衡变换,同时具备阻抗变换作用的巴伦,兼有扼流式和磁耦合式的特征。

传输线变换器的结构如上图,它是在高频磁环上缠绕一组或几组传输线,利用不同的连接方法来完成阻抗变换和平衡-不平衡变换作用。

能量从变换器的始端到终端是通过传输线的分布电容、分布电感以及电磁能量交换的形式来传送的,这和通常的绕匝变压器不同,它克服了绕匝变压器在高频时由于线圈的分布电容所带来的不利影响,改善了高频特性。

LVDS信号原理及相关介绍 2013年7月2日

所以,LVDS具有高速、超低功耗、低噪声和低成本的优良特性。

3、差分信号抗噪特性 :

从差分信号传输线路上可以看出,若是理想状况,线路没有干扰时, 在发送侧,可以形象理解为:

噪声被抑止掉。

上述可以形象理解差分方式抑止噪声的能力。在实际芯片 中,是在噪声容限内,采用“比较”及“量化”来处理的。

LVDS接收器可以承受至少±1V的驱动器与接收器之间的地 的电压变化。由于LVDS驱动器典型的偏置电压为+1.2V,地的 电压变化、驱动器偏置电压以及轻度耦合到的噪声之和,在接 收器的输入端相对于接收器的地是共模电压。这个共模范围是: +0.2V~+2.2V。建议接收器的输入电压范围为:0V~+2.4V。

最基本的LVDS器件就是LVDS驱动器和接收器。LVDS的驱动器由驱动差分线对

的电流源组成,电流通常为3.5 mA。LVDS接收器具有很高的输入阻抗,因此驱

动器输出的大部分电流都流过100 Ω 的匹配电阻,并在接收器的输入端产生大 约350 mV的电压。当驱动器翻转时,它改变流经电阻的电流方向,因此产生有 效的逻辑“1”和逻辑“0”状态。

抑止共模噪声是DS(差分信号)的共同特性,采用差分平 衡传输,由于其电平幅度大,更不容易受干扰,适合工业现场 不太恶劣环境下通讯。

四、LVDS信号Vid的技术要求和测试方法:

五、实际应用中常见问题 :

1、PCB走线要求 :

2、PCB 过孔要求:

一般原则:对于高速信号,尽量减少过孔;信号速度低于 155Mbps,使用过孔也无妨; 对于表面贴片器件,其管脚的LVDS信号走线在PCB表层或者底层, 尽量使用“微带布线”方式,避免使用过孔联接信号; 对于插件器件,由于不使用过孔,其信号线本就可以联接到PCB 的“中间层”,这样一来,尽量使用“带状走线”,其性能更好。

LVDS简介

LVDS原理与应用简介1 LVDS信号介绍LVDS:Low Voltage Differential Signaling,低电压差分信号。

LVDS传输支持速率一般在155Mbps(大约为77MHZ)以上。

LVDS是一种低摆幅的差分信号技术,它使得信号能在差分PCB线对或平衡电缆上以几百Mbps的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗。

IEEE在两个标准中对LVDS信号进行了定义。

ANSI/TIA/EIA-644中,推荐最大速率为655Mbps,理论极限速率为1.923Mbps。

1.1 LVDS信号传输组成TTL TTLLVDS差分接收器图1 LVDS信号传输组成图LVDS信号传输一般由三部分组成:差分信号发送器,差分信号互联器,差分信号接收器。

差分信号发送器:将非平衡传输的TTL信号转换成平衡传输的LVDS信号。

通常由一个IC来完成,如:DS90C031差分信号接收器:将平衡传输的LVDS信号转换成非平衡传输的TTL信号。

通常由一个IC来完成,如:DS90C032差分信号互联器:包括联接线(电缆或者PCB走线),终端匹配电阻。

按照IEEE规定,电阻为100欧。

我们通常选择为100,120欧。

1.2 LVDS信号电平特性LVDS物理接口使用1.2V偏置电压作为基准,提供大约400mV摆幅。

LVDS驱动器由一个驱动差分线对的电流源组成(通常电流为3.5mA),LVDS接收器具有很高的输入阻抗,因此驱动器输出的电流大部分都流过100Ω 的匹配电阻,并在接收器的输入端产生大约350mV 的电压。

电流源为恒流特性,终端电阻在100――120欧姆之间,则电压摆动幅度为:3.5mA * 100 = 350mV ;3.5mA * 120 = 420mV 。

下图为LVDS 与PECL (光收发器使用的电平)电平变化。

图2 LVDS 与PECL 电平图示由逻辑“0”电平变化到逻辑“1”电平是需要时间的。

阻抗测试

PCB的差分阻抗测试技术作者: 周英航上网日期: 2006年11月10日打印版订阅关键字:PCB电路板TDR真差分TDR特征阻抗Coupon为了提高传输速率和传输距离,计算机行业和通信行业越来越多的采用高速串行总线。

在芯片之间、板卡之间、背板和业务板之间实现高速互联。

这些高速串行总线的速率从以往USB2.0、LVDS以及FireWire1394的几百Mbps到今天的PCI-Express G1/G2、SATA G1/G2 、XAUI/2XAUI、XFI的几个Gbps乃至10Gbps。

计算机以及通信行业的PCB客户对差分走线的阻抗控制要求越来越高。

这使PCB生产商以及高速PCB设计人员所面临的前所未有的挑战。

本文结合PCB行业公认的测试标准IPC-TM-650手册,重点讨论真差分TDR测试方法的原理以及特点。

IPC-TM-650手册以及PCB特征阻抗测试背景IPC-TM-650测试手册是一套非常全面的PCB行业测试规范,从PCB的机械特性、化学特性、物理特性、电气特性、环境特性等各方面给出了非常详尽的测试方法以及测试要求。

其中PCB板电气特性要求在第2.5节中描述,而其中的2.5.5.7a(IPC-TM-650官方网站下载链接/4.0_Knowledge/4.1_Standards/test/2-5-5-7a.pdf)则全面的介绍了PCB特征阻抗测试方法和对相应的测试仪器要求,重点包括单端走线和差分走线的阻抗测试。

TDR的基本原理及IPC-TM-650对TDR设备的基本要求1.TDR的基本原理图1是一个阶跃信号在传输线(如PCB的走线)上传输时的示意图。

而传输线是通过电介质与GND分隔的,就像无数个微小的电容的并联。

电信号到达某个位置时,就会令该位置上的电压产生变化,就像是给电容充电。

因此,传输线在此位置上是有对地的电流回路的,因此就有阻抗的存在。

但是该阻抗只有阶跃信号自身才能“感觉到”,这就是我们所说的特征阻抗。

示波器的差分信号测量

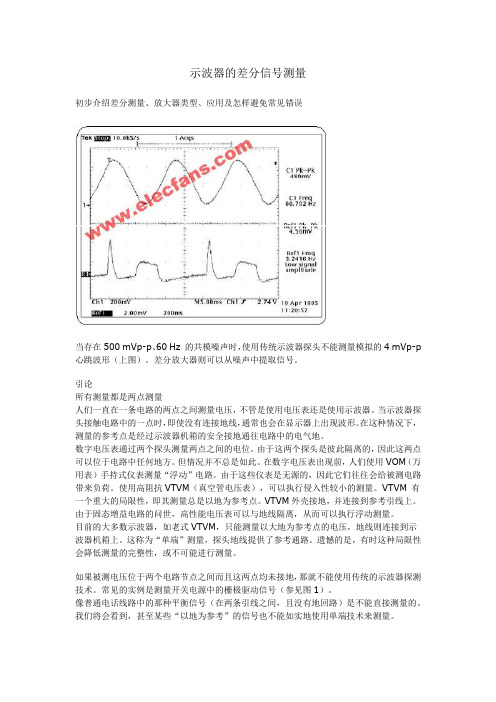

示波器的差分信号测量初步介绍差分测量、放大器类型、应用及怎样避免常见错误当存在500 mVp-p、60 Hz 的共模噪声时,使用传统示波器探头不能测量模拟的4 mVp-p 心跳波形(上图)。

差分放大器则可以从噪声中提取信号。

引论所有测量都是两点测量人们一直在一条电路的两点之间测量电压,不管是使用电压表还是使用示波器。

当示波器探头接触电路中的一点时,即使没有连接地线,通常也会在显示器上出现波形。

在这种情况下,测量的参考点是经过示波器机箱的安全接地通往电路中的电气地。

数字电压表通过两个探头测量两点之间的电位。

由于这两个探头是彼此隔离的,因此这两点可以位于电路中任何地方。

但情况并不总是如此。

在数字电压表出现前,人们使用VOM(万用表)手持式仪表测量“浮动”电路。

由于这些仪表是无源的,因此它们往往会给被测电路带来负荷。

使用高阻抗VTVM(真空管电压表),可以执行侵入性较小的测量。

VTVM 有一个重大的局限性,即其测量总是以地为参考点。

VTVM外壳接地,并连接到参考引线上。

由于固态增益电路的问世,高性能电压表可以与地线隔离,从而可以执行浮动测量。

目前的大多数示波器,如老式VTVM,只能测量以大地为参考点的电压,地线则连接到示波器机箱上。

这称为“单端”测量,探头地线提供了参考通路。

遗憾的是,有时这种局限性会降低测量的完整性,或不可能进行测量。

如果被测电压位于两个电路节点之间而且这两点均未接地,那就不能使用传统的示波器探测技术。

常见的实例是测量开关电源中的栅极驱动信号(参见图1)。

像普通电话线路中的那种平衡信号(在两条引线之间,且没有地回路)是不能直接测量的。

我们将会看到,甚至某些“以地为参考”的信号也不能如实地使用单端技术来测量。

如果地线不成其为地线我们都听说过“接地环路”,书本上教我们避免“接地环路”。

但接地环路是怎样破坏示波器测量的呢?当两条或多条单独的接地通路聚结于两点或多点时,将会产生接地环路。

其结果是导体连成了一个环。

LVDS(低电压差分信号)原理简介

LVDS(低电压差分信号)原理简介1 LVDS信号介绍LVDS:Low Voltage Differential Signaling,低电压差分信号。

LVDS传输支持速率一般在155Mbps(大约为77MHZ)以上。

LVDS是一种低摆幅的差分信号技术,它使得信号能在差分PCB线对或平衡电缆上以几百Mbps的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗。

IEEE在两个标准中对LVDS信号进行了定义。

ANSI/TIA/EIA-644中,推荐最大速率为655Mbps,理论极限速率为1.923Mbps。

1.1 LVDS信号传输组成图1 LVDS信号传输组成图LVDS信号传输一般由三部分组成:差分信号发送器,差分信号互联器,差分信号接收器。

差分信号发送器:将非平衡传输的TTL信号转换成平衡传输的LVDS信号。

通常由一个IC来完成,如:DS90C031差分信号接收器:将平衡传输的LVDS信号转换成非平衡传输的TTL信号。

通常由一个IC来完成,如:DS90C032差分信号互联器:包括联接线(电缆或者PCB走线),终端匹配电阻。

按照IEEE规定,电阻为100欧。

我们通常选择为100,120欧。

1.2 LVDS信号电平特性LVDS物理接口使用1.2V偏置电压作为基准,提供大约400mV摆幅。

LVDS驱动器由一个驱动差分线对的电流源组成(通常电流为3.5mA),LVDS接收器具有很高的输入阻抗,因此驱动器输出的电流大部分都流过100Ω的匹配电阻,并在接收器的输入端产生大约350mV 的电压。

电流源为恒流特性,终端电阻在100――120欧姆之间,则电压摆动幅度为:3.5mA * 100 = 350mV ;3.5mA * 120 = 420mV 。

下图为LVDS与PECL(光收发器使用的电平)电平变化。

图2 LVDS与PECL电平图示由逻辑“0”电平变化到逻辑“1”电平是需要时间的。

由于LVDS信号物理电平变化在0。

射频微波器件测试解决方案

Agilent Measurement Forum

支持外置推动放大器扩展激励功率

• 提供外置推动放大器接入通道

• 支持功率校准消除外置放大器误差, 保证激励信号功率精度

最小输出功率:-95dBm

测试频率:20GHz,输出功率>13dBm

PNA-X网络仪的激励源频谱性能

激励信号频谱纯度高,杂波和谐波抑制性能高

Scopes / Digitizers / VSA Software

校准标准

E5052B 信号源分析仪 Power Sensor, E-Cal, Noise Source

Welcome to the PNA-X

Page 10 January 2009

Agilent网络仪覆盖广阔的测试应用

Amplifier Test

Agilent Measurement Forum

接收机功率压缩点

接收机灵敏度

基于PNA-X的器件测试平台

Agilent Measurement Forum

rear panel

J11

J10

J9

J8

J7

J4

J3

J2

J1

Source 2 (standard) Source 1

OUT 1

Pulse modulator

Agilent Measurement Forum

从 2009年 10 月 开始安捷伦科技推向市场的新的 ENA 系列产品

2 端口和 4 端口两种配置 混频器测量 夹具仿真、嵌入/去嵌入 放大器测量, 等等

E5071C, 9/100 kHz 到 4.5/6.5/8.5 GHz, E5071C

300 kHz 到 14/20 GHz

TDR的基本原理及IPC TM 650TDR的基本要求

为了提高传输速率和传输距离,计算机行业和通信行业越来越多的采用高速串行总线。

在芯片之间、板卡之间、背板和业务板之间实现高速互联。

这些高速串行总线的速率从以往USB2.0、LVDS以及FireWire1394的几百Mbps到今天的PCI-Express G1/G2、SATA G1/G2 、XAUI/2XAUI、XFI的几个Gbps乃至10Gbps。

计算机以及通信行业的PCB客户对差分走线的阻抗控制要求越来越高。

这使PCB 生产商以及高速PCB设计人员所面临的前所未有的挑战。

本文结合PCB行业公认的测试标准IPC-TM-650手册,重点讨论真差分TDR测试方法的原理以及特点。

IPC-TM-650手册以及PCB特征阻抗测试背景IPC-TM-650测试手册是一套非常全面的PCB行业测试规范,从PCB的机械特性、化学特性、物理特性、电气特性、环境特性等各方面给出了非常详尽的测试方法以及测试要求。

其中PCB板电气特性要求在第2.5节中描述,而其中的2.5.5.7a(IPC-TM-650官方网站下载链接/4.0_Knowledge/4.1_Standards/test/2-5-5-7a.pdf)则全面的介绍了PCB特征阻抗测试方法和对相应的测试仪器要求,重点包括单端走线和差分走线的阻抗测试。

TDR的基本原理及IPC-TM-650对TDR设备的基本要求1.TDR的基本原理图1是一个阶跃信号在传输线(如PCB的走线)上传输时的示意图。

而传输线是通过电介质与GND分隔的,就像无数个微小的电容的并联。

电信号到达某个位置时,就会令该位置上的电压产生变化,就像是给电容充电。

因此,传输线在此位置上是有对地的电流回路的,因此就有阻抗的存在。

但是该阻抗只有阶跃信号自身才能“感觉到”,这就是我们所说的特征阻抗。

当传输线上出现阻抗不连续的现象时,在阻抗变化的地方阶跃信号就会产生反射的现象,如果将反射信号进行取样并显示在示波器的屏幕上,就会得出如图2所示的波形,从波形中我们可以看出一条被测试的传输线在不同位置上的阻抗变化。

电子电路设计工程师面试题及答案(精选)

电子电路设计工程师面试题及答案1.请描述一次您在电子电路设计中解决复杂问题的经验。

在我的上一份工作中,我们遇到了一个性能优化的挑战,需要在电路设计中提高信号传输速度。

我通过采用差分信号传输、优化PCB布局以减小信号路径长度,以及使用高速电路设计工具进行仿真和分析,成功提高了系统的整体性能。

2.如何处理设计中的电磁干扰问题,以确保电路的稳定性和抗干扰能力?在面对电磁干扰时,我采用了合适的屏蔽措施,如使用屏蔽罩、优化地线布局,并利用滤波器来降低干扰。

此外,我通过仿真工具进行电磁兼容性分析,以确保电路在实际环境中的稳定性。

3.请详细介绍您在高频电路设计中的经验,特别是在射频设计方面的成就。

在之前的项目中,我负责设计了一套射频前端电路,涉及频率范围较广。

通过合理选择元器件、进行频域仿真和优化,成功实现了对不同频段信号的高效捕获和处理,使系统在复杂环境中表现卓越。

4.如何平衡在电路设计中的功耗和性能,尤其是在移动设备等有限电源环境下?在移动设备电路设计中,我注重优化功耗和性能的平衡。

通过采用低功耗元器件、优化电源管理策略,以及采用动态电压调整技术,成功实现了在有限电源环境下的长时间运行,同时保持了系统的高性能。

5.请描述您在模拟电路设计中解决过的一个挑战,以及您的解决方法。

在之前的项目中,我遇到了一个模拟电路中的非线性问题,导致信号失真。

我通过引入反馈控制、调整电路增益和采用精准的元器件进行替代,成功地解决了信号失真的问题,并提升了整体电路性能。

6.在数字电路设计中,如何确保电路的稳定性和可靠性,尤其是在高温或极端环境下?在数字电路设计中,我采用了工艺上的优化,选择耐高温材料和元器件,以及通过热仿真工具来评估电路在不同温度条件下的性能。

这些措施有效地提高了电路的稳定性和可靠性,确保在极端环境中仍能正常工作。

7.在多层PCB设计中,您是如何优化信号完整性和降低串扰的?我在多层PCB设计中采用分层布局、差分信号传输、地孔的合理设置等手段,以降低信号路径的交叉和减小串扰。

浅谈TDR测试的原理和常见问题

浅谈 TDR 测试的原理和常见问题唐亮 胡海洋本文从 TDR 测试原理,TDR 与网络分析仪测试方法的比较,以及测试 TDR 测试常见的问题进行了全面的 讨论。

结合上述介绍,文章对安捷伦 54754A TDR 测试模块的特点进行了全面总结。

一 TDR 测试原理评价频率响应的最普通的方法是在频域中解 Maxwell 方程。

这个过程能够把系统所有的物理和电气特性都 考虑进去,包括传输线。

因而已经有很多基于此原理的测量方法来帮助电气工程师分析信号完整性。

当和其他测试方法比较时, 时域反射 (TDR: Time Domain Reflector) 可以提供更加直观观察 DUT 的特性。

TDR 使用阶跃信号发生仪和示波器,在被测得传输线上发送一个快速的上升沿,再特定的点上用示波器观 察反射电压波形。

这种技术可以测出传输显得特性阻抗,并显示出每个阻抗不连续点的位置和特性(阻抗、感抗和容抗)。

所有这些信息都是示波器上实时显示。

相对于其他技术,TDR 能够给出更多的关于系统宽带相应的信息。

图1时域反射计工作原理阶跃信号发生器向被测系统产生一个正向的阶跃信号。

该信号沿着传输线向前传输。

如果负载组抗等于传 输线的特性阻抗,将没有信号反射,示波器上能看到的只有发送的阶跃信号。

假如负载存在失配,将有部分的输入信号被反射,示波器上将出现反射信号和输入信号的叠加。

图 2 是一个传输线的测试波形,由此可以看出,对于非连续的阻抗,示波器对应位置将出现变化的波形, 由此我们就能够分析每个中断点的特性。

TDR 测试的典型结果 ・ ・ ・ ・ ・ ・ A: 50 Ohm 电缆 B:微波传输带开始C: 50 Ohm 微波传输带 D: 75 Ohm 微波传输带 E: F: 50 Ohm 微波传输带AB CDEF开路二 TDR 与其他测试方法的比较 最常用的测量传输线和负载的方图 2 时域反射计测试结果法是向系统发送一个正弦波,并观察线上不连续点的波形。

PNA-X产品介绍

● 内置信号合路器,非常方便地实现互调失真测量 (IMD) 和热态下的 S22 测量

● 内置脉冲调制器和脉冲发生器,便于实现脉冲 S 参数 测量

● 内置多路机械开关,可以灵活配置信号路径从而实现 单次连接多项测量; 按照需求可以灵活添加外置的滤波 器、放大器和测试设备 (如: 信号源和频谱分析仪)

● 脉冲射频功能能够用于远场天线测量系统

● 脉冲射频功能可与基于 PNA-X 的毫米波系统结合 使用

● 支持脉冲模式下全 2 端口校准和增强型响应校准

5

/find/pna-x

脉冲射频测试解决方案

脉冲测试面临的工业挑战

针对窄脉冲射频测试的创新技术和 专利技术

随着雷达技术和雷达应用的快速发展,某些雷达需要 越来越窄的脉冲射频信号。

图 3 给出了 PNA-X 与其他传统解决方案的对比。不 难看出,与传统的 8510 或 PNA 解决方案相比,在相同的 占空比下,PNA-X 的动态范围有了明显改善。

动态范围 (dB)

脉冲占空比 (%) 增强的 PNA-X 窄带检测 PNA 窄带检测 8150 窄带检测

图 3.窄带检测性能对比

7

/find/pna-x

PNA-X 结构方框图 (以选件 400、419 和 423 为例)

测试端口 2

内置机械开关可以 非常灵活地根据 测试需求切换 各种激励信号

高性能激励源

出色的灵活性

● 10 MHz 至 13.5/26.5/43.5/50 GHz ● 内置的第二个高性能信号源便于进行互调失真测量、

热态下的 S22 测量和快速的本振扫描测量 ● 高达 +22 dBm 的输出功率和 48 dB 的功率扫描范围 ● 出色的谐波性能 (≤ -60 dBc),大大提高了谐波失真和

mos rg测试原理

mos rg测试原理

Mos Regulator是一种电压稳压器,用于将输入电压稳定为所需的输出电压。

它通过利用负反馈控制系统来保持输出电压不变,在输入电压变化时调整所需的电压。

Mos Regulator的工作原理如下:

1. 输入电压进入Mos Regulator的输入端,经过限流电阻限制电流。

2. 输入电压经过一个差分放大器,与参考电压进行比较,并产生一个误差信号。

3. 误差信号经过一个误差放大器,进行放大,得到一个控制信号。

4. 控制信号进入一个MOSFET(金属氧化物半导体场效应晶体管),通过调整MOSFET的导通程度,来控制输出电压的稳定性。

5. 输出电压通过一个反馈电路回馈给差分放大器,与参考电压进行比较,以确认输出电压是否符合标准。

6. 如果输出电压低于标准值,差分放大器将相应的信号传递给误差放大器,进一步调整MOSFET的导通程度,提高输出电压。

7. 如果输出电压高于标准值,差分放大器也会相应地调整MOSFET的导通程度,降低输出电压。

8. 通过不断调整MOSFET的导通程度,Mos Regulator可以稳定输出电压,使其与参考电压保持一致。

总结:Mos Regulator使用负反馈控制系统来调整MOSFET的导通程度,以稳定输出电压。

S参数的介绍以及一些理解

关于S参数的一些理解无源网络如电阻、电感、电容、连接器、电缆、PCB线等在高频下会呈现射频、微波方面的特性。

S参数是表征无源网络特性的一种模型,在仿真中即用S参数来代表无源网络,在射频、微波和信号完整性领域的应用都很广泛。

本文将从S参数的定义,S参数的表达方式,S参数的特性,混合模式S参数,S参数测量等多个方面介绍S参数的一些最基本的知识。

1,S参数的定义人们都喜欢用一句话来概括一个术语。

譬如用一句话来表达什么是示波器的带宽,笔者概括为:带宽就是示波器前端放大器幅频特性曲线的截止频率点。

如何用一句话来回答什么是S参数呢?笔者在网上搜索了很多关于S参数的文章,现摘录几段关于S参数的定义。

在维基百科上,关于S参数的定义是:Scattering parameters or S-parameters (the elements of a scattering matrix or S-matrix) describe the electrical behaviors of linear electrical networks when undergoing various steady state stimuli by electrical signals. The parameters are useful for electrical engineering, electronics engineering, and communication systems design. 翻译成中文:散射参数或者说S参数描述了线性电气网络在变化的稳态电信号激励时的电气行为。

该参数对于电气工程、电子工程和通信系统的研发是很有用的。

(抱歉,英语水平太差,翻译得很别扭。

)这个定义似乎不够好!在另外一篇文章中的定义是:The S-parameter (Scattering parameter) expresses device characteristics using the degree of scattering when an AC signal is considered as a wave. The word “scattering” is a general term that refers to refl ection back to the source and transmission to other directions.中文含义是:“S参数是利用器件在受到带有“波”特点的AC信号激励下的散射程度来表达器件的特征。

差分信号(DifferentialSignal)

差分信号(DifferentialSignal)差分信号(Differential Signal)在⾼速电路设计中的应⽤越来越⼴泛,电路中最关键的信号往往都要采⽤差分结构设计,什么另它这么倍受青睐呢?在 PCB 设计中⼜如何能保证其良好的性能呢?带着这两个问题,我们进⾏下⼀部分的讨论。

何为差分信号?通俗地说,就是驱动端发送两个等值、反相的信号,接收端通过⽐较这两个电压的差值来判断逻辑状态“0”还是“1”。

⽽承载差分信号的那⼀对⾛线就称为差分⾛线。

差分信号和普通的单端信号⾛线相⽐,最明显的优势体现在以下三个⽅⾯:a.抗⼲扰能⼒强,因为两根差分⾛线之间的耦合很好,当外界存在噪声⼲扰时,⼏乎是同时被耦合到两条线上,⽽接收端关⼼的只是两信号的差值,所以外界的共模噪声可以被完全抵消。

b.能有效抑制 EMI,同样的道理,由于两根信号的极性相反,他们对外辐射的电磁场可以相互抵消,耦合的越紧密,泄放到外界的电磁能量越少。

c.时序定位精确,由于差分信号的开关变化是位于两个信号的交点,⽽不像普通单端信号依靠⾼低两个阈值电压判断,因⽽受⼯艺,温度的影响⼩,能降低时序上的误差,同时也更适合于低幅度信号的电路。

⽬前流⾏的 LVDS(low voltage differential signaling)就是指这种⼩振幅差分信号技术。

对于 PCB ⼯程师来说,最关注的还是如何确保在实际⾛线中能完全发挥差分⾛线的这些优势。

也许只要是接触过 Layout 的⼈都会了解差分⾛线的⼀般要求,那就是“等长、等距”。

等长是为了保证两个差分信号时刻保持相反极性,减少共模分量;等距则主要是为了保证两者差分阻抗⼀致,减少反射。

“尽量靠近原则”有时候也是差分⾛线的要求之⼀。

但所有这些规则都不是⽤来⽣搬硬套的,不少⼯程师似乎还不了解⾼速差分信号传输的本质。

下⾯重点讨论⼀下 PCB 差分信号设计中⼏个常见的误区。

误区⼀:认为差分信号不需要地平⾯作为回流路径,或者认为差分⾛线彼此为对⽅提供回流途径。

cml差分电路讲解

cml差分电路讲解

CML(Current Mode Logic)差分电路是一种用于高速数字信号传输的电路,它采用差分信号传输方式,可以有效地抑制共模噪声和电磁干扰,提高信号的传输质量和可靠性。

下面将对CML差分电路进行简单讲解:

1. 工作原理:CML差分电路由两个对称的差分对组成,每个差分对由一个晶体管和电阻组成。

当输入信号发生变化时,两个差分对中的晶体管会交替导通和截止,从而产生相位相反、幅度相等的差分信号。

由于差分信号的幅度相等、相位相反,因此它们在传输过程中可以相互抵消共模噪声,提高信号的抗干扰能力。

2. 电路结构:CML差分电路通常由输入缓冲器、差分对和输出缓冲器三部分组成。

输入缓冲器的作用是将输入信号进行适当的放大和缓冲,以便更好地驱动差分对。

差分对由两个晶体管和两个电阻组成,其中每个晶体管的基极和发射极之间连接一个电阻。

输出缓冲器的作用是将差分对的输出信号进行适当的放大和缓冲,以便更好地驱动后级电路。

3. 特点:CML差分电路具有高速、低噪声、低失真、低功耗等优点,因此在高速数字信号传输、光纤通信、雷达等领域得到广泛应用。

此外,CML 差分电路还可以通过调节偏置电流来改变输出信号的幅度和直流电平,具有一定的灵活性。

总之,CML差分电路是一种高性能的数字信号传输电路,具有广泛的应用前景。